TIDT244 July 2021

3.5 Voltage Regulation

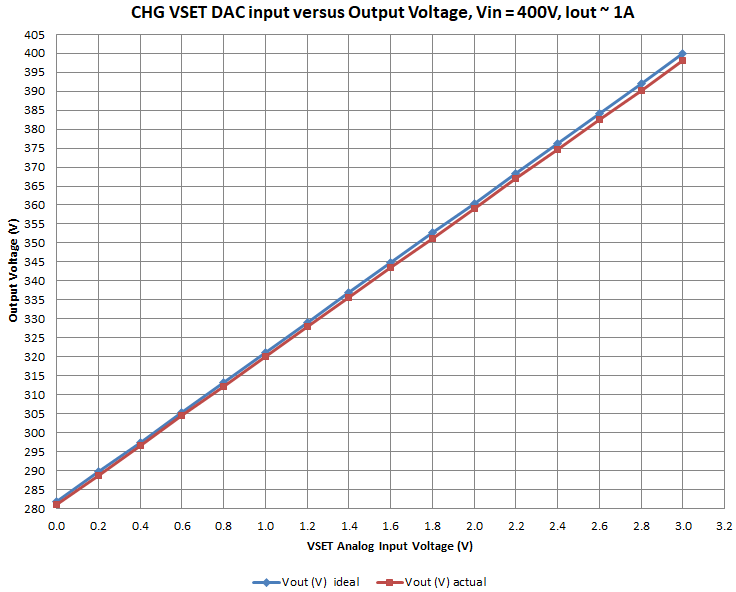

This graph displays the measured output voltage versus CHG VSET DAC at an input voltage of 400 Vdc. A DC voltage ranging from 0 V–3 V is applied at J6 and a constant resistance mode load is used with the resistance equal to VOUT ideal at each setpoint.

Figure 3-9 CHG VSET DAC Accuracy Curve

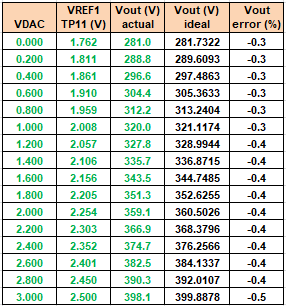

Figure 3-9 CHG VSET DAC Accuracy Curve Figure 3-10 CHG VSET DAC Accuracy Table

Figure 3-10 CHG VSET DAC Accuracy Table