JAJSC24H June 2013 – November 2016 TPS65132

UNLESS OTHERWISE NOTED, this document contains PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Detailed Description

-

9 Application and Implementation

- 9.1 Application Information

- 9.2

Typical Applications

- 9.2.1

Low-current Applications (≤ 40 mA)

- 9.2.1.1 Design Requirements

- 9.2.1.2 Detailed Design Procedure

- 9.2.1.3 Application Curves

- 9.2.2

Mid-current Applications (≤ 80 mA)

- 9.2.2.1 Design Requirements

- 9.2.2.2 Detailed Design Procedure

- 9.2.2.3 Application Curves

- 9.2.3 High-current Applications (≤ 150 mA)

- 9.2.1

Low-current Applications (≤ 40 mA)

- 10Power Supply Recommendations

- 11Layout

- 12デバイスおよびドキュメントのサポート

- 13メカニカル、パッケージ、および注文情報

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

サーマルパッド・メカニカル・データ

- RVC|20

発注情報

1 特長

- 入力電圧範囲: 2.5V~5.5V

- VPOS昇圧コンバータ:

4V~6V (0.1Vステップ) - VNEG反転昇降圧型コンバータ:

-6V~-4V (0.1Vステップ) - 最大出力電流:

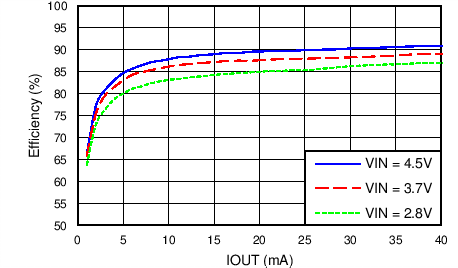

80mAまたは150mA - 非常に優れた総合効率

- IOUT > 10mAにおいて85%超

- IOUT > 40mAにおいて90%超

- 優れた性能

- 非常に優れた過渡応答

- 温度範囲の全体にわたって

出力電圧精度1%

- I2Cインターフェイス

- 電源オン/オフのシーケンシング・オプションを

プログラム可能 - 出力電圧を柔軟にプログラム可能

- アクティブ出力放電をプログラム可能

- 1000回以上プログラム可能な不揮発性メモリ

- 電源オン/オフのシーケンシング・オプションを

- 低電圧誤動作防止と過熱保護

- 2つのパッケージ・オプション

- 15ボールCSPパッケージ

- 20ピンQFNパッケージ

2 アプリケーション

- 小型または中型のバイポーラLCDディスプレイ

- スマートフォン、タブレット

- カメラ、GPS

- ホーム・オートメーション、ポイント・オブ・セールス

- ウェアラブル機器(スマートウォッチ、活動量計)

- 汎用分割レール電源

- 差動オーディオ、ヘッドフォン・アンプ

- 計測機器、オペアンプ、コンパレータ

- DAC/ADC

3 概要

TPS65132ファミリは、一般的な正/負駆動アプリケーションに電源を供給するよう設計されています。このデバイスは、両方の出力に単一インダクタのスキーマを使用し、最小のソリューション・サイズ、少ない部品点数、高効率を実現しています。このデバイスは、低ノイズで最高のラインおよび負荷レギュレーションを実現しています。2.5V~5.5Vの入力電圧範囲により、シングル・セル・バッテリ(リチウム・イオン、ニッケル・リチウム、リチウム・ポリマー)で駆動される製品、および3.3Vと5Vの固定電圧レールに対して最適化されています。TPS65132ファミリは、80mAおよび150mAの出力電流オプションがあり、40mAにもプログラム可能です。CSPとQFNの両方のパッケージ・オプションを利用可能です。

製品情報 (1)

| 型番 | パッケージ | 本体サイズ(公称.) |

|---|---|---|

| TPS65132 -B、-L、-T、-S |

DSBGA (15) | 2.11mm×1.51mm |

| TPS65132W | WQFN (20) | 4.00mm×3.00mm |

- 利用可能なすべてのパッケージについては、このデータシートの末尾にある注文情報を参照してください。

標準アプリケーション

効率 対 出力電流