# インターリーブ動作 連続導通モードPFCコントローラ

## 特 長

- 独自の電流マッチングを用いたインターリーブ動作で平均電流モードのPFCコントロール

- 高度な電流合成の検出による高効率の実現

- 内部Vff補正回路を用いた広い直線性をもつ乗算器によりほぼ1のPFが実現

- プログラム可能な周波数(10kHz~300kHz)

- プログラム可能な最大デューティ・サイクル・クランプ

- 周波数ディザリングのレートと大きさがプログラム可能なためEMI低減の改善

- 大きさ: 3kHz ~ 30kHz

- レート: 最大30kHz

- 外部クロック同期が可能

- 電圧誤差増幅器のスルーレート補正による負荷/ライン過渡応答の改善

- プログラム可能なピーク電流制限

- バイアス電源のUVLO、過電圧保護、開ループの検出、PFCイネーブルのモニタ

- PFCディセーブルの外部インターフェイス

- VSENSEピンとVINACピンのオープン回路保護

- プログラム可能なソフトスタート

- 20ピンTSSOPパッケージ

## ア プ リ ケ ジ シ ョ ン

- 高効率サーバー及びデスクトップPCの電源

- テレコム機器

## 概 要

UCC28070は180°の位相のずれで動作する2つのパルス幅変調器(PWM)を内蔵した最新式の力率改善デバイスです。このデバイスは各相がインターリーブ動作を行うため、入出力リップル電流が大幅に低減し、EMI用のフィルタが容易で、安価になります。大幅に改善された乗算器により、2つの独立した電流増幅器に共通の基準電流が供給されるため、安定した、低歪みの正弦波入力ライン電流を維持すると同時に、確実に両方の出力で整合のとれた平均電流モード・コントロールが行われます。

UCC28070は、力率、効率、THD、過渡応答の性能を改善するために電流合成、内部に段階的に補正されたVff機能などの複数の革新的手法を含んでいます。また、周波数ディザリング、外部同期、スルーレートの向上などの機能も性能の改善の可能性を広げています。

UCC28070は出力の過電圧保護、プログラム可能なピーク電流制限、低電圧ロックアウト、開ループ保護などのさまざまな保護機能も内蔵しています。

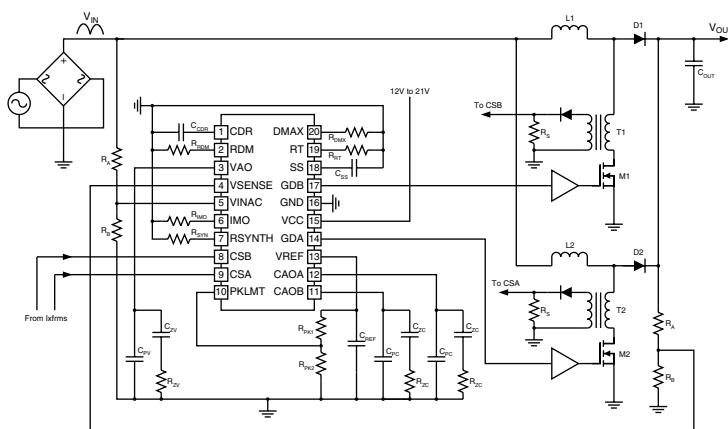

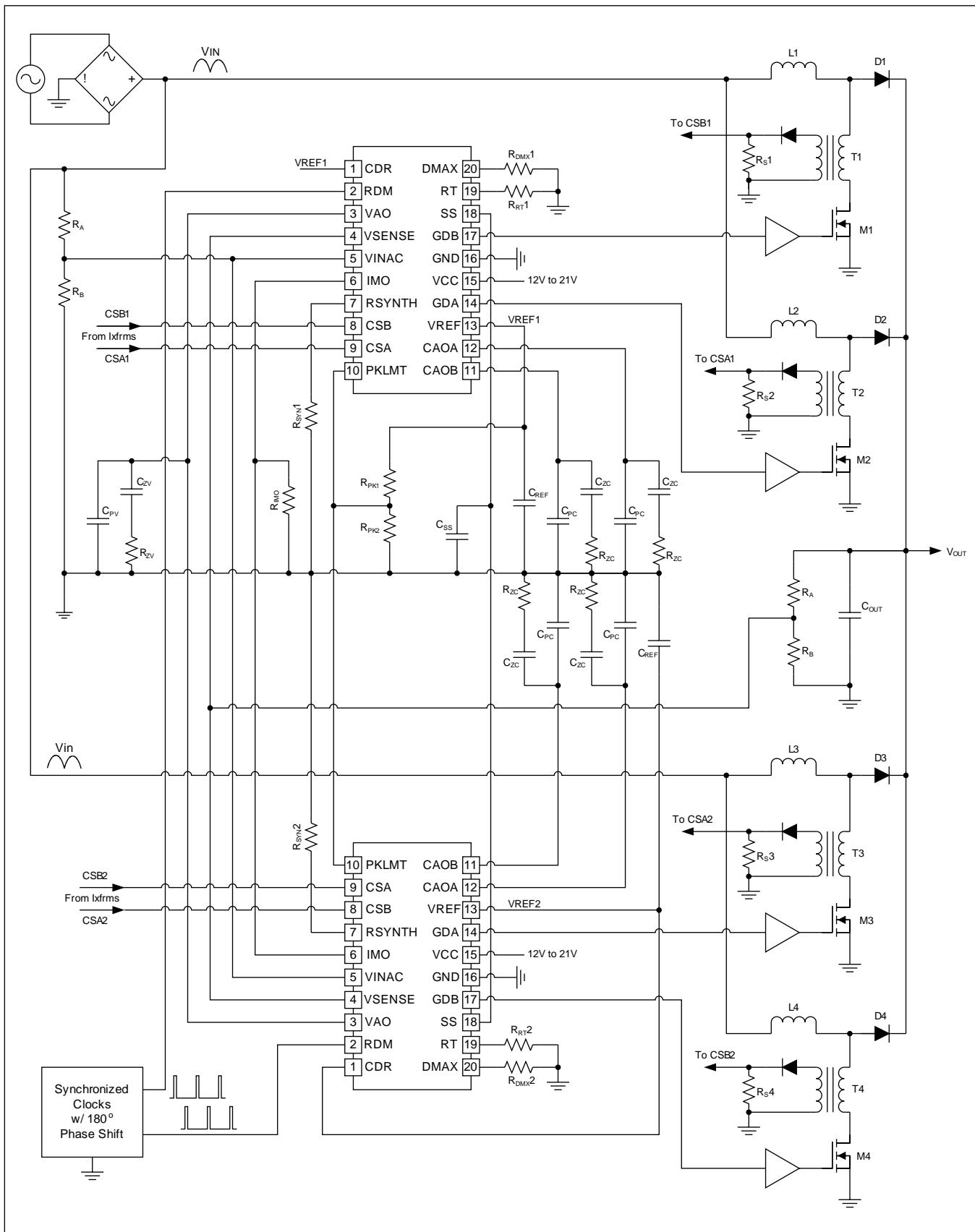

## Simplified Application Diagram

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ(日本TI)が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。

TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

SLUS794A 翻訳版

## 製品情報

| PART NUMBER | パッケージ                      | PACKING                |

|-------------|----------------------------|------------------------|

| UCC28070PW  | Plastic, 20-Pin TSSOP (PW) | 70-Pc. Tube            |

| UCC28070PWR | Plastic, 20-Pin TSSOP (PW) | 2000-Pc. Tape and Reel |

## 絶対最大定格 <sup>(1)(2)(3)(4)</sup>

over operating free-air temperature range (unless otherwise noted)

| パラメータ                                                                                        | LIMIT          | 単位 |

|----------------------------------------------------------------------------------------------|----------------|----|

| Supply voltage : VCC                                                                         | 22             | V  |

| Supply current : I <sub>VCC</sub>                                                            | 20             | mA |

| Voltage : GDA, GDB                                                                           | -0.5 ~ VCC+0.3 | V  |

| Gate drive current – continuous : GDA, GDB                                                   | +/- 0.25       | A  |

| Gate drive current – pulsed : GDA, GDB                                                       | +/- 0.75       |    |

| Voltage : DMAX, RDM, RT, CDR, VINAC, VSENSE, SS, VAO, IMO, CSA, CSB, CAOA, CAOB, PKLMT, VREF | -0.5 ~ +7      | V  |

| Current : RT, DMAX, RDM, RSYNTH                                                              | -0.5           | mA |

| Current : VREF, VAO, CAOA, CAOB, IMO                                                         | 10             |    |

| Operating junction temperature, T <sub>J</sub>                                               | -40 ~ +125     | °C |

| Storage temperature, T <sub>STG</sub>                                                        | -65 ~ +150     |    |

| Lead temperature (10 seconds)                                                                | 260            |    |

- (1) 絶対最大定格以上のストレスは、致命的なダメージを製品に与えることがあります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を越える状態での本製品の機能動作は含まれていません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

- (2) 全ての電圧はGNDを基準としています。

- (3) 電流の極性は端子に流入する方向が正、流出する方向が負です。

- (4) 通常使用時、端子GDAとGDBは外部のゲート・ドライバに接続され、内部で出力電流が制限されています。

## ELECTROSTATIC DISCHARGE (ESD) PROTECTION

|                            | RATING | 単位 |

|----------------------------|--------|----|

| Human Body Model (HBM)     | 2,000  | V  |

| Charged Device Model (CDM) | 500    |    |

## DISSIPATION RATINGS

| パッケージ        | THERMAL IMPEDANCE JUNCTION-TO-AMBIENT        | T <sub>A</sub> = 25°C POWER RATING | T <sub>A</sub> = 85°C POWER RATING |

|--------------|----------------------------------------------|------------------------------------|------------------------------------|

| 20-Pin TSSOP | 125°C/Watt <sup>(1)</sup> and <sup>(2)</sup> | 800 mW <sup>(1)</sup>              | 320 mW <sup>(1)</sup>              |

(1) 熱抵抗はボードの構造とレイアウトに大きな相関のある関数です。エアー・フローを与えることで熱抵抗は低下します。この値は単なる一般的な指針です。

(2) 热抵抗はlow-K手法で計算されています。

## 推奨動作条件

over operating free-air temperature range (unless otherwise noted)

| パラメータ                                           | MIN                     | MAX | 単位 |

|-------------------------------------------------|-------------------------|-----|----|

| VCC Input Voltage (from a low-impedance source) | V <sub>UVLO</sub> + 1 V | 21  | V  |

| VREF Load Current                               |                         | 2   | mA |

| VINAC Input Voltage Range                       | 0                       | 3   | V  |

| IMO Voltage Range                               | 0                       | 3.3 |    |

| PKLMT, CSA, & CSB Voltage Range                 | 0                       | 3.6 |    |

| RSYNTH Resistance (R <sub>SYN</sub> )           | 15                      | 750 | kΩ |

| RDM Resistance (R <sub>RDM</sub> )              | 30                      | 330 |    |

## 電気的特性

over operating free-air temperature range  $-40^{\circ}\text{C} < T_A < 125^{\circ}\text{C}$ ,  $T_J = T_A$ ,  $\text{VCC} = 12\text{V}$ ,  $\text{GND} = 0\text{V}$ ,  $R_{RT} = 75\text{k}\Omega$ ,  $R_{DMX} = 68.1\text{k}\Omega$ ,  $R_{RDM} = R_{SYN} = 100\text{k}\Omega$ ,  $C_{CDR} = 2.2\text{nF}$ ,  $C_{SS} = C_{VREF} = 0.1\mu\text{F}$ ,  $C_{VCC} = 1\mu\text{F}$ , (unless otherwise noted)

| SYMBOL                                | パラメータ                                                | テスト条件                                                                                                          | MIN  | TYP  | MAX  | 単位            |

|---------------------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------|------|------|---------------|

| <b>Bias Supply</b>                    |                                                      |                                                                                                                |      |      |      |               |

| $V_{CCSHUNT}$                         | VCC shunt voltage <sup>(1)</sup>                     | $I_{VCC} = 10\text{mA}$                                                                                        | 23   | 25   | 27   | V             |

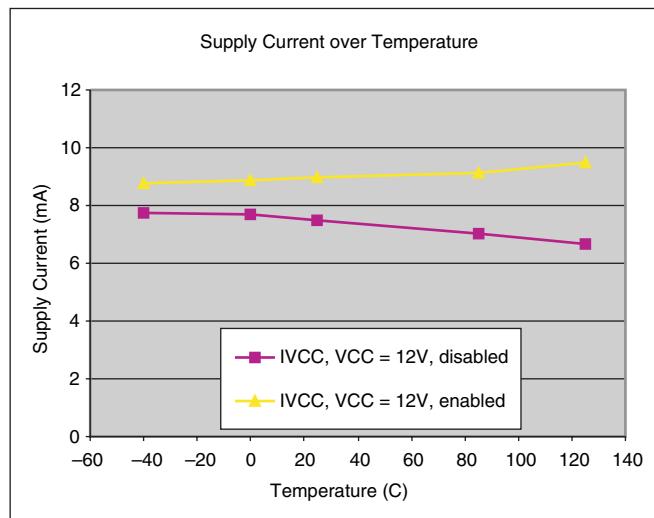

|                                       | VCC current, disabled                                | $VSENSE = 0\text{V}$                                                                                           |      | 7    |      | mA            |

|                                       | VCC current, enabled                                 | $VSENSE = 3\text{V}$ (switching)                                                                               |      | 9    | 12   |               |

|                                       | VCC current, UVLO                                    | $VCC = 7\text{V}$                                                                                              |      |      | 200  | $\mu\text{A}$ |

|                                       |                                                      | $VCC = 9\text{V}$                                                                                              |      | 4    | 6    | mA            |

| $V_{UVLO}$                            | UVLO turn-on threshold                               | Measured at VCC (rising)                                                                                       | 9.8  | 10.2 | 10.6 |               |

|                                       | UVLO hysteresis                                      | Measured at VCC (falling)                                                                                      |      | 1    |      |               |

|                                       | VREF enable threshold                                | Measured at VCC (rising)                                                                                       | 7.5  | 8    | 8.5  | V             |

| <b>Linear Regulator</b>               |                                                      |                                                                                                                |      |      |      |               |

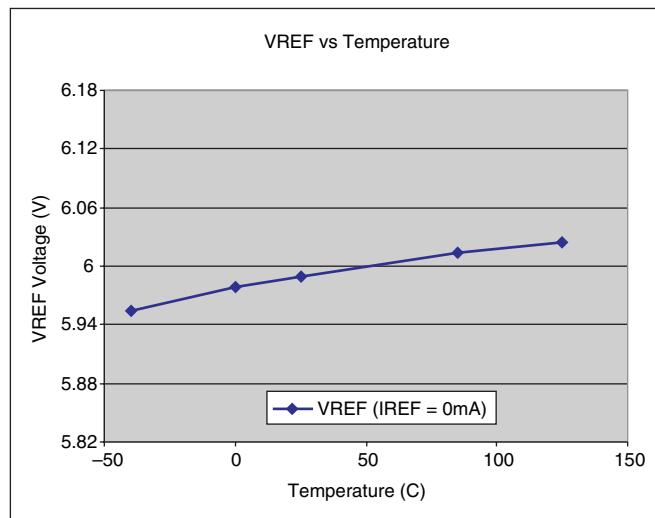

|                                       | VREF voltage, no load                                | $I_{VREF} = 0\text{ mA}$                                                                                       | 5.82 | 6    | 6.18 | V             |

|                                       | VREF load rejection                                  | Measured as the change in VREF, ( $I_{VREF} = 0\text{ mA}$ and $-2\text{mA}$ )                                 | -12  |      | 12   |               |

|                                       | VREF line rejection                                  | Measured as the change in VREF, ( $VCC = 11\text{V}$ and $20\text{V}$ , $I_{VREF} = 0\mu\text{A}$ )            | -12  |      | 12   | mV            |

| <b>PFC Enable</b>                     |                                                      |                                                                                                                |      |      |      |               |

| $V_{EN}$                              | Enable threshold                                     | Measured at $VSENSE$ (rising)                                                                                  | 0.65 | 0.75 | 0.85 |               |

|                                       | Enable hysteresis                                    |                                                                                                                |      | 0.15 |      | V             |

| <b>External PFC Disable</b>           |                                                      |                                                                                                                |      |      |      |               |

|                                       | Disable threshold                                    | Measured at $SS$ (falling)                                                                                     | 0.5  | 0.6  |      |               |

|                                       | Hysteresis                                           | $VSENSE > 0.85\text{V}$                                                                                        |      | 0.15 |      | V             |

| <b>Oscillator</b>                     |                                                      |                                                                                                                |      |      |      |               |

|                                       | Output phase shift                                   | Measured between GDA and GDB                                                                                   | 179  | 180  | 181  | Degree        |

| $V_{DMAX}$ , $V_{RT}$ , and $V_{RDM}$ | Timing regulation voltages                           | Measured at $DMAX$ , $RT$ , & $RDM$                                                                            | 2.91 | 3    | 3.09 | V             |

| $f_{PWM}$                             | PWM switching frequency                              | $R_{RT} = 750\text{k}\Omega$ , $R_{DMX} = 681\text{k}\Omega$ , $V_{RDM} = 0\text{V}$ , $V_{CDR} = 6\text{V}$   | 9.5  | 10   | 10.5 |               |

|                                       |                                                      | $R_{RT} = 75\text{k}\Omega$ , $R_{DMX} = 68.1\text{k}\Omega$ , $V_{RDM} = 0\text{V}$ , $V_{CDR} = 6\text{V}$   | 95   | 100  | 105  |               |

|                                       |                                                      | $R_{RT} = 24.9\text{k}\Omega$ , $R_{DMX} = 22.6\text{k}\Omega$ , $V_{RDM} = 0\text{V}$ , $V_{CDR} = 6\text{V}$ | 270  | 290  | 330  | kHz           |

| $D_{MAX}$                             | Duty-cycle clamp                                     | $R_{RT} = 75\text{k}\Omega$ , $R_{DMX} = 68.1\text{k}\Omega$ , $V_{RDM} = 0\text{V}$ , $V_{CDR} = 6\text{V}$   | 92%  | 95%  | 98%  |               |

|                                       | Minimum programmable off-time                        | $R_{RT} = 24.9\text{k}\Omega$ , $R_{DMX} = 22.6\text{k}\Omega$ , $V_{RDM} = 0\text{V}$ , $V_{CDR} = 6\text{V}$ | 50   | 150  | 250  | ns            |

| $f_{DM}$                              | Frequency dithering magnitude change in $f_{PWM}$    | $R_{RDM} = 316\text{k}\Omega$ , $R_{RT} = 75\text{k}\Omega$                                                    | 2    | 3    | 4    |               |

|                                       |                                                      | $R_{RDM} = 31.6\text{k}\Omega$ , $R_{RT} = 24.9\text{k}\Omega$                                                 | 24   | 30   | 36   |               |

| $f_{DR}$                              | Frequency dithering rate rate of change in $f_{PWM}$ | $C_{CDR} = 2.2\text{nF}$ , $R_{RDM} = 100\text{k}\Omega$                                                       |      | 3    |      |               |

|                                       |                                                      | $C_{CDR} = 0.3\text{nF}$ , $R_{RDM} = 100\text{k}\Omega$                                                       |      | 20   |      |               |

| $I_{CDR}$                             | Dither rate current                                  | Measure at CDR (sink and source)                                                                               |      | 10   |      | $\mu\text{A}$ |

|                                       | Dither disable threshold                             | Measured at $C_{CDR}$ (rising)                                                                                 |      | 5    | 5.25 | V             |

(1) VCC入力電圧及び電流が過度に大きいとデバイスを損傷します。このクランプはデバイスをレギュレーションされていない電源からの保護は行いません。レギュレーションされていない電源が用いられる場合は、UA78L15Aなどの固定正電圧レギュレータを直列に接続して使用することを推奨します。VCC電圧 / 電流の制限については絶対最大定格の項を参照してください。

## 電気的特性

over operating free-air temperature range  $-40^{\circ}\text{C} < T_A < 125^{\circ}\text{C}$ ,  $T_J = T_A$ ,  $\text{VCC} = 12\text{V}$ ,  $\text{GND} = 0\text{V}$ ,  $R_{RT} = 75\text{k}\Omega$ ,  $R_{DMX} = 68.1\text{k}\Omega$ ,  $R_{RDM} = R_{SYN} = 100\text{k}\Omega$ ,  $C_{CDR} = 2.2\text{nF}$ ,  $C_{SS} = C_{VREF} = 0.1\mu\text{F}$ ,  $C_{VCC} = 1\mu\text{F}$ , (unless otherwise noted)

| SYMBOL                       | パラメータ                                            | テスト条件                                                                              | MIN  | TYP  | MAX  | 単位            |

|------------------------------|--------------------------------------------------|------------------------------------------------------------------------------------|------|------|------|---------------|

| <b>Clock Synchronization</b> |                                                  |                                                                                    |      |      |      |               |

| $V_{CDR}$                    | SYNC enable threshold                            | Measured at CDR (rising)                                                           |      | 5    | 5.25 | V             |

|                              | SYNC propagation delay                           | $V_{CDR} = 6\text{V}$ , Measured from RDM (rising) to GDx (rising)                 |      | 50   | 100  | ns            |

|                              | SYNC threshold (Rising)                          | $V_{CDR} = 6\text{V}$ , Measured at RDM                                            |      | 1.2  | 1.5  | V             |

|                              | SYNC threshold (Falling)                         | $V_{CDR} = 6\text{V}$ , Measured at RDM                                            | 0.4  | 0.7  |      |               |

|                              | SYNC pulses                                      | Positive pulse width                                                               | 0.2  |      |      | $\mu\text{s}$ |

|                              |                                                  | Maximum duty cycle <sup>(2)</sup>                                                  |      | 50   |      | %             |

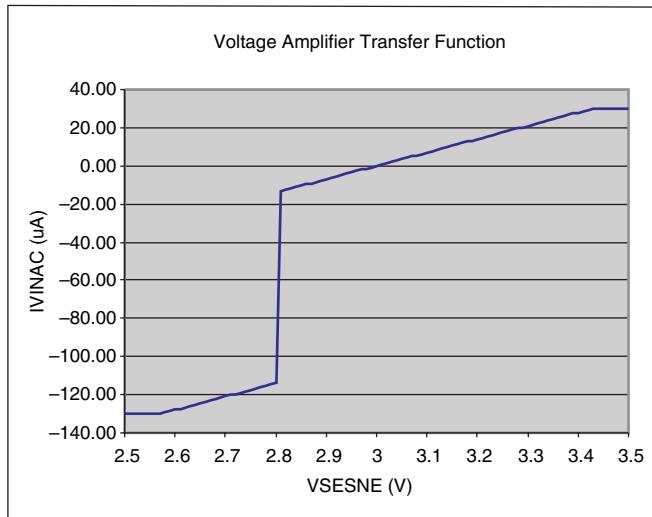

| <b>Voltage Amplifier</b>     |                                                  |                                                                                    |      |      |      |               |

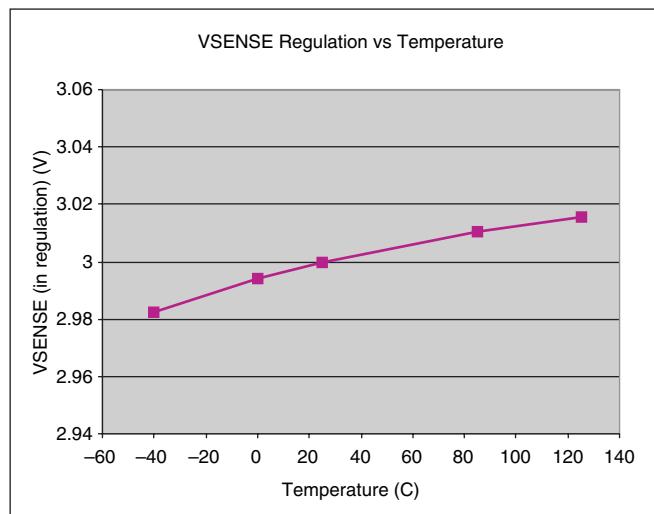

|                              | VSENSE voltage                                   | In regulation, $T_A = 25^{\circ}\text{C}$                                          | 2.97 | 3    | 3.03 | V             |

|                              | VSENSE voltage                                   | In regulation                                                                      | 2.94 | 3    | 3.06 |               |

|                              | VSENSE input bias current                        | In regulation                                                                      |      | 250  | 500  | nA            |

|                              | VAO high voltage                                 | $\text{VSENSE} = 2.9\text{V}$                                                      | 4.8  | 5    | 5.2  | V             |

|                              | VAO low voltage                                  | $\text{VSENSE} = 3.1\text{V}$                                                      |      | 0.05 | 0.50 |               |

| $g_{MV}$                     | VAO transconductance                             | $2.8\text{V} < \text{VSENSE} < 3.2\text{V}$ , $\text{VAO} = 3\text{V}$             |      | 70   |      | $\mu\text{S}$ |

|                              | VAO sink current, overdriven limit               | $\text{VSENSE} = 3.5\text{V}$ , $\text{VAO} = 3\text{V}$                           |      | 30   |      | $\mu\text{A}$ |

|                              | VAO source current, overdriven                   | $\text{VSENSE} = 2.5\text{V}$ , $\text{VAO} = 3\text{V}$ , $\text{SS} = 3\text{V}$ |      | -30  |      |               |

|                              | VAO source current, overdriven limit + $I_{SRC}$ | $\text{VSENSE} = 2.5\text{V}$ , $\text{VAO} = 3\text{V}$                           |      | -130 |      |               |

|                              | Slew-rate correction threshold                   | Measured as VSENSE (falling) / VSENSE (regulation)                                 | 92   | 93   | 95   | %             |

|                              | Slew-rate correction hysteresis                  | Measured at VSENSE (rising)                                                        |      | 3    | 9    | mV            |

| $I_{SRC}$                    | Slew-rate correction current                     | Measured at VAO, in addition to VAO source current.                                |      | -100 |      | $\mu\text{A}$ |

|                              | Slew-rate correction enable threshold            | Measured at SS (rising)                                                            |      | 4    |      | V             |

|                              | VAO discharge current                            | $\text{VSENSE} = 0.5\text{V}$ , $\text{VAO} = 1\text{V}$                           |      | 10   |      | $\mu\text{A}$ |

| <b>Soft Start</b>            |                                                  |                                                                                    |      |      |      |               |

| $I_{SS}$                     | SS source current                                | $\text{VSENSE} = 0.9\text{V}$ , $\text{SS} = 1\text{V}$                            |      | -10  |      | $\mu\text{A}$ |

|                              | Adaptive source current                          | $\text{VSENSE} = 2.0\text{V}$ , $\text{SS} = 1\text{V}$                            |      | -1.5 | -2.5 | mA            |

|                              | Adaptive SS disable                              | Measured as $\text{VSENSE} - \text{SS}$                                            | -30  | 0    | 30   | mV            |

|                              | SS sink current                                  | $\text{VSENSE} = 0.5\text{V}$ , $\text{SS} = 0.2\text{V}$                          | 0.5  | 0.9  |      | mA            |

(2) PWMの最大スイッチング・デューティ・サイクル(DMAX)をプログラムする際の同期パルス幅の影響により、同期信号のデューティ・サイクルを最小限にすることを推奨します。

## 電気的特性

over operating free-air temperature range  $-40^{\circ}\text{C} < T_A < 125^{\circ}\text{C}$ ,  $T_J = T_A$ ,  $\text{VCC} = 12\text{V}$ ,  $\text{GND} = 0\text{V}$ ,  $R_{RT} = 75\text{k}\Omega$ ,  $R_{DMX} = 68.1\text{k}\Omega$ ,  $R_{RDM} = R_{SYN} = 100\text{k}\Omega$ ,  $C_{CDR} = 2.2\text{nF}$ ,  $C_{SS} = C_{VREF} = 0.1\mu\text{F}$ ,  $C_{VCC} = 1\mu\text{F}$ , (unless otherwise noted)

| SYMBOL                                | パラメータ                            | テスト条件                                                           | MIN  | TYP  | MAX  | 単位 |

|---------------------------------------|----------------------------------|-----------------------------------------------------------------|------|------|------|----|

| <b>Over Voltage</b>                   |                                  |                                                                 |      |      |      |    |

| $V_{OVP}$                             | OVP threshold                    | Measured as VSENSE (rising) / VSENSE (regulation)               | 104  | 106  | 108  | %  |

|                                       | OVP hysteresis                   | Measured at VSENSE (falling)                                    |      | 100  |      | mV |

|                                       | OVP propagation delay            | Measured between VSENSE (rising) and GDx (falling)              |      | 0.2  | 0.3  | μs |

| <b>Zero-Power</b>                     |                                  |                                                                 |      |      |      |    |

| $V_{ZPWR}$                            | Zero-power detect threshold      | Measured at VAO (falling)                                       | 0.65 | 0.75 |      | V  |

|                                       | Zero-power hysteresis            |                                                                 |      | 0.15 |      |    |

| <b>Multiplier</b>                     |                                  |                                                                 |      |      |      |    |

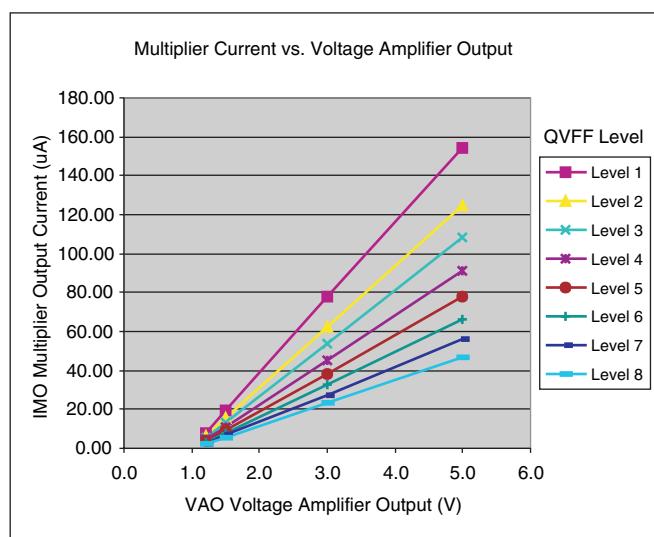

| $k_{MULT}$                            | Gain constant                    | VAO $\geq 1.5\text{V}$ , $T_A = 25^{\circ}\text{C}$             | 16   | 17   | 18   | μA |

|                                       |                                  | VAO = $1.2\text{V}$ , $T_A = 25^{\circ}\text{C}$                | 14.5 | 17.0 | 19.5 |    |

|                                       |                                  | VAO $\geq 1.5\text{V}$                                          | 15   | 17   | 19   |    |

|                                       |                                  | VAO = $1.2\text{V}$                                             | 13   | 17   | 21   |    |

| $I_{IMO}$                             | Output current : zero            | VINAC = $0.9V_{PK}$ , VAO = $0.8\text{V}$                       | -0.2 | 0    | 0.2  |    |

|                                       |                                  | VINAC = $0\text{V}$ , VAO = $5\text{V}$                         | -0.2 | 0    | 0.2  |    |

| <b>Quantized Voltage Feed Forward</b> |                                  |                                                                 |      |      |      |    |

| $V_{LVL1}$                            | Level 1 threshold <sup>(3)</sup> | Measured at VINAC (rising)                                      | 0.6  | 0.7  | 0.8  | V  |

| $V_{LVL2}$                            | Level 2 threshold                |                                                                 |      | 1    |      |    |

| $V_{LVL3}$                            | Level 3 threshold                |                                                                 |      | 1.2  |      |    |

| $V_{LVL4}$                            | Level 4 threshold                |                                                                 |      | 1.4  |      |    |

| $V_{LVL5}$                            | Level 5 threshold                |                                                                 |      | 1.65 |      |    |

| $V_{LVL6}$                            | Level 6 threshold                |                                                                 |      | 1.95 |      |    |

| $V_{LVL7}$                            | Level 7 threshold                |                                                                 |      | 2.25 |      |    |

| $V_{LVL8}$                            | Level 8 threshold                |                                                                 |      | 2.6  |      |    |

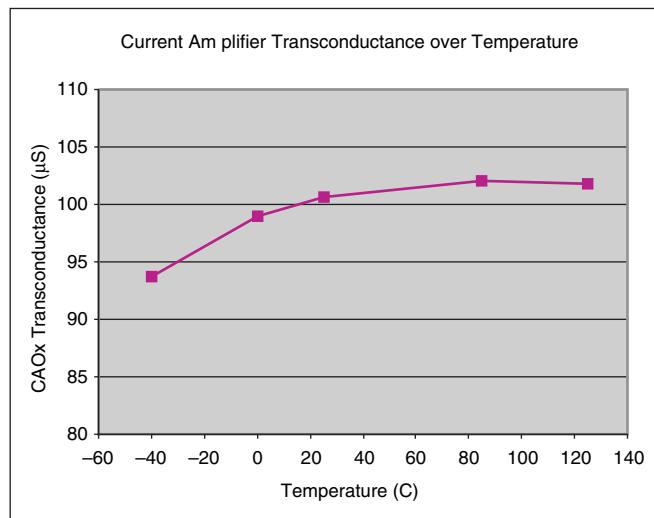

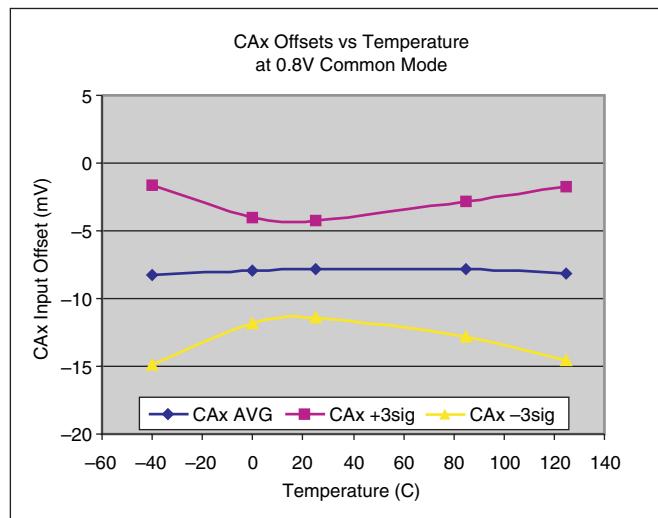

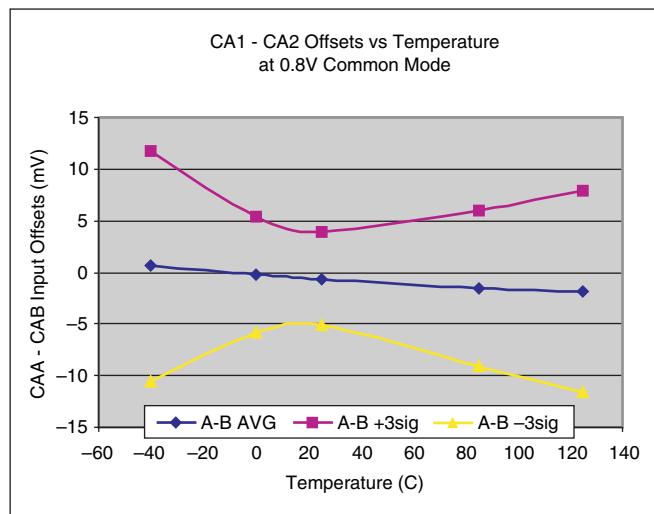

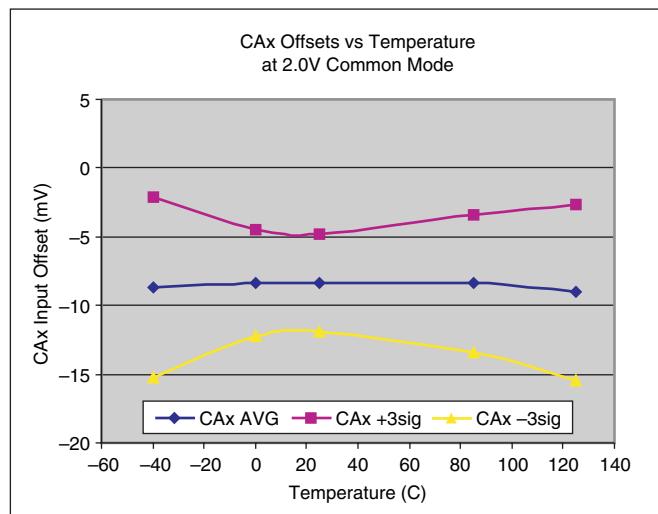

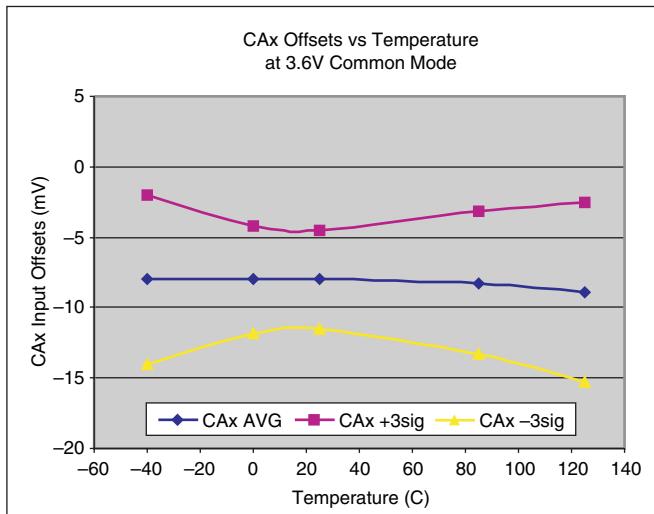

| <b>Current Amplifiers</b>             |                                  |                                                                 |      |      |      |    |

|                                       | CAOx high voltage                |                                                                 | 5.75 | 6    |      | V  |

|                                       | CAOx low voltage                 |                                                                 |      |      | 0.1  |    |

| $g_{MC}$                              | CAOx transconductance            |                                                                 |      | 100  |      | μS |

|                                       | CAOx sink current, overdriven    |                                                                 |      | 50   |      | μA |

|                                       | CAOx source current, overdriven  |                                                                 |      | -50  |      |    |

|                                       | Input common mode range          |                                                                 | 0    |      | 3.6  | V  |

|                                       | Input offset voltage             |                                                                 | 0    | -8   | -20  | mV |

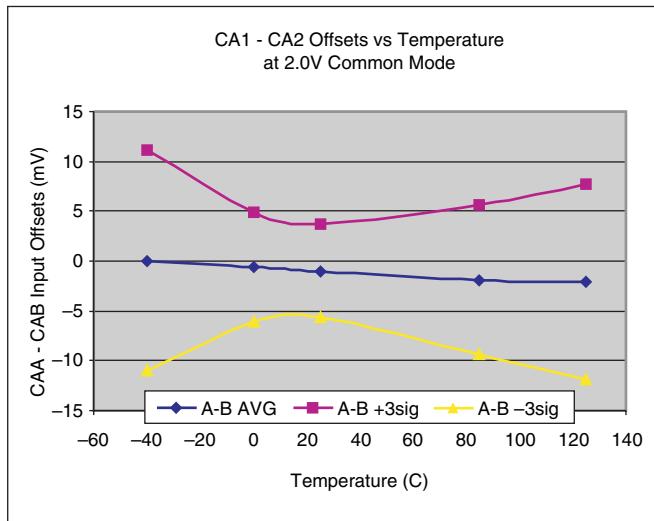

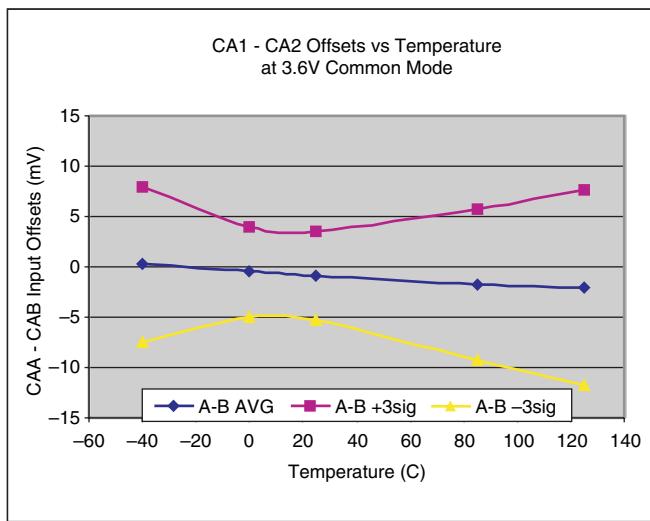

|                                       | Phase mismatch                   | Measured as Phase A's input offset minus Phase B's input offset | -12  | 0    | 12   |    |

|                                       | CAOx pull-down current           | $VSENSE = 0.5\text{V}$ , CAOx = $0.2\text{V}$                   | 0.5  | 0.9  |      | mA |

(3) レベル1のスレッショルドはVINACが新規の半サイクルを開始するために上昇しなければならない上側の“ゼロクロス検出”スレッショルドを、また、VINACが半サイクル終了するために下降する下側の“ゼロクロス検出”スレッショルドを表します。

## 電気的特性

over operating free-air temperature range  $-40^{\circ}\text{C} < T_A < 125^{\circ}\text{C}$ ,  $T_J = T_A$ ,  $\text{VCC} = 12\text{V}$ ,  $\text{GND} = 0\text{V}$ ,  $R_{RT} = 75\text{k}\Omega$ ,  $R_{DMX} = 68.1\text{k}\Omega$ ,  $R_{RDM} = R_{SYNTH} = 100\text{k}\Omega$ ,  $C_{CDR} = 2.2\text{nF}$ ,  $C_{SS} = C_{VREF} = 0.1\mu\text{F}$ ,  $C_{VCC} = 1\mu\text{F}$ , (unless otherwise noted)

| SYMBOL                     | パラメータ                                   | テスト条件                                                 | MIN  | TYP   | MAX   | 単位    |

|----------------------------|-----------------------------------------|-------------------------------------------------------|------|-------|-------|-------|

| <b>Current Synthesizer</b> |                                         |                                                       |      |       |       |       |

| V <sub>RSYNTH</sub>        | Regulation voltage                      | VSENSE = 3V, VINAC = 0V                               | 2.91 | 3     | 3.09  | V     |

|                            |                                         | VSENSE = 3V, VINAC = 2.85V                            | 0.10 | 0.15  | 0.20  |       |

|                            | Synthesizer disable threshold           | Measured at RSYNTH (rising)                           |      | 5     | 5.25  |       |

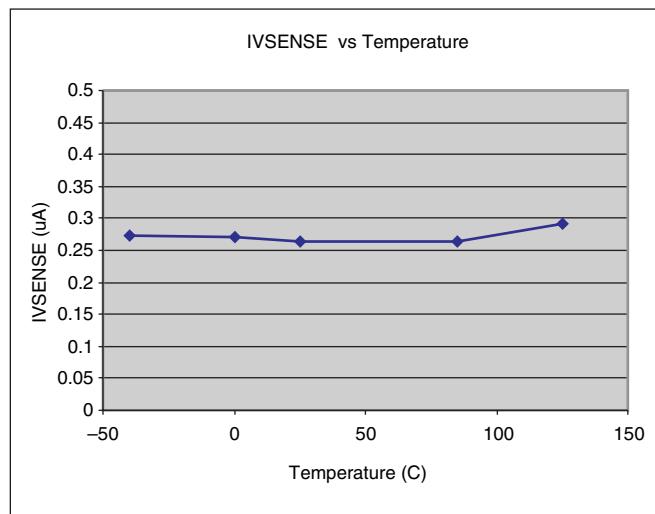

|                            | VINAC input bias current                |                                                       |      | 0.250 | 0.500 | μA    |

| <b>Peak Current Limit</b>  |                                         |                                                       |      |       |       |       |

|                            | Peak current limit threshold            | PKLMT = 3.30V, measured at CSx (rising)               | 3.27 | 3.3   | 3.33  | V     |

|                            | Peak current limit propagation delay    | Measured between CSx (rising) and GDx (falling) edges |      | 60    | 100   | ns    |

| <b>PWM Ramp</b>            |                                         |                                                       |      |       |       |       |

| V <sub>RMP</sub>           | PWM ramp amplitude                      |                                                       | 3.8  | 4.0   | 4.2   | V     |

|                            | PWM ramp offset voltage                 | T <sub>A</sub> = 25°C, R <sub>RT</sub> = 75kΩ         | 0.65 | 0.7   |       |       |

|                            | PWM ramp offset temperature coefficient |                                                       |      | -2    |       | mV/°C |

| <b>Gate Drive</b>          |                                         |                                                       |      |       |       |       |

|                            | GDA, GDB output voltage, high, clamped  | VCC = 20V, C <sub>LOAD</sub> = 1nF                    | 11.5 | 13    | 15    | V     |

|                            | GDA, GDB output voltage, High           | C <sub>LOAD</sub> = 1 nF                              | 10   | 10.5  |       |       |

|                            | GDA, GDB output voltage, Low            | C <sub>LOAD</sub> = 1nF                               |      | 0.2   | 0.3   |       |

|                            | Rise time GDx                           | 1V ~ 9V, C <sub>LOAD</sub> = 1nF                      |      | 18    | 30    | ns    |

|                            | Fall time GDx                           | 9V ~ 1V, C <sub>LOAD</sub> = 1nF                      |      | 12    | 25    |       |

|                            | GDA, GDB output voltage, UVLO           | VCC = 0V, I <sub>GDA</sub> , I <sub>GDB</sub> = 2.5mA |      | 0.7   | 2     |       |

| <b>Thermal Shutdown</b>    |                                         |                                                       |      |       |       |       |

|                            | Thermal shutdown threshold              |                                                       |      | 160   |       | °C    |

|                            | Thermal shutdown recovery               |                                                       |      | 140   |       |       |

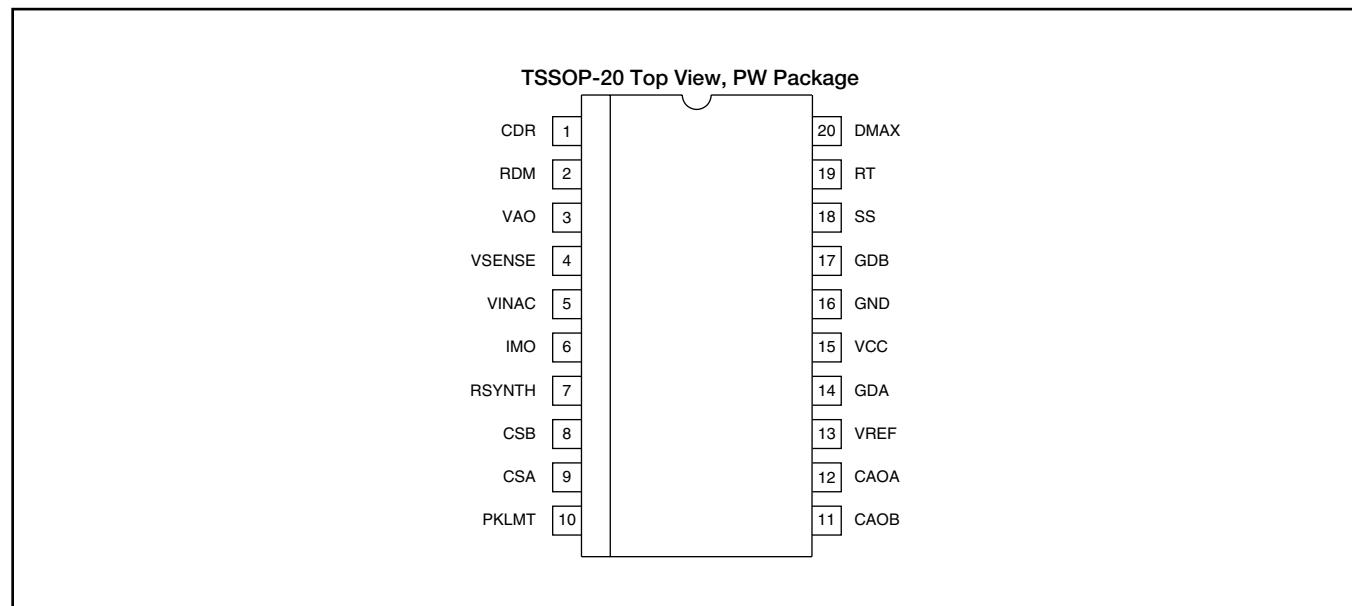

## ピン配置

## ピン機能

| NAME          | PIN # | I/O | 説明                                                                                                                                                                                                                                                                    |

|---------------|-------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CDR           | 1     | I   | ディザー・レート用コンデンサ。周波数ディザリングのタイミング設定ピンです。このピンからGNDへコンデンサを外付けすると発振器ディザーのレートをプログラムすることができます。CDRピンをVREFピンに接続するとディザリングはディセーブルになります。                                                                                                                                           |

| RDM<br>(SYNC) | 2     | I   | ディザー振幅設定用抵抗。周波数ディザリングの振幅設定及び外部同期ピンです。このピンからGNDへ抵抗を外付けすると発振器周波数ディザーの大きさをプログラムすることができます。周波数ディザリングがディセーブルの時(CDR>5V)、内部のマスター・クロックはRDMピン上の正のエッジに同期します。ディザリングがディセーブルで同期が不要の場合はRDMをGNDに接続します。                                                                                |

| VAO           | 3     | O   | 電圧増幅器出力。トランスコンダクタンス電圧誤差増幅器の出力です。このピンは内部で乗算器の入力とゼロパワー・コンパレータに接続されています。電圧レギュレーション・ループの補償用部品をこのピンとGNDの間に接続します。                                                                                                                                                           |

| VSENSE        | 4     | I   | 出力電圧検出。このピンは内部で電流合成差動増幅器の正端子に加えトランスコンダクタンス電圧誤差増幅器の反転入力にも接続されています。また、このピンはOVP、PFCイネーブル、スルーレート・コンパレータにも接続されています。PFC出力は抵抗分圧回路を用いて接続します。                                                                                                                                  |

| VINAC         | 5     | I   | 交流ライン入力電圧の拡大縮小。このピンは内部で乗算器と電流合成差動増幅器の負端子に接続されています。VIN、VINAC、GND間に、VSENSEに接続したPFC出力の抵抗分圧回路と同一の抵抗分圧回路を接続します。                                                                                                                                                            |

| IMO           | 6     | O   | 乗算器電流出力。乗算器のゲインを設定するためこのピンとGNDの間に抵抗を接続します。                                                                                                                                                                                                                            |

| RSYNTH        | 7     | I   | 電流合成のダウンスロープ・プログラミング。電流合成の割合の大きさを設定するためこのピンとGNDの間に抵抗を接続します。RSYNTHをVREFに接続すると電流合成はディセーブルになり、CSAとCSBはそれぞれの電流増幅器に直接接続されます。                                                                                                                                               |

| CSB           | 8     | I   | フェーズB電流検出入力。GDBのオン時間で、CSBは電流合成段を経て内部でフェーズBの電流増幅器の反転入力に接続されます。                                                                                                                                                                                                         |

| CSA           | 9     | I   | フェーズA電流検出入力。GDAのオン時間で、CSAは電流合成段を経て内部でフェーズAの電流増幅器の反転入力に接続されます。                                                                                                                                                                                                         |

| PKLMT         | 10    | I   | ピーク電流制限のプログラミング。サイクルごとのピーク電流制限コンパレータの電圧スレッショルドを設定するためVREFとこのピンの間に抵抗分圧回路を接続します。目的とする $\Delta I_{LB}$ の調整ができます。                                                                                                                                                         |

| CAOB          | 11    | O   | フェーズB電流増幅器出力。フェーズBのトランスコンダクタンス電圧増幅器の出力です。このピンは立下りエッジ変調を行うよう内部でフェーズBのPWMコンパレータの反転入力に接続されています。このピンとGNDの間に電流レギュレーション・ループの補償部品を接続します。                                                                                                                                     |

| CAOA          | 12    | O   | フェーズA電流増幅器出力。フェーズAのトランスコンダクタンス電圧増幅器の出力です。このピンは立下りエッジ変調を行うよう内部でフェーズAのPWMコンパレータの反転入力に接続されています。このピンとGNDの間に電流レギュレーション・ループの補償部品を接続します。                                                                                                                                     |

| VREF          | 13    | O   | 6V基準電圧及び内部バイアス電圧。0.1μFのセラミック・バイパス・コンデンサをこのピンとGNDにできるだけ近づけて接続します。                                                                                                                                                                                                      |

| GDA           | 14    | O   | フェーズAのゲート駆動。この制限された電流出力はフェーズAのスイッチング部品を駆動するのに適した別々のゲート駆動デバイスに接続することを目的としています。出力電圧は標準で13.5Vにクランプされています。                                                                                                                                                                |

| VCC           | 15    | I   | バイアス電圧入力。0.1μFのセラミック・バイパス・コンデンサをこのピンとGNDにできるだけ近づけて接続します。                                                                                                                                                                                                              |

| GND           | 16    | I/O | デバイスの基準グランド。全ての補償回路、プログラミング抵抗、コンデンサをこのピンに接続します。このピンは大電流ノイズを絶縁するため別々の配線を用いてシステムに接続します。                                                                                                                                                                                 |

| GDB           | 17    | O   | フェーズBのゲート駆動。この制限された電流出力はフェーズBのスイッチング部品を駆動するのに適した別々のゲート駆動デバイスに接続することを目的としています。出力電圧は標準で13.5Vにクランプされています。                                                                                                                                                                |

| SS            | 18    | I   | ソフトスタート及び外部異常インターフェイス。内部で固定されている10μAの電流源をもとにソフトスタートのスルーレートを設定するためこのピンからGNDにコンデンサを接続します。VSENSE用のレギュレーション基準電圧はV <sub>SS</sub> が3Vを越えるまでV <sub>SS</sub> にクランプされます。ある異常状態からの復帰時は、SS電圧がVSENSE電圧に等しくなるまで1mAの電流源はSSピンに接続されています。SSピンを6Vより低くするとGDA出力とGDB出力の両方とも直ちにディセーブルになります。 |

| RT            | 19    | I   | タイミング抵抗。発振器周波数のプログラミング・ピンです。このピンからGNDに抵抗を接続すると内部発振器の動作周波数を設定することができます。                                                                                                                                                                                                |

| DMAX          | 20    | I   | 最大デューティ・サイクル抵抗。PWMの最大デューティ・サイクルのプログラミング・ピンです。このピンからGNDに抵抗を接続するとRDMX/RRTの比をもとにPWMの最大デューティ・サイクルを設定することができます。                                                                                                                                                            |

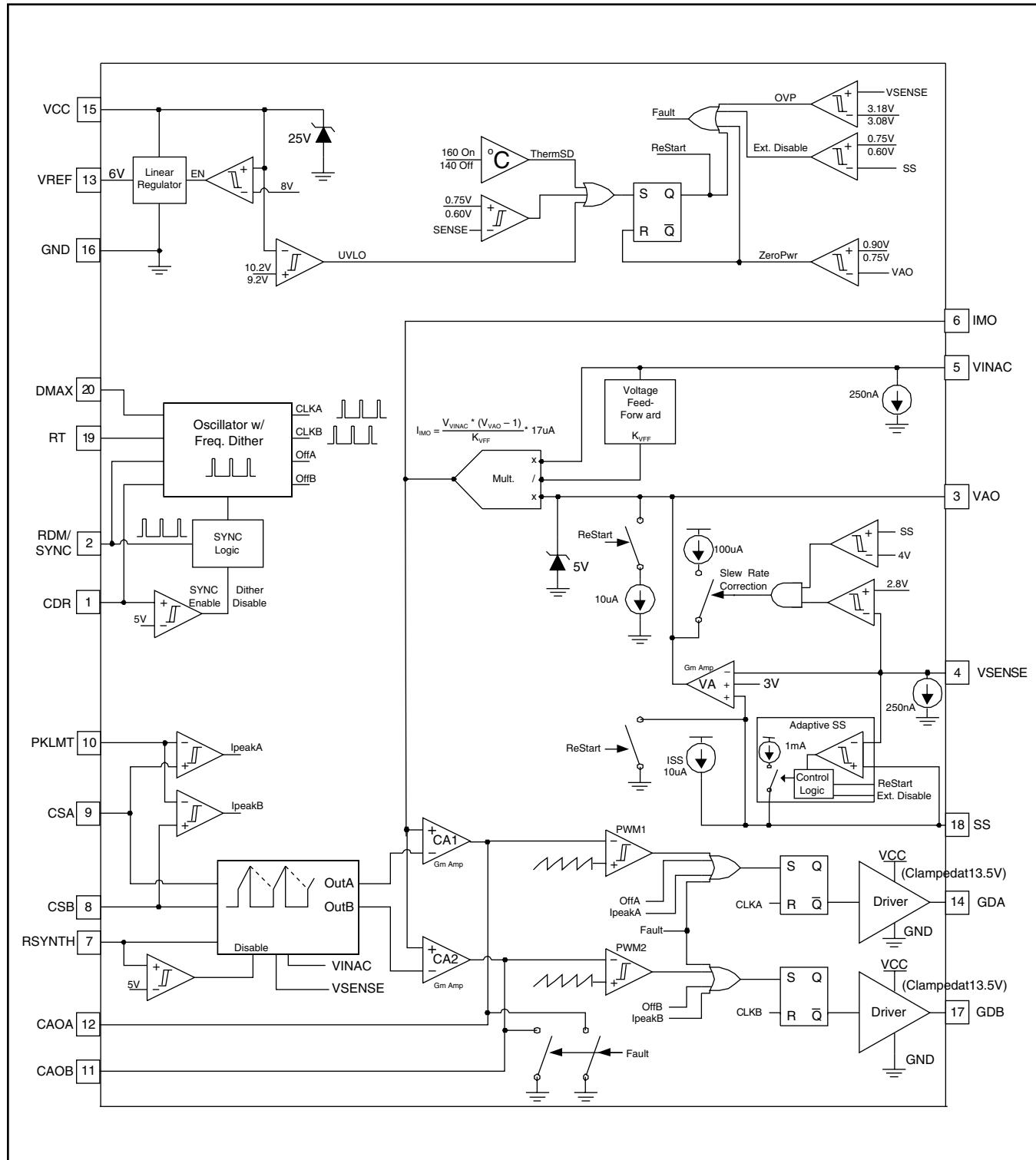

## Functional Block Diagram

## 代表的特性

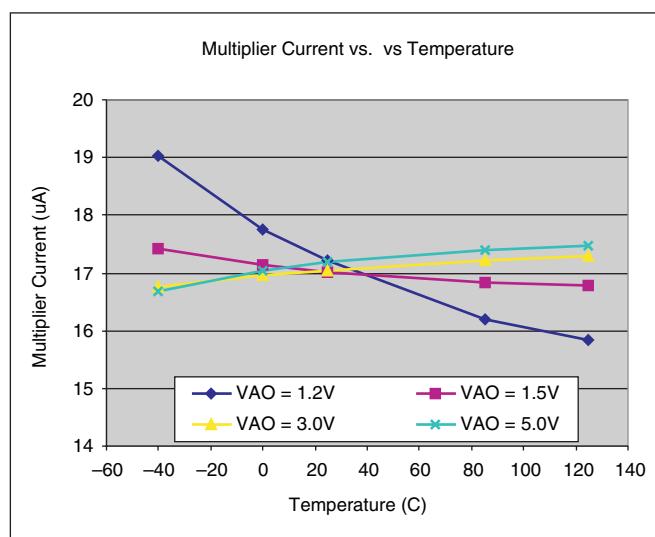

図1

図2

図3

図4

図5

図6

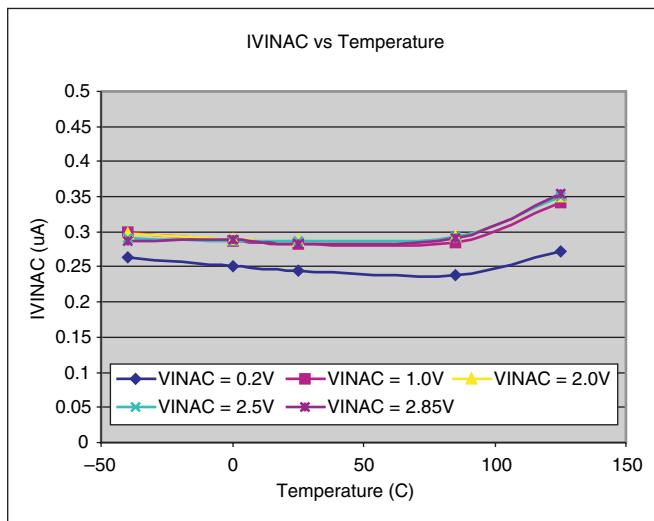

## 代表的特性

図7

図8

図9

図10

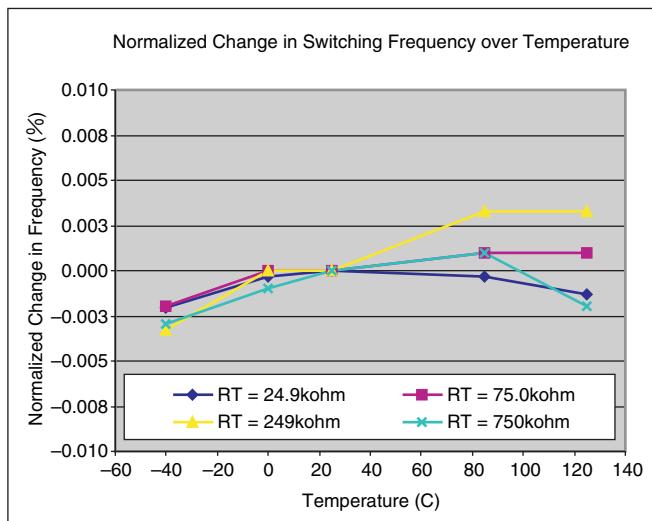

## 代表的特性

図11

図12

図13

図14

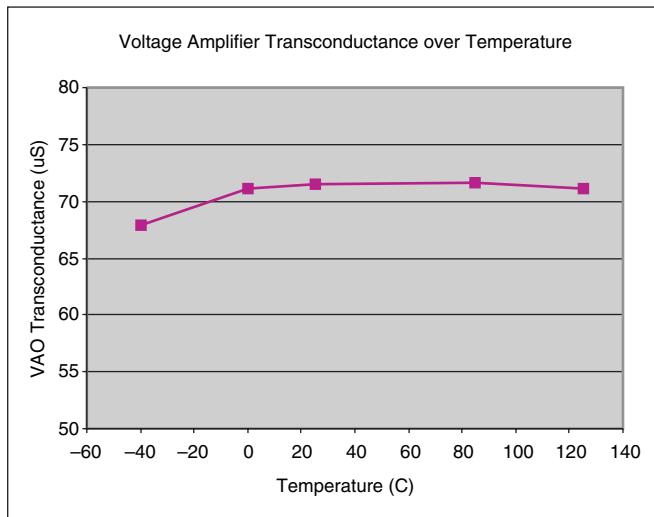

## 代表的特性

图15

图16

图17

# アプリケーション情報

## 動作原理

### インターリーブ動作

180°の位相インターリーブ動作の主な利点の1つは入力電流とPFCプリレギュレータの出力コンデンサへの電流の両方の高周波リップル成分が大幅に減少することです。電力の等しい単相のPFC段と比較して、入力電流のリップルが減少することは伝導性EMIノイズに対するフィルタの負荷が軽減し、EMIフィルタとC<sub>IN</sub>の大きさを減少させる手助けになります。さらに、PFCの出力コンデンサC<sub>OUT</sub>への高周波リップル電流が減少すると、その大きさやコストを低減するのに役立ちます。また、各相でのリップルの減少と平均電流により、ブースト・インダクタの大きさは単相での設計よりも小さくすることができます[1]。

インターリーブ動作によるリップル電流の減少はしばしば“リップルのキャンセル”と呼ばれますが、厳密に言えば、ピーク間リップルは2相システムで50%のデューティ・サイクルでのみ完全にキャンセルされます。50%以外のデューティ・サイクルでは、個々の位相電流が重ね合わされることにより一部分のキャンセルという形でリップルが低減します。それでも、同等の単相のPFCプリレギュレータのリップル電流に比べても、2相のインターリーブ設計でのリップル電流は極めて小さくなります[1]。リップルのキャンセルとは無関係に、インターリーブ動作によるリップルの周波数は、入力と出力の両方とも、 $2 \times f_{\text{PWM}}$ となります。

入力では、180°のインターリーブ動作によりピーク間のリップルの大きさは同等の単相電流のリップルの大きさの1/2以下に低減します。

出力では、180°のインターリーブ動作により出力コンデンサでのPFCで生じるリップル電流のRMS値はPWMのデューティ・サイクルが50%より大きいと $\sqrt{2}$ 倍より少し大きくなります。

このことは以下の式で理解することができます。

単相のPFCプリレギュレータでは、全てのデューティ・サイクルでPFC段により提供されるコンデンサの総RMS電流は以下の式で概算されます。

$$i_{\text{CRMS1}\phi} = \left( \frac{I_O}{\eta} \right) \sqrt{\left( \left( \frac{16V_O}{3\pi V_M} \right) - 1 \right) \eta^2} \quad (1)$$

2相のインターリーブ動作PFCプリレギュレータでは、50%より大きいデューティ・サイクルでPFC段により提供されるコンデンサの総RMS電流は以下の式で概算されます。

$$i_{\text{CRMS2}\phi} = \left( \frac{I_O}{\eta} \right) \sqrt{\left( \left( \frac{16V_O}{6\pi V_M} \right) - 1 \right) \eta^2} \quad (2)$$

これらの式で、I<sub>O</sub> = PFCの平均出力負荷電流、V<sub>O</sub> = PFCの平均出力電圧、V<sub>M</sub> = 入力交流ライン電圧のピーク電圧、η = これらの条件でのPFC段の効率です。i<sub>CRMS2φ</sub>の平方根の値はi<sub>CRMS1φ</sub>の平方根の値の1/2より少し小さくなります。示されているRMS電流値にはPFC出力電流の低周波成分と高周波成分の両方が含まれています。インターリーブ動作により高周波成分は減少しますが、低周波成分は減少しません。

### PWM周波数と最大デューティ・サイクル・クランプのプログラミング

UCC28070の両方のGDX出力に対するPWM周波数と最大デューティ・サイクル・クランプはそれぞれRTピンとDMAXピンに接続される抵抗を選択することで設定されます。RT抵抗(R<sub>RT</sub>)を選択することでPWM周波数(f<sub>PWM</sub>)が設定されます。

$$R_{\text{RT}}(\text{k}\Omega) = \frac{7500}{f_{\text{PWM}}(\text{kHz})} \quad (3)$$

R<sub>RT</sub>が決まると、DMAX抵抗(R<sub>DMAX</sub>)が得られます。

$$R_{\text{DMX}} = R_{\text{RT}} \times (2 \times D_{\text{MAX}} - 1) \quad (4)$$

但し、D<sub>MAX</sub>は目的とするPWMの最大デューティ・サイクルです。

### 周波数ディザリング(規模とレート)

周波数ディザリングはライン・フィルタの能力以上に伝導性EMIノイズを減少させるためスイッチング周波数を拡散することを行います。UCC28070は三角波変調方式を組み込んでおり、スイッチング周波数範囲のあらゆる点でかかる時間が等しくなります。最小周波数から最大周波数までの全範囲がディザー規模と定義され、R<sub>RT</sub>で設定される標準スイッチング周波数f<sub>PWM</sub>が中央値です。例えば、100kHzの標準f<sub>PWM</sub>で20kHzのディザー規模の場合周波数範囲は100kHz ±10kHzになります。さらに、R<sub>DMX</sub>で設定されるプログラムされたデューティ・サイクル・クランプは周波数ディザリングの全範囲にわたってプログラム値のまま一定です。

f<sub>PWM</sub>が極端に動き、また戻るレートがディザー・レートと定義されます。例えば、1kHzのディザー・レートとは標準周波数を1ミリ秒に1回110kHzから90kHz、110kHzに線形に変調することです。ディザー規模の初期設計での妥当な目標値はf<sub>PWM</sub>の±10%です。多くのブースト部品はそのようにf<sub>PWM</sub>が分散するのを許容することができます。よって、デザイナーはEMIの低減、部品の公差、ループ安定性で最良の妥協点を見出すためその付近の値で設計調整ができます。

目的とするディザイナー規格はRDMピンからGNDに接続される抵抗値で設定され、その値は以下の式で計算されます。

$$R_{RDM}(k\Omega) = \frac{937.5}{f_{DR}(\text{kHz})} \quad (5)$$

$R_{RDM}$ の値が決まると、目的とするディザイナー・レートはCDRピンからGNDに接続されるコンデンサで設定され、その値は以下の式で計算されます。

$$C_{CDR}(\text{pF}) = 66.7 \times \left( \frac{R_{RDM}(k\Omega)}{f_{DR}(\text{kHz})} \right) \quad (6)$$

周波数ディザーリングはCDRピンを5Vより大きくするか、またはVREF(6V)に接続しRDMピンを直接GNDに接続することで完全にディセーブルすることができます(RDM抵抗が実装された場合、ディザーリングがディセーブルの時低インピーダンスのパスでバイパスされていないと、RDM抵抗の相対的に大きなインピーダンスがシステムのスイッチング・ノイズを結合させ、コントローラのタイミング機能に干渉することがあります)。

$f_{PWM}$ を同期させるのに外部周波数源が使用され、かつ、周波数ディザーリングが必要とされる場合、内部のディザイナー回路が同期時不要な動作を防止するためにディセーブルとなるため外部周波数源がディザイナー規格とディザイナー・レート機能を供給してください(詳細については以下の項を参照してください)。

## 外部クロック同期

UCC28070はほぼ全ての外部周波数源に容易に同期するよう設計されています。周波数ディザーリングをディセーブルすることで(CDRピンを5Vより大きくする)、UCC28070のSYNC回路がイネーブルになり内部発振器がRDMピンのパルスに同期することを可能にします。確実に正確な180°の位相シフトがGDA出力とGDB出力の両方で維持されるには、RDMピンのパルスの周波数( $f_{SYNC}$ )は目標とする $f_{PWM}$ の2倍であることが必要です。例えば、目的とするスイッチング周波数が100kHzである場合、 $f_{SYNC}$ は200kHzでなければなりません。

$$f_{PWM} = \frac{f_{SYNC}}{2} \quad (7)$$

確実に内部発振器がSYNC機能に干渉しないようにするため、 $R_{RT}$ は内部発振器周波数を $f_{SYNC}$ よりも10%低く設定する必要があります。PWM変調器のゲインはPWMランプ電流と $R_{RT}$ には直接的な相関関係があるため $R_{RT}$ が拡大縮小されるのと同じ率で低減することに注意してください。電流ループのゲインの調整はそれに沿って行われなければなりません。

外部同期時は最大デューティ・サイクル・クランプのプログラムの可能性も影響されることにも注意してください。最大デューティ・サイクルの設定に関与している内部タイミング回路は同期パルスの立ち下がりエッジで起動します。よって、 $R_{DMX}$ の選択は同期パルス幅( $t_{SYNC}$ )に依存するようになります。

$$t_{OFF} = \frac{2 \times (1 - D_{MAX})}{f_{SYNC}} \quad (8)$$

$R_{DMX}$ の式は以下のようになります。

$$R_{DMX}(k\Omega) = \frac{\frac{1}{f_{SYNC}} t_{SYNC} - t_{OFF}}{66 \times 10^{-9}} \quad (9)$$

従って $t_{SYNC}$ の影響を最小限に抑えるには、実現可能な最小の同期パルス幅を利用することが明らかに有利になります。

$$R_{RT}(k\Omega) = 1.1 \times \frac{15000}{f_{SYNC}(\text{kHz})} \quad (10)$$

$$f_{SYN(maxD)} \leq 0.9 \times (2 \times D_{MAX} - 1) \quad (11)$$

注：外部同期が用いられた時、約50ns～100nsの伝搬遅延が内部タイミング回路とSYNC信号の立下りエッジ間に存在し、その結果スイッチング周波数の最大時オフ時間が減少するようになります。よって、 $R_{DMX}$ は補償用に( $T_{SYNC}=0.1\mu\text{s}$ )/ $T_{SYNC}$ ほど少し低く調整しなければなりません。SYNC周波数が低い時は、この遅延はPWM期間で重要でなくなり、無視することができます。

## 多相動作

外部同期によりインターリープ動作に2相より多い相を用いることが容易になります。大電力アプリケーション用に複数のUCC28070を並列接続して偶数の相を追加することが簡単にできます。適切に同期信号の位相シフトを行うことで、さらなる入出力リップル電流のキャンセルを行うことができます(必要なら奇数の位相にも対応可能ですが、リップルのキャンセルは最適とはなりません)。4相、6相、いかなる2のn倍の相(nはUCC28070コントローラ数)では、各コントローラは $360/n^{\circ}$ 位相が互いにずれているSYNC信号を受け入れる必要があります。2つのコントローラでインターリープ動作を行う4相の場合、最適なリップルのキャンセルを行うにはSYNC1はSYNC2と $180^{\circ}$ の位相ずれでなければなりません。同様に6相のシステムでは、最適なリップルのキャンセルを行うにはSYNC1、SYNC2、SYNC3は互いに $120^{\circ}$ の位相ずれの必要があります。

多相のインターリープ・システムでは、各電流ループは独立しており、別々に処理されますが、電圧ループは共通で1つだけです。单一コントロール・ループを維持するため、VSENSE、VINAC、SS、IMO、VAOの全信号はn個のコントローラ間でそれぞれ並列となります。電流源の出力は結合され(SS、IMO、VAO)、計算される負荷インピーダンスは单一コントローラの場合と同じ性能を保持するよう $1/n$ に調整しなければなりません。図18に、4相で $90^{\circ}$ のインターリープ動作を行うPFCシステム用に構築した2つの並列コントローラを示します。

## VSENSE、VINAC抵抗構成

VSENSE入力の主な目的は出力から電圧コントロール・ループに電圧フィードバックを供給することです。よって、VSENSEでの3Vのレギュレーション電圧に基づいて目的とする出力電圧を設定するため出力コンデンサとVSENSEピン間に従来どおりの抵抗分圧回路を大きさを決め接続することが必要です。

UCC28070の独特な点とはVINACピンに対しインダクタのV<sub>IN</sub>側に同一の抵抗分圧回路を置くことが必要であるということです。このことにより線形乗算器と電流合成回路に必要とされる上下された入力電圧をモニタすることができます。VINAC回路の実際の抵抗はVSENSE回路と同一である必要はありませんが、PFC動作を適切に行うにはこの2つの分圧回路の減衰係数( $k_R$ )が等しいことが必要となります。

$$k_R = \frac{R_B}{(R_A + R_B)} \quad (12)$$

ノイズの多い環境での対応策は、VSENSE入力とVINAC入力に小さなフィルタ・コンデンサを接続して過度のノイズによりこれらの入力が不安定となることを避けることです。これらを接続した場合は、出力の過渡応答が大きく遅延することを避けるためVSENSE入力のRC時定数は $100\mu s$ を越えないでください。また、波形のゼロクロスが低下することを避けるためVINAC入力のRC時定数も $100\mu s$ を越えないでください。通常、VSENSEとVINACの典型的なノイズをフィルタで除去するには $3/f_{PWM}$ の時定数で十分です。特定のアプリケーションに必要な最適のフィルタ量を見出すために何回かの設計及びテストを繰り返すことが必要となる場合があります。

## VSENSE、VINACオープン回路保護

VSENSEピンとVINACピンの両方とも、どちらかのピンオープンが起こった場合に、異常動作モードにならないように、 $250nA$ の電流シンクを内蔵しています。

図18. Simplified Four-Phase Application Diagram Using Two UCC28070

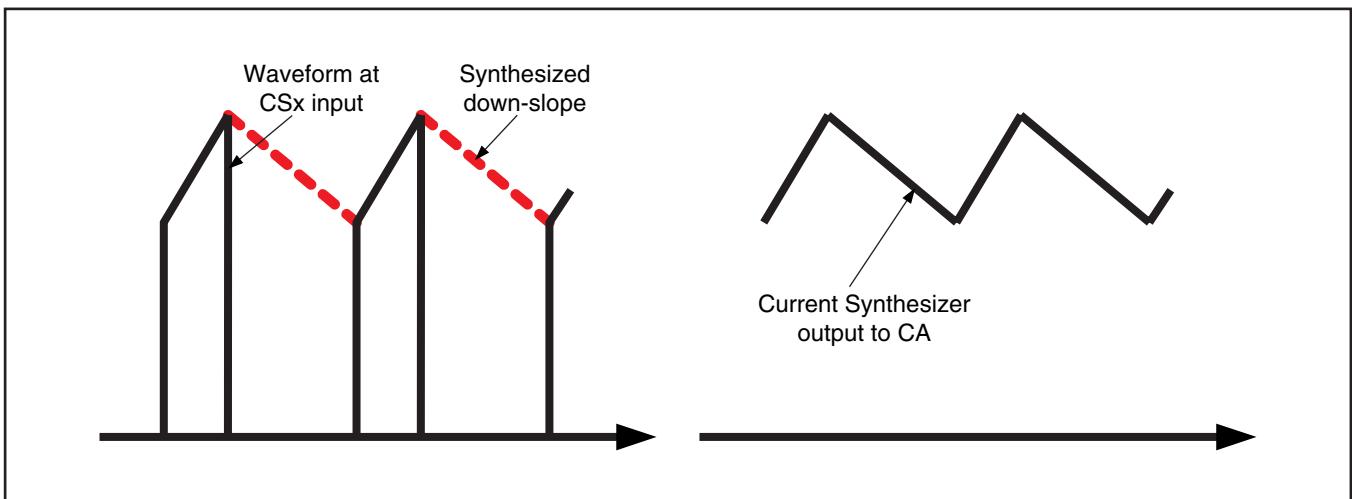

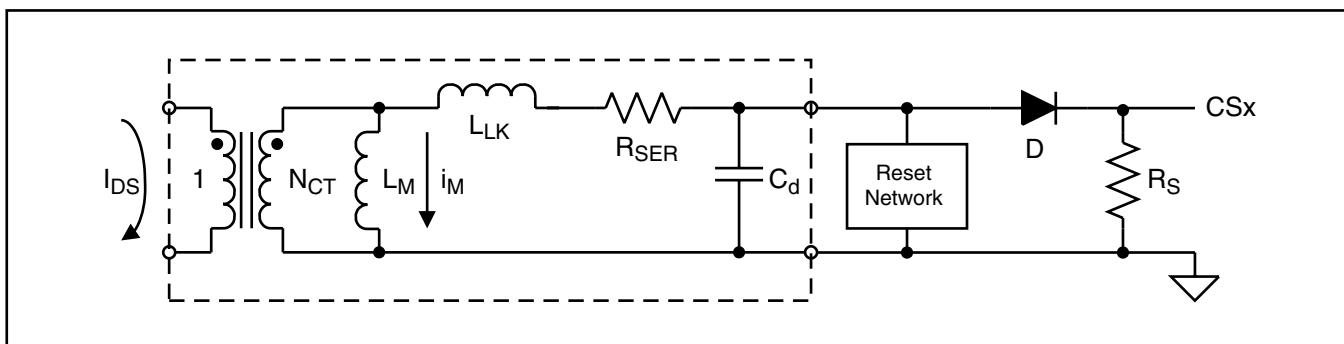

## 電流シンセサイザー

UCC28070の設計でもっとも卓越した革新的手法の1つがインダクタの瞬時電流をオン時間サンプリングとオフ時間ダウントロープ・エミュレーションの組み合わせにより同期的にモニタする電流合成回路です。

GDA出力とGDB出力のオン時間で、インダクタ電流は各出力フェーズの電流トランスマス回路を介してそれぞれCSAピンとCSBピンに計上されます。その一方、VINACピンとVSENSEピンを介して入出力電圧を連続してモニタすることで各出力のそれぞれのオフ時間でインダクタ電流のダウントロープを内部で再生成することができます。以下の式により、RSYNTH抵抗( $R_{SYN}$ )を選択することで、内部応答は幅広いアプリケーションで期待される広範囲のインダクタンスに対応するよう調整することができます。

起動時や交流電圧降下後の復帰時に突入電流により電圧が急激に変化する場合、VINACはVSENSEより大きいため、合成されたダウントロープはゼロになります。この場合、合成されたインダクタ電流はIMO基準電流より大きい今まで、電流ループ

はデューティ・サイクルをゼロにします。このことにより、電圧が急激に変化した時MOSFETに過度のストレスがかかることが回避されます。VINACがVSENSEより低くなると、デューティ・サイクルは定常状態動作が再開するまで増加します。

$$R_{SYN}(k\Omega) = \frac{(10 \times N_{CT} \times L_B (\mu H) \times k_R)}{R_S (\Omega)} \quad (13)$$

変数は以下のとおりです。

- $L_B$  = ゼロ・バイアスの標準ブースト・インダクタンス ( $\mu H$ )

- $R_S$  = 検出抵抗 ( $\Omega$ )

- $N_{CT}$  = 電流検出トランスマスの巻線比

- $k_R = R_B / (R_A + R_B) = VSENSE ピンと VINAC ピンでの抵抗分圧の減衰係数$

図19. Inductor Current's Down Slope

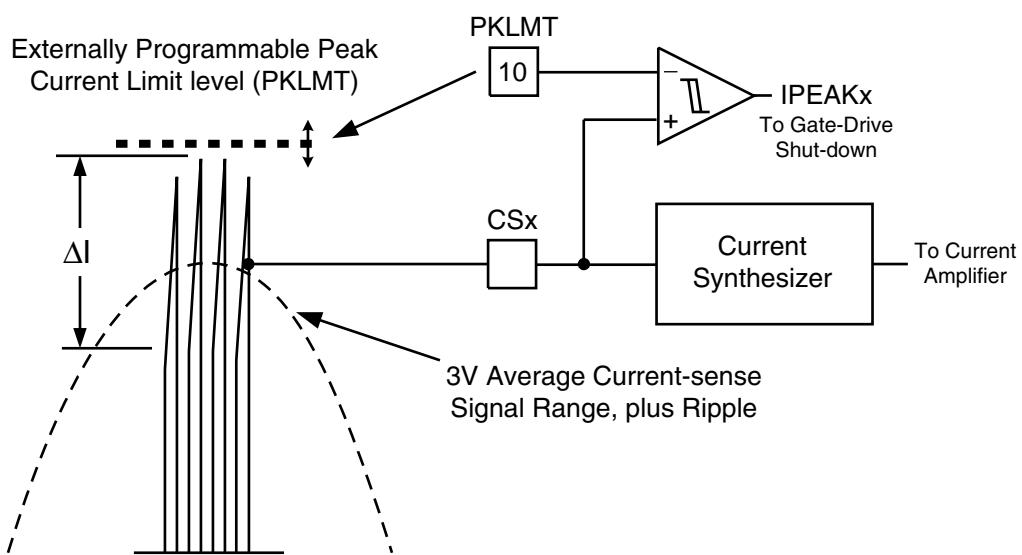

## プログラム可能なピーク電流制限

UCC28070には、対応する電流検出入力（それぞれCSAとCSB）がPKLMTピンに構築された電圧より高くなった時、GDA出力またはGDB出力をディセーブルにするcycle-by-cycle ピーク電流制限回路が内蔵されており、設定値のプログラムが可能です。出力がピーク電流制限の検出によりディセーブルになると、出力は次のクロック・サイクルにより新しいPWM期間が開始されるまでディセーブルのままでです。PKLMT電圧のプログラム範囲は4V以上と広いため、3Vの平均電流検出信号範囲を最大限に活用することができますが、電流増幅器の直線性は3.6V以上で圧縮し始めるに注意が必要です。

6VのVREF電圧のドリープを回避するためVREFから流れる総電流が2mAより低ければ、VREFからGNDの抵抗分圧回路によりPKLMTのピーク電流制限電圧を容易にプログラムすることができます。0.5mAより小さい負荷を推奨しますが、PKLMTの抵抗が高い場合、高ノイズの環境における動作上の問題を回避するためPKLMTに小さなフィルタ・コンデンサを接続することを推奨します。

図20. Externally Programmable Peak Current Limit

## 線形乗算器

UCC28070の乗算器は目的とする波形と交流入力電流に比例した大きさの基準電流を生成します。この電流は $R_{IMO}$ 抵抗により基準電圧信号に変換され、電流検出信号の電圧に合致する値に増減されます。瞬時乗算器電流は整流され増減された入力電圧 $V_{VINAC}$ と電圧増幅器の出力 $V_{VAO}$ により決まります。 $V_{VINAC}$ 信号は乗算器に以下の3つの情報を送ります。

1. 入力電圧の全波形(通常は正弦波)

2. ライン・サイクルの全ての点での瞬間入力電圧の大きさ

3. 入力電圧のRMSレベル

$V_{VAO}$ 信号はPFCプリレギュレータの総出力電力を表しています。

UCC28070の乗算器アーキテクチャの主な革新的手法とは段階的に調整された $V_{RMS}$ フィードフォワード(QVFF)回路が内蔵されていることで、これによりVINAC信号の外付けフィルタが必要になり、その後の過渡ラインの変動に対する応答が遅くなることが解消されます。独特の回路アルゴリズムが7つのスレッショルドにより $V_{VINAC}$ のピークの遷移を検出し、8つのQVFF範囲の中の中央の等価VFFレベルを生成します。この範囲の境界はレベル間の差分がおよそ等しい割合となるよう $V_{IN}$ が増加するにつれ広がってゆきます。この8つのQVFFレベルは85V - 265V<sub>RMS</sub>の“一般的な”ライン電圧範囲の全てに対応するよう間隔があけられています。

QVFF 技法の大きな利点は、回避不可能な第二高調波歪成分を含み外部でフィルタされるVINAC信号とは異なり、固定のkVFFファクタが乗算器出力の歪みの原因を除去することができます。さらに、QVFFアルゴリズムによりPFC出力へ送られる外乱が最小限となるよう入力RMS電流の増減変化に対する高速応答が可能になっています。レベル・スレッショルドの5%のヒステリシスは、あるスレッショルドに近いか、または軽度のリンクギングもしくは歪みを含む $V_{VINAC}$ 電圧に対しQVFFレベル間の“チャタリング”を回避する手助けになります。QVFF 技法では入力電圧は主として正弦波であることが必要であり、入力電圧の減少時QVFFを下方に調整するためゼロクロスを検出することに依存しています。ゼロクロスは一般的に最小50μs間 $V_{VINAC}$ が0.7Vより下がるということで定義されます。

表1に乗算器の式での各種VINACピーク電圧とそれに対応するkVFF項の関係を示します。

| レベル | $V_{VINAC}$ ピーク電圧                  | $k_{VFF} (V^2)$ | $V_{IN}$ ピーク電圧 <sup>(1)</sup> |

|-----|------------------------------------|-----------------|-------------------------------|

| 8   | $2.60V \leq V_{VINAC(pk)}$         | 3.857           | > 345V                        |

| 7   | $2.25V \leq V_{VINAC(pk)} < 2.60V$ | 2.922           | 300V ~ 345V                   |

| 6   | $1.95V \leq V_{VINAC(pk)} < 2.25V$ | 2.199           | 260V ~ 300V                   |

| 5   | $1.65V \leq V_{VINAC(pk)} < 1.95V$ | 1.604           | 220V ~ 260V                   |

| 4   | $1.40V \leq V_{VINAC(pk)} < 1.65V$ | 1.156           | 187V ~ 220V                   |

| 3   | $1.20V \leq V_{VINAC(pk)} < 1.40V$ | 0.839           | 160V ~ 187V                   |

| 2   | $1.00V \leq V_{VINAC(pk)} < 1.20V$ | 0.600           | 133V ~ 160V                   |

| 1   | $V_{VINAC(pk)} \leq 1.00V$         | 0.398           | < 133V                        |

表1. VINACピーク電圧

(1) 上記の $V_{IN}$ ピーク電圧の境界値は400VのPFC出力電圧、及びVINACとVSENSEの同一抵抗分圧回路( $k_R = 3V/400V = 0.0075$ )の使用に基づいて計算されています(電流合成に必要)。 $V_{OUT}$ が400Vより上または下に設計された時、 $k_R = 3V/V_{OUT}$ で各QVFFレベルに対する $V_{IN}$ ピーク電圧の境界値は $V_{VINAC(pk)}/k_R$ に調整されます。

全てのライン/負荷状態での乗算器の出力電流 $I_{IMO}$ は以下の式で決まります。

$$I_{IMO} = \frac{17\mu A \times (V_{VINAC}) \times (V_{VAO} - 1)}{k_{VFF}} \quad (14)$$

$k_{VFF}$ の値はレベルの中央での増減された $V_{RMS}^2$ を表しているため、 $V_{VAO}$ は差分を調整するため $V_{INAC_{pk}}$ が $Q_{VFF}$ 電圧範囲の中央より高いかまたは低い場合には、少し上下に調整します。このことは $V_{IN}$ がレベル内及びレベル間での遷移後変化した時に電圧ループ・コントロールにより自動的に行われます。

電圧誤差增幅器の出力 $VAO$ は5.0Vにクランプされており、これはPFCの最大出力電力を表しています。この値はIMOピンでの最大基準電流を計算するのに用いられ、最大許容入力電力の限界値を設定します(結果として最大出力電力を制限します)。

最大入力電力がいかなる $V_{RMS}$ 入力でも固定電力である連続した $V_{FF}$ 状態とは異なり、不連続の $Q_{VFF}$ レベルは入力 $V_{RMS}$ が各レベル内で変化する時最大入力電力の変動を限られた境界内に収めます。

もっとも低い最大電力制限は $V_{INAC}$ 電圧が0.76Vの時に起こり、一方、もっとも高い最大電力制限はスレッショルドがレベル1からレベル2に増加する時に起こります。この傾向はあらゆるレベルの遷移スレッショルドで繰り返されるため、減少スレッショルドは増加スレッショルド値の95%であるということを留意しておきます。 $V_{INAC}$ が0.76Vより低い時は、 $P_{IN}$ は常に $P_{IN(max)}$ より小さく、入力電圧が減少してゆくと直線的にゼロに低下します。

例えば、もっとも低い最大許容電力を設計するためには、PFCプリレギュレータに必要な定常状態(平均)の最大出力電力を決め、ライン電圧の降下からの復帰電力(全負荷電力時に $C_{OUT}$ を再充電するため)を計上するため $P_{OUT(max)}$ の10%ないし20%といった少しマージンを追加します。次に、もっとも低い最大許容入力電力を求めるため予想される効率ファクタを当てはめます。

$$P_{IN(max)} = \frac{1.10 \times P_{OUT(max)}}{\eta} \quad (15)$$

$P_{IN(max)}$ の設計スレッショルドでは、 $V_{VINAC} = 0.76V$ 、よって400Vの標準出力システムでは $Q_{VFF} = 0.398$ 、入力VAC = 73V<sub>RMS</sub>(2Vのブリッジ整流器の電圧降下を計上)です。

$$\text{Thus } I_{IN(rms)} = \frac{P_{IN(max)}}{73V_{RMS}}, \text{ and } I_{IN(pk)} = 1.414 \times I_{IN(rms)} \quad (16)$$

この $I_{IN(pk)}$ 値はライン電圧のピーク時にブースト・インダクタを流れる結合した平均電流を表しています。各インダクタ電流は電流検出トランジスト(CT)で検出され拡大縮小されます。インターリード動作の各相を流れる電流は等しいと仮定すると、各電流検出ピン(CSAとCSB)での信号電圧は、 $(1/2) \times I_{IN(pk)} \times R_S/N_{CT}$ をもとに3Vまでの電圧を生成するよう選択された検出抵抗端に生じます。ここで、 $R_S$ は電流検出抵抗で $N_{CT}$ はCTの巻線比です。

よって、 $I_{IMO}$ は以下のように同一のもっとも低い入力電圧での最大電力点で計算されます。

$$I_{IMO(max)} = 17\mu A \times \frac{(0.76V)(5V - 1V)}{0.398} = 130\mu A \quad (17)$$

$R_{IMO}$ は以下のように選択されます。

$$R_{IMO} \times I_{IMO(max)} = \left(\frac{1}{2}\right) \times I_{IN(pk)} \times \frac{R_S}{N_{CT}} \quad (18)$$

従って、

$$R_{IMO} = \frac{\left(\frac{1}{2}\right) \times I_{IN(pk)} \times R_S}{(N_{CT} \times I_{IMO(max)})} \quad (19)$$

レベル1からレベル2のスレッショルドへ増加する方向で、IMO電流は低ラインでより大きな電流を流すことができるということに注意してください。

$$I_{IMO(L1-L2)} = 17\mu A \times \frac{(1.0V)(5V - 1V)}{0.398} = 171\mu A \quad (20)$$

しかしながら、必要ならこの電流はパワーワークの設計でUCC28070のプログラマブル・ピーク電流制限(PKLM)機能により容易に制限することができます。

それぞれの $Q_{VFF}$ レベルの遷移スレッショルドで最小及び最大入力電力制限を求めるのに同じ手順を使用することができます。インダクタにリップルをもつ平均電流が従来どおりPKLMスレッショルドより低い高ライン電圧時では、最大入力電力に大きな変動が現れます。入力電流は本質的にパワーワークの最大許容電流レベルより低くなります。

UCC28070の乗算器の性能はほとんどの入力範囲にわたって高い直線性と精度の点で、前世代のPFCコントローラと比較しても大幅に改善されています。精度は、 $(V_{VAO}-1)$ 減算の誤差が増加しIMO基準電流を大きく歪ませはじめると $V_{VAO}$ が1Vに近づくにつれ最悪になります。

## 過渡応答の改善(VAスルーレートの補正)

適切なPFCを維持し出力の極めて小さな120Hzリップルを無視するのに必要とされる電圧ループ帯域幅が低いため、入力電圧と負荷過渡に対する通常のコントローラの応答は遅くなります。しかし、QVFF機能がQVFFレベル内の必要な微調整を除いてラインの過渡応答を効率的に処理します。その一方、負荷過渡は電圧ループのみで処理されるため、UCC28070は、VSENSE電圧がレギュレーションの93% (2.79V) より下がった場合、100 $\mu$ Aの電流を付加して電圧増幅器の出力 (VAO) をプルアップすることで過渡応答を改善するよう設計されています。ソフトスタート・サイクル時、VSENSEが0.75VのPFCイネーブル・スレッショルドから上昇している時、100 $\mu$ Aの補正電流源はソフトスタート時の出力電圧 / 電流が確実に緩やかに、またコントロールされた上昇を行えるようディセーブルになります。

## 電圧バイアス (VCCとVREF)

UCC28070は10Vから21VのVCCバイアス電源範囲内で動作します。低電圧ロックアウト (UVLO) スレッショルドによりVCCが10.2Vより高くなるまで始動しないようにし、1Vのヒステリシスにより供給能力の低いバイアス源からの確実な起動が保証されます。VCC内部の25Vのツェナーはバイアス電源からの限られたエネルギーをもつ短期間のサージからデバイスを保護するためだけの目的であり、電流制限された電圧源のレギュレータとして使用することはできません。

バイアス電源にローカル・フィルタを施すため最小0.1 $\mu$ Fのセラミック・バイパス・コンデンサをデバイスのピンに近づけてVCCからGNDに接続しなければなりません。VCCのリップル電圧を最小限に抑えるためI<sub>CC</sub>ピーク電流の大きさや継続時間によってはこれより大きな値が必要となることがあります。

UVLOから円滑に遷移させるため、また、できるだけ早く6Vの基準電圧が使用できるようにするために、VREF出力はVCCが標準で8Vを越えた時イネーブルになります。

VREF回路は内部の全コントロール回路のバイアスを供給するため、また、外部での限定使用のために設計されています。回路の安定性を確実にするため最小22nFのセラミック・バイパス・コンデンサをデバイスのピンに近づけてVREFからGNDに接続しなければなりません。VREFの外部負荷電流は2mAより低い値に制限しなければなりません。そうしないと、レギュレーションが劣化することがあります。

## PFCイネーブルとディセーブル

UCC28070にはVSENSEピンまたはSSピンのバイアス状態に基づいてGDx出力をディセーブルにする専用の回路が2つそれぞれ独立して内蔵されています。VVSENSEをモニタする最初の回路は、出力が25%までプリチャージするまでソフトスタートと全PFC機能を留保する従来のPFCイネーブルです。VVSENSEが0.75Vに達するまでは、ほとんど全ての内部回路はディセーブルです。VVSENSEが0.75Vに達し、VAOが0.75Vより低いと、発振器、乗算器、電流合成がイネーブルになり、SS回路はSSピンの電圧を上昇させ始めます。2番目の回路は、電圧ループと乗算器を完全にはディセーブルすることなくGDx出力をディセーブルにするため内部異常状態に匹敵した情報を外部インターフェイスに供給します。外部からSSピンを0.6Vより低くすることで、GDx出力は直ちにディセーブルになり“L”レベルに保持されます。ほかに異常状態がないとすると、外部からSSピンのプルダウンが解除された時、通常のPWM動作が再開します。外部からのプルダウンは、内部の1.5mAプルアップを十分シンクして、SS電圧が確実にディセーブルとなるような回路とするよう注意してください。確実にSSピンがディセーブル・スレッショルドより十分に低くなるようR<sub>DS(on)</sub>が100 $\Omega$ より小さいMOSFETを使用することを推奨します。

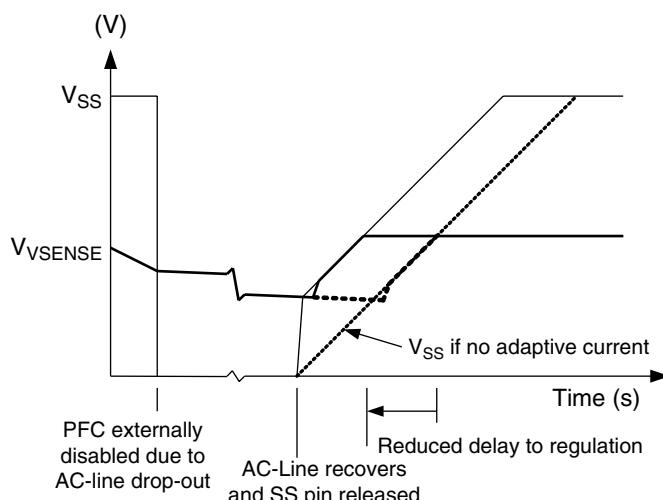

## アダプティブ・ソフトスタート

起動がコントロールされて行われるよう、UCC28070には起動時に内部基準電圧を無効にしコントロールされた電圧ランプを用いるアダプティブ・ソフトスタート機能が設計されています。最初の起動時、 $V_{VSENSE}$ が0.75Vのイネーブル・スレッショルド ( $V_{EN}$ ) を越えると、SSピンの内部プルダウンが解除され、1.5mAのアダプティブ・ソフトスタート電流源が作動します。この1.5mAのプルアップは、従来の0Vから $V_{regulation}$ へのSSランプ時にデッドタイムの初めの25%をバイパスするため、ほぼすぐにSSピンを0.75V ( $V_{VSENSE}$ ) にします。SSピンが $V_{SENSE}$ の電圧に達すると、10μAのソフトスタート電流 ( $I_{SS}$ ) に引き継がれます。よって、ソフトスタート・コンデンサ ( $C_{SS}$ ) を選択することにより、実効ソフトスタート時間 ( $t_{SS}$ ) を以下の式により容易にプログラムすることができます。

$$t_{SS} = C_{SS} \times \left( \frac{2.25V}{10\mu A} \right) \quad (21)$$

多くの場合、短期間のシャットダウンの後にシステムのリスタートが求められます。このような場合、 $V_{SENSE}$ は、 $V_{OUT}$ が完全には放電されていないか、または高ラインが $C_{OUT}$ をピーク充電してしまうと、いまだに大きな電圧があることがあります。

$C_{SS}$ を10μAの電流源のみで0Vからプリチャージされた $V_{VSENSE}$ まで充電することにより生じる遅延を除去し、出力電圧のさらなる下落を最小限に抑えるために、アダプティブ・ソフトスタートは、1.5mAの電流源を使用して $C_{SS}$ を $V_{VSENSE}$ まで急速充電し、その後、10μAの電流源が目的とするソフトスタートのランプ・レートとなるよう $V_{SS}$ をコントロールします。このような場合、 $t_{SS}$ は以下の式により見積もられます。

$$t_{SS} = C_{SS} \times \left( \frac{3V - V_{VSENSE0}}{10\mu A} \right) \quad (22)$$

但し、 $V_{VSENSE0}$ はソフトスタートまたはリスタートが起動した時の $V_{SENSE}$ の電圧です。

注：ソフトスタートが有効になり、 $V_{OUT}$ のオーバーシュートを回避するためには、SSランプは電圧ループ・コントロールの応答よりも遅くなければなりません。このことを確実にするため $C_{SS}$ は $C_{VZ}$ より大きくなるよう選択してください。

図21. Soft-Start Ramp Rate

## PFCスタートアップ・ホールド・オフ

UCC28070で設計されている付加機能として、VAOがゼロパワーのスレッショルド(0.75V)より低くなるまでデバイスはソフトスタート・サイクルを始動しないようにする“スタートアップ・ホールド・オフ”ロジックがあります。この機能により、確実にSSサイクルはVAO補償回路の蓄積電荷による大きな突入電流が生じる可能性を回避すると同時にゼロパワー及びゼロのデューティ・サイクルから始動することができます。

## 出力過電圧保護(OVP)

出力コンデンサは電圧出力が高く設計マージンに限界があるため、PFC回路には出力の過電圧保護が不可欠です。UCC28070はVSENSE電圧を連続してモニタすることでOVPを実行します。V<sub>VSENSE</sub>がレギュレーション電圧の106% (3.18V)より高くなった場合、出力電圧が過度のレベルまで達しないようGDX出力は直ちにディセーブルになります。その一方、CAOx出力はOVP異常が解除された後コントロールされた復帰手順が確実に0%のデューティ・サイクルから開始するよう“L”レベルになります。V<sub>VSENSE</sub>電圧が3.08Vより低くなると、PWM動作は通常動作を再開します。

## ゼロパワーの検出

無負荷及びほぼ無負荷に近い状態での好ましくない動作を回避するため、UCC28070はVAO電圧が0.75Vより下がった場合はゼロパワー検出コンパレータがGDAとGDB出力の両方をディセーブルするよう設計されています。150mVのヒステリシスによりVAOが上昇し乗算器の線形範囲(VAO ≥ 0.9V)にほぼ戻るまで確実に出力はディセーブルのままです。

## サーマル・シャットダウン

温度が過度に高い時電源が異常にならぬようにするため、チップ温度が160°Cより高くなると、UCC28070はGDAとGDB出力をディセーブルにする温度検出コンパレータが内蔵されているので、ほぼ全ての内部回路をシャットダウンします。チップ温度が140°Cより低くなると、デバイスは標準のソフトスタートにより出力を上昇させます。

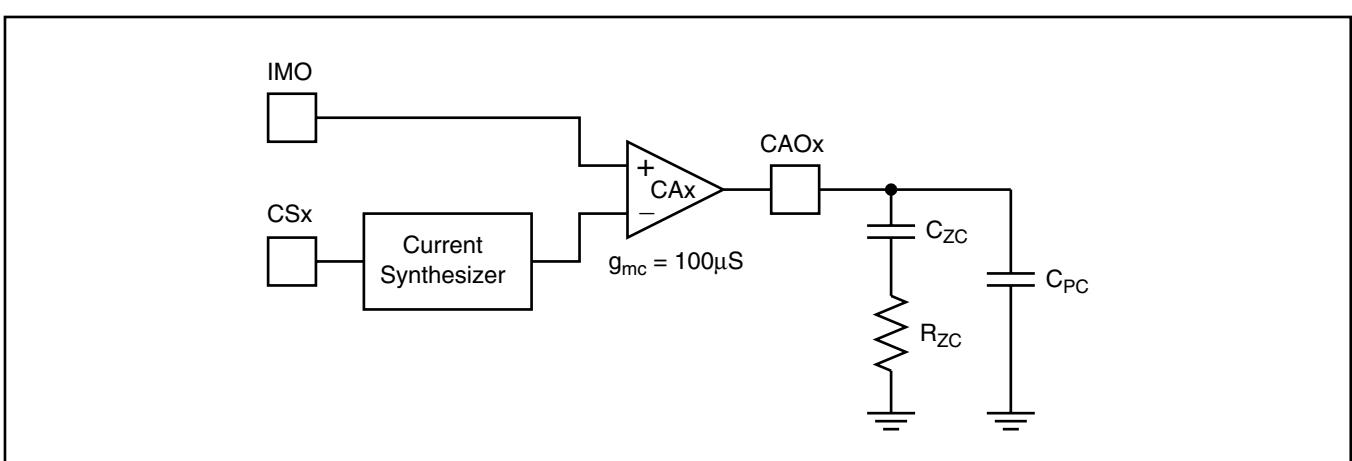

## 電流ループの補償

UCC28070はPFC入力電流波形の整形をコントロールする2つの同一で独立したトランスクンダクタンス・タイプの電流誤差増幅器(各相に1つずつ)を内蔵しています。電流誤差増幅器(CA)はブーストPFCプリレギュレータに組み込まれた電流コントロール・ループの中心部を形成し、よく知られている原理[4, 5]を用いてループの安定性を補償します。フェーズAのCAの出力はCAOAで、フェーズBのCAの出力はCAOBです。設計で考慮する事項は両方とも同じであるため、それらはまとめてCAOxと見なします。ここで“x”は“A”または“B”です。

ブーストPFCプリレギュレータでは、電流コントロール・ループはブースト・パワー段、電流検出回路、波形整形基準回路、PWM段、補償部品をもつCAから成っています。CAは乗算器段からの波形整形基準回路で検出された平均ブースト・インダクタ電流を比較し、差分に比例した出力電流を生成します。

このCA出力電流は補償回路のインピーダンスを流れ、出力電圧V<sub>CAO</sub>を生成し、次にPFCを実現するのに必要なPWM信号を生成するため周期的な電圧ランプと比較されます。

ブーストLC共振周波数より高く、f<sub>PWM</sub>より低い周波数では、ブースト段の小信号モデルは、電流検出機能を含んでおり、それは以下の式のように簡素化されます。

$$\frac{V_{RS}}{V_{CA}} = \frac{V_{out} \times R_S / N_{CT}}{\Delta V_{RMP} \times K_{SYNC} \times s \times L_B} \quad (23)$$

但し、L<sub>B</sub>はブースト・インダクタンスの中央値、R<sub>S</sub>はCT検出抵抗、N<sub>CT</sub>はCTの巻線比、V<sub>OUT</sub>は平均出力電圧、ΔV<sub>RMP</sub>はPWM電圧ランプの4V<sub>pk-pk</sub>の振幅、k<sub>SYNC</sub>はランプ減衰係数(PWM周波数が外部発振器に同期している場合。そうでない場合はk<sub>SYNC</sub> = 1)、sはラプラス複素変数です。

インダクタ電流信号の低周波成分用に高ゲインを得るためにR<sub>ZC</sub>C<sub>ZC</sub>回路がCAOxに導入されますが、信号の高周波スイッチング・リップル成分を減衰させるためゼロ周波数からf<sub>PWM</sub>までゲインは減少し均一になります(このように平均化します)。

図22. Current Error Amplifier With Type II Compensation

スイッチング時のリップル電圧は、“無視できる”リップルと見なされるよう $\Delta V_{RMP}$ 振幅の1/10より低く減衰されなければなりません。

よって、 $f_{PWM}$ 時のCAOxのゲインは以下のようになります。

$$g_{mc} R_{zc} \leq \frac{\Delta V_{RMP} \times k_{SYNC}}{\Delta I_{LB} \times \frac{R_s}{N_{CT}}} \times \frac{1}{10} \quad (24)$$

但し、 $\Delta I_{LB}$ はブースト・インダクタの最大ピーク間リップル電流、 $g_{mc}$ はCAのトランスコンダクタンスで100 $\mu$ sです。

$$R_{zc} \leq \frac{4V \times N_{CT}}{10 \times 100\mu S \times \Delta I_{LB} \times R_s} \quad (25)$$

次に、電流ループのクロスオーバー周波数は開ループのゲインを1とすることで求められ、 $f_{CXO}$ について解くと以下のようにになります。

$$f_{CXO} = \frac{V_{out} \times \frac{R_s}{N_{CT}}}{\Delta V_{RMP} \times k_{SYNC} \times 2\pi \times L_B} \times g_{mc} R_{zc} \quad (26)$$

次に、 $C_{ZC}$ は $f_{ZC} = f_{CXO} = 1 / (2\pi R_{ZC} C_{ZC})$ に設定し $C_{ZC}$ について解くことで決まります。 $f_{ZC} = f_{CXO}$ の場合、 $f_{CXO}$ での位相余裕は45°になります。 $f_{ZC} < f_{CXO}$ にすると位相余裕はそれより大きくなります。

$f_{PWM}$ やそれ以上でリップルやノイズをさらに減衰させるため一般的に高周波の極を $f_{PWM}$ に追加します。このことは $R_{ZC}$ 回路端に小さな値のコンデンサ $C_{pc}$ を付加することで実現します。

$$C_{pc} = \frac{1}{2\pi \times f_{PWM} \times R_{ZC}} \quad (27)$$

上記手順は固定値のインダクタに有効です。

注：“スイッチング・チョーク”的ブースト・インダクタ（インダクタンスが電流の増加とともに減少する）が用いられた場合、 $f_{CXO}$ はインダクタンスによって変化するため、 $C_{ZC}$ は最大インダクタンスで決めてください。

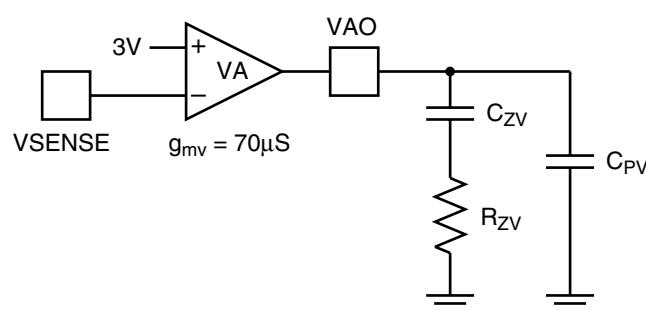

### 電圧ループの補償

2相のPFCコントローラの外部電圧コントロール・ループは単相コントローラと同様に機能し、ループ安定性に対する補償手法も標準的なものです[4]。電圧ループの帯域幅は、出力電圧に歪みを生じさせる補正を避けるため、出力コンデンサでのライン周波数の2倍のリップル周波数( $f_{2LF}$ )よりも大幅に低くなければなりません。電圧誤差增幅器(VA)の出力は、必要とされる出力電力に応じて入力電流の振幅を調整するため、乗算器の入力となります。VAOの電流ループの帯域幅内の変動は入力電流の波形に影響を与えます。 $C_{OUT}$ の低周波リップルは入力電力のみの関数であるため、そのピーク間振幅は高ライン時も低ライン時も同じになります。このリップルに対する電圧ループの応答は低ライン電流よりも高ライン電流に歪みの影響を大きく及ぼします。従って、VAOにより導かれる入力電流上の第三次高調波歪の許容パーセントは高ライン条件を用いて決められます。

電圧誤差增幅器(VA)はトランスコンダクタンス・タイプの増幅器であるため、その入力のインピーダンスは増幅器のゲインには何の関係もなく、単にそのトランスコンダクタンス( $g_{mv}$ )とその出力インピーダンス( $Z_{ov}$ )の積で決まります。よって、VSENSEの入力分圧回路の値はVINACの項で説明した基準に基づいてそれぞれ個別に決められます。その出力はVAOピンです。

図23. Voltage Error Amplifier With Type II Compensation

VSENSEのライン周波数の2倍の周波数のリップル電圧成分は入力電流波形の第三次高調波歪を目標レベルにするためVAOで十分に減衰され位相シフトされなければなりません[4]。1%の第三次高調波の許容入力歪みに対して、ライン周波数の2倍の周波数での小信号ゲイン $G_{VEA} = V_{VAOpk}/V_{SENSEpk} = g_{mv} \times Z_{OV}$ はVAO電圧の全範囲にわたってリップルはわずか2%です。UCC28070では、 $V_{VAO}$ は $\Delta V_{VAO} = 3.2V$ の場合、ゼロ負荷電力での1Vから全負荷電力での4.2V(下記注を参照してください)まで変動するため、3.2Vの2%でリップルはピークで64mVになります。

**注：**VAOの最大電圧は5Vにクランプされますが、全負荷時 $V_{VAO}$ は乗算器段で段階的に調整されたフィードフォワード電圧の影響を補償するためおおよそ4.2Vの中心点あたりを変動します(詳細については乗算器の項を参照してください)。従って、電圧ループのゲインの計算を行う時に最大出力電力を表すのに用いる電圧は4.2Vが適切です。

出力コンデンサの低周波での最大ゼロ/ピーク間リップル電圧は以下の式で概算されます。

$$v_{0pk} = \frac{Pin_{avg} \times X_{Cout}}{Vout_{avg}} \\ = \frac{Pin_{avg}}{Vout_{avg} \times 2\pi \times f_{2LF} \times Cout} \quad (28)$$

但し、 $P_{IN(avg)}$ はインターリープ動作のPFCプリレギュレータの総最大入力電力、 $V_{OUT(avg)}$ は平均出力電圧、 $C_{OUT}$ は出力容量です。

$V_{SENSEpk} = V_{opk} \times k_R$ 。 $k_R$ はVSENSEの抵抗分圧回路のゲインです。

よって、VAOリップルに起因する入力電流の許容第三次高調波歪の $k_{3rd}\%$ については、以下のようにになります。

$$Z_{OV(f_{2LF})} = \frac{k_{3rd} \times 64mV \times Vout_{avg} \times 2\pi f_{2LF} \times Cout}{g_{mv} \times k_R \times Pin_{avg}} \quad (29)$$

VAOのこのインピーダンスはコンデンサ( $C_{PV}$ )により設定されます。但し、 $CPV = 1 / (2\pi f_{2LF} \times Z_{OV}(f_{2LF}))$ 。従って、

$$C_{PV} = \frac{g_{mv} \times k_R \times Pin_{avg}}{k_{3rd} \times 64mV \times Vout_{avg} \times (2\pi f_{2LF})^2 \times Cout} \quad (30)$$

ここで、電圧ループの単一ゲインのクロスオーバー周波数( $f_{VXO}$ )は開ループ・ゲインを1に設定することで解くことができます。

$$Tv(f_{VXO}) = G_{BST} \times G_{VEA} \times k_R =$$

$$\left( \frac{Pin_{avg} \times X_{Cout}}{\Delta V_{VAO} \times Vout_{avg}} \right) \times (g_{mv} \times X_{CPV}) \times k_R = 1 \quad (31)$$

よって、

$$f_{VXO}^2 = \frac{g_{mv} \times k_R \times Pin_{avg}}{\Delta V_{VAO} \times Vout_{avg} \times (2\pi)^2 \times CPV \times Cout} \quad (32)$$

補償のゼロ点位置回路から“ゼロ抵抗”( $R_{ZV}$ )を計算することができます。 $C_{PV}$ とともに、 $R_{ZV}$ はクロスオーバー周波数で45°の位相余裕を得るため $f_{VXO}$ の右側に極を設定します。

よって、

$$R_{ZV} = \frac{1}{2\pi f_{VXO} \times CPV} \quad (33)$$

最後に、位相余裕を大幅に減少させないように、直流で高いゲインと、しかし $f_{VXO}$ より十分に低いブレークポイントを供給するため、ゼロはコンデンサ $C_{ZV}$ を用いて $f_{VXO}/6$ 以下に置かなければなりません。例えば $f_{VXO}/10$ に選ぶと、 $C_{ZV}$ と $C_{PV}$ の並列合成値を $C_{ZV}$ として概算することができ、 $C_{ZV}$ について解くと以下のように簡素化されます。

$$C_{ZV} = \frac{10}{2\pi f_{VXO} \times R_{ZV}} \approx 10 \times CPV \quad (34)$$

表計算ソフトまたは数学プログラムを使用することで、 $f_{VXO}$ 、位相余裕、第三次高調波歪への寄与率への影響を観察するため $C_{ZV}$ 、 $R_{PV}$ 、 $C_{PV}$ を操作することができます(以下の注を参照)。また、 $P_{IN(avg)}$ レベルとシステム・パラメータの公差が変動している時の位相余裕もチェックすることができます。

**注：**この項で計算された第三次高調波歪の率は $C_{OUT}$ の $f_{2LF}$ 電圧リップルによる寄与率のみを表しています。電流検出トランス、電流シンセサイザ一段、さらに、歪んだ $V_{IN}$ などのその他の歪みの発生源は付加第三次高調波歪及びそれ以上の高次高調波歪の原因となります。

## 高度な設計手法

### 電流ループのフィードバック構成(電流トランスの巻線比と検出抵抗( $R_S$ )の大きさ)

電流検出トランス(CT)は検出抵抗での大きな損失を避けながらインダクタ電流を検出するため一般的に大電力のアプリケーションで使用されます。平均電流モード・コントロールの場合は、全てのインダクタ電流波形が必要とされますが、低周波のCTは明らかに実用的ではありません。通常は、高周波のCTが2つ使用され、1つはアップスロープ電流を得るためスイッチング・レグに、もう1つはダウンスロープ電流を得るためダイオード・レグに使用されます。これらの2つの電流信号は全体のインダクタ電流を形成するために合算されますが、UCC28070ではこれは当てはまりません。

UCC28070設計の主な利点は電流合成機能で、スイッチング期間のオフ時間でインダクタのダウンスロープ電流を内部で再生成します。このことにより各相でダイオード・レグCTが不要になり、スペース、コスト、複雑さが大きく低減します。電流シンセサイザーの項で前述したように、1つの抵抗でシンセサイザーのダウンスロープをプログラムすることができます。

CTを選択するには多くのトレードオフを考慮しなければなりません。さまざまな内部/外部ファクタがCTの大きさ、コスト、性能、歪みへの寄与度に影響を与えます。

以下にそのファクタを挙げますが、制限はされません。

- 巻線比 ( $N_{CT}$ )

- 磁化インダクタンス ( $L_M$ )

- 漏れインダクタンス ( $L_{LK}$ )

- ボルト・マイクロ秒 ( $V_{\mu s}$ )

- 分散容量 ( $C_d$ )

- 直列抵抗 ( $R_{SER}$ )

- 外付けダイオードの電圧降下 ( $V_D$ )

- 外付け電流検出抵抗 ( $R_S$ )

- 外付けリセット回路

従来は、巻線比と電流検出抵抗が最初に選択されていました。ほかの検討事項が入ってくると選択作業を洗練するため何回かの繰り返しが必要になることがあります。

概して、 $50 \leq N_{CT} \leq 200$ が選択する際の妥当な範囲です。 $N_{CT}$ が小さすぎると、 $R_S$ の電力損失が大きくなり、 $L_M$ が不十分になることがあります。逆に、大きすぎると $L_{LK}$ と $C_d$ が過度に大きくなります(主巻線比は1と仮定しています)。

入力電流の歪みの主な原因是磁化電流のCT出力信号 ( $i_{RS}$ )への影響です。巻線比が大きいと与えられたコア・サイズで $L_M$ が大きくなります。 $L_M$ は生成される磁化電流 ( $i_M$ )が総変換電流に対しきわめて小さな割合となるよう十分に大きくなればなりません。このことは入力電流がゼロに低下してゆくにつれ $i_M$ が  $i_{RS}$ に対し大きな割合となることが必至であるため、この基準は全電流範囲にわたり維持することが不可能です。 $i_M$ の影響はいくつかの信号電流を  $R_S$ から“奪い去る”ことであるため、 $CS_x$ 電圧は減少し、検出される実際の電圧を事実上低く評価してしまいます。電流が小さい時、この過小評価されたことは重大で、CAOxはIMO基準電圧に合致させるよう $CS_x$ 入力を補正しようとして電流ループのデューティ・サイクルを増加させます。この交流ラインのゼロクロスの近辺などにおいて望ましくない補正により、CTの過小評価が大きく入力波形の電流に影響してしまいます。これは高ライン、軽負荷状態で全体の波形にある程度影響があります。

$CS_x$ の検出電圧が最大負荷時インダクタのリップル電流の中央で約3Vとなるよう検出抵抗  $R_S$  は  $N_{CT}$  とともに選択されます。目標は、 $V_{CMCAO}$  内にリップル電流のピークの余地を残しながら、CAOx電流誤差增幅器の同相入力電圧  $V_{CMCAO}$  内で平均信号を最大にすることです。設計条件は乗算器の項で決められたようにもっとも小さな最大入力電力制限時でなければなりません。

$V_{CS}$ に含まれるインダクタのリップル電流成分が  $V_{CMCAO}$  を越えるほど大きい場合、 $R_S$  または  $N_{CT}$ 、あるいは両方ともピークの  $V_{CS_x}$  を低減させるよう調整が必要です。それにより、平均検出電圧の中央値は3Vより低くなります。この状態は何も問題はありませんが、信号は全負荷と無負荷間でさらに圧縮され、軽負荷時大きな歪みとなる可能性があることに注意してください。

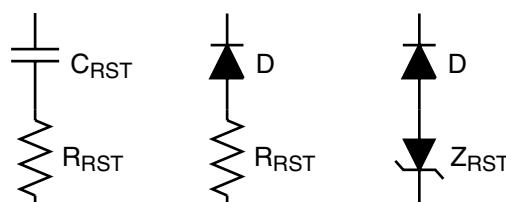

図24. Current Sense Transformer Equivalent Circuit

ボルト・秒の平衡の問題は、PFC段でデューティ・サイクルが大きく変動する場合に特に重要です。理想は、CTが各スイッチング期間で一度リセットされることです。すなわち、オフ時間のV<sub>μs</sub>積はオン時間のV<sub>μs</sub>積に等しくなります(スイッチング期間は通常マイクロ秒で測定されるため、小数点以下を回避するようボルト・秒積をボルト・マイクロ秒に変換することが好ましくなります)。オン時間のV<sub>μs</sub>は直列素子R<sub>SER</sub>、L<sub>LK</sub>、D、R<sub>S</sub>により生成されるL<sub>M</sub>端の電圧の時間積分です。オフ時間のV<sub>μs</sub>はオフ時間でのリセット回路端の電圧の時間積分です。受動リセットを用いると、V<sub>μs</sub>オフはV<sub>μs</sub>オンを越えそうにありません。オンまたはオフのV<sub>μs</sub>積で不平衡が持続すると、コアの飽和と電流検出信号の損失が引き起こされてしまいます。V<sub>CSx</sub>の損失はV<sub>CAOx</sub>をその最大まで急速に上昇させてしまい、全てのライン条件下で最大デューティ・サイクルをプログラムさせてしまいます。このことは同様に、システムのヒューズまたはある部品異常により入力電流が遮断されるまでブースト・インダクタ電流をとめどなく増加させてしまいます。

ピーク電流制限などの最大入力電流時にいくつか連続する最大デューティ・サイクル期間が存在するいろいろな特殊状態に対応するためCTはV<sub>μs</sub>に多くの設計マージンをもっていることが不可欠となります。

最大のV<sub>μs(on)</sub>は以下の式で見積もることができます。

$$V_{\mu(\text{on})\text{max}} = t_{\text{ON}(\text{max})} \times (V_{RS} + V_D + V_{RSER} + V_{LK}) \quad (35)$$

ここで全てのファクタは最悪の場合の過渡状態を考慮して最大にし、t<sub>ON(max)</sub>は周波数ディザリングがイネーブルの時最小ディザー周波数で起こります。設計にマージンをもたせるため、5\*V<sub>μs(on)</sub>maxまたはそれ以上のCT定格のものを推奨します。V<sub>RS</sub>への寄与度はライン電流に比例しますが、V<sub>D</sub>はゼロ近辺の電流でも大きな電圧となることがあるため、大量のV<sub>μs(on)</sub>がデューティ・サイクル最大のゼロクロスで生じることがあります。V<sub>RSER</sub>はほんの少しあ寄与せず、R<sub>SER</sub> << R<sub>S</sub>であればほとんど無視することができます。V<sub>LK</sub>は検出された電流の

di/dtにより生じますが、外部からは見えません。しかしながら、電流信号のマイクロ秒以下の立ち上がり時間にインダクタ電流のスロープが加わると、その影響は多大です。幸いにも、オン時間でL<sub>M</sub>端に形成される多くのV<sub>μs</sub>は、デューティ・サイクルの終わりの立下り時間で除去され、オフ時間で少量のV<sub>μs(on)</sub>はリセットされています。それでも、CTは、少なくとも、スイッチング期間内でターンオフの瞬間まで蓄えられた全ての内部V<sub>μs(on)</sub>maxを維持することができなければなりません。

V<sub>μs(off)</sub>はi<sub>M</sub>をバイアス電流として用い、抵抗またはツェナー・ダイオードにより生成することができます。

さまざまなCT回路の設計に対応し、CTの飽和による破壊の可能性から回避するため、UCC28070の最大デューティ・サイクルは、結果の最小オフ時間が要求される最悪の場合でのリセットを行えるようプログラムされる必要があります(R<sub>DMX</sub>の大きさを決める際の詳細についてはこのデータシートのPWM周波数とデューティ・サイクル・クランプの項を参照してください)。CTの自己共振周波数の1/4期間の後まで最大リセット電圧には達しないため、CTのC<sub>d</sub>が大きすぎるとリセット動作に干渉してしまうことに留意してください。巻線比が大きいとC<sub>d</sub>が大きくなるため[3]、N<sub>CT</sub>とD<sub>MAX</sub>でトレードオフを行う必要があります。

また、選択した巻線比はL<sub>M</sub>とL<sub>LK</sub>にも影響を与え、それらは巻線の2乗に比例して変化します。L<sub>M</sub>が大きいことは良いことですが、L<sub>LK</sub>が大きいことは良くありません。オン時間でL<sub>M</sub>端の電圧が一定であるとすれば(それはあり得ませんが、単純化すればほぼそうなります)、磁化電流はRampを増加させます。

この上昇するRamp電流はi<sub>RS</sub>から差し引かれ、前述のように、ゼロクロスや軽負荷時V<sub>CSX</sub>に特に大きく影響します。V<sub>CSX</sub>のピークが低下することで、電流シンセサイザーは低い電圧でダウンスロープを開始し、CAOxへの平均信号をさらに低減させ、これらの状態において歪みをさらに増加させてしまいます。極めて小さい負荷において入力電流の歪みが小さいことが必要とされる場合には、この目標を達成するよう特別の軽減方法を開発する必要があるかも知れません。

図25. Possible Reset Networks

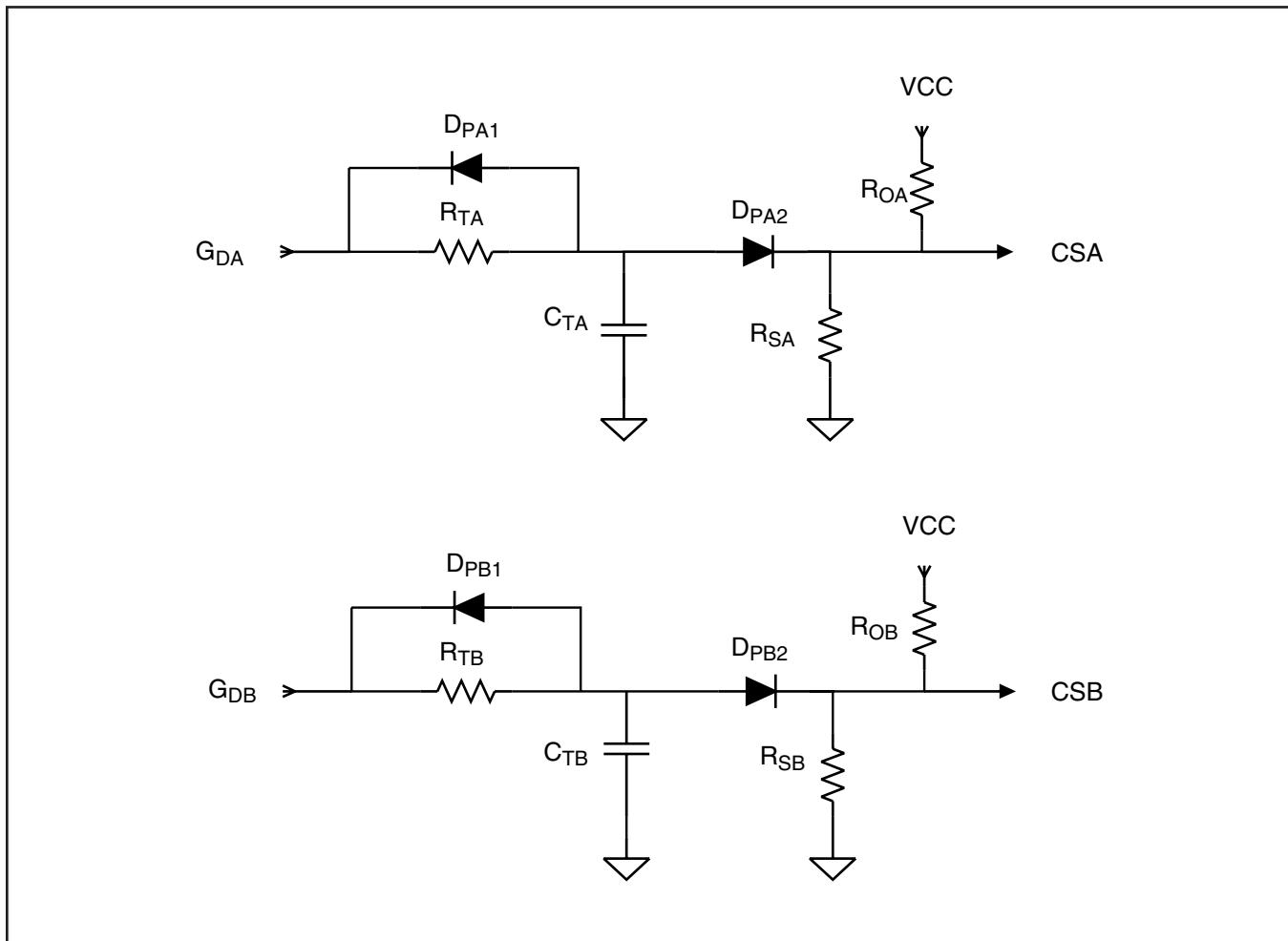

## ノイズ耐性の改善のための電流検出オフセットとPWMランプ

極度の軽負荷時のノイズ耐性を改善するには、直流のオフセットをもつPWM Rampを電流検出信号に付加することを推奨します。電気部品の $R_{TA}$ 、 $R_{TB}$ 、 $R_{OA}$ 、 $R_{OB}$ 、 $C_{TA}$ 、 $C_{TB}$ 、 $D_{PA1}$ 、 $D_{PB1}$ 、 $C_{TA}$ 、 $C_{TB}$ がUCC28070のゲート駆動出力により作動または停止するPWM Rampを形成します。抵抗 $R_{OA}$ 、 $R_{OB}$ がCS抵抗( $R_{SA}$ と $R_{SB}$ )に直流オフセットを加えます。

図26. PWM Ramp and Offset Circuit

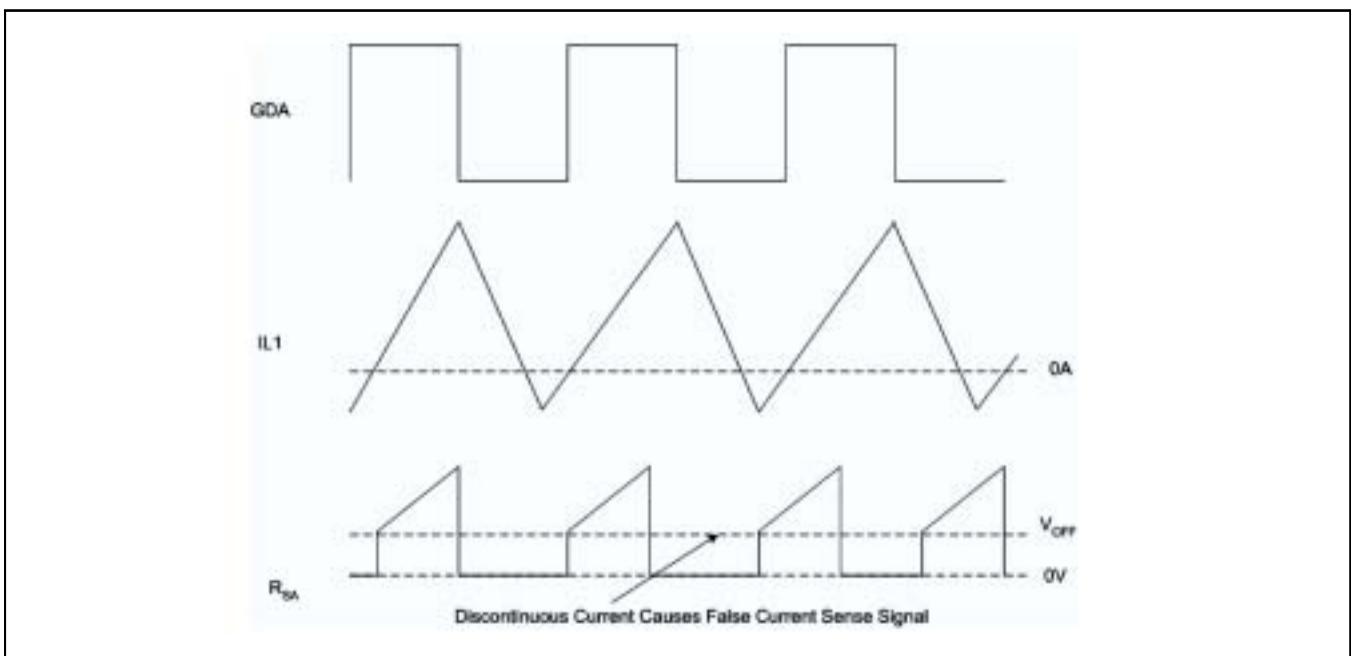

インダクタ電流が不連続になった時ブースト・インダクタはブースト段で寄生容量によりリングを起こします。このインダクタ電流はCTを介してリングを起こすため、誤った電流検出信号を生じさせます。電流検出信号がインダクタ電流が不連続になった時どのようになるかは以下のグラフ表示を参照してください。

注：インダクタ電流とRSは、不連続になった時設計におけるインダクタのリング量によってはこのグラフ表示とは異なることがあります。

オフセット ( $V_{OFF}$ ) の対策としては、不連続になった時に確実に電流検出抵抗にゼロであるべきなのに正の電流が現われないよう抵抗  $R_{OA}$  と  $R_{OB}$  を調整することが必要です。最初はオフセットを120mVに設定することが妥当であり、その後個々の設計基準に基づいて調整することが必要なことがあります。

$$R_{SA} = R_{SB} \quad (36)$$

$$R_{OA} = R_{OB} = \frac{(V_{VCC} - V_{OFF}) R_{SA}}{V_{OFF}} \quad (37)$$

オフセットの小さい最大電流検出信号 ( $V_S$ ) の10%といった小さなPWM Rampを  $R_{TA}$ 、 $R_{TB}$ 、 $C_{TA}$ 、 $C_{TB}$  を適切に選択することで追加することができます。

$$R_{TA} = R_{TB} = \frac{(V_{VCC} - (V_S \times 0.1 - V_{OFF}) + V_{DA2}) R_{SA}}{V_{OFF}} \quad (38)$$

$$C_{TA} = C_{TB} = \frac{1}{R_{TA} \times f_S \times 3} \quad (39)$$

図27. False Current Sense Signal

図27. False Current Sense Signal

## 推奨するPCBレイアウト

インターリープ動作のPFC手法によりPFCブースト・インダクタにより生じる入出力リップル電流を劇的に低減することができ、それにより回路は小型で安価なフィルタを使用することができます。インターリープ動作の利点を最大限に活用するため、各相の電流がブースト・コンデンサに入る前に結合できるよう出力フィルタ・コンデンサを2つの相の後に配置する必要があります。他のパワー・マネージメント・デバイスと同様に、PCBにレイアウトする際には、スター・グランド手法を用い、フィルタ・コンデンサと高周波バイパス・コンデンサができるだけデバイスのピンとグランドに近づけておくことが重要です。ブースト・インダクタによる電磁結合で引き起こされる干渉の可能性を最小限にするには、デバイスはブースト・インダクタから少なくとも1インチ離して配置する必要があります。また、デバイスは磁気素子の下に置かないようにすることも推奨します。

## 参考資料

1. O'Loughlin, Michael, "An Interleaving PFC Pre-Regulator for High-Power Converters", Texas Instruments, Inc. 2006 Unitrode Power Supply Seminar, Topic 5

2. Erickson, Robert W., "Fundamentals of Power Electronics", 1st ed., pp. 604-608 Norwell, MA: Kluwer Academic Publishers, 1997

3. Creel, Kirby "Measuring Transformer Distributed Capacitance", White Paper, Datatronic Distribution, Inc.

website:[http://www.datatronics.com/pdf/distributed\\_capacitance\\_paper.pdf](http://www.datatronics.com/pdf/distributed_capacitance_paper.pdf)

4. L. H. Dixon, "Optimizing the Design of a High Power Factor Switching Preregulator", Unitrode Power Supply Design Seminar Manual SEM700, 1990. Texas Instruments Literature Number SLUP093

5. L. H. Dixon, "High Power Factor Preregulator for Off-Line Power Supplies", Unitrode Power Supply Design Seminar Manual SEM600, 1988. Texas Instruments Literature Number SLUP087

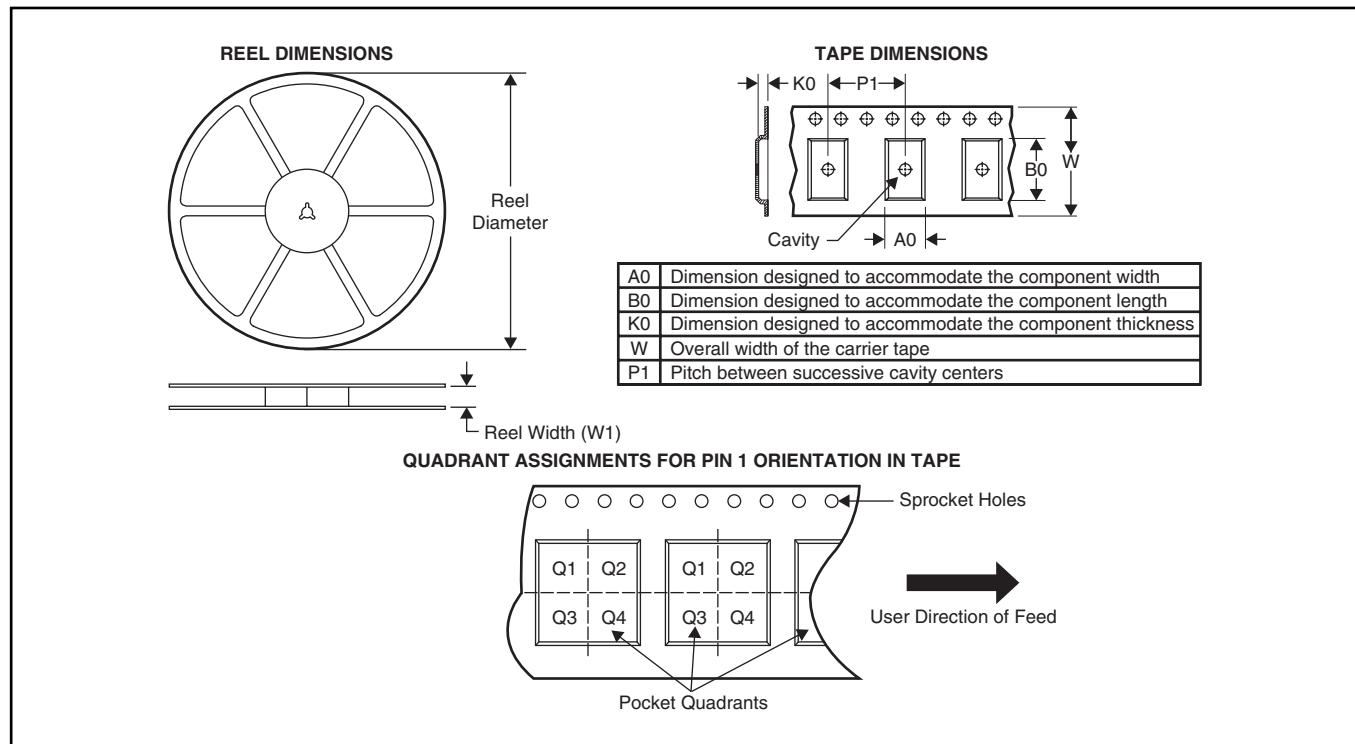

# パッケージ・マテリアル情報

## テープおよびリール・ボックス情報

\*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|-------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| UCC28070PWR | TSSOP        | PW              | 20   | 2000 | 330.0              | 16.4               | 6.95    | 1.6     | 1.4     | 8.0     | 16.0   | Q1            |

## パッケージ・マテリアル情報

### TAPE AND REEL BOX DIMENSIONS

\*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| UCC28070PWR | TSSOP        | PW              | 20   | 2000 | 346.0       | 346.0      | 33.0        |

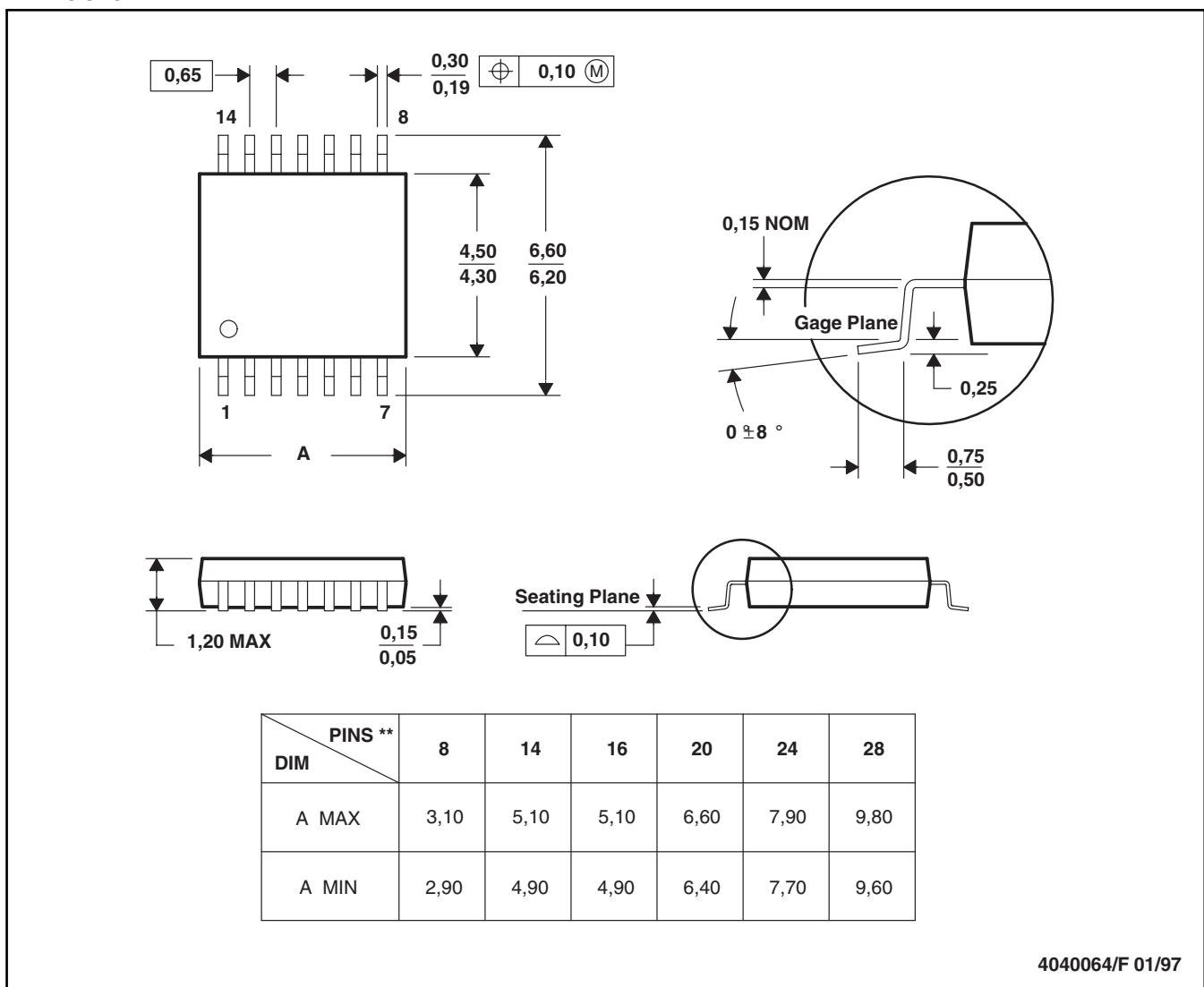

# メカニカル・データ

PW (P-PDSO-G\*\*)

14 PINS SHOWN

PLASTIC SMALL-OUTLINE PACKAGE

- 注：A. 全ての線寸法の単位はミリメートルです。

B. 図は予告なく変更することがあります。

C. ボディ寸法はモールド突起部を含みません。突起部は0,15を越えません。

D. パッケージはJEDEC MO-153に準拠しています。

(SLUS794A)

**PACKAGING INFORMATION**

| Orderable part number       | Status<br>(1) | Material type<br>(2) | Package   Pins  | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------------|---------------|----------------------|-----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| <a href="#">UCC28070DW</a>  | Active        | Production           | SOIC (DW)   20  | 25   TUBE             | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 85    | UCC28070            |

| UCC28070DW.B                | Active        | Production           | SOIC (DW)   20  | 25   TUBE             | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 85    | UCC28070            |

| <a href="#">UCC28070DWR</a> | Active        | Production           | SOIC (DW)   20  | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 85    | UCC28070            |

| UCC28070DWR.B               | Active        | Production           | SOIC (DW)   20  | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 85    | UCC28070            |

| UCC28070DWRG4               | Active        | Production           | SOIC (DW)   20  | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | UCC28070            |

| UCC28070DWRG4.B             | Active        | Production           | SOIC (DW)   20  | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | UCC28070            |

| <a href="#">UCC28070PW</a>  | Active        | Production           | TSSOP (PW)   20 | 70   TUBE             | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 28070               |

| UCC28070PW.B                | Active        | Production           | TSSOP (PW)   20 | 70   TUBE             | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 28070               |

| <a href="#">UCC28070PWR</a> | Active        | Production           | TSSOP (PW)   20 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 28070               |

| UCC28070PWR.B               | Active        | Production           | TSSOP (PW)   20 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 28070               |

| UCC28070PWRG4               | Active        | Production           | TSSOP (PW)   20 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 28070               |

| UCC28070PWRG4.B             | Active        | Production           | TSSOP (PW)   20 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 28070               |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

**OTHER QUALIFIED VERSIONS OF UCC28070 :**

- Automotive : [UCC28070-Q1](#)

NOTE: Qualified Version Definitions:

- Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適したTI製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているTI製品を使用するアプリケーションの開発の目的でのみ、TIはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TIや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TIおよびその代理人を完全に補償するものとし、TIは一切の責任を拒否します。

TIの製品は、[TIの販売条件](#)、[TIの総合的な品質ガイドライン](#)、[ti.com](#)またはTI製品などに関連して提供される他の適用条件に従い提供されます。TIがこれらのリソースを提供することは、適用されるTIの保証または他の保証の放棄の拡大や変更を意味するものではありません。TIがカスタム、またはカスタマー仕様として明示的に指定していない限り、TIの製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025年10月