## グリーン・モード対応フライバック・コントローラ

### 特 長

- カスコード構成により、外部センス抵抗なしで完全に内蔵された電流制御を実現

- 低スタンバイ電力での高速スタートアップをカスコード構成で実現

- 周波数変調およびピーク電流変調により動作範囲全体にわたって効率を最適化

- グリーン・モード(GM)のバースト・スイッチング・モードにより無負荷時効率を向上

- 高度な過電流保護でRMS入力/出力電流を制限

- 過熱シャットダウン

- リトライまたはラッチオフを選択可能なオン時間制限による過負荷保護

- 光学部品を使用しないプログラミング可能な出力過電圧保護

- 高速のラッチ障害回復

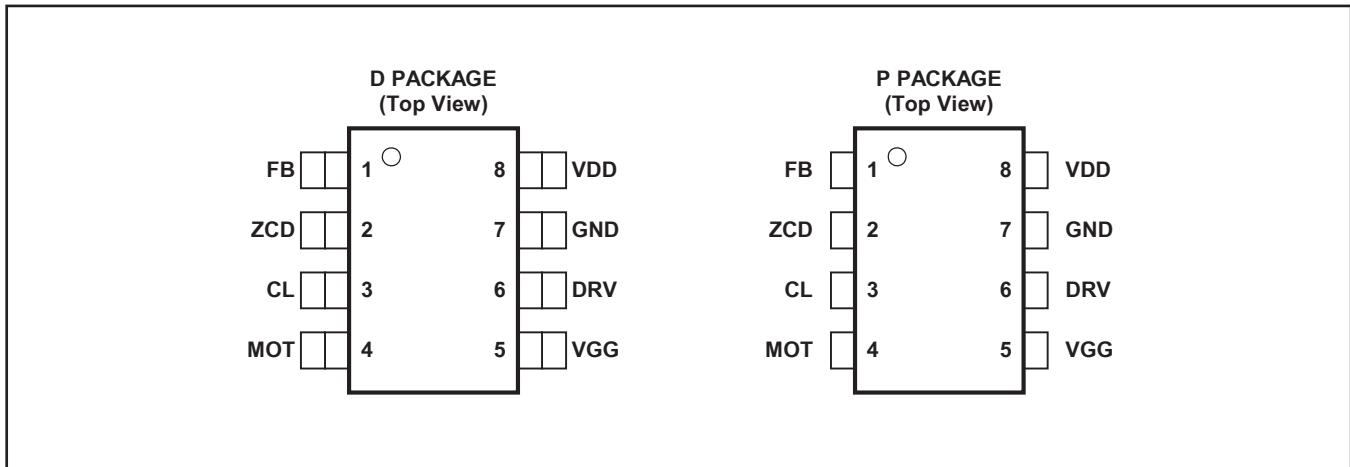

- 8ピンSOICパッケージおよび8ピンPDIP鉛フリー・パッケージ

### アプリケーション

- ユニバーサル入力AC/DCアダプタ、12W~65W

- 高効率のスタンバイ用電源および補助電源

- オフライン・バッテリ・チャージャ

- 民生用電子機器(DVDプレーヤー、セットトップ・ボックス、DTV、ゲーム、プリンタなど)

### 概 要

UCC28610は、AC/DC民生用電源ソリューションに新たなレベルの性能と信頼性をもたらします。

PWM変調アルゴリズムによってスイッチング周波数と1次電流の両方を変化させながら、動作範囲全体にわたって不連続または疑似共振モード動作を維持します。これらの革新的機能にカスコード・アーキテクチャを組み合わせることで、従来のフライバック構成を上回る効率、信頼性、およびシステム・コストの削減を実現しています。

UCC28610は、予測可能な最大電力スレッショルドと、タイミング制御された過負荷応答を備え、負荷急変への安全な対処を可能にしています。過負荷障害時の応答は、ユーザがリトライまたはラッチオフ・モードのどちらかを選択できます。他の保護機能として、出力過電圧保護、プログラミング可能な最大オン時間、および過熱シャットダウン保護があります。

すべての商標および登録商標は、それぞれの所有者に帰属します。

この資料は、Texas Instruments Incorporated(TI)が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ(日本TI)が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。

日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。

TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

# 静電気放電対策

これらのデバイスは、限定的なESD(静電破壊)保護機能を内蔵しています。保存時または取り扱い時に、MOSゲートに対する静電破壊を防止するために、リード線どうしを短絡しておくか、デバイスを導電性のフォームに入れる必要があります。

## ご発注の手引き

| 動作温度範囲、 $T_A$                                  | ピン | パッケージ                    | パッケージ・リード | 出荷形態    | 単位   | オーダー可能な部品番号 |

|------------------------------------------------|----|--------------------------|-----------|---------|------|-------------|

| $-40^{\circ}\text{C} \sim 125^{\circ}\text{C}$ | 8  | SOIC(プラスチック・スマール・アウトライン) | D         | テープ・リール | 2500 | UCC28610DR  |

|                                                | 8  | PDIP(プラスチック・デュアル・インライン)  | P         | チューブ    | 50   | UCC28610P   |

## 絶対最大定格<sup>(1)</sup>

すべての電圧はGNDを基準、 $-40^{\circ}\text{C} < T_J = T_A < 125^{\circ}\text{C}$ 、すべての電流は指定されたピンに流れ込む方向が正、ピンから流れ出る方向が負です(特に記述のない限り)。

|                          |                                                   | <b>UCC28610</b> | 単位 |

|--------------------------|---------------------------------------------------|-----------------|----|

| Input voltage range      | VDD                                               | -0.5 ~ +25      | V  |

|                          | DRV, during conduction                            | -0.5 ~ +2.0     |    |

|                          | DRV, during non-conduction                        | 20              |    |

|                          | VGG <sup>(2)</sup>                                | -0.5 ~ +16      |    |

|                          | ZCD, MOT, CL <sup>(3)</sup>                       | -0.5 ~ +7       |    |

|                          | FB <sup>(3)</sup>                                 | -0.5 ~ +1.0     |    |

|                          | VDD - VGG                                         | -7 ~ +10        |    |

| Continuous input current | $I_{VGG}$ <sup>(2)</sup>                          | 10              | mA |

| Input current range      | $I_{ZCD}, I_{MOT}, I_{CL}, I_{FB}$ <sup>(3)</sup> | -3 ~ +1         |    |

| Peak output current      | DRV                                               | -5              | A  |

|                          | DRV, pulsed 200ns, 2% duty cycle                  | -5 ~ +1.5       |    |

| $T_J$                    | Operating junction temperature range              | -40 ~ +150      | °C |

| $T_{stg}$                | Storage temperature range                         | -65 ~ +150      |    |

|                          | Lead Temperature (soldering, 10 sec.)             | +260            |    |

(1) これはストレスの定格のみについて示しております。絶対最大定格以上のストレスは、致命的なダメージを製品に与えることがあります。このデータシートの「推奨動作条件」に示された値を越える状態での本製品の機能動作は含まれていません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

(2) VGGの電圧は内部でクランプされています。クランプレベルは動作条件によって異なります。通常使用時は、VGGには内部制限電圧で電流供給されます。

(3) 通常使用時、MOT、CL、ZCD、およびFBは抵抗を介してGNDに接続され、電圧スイングが内部制限されています。

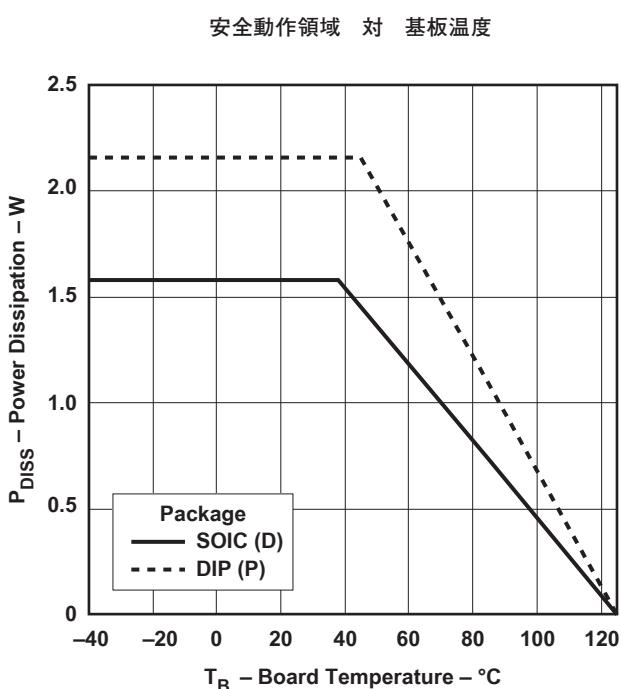

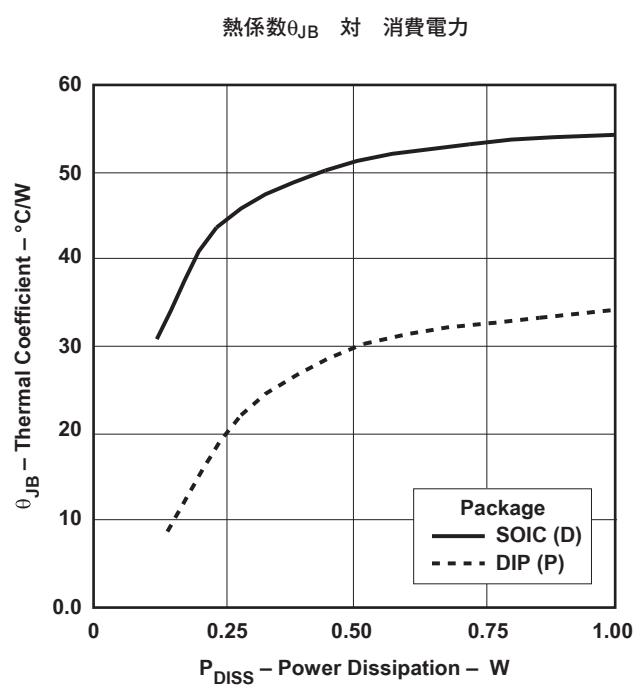

## パッケージ定格消費電力<sup>(1)(2)</sup>

| パッケージ      | $\theta_{JA}$ , THERMAL IMPEDANCE JUNCTION TO AMBIENT, NO AIRFLOW (°C/W) <sup>(1)</sup> | $\theta_{JB}$ , THERMAL IMPEDANCE JUNCTION TO BOARD, NO AIRFLOW (°C/W) <sup>(2)</sup> | $T_A = 25^{\circ}\text{C}$ POWER RATING (mW) <sup>(3)</sup> | $T_A = 85^{\circ}\text{C}$ POWER RATING (mW) <sup>(3)</sup> | $T_B = 85^{\circ}\text{C}$ POWER RATING (mW) <sup>(2) (3)</sup> |

|------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------|

| SOIC-8 (D) | 165                                                                                     | 55                                                                                    | 606                                                         | 242                                                         | 730                                                             |

| PDIP-8 (P) | 110                                                                                     | 37                                                                                    | 909                                                         | 364                                                         | 1080                                                            |

(1) JEDEC EIA/JESD51-1に従って測定。熱抵抗は、基板の構造およびレイアウトによって変化します。エアフローによって熱抵抗は低下します。この数値は一般的なガイドラインとしてのみ示したものです。TIのドキュメント『IC Package Thermal Metrics』(SPRA953)を参照してください。

(2) 回路基板に対する熱抵抗は、より低くなります。標準の片面PCB構造で測定されています。基板温度 $T_B$ は、リードと基板の界面から約1cmの位置で測定しています。この数値は、一般的なガイドラインとしてのみ示したものです。

(3) 最大接合部温度 $T_J$ は $125^{\circ}\text{C}$ です。

## 推奨動作条件

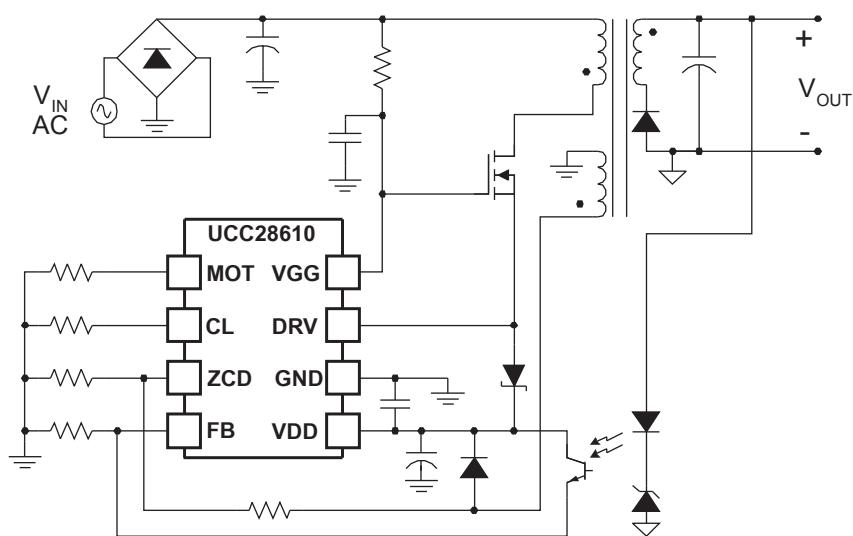

特に記述のない限り、すべての電圧はGNDを基準、 $-40^{\circ}\text{C} < T_J = T_A < 125^{\circ}\text{C}$ です。構成については図1を参照。

|                   |                                            | MIN  | MAX  | 単位 |

|-------------------|--------------------------------------------|------|------|----|

| VDD               | Input voltage                              | 9    | 20   | V  |

| VGG               | Input voltage from low- impedance source   | 9    | 13   |    |

| I <sub>VGG</sub>  | Input current from a high impedance source | 10   | 2000 | μA |

| R <sub>MOT</sub>  | Resistor to GND                            | 25   | 100  |    |

|                   | Shutdown/Retry mode                        | 150  | 750  |    |

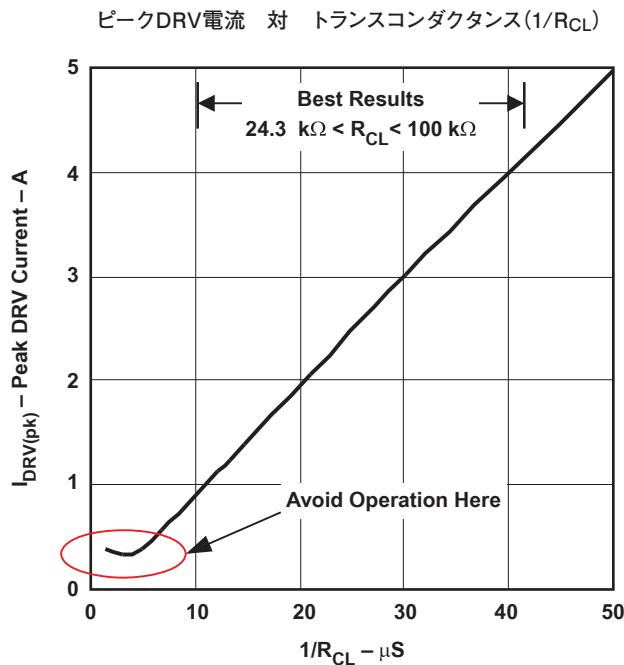

| R <sub>CL</sub>   | Resistor to GND                            | 24.3 | 100  | kΩ |

| R <sub>ZCD1</sub> | Resistor to auxiliary winding              | 50   | 200  |    |

| C <sub>VGG</sub>  | VGG capacitor                              | 33   | 200  | nF |

| C <sub>BP</sub>   | VDD bypass capacitor, ceramic              | 0.1  | 1    | μF |

図 1. 推奨動作条件アプリケーション

## 静電放電 (ESD) 保護

動作温度範囲内 (特に記述のない限り)

|                                        | MAX | 単位 |

|----------------------------------------|-----|----|

| ESD Rating, Human Body Model (HBM)     | 2   | kV |

| ESD Rating, Charged Device Model (CDM) | 500 | V  |

## 電気的特性

特に記述のない限り: VDD = 12V, VGG = 12V, ZCD = 1V, FB = 0V, GND = 0V, VDD-GND間に0.1μFのコンデンサ、VGG-GND間に0.1μFのコンデンサ、RCL = 33.2kΩ、RMOT = 380kΩ、-40°C < TA < +125°C、TJ = TA

| パラメータ                                                      |                                                                                  | テスト条件                                                                                                                   | MIN   | TYP  | MAX   | 単位   |

|------------------------------------------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------|

| <b>VDD and VGG SUPPLY</b>                                  |                                                                                  |                                                                                                                         |       |      |       |      |

| VGG <sub>(OPERATING)</sub>                                 | VGG voltage, operating                                                           | VDD = 14 V, I <sub>VGG</sub> = 2.0 mA                                                                                   | 13    | 14   | 15    | V    |

| VGG <sub>(DISABLED)</sub>                                  | VGG voltage, PWM disabled                                                        | VDD = 12 V, I <sub>VGG</sub> = 15 μA, I <sub>FB</sub> = 350 μA                                                          | 15    | 16   | 17    |      |

| ΔVGG                                                       | Rise in VGG clamping voltage during UVLO, GM, or Fault                           | VGG <sub>(DISABLED)</sub> – VGG <sub>(OPERATING)</sub>                                                                  | 1.75  | 2.00 | 2.15  |      |

| I <sub>VGG(SREG)</sub>                                     | VGG shunt regulator current                                                      | VGG = VGG <sub>(DISABLED)</sub> – 100 mV, VDD = 12 V                                                                    |       | 6    | 10    | μA   |

| ΔVGG <sub>(SREG)</sub>                                     | VGG shunt load regulation                                                        | 10 μA ≤ I <sub>VGG</sub> ≤ 5 mA, I <sub>FB</sub> = 350 μA                                                               |       | 125  | 200   | mV   |

| VGG <sub>(LREG)</sub>                                      | VGG LDO regulation voltage                                                       | VDD = 20 V, I <sub>VGG</sub> = – 2 mA                                                                                   |       | 13   |       | V    |

| VGG <sub>(LREG, DO)</sub>                                  | VGG LDO Dropout Voltage                                                          | VDD – VGG, VDD = 11 V, I <sub>VGG</sub> = – 2 mA                                                                        | 1.5   | 2    | 2.5   |      |

| VDD <sub>(ON)</sub>                                        | UVLO turn-on threshold                                                           |                                                                                                                         | 9.7   | 10.2 | 10.7  | V    |

| VDD <sub>(OFF)</sub>                                       | UVLO turn-off threshold                                                          |                                                                                                                         | 7.55  | 8    | 8.5   |      |

| ΔVDD <sub>(UVLO)</sub>                                     | UVLO hysteresis                                                                  |                                                                                                                         | 1.9   | 2.2  | 2.5   |      |

| I <sub>VDD(OPERATING)</sub>                                | Operating current                                                                | VDD = 20 V                                                                                                              | 2.5   | 3    | 3.7   | mA   |

| I <sub>VDD(GM)</sub>                                       | Idle current between bursts                                                      | I <sub>FB</sub> = 350 μA                                                                                                |       | 550  | 900   | μA   |

| I <sub>VDD(UVLO)</sub>                                     | Current for VDD < UVLO                                                           | VDD = VDD <sub>(ON)</sub> – 100 mV, increasing                                                                          |       | 225  | 310   |      |

| R <sub>DS,ON(VDD)</sub>                                    | VDD Switch on resistance, DRV to VDD                                             | VGG = 12 V, VDD = 7V, I <sub>DRV</sub> = 50 mA                                                                          |       | 4    | 10    | Ω    |

| VDD <sub>(FAULT RESET)</sub>                               | VDD for fault latch reset                                                        |                                                                                                                         | 5.6   | 6    | 6.4   | V    |

| <b>MODULATION</b>                                          |                                                                                  |                                                                                                                         |       |      |       |      |

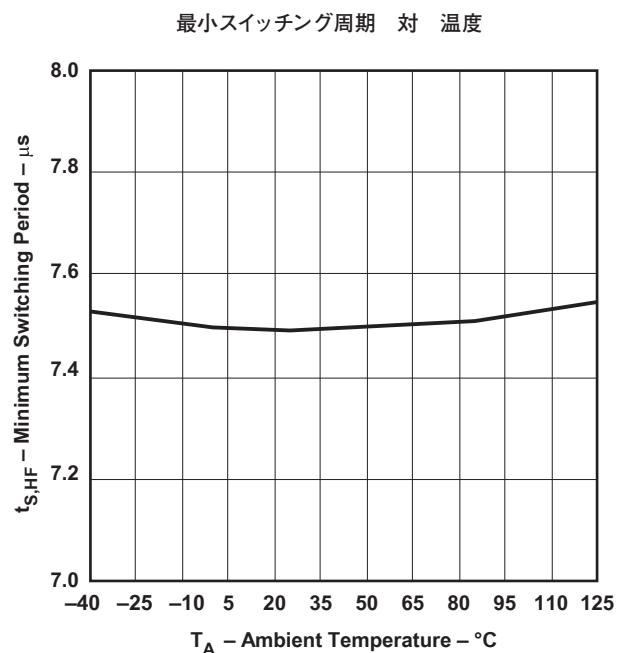

| t <sub>S(HF)</sub> <sup>(1)</sup>                          | Minimum switching period, frequency modulation (FM) mode                         | I <sub>FB</sub> = 0 μA <sup>(1)</sup>                                                                                   | 7.125 | 7.5  | 7.875 | μs   |

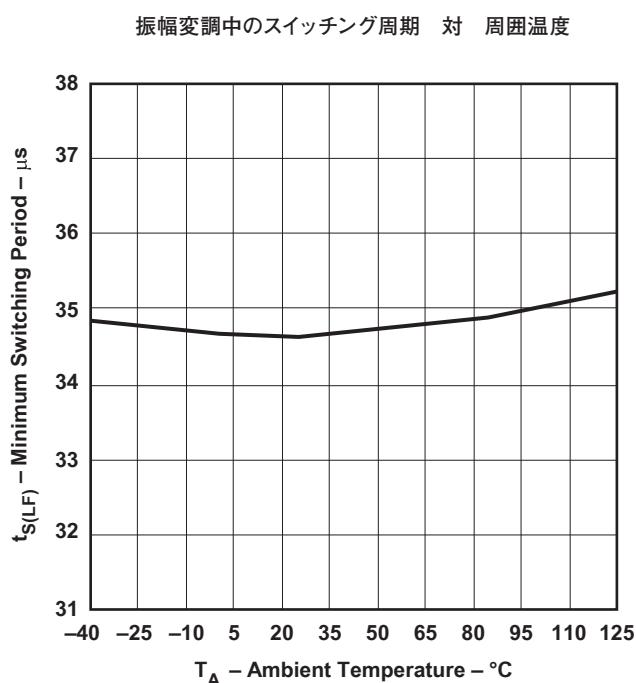

| t <sub>S(LF)</sub> <sup>(1)</sup>                          | Maximum switching period, reached at end of FM modulation range                  | I <sub>FB</sub> = I <sub>FB, CNR3</sub> – 20 μA <sup>(1)</sup>                                                          | 31    | 34   | 38    |      |

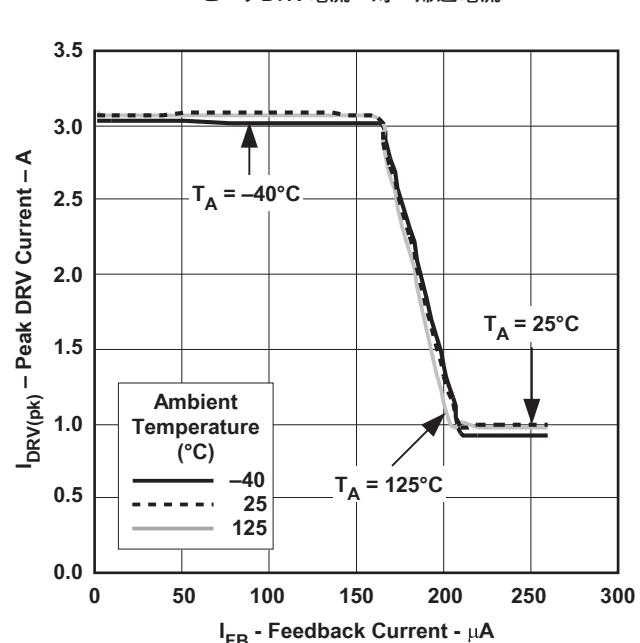

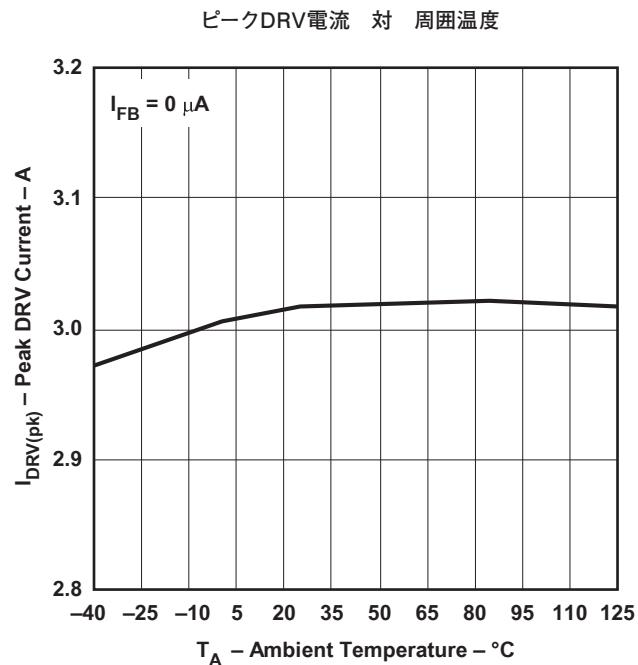

| I <sub>DRVpk(max)</sub>                                    | Maximum peak driver current over amplitude modulation(AM) range                  | I <sub>FB</sub> = 0 μA, R <sub>CL</sub> = 33.2 kΩ                                                                       | 2.85  | 3    | 3.15  | A    |

|                                                            |                                                                                  | I <sub>FB</sub> = 0 μA, R <sub>CL</sub> = 100 kΩ                                                                        | 0.80  | 0.90 | 1.0   |      |

| I <sub>DRVpk(min)</sub>                                    | Minimum peak driver current reached at end of AM modulation range                | I <sub>FB, CNR2</sub> + 10 μA, R <sub>CL</sub> = 33.2 kΩ                                                                | 0.7   | 0.85 | 1.1   |      |

|                                                            |                                                                                  | I <sub>FB, CNR2</sub> + 10 μA, R <sub>CL</sub> = 100 kΩ                                                                 | 0.2   | 0.33 | 0.5   |      |

| K <sub>P</sub>                                             | Maximum power constant                                                           | For I <sub>DRVpk(max)</sub> = 3 A                                                                                       | 0.54  | 0.60 | 0.66  | W/μH |

| I <sub>DRVpk(absmin)</sub>                                 | Minimum peak driver independent of R <sub>CL</sub> or AM control                 | R <sub>CL</sub> = OPEN                                                                                                  | 0.3   | 0.45 | 0.6   | A    |

| t <sub>BLANK(llim)</sub>                                   | Leading edge current limit blanking time                                         | I <sub>FB</sub> = 0 μA, R <sub>CL</sub> = 100 kΩ, 1.2-A pull-up on DRV                                                  | 120   | 220  | 450   | ns   |

| V <sub>CL</sub>                                            | Voltage of CL pin                                                                | I <sub>FB</sub> = 0 μA                                                                                                  | 2.94  | 3    | 3.06  | V    |

|                                                            |                                                                                  | I <sub>FB</sub> = (I <sub>FB,CNR3</sub> – 20 μA) <sup>(1)</sup>                                                         | 0.95  | 1    | 1.05  |      |

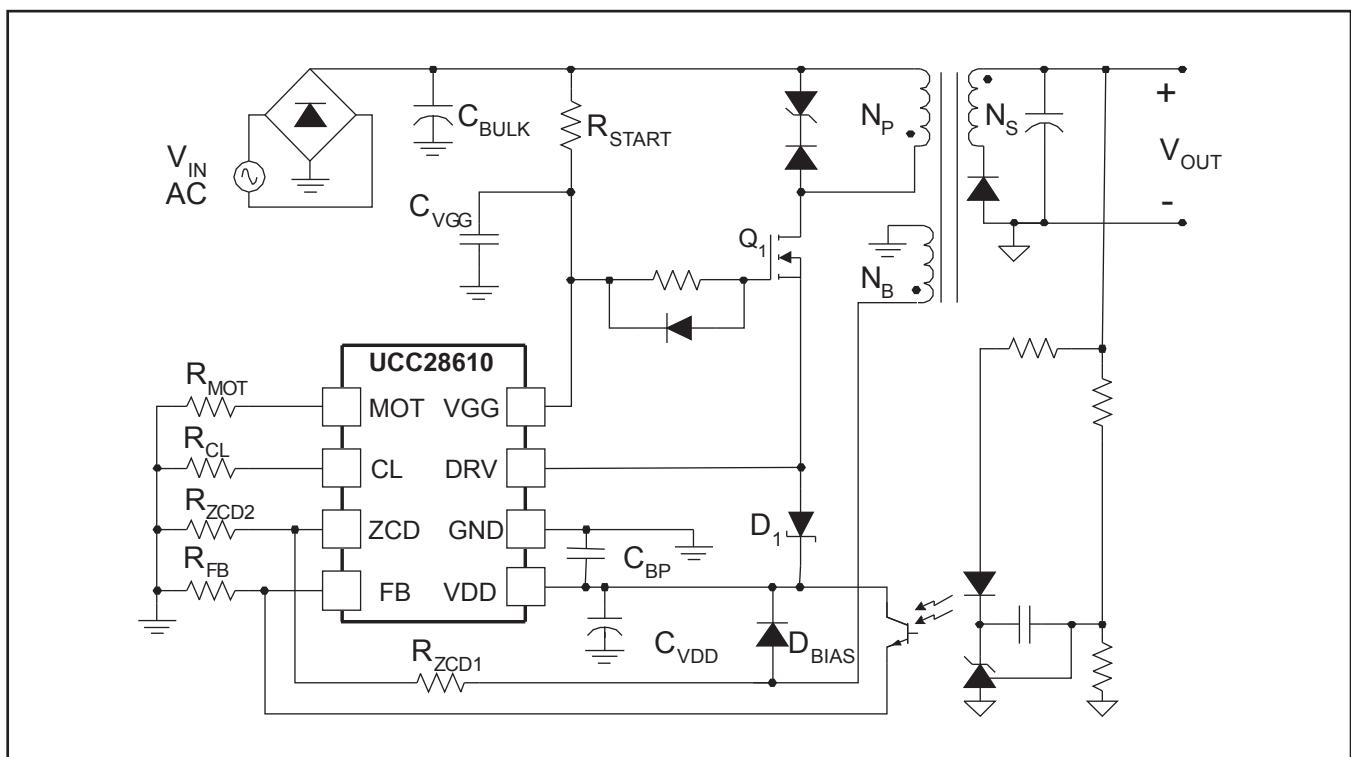

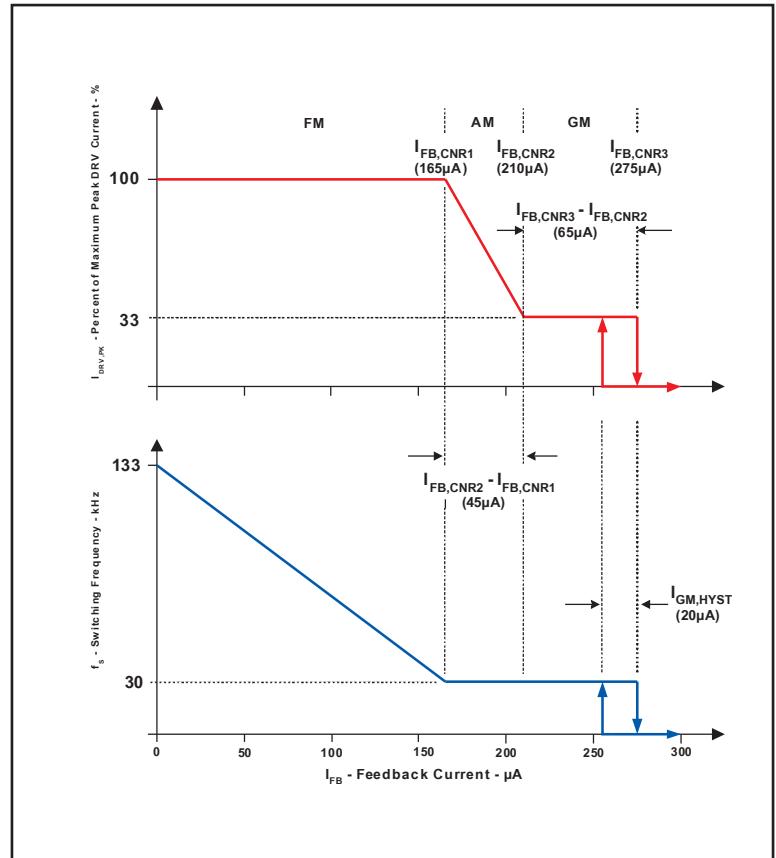

| I <sub>FB,CNR1</sub> <sup>(2)</sup>                        | I <sub>FB</sub> range for FM modulation                                          | I <sub>FB</sub> increasing, t <sub>S</sub> = t <sub>S(LF)</sub> , I <sub>DRVpk</sub> = I <sub>DRVpk(max)</sub>          | 145   | 165  | 195   | μA   |

| I <sub>FB,CNR2</sub> – I <sub>FB,CNR1</sub> <sup>(2)</sup> | I <sub>FB</sub> range for AM modulation                                          | t <sub>S</sub> = t <sub>S(LF)</sub> , I <sub>DRVpk</sub> ranges from I <sub>DRVpk(max)</sub> to I <sub>DRVpk(min)</sub> | 35    | 45   | 65    |      |

| I <sub>FB,CNR3</sub> – I <sub>FB,CNR2</sub> <sup>(2)</sup> | I <sub>FB</sub> range for Green Mode (GM) modulation                             | I <sub>FB</sub> increasing until PWM action is disabled entering a burst-off state                                      | 50    | 70   | 90    |      |

| I <sub>FB, GM-HYST</sub> <sup>(2)</sup>                    | I <sub>FB</sub> hysteresis during GM modulation to enter burst on and off states | I <sub>FB</sub> decreasing from above I <sub>FB,CNR3</sub>                                                              | 10    | 25   | 40    |      |

(1) t<sub>S</sub>は最小スイッチング周期を設定します。通常条件下では、PWMオン時間の開始エッジ以降、t<sub>S</sub>経過後にZCDで最初にゼロクロスが検出されたときに、次のオン時間が開始されます。t<sub>S</sub>の値は、I<sub>FB</sub>によって最小t<sub>S(HF)</sub>～最大t<sub>S(LF)</sub>の間で変調されます。通常動作時、t<sub>S(HF)</sub>は電源の最大動作周波数を設定し、t<sub>S(LF)</sub>は電源の最小動作周波数を設定します。

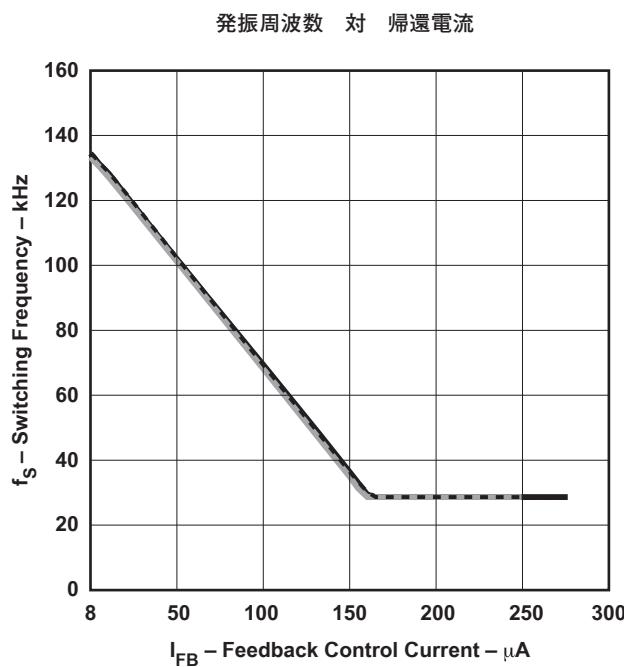

(2) 図2を参照。

## 電気的特性

特に記述のない限り: VDD = 12V、VGG = 12V、ZCD = 1V、FB = 0V、GND = 0V、VDD-GND間に0.1 $\mu$ Fのコンデンサ、VGG-GND間に0.1 $\mu$ Fのコンデンサ、R<sub>CL</sub> = 33.2k $\Omega$ 、R<sub>MOT</sub> = 380k $\Omega$ 、-40°C < T<sub>A</sub> < +125°C、T<sub>J</sub> = T<sub>A</sub>

| パラメータ                              |                                                                | テスト条件                                                                                       | MIN  | TYP   | MAX  | 単位         |

|------------------------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------|------|-------|------|------------|

| V <sub>FB</sub>                    | Voltage of FB pin                                              | I <sub>FB</sub> = 10 $\mu$ A                                                                | 0.34 | 0.7   | 0.84 | V          |

| <b>ZERO CROSSING DETECTION</b>     |                                                                |                                                                                             |      |       |      |            |

| ZCD <sub>(TH)</sub>                | ZCD zero crossing threshold                                    | ZCD high to low generates switching period (t <sub>S</sub> has expired)                     | 5    | 20    | 50   | mV         |

| ZCD <sub>(CLAMP)</sub>             | ZCD low clamp voltage                                          | I <sub>ZCD</sub> = -10 $\mu$ A                                                              | -200 | -160  | -100 | mV         |

| ZCD <sub>(START)</sub>             | ZCD voltage threshold to enable the internal start timer       | Driver switching periods generated at start timer rate                                      | 0.1  | 0.15  | 0.2  | V          |

| t <sub>DLY(ZCD)</sub>              | Delay from zero crossing to Driver turn-on                     | 150- $\Omega$ pull-up to 12-V on DRV                                                        |      | 150   |      | ns         |

| t <sub>WAIT(ZCD)</sub>             | Wait time for zero crossing detection                          | Driver turn-on edge generated following t <sub>S</sub> with previous zero crossing detected | 2    | 2.4   | 2.8  | $\mu$ s    |

| t <sub>ST</sub>                    | Starter time-out period                                        | ZCD = 0 V                                                                                   | 150  | 240   | 300  |            |

| <b>DRIVER</b>                      |                                                                |                                                                                             |      |       |      |            |

| R <sub>DS(on)(DRV)</sub>           | Driver on-resistance                                           | I <sub>DRV</sub> = 4.0 A                                                                    | 90   | 190   |      | m $\Omega$ |

| I <sub>DRV(OFF)</sub>              | Driver off-leakage current                                     | DRV = 12 V                                                                                  |      | 1.5   | 20   | $\mu$ A    |

| R <sub>DS(on)(HSDRV)</sub>         | High-side driver on-resistance                                 | I <sub>DRV</sub> = -50 mA                                                                   |      | 6     | 11   | $\Omega$   |

| I <sub>DRV(DSCH)</sub>             | DRV bulk discharge current                                     | VDD open, DRV= 12 V, Fault latch set                                                        | 2    | 2.8   | 3.6  | mA         |

| <b>OVERVOLTAGE FAULT</b>           |                                                                |                                                                                             |      |       |      |            |

| ZCD <sub>(OVP)</sub>               | Overvoltage fault threshold at ZCD                             | Fault latch set                                                                             | 4.85 | 5     | 5.15 | V          |

| t <sub>BLANK(OVP)</sub>            | ZCD blanking and OVP sample time from the turn-off edge of DRV |                                                                                             | 0.6  | 1     | 1.7  | $\mu$ s    |

| I <sub>ZCD(bias)</sub>             | ZCD Input bias current                                         | ZCD = 5 V                                                                                   | -0.1 | -0.05 | 0.1  | $\mu$ A    |

| <b>OVERLOAD FAULT</b>              |                                                                |                                                                                             |      |       |      |            |

| I <sub>FB(OL)</sub>                | Current to trigger overload delay timer                        |                                                                                             | 0    | 1.5   | 3    | $\mu$ A    |

| t <sub>OL</sub>                    | Delay to overload fault                                        | I <sub>FB</sub> = 0 A continuously                                                          | 200  | 250   | 325  | ms         |

| t <sub>RETRY</sub>                 | Retry delay in retry mode or after shutdown command            | R <sub>MOT</sub> = 76 k $\Omega$                                                            |      | 750   |      |            |

| R <sub>MOT(TH)</sub>               | Boundary R <sub>MOT</sub> between latch-off and retry modes    | See <sup>(3)</sup>                                                                          | 100  | 120   | 150  | k $\Omega$ |

| <b>SHUTDOWN THRESHOLD</b>          |                                                                |                                                                                             |      |       |      |            |

| MOT <sub>(SR)</sub>                | Shutdown-Retry threshold                                       | MOT high to low                                                                             | 0.7  | 1     | 1.3  | V          |

| I <sub>MOT</sub>                   | MOT current when MOT is pulled low                             | MOT = 1 V                                                                                   | -600 | -450  | -300 | $\mu$ A    |

| <b>MAXIMUM ON TIME</b>             |                                                                |                                                                                             |      |       |      |            |

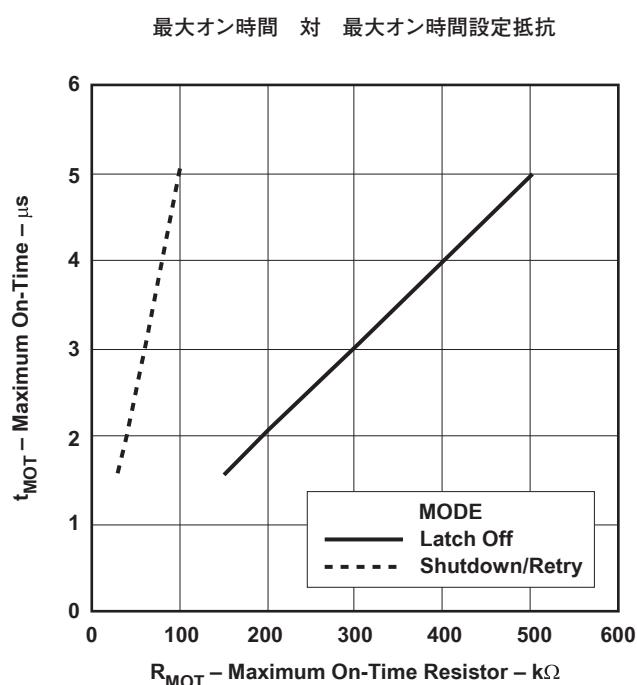

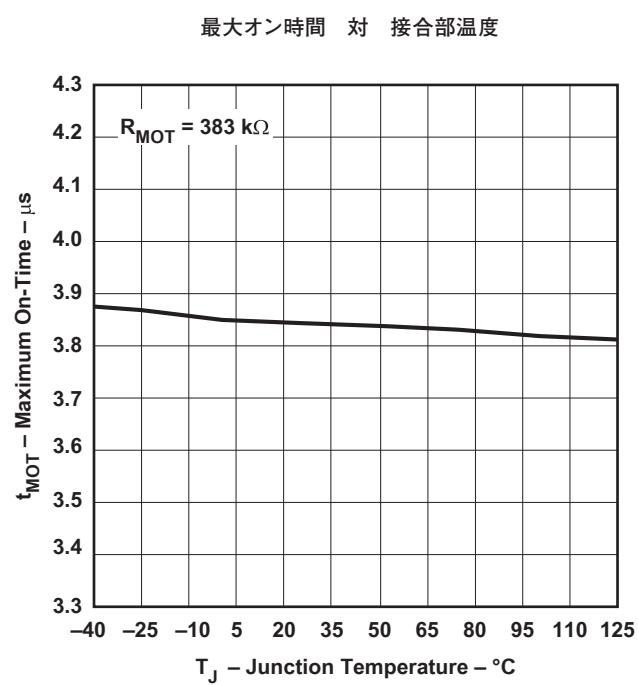

| t <sub>MOT</sub>                   | Latch-OFF                                                      | R <sub>MOT</sub> = 383 k $\Omega$                                                           | 3.43 | 3.83  | 4.23 | $\mu$ s    |

|                                    | Shutdown-retry                                                 | R <sub>MOT</sub> = 76 k $\Omega$                                                            | 3.4  | 3.8   | 4.2  |            |

| MOT                                | MOT voltage                                                    |                                                                                             | 2.7  | 3     | 3.3  | V          |

| <b>THERMAL SHUTDOWN</b>            |                                                                |                                                                                             |      |       |      |            |

| T <sub>SD</sub> <sup>(4)</sup>     | Shutdown temperature                                           | T <sub>J</sub> , temperature rising <sup>(4)</sup>                                          |      | 165   |      | °C         |

| T <sub>SD_HYS</sub> <sup>(4)</sup> | Hysteresis                                                     | T <sub>J</sub> , temperature falling, degrees below T <sub>SD</sub> <sup>(4)</sup>          |      | 15    |      |            |

(3) R<sub>MOT</sub>の範囲により、持続的な過負荷に対する応答として、ラッチオフまたはシャットダウン/リトライが選択されます。

ラッチオフ・モードを選択するには、R<sub>MOT</sub>を150k $\Omega$ より大きくする必要があります、t<sub>MOT</sub>はR<sub>MOT</sub> × (1.0 × 10<sup>-11</sup>)で与えられます。

シャットダウン/リトライ・モードを選択するには、R<sub>MOT</sub>を100k $\Omega$ より小さくする必要があります、t<sub>MOT</sub>はR<sub>MOT</sub> × (5.0 × 10<sup>-11</sup>)で与えられます。

(4) 過熱シャットダウンは、通常動作範囲よりも高い温度で生じます。過熱シャットダウン温度付近でのデバイス特性は規定されておらず、保証もされません。

図 2. FB電気的条件の詳細

## 製品情報

### ピン構成

### ピン説明

| 名前  | ピン | I/O | 説明                                                                                                                                                                                                                                                                                                 |

|-----|----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CL  | 3  | I   | (Current Limit: 電流制限) このピンは、各スイッチング・サイクルで到達するピーク1次インダクタ電流をプログラミングします。プログラミングは、CLとGNDの間に接続する抵抗によって行います。                                                                                                                                                                                             |

| DRV | 6  | O   | (DRiVe: ドライブ) このピンは、外部高耐圧パワーMOSFETのソースを駆動します。DRVピンには、コンバータの1次電流の全てが流れます。スタートアップ時の初期バイアスを与えるために、DRVとVDDの間にショットキー・ダイオードを接続します。                                                                                                                                                                       |

| FB  | 1  | I   | (FeedBack: 帰還) FBの電流 $I_{FB}$ は、UCC28610の動作モードを指示します。FBの電圧は常に0.7Vです。このピンは電流の検出のみを行います。                                                                                                                                                                                                             |

| GND | 7  | —   | (GrouND: グラント) このピンは、UCC28610のアナログ信号とパワー信号の両方に対する電流リターン端子です。この端子には、コンバータの1次電流全体が流れます。バルク・コンデンサのリターン・バスは、FB、ZCD、MOT、およびCLのリターン・バスから離してください。                                                                                                                                                         |

| MOT | 4  | I   | (Maximum On Time: 最大オン時間) このピンには3つの機能があります。<br>1. 内部ドライバの最大許容オン時間 $t_{MOT}$ をプログラミングします。<br>2. 過負荷状態および電源入力低電圧状態に対するコンバータの動作をプログラミングします(シャットダウン/リトライ、またはラッチオフ)。<br>3. MOTをGNDにプルダウンすることで、電源を外部でシャットダウンできます。解除すると、再起動遅延時間 $t_{RETRY}$ の経過後にコンバータが起動します。<br>機能1および2は、MOTとGNDの間に接続する抵抗によってプログラミングします。 |

| VDD | 8  | —   | これは、UCC28610のバイアス電圧ピンです。この電圧は外部電源または補助巻線から供給できます。このピンは、GNDとの間に $0.1\mu F$ のセラミック・コンデンサをデバイスにできるだけ近づけて配置することで、デカップリングする必要があります。                                                                                                                                                                     |

| VGG | 5  | —   | このピンは、外部高電圧MOSFETのゲートに対してDC電圧を提供します。このピンは、GNDの間に $0.1\mu F$ のセラミック・コンデンサをデバイスにできるだけ近づけて配置することで、デカップリングする必要があります。また、このピンは、入力バルク電圧に接続された値の大きな抵抗を通して、スタートアップ時のバイアスを提供します。                                                                                                                             |

| ZCD | 2  | I   | (Zero Current Detection: ゼロ電流検出) このピンには2つの機能があります。<br>1. 正確なゼロ電流検出信号に基づいてトランジストのリセットを検知します。<br>2. フライバック・トランジストの1次側バイアス巻線から分圧抵抗を使用して、出力過電圧保護(OVP)機能をプログラミングします。                                                                                                                                    |

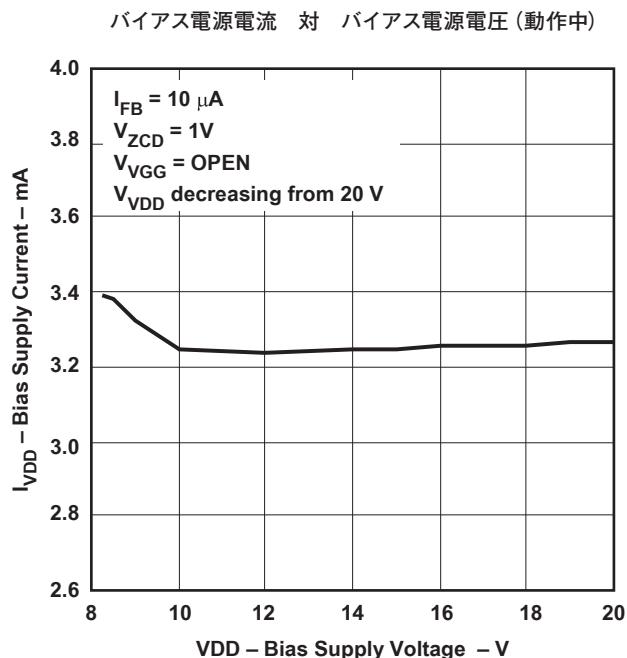

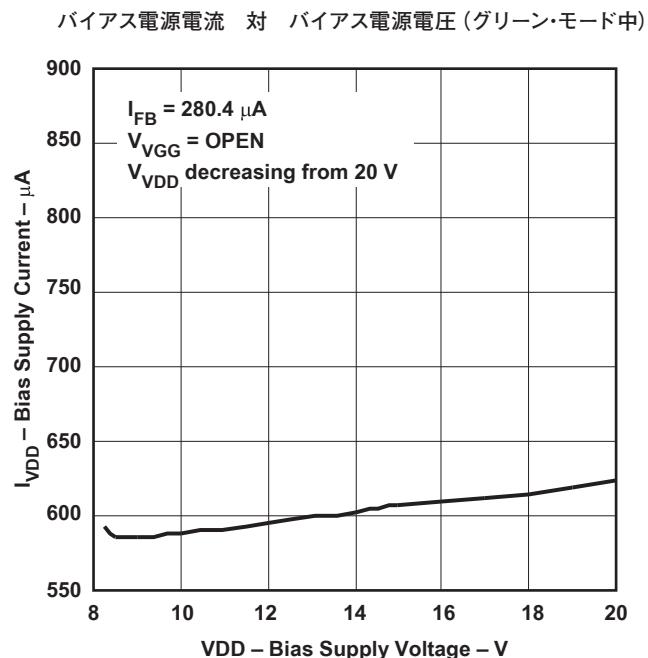

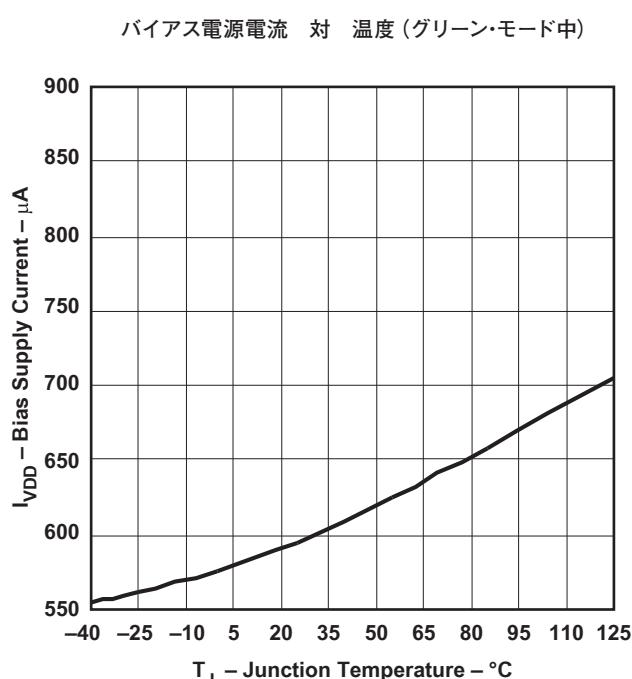

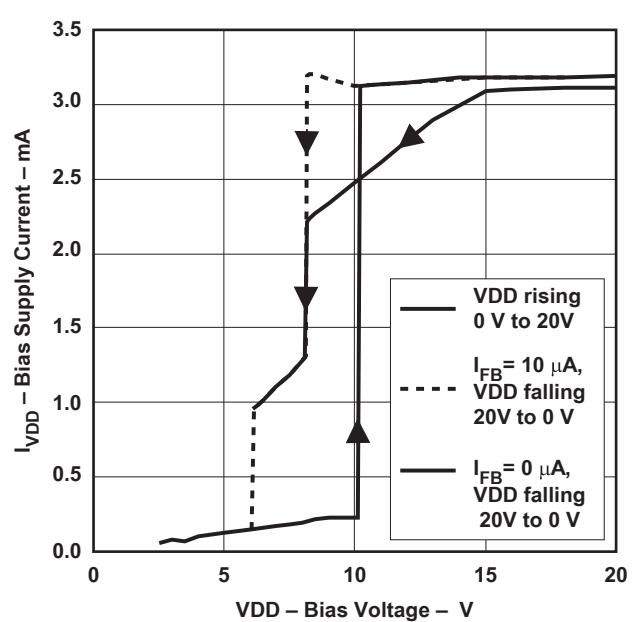

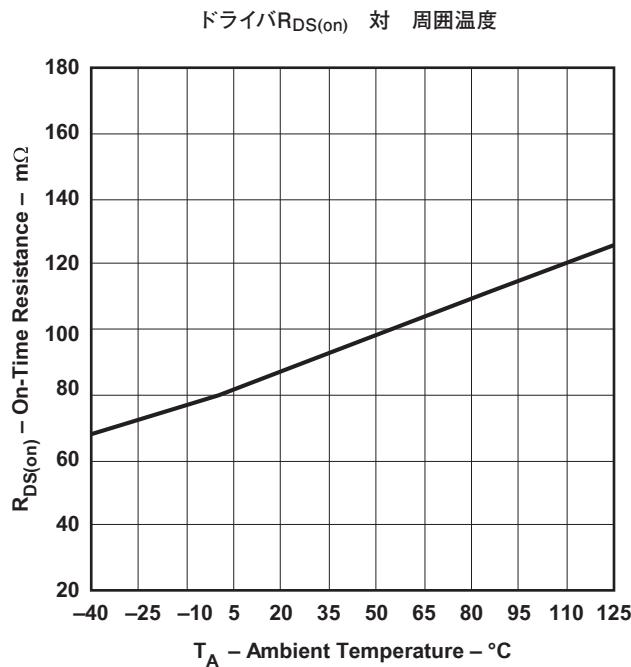

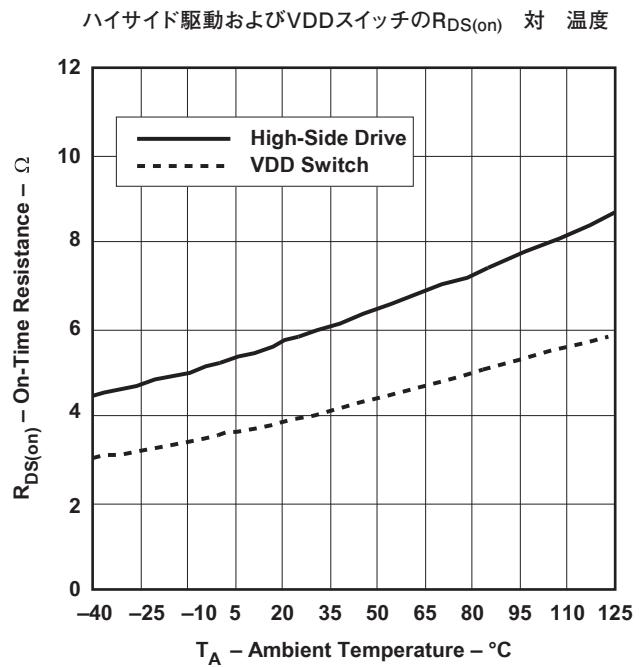

## 標準的特性

特に記述のない限り:  $V_{DD} = 12V$ 、 $V_{GG} = 12V$ 、 $Z_{CD} = 1V$ 、 $FB = 0V$ 、 $GND = 0V$ 、 $V_{DD}$ - $GND$ 間に $0.1\mu F$ のコンデンサ、 $V_{GG}$ - $GND$ 間に $0.1\mu F$ のコンデンサ、 $R_{CL} = 33.2k\Omega$ 、 $R_{MOT} = 380k\Omega$ 、 $-40^\circ C < T_A < +125^\circ C$ 、 $T_J = T_A$

図 3

図 4

図 5

図 6

## 標準的特性

特に記述のない限り: VDD = 12V、VGG = 12V、ZCD = 1V、FB = 0V、GND = 0V、VDD-GND間に0.1 $\mu$ Fのコンデンサ、VGG-GND間に0.1 $\mu$ Fのコンデンサ、R<sub>CL</sub> = 33.2k $\Omega$ 、R<sub>MOT</sub> = 380k $\Omega$ 、-40°C < T<sub>A</sub> < +125°C、T<sub>J</sub> = T<sub>A</sub>

図 7

図 8

図 9

図 10

## 標準的特性

特に記述のない限り: VDD = 12V、VGG = 12V、ZCD = 1V、FB = 0V、GND = 0V、VDD-GND間に0.1 $\mu$ Fのコンデンサ、VGG-GND間に0.1 $\mu$ Fのコンデンサ、 $R_{CL}$  = 33.2k $\Omega$ 、 $R_{MOT}$  = 380k $\Omega$ 、-40°C <  $T_A$  < +125°C、 $T_J$  =  $T_A$

図 11

図 12

図 13

図 14

## 標準的特性

特に記述のない限り: VDD = 12V、VGG = 12V、ZCD = 1V、FB = 0V、GND = 0V、VDD-GND間に0.1 $\mu$ Fのコンデンサ、VGG-GND間に0.1 $\mu$ Fのコンデンサ、R<sub>CL</sub> = 33.2k $\Omega$ 、R<sub>MOT</sub> = 380k $\Omega$ 、-40°C < T<sub>A</sub> < +125°C、T<sub>J</sub> = T<sub>A</sub>

図 15

図 16

図 17

図 18

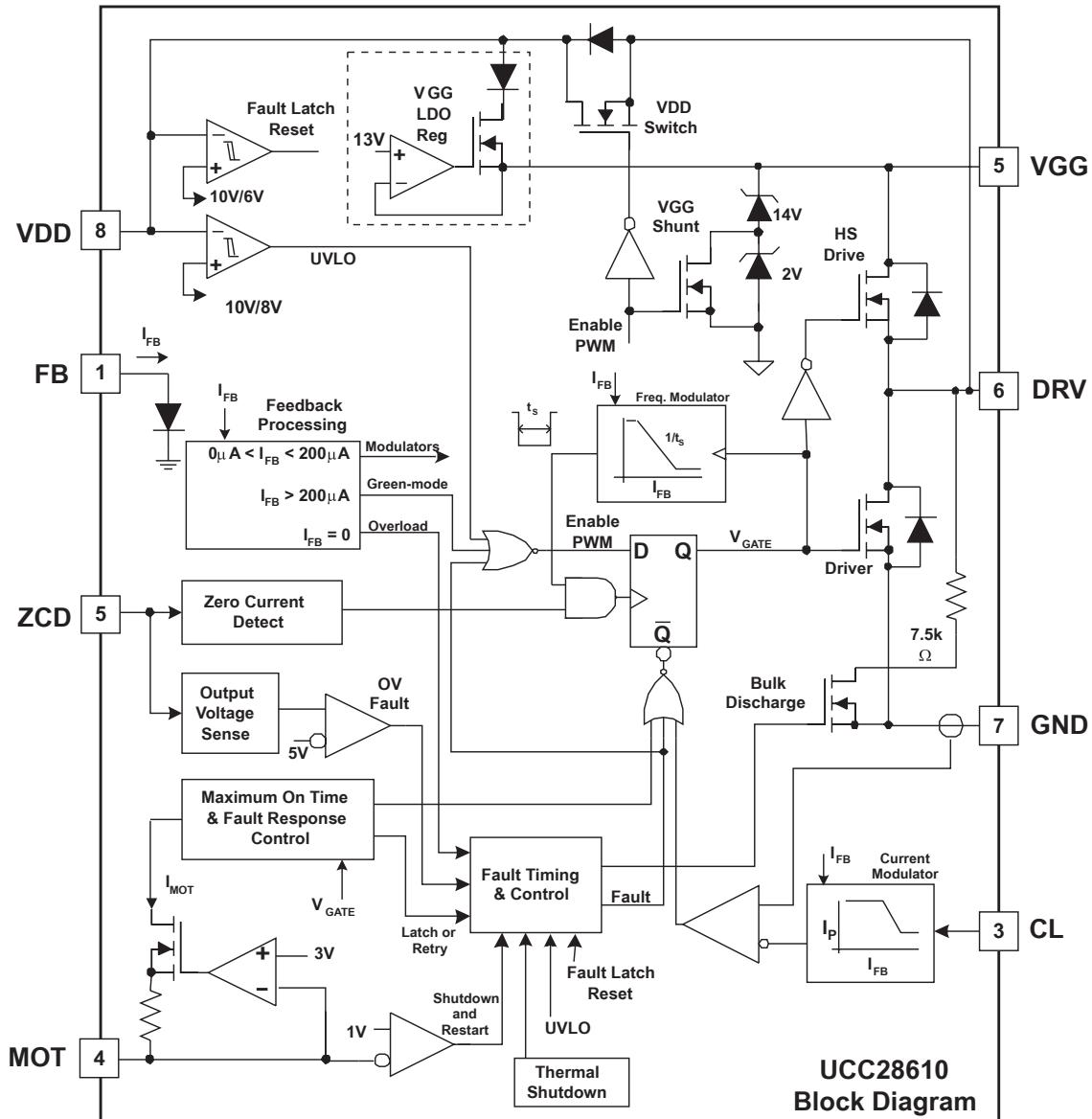

## ブロック図

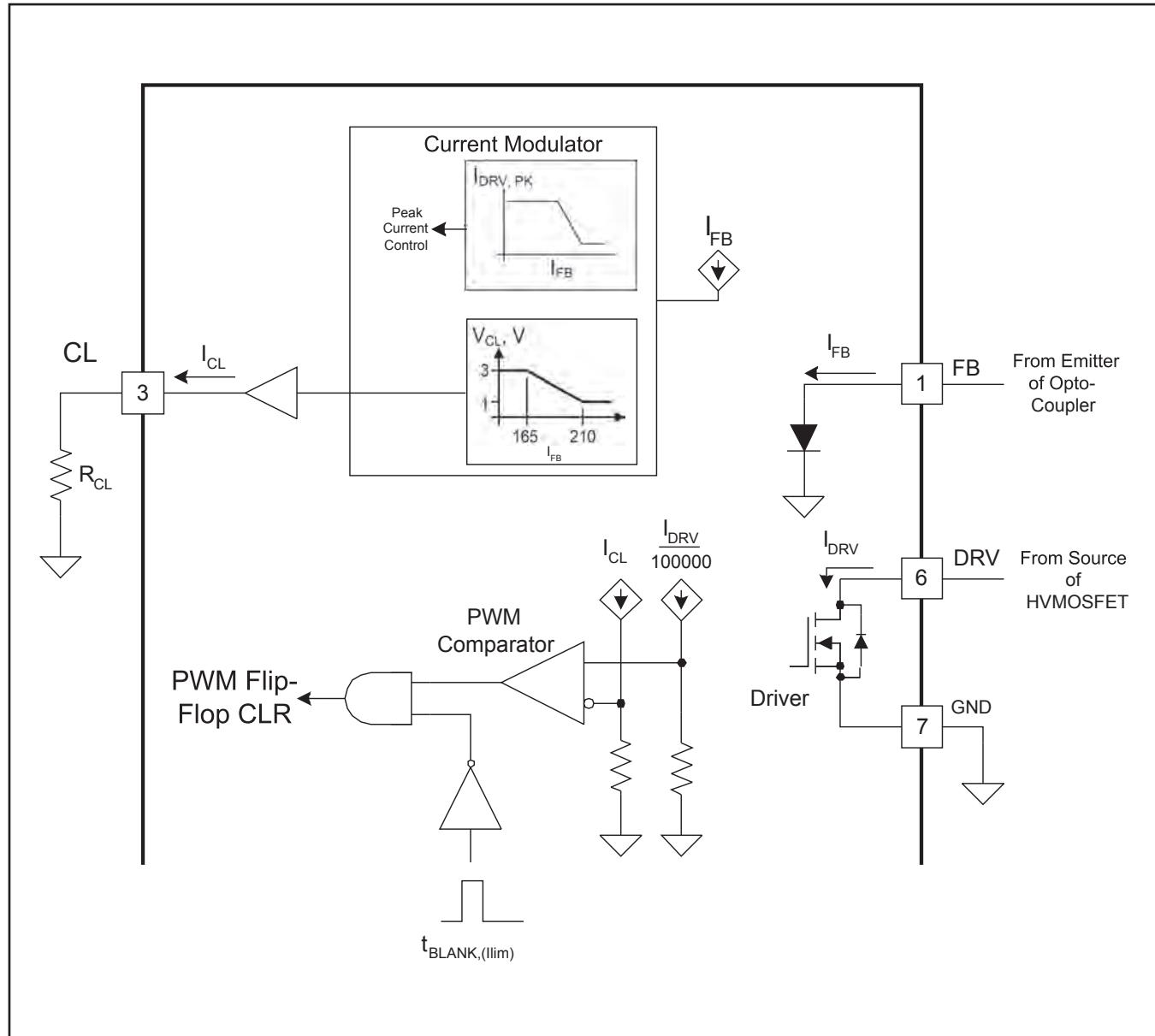

図 19. 概略ブロック図

# アプリケーション情報

## 一般的な動作

フライバック・コンバータは、出力との絶縁および幅広い入力動作能力を最小限の部品数で実現できるため、小電力AC/DCアプリケーションに最適です。特に、不連続導通モード(DCM)でのフライバック・コンバータの動作は、出力整流回路での逆電圧回復損失をなくし、制御を単純化できるという利点があります。

UCC28610は、無負荷動作時の低ACライン電力と高平均効率の両方を必要とする、12W~65WピークAC/DC電源アプリケーション向けのフライバック・コントローラです。このコントローラは、コンバータをDCM動作に制限します。連続導通モード(CCM)動作は行いません。強制的にDCM動作を行うことで、ACラインの変動に影響されない独自の安全な電流制限特性が得られます。コンバータがDCMで動作するため、ピーク電流モード変調回路にスロープ補償は必要ありません。

UCC28610の動作は、ソースを通して外部高電圧MOSFETを駆動することにより単純化されます。この構成をカスコード・ドライバと呼びます。この構成では、制御デバイスへの高電圧接続なしで、高速スタートアップと無負荷状態での低入力電力が実現されます。カスコード・ドライバは、フライバック・コンバータの動作全般には影響を与えません。

帰還ピンでは、電圧ではなく電流が使用されます。この独自の機能により、外部でフォトカプラの電流から電圧への抵抗による変換が不要となり、無負荷動作中の1次側消費電力が最小限に抑えられます。

UCC28610では、定ピーク電流、可変オフ時間の変調により、平均効率がピーク電力からピーク電力の22%までの範囲で最適化されます。この変調では、ピーク負荷の22%~100%の範囲内で効率が一定になる傾向があるため、EnergyStar™で要求される平均効率レベルを満足するために過剰な設計を行う必要がなくなります。

## トランジストの選択

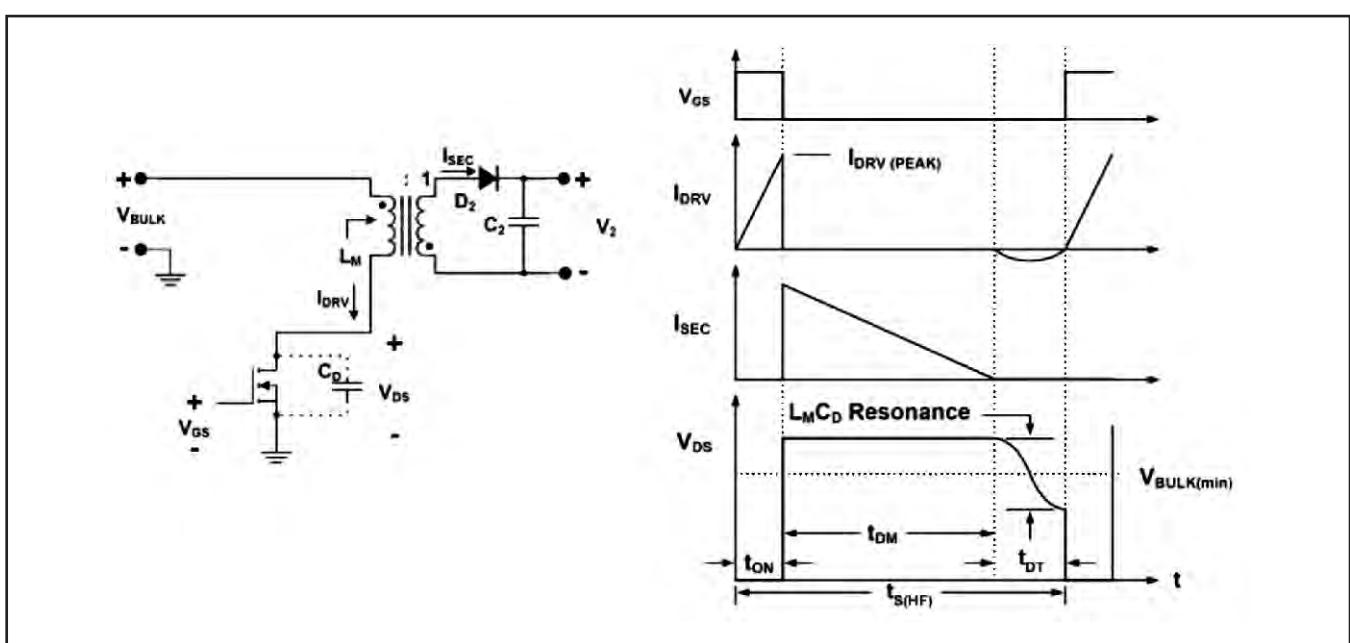

電源設計者は、電源設計を開始する前に、コンバータによって供給されるピーク電力、入力電圧範囲、出力電圧、および最大

許容バルク電圧リップルの見積り値を把握しておく必要があります。外部パワーMOSFETに対しては許容される最大のストレス電圧を選択します。ストレス電圧 $V_{DS}$ によって、フライバック・トランジストを反映する2次電圧と、1次/2次巻線比が決定されます。コンバータの概略図と波形を図20に示します。

ピーク電力は、コンバータ制御システムでレギュレーションを維持する必要のある最大電力レベルです。制御ループの時定数(100μs~300μs)よりも長く持続する負荷は、そのまま“ピーク電力”と見なされます。制御ループの時定数よりも短い時間の負荷は、制御ループ時定数の時間にわたって平均化できます。

最小スイッチング周期は、コンバータが周波数変調(FM)モードで動作しているときの値であり、 $t_{S(HF)}$ と表されます。このスイッチング周期は、最小入力電圧および最大負荷での合計スイッチング間隔に等しくなる必要があります(図20および式(1)を参照)。このスイッチング間隔は、 $t_{ON}$ (MOSFETの導通時間)、 $t_{DM}$ (トランジストの減磁時間)、および $t_{DT}$ (トランジスト減磁後のデッドタイム時間 = 共振サイクルの1/2)からなっています。

$$t_{S(HF)} = t_{ON} + t_{DM} + t_{DT} \quad (1)$$

最大許容 $V_{DS}$ 、最大入力ライン電圧、リーケージ・インダクタンスによる電圧スパイクの予測値、およびコンバータの目標レギュレーション出力電圧 $V_{OUT}$ を使用して、1次/2次巻線比 $N_{PS}$ を求めます。

$$N_{PS} = \frac{V_{DS} - \sqrt{2}V_{IN(max)} - V_{leakage\_spike}}{V_{OUT}} \quad (2)$$

HVMOSFETの出力容量およびリーケージ・インダクタンス値の変動を考慮して、デッドタイム $t_{DT}$ を合計最小スイッチング周期の5%と仮定します。

$$t_{DT} = 0.05 \times t_{S(HF)} \quad (3)$$

図 20. 基本的なフライバック・コンバータおよびピーク負荷で最小 $V_{BULK}$ 電圧での波形

VT積のバランスに基づき、減磁のためのVT積と等しい値を設定し、式をオン時間について解きます。

$$V_{BULK(min)} \times t_{ON} = V_{OUT} \times N_{PS} \times t_{DM} \quad (4)$$

$$t_{DM} = t_{S(HF)} - t_{ON} - t_{DT} \quad (5)$$

$$t_{ON} = \frac{V_{OUT} \times N_{PS} \times (t_{S(HF)} - t_{DT})}{V_{BULK(min)} + (V_{OUT} \times N_{PS})} \quad (6)$$

コンバータへの最大入力電力 $P_{IN}$ は、出力電力を全体効率で割った値に等しく、また、常に次の式に等しくなります。

$$P_{IN} = \frac{P_{OUT}}{\text{efficiency}} = \frac{(V_{BULK(min)} \times t_{ON})^2}{2 \times L_M \times t_{S(HF)}} \quad (7)$$

これを1次側インダクタンスの値について解きます。

$$L_M = \frac{(V_{BULK(min)} \times t_{ON})^2}{2 \times P_{IN} \times t_{S(HF)}} \quad (8)$$

この式は、1次側のRMS電流を最小にするために最適な1次側インダクタンスの近似値となります。実際の回路によっては、リーケイ・インダクタンスによる共振と遅延時間が測定可能である場合、低電圧スイッチングを最適化するために、励磁インダクタンス値を反復計算する必要があります。

CL抵抗 $R_{CL}$ は、コントローラの最大電力定数 $K_P$ に基づいて選択します。 $L_M$ の公差を考慮する必要があり（標準インダクタに対して-10%など）、CL抵抗の値は $L_M$ の最小値を使用して計算する必要があります。

通常動作範囲内でコントローラの過負荷保護機能が作動するのを防ぐため、電気的特性表に記載された $K_P$ の最小値を使用します。

$$R_{CL} = 33.2\text{k}\Omega \times \sqrt{\frac{K_P \times L_M}{P_{IN}}} \quad (9)$$

$R_{CL}$ を選択したら、ピークDRV電流を式 (10) で計算します。

$$I_{DRV(PK)} = \frac{100\text{kV}}{R_{CL}} \quad (10)$$

高効率を実現するために、バイアス巻線比 $N_{PB}$ は、コンバータがバースト・モードのときにVDD電圧がVGGクラップ値 (=  $V_{GG(DISABLED)}$ ) より高く保持されるよう設計する必要があります。VDDがこの値からHVMOSFETのスレッショルド電圧を引いた値よりも低く放電された場合、HVMOSFETがオンになり、バイアス巻線の代わりに高電圧レールからVDD電流がリニアに供給されます。VDDにツェナー・ダイオードを追加すると、過度のリーケージ・インダクタンスによるスパイク発生時にVDDがその絶対最大定格を超えないよう保護されます。

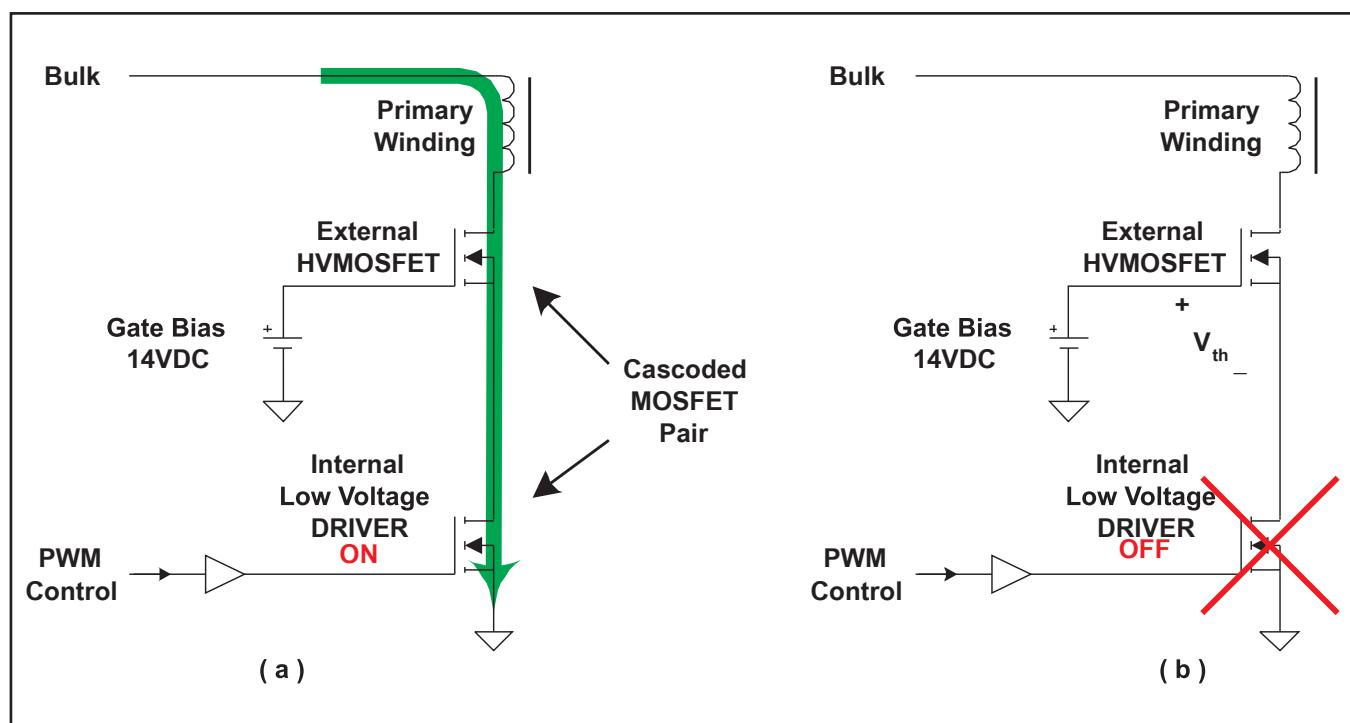

### カスコード・バイアスとスタートアップ

UCC28610では、カスコード構成のドライバおよびバイアスを使用して、高耐圧パワーMOSFETを制御し、スタートアップ時の初期バイアスを提供します。それにより、外部高電圧パワーMOSFETは、コンバータ動作中の電源スイッチングに加えてスタートアップ機能も提供します。カスコード・アキテクチャでは、図21のようなコモン・ゲート構成を利用し、高電圧MOSFET (HVMOSFET) のソースとグランドとの間で低電圧スイッチ動作を行います。これには、いくつかの重要なポイントがあります。

1. 外部HVMOSFETのゲートはDC電圧に保持されます。

2. HVMOSFETはゲートではなくソースを通して駆動されます。

3. 1次巻線電流の全体が内部低電圧ドライバMOSFETを流れます (DRVピンとGNDピンの両方)。

図 21. カスコード・アキテクチャ

UCC28610は、90mΩ FETの低電圧スイッチを、関連するすべての電流センスおよびドライブと統合しています。HVMOSFETは、高速の内部低電圧ドライバに追従するよう制御されます。ゲートは低インピーダンスDCソースに接続されているため、HVMOSFETのドレイン-ゲート電荷はターンオフ速度に影響を与えません。カスコード構成ではHVMOSFETのターンオフが非常に高速であるため、MOSFETのスイッチング損失が低く保持されます。

カスコード・ドライバ回路には、高速の電圧ゲインという特徴があります。このトポロジでは、小信号帯域幅が100MHz以上となり、高周波リギングが生じる可能性があります。高周波リギングはEMI問題の原因となり、状況によってはデバイスの破損にもつながります。ターンオンおよびターンオフ中およびその直後の短い期間が、特に発振の影響を受けやすくなります。この回避方法については、アプリケーション情報の「高周波リギングの解決」を参照してください。

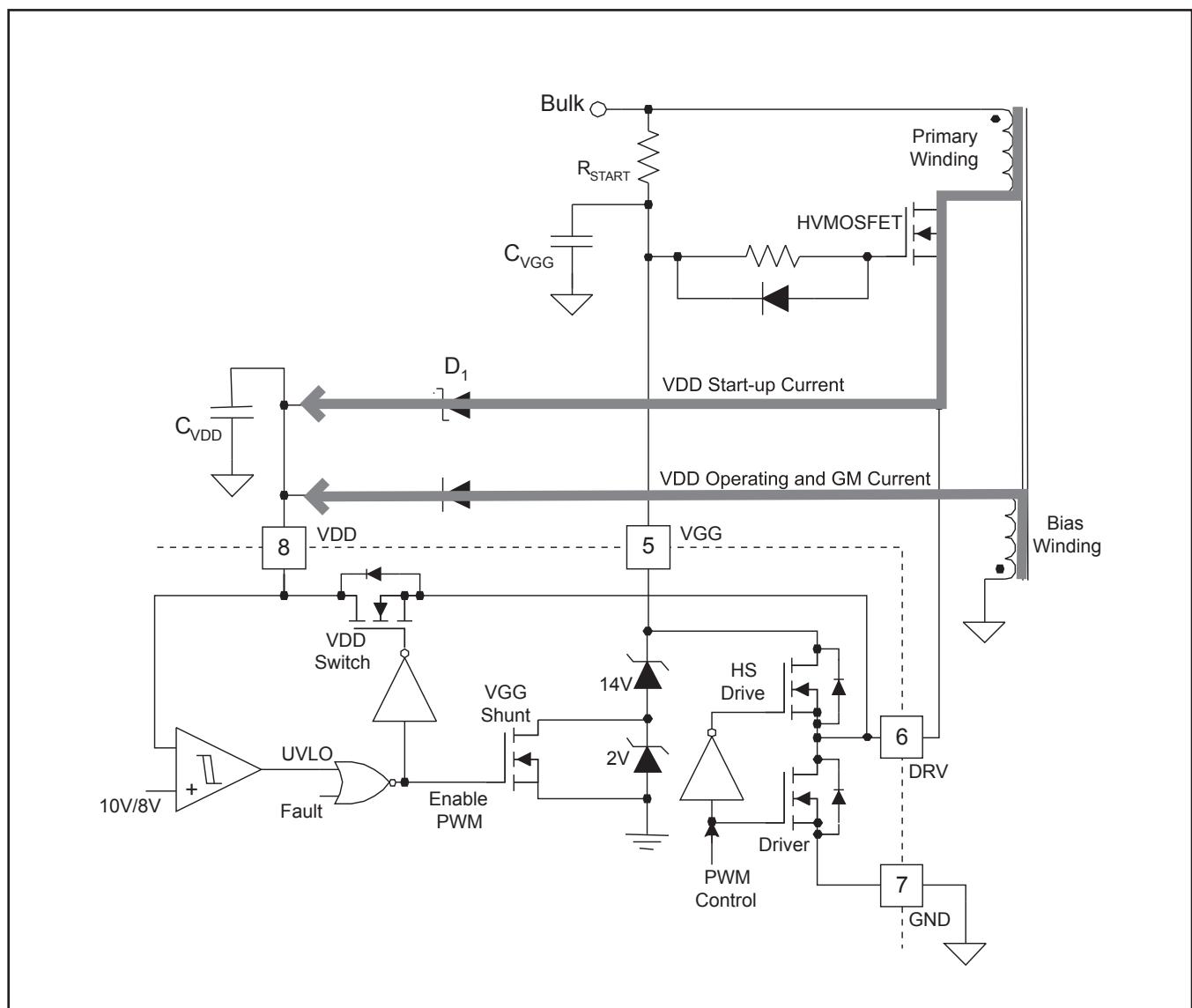

カスコード構成では、高速でありながら低損失である独自のスタートアップ・シーケンスを使用できます。スタートアップ・バイアスでは、ACライン、または整流とフィルタリングを経たACラインから、あるいは図22のようにバルク電圧( $R_{START}$ 経由)から、低レベルのブリード電流を使用します。この電流は、小さなVGGコンデンサ $C_{VGG}$ を充電し、HVMOSFETのゲート電圧が上昇します。この

間、VGGピンには標準で約6μAの電流( $I_{VGG(SREG)}$ )が流れ、小さなバルク・バイアス電流でVGGコンデンサの充電を維持できます。VGGがHVMOSFETのスレッショルド電圧に達すると、HVMOSFETはソース・フォロワとして動作します。その後、VGGが引き続き上昇すると、HVMOSFETはDRV電圧を持ち上げます。この間、UCC28610はUVLO状態であり、PWMイネーブル信号は“Low”です。これにより、VDDスイッチがオンになってVDDがDRVに接続されることで、VDDはHVMOSFETのソースによって上昇し、 $C_{VDD}$ を充電します。DRVとVDDの間には外部ショットキー・ダイオードD1が必要です。このダイオードは、内部VDDスイッチのボディ・ダイオードに高いスイッチング電流が流れるのを防ぎ、その電流の通り道となります。

可能な最小の無負荷電力を実現するには、VDDが16V-(HVMOSFETの $V_{TH}$ )より大きくなるようにバイアス巻線の巻数を選択します。通常は、バイアス巻線の電圧を17V~20Vとすると、損失が最小となります。多くの場合、バイアス巻線は1次リーカー・インダクタンスのターンオフ電圧スパイクに追従します。重負荷によってVDD電圧が過度に大きくなるようなアプリケーションでは、VDDとGNDの間に20Vのツェナー・ダイオードを配置してください。

図 22. カスコード・アーキテクチャのスタートアップ電流

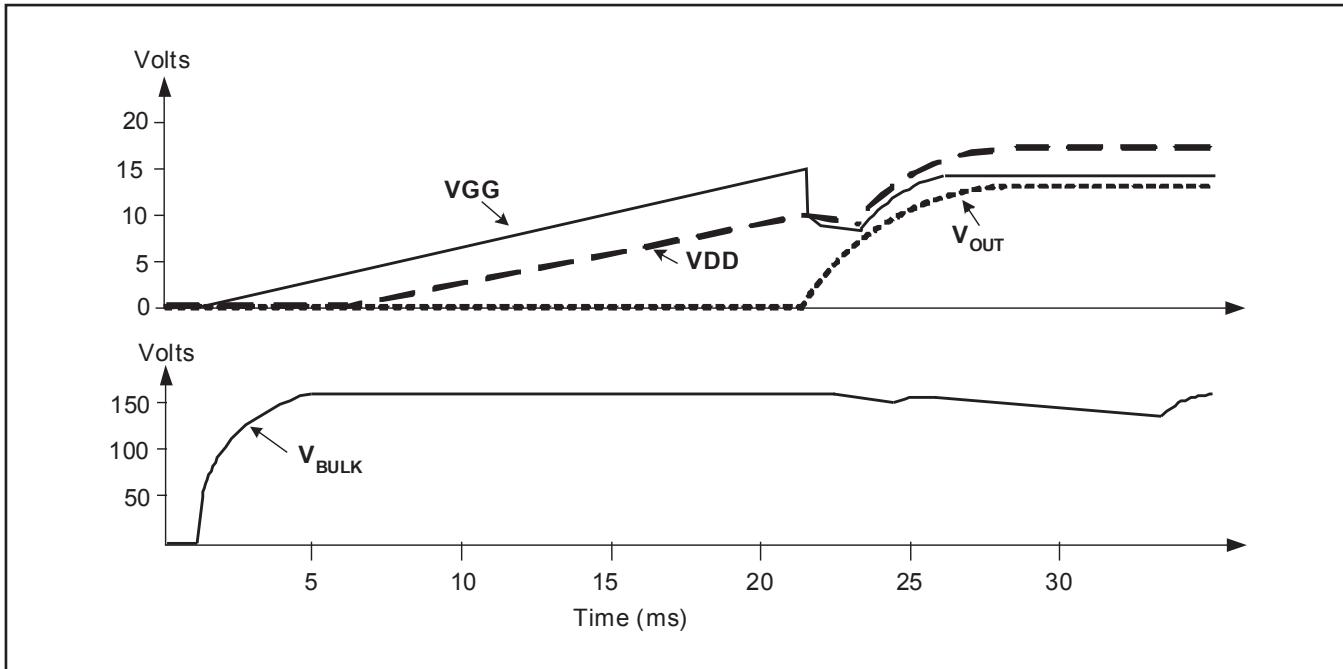

図 23. 17Vのバイアス巻線電圧に対する標準スタートアップ波形

標準のスタートアップ波形を図23に示します。VGGが上昇すると、VDD - (HVMOSFETのスレッショルド電圧)の値がそれに追従します。VDDが約10Vに達すると、UCC28610はスイッチングを開始します。バイアス電源電流 $I_{VDD}$ は動作レベルまで上昇し、これはVDDコンデンサから供給されます。VGGコンデンサを33nF~1000nFの範囲で選択し、最小ACライン電圧で15μAの電流が流れるような $R_{START}$ を選択することにより、スタートアップ時間を200ms以下に保持できます。コンデンサ $C_{VDD}$ の容量は、補助巻線に引き継ぐまでの時間、コントローラに動作バイアス電流を供給するのに十分な値を選択します。無負荷バースト動作を行う場合は、 $C_{VDD}$ 容量の要件がさらに大きくなる場合があります。

PWM動作がディスエーブルのときには、VGGの電圧は16Vにシャント・レギュレーションされます。外部HVMOSFETのゲートへの電圧ストレスを制限するため、これはスイッチング中には14Vに低減されます。適切なスタートを可能にするには、外部HVMOSFETのスレッショルド電圧が6V未満である必要があります。

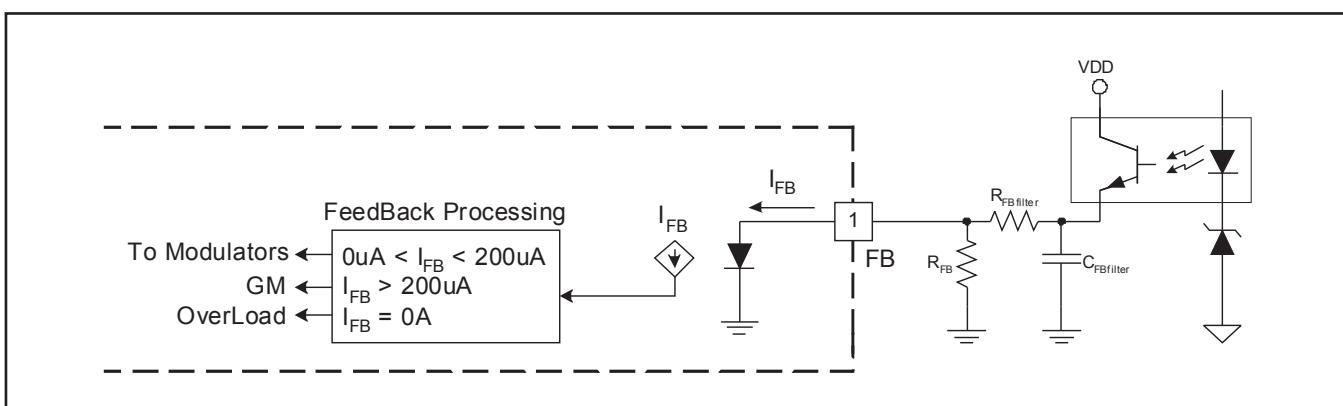

に使用されます。UCC28610では、内部電流ミラーを使用し、帰還処理ブロックにFB電流を印加した後、周波数変調回路および電流変調回路ブロックへと印加します。FBピンの電圧は、0.7Vで一定です。図24に示すように、フォトカップラのエミッタには、フォトカップラ出力のACフィルタリングを適用する必要があります。図24のフィルタのコーナー周波数は、コンバータの最大スイッチング周波数よりも10倍以上高くする必要があります(式(11)を参照)。FBピンとGNDの間に100kΩの抵抗 $R_{FB}$ を配置することにより、グランド・ノイズによってFBピンに負電流がバイアスされて過負荷タイマがリセットされるのを防ぎます。多くの場合、電流伝達比(CTR)が低いフォトカップラを使用すると、2次リファレンスのバイアス電流によって、高CTRデバイスよりも無負荷時の性能が向上します。また、CTRが低いと、高CTRデバイスよりもノイズ耐性が向上します。

$$f_{FB} = \frac{1}{2 \times \pi \times R_{FBfilter} \times C_{FBfilter}} \quad (11)$$

## 帰還機能

FBピンに電流を印加することで、変調およびモードを制御します。通常、FBピンは、出力誤差信号を変調回路に帰還するため

図 24. FBの詳細

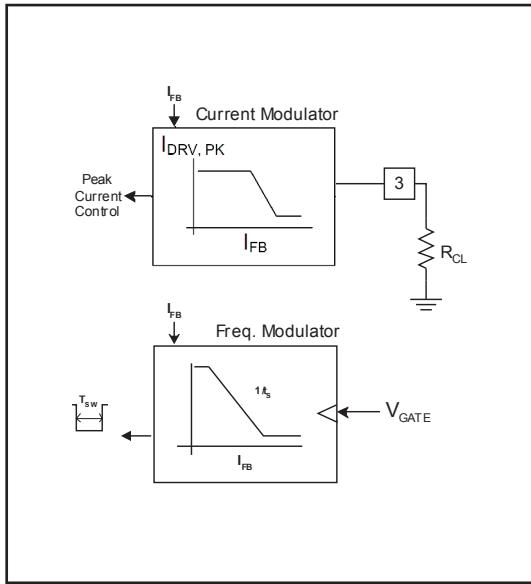

図 25. 変調制御ブロック

図 26 動作モードの制御図

## 変調モード

図25および図26に示すように、通常動作状態では、FBの電流によってUCC28610の動作モードが決定されます。FB電流により、コンバータは周波数変調(FM)モード、振幅変調(AM)モード、グリーン・モード(GM)という3つのモードのいずれかで動作します。

大きな電力負荷(ピーク・レギュレーション電力の22%~100%)では、コンバータはFMモードで動作します。ピークHVMOSFET電流は最大プログラミング値に達し、FB電流によってスイッチング周波数( $t_S$ に逆比例)を変化させることで出力電圧のレギュレーションを行います。スイッチング周波数は30kHz(ピーク電力の22%)~133kHz(ピーク電力の100%)の範囲で変調され、オン時間は一定であり、 $I_{DRV,PK}$ も一定です。最大のHVMOSFET電流 $I_{DRV,PK(max)}$ のプログラミングは、式(10)に示されるように、CLピンの抵抗によって設定されます。

中程度の電力レベル(ピーク・レギュレーション電力の2.5%~22%)では、コンバータはAMモードで動作します。FB電流により、スイッチング周波数を約30kHzに固定しながら、ピークHVMOSFET電流の振幅を最大プログラミング値の33%~100%の範囲で変調することで、出力電圧のレギュレーションを行います。UCC28610では、図25および図26に示されるように、CLピンの電圧を3V~1Vの範囲で変調することにより、ピーク電流の値を変化させます。

軽負荷(ピーク・レギュレーション電力の0%~2.5%)では、コンバータはGMモードで動作します。グリーン・モードでは、FB電流スレッショルドを使用したパルスのヒステリシス付きバーストによって、出力電圧のレギュレーションを行います。ピークHVMOSFET電流は、最大プログラミング値の33%です。パルス・バースト内でのスイッチング周波数は、約30kHzです。バースト間の間隔は、電源供給の制御ダイナミクスおよびFBヒステリシスによって制御されます。UCC28610では、軽負荷および無負荷状態中のエネルギーを節約するために、バースト間の内部バイアス電力を低減しています。

図 27. CLピンとDRV電流センス

## 1次電流センス

UCC28610では、カレントミラー手法を用いて、電流変調回路内の1次電流をセンスします。詳細については、図27を参照してください。1次電流はすべて、GNDピンからドライバMOSFETを通ってDRVピンへと流れます。ドライバMOSFET電流はスケーリングされてPWMコンパレータへ送られ、そこでCL電流と比較されます。各スイッチング・サイクルの開始時には、約220nsのブランкиング・パルス $t_{BLANK, (l)im}$ が内部電流制限回路に印加されることにより、回路に通常存在する容量性放電電流を立ち上がりエッジで誤って制限することなく、ドライバがオンになります。

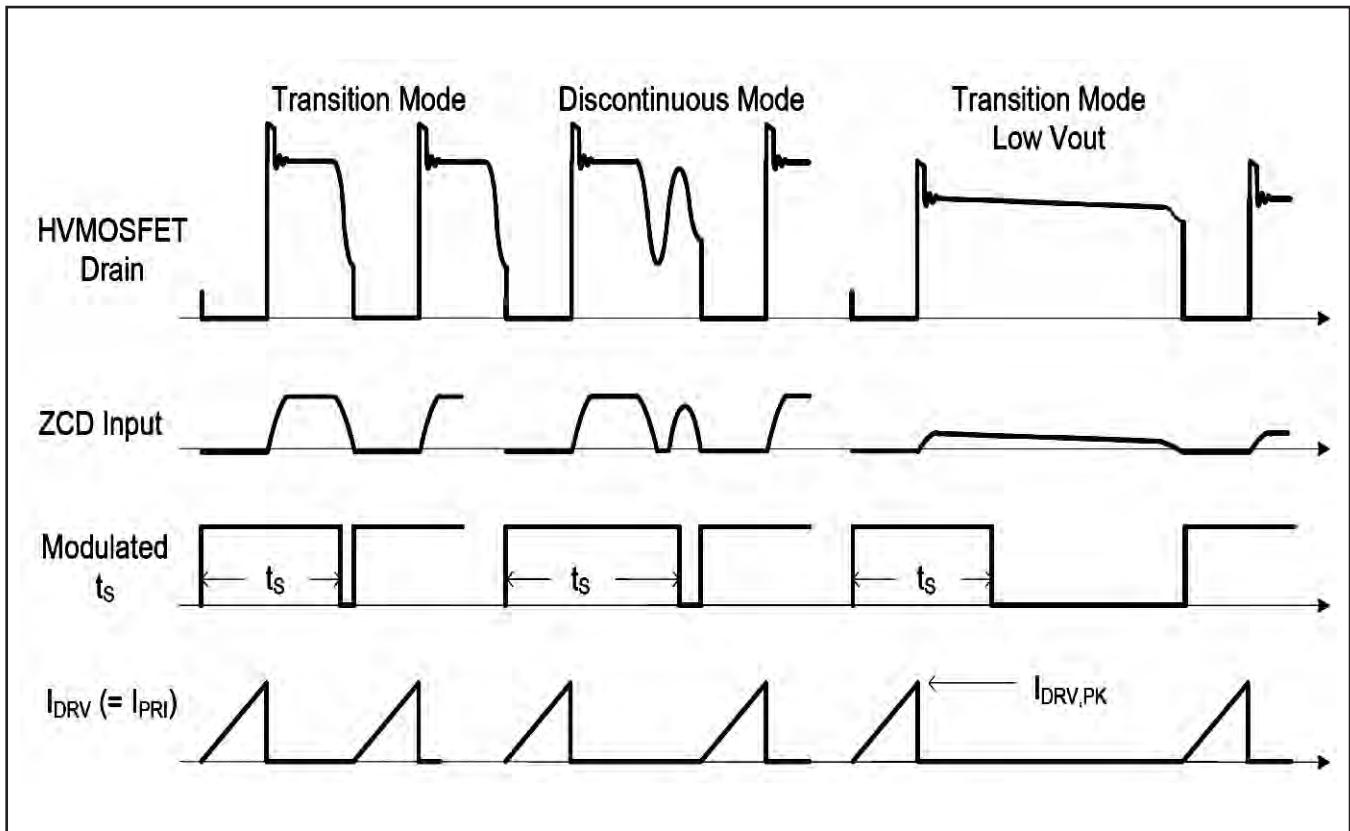

図 28. スイッチング・サイクル波形

### ゼロクロス検出

変調回路では、次のスイッチング・サイクルを開始するために3つの条件が必要となります。

1. 前回のターンオン・エッジからの時間が、帰還プロセッサによって要求される時間 (帰還電流I<sub>FB</sub>で決定) 以上経過した。

2. 前回のターンオン・エッジからの時間が、UCC28610に設定された最小期間 (通常は7.5μs = 133kHz) よりも長い。

3. ZCD電圧の正から負へのゼロクロスの直後。または、前回のゼロクロス検出からの時間がt<sub>WAIT,ZCD</sub> (約2.4μs) よりも長い。

各スイッチング・サイクルの前には、ZCDピンで最低1回ゼロクロスが検出されます。変調回路では、周期がダンピング制限を超える必要がある場合、パルス間で共振リングを抑制することができ、それによって無負荷動作中のパルス間に長い一時停止を挿入できます。

スイッチング周波数が133kHz(公称)を超えることは許可されません。これによって最大電力制限が設定されるため、この値は最小ライン電圧値を超えるすべてのバルク電圧に対して一定となります。

図28に、各種の動作状態におけるスイッチング・サイクル波形を示します。UCC28610は、インダクタ電流を常に不連続に保つよう設計されています。これにより、スタートアップ中や短絡状態時の電流のテーリングを防ぎ、供給される最大電力の制御を可能にしています。

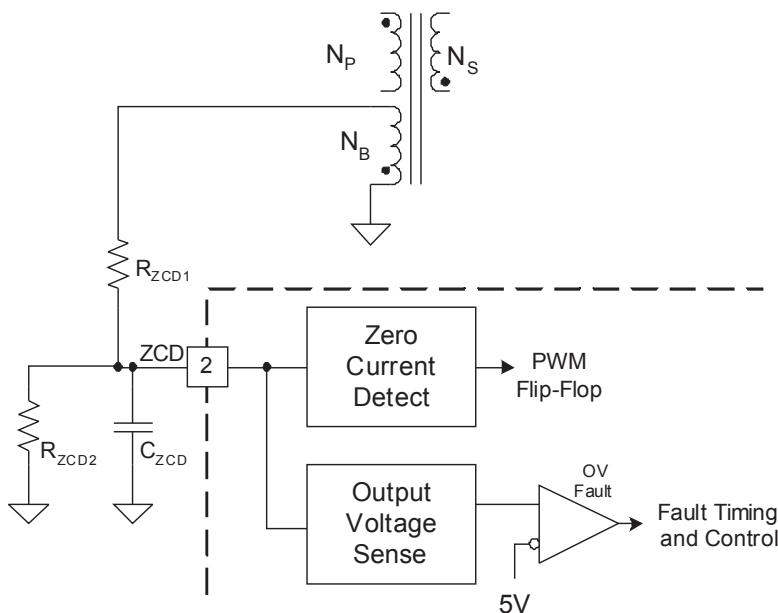

図29. ゼロクロス検出

図29に示すように、ゼロクロスはバイアス巻線に接続された分圧抵抗回路を使用して検出されます。バイアス巻線は、出力巻線と同相で動作します。ZCD機能では、ZCD電圧が低下して20mVのZCDスレッショルドZCD<sub>TH</sub>を通過したときに、トランジストの減磁を検出します。ZCDピンの電圧は、負の偏移を抑えるために内部で-160mV(ZCD CLAMP)にクランプされます。1次スイッチのターンオンを1次巻線波形の共振パレーに合わせるために、50ns~200nsの短い遅延をC<sub>ZCD</sub>によって追加できます。

$$R_{ZCD1} = \frac{V_{OUT} + V_F}{100\mu A} \times \frac{N_B}{N_S} \quad (12)$$

$$R_{ZCD2} = \frac{ZCD_{(ovp)} \times R_{ZCD1}}{\left( V_{OUT(pk)} \times \frac{N_B}{N_S} \right) - ZCD_{(ovp)}} \quad (13)$$

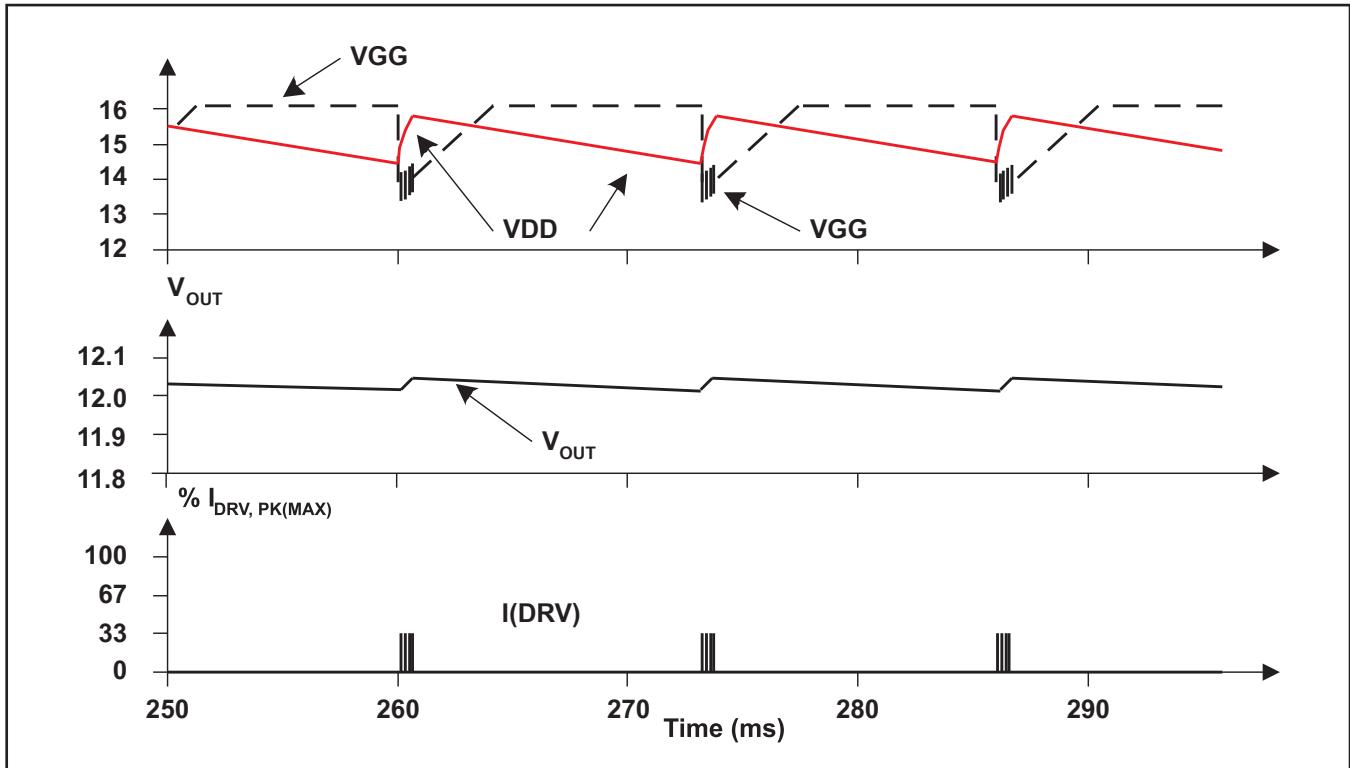

図 30. グリーン・モード動作

### グリーン・モード動作

軽負荷動作時、UCC28610は“GMオン”と“GMオフ”的2つの状態を周期的に繰り返します。図30に詳細を示します。GMオン状態では、変調回路が1つまたは複数のパルスからなるバーストを発行する間、コントローラがアクティブです。GMオフ状態では、コントローラが動作電流を低減し、スイッチング動作は禁止されます。オン状態とオフ状態の速さおよび長さは、 $I_{FB,GM\_HYST}$ だけ離れた2つのヒステリシス・スレッショルド間でFBピンへ流れる電流、および負荷電流、出力フィルタ・コンデンサ、さらに帰還回路の詳細によって決定されます。

GMオフ状態では、VDD電源電流が約550 $\mu$ Aの $I_{VDD(GM)}$ まで低減されます。PWMイネーブル信号は“Low”になり、それによってスイッチングが禁止され、VGGシャント・レギュレーションが約16Vの $VGG_{(DISABLED)}$ に設定され、VDDスイッチがオンになります。VGGノードは急速に16Vに充電され、VDDコンデンサから低いVDD電流が供給されます。

GMオン状態中、UCC28610は30kHzのレートでピーク1次電流を $I_{DRV,PK(max)}$ の33%にて制御します。スイッチング時、VGGシャント・レギュレータによってVGG電圧は約14Vに低下します。この時間中、VDDが14Vを下回らない限り、VDDは補助巻線から供給されます。コンバータの出力電圧の充電は、帰還回路によってFB電流がGMオフ・スレッショルド $I_{FB,CNR3}$ に達するまで行われ、その時点でコントローラはGMオフ状態に戻ります。

非常に軽い負荷では、PWMバースト間の時間が長くなる可能性があります。無負荷時電力を最小限に抑えるには、VDDが16VからHVMOSFETのスレッショルド電圧以上下回らないことが重要です。さもなければ、HVMOSFETがオンになり、高電圧バブル・レールからVDD電流がリニアに供給されます。 $C_{VDD}$ 容量を大きくすることで、スタートアップ時間に大きな影響を与えることなくVDD電圧を拡張できます。

### 最大コンバータ電力制限

UCC28610の推奨ピーク電力範囲は、電圧定格600Vの外部高電圧MOSFETを使用したとき、ユニバーサルACライン・コンバータ(AC90V~265Vの入力ライン電圧)に基づいて12W~65Wです。この電力範囲は、アプリケーションおよび外部MOSFETのストレス電圧によって異なる場合があります。最終的には、UCC28610を通って流れる必要があるピーク1次電流が制限要素となります。ピーク1次電流の制限により、ピーク1次電力が制限されます。平均電力ではなく、ピーク電力を65W未満とする必要があります。ピーク電力は、コントローラがレギュレーションを維持する最大の電力レベルと定義されます。

すべての電力レベルにおいて、UCC28610は1次インダクタンス、ピーク電流、および最大スイッチング周波数(133kHz)によって電力制限を制御するようプログラミングします。最大ピーク入力電力レベルは、式(14)で与えられます。電力制限の精度は、 $L_M$ 誤差および $f_{S(max)}$ 誤差よりも、 $I_{DRV(PK)}$ 誤差によって2倍大きな影響を受けます。負荷からの電力需要がプログラミングしたレベルよりも大きい場合は、電源出力電圧が低下し、過負荷タイマが開始されます。

$$P_{IN(max)} = \frac{L_m \times I_{DRV(pk)}^2 \times f_{S(max)}}{2} \quad (14)$$

### 最小コンバータ電力制限

DRV電流センスのダイナミクスにより、このコントローラには12Wの最小電力レベル制限があります。この電力レベル制限は、600VのMOSFETを使用した標準のユニバーサルACアダプタに対して見積もられるDRV電流から得られます。電力範囲および対応するピーク電流範囲は式(15)で与えられます。

$$P_{IN} \geq 12W$$

$$I_{DRV,PK(min)} \geq 1A \quad (15)$$

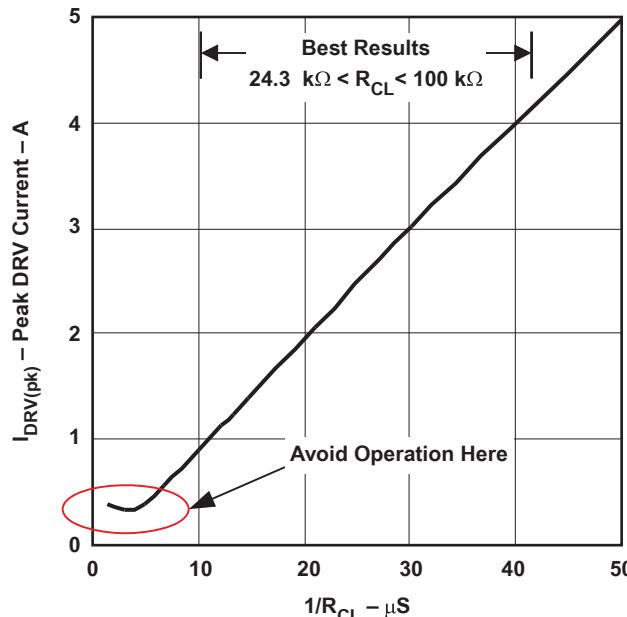

図31. 動的動作範囲

図31に示されるように、最小電力レベルは電力ミラーの直線性の喪失によるものです。 $I_{DRV,PK}$ レベルを0.66A~1Aにプログラミング( $100\text{k}\Omega \leq R_{CL} \leq 150\text{k}\Omega$ を使用)した場合、ピークDRV電流の2:1の振幅変調範囲だけが許可されます。 $I_{DRV,PK}$ を推奨動作範囲( $1.0\text{A} < I_{DRV,PK} < 4.1\text{A}$ 、それぞれ $100\text{k}\Omega > R_{CL} > 24.3\text{k}\Omega$ に対応)内にプログラミングした場合、 $I_{DRV}$ の振幅はリニアに変調されます。

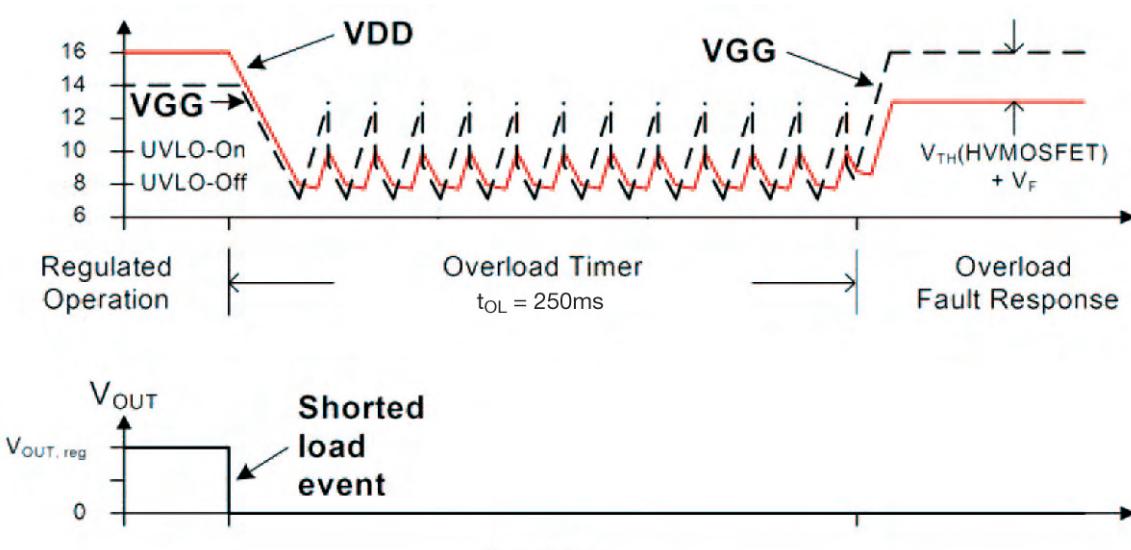

## 障害回復

過負荷状態が $t_{OL}$ (公称250ms)よりも長く継続した場合、UCC28610はプログラミングされた過負荷応答を行います。過負荷障害時の応答は、(1) ラッチオフ、または(2) シャットダウン/リトライ(750msのリトライ遅延時間後)です。過負荷応答は、MOT

ピンを使用してプログラミングします。強制DCM機能により、トランジストの飽和を防ぎ、トランジストの2次巻線の平均およびRMS出力電流を制限します。短絡負荷状態の場合も、トランジストの出力電流は式(16)に示されるレベルに制限されます。ここで、 $N_{PS}$ は1次/2次巻線比です。短絡負荷に対する標準的な動作を図32に示します。

$$I_{SECONDARY, AVG (SHORTELOAD)} = \frac{N_{PS} \times I_{DRV(Peak)}}{2}$$

$$I_{SECONDARY, RMS (SHORTELOAD)} = \frac{N_{PS} \times I_{DRV(Peak)}}{\sqrt{3}} \quad (16)$$

図32. 出力短絡時の過負荷動作

シャットダウン/リトライ・モードでは、750msのリトライ遅延時間後にスイッチングが再イネーブルされます。ラッチオフ・モードでは、障害状態の検出時にDRVピンで7.5kΩの負荷がアクティブになります。この内部の7.5kΩ負荷には、バルク・コンデンサからHVMOSFETおよびトランジスタの1次巻線を通じて電流が流れます。また、ラッチオフ状態では、バイアス電圧VDDもHVMOSFETによってレギュレーションされます。ACライン電圧が供給されなくなると、2.8mAの電流I<sub>DRV,DSCH</sub>によってバルク・コンデンサが放電されます。最終的に、バルク電圧が十分低くなると、VDDが放電されます。VDDが障害リセット・レベルVDD<sub>(FAULT RESET)</sub>(= 約6V)を下回った後、入力電圧が印加されると、通常のスタートアップ・サイクルを開始できます。

## 最大オン時間とブラウンアウト

強制DCM機能により、入力電圧が非常に低くなった場合の過度な1次電流に対する保護が提供されます。起こりうる最大の2次電流は式 (16) で表されます。UCC28610では、ユーザが最大オン時間をプログラミングすることで、さらに保護を強化できます。

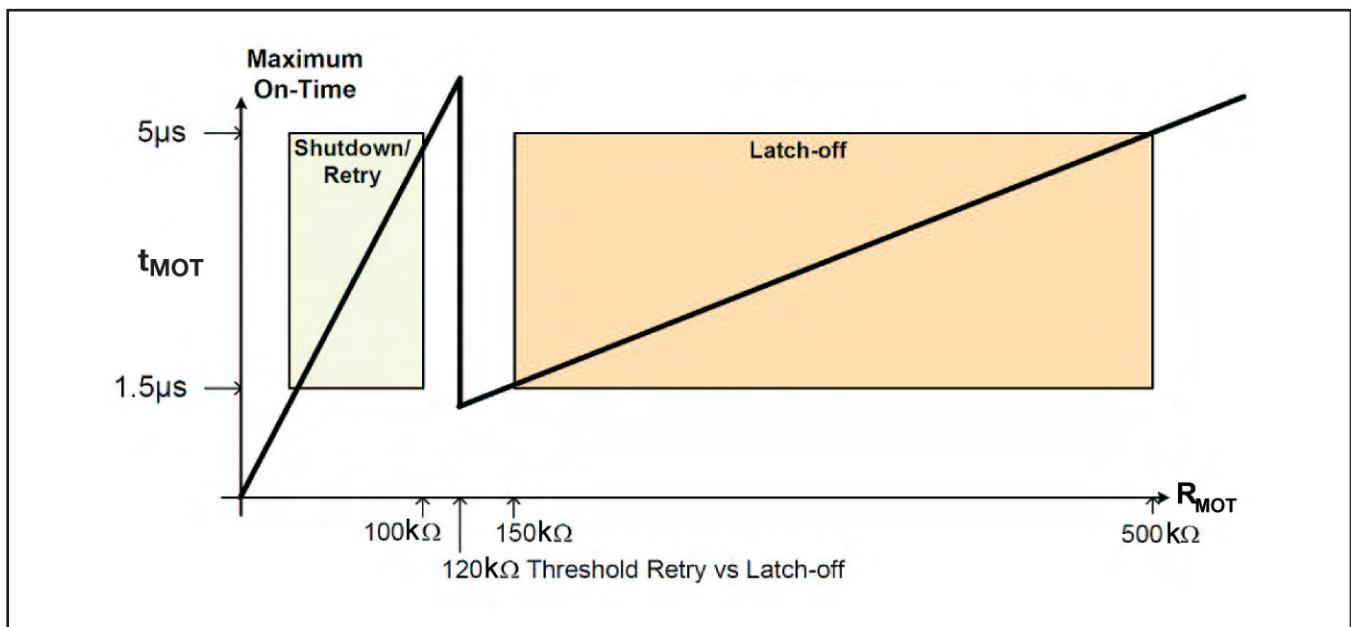

最大オン時間 (MOT) 機能により、ライン電圧の降下状態中に負荷が十分に大きい場合、コンバータは過負荷状態であるかのように動作します。低ライン電圧状態中は、MOT機能によって1次スイッチのオン時間が制限され、それにより1次電源段のピーク電流が制限されます。図33では、各範囲のプログラミング抵抗に対して、MOT期間t<sub>MOT</sub>を1.5μs～5μsの範囲にわたってどうプログラミングするかを示しています。この抵抗の範囲によって、過負荷障害が持続した場合のコントローラの応答(ラッチオフまたはシャットダウン/リトライ)が決定されます。これは、ラインの低下(ブラウンアウト)状態に対する応答と同じです。

## MOTピンを使用した外部シャットダウン

多くのアプリケーションでは、外部手段によって電源をシャットダウンする機能が必要となります。この機能は、MOTとGNDの間にそれぞれNPNトランジスタのコレクタとエミッタを接続することで簡単に実現できます。このNPNトランジスタは、絶縁型アプリケーション

の場合はオプトアイソレータのフォトトランジスタを使用できます。

過電流またはブラウンアウトに対するラッチオフ応答の場合:

$$R_{MOT} = t_{MOT} \times \left( 1 \times 10^{11} \frac{\Omega}{s} \right) \quad (17)$$

ここで

$$150 \text{ k}\Omega \leq R_{MOT} \leq 500 \text{ k}\Omega \quad (18)$$

$$1.5 \text{ }\mu\text{s} \leq t_{MOT} \leq 5 \text{ }\mu\text{s}$$

過電流またはブラウンアウトに対するシャットダウン/リトライ応答の場合:

$$R_{MOT} = t_{MOT} \times \left( 2 \times 10^{10} \frac{\Omega}{s} \right) \quad (19)$$

ここで

$$25 \text{ k}\Omega \leq R_{MOT} \leq 100 \text{ k}\Omega \quad (20)$$

$$1.5 \text{ }\mu\text{s} \leq t_{MOT} \leq 5 \text{ }\mu\text{s}$$

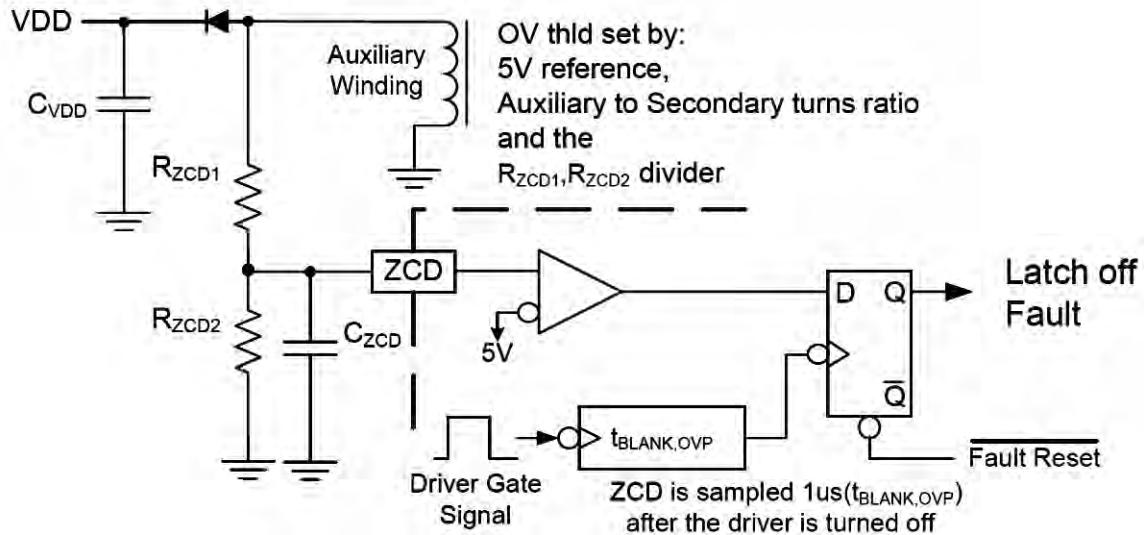

## 過電圧検出

UCC28610コントローラは、補助巻線の電圧をサンプリングすることにより、出力電圧を監視します。サンプリング時間には、内部ドライバがオフになった後、1μsの固定遅延(t<sub>BLANK,OVP</sub>)があります。これにより、バイアス巻線電圧が過渡事象から安定した後で補助巻線をサンプリングできます。この同じ遅延時間を使用してZCD入力をブランディングすることにより、リングが大きくZCDゼロクロス・スレッショルドを超えるような場合に、意図しないゼロクロス検出を避けることができます。

出力過電圧(OV)スレッショルドは、出力2次巻線に対する補助巻線の巻線比、およびZCD入力ピンへの分圧抵抗を使用して設定されます。UCC28610は、OV状態を検出すると常にラッチオフ状態になります。再起動して回復するためには、VDD電源がいったん障害リセット・スレッショルドを下回る必要があります。過電圧検出機能の動作を図34に示します。

図 33. MOTのプログラミングと過負荷障害応答

図 34. ZCDピンによる出力過電圧保護

## 高周波リングングの解決

カスコード・ドライバ回路には、高速の電圧ゲインという特徴があります。このトポロジでは、小信号帯域幅が100MHzを大きく上回り、高周波リングングが生じる可能性があります。スイッチ・サイクルのターンオフ期間中、内部のHSドライブMOSFETによって、外部HVMOSFETのゲート-ソース間が短絡されます。これにより、HVMOSFETによってコンバータ内のLC共振回路（トランスの磁化インダクタンスと浮遊ドレイン容量）が無用に励磁されるのを防ぎます。DRVのターンオフとHSドライブのターンオンの間の組み込みデッド・タイム中には、高周波リングングが生じる場合があります。このデッド・タイム中は、電源部品を通して大きなエネルギーが伝達されます。過度の高周波リングングはEMI問題の原因となり、状況によってはデバイスの破損にもつながります。

## 高周波リングングの特定

高周波リングングは、HVMOSFETのソースとDRVピンとの間で生じる浮遊容量と浮遊インダクタンスのリングングによるものです。高電圧MOSFETのスレッショルド電圧が低く、ピークDRV電流が大きい場合、リングングが悪化する可能性があります。破壊的なリングング状況では、コンバータが最初は容易にパワーアップしてレギュレーションに達しても、それ以降起動しなくなる可能性があります。

リングングは、次のいずれかまたは両方の条件で観測されます。

- コンバータのコールド・スタート中の最初のHVMOSFETのターンオフ( $V_{GG} > V_{DD}$ )。

- コンバータがプログラミングされた $I_{DRV,PK}$ レベルでHVMOSFETをスイッチングしている定常状態での、HVMOSFETのターンオフ・エッジ( $V_{DD} > V_{GG}$ )。

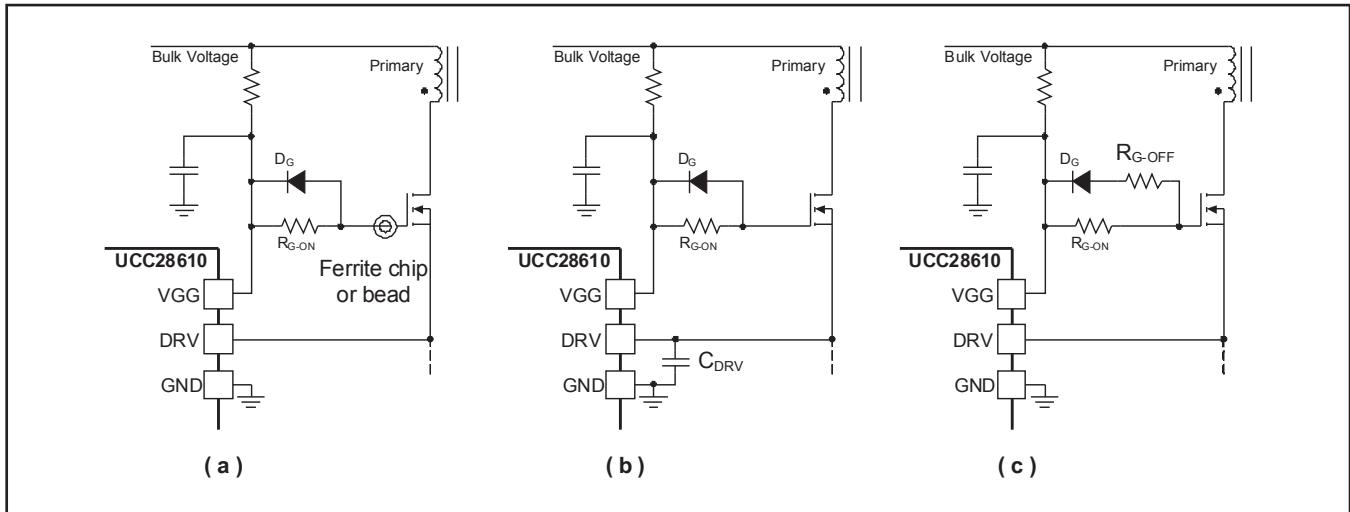

図 35. 高周波リングの解決方法、(a) フェライト・チップ、(b) CDRV、(c) RG-OFF

## HFリングの回避

カスコードMOSFETドライブでの高周波リング問題は、多くの場合、回避することができます。多くのコンバータでは、大きな $V_{th}$ 、大きな $R_{DS(on)}$ 、低いトランスコンダクタンス・ゲインのHVMOSFETを使用するか、または低電流で動作することにより、この問題が生じません。また、浮遊インダクタンスを最小限に抑えることによっても、リングの問題を回避できます。HVMOSFETのソースとDRVピンの間のパターンは、ごく短く、1cm未満にする必要があります。HVMOSFETのソース・リードには電流プローブ・ループを追加しないでください。また、HVMOSFETのソース・リードにはフェライト・ビーズを配置しないでください。

リングを避けることができない場合、スイッチング過渡事象中のリングを解決する最も効率的で効果的な方法は、以下のとおりです。

1. HVMOSFETのゲートにフェライト・チップまたはフェライト・ビーズを接続。

2. DRVとGNDの間に小さなコンデンサを接続。

3. ゲート・ターンオフ抵抗を使用。この3つの方法は、図35に示すように、別々にまたは組み合わせて使用できます。

## フェライト・チップまたはビーズによる解決

HVMOSFETのゲートにフェライト・チップまたはビーズを接続すると、HVMOSFETのゲート、ソース、およびドレン回路のリングを最小の追加損失で抑制できるため、最良の結果が得られます。リング周波数範囲内の抵抗値に対してフェライト・チップを選択します(例えば、100MHzで60Ω)。フェライト・チップまたはビーズのピーク電流定格は、ターンオフ中に発生するドレン-ゲート間放電電流に対して十分に大きい必要があります。ビーズのリアクタンスが大きすぎると、ピーク負荷時にVGGで低周波サージが発生する可能性があります。通常は、0603フェライト・チップ・デバイスで良好な結果が得られます。

## DRVコンデンサによる解決

DRVとGNDの間にコンデンサを接続すると、VGGでのリングを低減できます。DRVコンデンサは、最初のターンオフ・エッジ中および全負荷動作時のターンオフ・エッジ中のVGGピンに対する

効果を観察しながら、実験的に選択します。効率が大きく低下することのないよう、コンデンサは3.3nF未満にする必要があります。Y5V誘電体を使用したものなど、低Qのコンデンサを使用します。この手法は、リングを完全に抑制することはできませんが、HVMOSFETのソースとDRVピンとの間の浮遊インダクタンスに対して十分な保護を提供します。

## ゲート・ターンオフ抵抗による解決

$0\Omega < R_{G-OFF} < 5\Omega$ の範囲のゲート・ターンオフ抵抗によって、リングを抑制できます。HVMOSFETの浮遊ソース・インダクタンスによってHSドライブMOSFETのボディ・ダイオード経由でVGGが過充電されるのを防ぐため、また、追加の遅延によって生じるピーク電流誤差の問題を防ぐために、ターンオフ抵抗は制限されます。ゲート抵抗によるダンピング効果は、低電流でソース・インダクタンスの小さいアプリケーションで良好に機能します。

DCM動作によるHVMOSFETターンオン遷移中は、ずっと大きな抵抗が許容できます。ターンオン遅延によるバレー・スイッチングへの影響を防ぐため、ターンオン抵抗の推奨範囲は $0\Omega < R_{G-ON} < 200\Omega$ です。

## 過熱シャットダウン

UCC28610は、内部の過熱シャットダウン回路によって過熱から保護されます。接合部温度が過熱シャットダウン点 $T_{SD}$ を超えた場合、UCC28610は、シャットダウン・イベントを開始し、リトライ時間 $t_{RETRY}$ 後にリトライを許可します。接合部温度が $(T_{SD} - T_{SD\_HYST})$ を下回るまで、シャットダウン/リトライ・サイクルが継続されます。

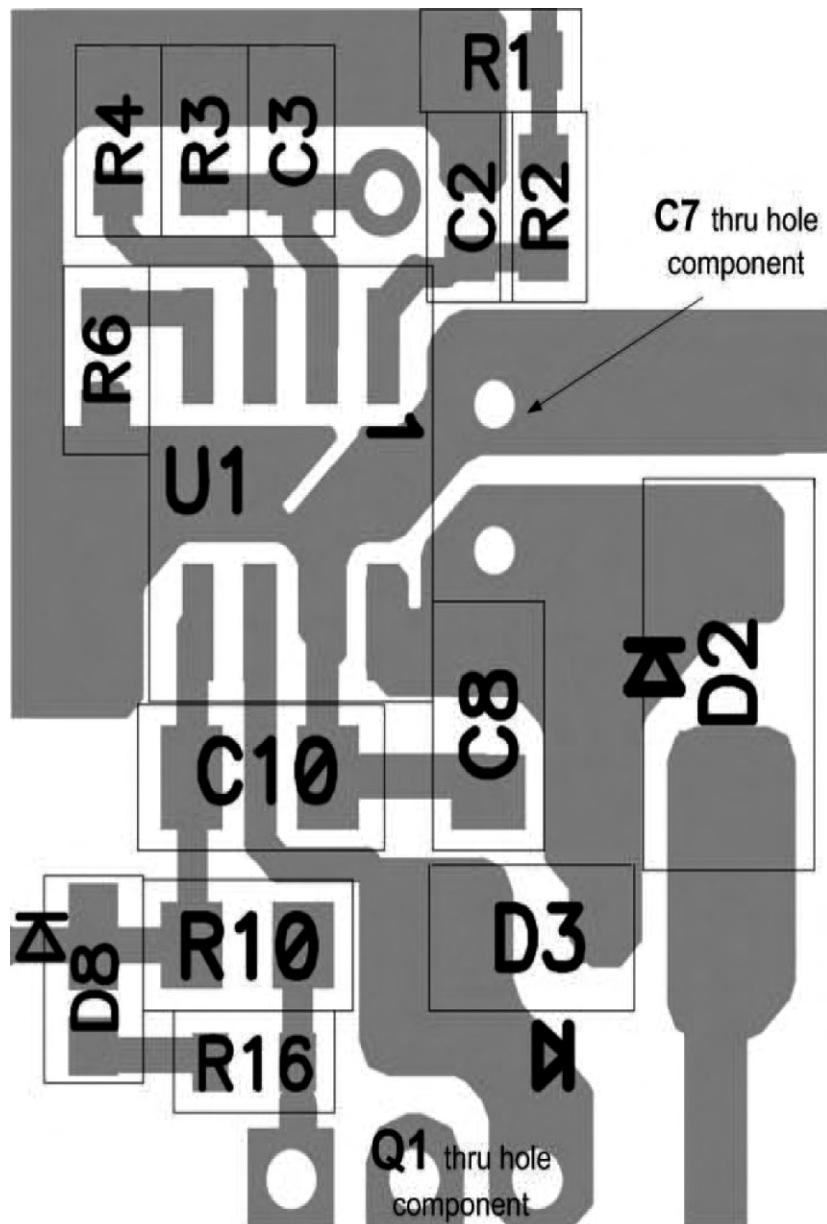

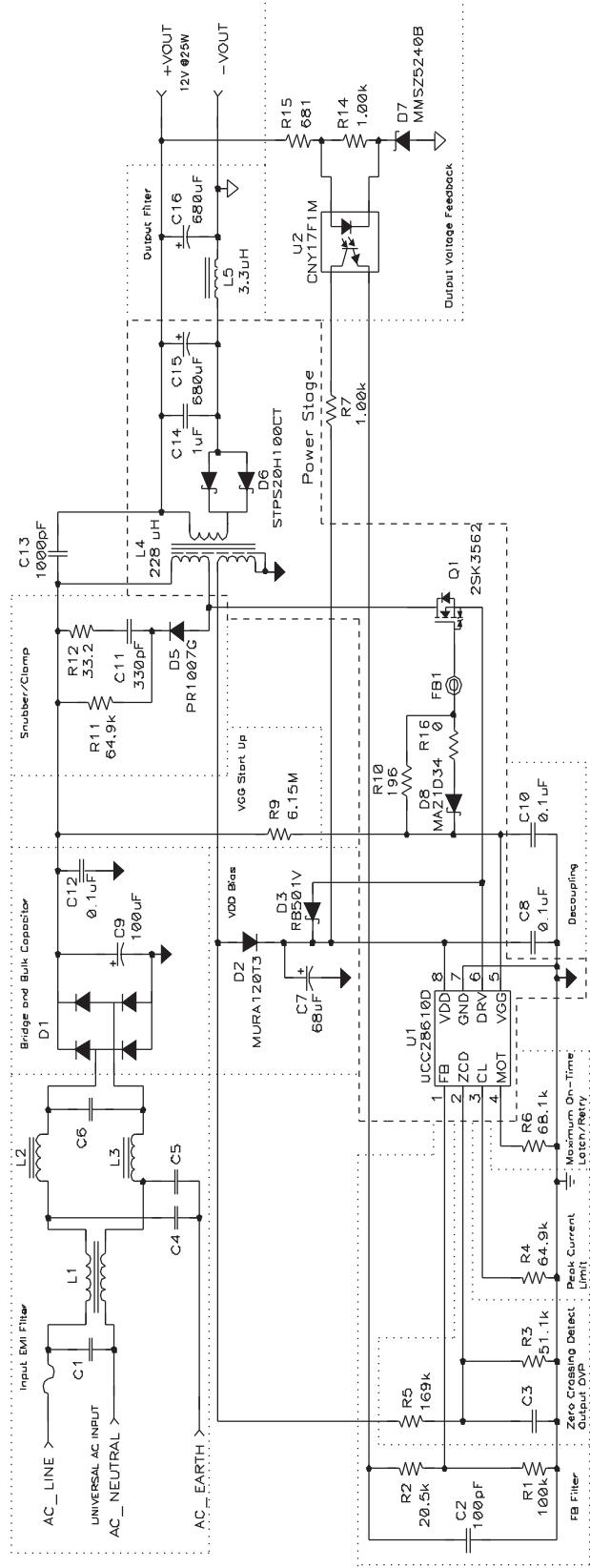

## 標準回路およびレイアウト

UCC28610を使用して、単層基板上での電源設計が可能です。図36および図37に、それぞれ標準レイアウトおよび設計の例を示します。グランド・プレーンを適切に使用することで、EMIおよび熱の問題を解決できます。最良の結果を得るには、ピン1～4に関連付けられた部品に対して、低雑音のグランド・プレーンを作成しま

す。これは、制御信号に対するシールドとなります。また、UCC28610に対する熱源とならないよう、グランド・プレーンは、ヒート・シンク、サーミスタ、およびスナバの下を避けて配置します。

図 36. 単層PCB上の標準レイアウト

注:部品の識別記号は、図37の回路図に示された各部品に対応しています。

図 37. 標準設計回路図

## 端子部品

部品の識別記号については、図1を参照してください。

表 1. 端子部品

| 名前  | 端子 | 説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CL  | 3  | $R_{CL} = 33.2k\Omega \times \sqrt{\frac{K_p \times L_M}{P_{IN}}}$ $I_{DRV(PK)} = \frac{100 \text{ kV}}{R_{CL}}$ <p>ここで、<math>K_p = 0.54 \text{ W}/\mu\text{H}</math><br/> <math>L_M = 1\text{次インダクタンスの最小値}</math><br/> <math>P_{IN} = P_{OUT}/\eta</math><br/> <math>\eta = \text{効率}</math></p>                                                                                                                                                                                                                                                                                                                 |

| DRV | 6  | <p>Q1: 十分な電圧/電流定格を持つパワーMOSFET。<math>V_{GS}</math>は20V以上の静的定格を持つ必要があります。</p> <p>D1: ショットキー・ダイオード、定格30V以上、DRV-VDD間に配置。</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| FB  | 1  | $R_{FB} = 100 \text{ k}\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| GND | 7  | $VDD$ へのバイパス・コンデンサ、 $C_{BP} = 0.1\mu\text{F}$ 、セラミック                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| MOT | 4  | <p>過電流障害に対してラッチオフ応答を行う場合:<br/> <math>t_{MOT} = 250\text{ms}</math>遅延後のユーザ・プログラミング可能な最大オン時間</p> $R_{MOT} = t_{MOT} \times \left( 1 \times 10^{11} \frac{\Omega}{\text{s}} \right)$ <p>ここで</p> <ul style="list-style-type: none"> <li><math>150 \text{ k}\Omega \leq R_{MOT} \leq 500 \text{ k}\Omega</math></li> </ul> <p>過電流障害に対してシャットダウン/リトライ応答を行う場合:</p> $R_{MOT} = t_{MOT} \times \left( 2 \times 10^{10} \frac{\Omega}{\text{s}} \right)$ <ul style="list-style-type: none"> <li><math>25 \text{ k}\Omega \leq R_{MOT} \leq 100 \text{ k}\Omega</math> および <math>t_{MOT} \leq 5 \mu\text{s}</math></li> </ul> |

| VDD | 8  | $C_{VDD} = \frac{I_{VDD(GM)} \times t_{BURST}}{\Delta VDD_{(BURST)}}$ <p>ここで:<br/> <math>\Delta VDD_{(BURST)}</math>はバースト動作中の許容VDDリップル<br/> <math>t_{BURST}</math>はバースト期間の見積もり値<br/> 標準<math>C_{VDD}</math>値は約<math>47\mu\text{F}</math><br/> <math>D_{BIAS}</math>の電圧定格は下記の値以上:</p> $V_{DBIAS} \geq V_{OUT} \frac{N_{PS}}{N_{PB}} + \frac{V_{BULK(max)}}{N_{PB}}$ <p>ここで:<br/> <math>V_{DBIAS}</math>はダイオードD2の逆方向電圧定格<br/> <math>V_{BULK(max)}</math>は、最大ライン電圧での<math>C_{BULK}</math>の最大整流電圧</p>                                                                                                                 |

| VGG | 5  | $C_{VGG}$ からGNDへの接続長は最小化<br>$C_{VGG} = \text{HVMOSFETの} C_{GS} \text{の10倍以上、通常は}$<br>$C_{VGG} = 0.1\mu\text{F}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 名前  | 端子 | 説明                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ZCD | 2  | $R_{ZCD1} = \frac{V_{OUT} + V_F}{100 \mu A} \times \frac{N_{PS}}{N_{PB}}$ $R_{ZCD2} = \frac{ZCD_{(ovp)} \times R_{ZCD1}}{\left( V_{OUT(pk)} \times \frac{N_{PS}}{N_{PB}} \right) - ZCD_{(ovp)}}$ <p>ここで<br/> <math>ZCD_{(ovp)}</math>はZCDでの過電圧障害スレッショルド<br/> <math>N_{PS}</math>は1次/2次巻線比<br/> <math>N_{PB}</math>は1次/バイアス巻線比<br/> <math>V_{OUT}</math>は2次側の平均出力電圧<br/> <math>V_F</math>は2次側整流回路の順方向バイアス電圧<br/> <math>V_{OUT,PEAK}</math>は目的の出力過電圧障害レベル</p> |

注1. 特に記述のない限り、すべての定数および測定値については、電気的特性表を参照してください。

注2. 表1に示されたすべての部品の位置については、図1を参照してください。

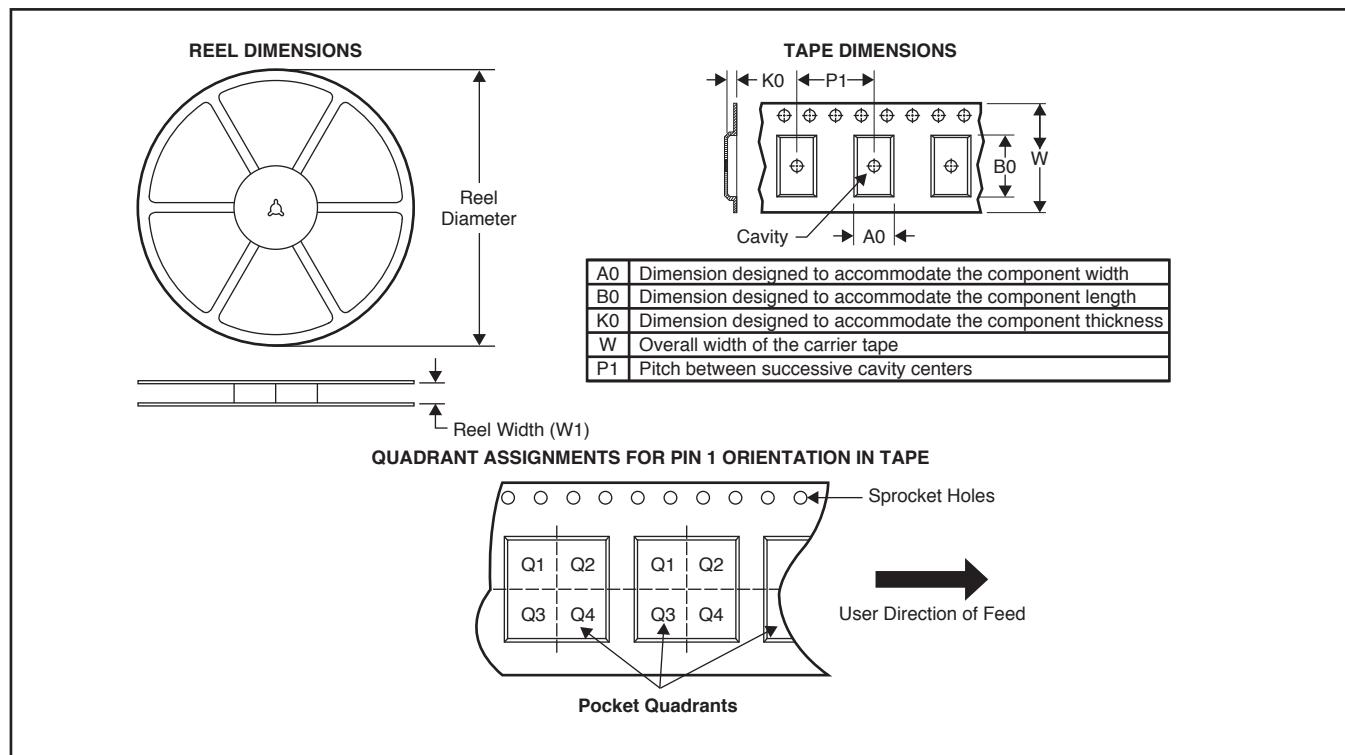

# パッケージ・マテリアル情報

## テープおよびリール・ボックス情報

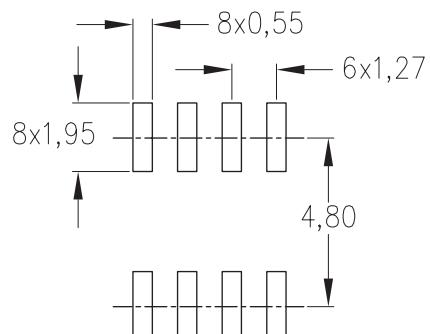

\*All dimensions are nominal

| Device     | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| UCC28610DR | SOIC         | D               | 8    | 2500 | 330.0              | 12.4               | 6.4     | 5.2     | 2.1     | 8.0     | 12.0   | Q1            |

## パッケージ・マテリアル情報

### TAPE AND REEL BOX DIMENSIONS

\*All dimensions are nominal

| Device     | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------|--------------|-----------------|------|------|-------------|------------|-------------|

| UCC28610DR | SOIC         | D               | 8    | 2500 | 340.5       | 338.1      | 20.6        |

# メカニカル・データ

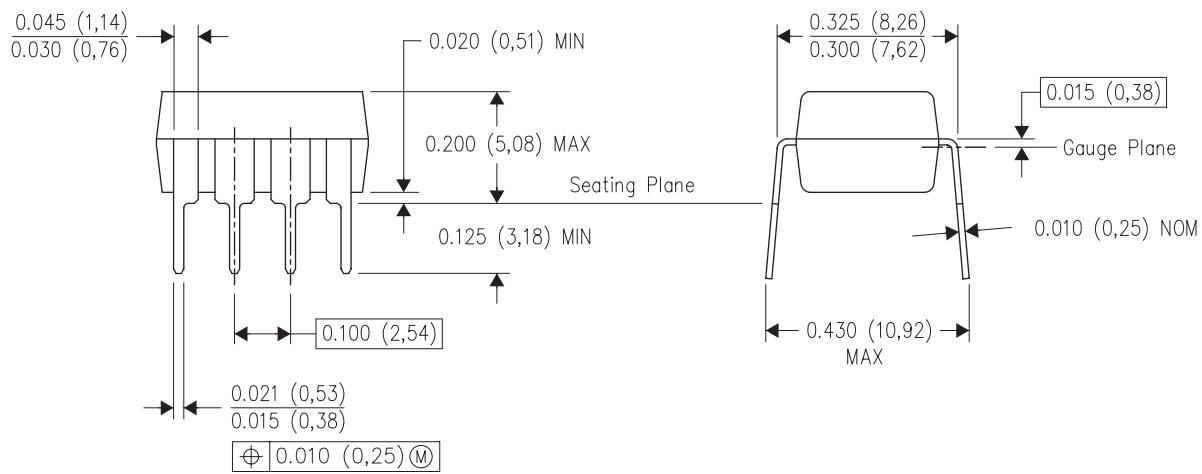

P(R-PDIP-T8)

PLASTIC DUAL-IN-LINE PACKAGE

4040082/E 04/2010

- 注: A. 全ての線寸法の単位はミリメートルです。

B. 図は予告なく変更することがあります。

C. JEDEC MS-001 variation BAに適合しています。

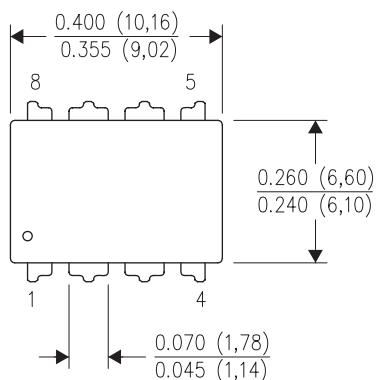

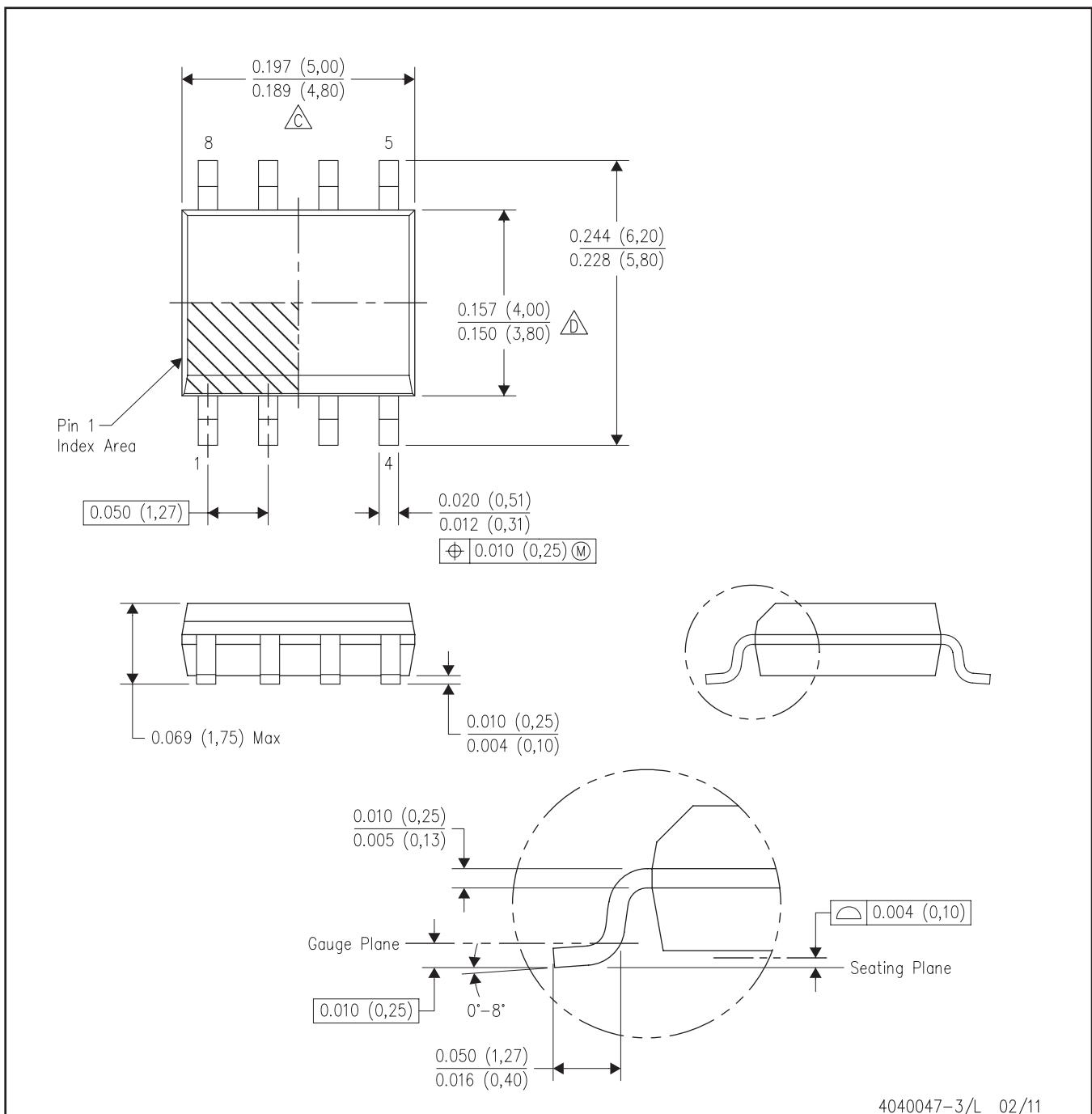

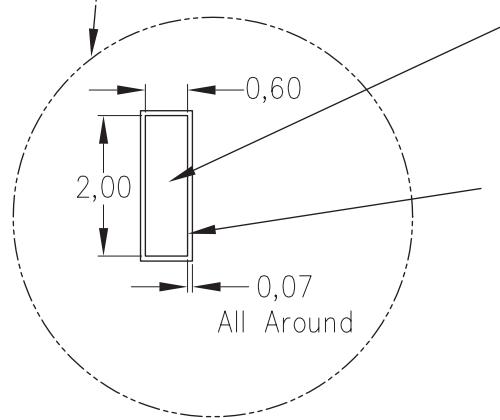

# メカニカル・データ

D(R-PDSO-G8)

PLASTIC SMALL OUTLINE

注: A. 全ての線寸法の単位はミリメートルです。寸法/公差はASME Y14.5M-1994によります。

B. 図は予告なく変更することがあります。

△ボディ寸法には、0.15mmを超えるモールド・フラッシュや突起は含まれません。

△ボディ幅には、インターリード・フラッシュは含まれません。インターリード・フラッシュは、片側で0.17(0.43mm)を超えることはありません。

E. JEDEC MS-012 バージョンAAに適合しています。

4040047-3/L 02/11

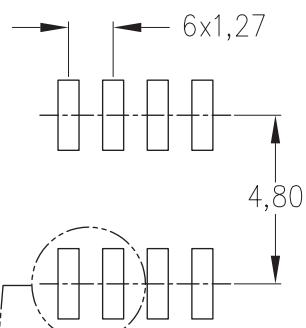

Example Board Layout

(Note C)Stencil Openings

(Note D)Example

Non Soldermask Defined PadExample

Pad Geometry

(See Note C)Example

Solder Mask Opening

(See Note E)

4211283-2/C 02/11

- 注: A. 全ての線寸法の単位はミリメートルです。

B. 図は予告なく変更することがあります。

C. 代替設計については、資料IPC-7351を推奨します。

D. レーザ切断開口部の壁面を台形にし、角に丸みを付けることで、ペーストの離れがよくなります。ステンシル設計要件については、基板組み立て拠点にお問い合わせください。例に示したステンシル設計は、50%容積のメタルロード半田ペーストに基づいています。ステンシルに関する他の推奨事項については、IPC-7525を参照してください。

E. 半田マスクの許容差については、基板組み立て拠点にお問い合わせください。

(SLUS888D)

**PACKAGING INFORMATION**

| Orderable part number      | Status<br>(1) | Material type<br>(2) | Package   Pins | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|----------------------------|---------------|----------------------|----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| <a href="#">UCC28610D</a>  | Active        | Production           | SOIC (D)   8   | 75   TUBE             | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 28610               |

| UCC28610D.A                | Active        | Production           | SOIC (D)   8   | 75   TUBE             | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 28610               |

| UCC28610D.B                | Active        | Production           | SOIC (D)   8   | 75   TUBE             | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 28610               |

| <a href="#">UCC28610DR</a> | Active        | Production           | SOIC (D)   8   | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 28610               |

| UCC28610DR.A               | Active        | Production           | SOIC (D)   8   | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 28610               |

| UCC28610DR.B               | Active        | Production           | SOIC (D)   8   | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 28610               |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月