**THP210** JAJSIK7C - JANUARY 2020 - REVISED MARCH 2021

# THP210 超低オフセット、高電圧、低ノイズ、高精度、 完全差動アンプ

# 1 特長

- 入力オフセット電圧:±40µV 以下

- 入力オフセット電圧ドリフト:0.35µV/℃以下

- 低消費電流:950µA (±18V の場合)

- 低入力バイアス電流:2nA 以下

- 低入力バイアス電流ドリフト:15pA/℃以下

- ゲイン帯域幅積:9.2MHz

- 差動出力スルーレート: 15V/µs

- 小さい入力電圧ノイズ:1kHz 時に 3.7nV/√Hz

- 優れた THD+N: 10kHz 時に -120dB

- 広い入出力同相範囲

- 幅広い単一電源動作範囲:3V~36V

- 低消費電流のパワーダウン機能:20µA 未満

- 過負荷電力制限

- 電流制限

- パッケージ:8ピン VSSOP、8ピン SOIC

- 温度範囲:-40℃~+125℃

# 2 アプリケーション

- データ・アクイジション (DAQ)

- アナログ入力モジュール

- サブステーション・オートメーション

- 半導体テスト

- 実験室およびフィールド用計測機器

# 3 概要

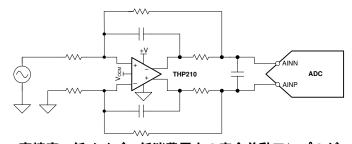

THP210 は、完全差動信号チェーンを簡単にフィルタお よび駆動できる超低オフセット、低ノイズ、高電圧、高精度 の完全差動アンプです。また THP210 は、シングルエンド の信号源を、高分解能アナログ / デジタル・コンバータ (ADC) が必要とする差動出力に変換するためにも使用さ れます。非常に優れたオフセット、低ノイズ、THD を実現 するように設計されたバイポーラ・スーパー・ベータ入力 は、非常に小さい静止電流と入力バイアス電流において 超低ノイズ指数を実現します。このデバイスは、優れた信 号対雑音比 (SNR) とともに小さな電力オフセットと消費電 力が必要とされる信号コンディショニング回路用に設計さ れています。

THP210 は高電圧電源に対応しており、電源電圧を最高 ±18V に上げることができます。この特性により、改善され たヘッドルームとダイナミック・レンジを活用して高電圧の 差動信号チェーンを実現できます。差動信号の極性ごと に個別のアンプを追加する必要はありません。THP210 は電圧および電流ノイズが非常に低いため、信号忠実度 への影響を最小限に抑えながら高ゲイン構成で使用でき ます。

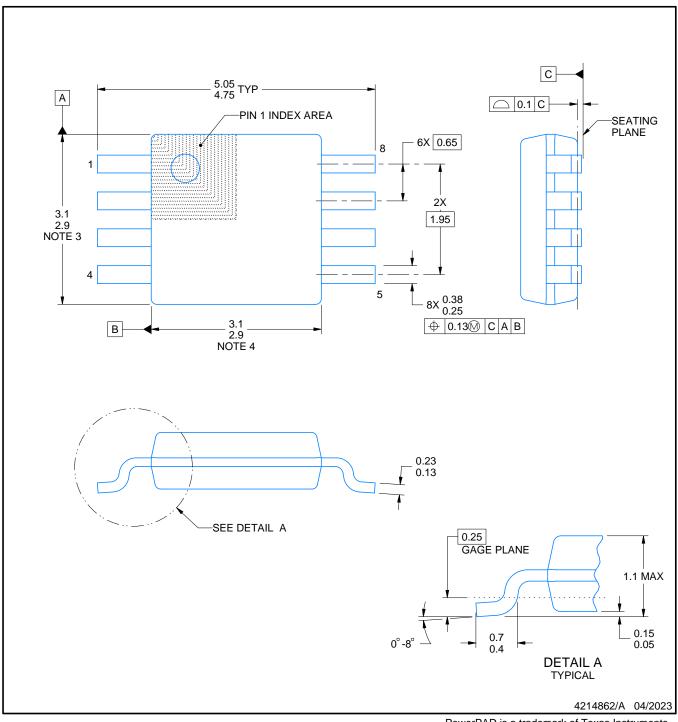

### 製品情報(1)

| 部品番号   | パッケージ     | 本体サイズ (公称)      |

|--------|-----------|-----------------|

| THP210 | VSSOP (8) | 3.00mm × 3.00mm |

| THEZIO | SOIC (8)  | 4.90mm × 3.91mm |

利用可能なすべてのパッケージについては、このデータシートの 末尾にあるパッケージ・オプションについての付録を参照してくだ

高精度、低ノイズ、低消費電力の完全差動アンプのゲ イン・ブロックとインターフェイス

小さな入力電圧オフセット

# **Table of Contents**

| 1 特長                                 | 1 | 8.4 Device Functional Modes                           | .18  |

|--------------------------------------|---|-------------------------------------------------------|------|

| 2 アプリケーション                           |   | 9 Application and Implementation                      | . 19 |

| 3 概要                                 |   | 9.1 Application Information                           | . 19 |

| 4 Revision History                   |   | 9.2 Typical Applications                              | . 27 |

| 5 Pin Configuration and Functions    |   | 10 Power Supply Recommendations                       | .32  |

| 6 Specifications                     |   | 11 Layout                                             | . 33 |

| 6.1 Absolute Maximum Ratings         |   | 11.1 Layout Guidelines                                | . 33 |

| 6.2 ESD Ratings                      |   | 11.2 Layout Example                                   | . 33 |

| 6.3 Recommended Operating Conditions |   | 12 Device and Documentation Support                   | .34  |

| 6.4 Thermal Information              |   | 12.1 Device Support                                   | . 34 |

| 6.5 Electrical Characteristics       |   | 12.2 Documentation Support                            | . 34 |

| 6.6 Typical Characteristics          |   | 12.3 Receiving Notification of Documentation Updates. | .34  |

| 7 Parameter Measurement Information  |   | 12.4 サポート・リソース                                        | . 34 |

| 7.1 Characterization Configuration   |   | 12.5 Trademarks                                       | .34  |

| 8 Detailed Description               |   | 12.6 静電気放電に関する注意事項                                    | . 34 |

| 8.1 Overview                         |   | 12.7 用語集                                              | . 34 |

| 8.2 Functional Block Diagram         |   | 13 Mechanical, Packaging, and Orderable               |      |

| 8.3 Feature Description              |   | Information                                           | . 34 |

| •                                    |   |                                                       |      |

# **4 Revision History**

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| С | hanges from Revision B (October 2020) to Revision C (March 2021)                                                                                                                                        | Page              |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| • | Changed PD pin description to clarify use of pin                                                                                                                                                        | 3                 |

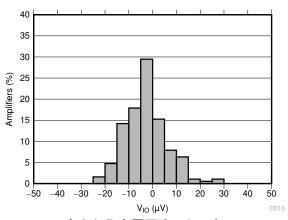

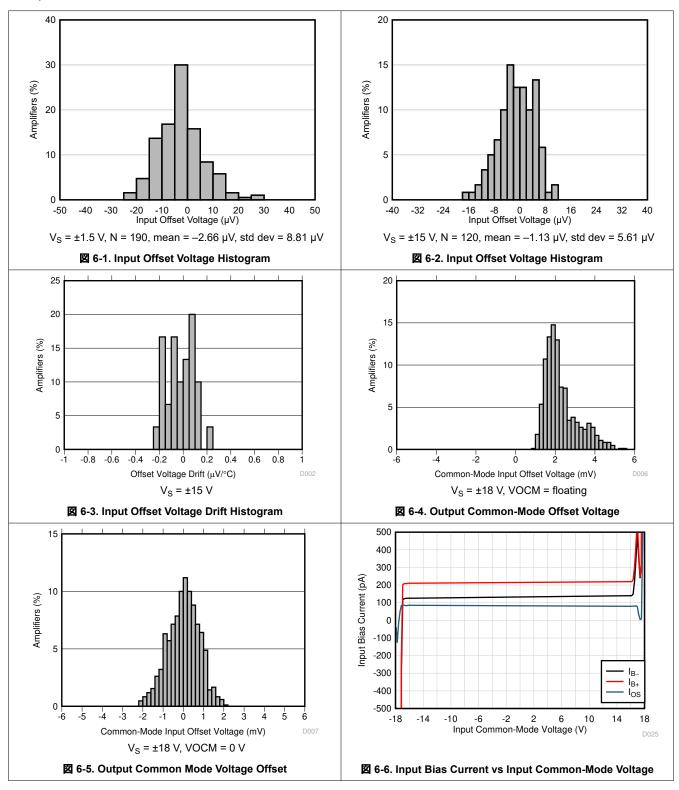

| • | Changed Figure 6-1, Input Offset Voltage Histogram                                                                                                                                                      |                   |

| • | Changed Figure 6-2, Input Offset Voltage Histogram                                                                                                                                                      | 8                 |

| • | Changed Figure 6-19, Output Impedance vs Frequency                                                                                                                                                      |                   |

| • | Changed Y-axis unit from nV/√HZ to V/√HZ for Figure 9-5, Calculated Noise Densities vs Gain Setting Changed Y-axis unit from nV/√HZ to V/√HZ for Figure 9-6, Calculated Noise Densities vs Gain Setting | s <mark>22</mark> |

| C | hanges from Revision A (May 2020) to Revision B (October 2020)                                                                                                                                          | Page              |

| • | 文書全体にわたって表、図、相互参照の採番方法を更新                                                                                                                                                                               | 1                 |

|   | D (SOIC-8) パッケージとそれに関連する項目を追加                                                                                                                                                                           |                   |

| • | Changed Figure 7-1, Differential Source to a Differential Gain of a 1-V/V Test Circuit, for clarity                                                                                                     |                   |

| • | Changed layout example circuit drawing for clarity                                                                                                                                                      |                   |

| C | hanges from Revision * (February 2020) to Revision A (May 2020)                                                                                                                                         | Page              |

| • | デバイスのステータスを事前情報 (プレビュー) から量産データ (アクティブ) に変更                                                                                                                                                             | 1                 |

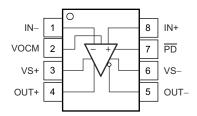

# **5 Pin Configuration and Functions**

図 5-1. D (SOIC-8) and DGK (VSSOP-8) Packages, Top View

# **Pin Functions**

| PIN  |     | 1/0 | DESCRIPTION                                                                                                                                                             |  |  |  |

|------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME | NO. | 1/0 | DESCRIPTION                                                                                                                                                             |  |  |  |

| IN-  | 1   | Į.  | Inverting (negative) amplifier input                                                                                                                                    |  |  |  |

| IN+  | 8   | I   | oninverting (positive) amplifier input                                                                                                                                  |  |  |  |

| OUT- | 5   | 0   | Inverting (negative) amplifier output                                                                                                                                   |  |  |  |

| OUT+ | 4   | 0   | Noninverting (positive) amplifier output                                                                                                                                |  |  |  |

| PD   | 7   | ı   | Power down.  PD = logic low = power off mode.  PD = logic high = normal operation.  The logic threshold is referenced to VS+.  If power down is not needed, pull up PD. |  |  |  |

| VOCM | 2   | ı   | Output common-mode voltage control input                                                                                                                                |  |  |  |

| VS-  | 6   | I   | Negative power-supply input                                                                                                                                             |  |  |  |

| VS+  | 3   | ı   | Positive power-supply input                                                                                                                                             |  |  |  |

# **6 Specifications**

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                  |                                               |                        |     | MIN                    | MAX                    | UNIT |

|------------------|-----------------------------------------------|------------------------|-----|------------------------|------------------------|------|

| V <sub>S</sub>   | Supply voltage                                | Single supply          |     |                        | 40                     | V    |

|                  | Supply voltage                                | Dual supply            |     |                        | ±20                    | V    |

|                  | IN+, IN-, differential voltage <sup>(2)</sup> |                        |     |                        | ±0.5                   | V    |

|                  | IN+, IN-, VOCM, PD, OUT+, OUT-                | voltage <sup>(3)</sup> |     | V <sub>VS-</sub> - 0.5 | V <sub>VS+</sub> + 0.5 | V    |

|                  | IN+, IN- current                              |                        | -10 | 10                     | mA                     |      |

|                  | OUT+, OUT- current                            |                        | -50 | 50                     | mA                     |      |

|                  | Output short-circuit <sup>(4)</sup>           |                        |     |                        | Continuous             |      |

| T <sub>A</sub>   | Operating temperature                         |                        |     | -40                    | 150                    | °C   |

| T <sub>J</sub>   | Junction temperature                          |                        |     | -40                    | 175                    | °C   |

| T <sub>stg</sub> | Storage temperature                           |                        |     | -65                    | 150                    | °C   |

- (1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) Input pins IN+ and IN- are connected with anti-parallel diodes in between the two terminals. Differential input signals that are greater than 0.5 V or less than -0.5 V must be current-limited to 10 mA or less.

- (3) Input terminals are diode-clamped to the supply rails (VS+, VS-). Input signals that swing more than 0.5 V greater or less the supply rails must be current-limited to 10 mA or less.

- (4) Short-circuit to V<sub>S</sub> / 2.

### 6.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

| V                  | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±1000 | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                               |                       |               | MIN  | NOM | MAX | UNIT |

|-------------------------------|-----------------------|---------------|------|-----|-----|------|

| V <sub>S</sub> Supply voltage | Supply voltage        | Single-supply | 3    |     | 36  | V    |

|                               | Supply voltage        | Dual-supply   | ±1.5 |     | ±18 | v    |

| T <sub>A</sub>                | Specified temperature |               | -40  |     | 125 | °C   |

Product Folder Links: THP210

# **6.4 Thermal Information**

|                       |                                              | THI      | THP210      |      |  |  |

|-----------------------|----------------------------------------------|----------|-------------|------|--|--|

|                       | THERMAL METRIC(1)                            | D (SOIC) | DGK (VSSOP) | UNIT |  |  |

|                       |                                              | 8 PINS   | 8 PINS      |      |  |  |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 129.1    | 181.1       | °C/W |  |  |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 69.4     | 68.3        | °C/W |  |  |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 72.5     | 102.8       | °C/W |  |  |

| ΨЈТ                   | Junction-to-top characterization parameter   | 20.7     | 10.6        | °C/W |  |  |

| ΨЈВ                   | Junction-to-board characterization parameter | 71.8     | 101.1       | °C/W |  |  |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | N/A      | N/A         | °C/W |  |  |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 6.5 Electrical Characteristics

at T<sub>A</sub> = 25°C, V<sub>S</sub> (dual supply) =  $\pm 1.5$  V to  $\pm 18$  V, V<sub>VOCM</sub> = V<sub>ICM</sub> = 0 V, R<sub>F</sub> = 2 k $\Omega$ , R<sub>L</sub> = 10 k $\Omega^{(1)}$ , gain = -1 V/V, V $\overline{PD}$  = V<sub>VS+</sub>, (unless otherwise noted)

|                 | PARAMETER                         | TEST CONDITIONS                                                                                | MIN                 | TYP    | MAX                  | UNIT               |

|-----------------|-----------------------------------|------------------------------------------------------------------------------------------------|---------------------|--------|----------------------|--------------------|

| OFFSET          | VOLTAGE                           |                                                                                                |                     |        |                      |                    |

| \/              | Input referred effect voltage     |                                                                                                |                     | 10     | ±40                  | \/                 |

| $V_{IO}$        | Input-referred offset voltage     | T <sub>A</sub> = -40°C to +125°C                                                               |                     |        | ±75                  | μV                 |

|                 | Input offset voltage drift        | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                                           |                     | 0.1    | ±0.35                | μV/°C              |

| PSRR            | Power-supply rejection ratio      |                                                                                                |                     | ±0.025 | ±0.25                | μV/V               |

| FORK            | Power-supply rejection ratio      | T <sub>A</sub> = -40°C to +125°C                                                               |                     |        | ±0.5                 | μν/ν               |

| INPUT B         | IAS CURRENT                       |                                                                                                |                     |        |                      |                    |

|                 | Input bias current                |                                                                                                |                     | ±0.2   | ±2                   | nA                 |

| l <sub>B</sub>  | input bias current                | T <sub>A</sub> = -40°C to +125°C                                                               |                     |        | ±4                   | ПА                 |

|                 | Input bias current drift          | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                                           |                     | ±2     | ±15                  | pA/°C              |

|                 | Input offset current              |                                                                                                |                     | ±0.2   | ±1                   | nA                 |

| I <sub>OS</sub> |                                   | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$                                                 |                     |        | ±3                   | IIA                |

|                 | Input offset current drift        | T <sub>A</sub> = -40°C to +125°C                                                               |                     | 1      | ±10                  | pA/°C              |

| NOISE           |                                   |                                                                                                |                     |        |                      |                    |

|                 |                                   | f = 1 kHz                                                                                      |                     | 3.7    |                      | nV/√ <del>Hz</del> |

| e <sub>n</sub>  | Input differential voltage noise  | f = 10 Hz                                                                                      |                     | 4      |                      | IIV/ VIIZ          |

|                 |                                   | f = 0.1 to 10 Hz                                                                               |                     | 0.1    |                      | $\mu V_{PP}$       |

|                 |                                   | f = 1 kHz                                                                                      |                     | 300    |                      | fA/√Hz             |

| ei              | Input current noise, each input   | f = 10 Hz                                                                                      |                     | 400    |                      | IAV VIIZ           |

|                 |                                   | f = 0.1 to 10 Hz                                                                               |                     | 13.4   |                      | pA <sub>PP</sub>   |

| INPUT V         | OLTAGE                            |                                                                                                |                     |        |                      |                    |

|                 | Common-mode voltage range         | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$                                                 | V <sub>VS</sub> -+1 |        | V <sub>VS+</sub> – 1 | V                  |

|                 |                                   | $V_{VS-} + 1 V \le V_{ICM} \le V_{VS+} - 1 V$                                                  |                     | 140    |                      |                    |

| CMRR            | Common-mode rejection ratio       | $V_{VS-} + 1 V \le V_{ICM} \le V_{VS+} - 1 V, V_S = \pm 18 V$                                  | 126                 | 140    |                      | dB                 |

| · · · · · ·     | Common-mode rejection ratio       | $V_{VS-} + 1 V \le V_{ICM} \le V_{VS+} - 1 V$ , $V_S = \pm 18 V$ , $T_A = -40$ °C to $+125$ °C | 120                 |        |                      |                    |

| INPUT IN        | MPEDANCE                          |                                                                                                |                     |        |                      |                    |

|                 | Input impedance differential mode | V <sub>ICM</sub> = 0 V                                                                         |                     | 1    1 |                      | GΩ    pF           |

# **6.5 Electrical Characteristics (continued)**

at  $T_A$  = 25°C,  $V_S$  (dual supply) = ±1.5 V to ±18 V,  $V_{VOCM}$  =  $V_{ICM}$  = 0 V,  $R_F$  = 2 k $\Omega$ ,  $R_L$  = 10 k $\Omega^{(1)}$ , gain = -1 V/V,  $V\overline{PD}$  =  $V_{VS+}$ , (unless otherwise noted)

|                   | PARAMETER                           | TEST CONDITIONS                                                                                                                          | MIN  | TYP  | MAX  | UNIT |

|-------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| OPEN-LC           | OOP GAIN                            |                                                                                                                                          |      |      |      |      |

|                   |                                     | $V_S = \pm 2.5 \text{ V}, V_{VS-} + 0.2 \text{ V} < V_O < V_{VS+} - 0.2 \text{ V}$                                                       | 115  | 120  |      |      |

|                   |                                     | $V_S = \pm 2.5 \text{ V}, V_{VS-} + 0.3 \text{ V} < V_O < V_{VS+} - 0.3 \text{ V},$ $T_A = -40^{\circ}\text{C to} + 125^{\circ}\text{C}$ | 110  | 120  |      |      |

| A <sub>OL</sub>   | Open-loop voltage gain              | $V_S = \pm 15 \text{ V}, V_{VS-} + 0.6 \text{ V} < V_O < V_{VS+} - 0.6 \text{ V}$                                                        | 115  | 120  |      | dB   |

|                   |                                     | V <sub>S</sub> = ±15 V, V <sub>VS-</sub> + 0.6 V < V <sub>O</sub> < V <sub>VS+</sub> - 0.6 V,<br>T <sub>A</sub> = -40°C to +125°C        | 110  | 120  |      |      |

| FREQUE            | NCY RESPONSE                        |                                                                                                                                          |      |      |      |      |

| SSBW              | Small-signal bandwidth              | V <sub>O</sub> = 100 mV <sub>PP</sub>                                                                                                    |      | 7    |      | MHz  |

| GBP               | Gain-bandwidth product              | V <sub>O</sub> = 100 mV <sub>PP</sub> , gain = -10 V/V                                                                                   | ,    | 9.2  |      | MHz  |

| FBP               | Full-power bandwidth                | V <sub>O</sub> = 1 V <sub>PP</sub>                                                                                                       |      | 2.4  |      | MHz  |

| SR                | Slew rate                           | 10-V step                                                                                                                                |      | 15   |      | V/µs |

|                   | 0.40                                | To 0.1% of final value, V <sub>O</sub> = 10-V step                                                                                       | ,    | 1    |      |      |

|                   | Settling time                       | To 0.01% of final value, V <sub>O</sub> = 10-V step                                                                                      | ,    | 1.2  |      | μs   |

| THD+N             | Total harmonic distortion and noise | Differential input, f = 1 kHz, V <sub>O</sub> = 10 V <sub>PP</sub>                                                                       |      | -120 | -120 |      |

| THD+N             | Total harmonic distortion and noise | Single-ended input, f = 1 kHz, V <sub>O</sub> = 10 V <sub>PP</sub>                                                                       |      | -115 |      |      |

| THD+N             | Total harmonic distortion and noise | Differential input, f = 10 kHz, V <sub>O</sub> = 10 V <sub>PP</sub>                                                                      |      | -112 |      |      |

|                   | Total harmonic distortion and noise | Single-ended input, f = 10 kHz, V <sub>O</sub> = 10 V <sub>PP</sub>                                                                      | -107 |      |      | dB   |

| HD2               | Second-order harmonic               | Differential input, f = 1 kHz, V <sub>O</sub> = 10 V <sub>PP</sub>                                                                       |      | -120 |      |      |

| пи2               | distortion                          | Single-ended input, f = 1 kHz, V <sub>O</sub> = 10 V <sub>PP</sub>                                                                       |      | -126 |      |      |

| HD3               | Third and a harmanic distantion     | Differential input, f = 1 kHz, V <sub>O</sub> = 10 V <sub>PP</sub>                                                                       |      | -120 |      |      |

| 1103              | Third-order harmonic distortion     | Single-ended input, f = 1 kHz, V <sub>O</sub> = 10 V <sub>PP</sub>                                                                       |      | -119 |      |      |

|                   | Overdrive recovery time             | gain = -5 V/V, 2x output overdrive, dc-coupled                                                                                           | ,    | 3.3  |      | μs   |

| Z <sub>O</sub>    | Open-loop output impedance          | f = 100 kHz (differential)                                                                                                               |      | 14   |      | Ω    |

| C <sub>LOAD</sub> | Capacitive load drive               | Differential capacitive load, no output isolation resistors, phase margin = 30°                                                          |      | 50   |      | pF   |

| OUTPUT            |                                     |                                                                                                                                          |      |      |      |      |

|                   |                                     | V <sub>S</sub> = ±2.5 V                                                                                                                  |      | 100  |      |      |

| V                 | Negative output voltage swing       | $V_S = \pm 2.5 \text{ V}, T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                                                            |      | 100  |      |      |

| V <sub>OL</sub>   | from rail                           | V <sub>S</sub> = ±18 V                                                                                                                   | ,    | 230  |      |      |

|                   |                                     | $V_S = \pm 18 \text{ V}, T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                                                             |      | 270  |      | mV   |

|                   |                                     | $V_S = \pm 2.5 \text{ V}$                                                                                                                |      | 100  |      | 1117 |

| V                 | Positive output voltage swing       | $V_S = \pm 2.5 \text{ V}, T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                                                            |      | 100  |      |      |

| V <sub>OH</sub>   | from rail                           | V <sub>S</sub> = ±18 V                                                                                                                   |      | 230  |      |      |

|                   |                                     | $V_S = \pm 18 \text{ V}, T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                                                             |      | 270  |      |      |

| I <sub>SC</sub>   | Short-circuit current               |                                                                                                                                          |      | ±31  |      | mA   |

# **6.5 Electrical Characteristics (continued)**

at T<sub>A</sub> = 25°C, V<sub>S</sub> (dual supply) =  $\pm 1.5$  V to  $\pm 18$  V, V<sub>VOCM</sub> = V<sub>ICM</sub> = 0 V, R<sub>F</sub> = 2 k $\Omega$ , R<sub>L</sub> = 10 k $\Omega^{(1)}$ , gain = -1 V/V, VPD = V<sub>VS+</sub>, (unless otherwise noted)

|                      | PARAMETER                            | TEST CONDITIONS                                                               | MIN                    | TYP      | MAX                    | UNIT     |  |

|----------------------|--------------------------------------|-------------------------------------------------------------------------------|------------------------|----------|------------------------|----------|--|

| OUTPUT               | COMMON-MODE VOLTAGE                  |                                                                               |                        |          |                        |          |  |

|                      | Small-signal bandwidth from VOCM pin | V <sub>VOCM</sub> = 100 mV <sub>PP</sub>                                      |                        | 2        |                        | MHz      |  |

|                      | Large-signal bandwidth from VOCM pin | V <sub>VOCM</sub> = 0.6 V <sub>PP</sub>                                       |                        | 5.7      |                        | IVITZ    |  |

|                      | Claurate from VOCM nin               | V <sub>VOCM</sub> = 0.5-V step, rising                                        |                        | 4.2      |                        | 1////    |  |

|                      | Slew rate from VOCM pin              | V <sub>VOCM</sub> = 0.5-V step, falling                                       |                        | 5.5      |                        | V/µs     |  |

|                      | DC output balance                    | V <sub>VOCM</sub> fixed midsupply (V <sub>O</sub> = ±1 V)                     |                        | 78       |                        | dB       |  |

|                      | VOCM Input valtage renge             | V <sub>S</sub> = ±2.5 V                                                       | V <sub>VS-</sub> + 1   |          | V <sub>VS+</sub> – 1   | V        |  |

|                      | VOCM Input voltage range             | V <sub>S</sub> = ±18 V                                                        | V <sub>VS</sub> _ + 2  |          | V <sub>VS+</sub> – 2   | V        |  |

|                      | VOCM input impedance                 |                                                                               |                        | 2.5    1 |                        | MΩ    pF |  |

|                      | VOCM offset from mid-supply          | V <sub>VOCM</sub> pin floating, V <sub>O</sub> = V <sub>ICM</sub> = 0 V       |                        | ±1       |                        |          |  |

|                      | VOCM common-mode offset              | V <sub>VOCM</sub> = V <sub>ICM</sub> , V <sub>O</sub> = 0 V                   |                        | ±1       | ±6                     | mV       |  |

|                      | voltage                              | $V_{VOCM} = V_{ICM}, V_O = 0 V, T_A = -40^{\circ}C \text{ to } +125^{\circ}C$ |                        |          | ±10                    |          |  |

|                      | VOCMcommon-mode offset voltage drift | $V_{VOCM} = V_{ICM}, V_O = 0 V, T_A = -40^{\circ}C \text{ to } +125^{\circ}C$ |                        | ±20      | ±60                    | μV/°C    |  |

| POWER S              | SUPPLY                               | 1                                                                             |                        |          |                        |          |  |

|                      | 0                                    |                                                                               |                        | 0.95     | 1.05                   |          |  |

| IQ                   | Quiescent operating current          | T <sub>A</sub> = -40°C to +125°C                                              |                        | -        | 1.4                    | mA       |  |

| POWER D              | OOWN                                 |                                                                               |                        |          |                        |          |  |

| V <sub>PD(HI)</sub>  | Power-down enable voltage            | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$                                | V <sub>VS+</sub> - 0.5 |          |                        | .,       |  |

| V <sub>PD(LOW)</sub> | Power-down disable voltage           | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$                                |                        |          | V <sub>VS+</sub> – 2.0 | V        |  |

|                      | PD bias current                      | V <sub>PD</sub> = V <sub>VS+</sub> - 2 V                                      |                        | 1        | 2                      | μΑ       |  |

|                      | Powerdown quiescent current          |                                                                               |                        | 10       | 20                     | μA       |  |

|                      | Turn-on time delay                   | $V_{IN}$ = 100 mV, Time to $V_{O}$ = 90% of final value                       |                        | 10       |                        |          |  |

|                      | Turn-off time delay                  | $V_{IN}$ = 100 mV, Time to $V_{O}$ = 10% of original value                    |                        | 15       |                        | μs       |  |

<sup>(1)</sup> R<sub>L</sub> is connected differentially, from OUT+ to OUT-.

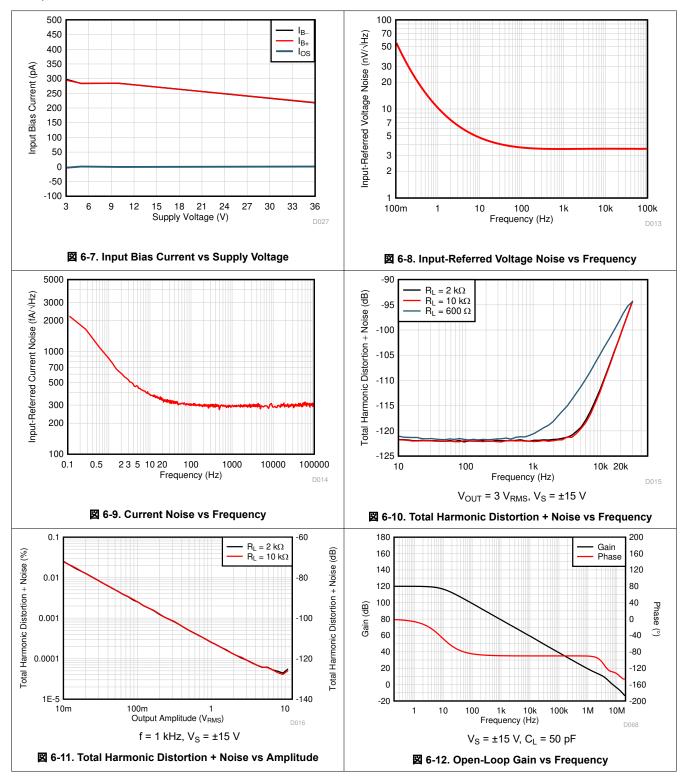

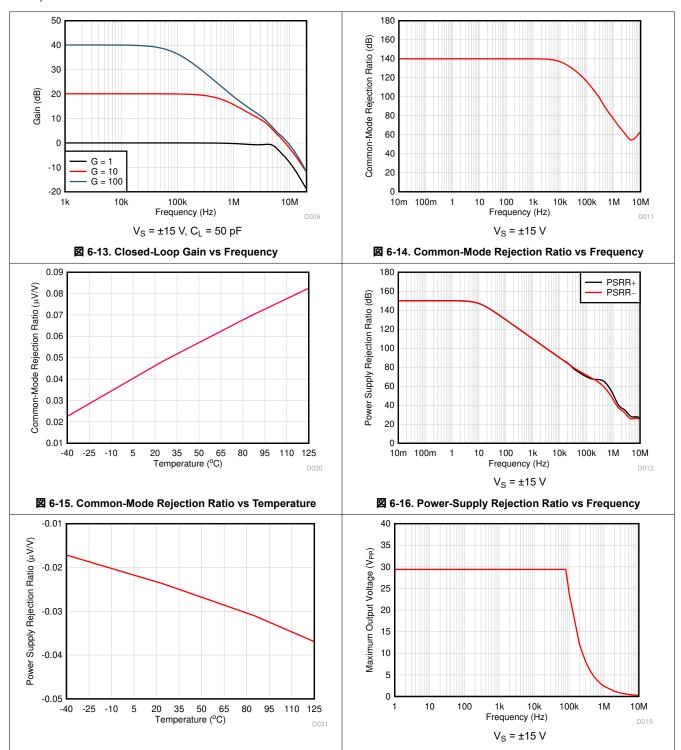

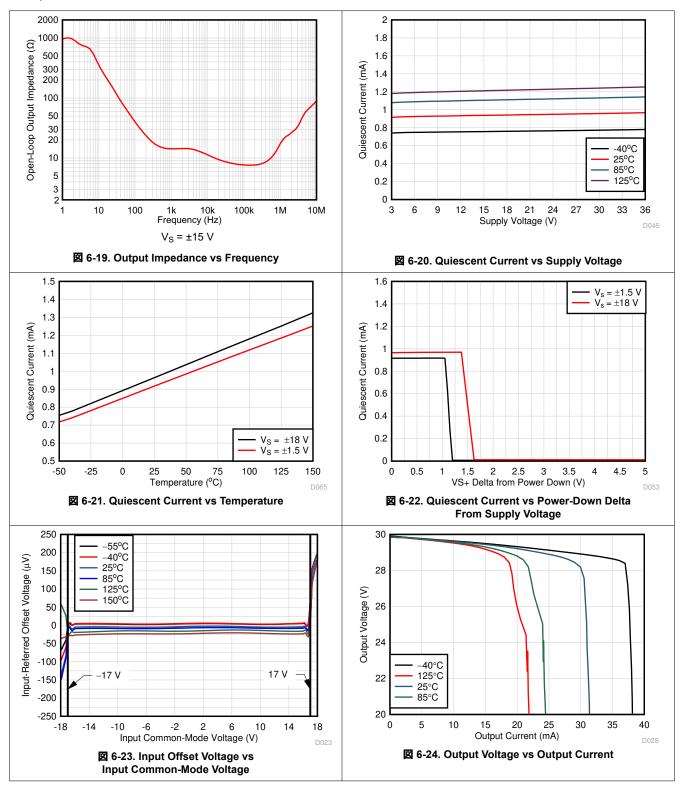

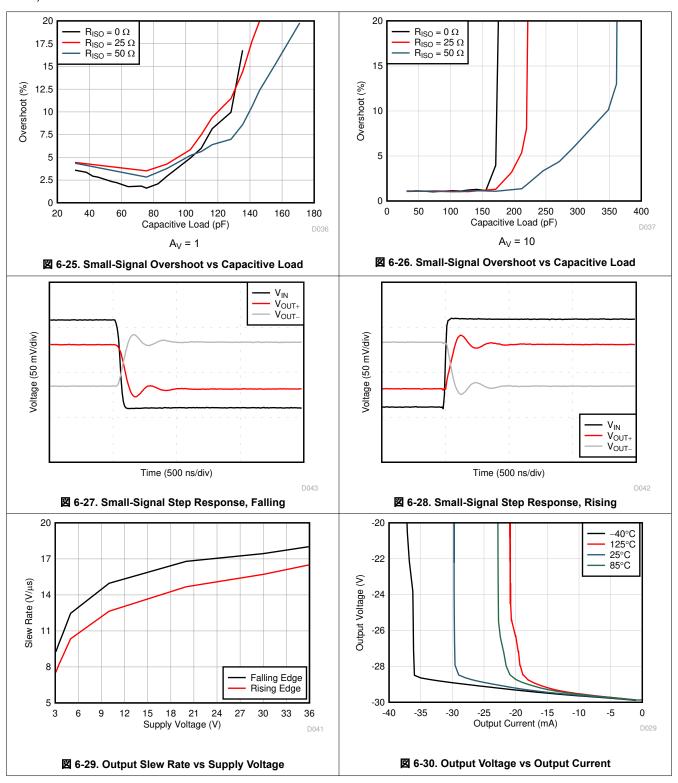

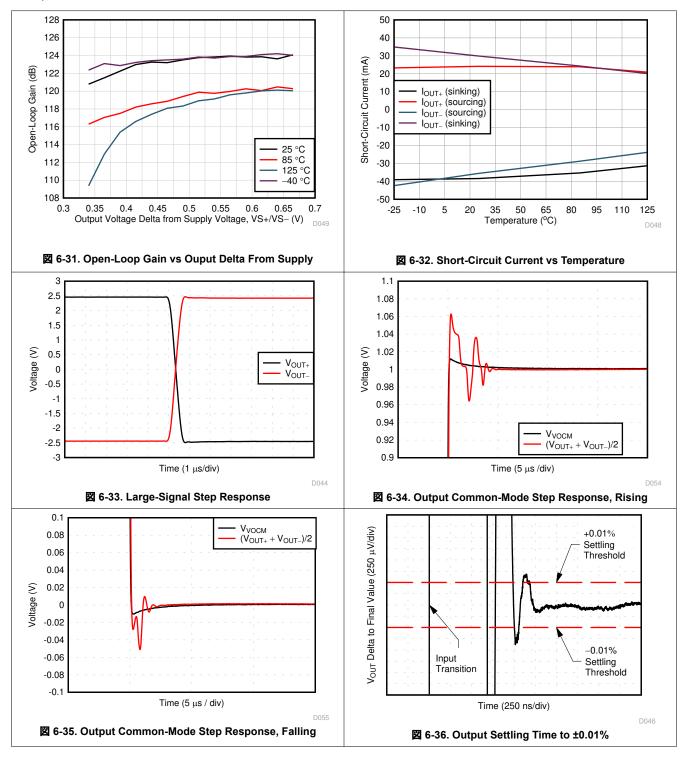

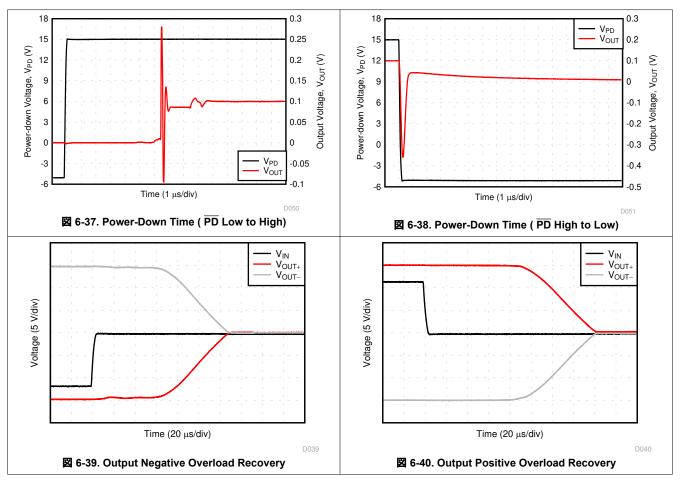

# 6.6 Typical Characteristics

at  $V_{VS}$  = ±15 V,  $T_A$  = 25°C,  $V_{VOCM}$  =  $V_{VICM}$  = 0 V,  $R_F$  = 2 k $\Omega$ ,  $R_L$  = 10 k $\Omega$ , gain = -1 V/V, and  $V_{\overline{PD}}$  =  $V_{VS+}$  (unless otherwise noted)

図 6-17. Power-Supply Rejection Ratio vs Temperature

☑ 6-18. Maximum Output Voltage vs Frequency

# 7 Parameter Measurement Information

# 7.1 Characterization Configuration

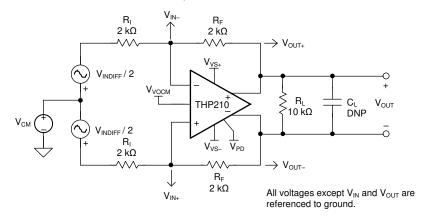

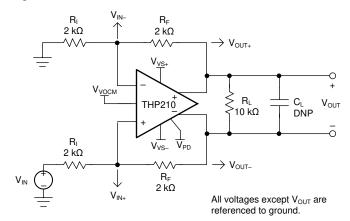

The THP210 is a fully differential amplifier (FDA) configuration that offers high dc precision, very low noise and harmonic distortion in a single, low-power amplifier. The FDA is a flexible device where the main aim is to provide a purely differential output signal centered on a user-configurable, common-mode voltage that is usually matched to the input common-mode voltage required by an analog-to-digital converter (ADC). The circuit used for characterization of the differential-to-differential performance is seen in  $\boxtimes$  7-1

図 7-1. Differential Source to a Differential Gain of a 1-V/V Test Circuit

A similar circuit is used for single-ended to differential measurements, as shown in Z 7-2.

☑ 7-2. Single-ended Source to Differential Gain of 1-V/V Test Circuit

The characterization plots fix the  $R_F$  ( $R_{F1}$  =  $R_{F2}$ ) value at 2 k $\Omega$ , unless otherwise noted. This value can be adjusted to match the system design parameters with the following considerations in mind:

- The current required to drive RF from the peak output voltage to the input common-mode voltage add to the

overall output load current. If the total current (current through R<sub>F</sub> + current through R<sub>L</sub>) exceeds the current

limit conditions, the device enters a current limit, causing the output voltage to collapse.

- High feedback resistor values (R<sub>F</sub> > 100 kΩ) interact with the amplifier input capacitance to create a zero in the feedback network. Compensation must be added to account for potential source of instability; see the TI Precision Labs FDA Stability Training for guidance on designing an appropriate compensation network.

# 8 Detailed Description

### 8.1 Overview

The THP210 is a low-noise, low-distortion fully-differential amplifier (FDA) that features Texas Instrument's super-beta bipolar input devices. Super-beta input devices feature very low input bias current as compared to standard bipolar technology. The low input bias current and current noise makes the THP210 an excellent choice for high-performance applications that require low-noise, differential-signal processing without significant current consumption. This device is also designed for analog-to-digital input circuits that require low offset and low noise in a single fully-differential amplifier. The THP210 features high-voltage capability, which allows the device to be used in ±15-V supply circuits without any additional voltage clamping or regulators. Because this device is unity-gain stable, the device allows high-voltage input signals to be attenuated to the low-voltage ADC domain without requiring additional compensation techniques.

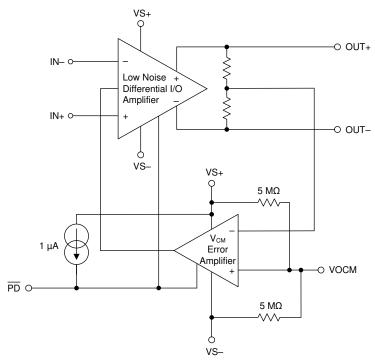

### 8.2 Functional Block Diagram

#### 8.3 Feature Description

### 8.3.1 Super-Beta Input Bipolar Transistors

The THP210 is designed on a modern bipolar process that features TI's super-beta input transistors. Traditional bipolar transistors feature excellent voltage noise and offset drift, but suffer a tradeoff in high input bias current (I<sub>B</sub>) and high input bias current noise. Super-beta transistors offer the benefits of low voltage noise and low offset drift with an order of magnitude reduction in input bias current and reduction in input bias current noise. For many filter circuits, input bias current noise can dominate in circuits where higher resistance input resistors are used. The THP210 enables a fully-differential, low-noise amplifier design without restrictions of low input resistance at a power level unmatched by traditional single-ended amplifiers.

#### 8.3.2 Power Down

The THP210 features a power-down circuit to disable the amplifier when a low-power mode is required by the system. In the power-down state, the amplifier outputs are in a high-impedance state, and the amplifier total quiescent current is reduced to less than 20  $\mu$ A.

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

#### 8.3.3 Flexible Gain Setting

The THP210 offers considerable flexibility in the configuration and selection of resistor values. Low input bias current and bias current noise allows for larger gain resistor values with minimal impact to noise or offset, see セクション 9.1.3 for more details.

The design starts with the selection of the feedback resistor value. The  $2-k\Omega$  feedback resistor value used for the characterization curves is a good compromise among power, noise, and phase margin considerations. With the feedback resistor values selected (and set equal on each side), the input resistors are set to obtain the desired gain, with input impedance also set with these input resistors. Differential I/O designs provide an input impedance that is the sum of the two input resistors. Single-ended input to differential output designs present a more complicated input impedance. Most characteristic curves implement the single-ended to differential design as the more challenging requirement over differential-to-differential I/O designs.

### 8.3.4 Amplifier Overload Power Limit

During overload or fault conditions, many bipolar-based amplifiers draw significant (three to five times) quiescent current if the output voltage is clipped (meaning the output voltage becomes limited by the negative or positive supply rail).

The primary cause for this condition is that common-emitter output stages can consume excessive base current (up to 100x) when overdriven into saturation. In addition, the overload condition causes the feedback to be broken, which causes the slew boost to be permanently on. Depending on the slew boost circuit, this increases the tail current up to 4x.

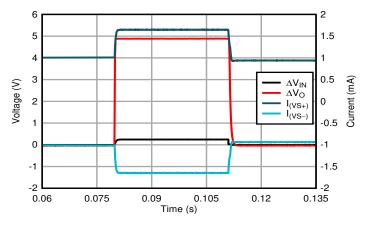

The THP210 has an intelligent overload detection scheme that eliminates this problem, meaning that there is virtually no additional current consumption in the case of an overload event, represented in  $\boxtimes$  8-1. The protection circuit continuously monitors both the input and output stages of the amplifier.  $\boxtimes$  8-1 shows a measurements of the overload power limit behavior. If a large input voltage step (referred to as  $\Delta V_{IN}$ ) is detected, the protection circuit checks for the presence of a rapid change in the voltage at the output (referred to as  $\Delta V_O$ ). If the output is not changing because the output is clipped at supply rail, the protection circuit disables the slew-boost circuit and limit the base current of the predriver to prevent output saturation. After the overload condition is removed, the amplifier rapidly recovers to normal operating condition.  $\boxtimes$  8-1 indicates that in case of an overloaded output the current consumption at the supply pins (referred to  $I_{(VS+)}$  and  $I_{(VS-)}$ ) does not exceed the limitations, and quickly recovers as soon as the overload condition has been removed.

図 8-1. Supply Current Change With Overloaded Outputs

#### 8.3.5 Unity Gain Stability

The stability of the amplifiers is of key importance when designing application circuits with fully differential amplifiers. This stability becomes especially important when driving capacitive loads, such as the input for successive-approximation-register (SAR) analog-to-digital converters (ADCs). A trade-off is made between the bandwidth of an amplifier and keeping power consumption low; in many cases, FDAs are not unity gain stable. Currently, many FDAs are primarily designed to support high-speed ADCs, and thus, are typically decompensated. This decompensation comes with the drawback that the noise performance degrades because of noise gain peaking. Additional components and compensation techniques are required to handle these challenges and prevent potential instability of the FDA. For detailed analysis of how stability is defined and affected, see TI Precision Labs – Fully Differential Amplifiers – FDA Stability and Simulating Phase Margin.

The THP210 is unity-gain stable; therefore, this device can be used in gain configurations with gains > 1, and also in attenuating configurations with gains < 1, without requiring compensation techniques and sacrificing dynamic performance. This device can be of prime use for applications that need to interface large input signals to the low-voltage ADC domain.

#### 8.4 Device Functional Modes

The THP210 has two functional modes: normal operation and power-down. The power-down state is enabled when the voltage on the power-down pin is lowered to less than the power-down threshold. In the power-down state, the quiescent current is significantly reduced, and the output voltage is high-impedance. This high impedance can lead to the input voltages (VIN+ and VIN-) separating.

Internal ESD protection diodes remain present across the input pins in both operating and power-down mode. Large input signals during disable can forward-biasing the ESD protection diodes, thus producing a load current in the supply, even in power-down. See セクション 9.1.5 for guidance on power-down operation.

The VOCM control pin sets the output average voltage. If left open, VOCM defaults to an internal midsupply value. Driving this high-impedance input with a voltage reference within the valid range sets a target for the internal  $V_{CM}$  error amplifier. If floated to obtain a default midsupply reference for VOCM, an external decoupling capacitor must be added on the VOCM pin to reduce the otherwise high output noise for the internal high-impedance bias.

# 9 Application and Implementation

#### Note

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes, as well as validating and testing their design implementation to confirm system functionality.

### 9.1 Application Information

Most applications for the THP210 strive to deliver the best dynamic range in a design that delivers the desired signal processing along with adequate phase margin for the amplifier. The following sections detail some of the design issues with analysis, and guidelines for improved performance.

#### 9.1.1 I/O Headroom Considerations

The starting point for most designs is to assign an output common-mode voltage for the THP210. For ac-coupled signal paths, this voltage is often the default midsupply voltage to retain the most available output swing around the voltage centered at the  $V_{OCM}$  voltage. For dc-coupled signal paths, set this voltage to minimum of  $V_{VS\pm}$  ±2 V at  $V_S$  = ± 18 V and  $V_{VS\pm}$  ±1 V at  $V_S$  = ± 2.5 V respectively. For precision ADC drivers, this output becomes the input common mode voltage of the ADC.

From the target output  $V_{OCM}$ , the next step is to verify that the desired output differential peak-to-peak voltage  $(V_{OPP})$  stays within the supplies. For any desired differential  $V_{OPP}$ , make sure that the absolute maximum voltage at the output pins swings with  $\pm$  1 and  $\pm$  2 and confirm that these expressions are within the supply rails minus the output headroom required for the RRO device.

$$V_{Omax} = V_{OCM} + \frac{V_{OPP}}{2}$$

(1)

$$V_{Omin} = V_{OCM} - \frac{V_{OPP}}{2}$$

(2)

Most designs do not run into an input range limit. However, using the approach shown in this section can allow a quick assessment of the input V<sub>ICM</sub> range under the intended full-scale output condition. The TINA-TI™ simulation software can be used to plot the input voltages under the intended swings and application circuit to verify that there is no limiting from this effect. Increasing the positive and negative supplies slightly in simulation is an easy way to discover the simulated swings that might be going out of range.

#### 9.1.2 DC Precision Analysis

#### 9.1.2.1 DC Error Voltage at Room Temperature

Good dc linearity allows the designer to minimize the total dc output error of the system. In particular, this error divides into two contributions: the initial error at the normal operating condition of 25°C, and the drift error over temperature. The main sources of these errors typically arise from:

- Voltage error due to the input offset voltage (V<sub>IO</sub>)

- Voltage error due to noninverting and inverting bias current (I<sub>B-</sub>, I<sub>B+</sub>)

- The common-mode rejection ratio (CMRR) of the FDA

- Voltage error due to mismatch between input and output common-mode voltages (V<sub>VOCM</sub> V<sub>ICM</sub>)

One major source of error comes from the effect of mismatched resistor values and the ratios on the two sides of the FDA. For this analysis, this error term is neglected. The effects are described separately in 2/23/9.1.4.

Copyright © 2021 Texas Instruments Incorporated

Submit Document Feedback

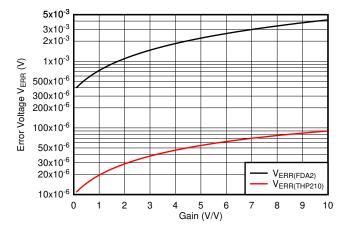

The THP210 super-beta input device features extremely-low input bias current, trimmed low input offset voltage, and the lowest offset drift over the full temperature operating range. These features allow the device to produce a negligible initial error band at 25°C, but also exceptional robust behavior over temperature. The red curve in  $\boxtimes$  9-1 showcases a simulation of the total dc error voltage at 25°C versus different gain configurations based on the application configuration shown in  $\boxtimes$  9-2.

図 9-1. TINA-TI™ Software Simulation of DC Error Voltage at Different Gain Settings (Variable R<sub>2</sub>)

図 9-2. FDA DC Error Model

One use case at a differential input voltage of  $V_{ID}$  = 200 mV and a gain of 5 V/V (that corresponds to  $R_2$  = 5 k $\Omega$ ) reveals that the initial dc error of the THP210 is 4.5  $\mu$ V. A comparable FDA2 with  $V_{IO}$  = 200  $\mu$ V,  $I_B$  = 650 nA, and  $I_{IO}$  = 30 nA results in a 2.22-mV dc error voltage that results in a factor of approximately 500 higher dc error.

In addition,  $\boxtimes$  9-3 shows that the absolute dc accuracy of the THP210 nearly adds an error voltage on the system. The dominant factors for the initial error band are mainly due to the feedback resistor mismatch that is not considered in the simulation plot.

# 9.1.2.2 DC Error Voltage Over Temperature

The THP210 offers excellent dc accuracy at room temperature. In many applications, calibration techniques are used to minimize the initial dc error; however, performing calibration over temperature is time-consuming and expensive.

The advanced drift specification of the THP210 helps to further mitigate the system error over temperature.

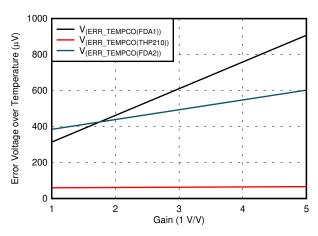

9-3 depicts the total error voltage at these given conditions:

- Temperature range from –40°C to +125°C

- Resistor tolerance of 1%

図 9-3. Calculation of Error Voltage Over Temperature at Different Gain Settings (Variable R<sub>2</sub>)

The main contributors that are considered in this analysis are offset voltage drift, offset current drift, and bias current drift. As a result of the ultra-low bias current drift of 15 pA/°C, the impact of higher gain resistors and resistor tolerances marginally affects the error voltage with the THP210.

A use case at a gain of 5 V/V shows that the total dc error over temperature of the THP210 is at 66  $\mu$ V, which is at least a factor of 10 smaller compared to existing, state-of-the-art FDAs.

#### 9.1.3 Noise Analysis

An accurate output-noise calculation allows the designer to compare the performance of alternate FDA solutions. The combination of differential spot noise at the output pins of the FDA with any passive filtering to the ADC enables an accurate signal-to-noise ratio (SNR) calculation. This chapter incorporates key elements for an output noise analysis.

The first step in the output noise analysis is to reduce the application circuit to the simplest form with equal feedback and gain setting elements to ground.

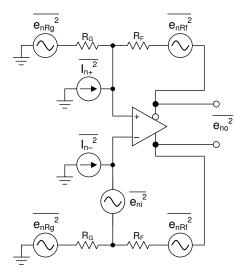

9-4 shows the simplest analysis circuit with the FDA. This circuit considers the thermal resistor noise terms of the external feedback network and the intrinsic input voltage and current noise terms.

図 9-4. FDA Noise Analysis Circuit

The noise powers are shown in  $\boxtimes$  9-4 for each term. When the R<sub>F</sub> and R<sub>G</sub> (or R<sub>I</sub>) terms are matched on each side, the total differential output noise is the root sum squared (RSS) of these separate terms.

Using NG  $\equiv$  1 + R<sub>F</sub> / R<sub>G</sub> as the noise gain, the total output noise density is given by  $\not\equiv$  3. Each resistor noise term is a 4kT × R power (4kT = 1.6E-20 J at 290 K).

$$e_o = \sqrt{(e_{ni}NG)^2 + 2(i_NR_F)^2 + 2(4kTR_FNG)}$$

(3)

where:

- e<sub>ni</sub> is the differential input spot noise times the noise gain.

- i<sub>n</sub> x R<sub>F</sub> is the input current noise terms times the feedback resistor.

Because there are two uncorrelated current noise terms, the power is two times one of them.

- e<sub>nRF</sub> is the thermal output noise resulting from both the R<sub>F</sub> and R<sub>G</sub> resistors at twice the value for the output noise power of each side added together.

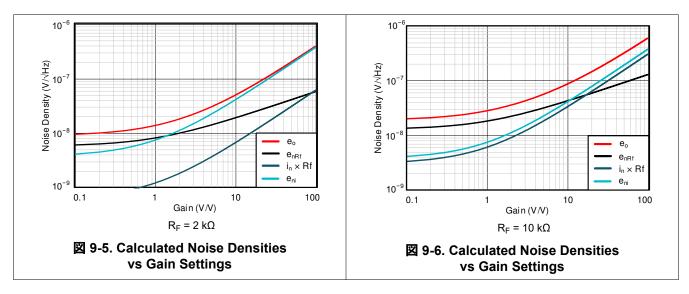

$\boxtimes$  9-5 and  $\boxtimes$  9-6 provide a graphical comparison of the described noise densities versus different gain settings. Each of the contributors are separately showcased in the graphs. As expected, lower feedback resistors (in this case, 2 k $\Omega$ ) show that the dominant factor of the total output noise is the intrinsic voltage noise of the FDA (at gains > 2). For smaller gain settings, the thermal noise of the feedback resistors is dominating.

The advancement of the THP210 can be seen at higher feedback resistors (in this case 10 k $\Omega$ ). Many FDAs exhibit an input current noise density in the range of some pA/ $\sqrt{\text{Hz}}$  that, in cases for higher feedback resistors, dictate the noise behavior. As a result of the superior current noise density of 300 fA/ $\sqrt{\text{Hz}}$  of the THP210, the overall output noise is mainly dominated by the thermal noise of the resistors (here, up to gains of approximately 15).

The total output voltage noise density is important when using FDAs as ADC input driver stages. To evaluate the compatibility between the input driver and the ADC from a noise perspective, compare the calculated RMS output noise of the FDA with the least-significant bit (LSB) of the desired ADC application, in respect to the effective number of bits (ENOB). \*\*\textsup 2.2.2\*\* shows measurements of the THP210 in combination with state-of-the-art SAR ADCs, and indicates the performance that is achieved.

#### 9.1.4 Mismatch of External Feedback Network

The common-mode rejection ratio (CMRR) is one of the key elements when designing with fully differential amplifiers. Although FDAs are designed to provide the best CMRR performance, poor selection of external gain setting resistors, as well as careless board layout techniques, significantly degrade CMRR performance.

In an ideal world, the resistors in a typical circuit, as shown in the test circuit  $\boxtimes$  7-1, are chosen to be  $R_{F1}$  /  $R_{F2}$  =  $R_{I1}/R_{I2}$ . Mismatch between these ratios causes the differential output to depend on the input common-mode voltage ( $V_{VOCM}$ ), and that in turn produces an offset and excess noise on the differential output. As mentioned in the previous section, the mismatch of the external resistor network primarily contributes to the dc error. Generally, a resistor mismatch of 0.1% and a ratio of 1 V/V results in a CMRR of 60 dB. The natural degradation of the external resistor network is minimized by the following guidelines:

- Consider input impedance matching, as shown in the *Input impedance matching with fully differential amplifiers* technical brief.

- Follow layout guidelines, as provided in セクション 11.1.

- Use compensation techniques, as described in the Improving PSRR and CMRR in Fully Differential Amplifiers application report

Despite the mismatch of the external feedback network, the internal common-mode feedback amplifier regulates the outputs to remain balanced in amplitude and remain 180° out of phase. The output balance performance stays unaffected by the CMRR degradation.

Copyright © 2021 Texas Instruments Incorporated

Submit Document Feedback

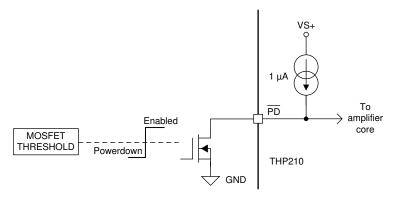

#### 9.1.5 Operating the Power-Down Feature

The power-down feature on the THP210 puts the device into a low power-consumption state, with quiescent current minimized. To force the device into the low-power state, drive the  $\overline{PD}$  pin lower than the power-down threshold voltage ( $V_{VS+}-2$  V). Driving the  $\overline{PD}$  pin lower than the power-down threshold voltage forces the internal logic to disable both the differential and common-mode amplifiers. The PD pin has an internal pullup current that allows the pin to be used in an open-drain MOSFET configuration without an additional pullup resistor, as seen in  $\boxtimes$  9-7. In this configuration, the logic level can be referenced to the MOSFET, and the voltage at the  $\overline{PD}$  pin is level-shifted to account for use with high supply voltages. Be sure to select an N-type MOSFET with a maximum  $B_{VDSS}$  greater than the total supply voltage.

図 9-7. Power-Down (PD) Pin Interface With Low-Voltage Logic Level Signals

For applications that do not use the power-down feature, tie the PD pin to the positive supply voltage.

When PD is low (device is in power down) the output pins is in a high-impedance state.

### 9.1.6 Driving Capacitive Loads

In most ADC applications, an FDA is required to drive capacitive load of an RC charge kickback filter. Other applications may require some other next-stage devices to be driven. The strong output stage of the THP210 drives higher capacitive loads compared to other FDAs.  $\boxtimes$  6-25 implies that the small-signal overshoot is less then 20% at a direct capacitive load connection of 140 pF. To help avoid instability and drive higher capacitive loads, add a small resistor (referred to as isolation resistor R<sub>ISO</sub> in both this plot and  $\boxtimes$  6-26) at the outputs of the THP210 before the capacitive load.

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

# 9.1.7 Driving Differential ADCs

The THP210 provides a differential output interface to drive a variety of modern, high-performance ADCs. The following section describes the key elements that must be considered when designing a differential input driver for SAR ADCs.

#### 9.1.7.1 RC Filter Selection (Charge Kickback Filter)

The sample-and-hold operating behavior of SAR ADCs causes charge transients at the input stage, and thus to the output stage of the amplifier. The RC filter helps to attenuate the sampling charge injection from the switched capacitor input stage of the ADC. A careful design is critical to meet linearity and noise performance of the ADC.

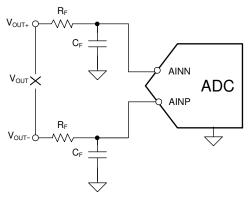

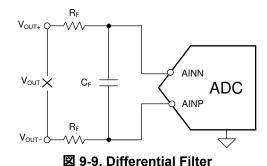

図 9-8. Single-Ended Filter

Choose the capacitor to be at least 10 times larger than the specified value of the SAR ADC sampling capacitor. A trade-off must be considered for the isolation resistor, where a higher damping effect is achieved at higher values, and lower value provide better THD at the input of the ADC. To select the best RC combination, use the Analog Engineering Tool.

One important element to consider is that the small-signal bandwidth of the FDA ( $f_{SSBW\_FDA}$ ) determines what the cutoff frequency of the RC filter combination can be driven at the inputs of the ADC. Depending whether a single-ended filter or a differential filter is used the minimum required small-signal bandwidth of the FDA ( $f_{SSBW\_FDA}$ ) can be estimated by  $\not \equiv 4$ :

$$f_{SSBW\_FDA} > \frac{1}{2\pi \cdot SEL \cdot R_F \cdot C_F}$$

(4)

where:

SEL = 1 for single-ended filter, SEL = 2 for differential filter

Driving higher capacitive loads degrades the phase margin of the FDA, and causes instability issues. Best practice is to perform a SPICE simulation using TINA-TI™ simulation software to confirm that the desired circuit is stable; that is, the FDA has more than a 45° phase margin.

Copyright © 2021 Texas Instruments Incorporated

#### 9.1.7.2 Settling Time Driving the ADC Sample-and-Hold Operating Behavior

The RC filter between the amplifier and the ADC helps the amplifier drive the sampling capacitor during charging (acquisition) and discharging (conversion) times. During the acquisition time, if the amplifier has a load transient at the output, the time needed to recover (or settle) is commonly defined as the settling time. Typically, to achieve minimal distortion, the end value to settle is within ½ of the ADC least significant bit (LSB).

The specified settling time of the FDA is the time required for the amplifier to recover from transients caused at the THP210 output. Although the frequency response characteristics impact the settling time of the ADC application, these characteristics are not the key element to consider. The settling time of the FDA to react to load transients depends primarily on the output impedance of the amplifier at the required signal bandwidth. 式 5 calculates the settling time, considering the time constant of the RC combination:

$$t_{\text{settle}} = -\ln\left(\frac{1}{2^{N} \times \text{SET}}\right) \times \tau \tag{5}$$

where:

- N is the number of bits in the ADC application

- T equals R<sub>F</sub> × C<sub>F</sub>

- SET = 2 for a settling of ½ LSB, SET = 4 for a settling of ¼ LSB, and so on.

In order to verify whether the chosen RC filter combination fulfills the settling behavior, simulate the desired circuit with TINA-TI™ simulation software.

#### 9.1.7.3 THD Performance

The input driver and the ADC both introduce harmonic distortion in the data acquisition block that generates undesired signals in the output harmonically related to the input signal. Total harmonic distortion (THD) can be very important in applications measuring ac signals. However, there are also ADC dc-measurement applications that are only concerned with SNR and linearity. To make sure that the total system distortion performance is not dominated by the front-end stage, the distortion of the driver circuitry must be at least 10 dB less than the distortion of the ADC, as shown in 3.6:

$$THD_{FDA} \le THD_{ADC} - 10 \text{ dB}$$

(6)

The harmonic distortion of an FDA mainly relates to the open-loop linearity in the output stage corrected by the loop gain at the fundamental frequency. When the total load impedance decreases, including the effect of the feedback resistors loadings, the output stage open-loop linearity degrades, and thus worsens the harmonic distortion, as seen in  $\boxtimes$  6-10.

Another effect that results from the RC filter is that the load impedance changes over frequency, which also influences the THD.

An additional dependency is given by the output voltage swing. Increasing the output voltage swing increases the nonlinearities of the open-loop output stage, thus degrading the harmonic distortion.

In summary, the harmonic distortion is negatively affected not only with decreasing load impedance and increasing output voltage swing, but also with increasing noise gain.

セクション 9.2.2 provides an measurement results of the THD performance using the THP210 and the ADS891x ADC series.

# 9.2 Typical Applications

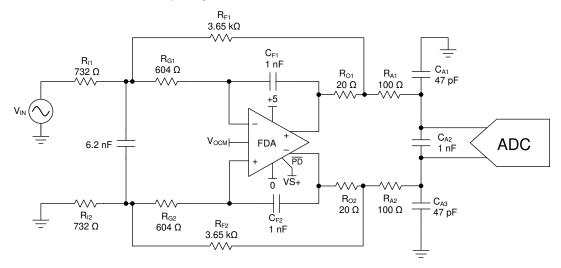

#### 9.2.1 MFB Filter

A common application use case for fully-differential amplifiers is to easily convert a single-ended signal into a differential signal to drive a differential input source, such as an ADC or class D amplifier.

9-12 shows an example of the THP210 used to convert a single-ended, low-voltage signal source, such as a small electric microphone, and deliver a low-noise differential signal that is common-mode shifted to the center of the ADC input range. A multiple-feedback (MFB) configuration is used to provide a Butterworth filter response, giving a 40-dB/decade cutoff with a -3-dB frequency of 30 kHz.

図 9-10. Example 30-kHz Butterworth Filter

#### 9.2.1.1 Design Requirements

The requirements for this application are:

- Single-ended to differential conversion

- 5-V/V gain

- Active filter set to a Butterworth, 30-kHz response shape

- Output RC elements set by SAR input requirements (not part of the filter design)

- Filter element resistors and capacitors are set to limit added noise over the THP210

### 9.2.1.2 Detailed Design Procedure

The design proceeds using the techniques and tools suggested in the *Design Methodology for MFB Filters in ADC Interface Applications* application note. The process includes:

- Scale the resistor values to not meaningfully contribute to the output noise produced by the THP210.

- Select the RC ratios to hit the filter targets when reducing the noise gain peaking within the filter design.

- Set the output resistor to 10  $\Omega$  into a 1-nF differential capacitor.

- Add 47-pF common-mode capacitors to the load capacitor to improve common noise filtering.

- Inside the loop, add 20-Ω output resistors after the filter feedback capacitor to increase the isolation to the load capacitor.

Copyright © 2021 Texas Instruments Incorporated

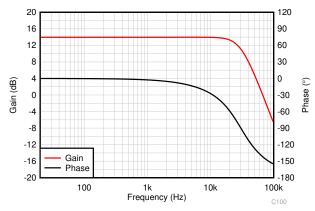

# 9.2.1.3 Application Curve

The gain and phase plots are shown in 🗵 9-11. The MFB filter features a Butterworth responses feature very flat passband gain, with a 2-pole rolloff at 30 kHz to eliminate any higher-frequency noise from contaminating the signal chain and potentially alias back into the desired band.

図 9-11. Gain and Phase Plot for a 30-kHz Butterworth Filter

# 9.2.2 ADS891x With Single-Ended RC Filter Stage

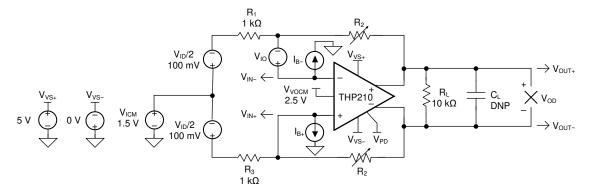

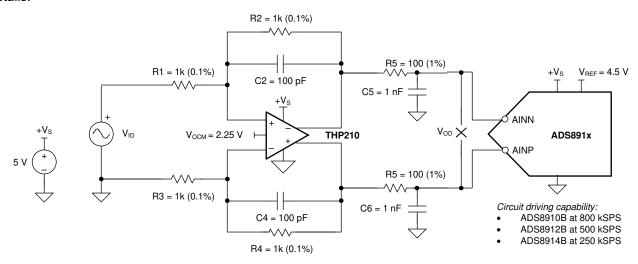

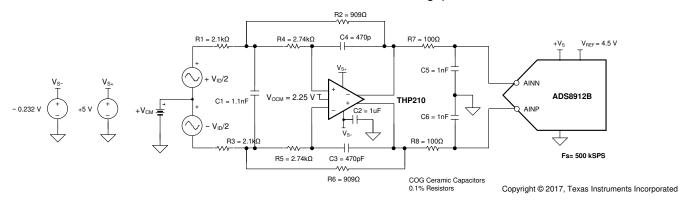

The application circuit in 🗵 9-12 shows the schematic of a complete reference driver circuit that generates a full-scale range of 4.5 V at the ADC using a unipolar supply voltage of 5 V. This circuit is used to measure the driving capability of the THP210 with the different variants of the ADS891x ADC.

To test the complete dynamic range of the circuit, the common-mode voltage  $V_{\text{OCM}}$  of the input of the ADC is established at a value of  $V_{\text{REF}}$  / 2. To exclude distortion caused by reference voltage  $V_{\text{REF}}$  and common-mode voltage  $V_{\text{OCM}}$  of the ADC, the test circuit uses the low-noise OPA2625 in an inverting gain configuration for  $V_{\text{OCM}}$ , and the high-precision, low-noise REF5050 for  $V_{\text{REF}}$ . See the ADS8910BEVM-PDK user's guide for more details.

図 9-12. Driving ADS891x With Single-Ended RC Filter Stage

#### 9.2.2.1 Design Requirements

The requirements for this application are:

- Differential to differential conversion

- Unipolar supply voltage of 5 V

- Full-scale range of ADC of FSR = ±4.5 V

- Input signal amplitude of V<sub>REF</sub> –0.4 dB

- Driver configuration in unity-gain buffer configuration (1-V/V gain)

- Circuit bandwidth f<sub>(-3dB)</sub> = 935 kHz

- · Output RC elements set by SAR input requirements

### 9.2.2.1.1 Measurement Results

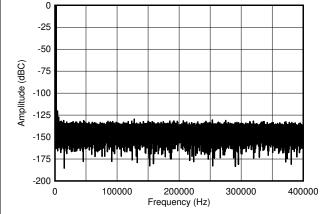

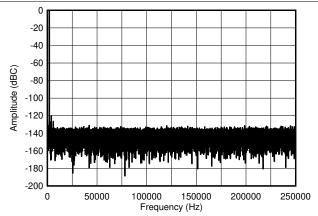

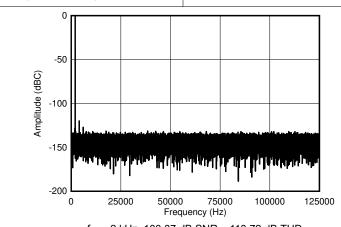

The THP210 and the filter combination listed in セクション 9.2.2.1 allow for the best trade-off between harmonic distortion and maintaining stability of the FDA. 表 9-1 and 図 9-13 through 図 9-15 showcase the device performance.

表 9-1. THP210 + ADS891x: FFT Data Summary

| ADC VERSION | ADC SPECIFICATION  | SAMPLING RATE | SNR       | THD <sup>(1)</sup> | SINAD     |

|-------------|--------------------|---------------|-----------|--------------------|-----------|

| ADS8910B    | 1-MSPS max, 18 bit | 800 kSPS      | 100.37 dB | –118.4 dB          | 100.31 dB |

| ADS8912B    | 500 kSPS, 18 bit   | 500 kSPS      | 100.4 dB  | -118.44 dB         | 100.33 dB |

| ADS8914B    | 250 kSPS, 18 bit   | 250 kSPS      | 100.37 dB | –118.72 dB         | 100.33 dB |

(1) THD can further be improved by providing a bipolar power supply for more headroom for the negative voltage swing. In the given circuit, a negative supply of V<sub>S</sub> = 0.23 V improved the THD to –120.5 dB.

f<sub>IN</sub> = 2 kHz, 100.37 dB SNR, -118.4 dB THD

図 9-13. Noise Performance FFT Plot: THP210 + ADS8910B, 800 kSPS, 18-Bit

$f_{IN} = 2 \text{ kHz}, 100.4 \text{ dB SNR}, -118.44 \text{ dB THD}$

図 9-14. Noise Performance FFT Plot: THP210 + ADS8912B, 500 kSPS, 18-Bit

$f_{\text{IN}}$  = 2 kHz, 100.37 dB SNR, -118.72 dB THD

図 9-15. Noise Performance FFT Plot: THP210 + ADS8914B, 250 kSPS, 18-Bit

#### 9.2.3 Attenuation Configuration Drives the ADS8912B

Many applications require to level-shift high-voltage input signals down to the lower-voltage ADC domain.  $\[mu]$  9-16 shows an example of the THP210 used to attenuate a  $\pm 10$ -V differential signal to drive a differential SAR ADC with full-scale range of  $\pm 4.5$ V. The common-mode voltage is shifted to the center of the ADC input range. A multiple-feedback (MFB) configuration as described in  $\pm 29$  9.2.1 is used to provide a Butterworth filter response, giving a 40-dB/decade roll-off with a -3-dB frequency of 100 kHz. The THP210 is powered with a 5-V supply and a -0.232-V negative supply generated by the low-noise negative bias generator (LM7705) allowing additional headroom for output swing to GND with ultra-low distortion. Alternatively, the THP210 can be powered using a unipolar 5-V supply with good distortion performance.

The circuit is able to drive the ADS8912B 18-Bit SAR ADC at full throughput of 500-kSPS.

図 9-16. Driving ADS8912B in Attenuation Configuration of 0.4333 V/V

#### 9.2.3.1 Design Requirements

The requirements for this application are:

- Differential to differential conversion

- Second order Butterworth filter with corner frequency of 100 kHz, offering flat frequency response

- Circuit accepts fully differential input signal of Vdiff = ± 10 V

- Circuit Attenuation is set to 0.433 V/V (–7.273 dB)

- Full-scale range of ADC of FSR = ±4.5 V

- · Filter elements set to limit added noise over THP210 while maintaining circuit stability

- Output RC elements set by SAR input requirements

For a detailed design procedure, see セクション 9.2.1.2.

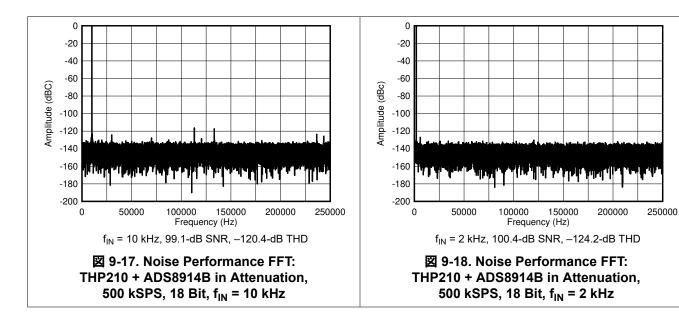

#### 9.2.3.1.1 Measurement Results

☑ 9-17 and ☑ 9-18 showcases the measured performance of the discussed circuit with SNR and THD results.

表 9-2. THP210 + ADS8912B in Attenuation - FFT Data Summary

| ADC VERSION | ADC SPECIFICATION | SAMPLING RATE | INPUT SIGNAL             | SNR      | THD       |

|-------------|-------------------|---------------|--------------------------|----------|-----------|

| ADS8912B    | 500 kSPS, 18 bit  | 500 kSPS      | f <sub>IN</sub> = 2 kHz  | 100.4 dB | –124.2 dB |

| ADS8912B    | 500 kSPS, 18 bit  | 500 kSPS      | f <sub>IN</sub> = 10 kHz | 99.1 dB  | -120.4 dB |

# 10 Power Supply Recommendations

The THP210 operates from supply voltages of 3.0 V to 36 V (±1.5 V to ±18 V for dual supply). Connect ceramic bypass capacitors from both VS+ and VS- to GND.

### 11 Layout

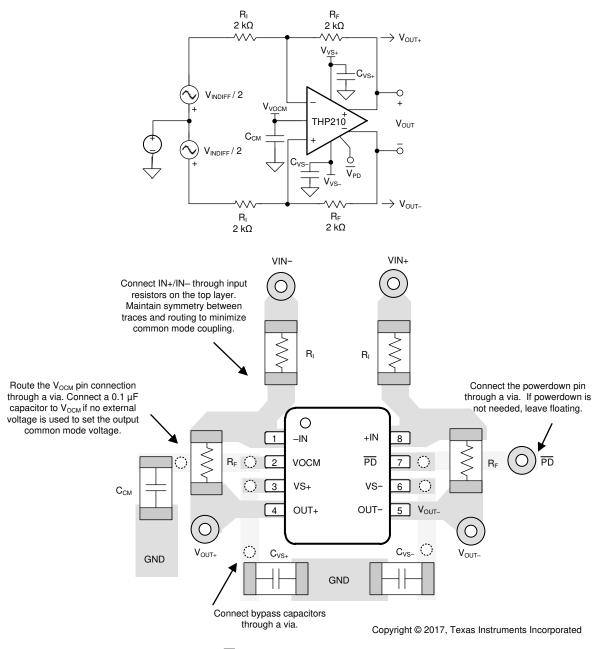

# 11.1 Layout Guidelines

# 11.1.1 Board Layout Recommendations

- Keep differential signals routed together to minimize parasitic impedance mismatch.

- Connect a 0.1-µF capacitor to the supply nodes through a via.

- If no external voltage is used, connect a 0.1-µF capacitor to the VOCM pin.

- Keep any high-frequency nodes that can couple through parasitic paths away from the VOCM node.

- Clean the printed circuit board (PCB) after assembly to minimize any leakage paths from excess flux into the VOCM node.

### 11.2 Layout Example

図 11-1. Example Layout

# 12 Device and Documentation Support

# 12.1 Device Support

### 12.1.1 Development Support

- THP210 TINA-TI™ Simulation Software model

- TINA-TI Gain of 0.2 100kHz Butterworth MFB Filter

- TINA-TI 100kHz MFB filter LG test

- TINA-TI Differential Transimpedance LG Sim

## **12.2 Documentation Support**

#### 12.2.1 Related Documentation

For related documentation see the following:

- Texas Instruments, INA188 Precision, Zero-Drift, Rail-to-Rail Out, High-Voltage Instrumentation Amplifier data sheet

- Texas Instruments, OPAx192 36-V, Precision, Rail-to-Rail Input/Output, Low Offset Voltage, Low Input Bias Current Op Amp with e-trim™ data sheet

- Texas Instruments, OPA161x SoundPlus™ High-Performance, Bipolar-Input Audio Operational Amplifiers data sheet

- Texas Instruments, Design Methodology for MFB Filters in ADC Interface Applications application report

- Texas Instruments, Design for Wideband Differential Transimpedance DAC Output application report

# 12.3 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. Click on *Subscribe to updates* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

### 12.4 サポート・リソース

TI E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、該当する貢献者により、現状のまま提供されるものです。これらは TI の仕様を構成するものではなく、必ずしも TI の見解を反映したものではありません。TI の使用条件を参照してください。

#### 12.5 Trademarks

TI E2E™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

#### 12.6 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい ESD 対策をとらないと、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

# 12.7 用語集

TI 用語集 この用語集には、用語や略語の一覧および定義が記載されています。

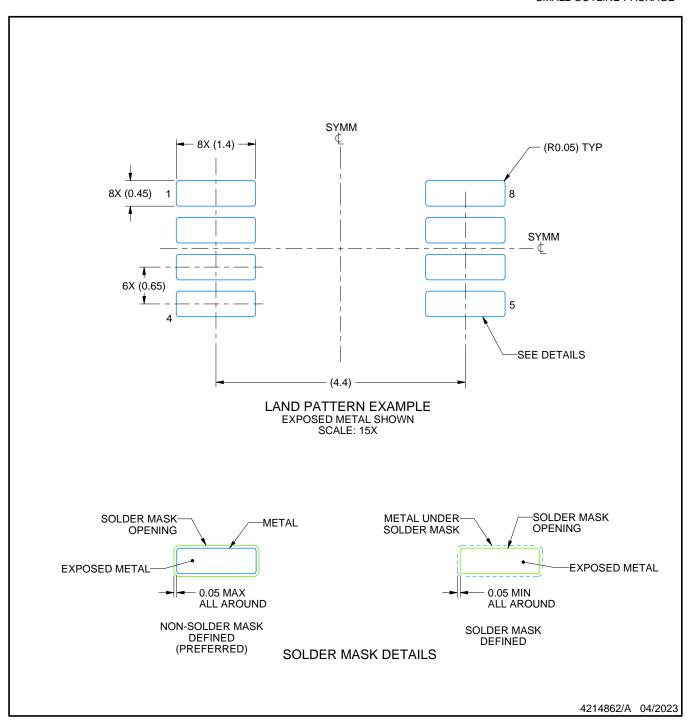

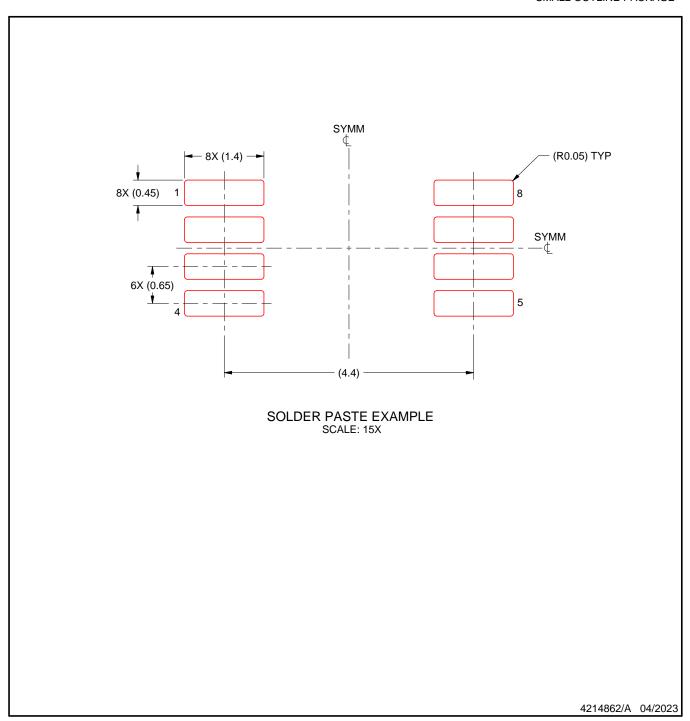

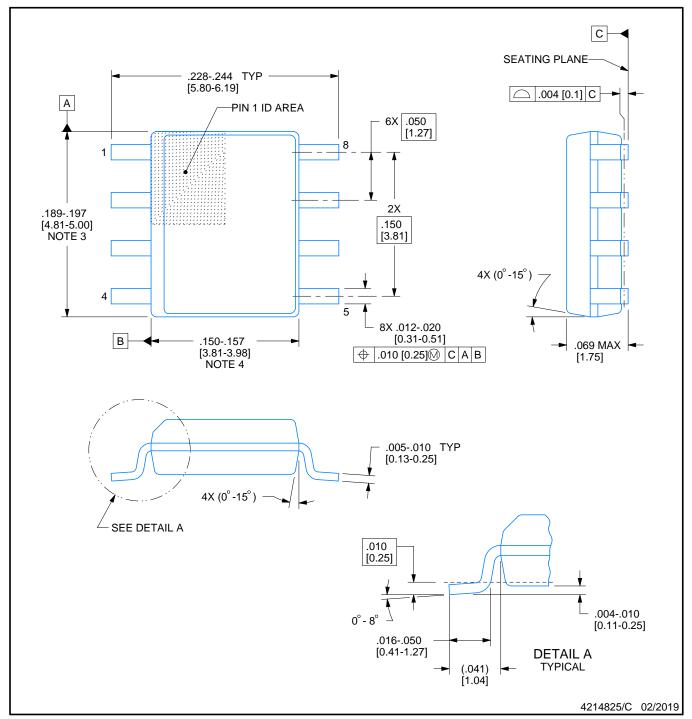

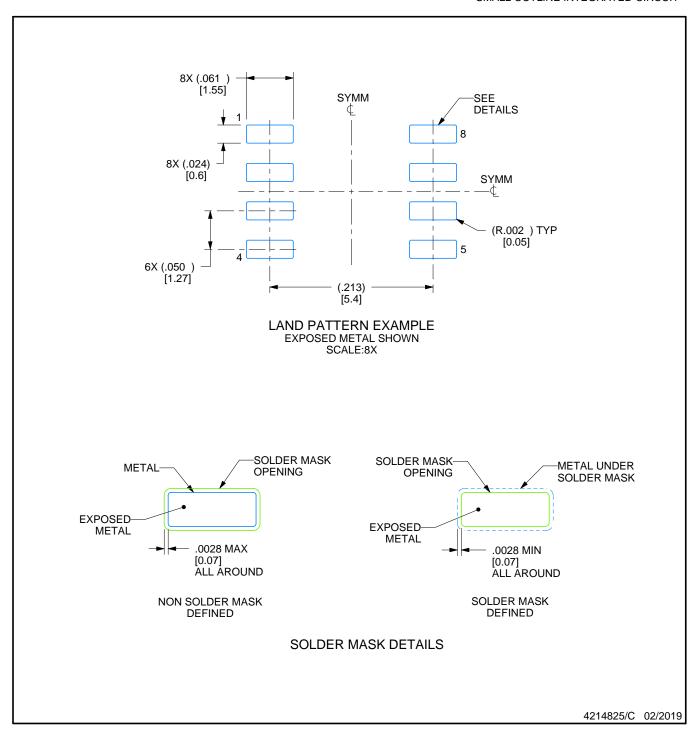

# 13 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

www.ti.com 2-Dec-2025

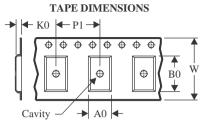

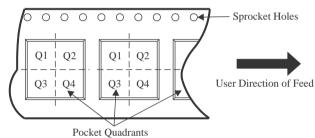

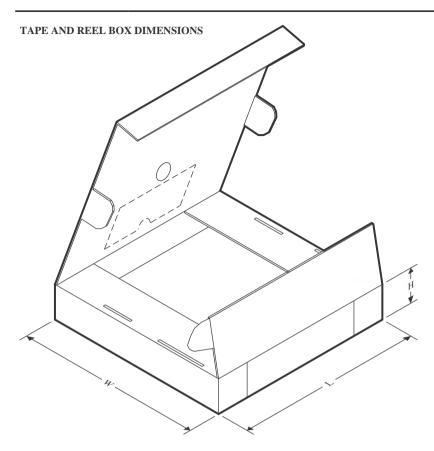

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins  | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|-----------------|-----------------------|------|-------------------------------|----------------------------|--------------|------------------|

|                       | ` '    | ``            |                 |                       |      | (4)                           | (5)                        |              | ` , ,            |

| THP210DGKR            | Active | Production    | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes  | NIPDAU   SN<br>  NIPDAUAG     | Level-2-260C-1 YEAR        | -40 to 125   | 1237             |

| THP210DGKR.B          | Active | Production    | VSSOP (DGK)   8 | 2500   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | 1237             |

| THP210DGKT            | Active | Production    | VSSOP (DGK)   8 | 250   SMALL T&R       | Yes  | NIPDAU   SN<br>  NIPDAUAG     | Level-2-260C-1 YEAR        | -40 to 125   | 1237             |

| THP210DGKT.B          | Active | Production    | VSSOP (DGK)   8 | 250   SMALL T&R       | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | 1237             |

| THP210DGKTG4          | Active | Production    | VSSOP (DGK)   8 | 250   SMALL T&R       | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | 1237             |

| THP210DGKTG4.B        | Active | Production    | VSSOP (DGK)   8 | 250   SMALL T&R       | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | 1237             |

| THP210DR              | Active | Production    | SOIC (D)   8    | 2500   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | THP210           |

| THP210DR.B            | Active | Production    | SOIC (D)   8    | 2500   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | THP210           |

| THP210DRG4            | Active | Production    | SOIC (D)   8    | 2500   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | THP210           |

| THP210DRG4.B          | Active | Production    | SOIC (D)   8    | 2500   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | THP210           |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.