SBAA532A February 2022 – March 2024 ADS1119 , ADS1120 , ADS1120-Q1 , ADS112C04 , ADS112U04 , ADS1130 , ADS1131 , ADS114S06 , ADS114S06B , ADS114S08 , ADS114S08B , ADS1158 , ADS1219 , ADS1220 , ADS122C04 , ADS122U04 , ADS1230 , ADS1231 , ADS1232 , ADS1234 , ADS1235 , ADS1235-Q1 , ADS124S06 , ADS124S08 , ADS1250 , ADS1251 , ADS1252 , ADS1253 , ADS1254 , ADS1255 , ADS1256 , ADS1257 , ADS1258 , ADS1258-EP , ADS1259 , ADS1259-Q1 , ADS125H01 , ADS125H02 , ADS1260 , ADS1260-Q1 , ADS1261 , ADS1261-Q1 , ADS1262 , ADS1263 , ADS127L01 , ADS130E08 , ADS131A02 , ADS131A04 , ADS131E04 , ADS131E06 , ADS131E08 , ADS131E08S , ADS131M02 , ADS131M03 , ADS131M04 , ADS131M06 , ADS131M08

- 1

- Abstract

- Trademarks

- 1Bridge Overview

- 2Bridge Construction

- 3Bridge Connections

- 4Electrical Characteristics of Bridge Measurements

- 5Signal Chain Design Considerations

-

6Bridge Measurement Circuits

- 6.1 Four-Wire Resistive Bridge Measurement with a Ratiometric Reference and a Unipolar, Low-Voltage (≤5 V) Excitation Source

- 6.2 Six-Wire Resistive Bridge Measurement With a Ratiometric Reference and a Unipolar, Low-Voltage (≤ 5 V) Excitation Source

- 6.3 Four-Wire Resistive Bridge Measurement With a Pseudo-Ratiometric Reference and a Unipolar, High-Voltage (> 5 V) Excitation Source

- 6.4 Four-Wire Resistive Bridge Measurement with a Pseudo-Ratiometric Reference and Asymmetric, High-Voltage (> 5 V) Excitation Source

- 6.5 Four-Wire Resistive Bridge Measurement With a Ratiometric Reference and Current Excitation

- 6.6 Measuring Multiple Four-Wire Resistive Bridges in Series with a Pseudo-Ratiometric Reference and a Unipolar, Low-Voltage (≤5V) Excitation Source

- 6.7 Measuring Multiple Four-Wire Resistive Bridges in Parallel Using a Single-Channel ADC With a Ratiometric Reference and a Unipolar, Low-Voltage (≤ 5 V) Excitation Source

- 6.8 Measuring Multiple Four-Wire Resistive Bridges in Parallel Using a Multichannel ADC With a Ratiometric Reference and a Unipolar, Low-Voltage (≤ 5 V) Excitation Source

- 7Summary

- 8Revision History

6.3.4 Design Notes

In the high-voltage, unipolar supply configuration, the excitation voltage applied to the bridge, VEXCITATION, cannot typically be used as the ADC supply voltage. Instead, an additional lower-voltage supply (≤ 5 V) is required to power the ADC. Moreover, the ADC cannot directly use the high-voltage excitation source as the differential reference voltage, VREF, and instead requires an attenuation circuit. A simple resistor divider as shown in Figure 6-3 is typically used, though other options include a difference amplifier or a discrete voltage reference. Using a resistor divider or an amplifier can introduce errors between the bridge and the reference inputs that are not present between the bridge and the ADC inputs, resulting in a pseudo-ratiometric reference configuration. Choosing a discrete voltage reference results in a non-ratiometric configuration. It is also necessary to ensure the higher-voltage bridge output signals are within the lower-voltage input range of the ADC. Solving this design challenge generally requires an amplifier as shown in Figure 6-3. Adding an amplifier between the bridge and the ADC can introduce errors that are not present between the bridge and the reference inputs, further reducing the effectiveness of the pseudo-ratiometric reference configuration.

A four-wire resistive bridge measurement with a pseudo-ratiometric reference and a unipolar, high-voltage (> 5 V) supply requires:

- Differential analog inputs (AINP and AINN)

- External reference input or integrated voltage reference

- Low-noise amplifier

- High-voltage supplies

- VREF attenuation circuit (resistor divider, difference amplifier, and so forth) or separate voltage reference

- VIN attenuation circuit (if applicable)

First, identify the maximum differential output voltage of the bridge, VOUT(Bridge Max), using the equation from Table 6-7 and parameters from Table 6-6. This value provides the maximum output voltage possible from the bridge under normal operating conditions and corresponds to the maximum load that can be applied to the bridge, Load(Bridge Max). If the system does not use the entire output range of the bridge, VOUT(System Max) defines the maximum differential output signal that is applied to a specific system and Load(System Max) is the corresponding maximum load. For example, if VOUT(Bridge Max) corresponds to Load(Bridge Max) = 5 kg, but the system specifications only require that Load(System Max) = 2.5 kg, then VOUT(System Max) is given by Equation 46:

Note that if Load(System Max) = Load(Bridge Max), then VOUT(System Max) = VOUT(Bridge Max).

After VOUT(System Max) has been determined, choose the corresponding gain value for the amplifier. For this specific circuit configuration, the gain can be applied by an external or internal amplifier. In either case, the amplifier gain should be the largest allowable value that is still less than the ADC full-scale range (FSR). In some cases it is not possible to choose an amplifier gain that uses the entire ADC FSR, especially when an ADC with an integrated PGA is selected. While this is often an acceptable tradeoff between resolution and ease-of-use, care should be taken to ensure that all system requirements are still met when the ADC FSR cannot be maximized.

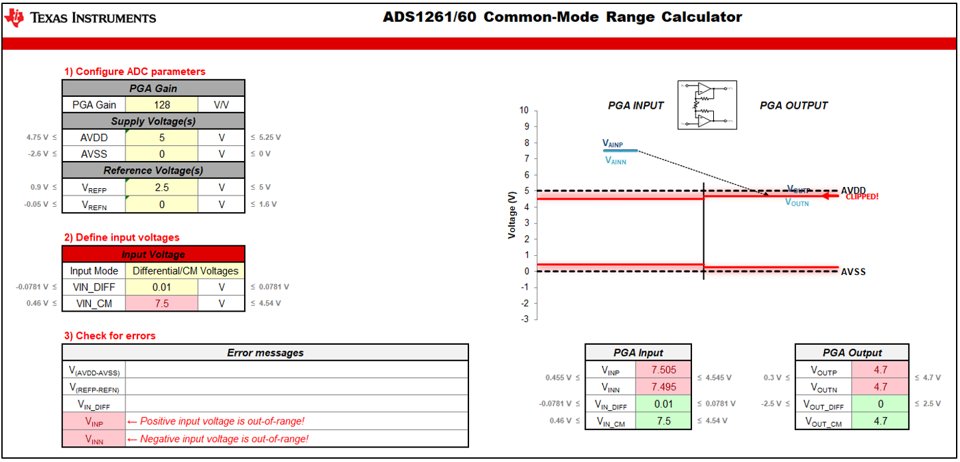

Next, consider if the bridge output common-mode voltage, VCM(Bridge), needs to be level-shifted prior to being applied to the ADC. Many ADCs used for bridge measurement applications have support collateral that can aid in this process. Figure 6-4 shows an example of how the Common-Mode Range Calculator from the ADS1261 Excel Calculator can be used to determine if VCM(Bridge) is within the input range of the amplifier integrated into the ADS1261.

Figure 6-4 Verifying System Requirements Using the ADS1261 VCM Calculator Tool

Figure 6-4 Verifying System Requirements Using the ADS1261 VCM Calculator ToolIn Figure 6-4, VIN_CM = 7.5 V, which is VCM(Bridge) in Figure 6-3 under a no-load condition (R1 = R2 = R3 = R4). The tool highlights several errors indicating that this is not a valid input condition. This result is in spite of the fact that the differential input voltage, VIN_DIFF, is well within the ±78-mV input range of the amplifier. It is possible to choose an ADC that can measure high-voltage signals directly, such as the ADS125H02, but most ADCs require an attenuation stage when VEXCITATION > 5 V.

If the ADC cannot directly support higher-voltage input signals, Figure 6-3 shows how an external amplifier can be used to level-shift the bridge output common-mode voltage. There are three options for the amplifier configuration:

- An instrumentation amplifier with a high gain such as INA849

- An integrated difference amplifier such as an INA105 with a gain of 1

- A discrete difference amplifier or instrumentation amplifier built from multiple op amps and a resistor feedback network

Adding an amplifier between the bridge and the ADC can introduce errors at the ADC input that are not present between the bridge and the VREF inputs, further reducing the effectiveness of the pseudo-ratiometric reference configuration. Choose an appropriate device based on the desired system accuracy and precision, while also factoring in system constraints such as cost, size, and power. Additionally, all amplifier configurations require a reference voltage, REF, to set the amplifier output common-mode voltage to an appropriate level for the ADC. This voltage is VCM(ADC) in Table 6-6, and is typically set to mid-supply (AVDD / 2). However, Figure 6-4 shows that the ADC amplifier has a VCM(ADC) range of 0.45 V to 4.54 V for this particular set of conditions.

Some ADCs, including the ADS1261 and ADS124S08, integrate a precision reference with an output pin that can be used to bias the amplifier and therefore minimize component count. If this feature is not available on the selected ADC, choose a low-drift, high-accuracy reference source to minimize errors. Moreover, ensure that the entire amplifier circuit is low noise and high accuracy because any error in the input signal conditioning circuitry passes to the ADC output.

After selecting an external amplifier circuit, choose the system reference source. When selecting a discrete voltage reference, ensure this component is high accuracy and low drift for best performance. To maintain a pseudo-ratiometric relationship between VEXCITATION and VREF, choose a resistor divider to attenuate the bridge excitation voltage. The resistor divider shown in Figure 6-3 consists of two resistors, with the reference voltage established across the bottom component, RREF. Since the ADC AVDD is unipolar, VREFN is typically set to 0 V such that the ratio of RTOP to RREF can be expressed using Equation 47:

Equation 48 determines the resistor ratio given the conditions shown in Figure 6-3 where VREF = 5 V and VEXCITATION = 15 V:

Therefore, if the impedance for RREF = R, then RTOP = 2 • R in Figure 6-3.

Select high accuracy (≤ 0.1 %), low temperature-drift (≤ 10 ppm/°C) resistors for the reference path. Keep the nominal resistance value low to limit thermal noise. As an example, a 1-kΩ resistor at 25°C and 1-kHz bandwidth contributes 128 nVRMS of noise. These conditions are important to keep VREF as close as possible to being ratiometric with VEXCITATION and minimize overall measurement error. Additionally, a buffer might be required depending on the impedance of the ADC differential reference inputs. The buffer can also introduce errors and further reduce the ratiometric relationship between VIN and VREF.

Finally, follow the instructions in Section 5.5 if calibration is required.