SLVUAW9C September 2016 – February 2020 UCD90320

-

UCD90320 Sequencer and System Health Controller PMBus Command Reference

- Trademarks

- 1 PMBus Specification

- 2 Data Formats

- 3 Memory Model

- 4 Alert Response Address Support

- 5 Supported PMBus Commands

- 6

Implementation Details for PMBus Core Commands

- 6.1 (00h) PAGE

- 6.2 (01h) OPERATION

- 6.3 (11h) STORE_DEFAULT_ALL

- 6.4 (12h) RESTORE_DEFAULT_ALL

- 6.5 (1Bh) SMBALERT_MASK

- 6.6 (20h) VOUT_MODE

- 6.7 (38h) IOUT_CAL_GAIN

- 6.8 (41h – 69h) xxx_FAULT_RESPONSE

- 6.9 (62h) TON_MAX_FAULT_LIMIT

- 6.10 (66h) TOFF_MAX_WARN_LIMIT

- 6.11 (80h) STATUS_MFR_SPECIFIC

- 6.12 (81h) STATUS_FAN_1_2 and (82h) STATUS_FAN_3_4

- 6.13 (8Dh) READ_TEMPERATURE_1

- 6.14 (8Eh) READ_TEMPERATURE_2

- 6.15 (90-93h) FAN_SPEED_1 Through FAN_SPEED_4

- 6.16 (ADh) IC_DEVICE_ID

- 6.17 (AEh) IC_DEVICE_REV

- 7 Input and Output Pin Configuration

- 8 PWM Configuration

- 9 Implementation Details for User Data Commands

- 10

Implementation Details for Manufacturer-Specific Commands

- 10.1 (D0h) FAULT_PIN_CONFIG (MFR_SPECIFIC_00)

- 10.2 (D1h) VOUT_CAL_MONITOR (MFR_SPECIFIC_01)

- 10.3 (D2h) SYSTEM_RESET_CONFIG (MFR_SPECIFIC_02)

- 10.4 (D3h) SYSTEM_WATCHDOG_CONFIG (MFR_SPECIFIC_03)

- 10.5 (D4h) SYSTEM_WATCHDOG_RESET (MFR_SPECIFIC_04)

- 10.6 (D5h) MONITOR_CONFIG (MFR_SPECIFIC_05)

- 10.7 (D6h) NUM_PAGES (MFR_SPECIFIC_06)

- 10.8 (D7h) RUN_TIME_CLOCK (MFR_SPECIFIC_07)

- 10.9 (D8h) RUN_TIME_CLOCK_TRIM (MFR_SPECIFIC_08)

- 10.10 (D9h) ROM_MODE (MFR_SPECIFIC_09)

- 10.11 (DAh) USER_RAM_00 (MFR_SPECIFIC_10)

- 10.12 (DBh) SOFT_RESET (MFR_SPECIFIC_11)

- 10.13 (DCh) RESET_COUNT (MFR_SPECIFIC_12)

- 10.14 (DDh) PIN_SELECTED_RAIL_STATES (MFR_SPECIFIC_13)

- 10.15 (DEh) RESEQUENCE (MFR_SPECIFIC_14)

- 10.16 (DFh) CONSTANTS (MFR_SPECIFIC_15)

- 10.17 (E0h) PWM_SELECT (MFR_SPECIFIC_16)

- 10.18 (E1h) PWM_CONFIG (MFR_SPECIFIC_17)

- 10.19 (E2h) PARM_INFO (MFR_SPECIFIC_18)

- 10.20 (E3h) PARM_VALUE (MFR_SPECIFIC_19)

- 10.21 (E4h) TEMPERATURE_CAL_GAIN (MFR_SPECIFIC_20)

- 10.22 (E5h) TEMPERATURE_CAL_OFFSET (MFR_SPECIFIC_21)

- 10.23 (E9h) FAULT_RESPONSES (MFR_SPECIFIC_25)

- 10.24 (EAh) LOGGED_FAULTS (MFR_SPECIFIC_26)

- 10.25 (EBh) LOGGED_FAULT_DETAIL_INDEX (MFR_SPECIFIC_27)

- 10.26 (ECh) LOGGED_FAULT_DETAIL (MFR_SPECIFIC_28)

- 10.27 (EDh) LOGGED_PAGE_PEAKS (MFR_SPECIFIC_29)

- 10.28 (EEh) LOGGED_COMMON_PEAKS (MFR_SPECIFIC_30)

- 10.29 (EFh) LOGGED_FAULT_DETAIL_ENABLES (MFR_SPECIFIC_31)

- 10.30 (F0h) EXECUTE_FLASH (MFR_SPECIFIC_32)

- 10.31 (F1h) SECURITY (MFR_SPECIFIC_33)

- 10.32 (F2h) SECURITY_BIT_MASK (MFR_SPECIFIC_34)

- 10.33 (F3h) MFR_STATUS (MFR_SPECIFIC_35)

- 10.34 (F4h) GPI_FAULT_RESPONSES (MFR_SPECIFIC_36)

- 10.35 (F5h) MARGIN_CONFIG (MFR_SPECIFIC_37)

- 10.36

(F6h) SEQ_CONFIG (MFR_SPECIFIC_38)

- 10.36.1 Enable Pin Configuration

- 10.36.2 GPI Sequence On Dependency Mask

- 10.36.3 GPI Sequence Off Dependency Mask

- 10.36.4 Sequencing Timeout Configuration

- 10.36.5 Sequencing On Timeout

- 10.36.6 Sequencing Off Timeout

- 10.36.7 Page Sequence On Dependency Mask

- 10.36.8 Page Sequence Off Dependency Mask

- 10.36.9 Fault Slaves Mask

- 10.36.10 GPO Sequence On Sependency Mask

- 10.36.11 GPO Sequence Off Sependency Mask

- 10.37 (F7h) GPO_CONFIG_INDEX (MFR_SPECIFIC_39)

- 10.38

(F8h) GPO_CONFIG (MFR_SPECIFIC_40)

- 10.38.1 Output Pin Configuration

- 10.38.2 Assert Delay Enable

- 10.38.3 De-Assert Delay Enable

- 10.38.4 Invert OR Output

- 10.38.5 Ignore Inputs During Delay

- 10.38.6 Invert AND Output

- 10.38.7 State Machine Mode Enable

- 10.38.8 High Resolution Delay Count

- 10.38.9 9 Millisecond Delay

- 10.38.10 Status Mask

- 10.38.11 Status Inversion Mask

- 10.38.12 GPI Mask

- 10.38.13 GPI Inversion Mask

- 10.38.14 GPO Mask

- 10.38.15 GPO Inversion Mask

- 10.38.16 Status Type Select

- 10.38.17 GPO Configuration Examples

- 10.39 (F9h) GPI_CONFIG (MFR_SPECIFIC_41)

- 10.40 (FAh) GPIO_SELECT (MFR_SPECIFIC_42)

- 10.41 (FBh) GPIO_CONFIG (MFR_SPECIFIC_43)

- 10.42 (FCh) MISC_CONFIG (MFR_SPECIFIC_44)

- 10.43 (FDh) DEVICE_ID (MFR_SPECIFIC_45)

- 11 Range Checking and Limits

- 12 Glossary

10.38 (F8h) GPO_CONFIG (MFR_SPECIFIC_40)

This Read/Write Block paged command configures the functionality of a given output pin. This paged command allows pins to be configured as status/GPI-influenced outputs. The state of the output pin is determined by a selection of GPIs and statuses that are processed through some combinational logic with optional inversion steps. In most cases, the statuses are related to pages (for example, Power Good).

NOTE

All configurations done with the MONITOR_CONFIG, GPI_CONFIG, and SEQ_CONFIG commands must be done before writing this command.

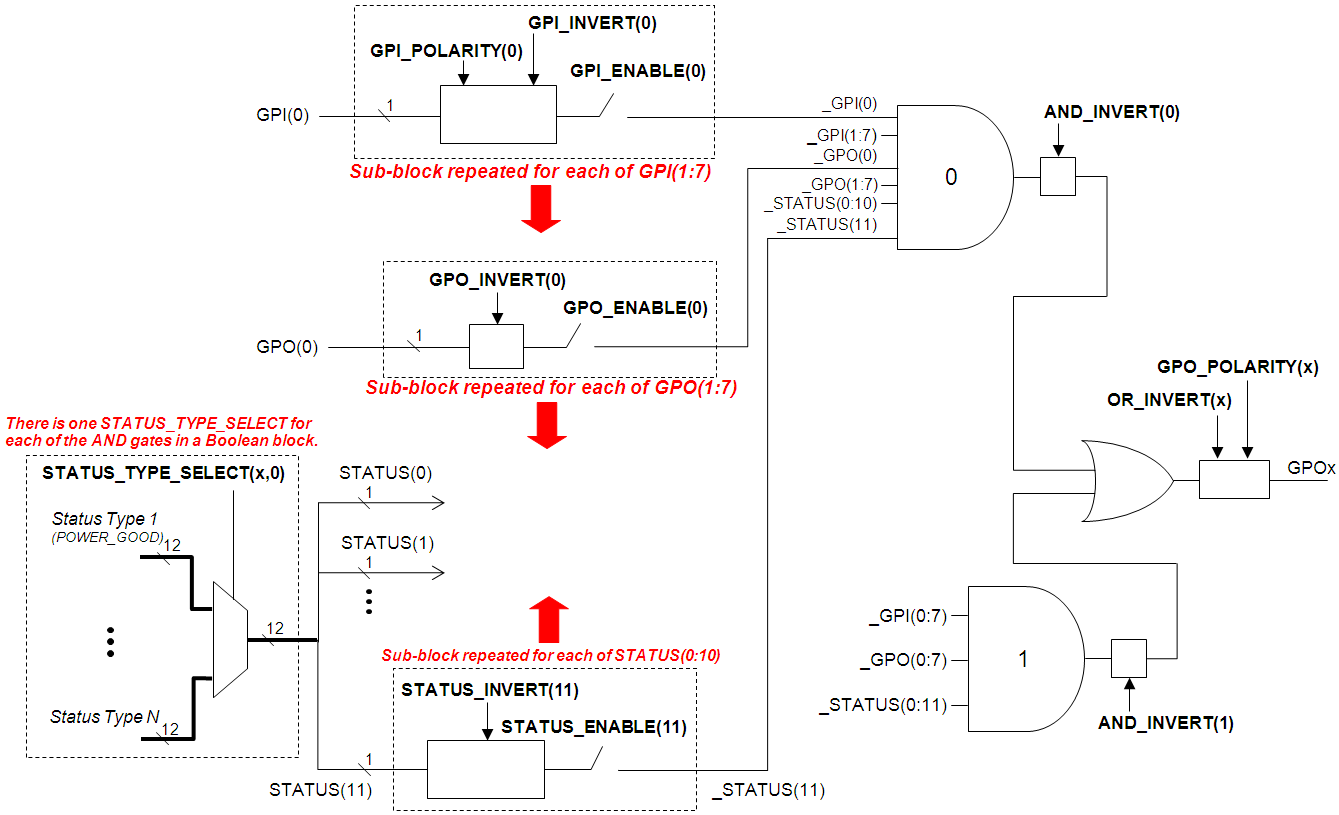

Figure 2 provides an overview of how the state of the GPO is determined.

NOTE

This document refers to the AND paths starting with “AND Path 0”. Fusion refers to the AND paths starting with and index of 1 instead of 0.

NOTE

The information in Figure 2 implies that the device supports 12 rails (0 to 11). For the UCD90320, this is not the case. It only supports 32 rails and the interpretation of this information should be adjusted for the correct number of rails.

Figure 2. Factors Determining the State of a GPO

Figure 2. Factors Determining the State of a GPO NOTE

For the sake of code efficiency, all configured/active GPOs must be packed in the lower page numbers. This means, if there is only one configured GPO, it must be associated with page zero. If there are two, they must be associated with page zero and one.

Table 62. GPO_CONFIG Command Format

| Byte Number

(Write) |

Byte Number

(Read) |

Payload Index | Description |

|---|---|---|---|

| 0 | CMD = F8 | ||

| 1 | 0 | BYTE_COUNT = 54 | |

| 2 | 1 | 0 | Output Pin Configuration

Bit Descriptions: 7:0: Pin ID for GPO pin |

| 3 | 2 | 1 | Output Pin Configuration

Bit Descriptions: 7:3: Reserved 2: Polarity of GPO pin 1:0: Pin Mode of GPO pin |

| 4 | 3 | 2 | Bit Descriptions:

7: Assert Delay Enable 6: De-assert Delay Enable 5: Invert OR Output 4: Ignore Inputs During Delay 3:0: High Resolution Delay Count |

| 5 | 4 | 3 | Millisecond Delay |

| 6 | 5 | 4 | AND Path 0 Configuration

Bit Description 7 Invert AND Output 6 State Machine Mode Enable 5:0 Status Type |

| 7 | 6 | 5 | AND Path 1 Configuration

Bit Description 7 Invert AND Output 6 Reserved 5:0 Status Type |

| AND Path 0 | |||

| 8 | 7 | 6 | Status Mask (Byte 0 - LSB) |

| 9 | 8 | 7 | Status Mask (Byte 1) |

| 10 | 9 | 8 | Status Mask (Byte 2) |

| 11 | 10 | 9 | Status Mask (Byte 3) |

| 12 | 11 | 10 | Status Inversion Mask (Byte 0 - LSB) |

| 13 | 12 | 11 | Status Inversion Mask (Byte 1) |

| 14 | 13 | 12 | Status Inversion Mask (Byte 2) |

| 15 | 14 | 13 | Status Inversion Mask (Byte 3) |

| 16 | 15 | 14 | GPI Mask (Byte 0 – LSB) |

| 17 | 16 | 15 | GPI Mask (Byte 1) |

| 18 | 17 | 16 | GPI Mask (Byte 2) |

| 19 | 18 | 17 | GPI Mask (Byte 3 – LSB) |

| 20 | 19 | 18 | GPI Inversion Mask (Byte 0 – LSB) |

| 21 | 20 | 19 | GPI Inversion Mask (Byte 1) |

| 22 | 21 | 20 | GPI Inversion Mask (Byte 2) |

| 23 | 22 | 21 | GPI Inversion Mask (Byte 3 - LSB) |

| 24 | 23 | 22 | GPO Mask (Byte 0 – LSB) |

| 25 | 24 | 23 | GPO Mask (Byte 1) |

| 26 | 25 | 24 | Reserved |

| 27 | 26 | 25 | GPO Mask (Byte 3)Reserved |

| 28 | 27 | 26 | GPO Inversion Mask (Byte 0 – LSB) |

| 29 | 28 | 27 | GPO Inversion Mask (Byte 1) |

| 30 | 29 | 28 | Reserved |

| 31 | 30 | 29 | Reserved |

| AND Path 0 | |||

| 32 | 31 | 30 | Status Mask (Byte 0 - LSB) |

| 33 | 32 | 31 | Status Mask (Byte 1) |

| 34 | 33 | 32 | Status Mask (Byte 2) |

| 35 | 34 | 33 | Status Mask (Byte 3) |

| 36 | 35 | 34 | Status Inversion Mask (Byte 0 - LSB) |

| 37 | 36 | 35 | Status Inversion Mask (Byte 1) |

| 38 | 37 | 36 | Status Inversion Mask (Byte 2) |

| 39 | 38 | 37 | Status Inversion Mask (Byte 3) |

| 40 | 39 | 38 | GPI Mask (Byte 0 – LSB) |

| 41 | 40 | 39 | GPI Mask (Byte !) |

| 42 | 41 | 40 | GPI Mask (Byte 2) |

| 43 | 42 | 41 | GPI Mask (Byte 3 – MSB) |

| 44 | 43 | 42 | GPI Inversion Mask (Byte 0 – LSB) |

| 45 | 44 | 43 | GPI Inversion Mask (Byte 1) |

| 46 | 45 | 44 | GPI Inversion Mask (Byte 2) |

| 47 | 46 | 45 | GPI Inversion Mask (Byte 3 – MSB) |

| 48 | 47 | 46 | GPO Mask (Byte 0 – LSB) |

| 49 | 48 | 47 | GPO Mask (Byte 1) |

| 50 | 49 | 48 | Reserved |

| 51 | 50 | 49 | Reserved |

| 52 | 51 | 50 | GPO Inversion Mask (Byte 0 – LSB) |

| 53 | 52 | 51 | GPO Inversion Mask (Byte 1) |

| 54 | 53 | 52 | Reserved |

| 55 | 54 | 53 | Reserved |