SLVUBI1 May 2021

4.5 Input Voltage Ripple

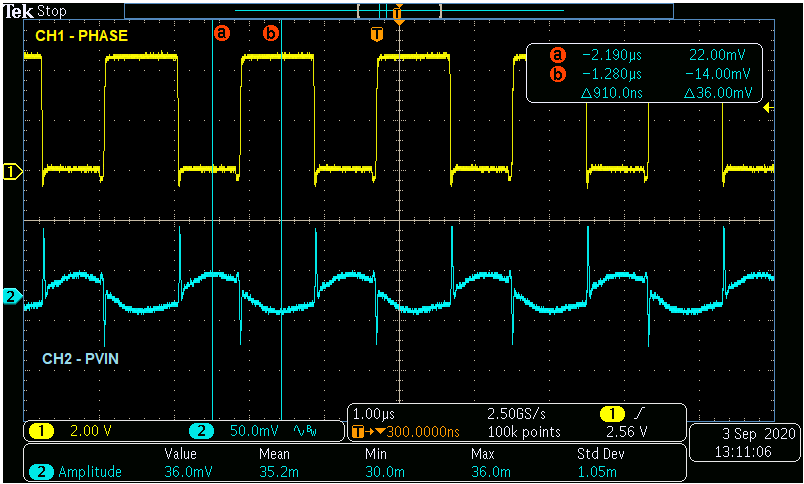

- Trigger CH1 of the oscilloscope on Phase Node and put the CH2 scope probe between test point TP6 (PVIN) and TP23 (GND).

As shown in Figure 4-6, the voltage ripple (ignoring the switching coupling to the input) is approximately 50 mV.

Figure 4-6 Input Voltage Ripple, VIN = 5

V, VOUT = 2.5 V, IOUT = 3 A

Figure 4-6 Input Voltage Ripple, VIN = 5

V, VOUT = 2.5 V, IOUT = 3 A