SNAK009A April 2022 – February 2024 ADC128S102-SEP

3 Test Device and Test Board Information

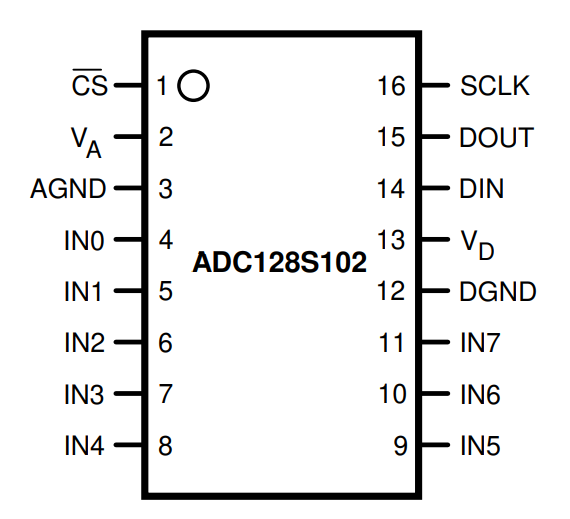

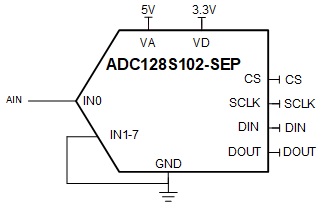

The ADC128S102-SEP is packaged in a 16-pin, TSSOP shown with the pinout in Figure 3-1. Figure 3-2 shows the biasing configuration used for both the SEL and SET tests.

ADC128S102-SEP pinout diagram. The package was decapped to reveal the die face for all heavy ion testing.

Figure 3-1 ADC128S102-SEP Pinout Diagram

Figure 3-1 ADC128S102-SEP Pinout Diagram Figure 3-2 ADC128S102-SEP Bias Configuration

Figure 3-2 ADC128S102-SEP Bias Configuration