SNLA415 August 2022 DS160PT801

5.2 Polling

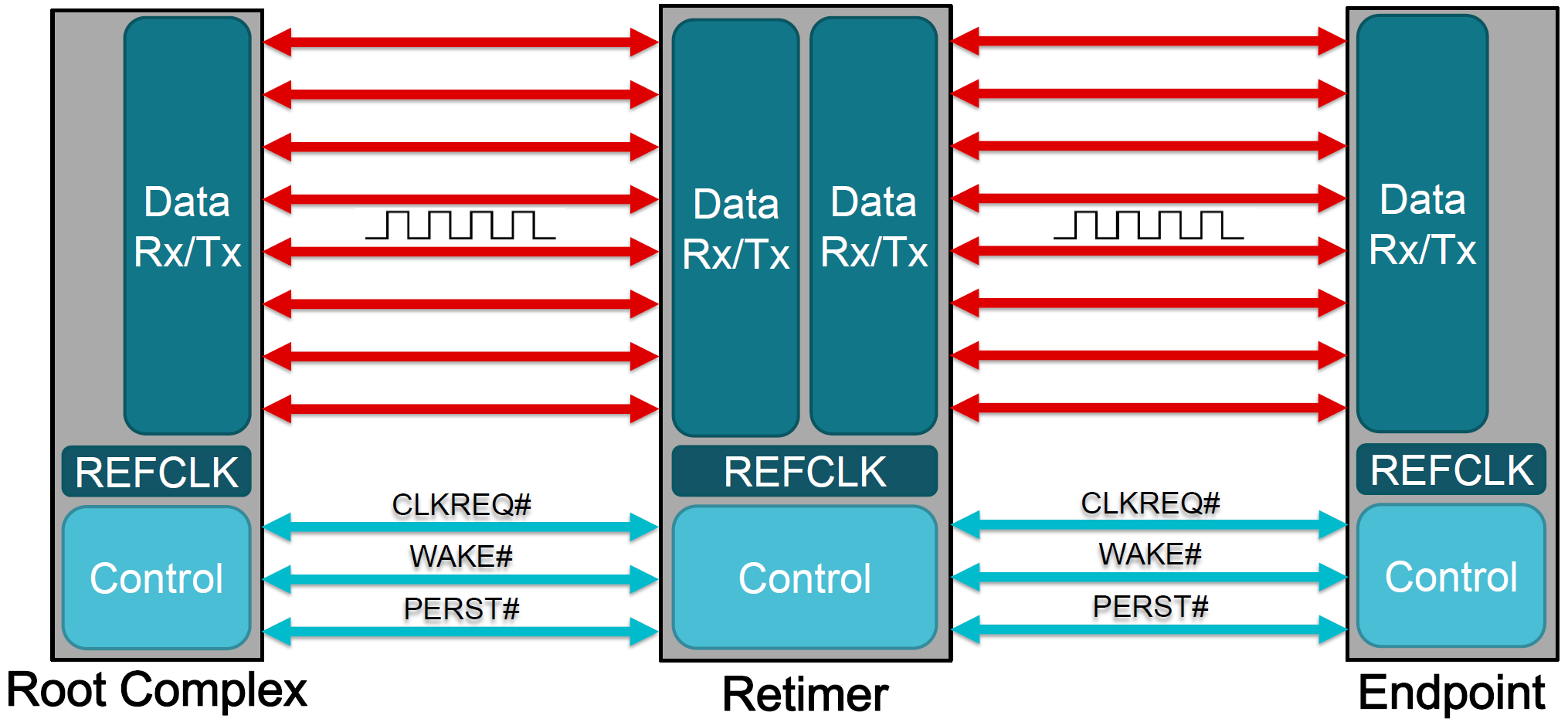

After Rx detect stage is done and each lane is transmitting data, PCIe link will start polling. Polling is a stage in which the root complex, repeater (referred as retimer in Figure 5-2), and the endpoint all begin transmitting ordered sets of data called training sequences at PCIe Gen 1 speeds in order to establish bit and symbol lock. Bit lock refers to when the receiver locks the clock frequency of the transmitter. Symbol lock refers to when the receiver is able to decode the valid 10-bit symbol coming from the transmitter. Figure 5-2 shows polling as red arrows with square signals pointing at PCIe devices. At the end of this process, each device is able to interpret the received data and respond accordingly and then proceed into the configuration stage.

Figure 5-2 PCIe Link Polling

Figure 5-2 PCIe Link Polling