SNLA415 August 2022 DS160PT801

5.3 Configuration

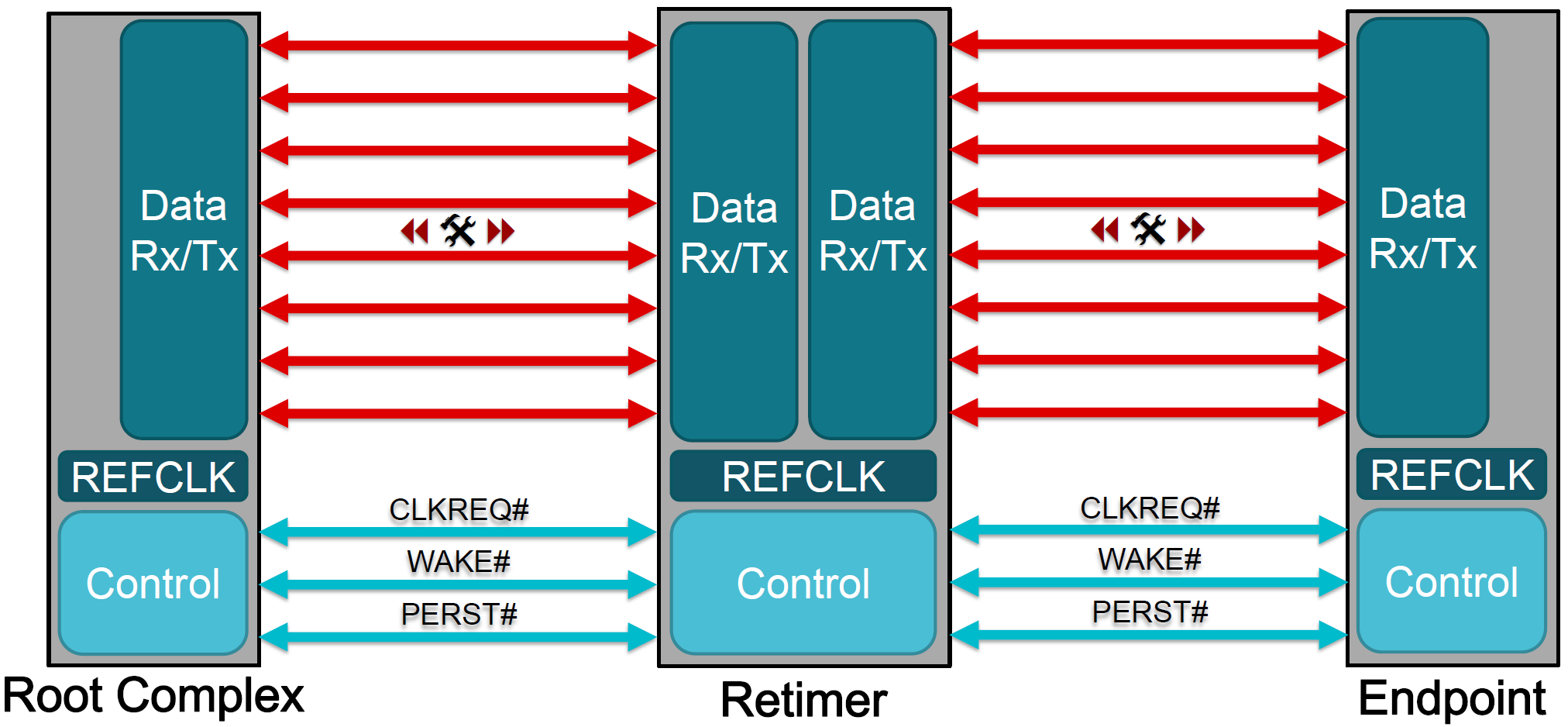

In the configuration state, a lane-to-lane deskew process takes place in which any misalignment in the data due to varying channel length is compensated for. The PCIe link width is also determined at this stage. At the end of this process, each lane is associated with a specific link number, and a lane number within that link. Figure 5-3 represents the configuration stage with red arrows showing the exchange of signals in order to align data signals. If there are multiple links, the PCIe connection as referred to as bifurcated. Because Figure 5-3 shows a single non-bifurcated connection, all lanes are assigned to link number 0. With bifurcation, the number of links will increase. For example, in the case of x8x8 (2 x 8 lane endpoints) bifurcation, the link number is 0 for the first 8 lanes and 1 for the next 8 lanes. In addition, the link can be split in two parts due to the PCIe retimer: root complex to the retimer and retimer to the endpoint as shown in Figure 5-3 with the retimer in the middle. The link on both sides of the retimer undergo link initialization separately.

After determining link width and lane numbers, the PCIe link can move into a number of states. The system in Figure 5-3 moves into what is called the L0 state, which is the normal operational state where data and packets are sent and received. Once the L0 state is reached, the root complex and endpoint can successfully communicate between each other. Alternatively, the PCIe link could transition into a number of low-power states or into another link training state called recovery.

Figure 5-3 PCIe Link

Configuration

Figure 5-3 PCIe Link

Configuration