SPRACT9 September 2020 – MONTH AM6526 , AM6528 , AM6546 , AM6548 , AM68 , AM68A , AM69 , AM69A , DRA829J , DRA829V , TDA4VM , TDA4VM-Q1

3 SW Tuning Algorithm

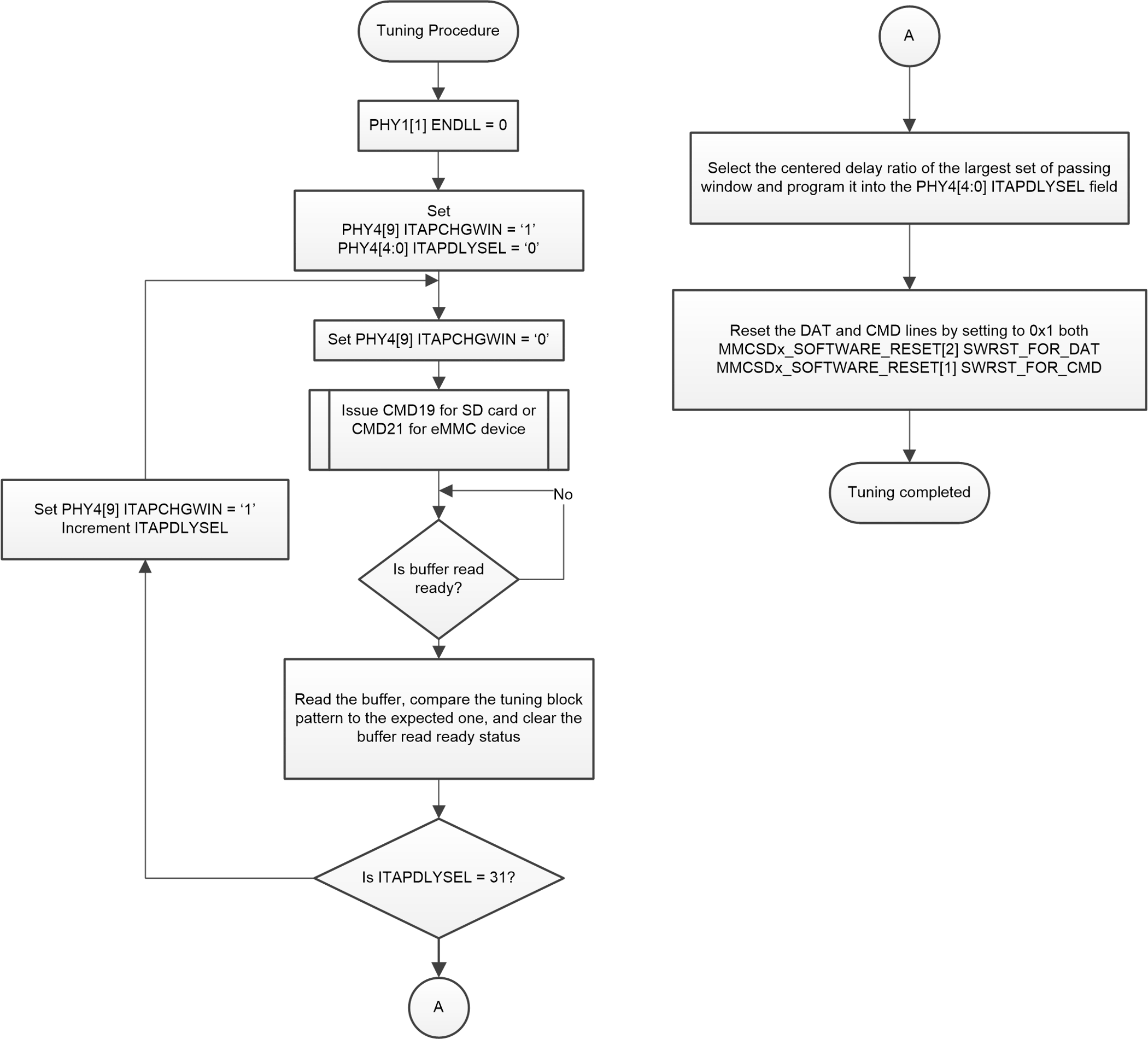

For software tuning, everything that would have been done automatically by the hardware module is now enabled via software coding. The software program will sequence through all 32 delay ratio elements, issue CMD19/CMD21 and record the pass and fail results at each ratio element. Then, the program will find the optimal delay ratio element for functionality use. Figure 3-1 describes the process in detail.

Figure 3-1 MMC SW Tuning Algorithm

Figure 3-1 MMC SW Tuning AlgorithmIf DLL is used (ENDLL = ‘1’), then the 32 ratio elements will constitute a whole clock cycle. Delaying the CLK by Ratio 32 will mean delaying the CLK by Ratio 0. As a result, the biggest passing window should be taken as the window that wrapped around from the end to the beginning of the delays. If DLL is not used (ENDLL = ‘0’), the biggest passing window should be taken as the window without the wraparound applied.

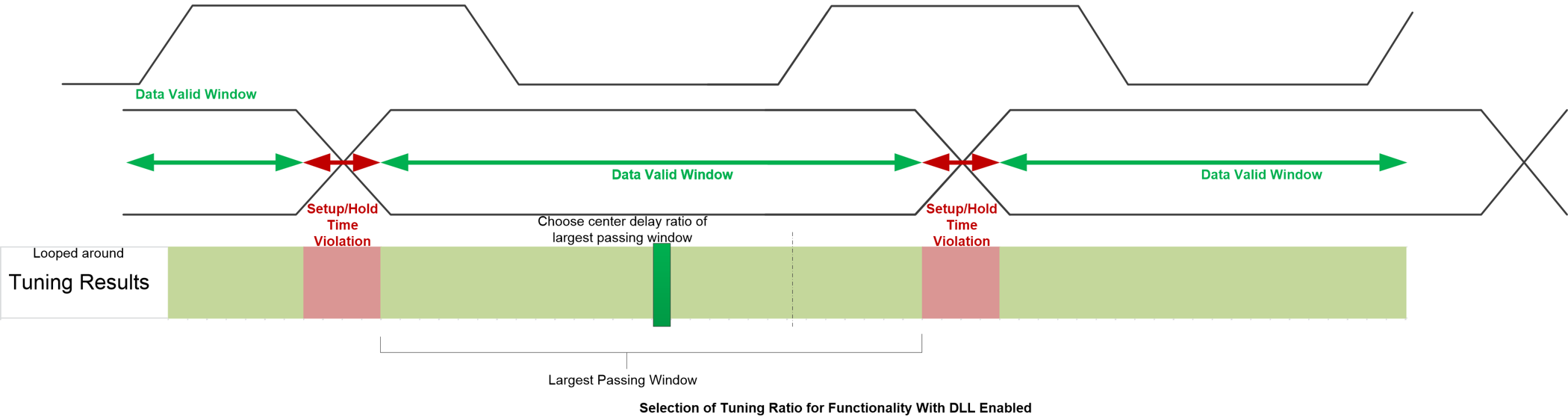

Figure 3-2 Setup Hold Time

Requirements

Figure 3-2 Setup Hold Time

Requirements Figure 3-3 Selection of Tuning Ratio for

Functionality With DLL Enabled

Figure 3-3 Selection of Tuning Ratio for

Functionality With DLL EnabledAs a safety precaution, software code should also implement a re-tuning mechanism to re-tune the delay module if the MMC functionality fails. This can be done by checking for data line status bits for errors. If errors occurred, re-execute the tuning sequence. Re-tuning should also be done at timer expiration by using the re-tuning functionality.