# UCC5870-Q1 30-A Isolated IGBT/SiC MOSFET Gate Driver with Advanced Protection Features for Automotive Applications

## 1 Features

- Split output driver provides 30-A peak source and 30-A peak sink currents

- Adjustable "on the fly" gate drive strength

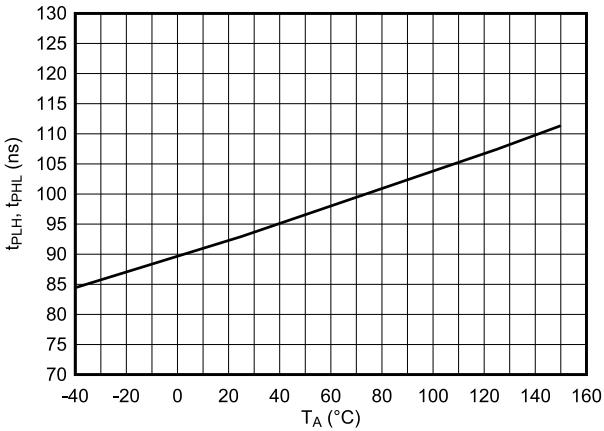

- Interlock and shoot-through protection with 150-ns(max) propagation delay and programmable minimum pulse rejection

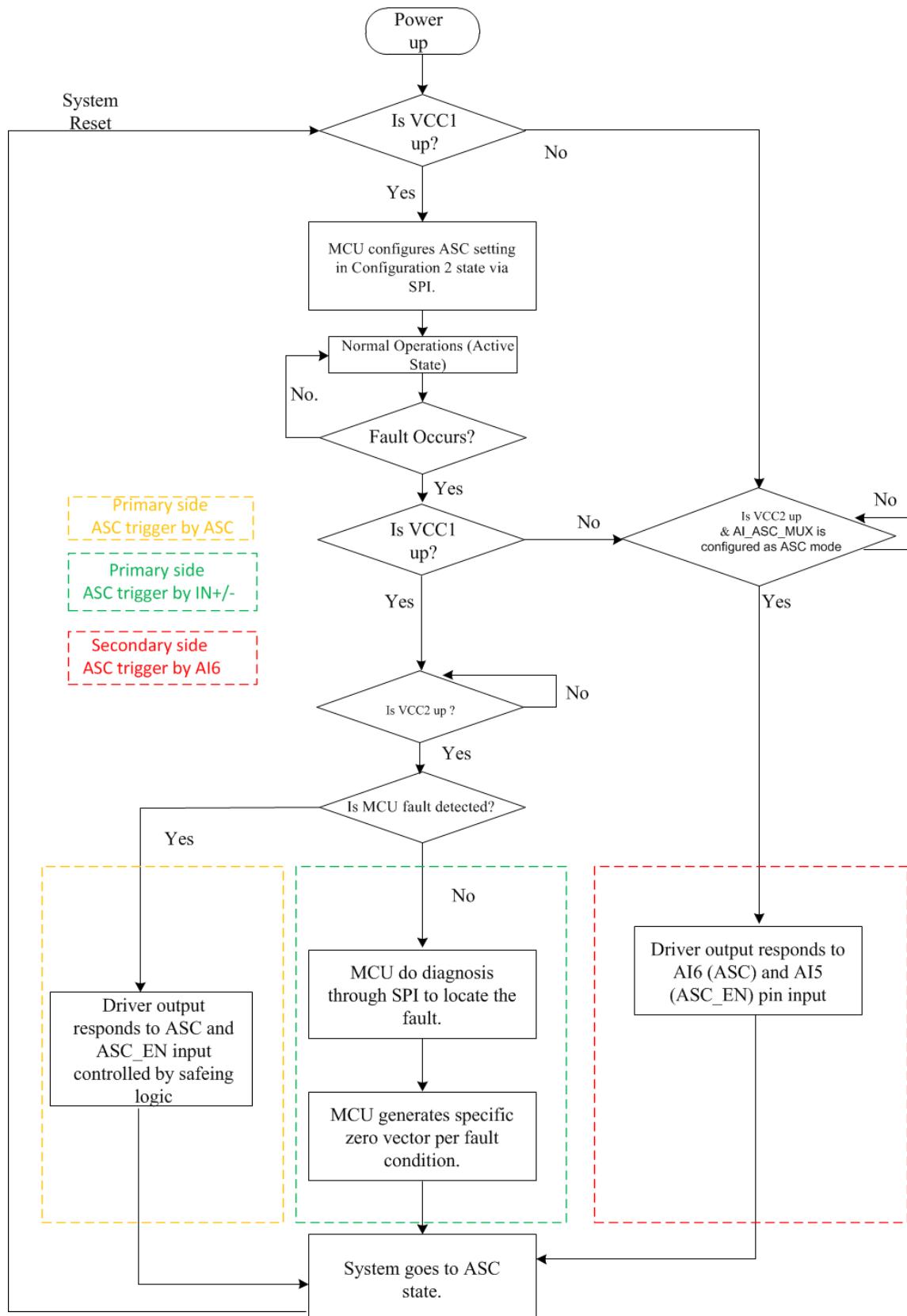

- Primary and Secondary side active short circuit (ASC) support

- Configurable power transistor protections

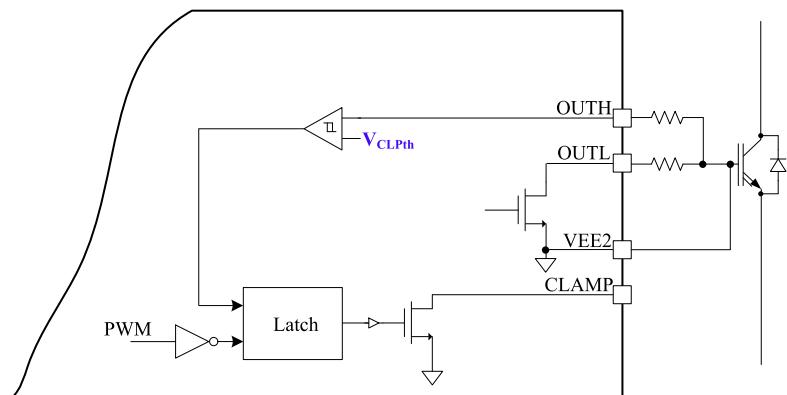

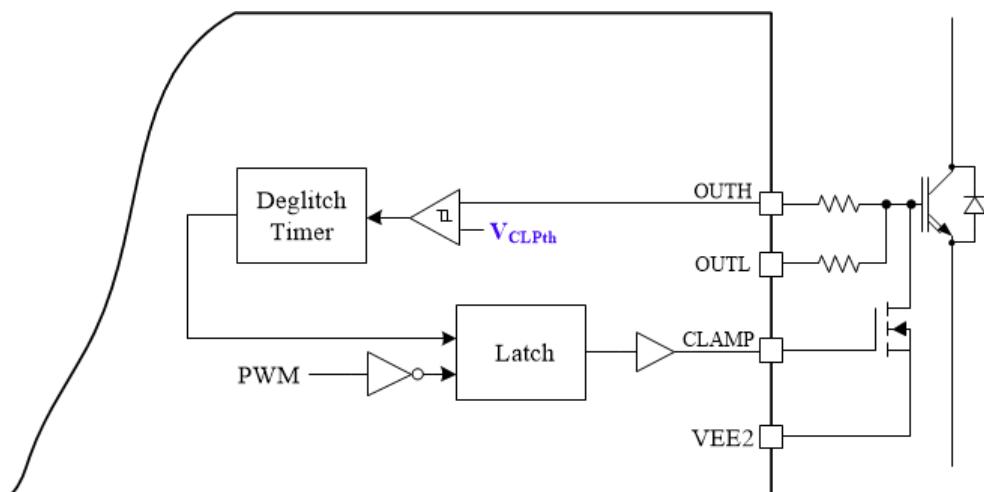

- DESAT based short circuit protection

- Shunt resistor based overcurrent and short circuit protection

- NTC based overtemperature protection

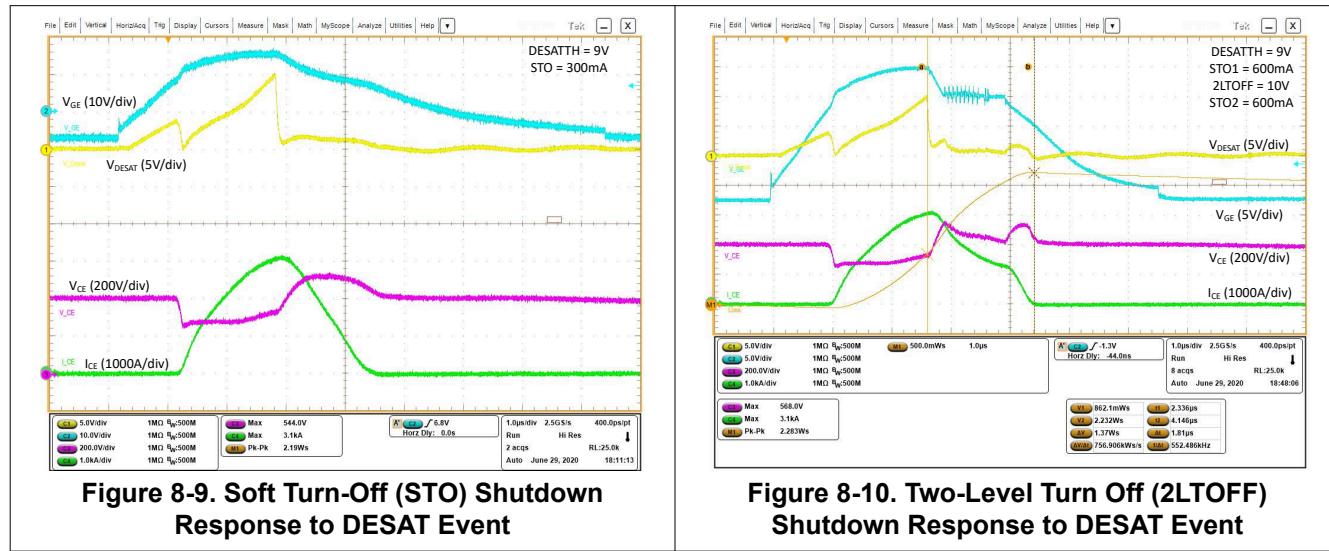

- Programmable soft turnoff (STO) and two-level turnoff (2LTOFF) during power transistor faults

- **Functional Safety-Compliant**

- Developed for functional safety applications

- Documentation available to aid ISO 26262 system design up to ASIL D

- Integrated diagnostics:

- Built-in self test (BIST) for protection comparators

- IN+ to transistor gate path integrity

- Power transistor threshold monitoring

- Internal clock monitoring

- Fault alarm (nFLT1) and warning (nFLT2) outputs

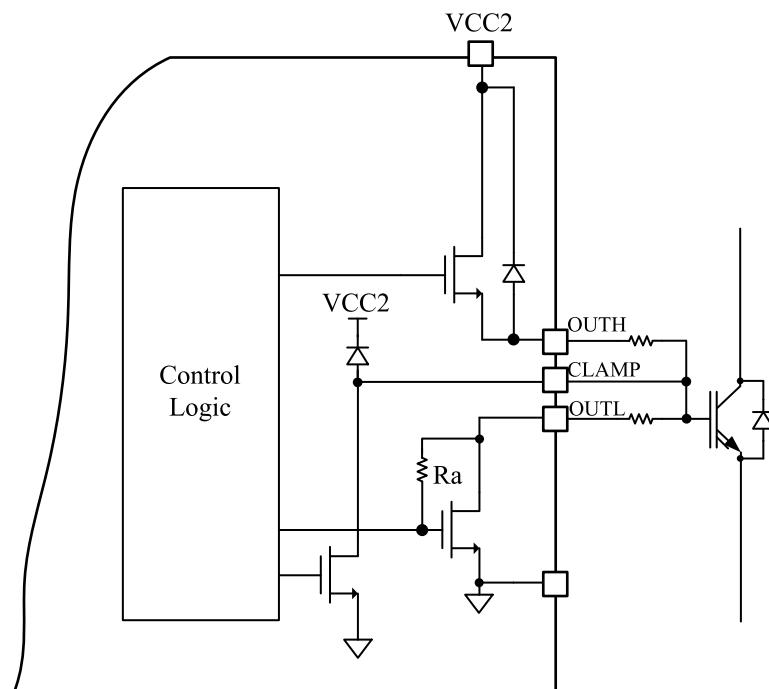

- Integrated 4-A active Miller clamp or optional external drive for Miller clamp transistor

- Advanced high voltage clamping control

- Internal and external supply undervoltage and overvoltage protection

- Active output pulldown and default low outputs with low supply or floating inputs

- Driver die temperature sensing and overtemperature protection

- 100-kV/μs minimum common mode transient immunity (CMTI) at  $V_{CM} = 1000$  V

- SPI based device reconfiguration, verification, supervision, and diagnosis

- Integrated 10-bit ADC for power transistor temperature, voltage, and current monitoring

- Safety-related certifications:

- 3750 –  $V_{RMS}$  isolation for 1 minute per UL1577 (planned)

- AEC-Q100 qualified with the following results:

- Device temperature grade 0:  $-40^{\circ}\text{C}$  to  $125^{\circ}\text{C}$  ambient operating temperature

- Device HBM ESD classification level 2

- Device CDM ESD classification level C4b

## 2 Applications

- HEV and EV traction inverter

- HEV and EV power modules

## 3 Description

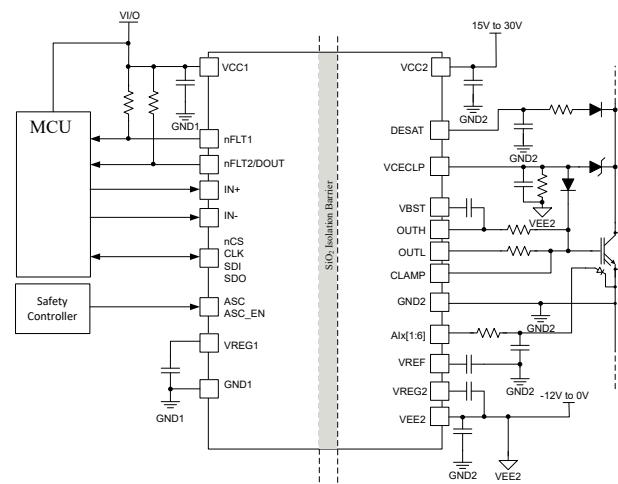

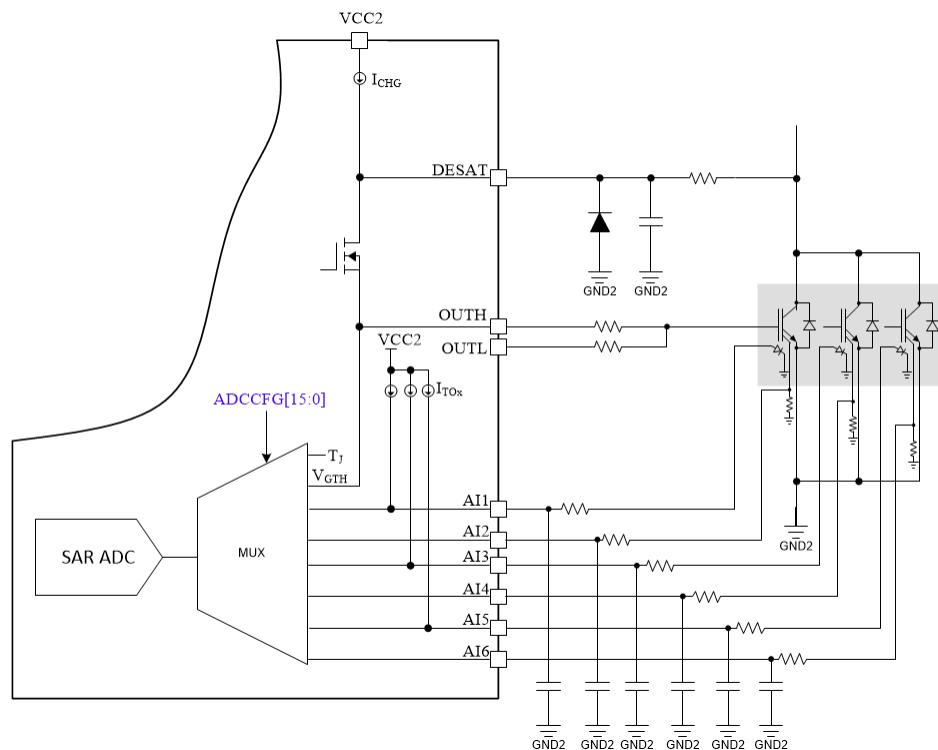

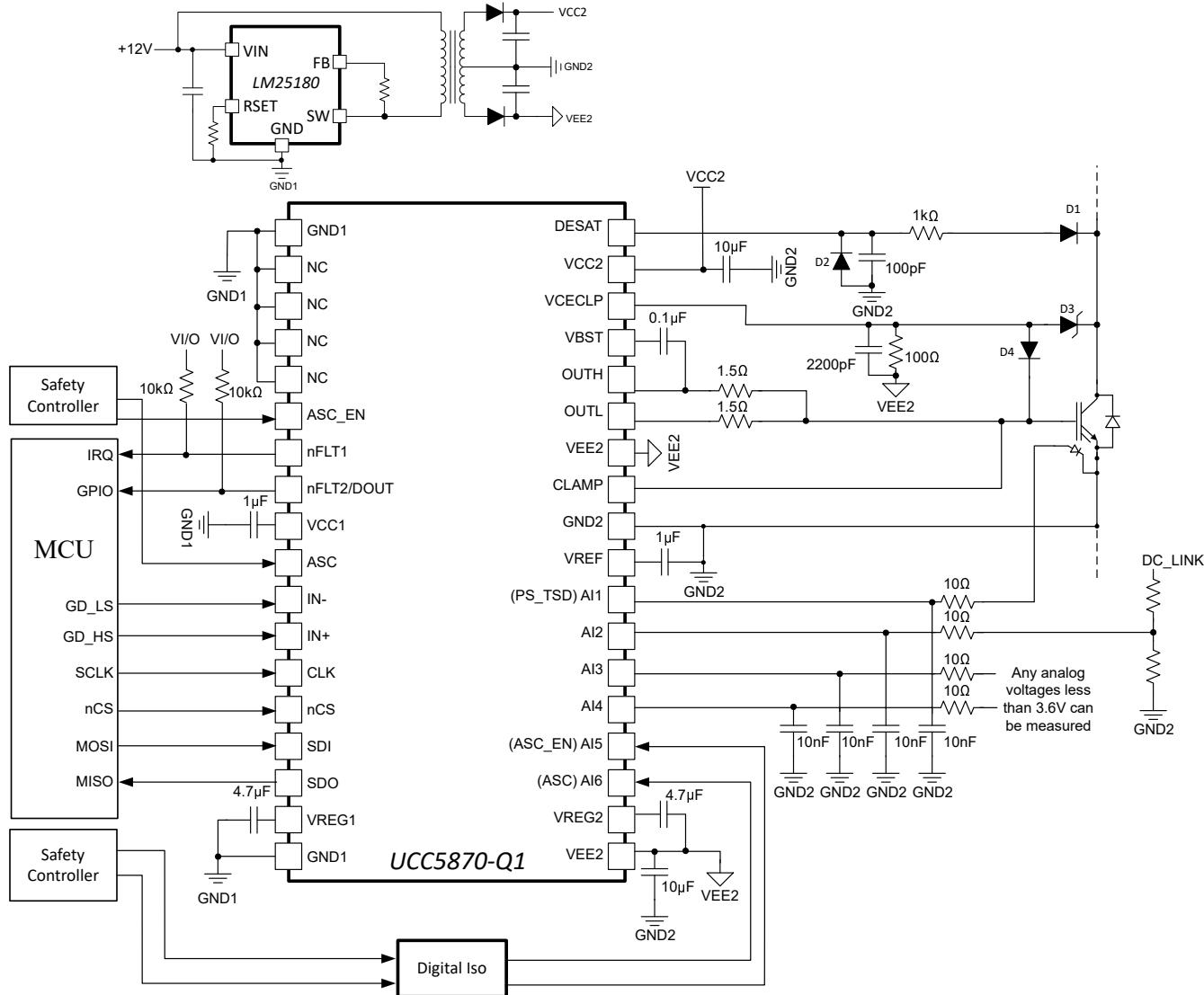

The UCC5870-Q1 device is an isolated, highly configurable single-channel gate driver targeted to drive high power SiC MOSFETs and IGBTs in EV/HEV applications. Power transistor protections, such as shunt-resistor-based overcurrent, NTC-based overtemperature, and DESAT detection, include selectable soft turn-off or two-level turn-off during these faults. To further reduce the application size, the UCC5870-Q1 integrates a 4-A active Miller clamp during switching, and an active gate pulldown while the driver is unpowered. An integrated 10-bit ADC enables monitoring of up to six analog inputs and the gate driver temperature for enhanced system management. Diagnostics and detection functions are integrated to simplify the design of ASIL-D compliant systems. The parameters and thresholds for these features are configurable using the SPI interface, which allows the device to be used with nearly any SiC MOSFET or IGBT.

## Device Information

| PART NUMBER <sup>(1)</sup> | PACKAGE   | BODY SIZE (NOM)  |

|----------------------------|-----------|------------------|

| UCC5870-Q1                 | SSOP (36) | 12.8 mm × 7.5 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

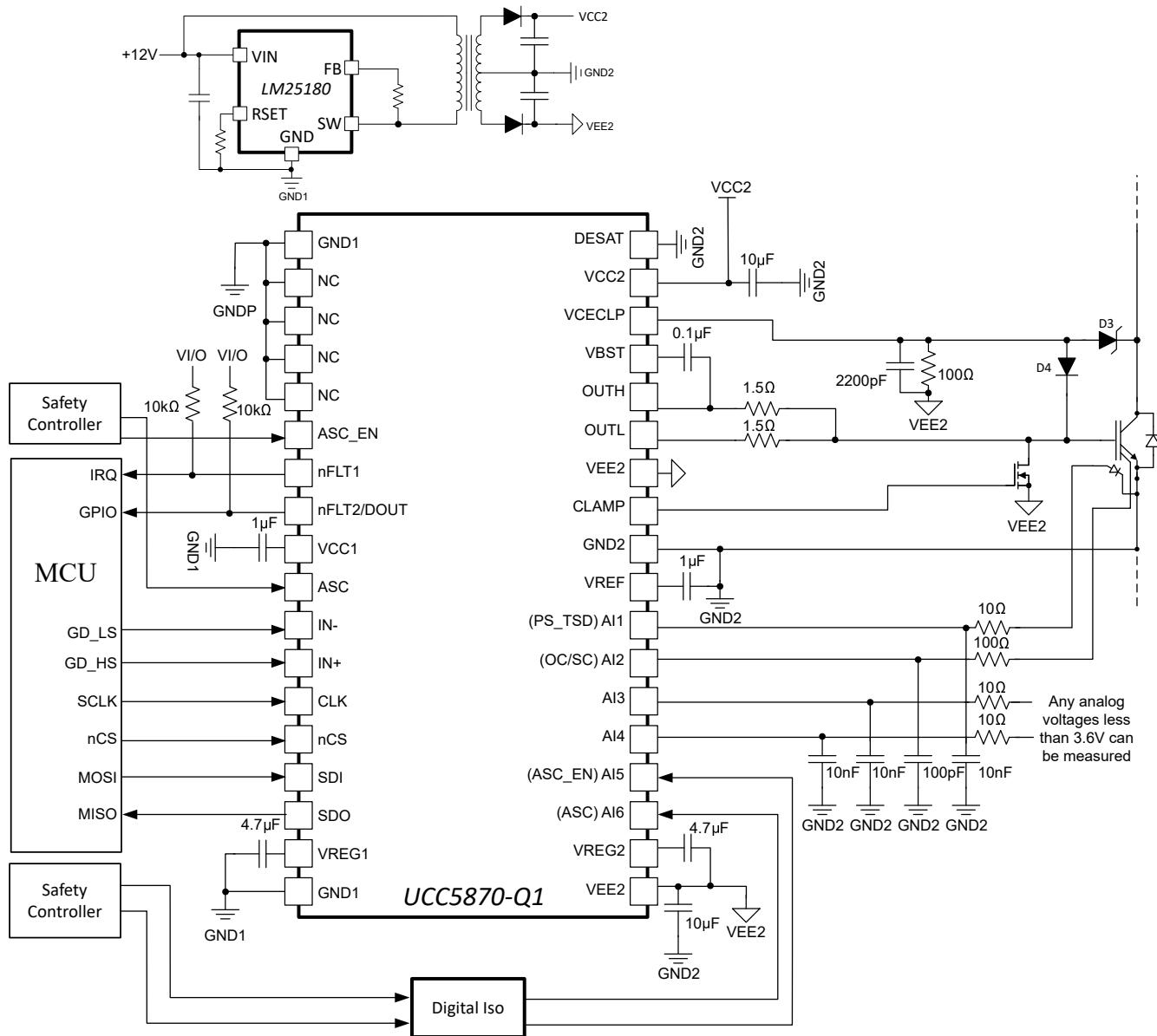

Simplified Schematic

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

## Table of Contents

|                                                |           |                                                                                                        |            |

|------------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------|------------|

| <b>1 Features</b> .....                        | <b>1</b>  | 8.1 Application Information.....                                                                       | <b>98</b>  |

| <b>2 Applications</b> .....                    | <b>1</b>  | 8.2 Typical Application Using Internal ADC<br>Reference and Power FET Sense Current<br>Monitoring..... | <b>100</b> |

| <b>3 Description</b> .....                     | <b>1</b>  | 8.3 Typical Application Using DESAT Power FET<br>Monitoring.....                                       | <b>104</b> |

| <b>4 Revision History</b> .....                | <b>2</b>  |                                                                                                        |            |

| <b>5 Pin Configuration and Functions</b> ..... | <b>3</b>  |                                                                                                        |            |

| <b>6 Specifications</b> .....                  | <b>6</b>  |                                                                                                        |            |

| 6.1 Absolute Maximum Ratings .....             | 6         | 9.1 VCC1 Power Supply.....                                                                             | <b>107</b> |

| 6.2 ESD Ratings .....                          | 6         | 9.2 VCC2 Power Supply.....                                                                             | <b>107</b> |

| 6.3 Recommended Operating Conditions .....     | 6         | 9.3 VEE2 Power Supply.....                                                                             | <b>107</b> |

| 6.4 Thermal Information .....                  | 7         | 9.4 VREF Supply (Optional).....                                                                        | <b>107</b> |

| 6.5 Power Ratings .....                        | 7         |                                                                                                        |            |

| 6.6 Insulation Specifications .....            | 7         | <b>10 Layout</b> .....                                                                                 | <b>108</b> |

| 6.7 Electrical Characteristics .....           | 8         | 10.1 Layout Guidelines.....                                                                            | <b>108</b> |

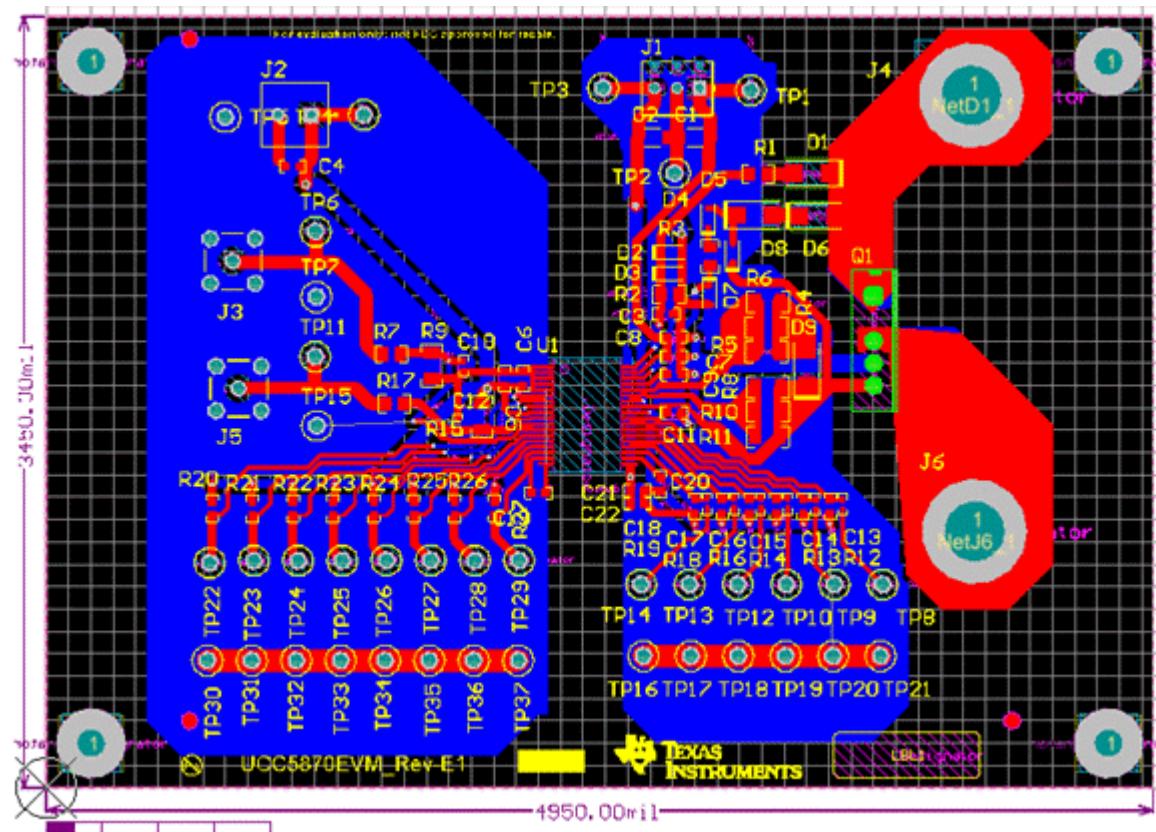

| 6.8 SPI Timing Requirements .....              | 15        | 10.2 Layout Example.....                                                                               | <b>109</b> |

| 6.9 Switching Characteristics .....            | 15        |                                                                                                        |            |

| 6.10 Typical Characteristics.....              | 17        | <b>11 Device and Documentation Support</b> .....                                                       | <b>110</b> |

| <b>7 Detailed Description</b> .....            | <b>21</b> | 11.1 Documentation Support.....                                                                        | <b>110</b> |

| 7.1 Overview.....                              | 21        | 11.2 Receiving Notification of Documentation Updates                                                   | <b>110</b> |

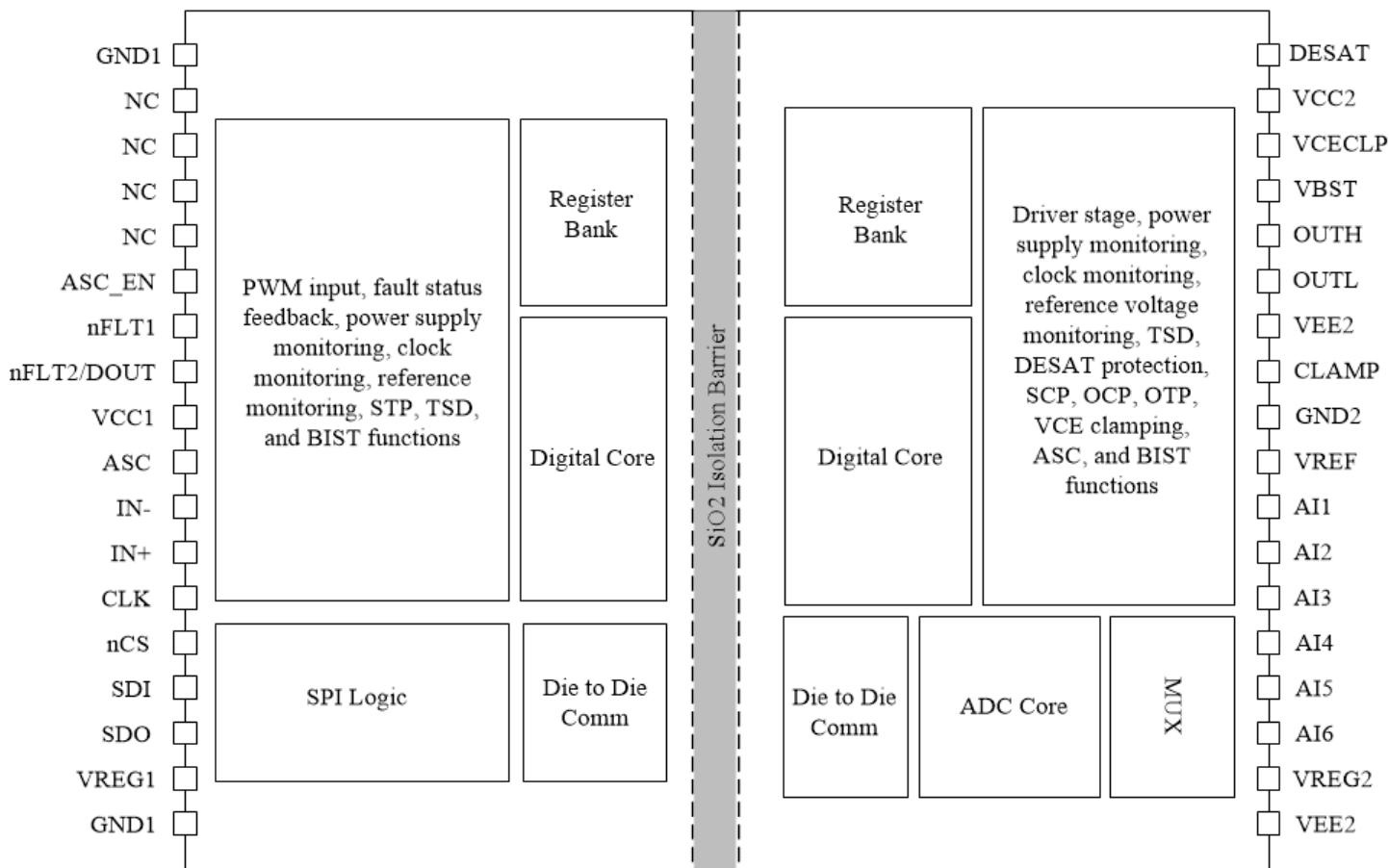

| 7.2 Functional Block Diagram.....              | 22        | 11.3 Support Resources.....                                                                            | <b>110</b> |

| 7.3 Feature Description.....                   | 22        | 11.4 Trademarks.....                                                                                   | <b>110</b> |

| 7.4 Device Functional Modes.....               | 52        | 11.5 Electrostatic Discharge Caution.....                                                              | <b>110</b> |

| 7.5 Programming.....                           | 54        | 11.6 Glossary.....                                                                                     | <b>110</b> |

| 7.6 Register Maps.....                         | 59        |                                                                                                        |            |

| <b>8 Applications and Implementation</b> ..... | <b>98</b> | <b>12 Mechanical, Packaging, and Orderable<br/>Information</b> .....                                   | <b>110</b> |

## 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| <b>Changes from Revision B (November 2020) to Revision C (July 2021)</b>                          | <b>Page</b> |

|---------------------------------------------------------------------------------------------------|-------------|

| • Updated peak currents to the typical value of 30 A and added functional safety information..... | <b>1</b>    |

| • Updated peak functional safety bullet in features.....                                          | <b>1</b>    |

| • Updated features with Q100 bullet.....                                                          | <b>1</b>    |

| • Removed values from VCECLP and DESAT components as these are customer selected.....             | <b>3</b>    |

| • Updated drive strength to 30 A to align with typical value.....                                 | <b>24</b>   |

| • Updated secondary side TSD behavior to clarify the functions operation.....                     | <b>44</b>   |

| • Added information about gate monitoring during secondary side ASC operation.....                | <b>44</b>   |

| • Corrected equation.....                                                                         | <b>49</b>   |

| • Corrected CONTROL2 bit name in list.....                                                        | <b>50</b>   |

| • Corrected CONTROL2 bit name.....                                                                | <b>54</b>   |

| • Corrected OVLO1_LEVEL selections.....                                                           | <b>59</b>   |

| • Updated DESATTH description for clarity.....                                                    | <b>59</b>   |

| • Updated SPI_FAULT description for clarity.....                                                  | <b>59</b>   |

| • Corrected OR_NFLT1_SEC and OR_NFLT2_SEC descriptions.....                                       | <b>59</b>   |

| • Removed graph to prevent confusion. ....                                                        | <b>98</b>   |

| <b>Changes from Revision A (June 2020) to Revision B (November 2020)</b>    | <b>Page</b> |

|-----------------------------------------------------------------------------|-------------|

| • Updated marketing status from Advance Information to initial release..... | <b>1</b>    |

## 5 Pin Configuration and Functions

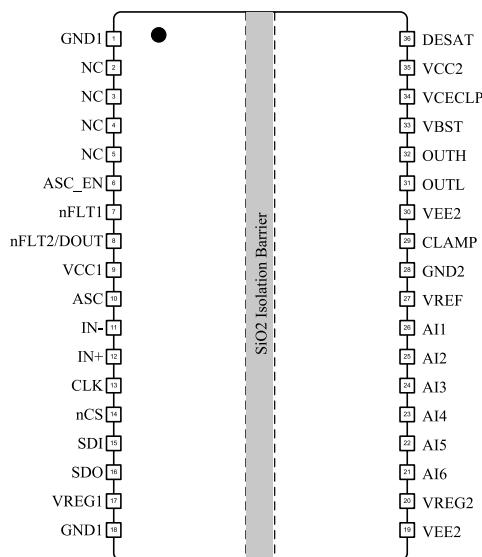

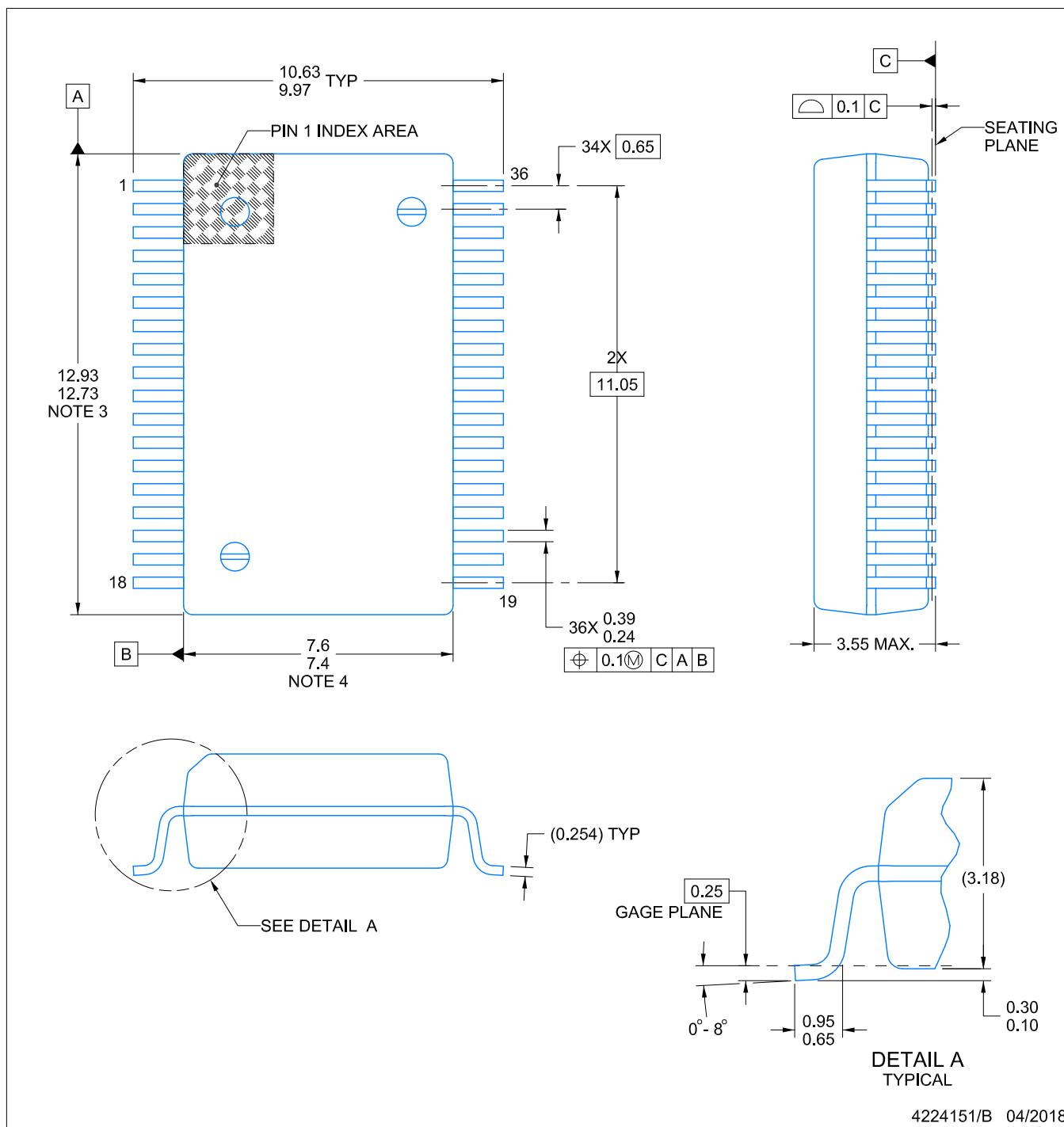

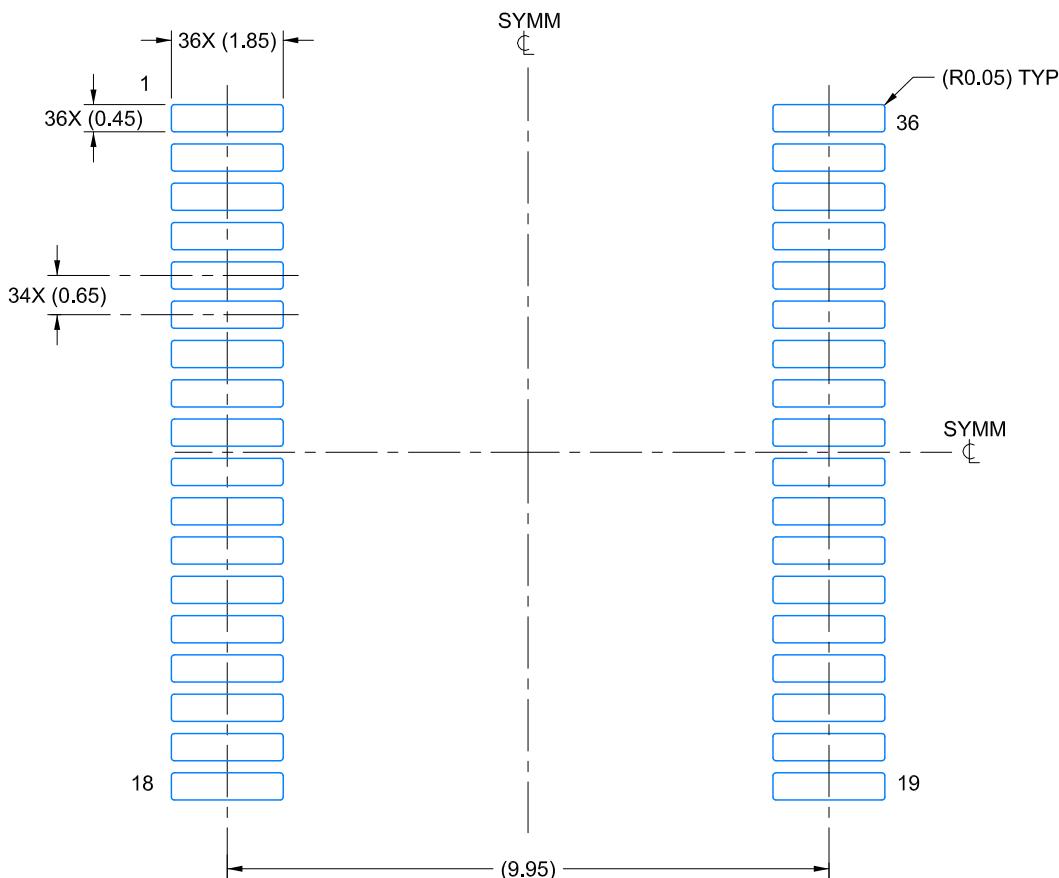

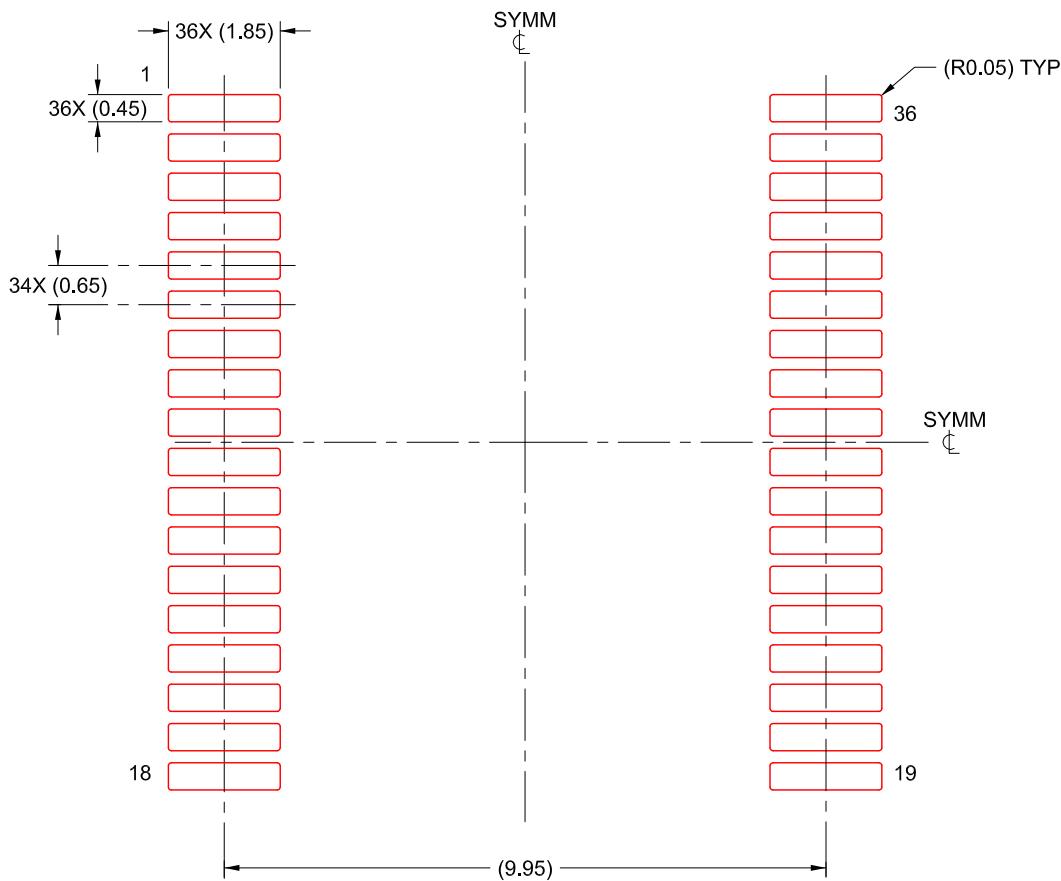

**Figure 5-1. (DWJ) 36-Pin SOIC Top View**

**Table 5-1. Pin Functions**

| PIN |                  | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME             |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1   | GND1             | G                  | Primary Side Ground. Connect all GND1 pins together and to the PCB ground plane on the primary side.                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2   | NC               | —                  | No internal connection. Connect to GND1.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3   | NC               | —                  | No internal connection. Connect to GND1.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4   | NC               | —                  | No internal connection. Connect to GND1.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5   | NC               | —                  | No internal connection. Connect to GND1.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

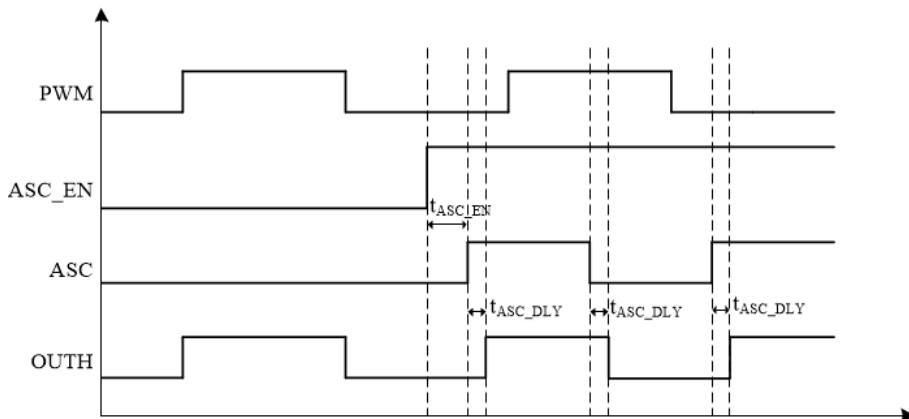

| 6   | ASC_EN           | I                  | Active Short Circuit Enable Input. ASC_EN enables the ASC function and forces the output of the driver to the state defined by the ASC input. If ASC is high, OUTH is pulled high. If ASC is low, OUTL is pulled low. See the <a href="#">Active Short Circuit (ASC)</a> section for additional details.                                                                                                                                                                                             |

| 7   | nFLT1            | O                  | Fault Indicator Output 1. nFLT1 is used to interrupt the host when a fault occurs. Faults that are unmasked pull nFLT1 low when the fault occurs. nFLT1 is high when all faults are either non-existent or masked. See the <a href="#">Fault and Warning Classification</a> section for additional details.                                                                                                                                                                                          |

| 8   | nFLT2/DOUT       | O                  | Fault Indicator Output 2. nFLT2 is used to interrupt the host when a fault occurs. Additionally, nFLT2 may be configured as DOUT to provide the host controller a PWM signal with a duty cycle relative to the ADC input of interest. Faults that are unmasked pull nFLT2 low when the fault occurs. nFLT2 is high when all faults are either non-existent or masked. See the <a href="#">Fault and Warning Classification</a> or <a href="#">DOUT Functionality</a> section for additional details. |

| 9   | V <sub>CC1</sub> | P                  | Primary Side Power Supply. Connect a 3V to 5.5V power supply to VCC1. Bypass VCC1 to GND1 with ceramic bulk capacitance as close to the VCC1 pin as possible. See the <a href="#">VCC1, VCC2, VEE2 Bypass Capacitors</a> section for more details on selecting the values.                                                                                                                                                                                                                           |

| 10  | ASC              | I                  | Active Short Circuit Control Input. ASC sets the drive state when ASC_EN is high. If ASC is high, OUTH is pulled high. If ASC is low, OUTL is pulled low. See the <a href="#">Active Short Circuit Support (ASC)</a> section for additional details.                                                                                                                                                                                                                                                 |

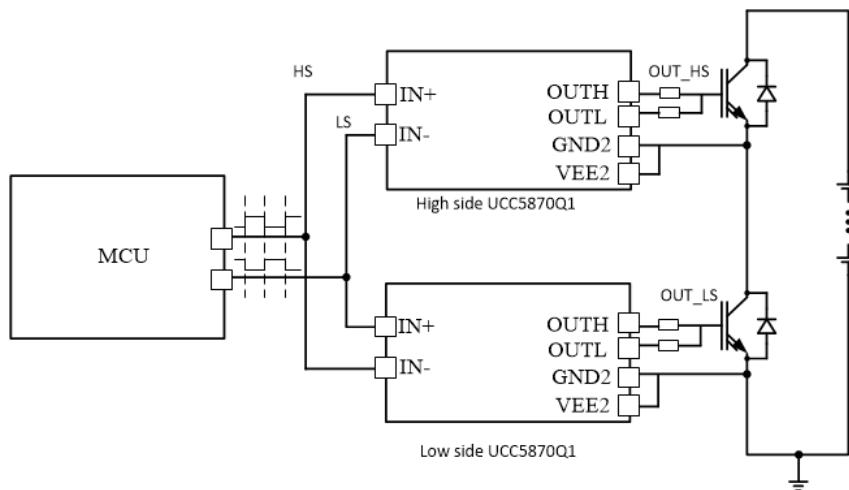

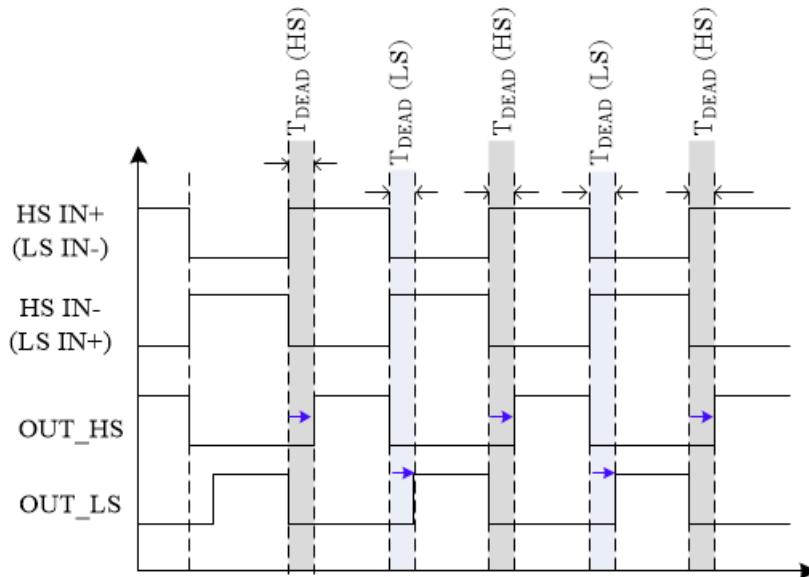

| 11  | IN-              | I                  | Negative PWM Input. IN- is connected to the IN+ from the opposite arm of the half-bridge. If IN+ and IN- overlap, the Shoot Through Protection (STP) fault is asserted. See the <a href="#">Shoot-Through Protection</a> section for additional details.                                                                                                                                                                                                                                             |

| 12  | IN+              | I                  | Positive PWM Input. IN+ drives the state of the driver output. With the driver enabled, when IN+ is high, OUTH is pulled high. When IN+ is low, OUTL is pulled low. Drive IN+ with a 1kHz to 50kHz PWM signal, with a logic level determined by the VCC1 voltage. IN+ is connected to the IN- of the opposite arm of the half-bridge. If IN+ and IN- overlap, the Shoot Through Protection (STP) fault is asserted. See the <a href="#">Shoot-Through Protection</a> section for additional details. |

| 13  | CLK              | I                  | SPI Clock. CLK is the clock signal for the main SPI interface. The SPI interface operates with clock rates up to 4MHz. See the <a href="#">SPI Communication</a> section for more details.                                                                                                                                                                                                                                                                                                           |

**Table 5-1. Pin Functions (continued)**

| PIN |                   | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|-------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME              |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 14  | nCS               | I                  | SPI Chip Selection Input. nCS is an active low input used to activate the SPI slave device. Drive nCS low during SPI communication. When nCS is high, the CLK and SDI inputs are ignored. See the <a href="#">SPI Communication</a> section for more details.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 15  | SDI               | I                  | SPI Data Input. SDI is the data input for the main SPI interface. Data is sampled on the falling edge of CLK, SDI must be in a stable condition to ensure proper communication. See the <a href="#">SPI Communication</a> section for more details.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 16  | SDO               | O                  | SPI Data Output. SDO is the data output for the main SPI interface. Data is clocked out on the falling edge of CLK, SDO is changed with a rising edge of CLK. See the <a href="#">SPI Communication</a> section for more details.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 17  | V <sub>REG1</sub> | P                  | Internal Voltage Regulator Output. VREG1 provides a 1.8V rail for internal primary-side circuits. Bypass VREG1 to GND1 with at least 4.7 $\mu$ F of ceramic capacitance. Do not put any additional load on VREG1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 18  | GND1              | G                  | Primary Side Ground. Connect all GND1 pins together and to the PCB ground plane on the primary side.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 19  | V <sub>EE2</sub>  | P                  | Secondary Negative Power Supply. Connect all VEE2 supply inputs together. Connect a -12V to 0V power supply to VEE2. The total voltage rail from VCC2 to VEE2 must not exceed 30V. Bypass VEE2 to GND2 with at least 1uF of ceramic capacitance as close to the VEE1 pin as possible. See the <a href="#">VCC1, VCC2, and VEE2 Bypass Capacitors</a> section for more details on selecting the values.                                                                                                                                                                                                                                                                              |

| 20  | V <sub>REG2</sub> | P                  | Internal voltage regulator output. VREG2 provides a 1.8V rail for internal secondary-side circuits. Bypass VREG2 to VEE2 with at least 4.7 $\mu$ F of ceramic capacitance. Do not put any additional load on VREG2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 21  | AI6               | I                  | Analog Input 6. AI6 is a multi-function input. It is configurable as an input to the internal ADC, a power FET current sense protection comparator input, and an ASC input for the secondary side. See the <a href="#">Integrated ADC for Front-End Analog (FEA) Signal Processing</a> section for details on configuring AI6 to be read by the ADC. See the <a href="#">Shunt Resistor based Overcurrent Protection (OCP) and Short Circuit Protection (SCP)</a> section for details on configuring AI6 as a power FET current sense protection input. Finally, see the <a href="#">Active Short Circuit Support (ASC)</a> section for details on configuring AI6 as an ASC input. |

| 22  | AI5               | I                  | Analog Input 5. AI5 is a multi-function input. It is configurable as an input to the internal ADC, a power FET over temperature protection comparator input, and an ASC_EN input for the secondary side. See the <a href="#">Integrated ADC for Front-End Analog (FEA) Signal Processing</a> section for details on configuring AI5 to be read by the ADC. See the <a href="#">Temperature Monitoring and Protection for the Power Transistors</a> section for details on configuring AI5 as a power FET over temperature protection input. Finally, see the <a href="#">Active Short Circuit Support (ASC)</a> section for details on configuring AI5 as an ASC_EN input.          |

| 23  | AI4               | I                  | Analog Input 4. AI4 is a multi-function input. It is configurable as an input to the internal ADC and a power FET current sense protection comparator input. See the <a href="#">Integrated ADC for Front-End Analog (FEA) Signal Processing</a> section for details on configuring AI4 to be read by the ADC. See the <a href="#">Shunt Resistor based Overcurrent Protection (OCP) and Short Circuit Protection (SCP)</a> section for details on configuring AI4 as a power FET current sense protection input.                                                                                                                                                                   |

| 24  | AI3               | I                  | Analog Input 3. AI3 is a multi-function input. It is configurable as an input to the internal ADC and a power FET current sense protection comparator input. See the <a href="#">Integrated ADC for Front-End Analog (FEA) Signal Processing</a> section for details on configuring AI3 to be read by the ADC. See the <a href="#">Temperature Monitoring and Protection for the Power Transistors</a> section for details on configuring AI3 as a power FET over temperature protection input.                                                                                                                                                                                     |

| 25  | AI2               | I                  | Analog Input 2. AI2 is a multi-function input. It is configurable as an input to the internal ADC and a power FET current sense protection comparator input. See the <a href="#">Integrated ADC for Front-End Analog (FEA) Signal Processing</a> section for details on configuring AI2 to be read by the ADC. See the <a href="#">Shunt Resistor based Overcurrent Protection (OCP) and Short Circuit Protection (SCP)</a> section for details on configuring AI2 as a power FET current sense protection input.                                                                                                                                                                   |

| 26  | AI1               | I                  | Analog Input 1. AI1 is a multi-function input. It is configurable as an input to the internal ADC and a power FET current sense protection comparator input. See the <a href="#">Integrated ADC for Front-End Analog (FEA) Signal Processing</a> section for details on configuring AI1 to be read by the ADC. See the <a href="#">Temperature Monitoring and Protection for the Power Transistors</a> section for details on configuring AI1 as a power FET over temperature protection input.                                                                                                                                                                                     |

| 27  | V <sub>REF</sub>  | P                  | Internal ADC Voltage Regulator Output. VREF provides an internal 4V, reference for the ADC. Bypass VREF to GND2 with at least 1uF of ceramic capacitance. If an external reference is desired, disable the internal VREF using the SPI register, and connect a 4V reference supply to VREF. Loads up to 5mA on VREF are allowed.                                                                                                                                                                                                                                                                                                                                                    |

| 28  | GND2              | G                  | Gate Drive Common Input. Connect GND2 to the power FET source/ IGBT emitter. All Alx inputs, VREF, and DESAT are referenced to GND2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

**Table 5-1. Pin Functions (continued)**

| PIN |                     | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|---------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME                |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 29  | CLAMP               | IO                 | Miller Clamp Input. The CLAMP input is used to hold the gate of the power FET strongly to VEE2 while the power FET is "off". CLAMP is configurable as an internal Miller clamp, or to drive an external clamping circuit. When using the internal clamping function, connect CLAMP directly to the power FET gate. When configured as an external clamp, connect CLAMP to the gate of an external pulldown MOSFET. See the <a href="#">Active Miller Clamp</a> section for additional details.                                                                                                                                                       |

| 30  | V <sub>EE2</sub>    | P                  | Secondary negative power supply. Connect all VEE2 supply inputs together. Connect a -12V to 0V power supply to VEE2. The total voltage rail from VCC2 to VEE2 must not exceed 30V. Bypass VEE2 to GND2 with at least 1uF of ceramic capacitance as close to the VEE2 pin as possible. Additional capacitance may be needed depending on the required drive current. See the <a href="#">VCC1, VCC2, VEE2 Bypass Capacitors</a> section for more details on selecting the values.                                                                                                                                                                     |

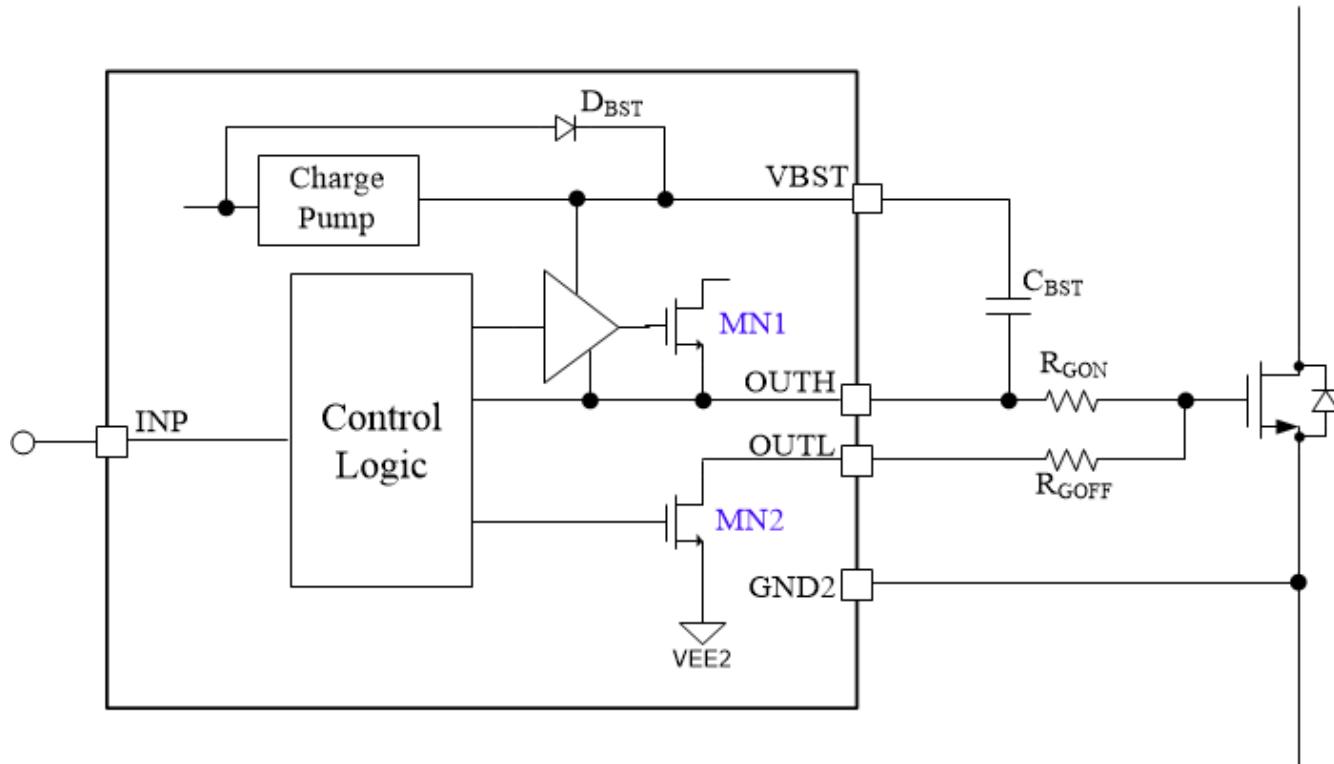

| 31  | OUTL                | O                  | Negative Gate Drive Voltage Output. When the driver is active, OUTL drives the gate of the power FET low when INP is low. Connect OUTL to the gate of the power FET through a gate resistor. The value of the gate resistor is chosen based on the slew rate required for the application. See the <a href="#">OUTH/ OUTL Outputs</a> section for details on choosing the gate resistor.                                                                                                                                                                                                                                                             |

| 32  | OUTH                | O                  | Positive Gate Drive Voltage Output. When the driver is active, OUTH drives the gate of the power FET high when INP is high. Connect OUTH to the gate of the power FET through a gate resistor. The value of the gate resistor is chosen based on the slew rate required for the application. See the <a href="#">OUTH/ OUTL Outputs</a> section for details on choosing the gate resistor.                                                                                                                                                                                                                                                           |

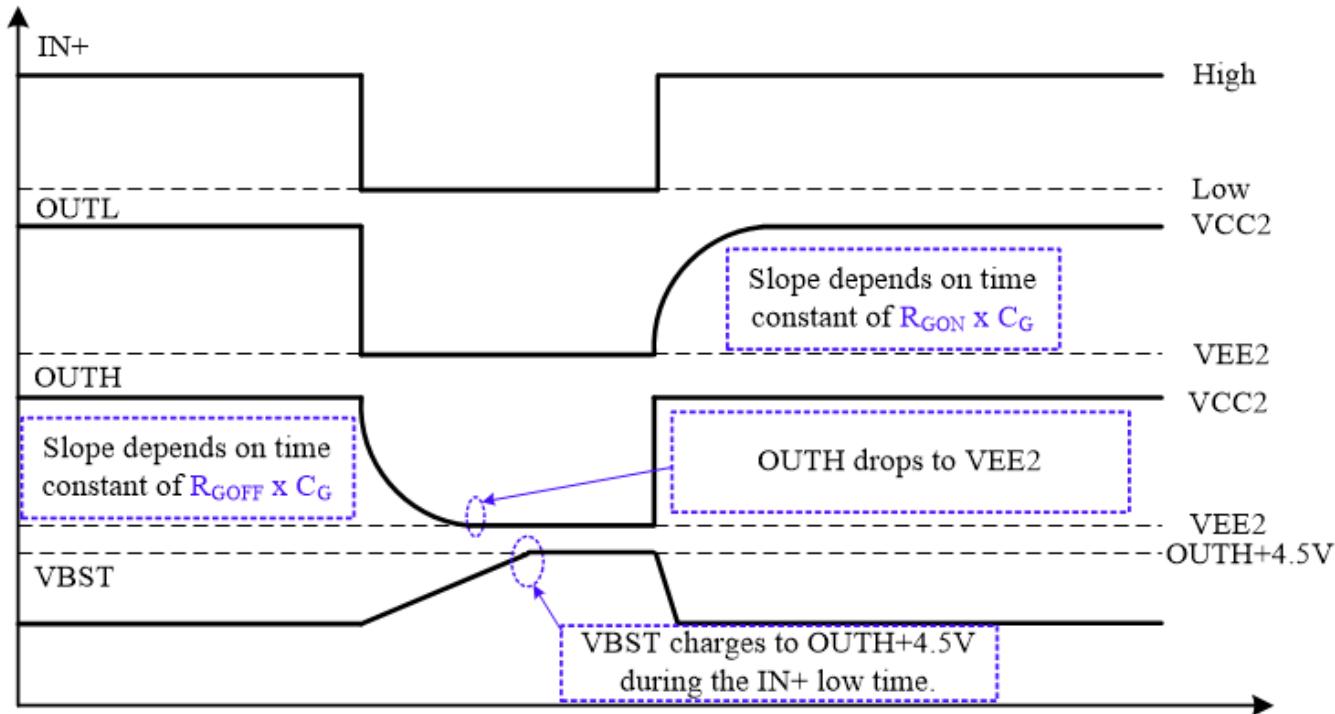

| 33  | V <sub>BST</sub>    | P                  | Bootstrap Supply. VBST supplies power for the OUTH drive. Connect a 0.1μF ceramic capacitor between VBST and OUTH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

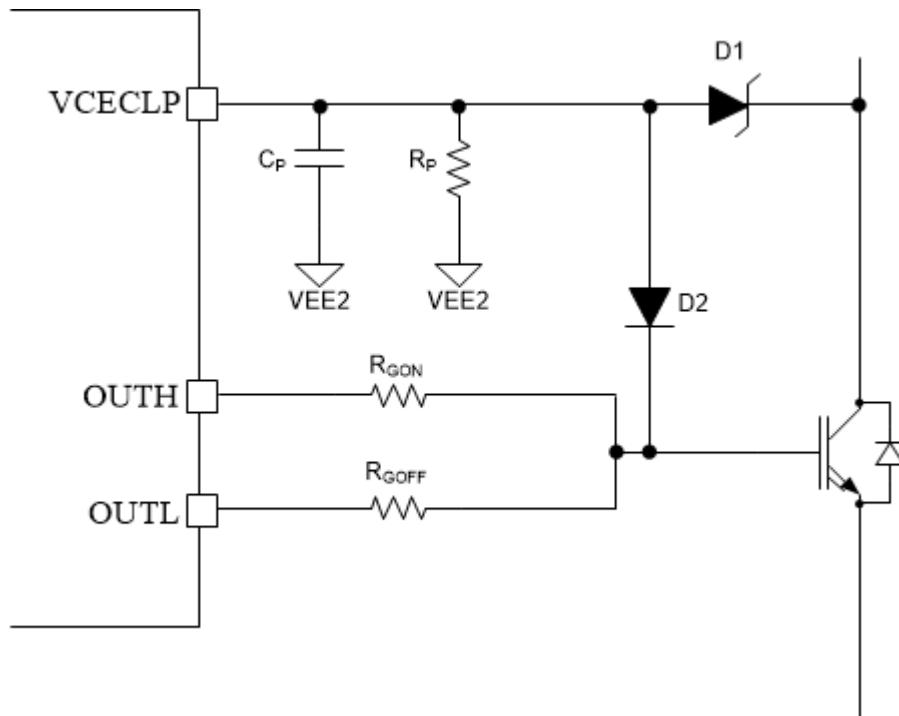

| 34  | V <sub>C ECLP</sub> | I                  | VCE Clamp Input. VCECLP clamps to a diode above the VCC2 rail and indicates a fault when the voltage at VCECLP is above the VCECLP <sub>th</sub> threshold. Bypass VCECLP to VEE2 with ceramic capacitor and, in parallel, connect a resistor. Additionally, connect VCECLP to the anode of a zener diode to the collector of the power FET. For details on selecting the values and ratings for the required components, see the <a href="#">VCECLP Input</a> section.                                                                                                                                                                              |

| 35  | V <sub>CC2</sub>    | P                  | Secondary Positive Power Supply. Connect a 15V to 30V power supply to VCC2. The total voltage rail from VCC2 to VEE2 must not exceed 30V. Bypass VCC2 to GND2 and VCC2 to VEE2 with bulk ceramic capacitance as close to the VCC2 pin as possible. Additional capacitance may be needed depending on the required drive current. See the <a href="#">VCC1, VCC2, VEE2 Bypass Capacitors</a> section for more details on selecting the values.                                                                                                                                                                                                        |

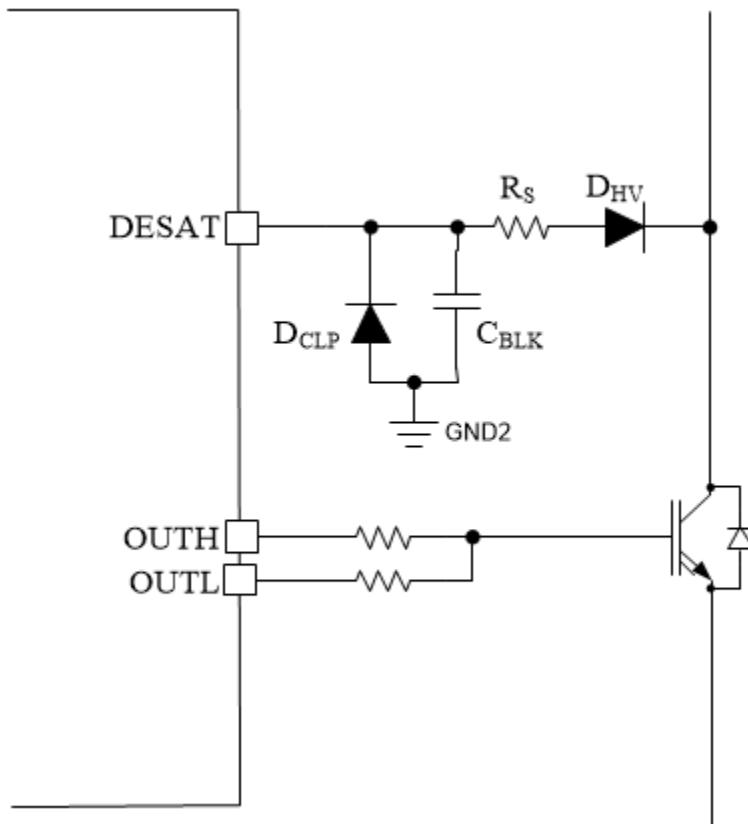

| 36  | DESAT               | I                  | Desaturation based Short Circuit Detection Input. DESAT is used to detect a short circuit in the power FET. Bypass DESAT to GND2 with a ceramic capacitor to program the DESAT blanking time. In parallel, connect a schottky diode with the cathode connected to the DESAT. Additionally, connect DESAT to a resistor to the anode of a diode to the collector of the power FET to adjust the DESAT protection threshold. DESAT detects a fault when the VCE voltage of the power FET exceeds the defined threshold while the power FET is on. See the <a href="#">DESAT based Short Circuit Protection (DESAT)</a> section for additional details. |

(1) P = Power, G = Ground, I = Input, O = Output, - = NA

## 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                      |                                                                                                          | MIN           | MAX           | UNIT |

|----------------------|----------------------------------------------------------------------------------------------------------|---------------|---------------|------|

| $V_{CC1}$            | Supply voltage primary side referenced to GND1                                                           | -0.3          | 6             | V    |

| $V_{CC2}$            | Positive supply voltage secondary side referenced to GND2                                                | -0.3          | 33            | V    |

| $V_{EE2}$            | Negative supply voltage output side referenced to GND2                                                   | -15           | 0.3           | V    |

| $V_{SUP2}$           | Total supply voltage output side ( $V_{CC2} - V_{EE2}$ )                                                 | -0.3          | 33            | V    |

| $V_{OUTH}, V_{OUTL}$ | Voltage on the driver output pins referenced to GND2                                                     | $V_{EE2}-0.3$ | $V_{CC2}+0.3$ | V    |

| $V_{IOP}$            | Voltage on IO pins (ASC, ASC_EN, CLK, IN+, IN-, nCS, nFLTx, SDI, SDO) on primary side referenced to GND1 | -0.3          | $V_{CC1}+0.3$ | V    |

| $V_{CLAMP}$          | Voltage on the Miller clamp pin referenced to GND2                                                       | $V_{EE2}-0.3$ | $V_{CC2}+0.3$ | V    |

| $V_{DESAT}$          | Voltage on DESAT referenced to GND2                                                                      | -0.3          | $V_{CC2}+0.3$ | V    |

| $V_{CECLP}$          | Voltage on VCECLP referenced to GND2                                                                     | $V_{EE2}-0.3$ | $V_{CC2}+0.3$ | V    |

| $V_{REG1}$           | Voltage on VREG1 referenced to GND1                                                                      | -0.3          | 2             | V    |

| $V_{REG2}$           | Voltage on VREG2 referenced to VEE2                                                                      | -0.3          | 2             | V    |

| $V_{REF}$            | Voltage on VREF referenced to GND2                                                                       | -0.3          | 5.5           | V    |

| $V_{BST}$            | Voltage on VBST referenced to OUTH                                                                       | -0.3          | 5.3           | V    |

| $V_{AI}$             | Voltage on the analog inputs referenced to GND2                                                          | -0.3          | 5.5           | V    |

| $T_J$                | Junction temperature                                                                                     | -40           | 150           | °C   |

| $T_{stg}$            | Storage temperature                                                                                      | -65           | 150           | °C   |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

### 6.2 ESD Ratings

|             |                         |                                                         | VALUE      | UNIT |

|-------------|-------------------------|---------------------------------------------------------|------------|------|

| $V_{(ESD)}$ | Electrostatic discharge | Human body model (HBM), per AEC Q100-002 <sup>(1)</sup> | $\pm 2000$ | V    |

|             |                         | Charged device model (CDM), per AEC Q100-011            | $\pm 750$  |      |

|             |                         | Corner pins (GND1 and VEE2)                             | $\pm 500$  |      |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|            |                                                               | MIN           | NOM           | MAX           | UNIT |

|------------|---------------------------------------------------------------|---------------|---------------|---------------|------|

| $V_{CC1}$  | Supply voltage input side                                     | 3             | 5.5           | 5.5           | V    |

| $V_{CC2}$  | Positive supply voltage secondary side ( $V_{CC2} - GND2$ )   | 15            | 30            | 30            | V    |

| $V_{EE2}$  | Negative supply voltage output side ( $V_{EE2} - GND2$ )      | -12           | 0             | 0             | V    |

| $V_{SUP2}$ | Total supply voltage output side ( $V_{CC2} - V_{EE2}$ )      | 15            | 30            | 30            | V    |

| $V_{IH}$   | High-level IO voltage (ASC, ASC_EN, IN+, IN-, nCS, SCLK, SDI) | $0.7*V_{CC1}$ | $V_{CC1}$     | $V_{CC1}$     | V    |

| $V_{IL}$   | Low-level IO voltage (ASC, ASC_EN, IN+, IN-, nCS, SCLK, SDI)  | 0             | $0.3*V_{CC1}$ | $0.3*V_{CC1}$ | V    |

| $I_{OHP}$  | Source current for primary side outputs (nFLTx, SDO)          |               |               | 5             | mA   |

| $I_{OLP}$  | Sink current for primary side outputs (nFLTx, SDO)            |               |               | 5             | mA   |

| $I_{OH}$   | Driver output source current from OUTH <sup>(1)</sup>         |               |               | 15            | A    |

| $I_{OL}$   | Driver output sink current into OUTL <sup>(1)</sup>           |               |               | 15            | A    |

| $V_{AI*}$  | Voltage on analog input (AI) pins referenced to GND2          | 0             | $V_{REF}+0.1$ | $V_{REF}+0.1$ | V    |

## 6.3 Recommended Operating Conditions (continued)

over operating free-air temperature range (unless otherwise noted)

|             |                                                                                 | MIN | NOM             | MAX | UNIT  |

|-------------|---------------------------------------------------------------------------------|-----|-----------------|-----|-------|

| $V_{VREG1}$ | Output voltage at VREG1 referenced to GND1 <sup>(2)</sup>                       |     | 1.8             |     | V     |

| $V_{VREG2}$ | Output voltage at VREG2 referenced to VEE2 <sup>(3)</sup>                       |     | 1.8             |     | V     |

| $V_{VBST}$  | Output voltage at VBST referenced to OUTH <sup>(4)</sup>                        |     | $V_{cc2} + 4.5$ |     | V     |

| $V_{VREF}$  | Voltage on the VREF pin vs GND2 <sup>(5)</sup>                                  | 0   | 4               | 4.1 | V     |

| CMTI        | Common mode transient immunity rating (dV/dt rate across the isolation barrier) |     |                 | 100 | kV/us |

| $f_{PWM}$   | PWM input frequency (IN+ and IN- pins)                                          |     |                 | 50  | kHz   |

| $f_{SPI}$   | SPI clock frequency                                                             |     |                 | 4   | MHz   |

| $T_J$       | Maximum junction temperature                                                    | -40 |                 | 150 | °C    |

| $t_{PWM}$   | PWM input pulse width (IN+ and IN- pins)                                        | 250 |                 |     | ns    |

(1) External gate resistor needs to be used to limit the max drive current to be not more than 15A.

(2) Connect a decoupling capacitor of 0.1uF+4.7uF between VREG1 and GND1. Do not connect external supply.

(3) Connect a decoupling capacitor of 0.1uF+4.7uF between VREG2 and VEE2. Do not connect external supply.

(4) Connect a decoupling capacitor of 100nF between VBST and OUTH. Do not connect external supply.

(5) Connect a decoupling capacitor of 1.0uF on the VREF pin.

## 6.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup> |                                              | UCC5870 | UNIT |

|-------------------------------|----------------------------------------------|---------|------|

|                               |                                              | DWJ     |      |

|                               |                                              | 36 SOIC |      |

| $R_{\theta JA}$               | Junction-to-ambient thermal resistance       | 50.6    | °C/W |

| $R_{\theta JC(\text{top})}$   | Junction-to-case (top) thermal resistance    | 17.5    | °C/W |

| $R_{\theta JB}$               | Junction-to-board thermal resistance         | 21.3    | °C/W |

| $\Psi_{JT}$                   | Junction-to-top characterization parameter   | 5.3     | °C/W |

| $\Psi_{JB}$                   | Junction-to-board characterization parameter | 20.2    | °C/W |

| $R_{\theta JC(\text{bot})}$   | Junction-to-case (bottom) thermal resistance | N/A     | °C/W |

(1) For more information about traditional and new thermal metrics, see the [Semiconductor and IC Package Thermal Metrics](#) application report.

## 6.5 Power Ratings

|          | PARAMETER                              | TEST CONDITIONS           | MIN | TYP | MAX | UNIT |

|----------|----------------------------------------|---------------------------|-----|-----|-----|------|

| $P_D$    | Maximum power dissipation (both sides) | $T_A = 125^\circ\text{C}$ |     |     | 500 | mW   |

| $P_{D1}$ | Maximum power dissipation (side-1)     | $T_A = 125^\circ\text{C}$ |     |     | 50  | mW   |

| $P_{D2}$ | Maximum power dissipation (side-2)     | $T_A = 125^\circ\text{C}$ |     |     | 450 | mW   |

## 6.6 Insulation Specifications

| PARAMETER                     |                                   | TEST CONDITIONS                                                   | SPECIFIC<br>ATION | UNIT |

|-------------------------------|-----------------------------------|-------------------------------------------------------------------|-------------------|------|

| <b>PACKAGE SPECIFICATIONS</b> |                                   |                                                                   |                   |      |

| CLR                           | External clearance <sup>(1)</sup> | Shortest terminal-to-terminal distance through air                | 8                 | mm   |

| CPG                           | External creepage <sup>(1)</sup>  | Shortest terminal-to-terminal distance across the package surface | 8                 | mm   |

| DTI                           | Distance through the insulation   | Minimum internal gap (internal clearance)                         | > 17              | μm   |

| CTI                           | Comparative tracking index        | DIN EN 60112 (VDE 0303-11); IEC 60112                             | 600               | V    |

|                               | Material group                    | According to IEC60664-1                                           | I                 |      |

## 6.6 Insulation Specifications (continued)

| PARAMETER            |                                                       | TEST CONDITIONS                                                                                                                                                                                   | SPECIFIC<br>ATION | UNIT             |

|----------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------|

| Overvoltage category |                                                       | Rated mains voltage $\leq 600$ V <sub>RMS</sub>                                                                                                                                                   | I-IV              |                  |

|                      |                                                       | Rated mains voltage $\leq 1000$ V <sub>RMS</sub>                                                                                                                                                  | I-III             |                  |

| <b>UL 1577</b>       |                                                       |                                                                                                                                                                                                   |                   |                  |

| C <sub>IO</sub>      | Barrier capacitance, input to output <sup>(2)</sup>   | V <sub>IO</sub> = 0.4 $\times$ sin (2 $\pi$ ft), f = 1 MHz                                                                                                                                        | 2                 | pF               |

| R <sub>IO</sub>      | Insulation resistance, input to output <sup>(2)</sup> | V <sub>IO</sub> = 500 V, T <sub>A</sub> = 25°C                                                                                                                                                    | 10 <sup>12</sup>  | Ω                |

|                      |                                                       | V <sub>IO</sub> = 500 V, 100°C $\leq$ T <sub>A</sub> $\leq$ 125°C                                                                                                                                 | 10 <sup>11</sup>  |                  |

|                      |                                                       | V <sub>IO</sub> = 500 V at T <sub>S</sub> = 150°C                                                                                                                                                 | 10 <sup>9</sup>   |                  |

| V <sub>ISO</sub>     | Withstand isolation voltage                           | V <sub>TEST</sub> = V <sub>ISO</sub> = 3750 V <sub>RMS</sub> , t = 60 s (qualification),<br>V <sub>TEST</sub> = 1.2 $\times$ V <sub>ISO</sub> = 4500 V <sub>RMS</sub> , t = 1 s (100% production) | 3750              | V <sub>RMS</sub> |

(1) Creepage and clearance requirements should be applied according to the specific equipment isolation standards of an application. Care should be taken to maintain the creepage and clearance distance of a board design to ensure that the mounting pads of the isolator on the printed-circuit board do not reduce this distance. Creepage and clearance on a printed-circuit board become equal in certain cases. Techniques such as inserting grooves, ribs, or both on a printed-circuit board are used to help increase these specifications.

(2) All pins on each side of the barrier tied together creating a two-pin device.

## 6.7 Electrical Characteristics

Over recommended operating conditions unless otherwise noted.

| PARAMETER                   | TEST CONDITIONS                                                          | MIN             | TYP  | MAX  | UNIT |

|-----------------------------|--------------------------------------------------------------------------|-----------------|------|------|------|

| <b>POWER SUPPLY</b>         |                                                                          |                 |      |      |      |

| V <sub>IT+</sub><br>(UVLO1) | UVLO threshold of V <sub>CC1</sub> rising                                | UVOV1_LEVEL = 0 | 2.6  | 2.75 | 2.9  |

| V <sub>IT+</sub><br>(UVLO1) | UVLO threshold of V <sub>CC1</sub> rising                                | UVOV1_LEVEL = 1 | 4.5  | 4.65 | 4.8  |

| V <sub>IT-</sub><br>(UVLO1) | UVLO threshold of V <sub>CC1</sub> falling                               | UVOV1_LEVEL = 0 | 2.3  | 2.45 | 2.6  |

| V <sub>IT-</sub><br>(UVLO1) | UVLO threshold of V <sub>CC1</sub> falling                               | UVOV1_LEVEL = 1 | 4.2  | 4.35 | 4.5  |

| V <sub>HYS</sub><br>(UVLO1) | UVLO threshold hysteresis of V <sub>CC1</sub>                            |                 | 0.30 |      | V    |

| t <sub>UVLO1</sub>          | VCC1 UVLO detection deglitch time                                        |                 | 20   |      | μs   |

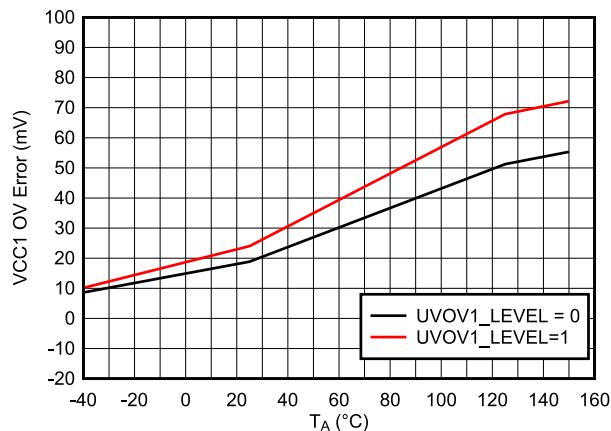

| V <sub>IT-</sub><br>(OVLO1) | OVLO threshold of V <sub>CC1</sub> falling                               | UVOV1_LEVEL = 0 | 3.7  | 3.85 | 4.0  |

| V <sub>IT-</sub><br>(OVLO1) | OVLO threshold of V <sub>CC1</sub> falling                               | UVOV1_LEVEL = 1 | 5.2  | 5.35 | 5.5  |

| V <sub>IT+</sub><br>(OVLO1) | OVLO threshold of V <sub>CC1</sub> rising                                | UVOV1_LEVEL = 0 | 4.0  | 4.15 | 4.3  |

| V <sub>IT+</sub><br>(OVLO1) | OVLO threshold of V <sub>CC1</sub> rising                                | UVOV1_LEVEL = 1 | 5.5  | 5.65 | 5.8  |

| V <sub>HYS</sub><br>(OVLO1) | OVLO threshold hysteresis of V <sub>CC1</sub>                            |                 | 0.30 |      | V    |

| t <sub>OVLO1</sub>          | VCC1 OVLO detection deglitch time                                        |                 | 20   |      | μs   |

| V <sub>IT+</sub><br>(UVLO2) | UVLO threshold voltage of V <sub>CC2</sub> rising with reference to GND2 | UVLO2TH = 00b   | 15.2 | 16   | 16.8 |

|                             |                                                                          | UVLO2TH = 01b   | 13.3 | 14   | 14.7 |

|                             |                                                                          | UVLO2TH = 10b   | 11.4 | 12   | 12.6 |

|                             |                                                                          | UVLO2TH = 11b   | 9.5  | 10   | 10.5 |

## 6.7 Electrical Characteristics (continued)

Over recommended operating conditions unless otherwise noted.

| PARAMETER             |                                                                    | TEST CONDITIONS                            | MIN    | TYP | MAX    | UNIT      |

|-----------------------|--------------------------------------------------------------------|--------------------------------------------|--------|-----|--------|-----------|

| $V_{IT^-}$<br>(UVLO2) | UVLO threshold voltage of $V_{CC2}$ falling with reference to GND2 | UVLO2TH = 00b                              | 14.25  | 15  | 15.75  | V         |

|                       |                                                                    | UVLO2TH = 01b                              | 12.35  | 13  | 13.65  | V         |

|                       |                                                                    | UVLO2TH = 10b                              | 10.45  | 11  | 11.55  | V         |

|                       |                                                                    | UVLO2TH = 11b                              | 8.55   | 9   | 9.45   | V         |

| $V_{HYS}$<br>(UVLO2)  | UVLO threshold voltage hysteresis of $V_{CC2}$                     |                                            |        | 1   |        | V         |

| $t_{UVLO2}$           | VCC2 UVLO detection deglitch time                                  |                                            |        | 20  |        | $\mu$ s   |

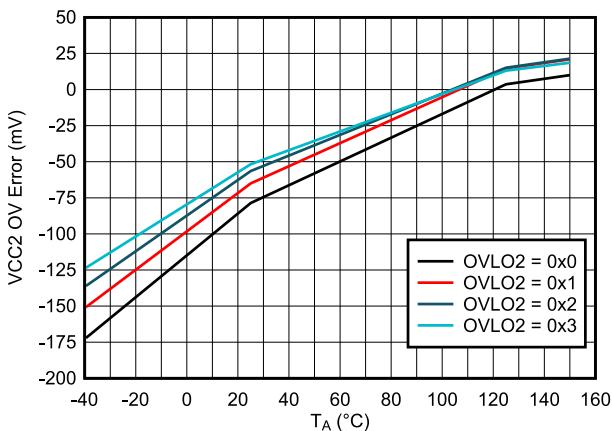

| $V_{IT^-}$<br>(OVLO2) | OVLO threshold voltage of $V_{CC2}$ falling with reference to GND2 | OVLO2TH = 00b                              | 21.85  | 23  | 24.15  | V         |

|                       |                                                                    | OVLO2TH = 01b                              | 19.95  | 21  | 22.05  | V         |

|                       |                                                                    | OVLO2TH = 10b                              | 18.05  | 19  | 19.95  | V         |

|                       |                                                                    | OVLO2TH = 11b                              | 16.15  | 17  | 17.85  | V         |

| $V_{IT^+}$<br>(OVLO2) | OVLO threshold voltage of $V_{CC2}$ rising with reference to GND2  | OVLO2TH = 00b                              | 22.8   | 24  | 25.2   | V         |

|                       |                                                                    | OVLO2TH = 01b                              | 20.9   | 22  | 23.1   | V         |

|                       |                                                                    | OVLO2TH = 10b                              | 19     | 20  | 21     | V         |

|                       |                                                                    | OVLO2TH = 11b                              | 17.1   | 18  | 18.9   | V         |

| $V_{HYS}$<br>(OVLO2)  | OVLO threshold voltage hysteresis of $V_{CC2}$                     |                                            |        | 1   |        | V         |

| $t_{OVLO2}$           | VCC2 OVLO detection blanking time                                  |                                            |        | 20  |        | $\mu$ s   |

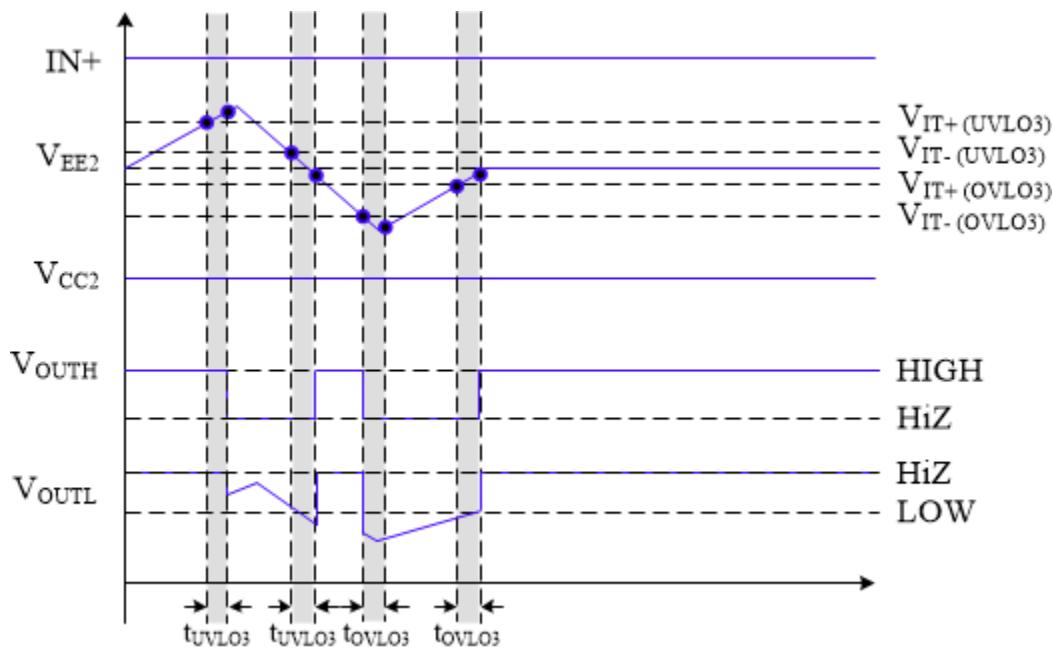

| $V_{IT^-}$<br>(UVLO3) | UVLO threshold voltage of $V_{EE2}$ falling with reference to GND2 | UVLO3TH = 00b                              | -3.15  | -3  | -2.85  | V         |

|                       |                                                                    | UVLO3TH = 01b                              | -5.25  | -5  | -4.75  | V         |

|                       |                                                                    | UVLO3TH = 10b                              | -8.4   | -8  | -7.6   | V         |

|                       |                                                                    | UVLO3TH = 11b                              | -10.5  | -10 | -9.5   | V         |

| $V_{IT^+}$<br>(UVLO3) | UVLO threshold voltage of $V_{EE2}$ rising with reference to GND2  | UVLO3TH = 00b                              | -2.1   | -2  | -1.9   | V         |

|                       |                                                                    | UVLO3TH = 01b                              | -4.2   | -4  | -3.8   | V         |

|                       |                                                                    | UVLO3TH = 10b                              | -7.35  | -7  | -6.65  | V         |

|                       |                                                                    | UVLO3TH = 11b                              | -9.45  | -9  | -8.55  | V         |

| $V_{HYS}$<br>(UVLO3)  | UVLO threshold voltage hysteresis of $V_{EE2}$                     |                                            |        | 1   |        | V         |

| $t_{UVLO3}$           | VEE2 UVLO detection blanking time                                  |                                            |        | 20  |        | $\mu$ s   |

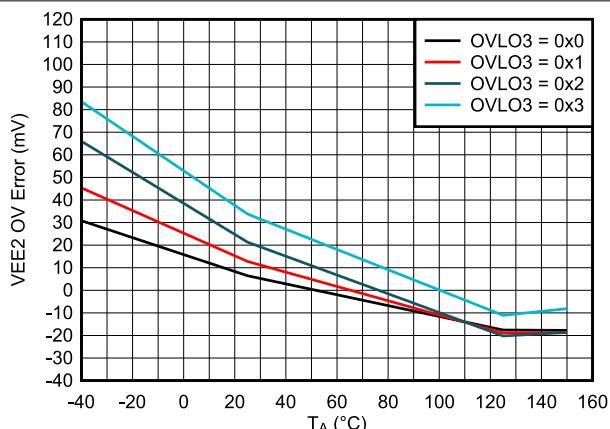

| $V_{IT^+}$<br>(OVLO3) | OVLO threshold voltage of $V_{EE2}$ rising with reference to GND2  | OVLO3TH = 00b                              | -5.25  | -5  | -4.75  | V         |

|                       |                                                                    | OVLO3TH = 01b                              | -7.35  | -7  | -6.65  | V         |

|                       |                                                                    | OVLO3TH = 10b                              | -10.5  | -10 | -9.5   | V         |

|                       |                                                                    | OVLO3TH = 11b                              | -12.6  | -12 | -11.4  | V         |

| $V_{IT^-}$<br>(OVLO3) | OVLO threshold voltage of $V_{EE2}$ falling with reference to GND2 | OVLO3TH = 00b                              | -6.3   | -6  | -5.7   | V         |

|                       |                                                                    | OVLO3TH = 01b                              | -8.4   | -8  | -7.6   | V         |

|                       |                                                                    | OVLO3TH = 10b                              | -11.55 | -11 | -10.45 | V         |

|                       |                                                                    | OVLO3TH = 11b                              | -13.65 | -13 | -12.35 | V         |

| $V_{HYS(OVLO3)}$      | OVLO threshold voltage hysteresis of $V_{EE2}$                     |                                            |        | 1   |        | V         |

| $t_{OVLO3}$           | VEE2 OVLO detection blanking time                                  |                                            |        | 20  |        | $\mu$ s   |

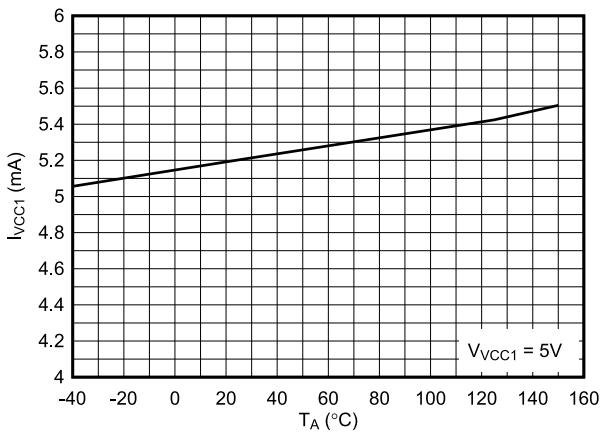

| $I_{QVCC1}$           | Quiescent Current of $V_{CC1}$                                     | No switching, $VCC1 = 5V$                  |        |     | 7.7    | mA        |

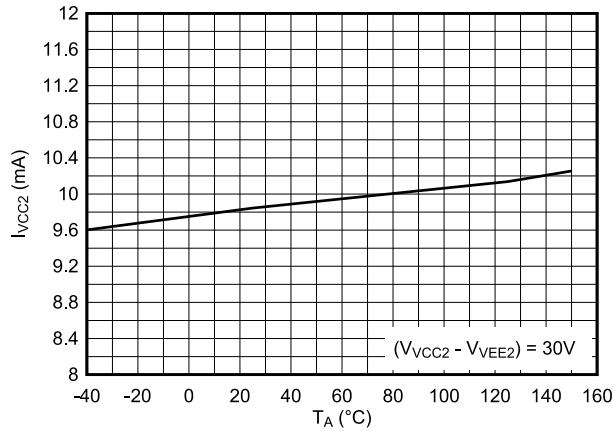

| $I_{QVCC2}$           | Quiescent Current of $V_{CC2}$                                     | No switching, $VCC2 = 20V$ , $VEE2 = -10V$ |        |     | 15     | mA        |

| $I_{QVEE2}$           | Quiescent Current of $VEE2$                                        | No switching, $VCC2 = 20V$ , $VEE2 = -10V$ |        |     | 15     | mA        |

| $t_{RP(VCC1)}$        | Slew rate of $V_{CC1}$                                             |                                            |        | 0.1 |        | $V/\mu$ s |

| $t_{RP(VCC2)}$        | Slew rate of $V_{CC2}$                                             |                                            |        | 0.1 |        | $V/\mu$ s |

## 6.7 Electrical Characteristics (continued)

Over recommended operating conditions unless otherwise noted.

| PARAMETER           | TEST CONDITIONS                                                             | MIN                                                      | TYP               | MAX           | UNIT      |

|---------------------|-----------------------------------------------------------------------------|----------------------------------------------------------|-------------------|---------------|-----------|

| $t_{RP(VEE2)}$      | Slew rate of $V_{EE2}$                                                      |                                                          |                   | 0.1           | $V/\mu s$ |

| <b>LOGIC IO</b>     |                                                                             |                                                          |                   |               |           |

| $V_{IH}$            | Input-high threshold voltage of primary IO (IN+, IN-, ASC, and ASC_EN)      | Input rising, $V_{CC1} = 3.3V$                           |                   | $0.7*V_{CC1}$ | V         |

|                     | Input-high threshold voltage of secondary IO in ASC mode (AI5, and AI6)     | Input rising, $V_{REF}=4V$                               |                   | 3.0           | V         |

| $V_{IL}$            | Input-low threshold voltage of primary IO (IN+, IN-, ASC, and ASC_EN)       | $V_{CC1} = 3.3V$                                         |                   | $0.3*V_{CC1}$ | V         |

|                     | Input-low input-threshold voltage of secondary IO in ASC mode (AI5 and AI6) | Input falling                                            |                   | 1.5           | V         |

| $V_{HYS(IN)}$       | Input hysteresis voltage of primary IO (IN+, IN-, ASC, and ASC_EN)          | $V_{CC1}=3.3V$                                           |                   | $0.1*V_{CC1}$ | V         |

|                     | Input hysteresis voltage of secondary IO in ASC mode (AI5, and AI6)         |                                                          |                   | 0.5           | V         |

| $I_{LI}$            | Leakage current on the input IO pins ASC, ASC_EN, IN+, IN-, CLK, and SDI    | $V_{IO} = GND1$ , $V_{IO}$ is the voltage on IO pins     |                   | 5             | $\mu A$   |

|                     | Leakage current on nCS                                                      | $V_{IO} = V_{CC1}$ , $V_{IO}$ is the voltage on IO pins  |                   | 5             | $\mu A$   |

| $R_{PUI}$           | Pullup resistance for nCS                                                   |                                                          | 40                | 100           | $k\Omega$ |

| $R_{PDI}$           | Pulldown resistance for ASC, ASC_EN, IN+, IN-, CLK, and SDI                 |                                                          | 40                | 100           | $k\Omega$ |

|                     | Pulldown resistance for AI5 and AI6 in ASC mode                             |                                                          | 800               | 1200          | $k\Omega$ |

| $V_{OH}$            | Output logic-high voltage (SDO)                                             | 4.5mA output current, $V_{CC1} = 5V$                     | $0.9*V_{CC1}$     |               | V         |

| $V_{OL}$            | Output logic-low voltage (nFLT1, nFLT2, and SDO)                            | 4.5mA sink current, $V_{CC1} = 5V$                       |                   | $0.1*V_{CC1}$ | V         |

| $f_{DOUT}$          | Output frequency of DOUT pin                                                | FREQ_DOUT = 00b                                          | 13.9              |               | $kHz$     |

|                     |                                                                             | FREQ_DOUT = 01b                                          | 27.8              |               | $kHz$     |

|                     |                                                                             | FREQ_DOUT = 10b                                          | 55.7              |               | $kHz$     |

|                     |                                                                             | FREQ_DOUT = 11b                                          | 111.4             |               | $kHz$     |

| $D_{DOUT}$          | Duty of DOUT                                                                | $V_{AI^*} = 0.36 V$                                      | 10                |               | %         |

|                     |                                                                             | $V_{AI^*} = 1.8 V$                                       | 50                |               | %         |

|                     |                                                                             | $V_{AI^*} = 3.24 V$                                      | 90                |               | %         |

| $I_{LO}$            | Leakage current on pin nFLT*                                                | $nFLT^* = HiZ$ , $V_{CC1}$ on nFLT* pin                  | -5                | 5             | $\mu A$   |

|                     | Leakage current on pin SDO                                                  | $nCS = 1$                                                | -5                | 5             | $\mu A$   |

| $R_{PVO}$           | Pullup resistance for pin nFLT*                                             |                                                          | 40                | 100           | $k\Omega$ |

| <b>DRIVER STAGE</b> |                                                                             |                                                          |                   |               |           |

| $V_{OUTH}$          | High-level output voltage (OUT and OUTH)                                    | $I_{OUT} = -100 mA$                                      | $V_{CC2} - 0.033$ |               | V         |

| $V_{OUTL}$          | Low-level output voltage (OUT and OUTL)                                     | $I_{OUT} = 100 mA$                                       |                   | 33            | $mV$      |

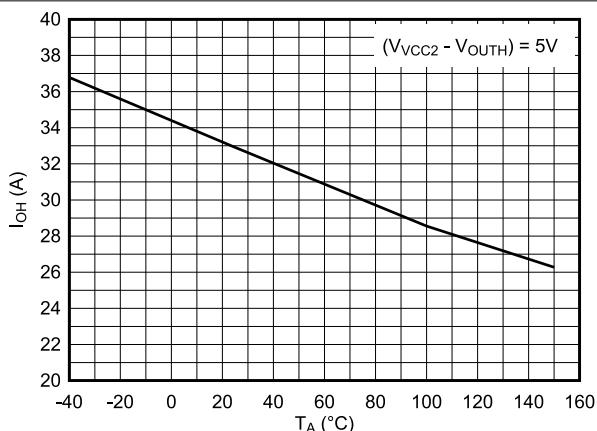

| $I_{OUTH}$          | Gate driver high output current                                             | $IN+= high$ , $IN- = low$ , $V_{CC2} - V_{OUTH} = 5 V$   | 15                |               | A         |

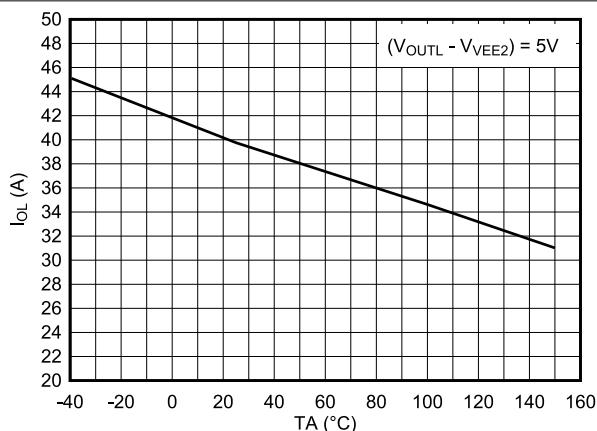

| $I_{OUTL}$          | Gate driver low output current                                              | $IN- = low$ , $IN + = high$ , $V_{OUTL} - V_{EE2} = 5 V$ | 15                |               | A         |

## 6.7 Electrical Characteristics (continued)

Over recommended operating conditions unless otherwise noted.

| PARAMETER                      |                                                                | TEST CONDITIONS                                                                                               | MIN  | TYP | MAX   | UNIT     |

|--------------------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------|-----|-------|----------|

| $I_{STO}$                      | Driver low output current during SC and OC faults              | VOUTL - VEE2 = 6 V and STO_CURR = 00b, 100°C to 150°C                                                         | 0.24 | 0.3 | 0.36  | A        |

|                                |                                                                | VOUTL - VEE2 = 6 V and STO_CURR = 01b, 100°C to 150°C                                                         | 0.48 | 0.6 | 0.72  | A        |

|                                |                                                                | VOUTL - VEE2 = 6 V and STO_CURR = 10b, 100°C to 150°C                                                         | 0.72 | 0.9 | 1.08  | A        |

|                                |                                                                | VOUTL - VEE2 = 6 V and STO_CURR = 11b, 100°C to 150°C                                                         | 0.96 | 1.2 | 1.44  | A        |

| ACTIVE MILLER CLAMP            |                                                                |                                                                                                               |      |     |       |          |

| $V_{CLP}$                      | Low-level clamp voltage (internal Miller clamp)                | $I_{CLP} = 100 \text{ mA}$                                                                                    |      |     | 100   | mV       |

|                                | Miller clamp current                                           | $MCLPTH = 11b, V_{CLAMP} = V_{EE2} + 4 \text{ V}$                                                             | 3.2  |     |       | A        |

| $V_{CLPTH}$                    | Clamp threshold voltage with reference to VEE2                 | MCLPTH = 00b                                                                                                  | 1.2  | 1.5 | 1.8   | V        |

|                                |                                                                | MCLPTH = 01b                                                                                                  | 1.6  | 2   | 2.5   | V        |

|                                |                                                                | MCLPTH = 10b                                                                                                  | 2.25 | 3   | 3.75  | V        |

|                                |                                                                | MCLPTH = 11b                                                                                                  | 3    | 4   | 5     | V        |

| $V_{ECLP}$                     | CLAMP output voltage in external Miller clamp mode             |                                                                                                               | 4.5  | 5   | 5.5   | V        |

| $R_{ECLP\_PD}$                 | CLAMP pulldown resistance in external Miller clamp mode        |                                                                                                               |      | 13  |       | $\Omega$ |

| $R_{ECLP\_PU}$                 | CLAMP pull-up resistance in external Miller clamp mode         |                                                                                                               |      | 13  |       | $\Omega$ |

| SHORT CIRCUIT CLAMPING         |                                                                |                                                                                                               |      |     |       |          |

| $V_{CLP-OUT}$                  | Clamping voltage ( $V_{OUTH} - V_{CC2}, V_{CLAMP} - V_{CC2}$ ) | $IN+ = \text{high}, IN- = \text{low}, t_{CLP} = 10\text{us}, I_{OUTH} \text{ or } I_{CLAMP} = 500 \text{ mA}$ |      | 0.8 | 1.6   | V        |

| ACTIVE PULLDOWN                |                                                                |                                                                                                               |      |     |       |          |

| $V_{OUTSD}$                    | Active shut-down voltage on OUTL                               | $I_{OUTL} = 30\text{mA}, V_{CC2} = \text{open}$                                                               |      |     | 1.55  | V        |

| $V_{OUTSD}$                    | Active shut-down voltage on OUTL                               | $I_{OUTL} = 0.1 \times I_{OUTL}, V_{CC2} = \text{open}$                                                       |      |     | 2.5   | V        |

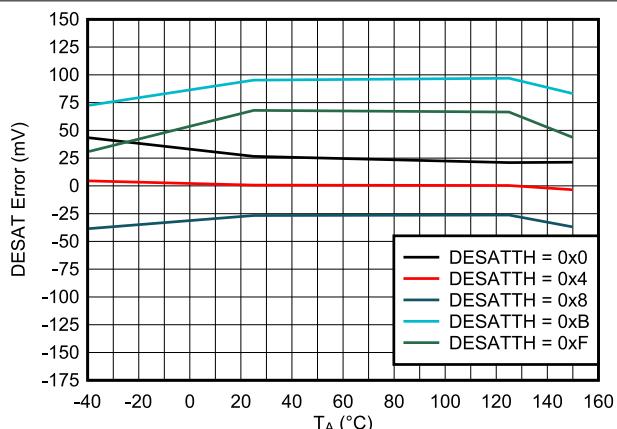

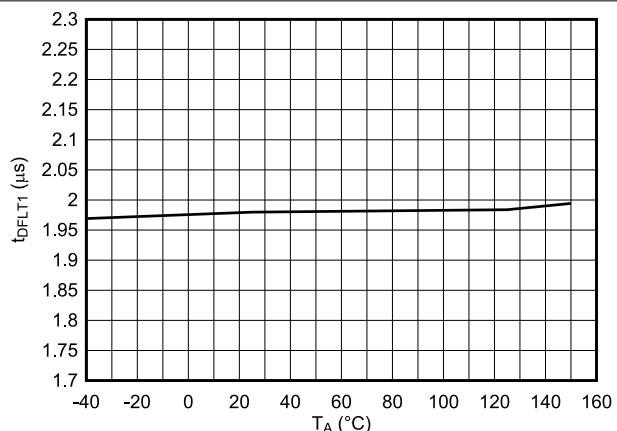

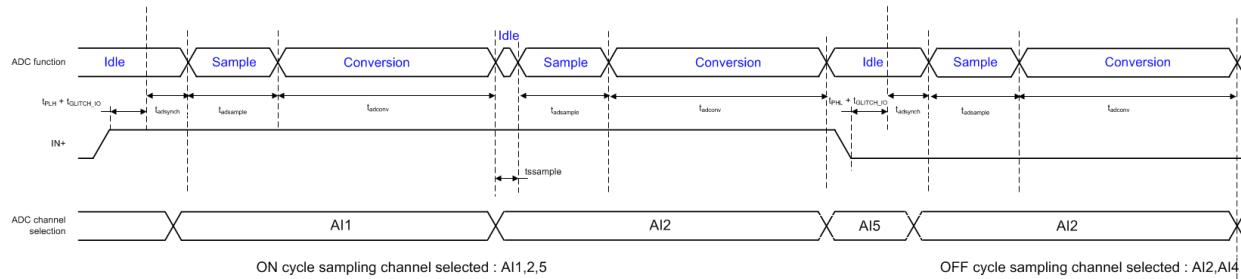

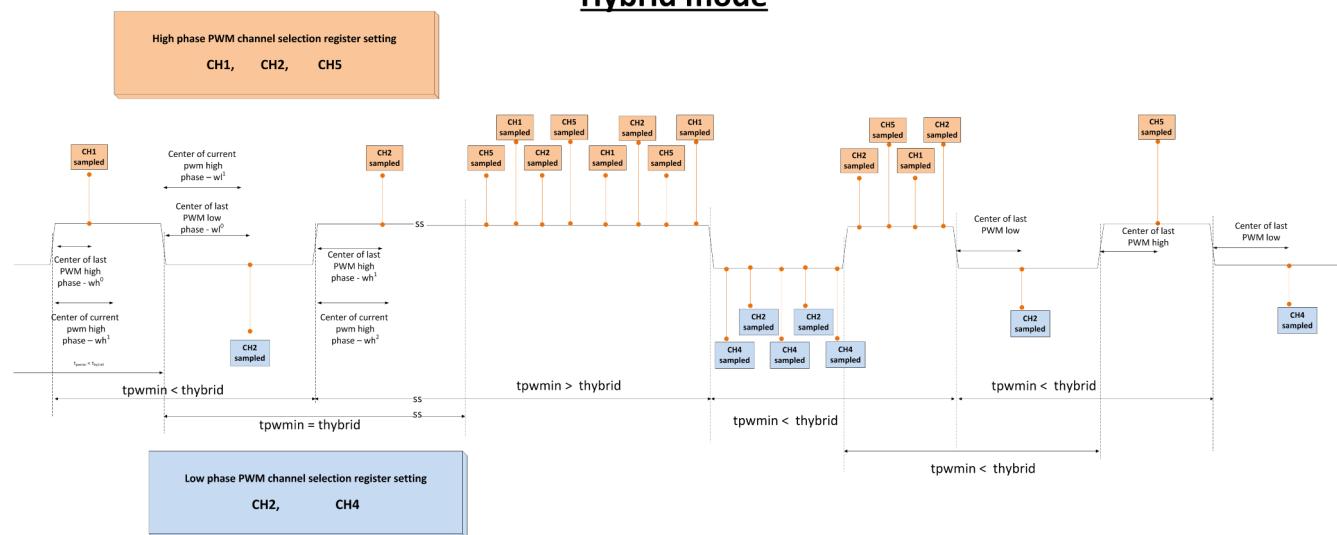

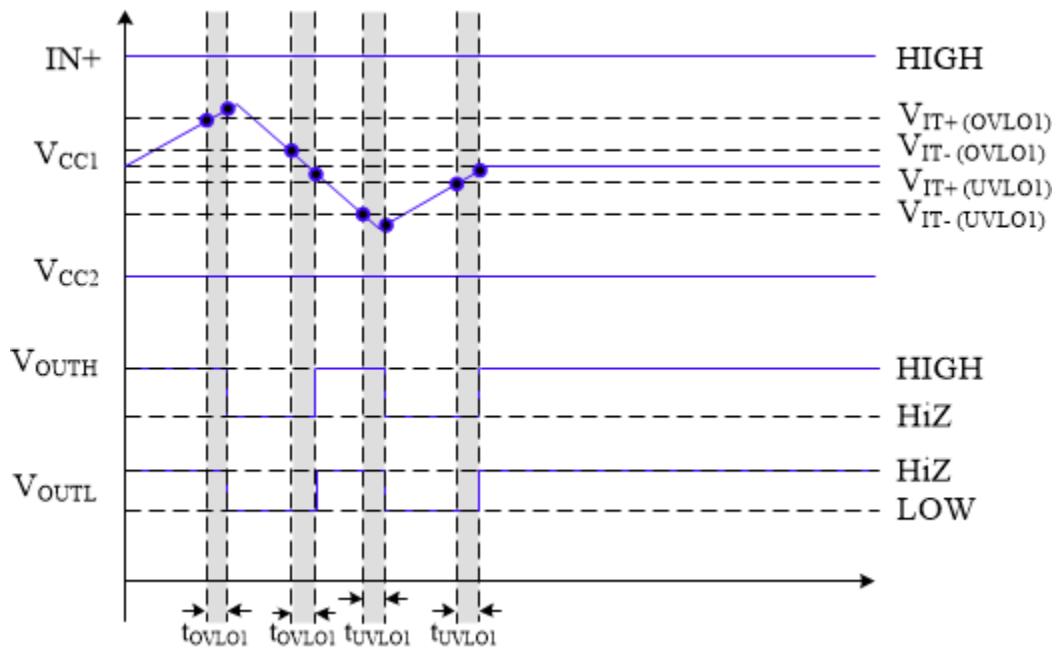

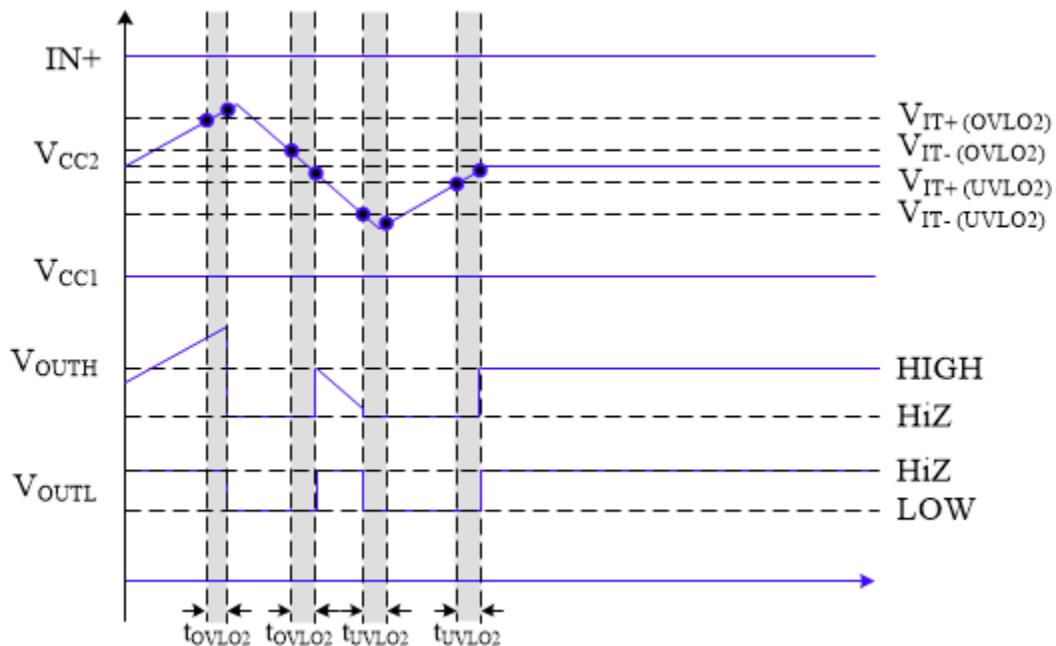

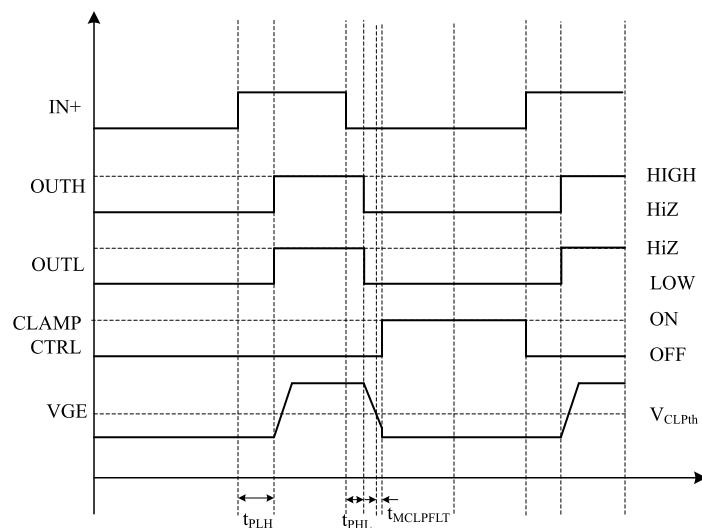

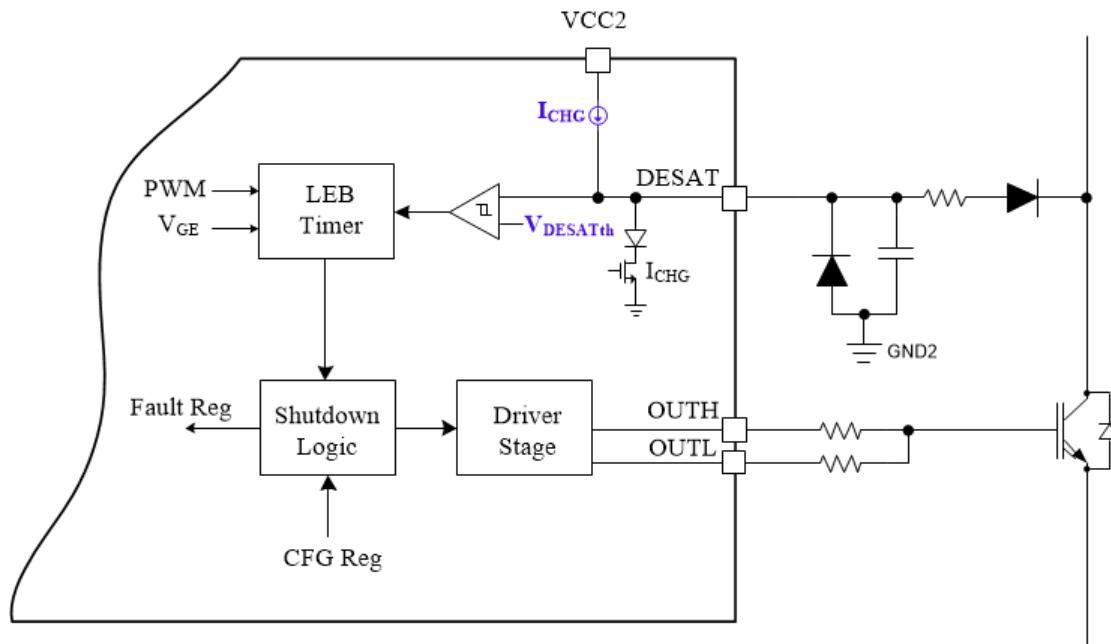

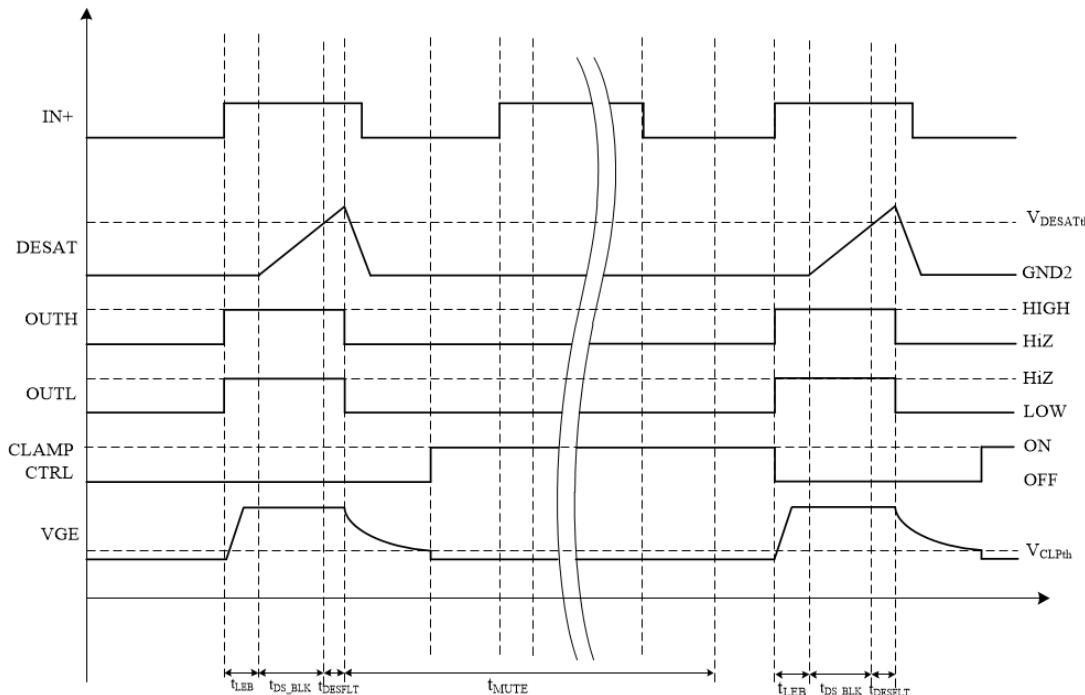

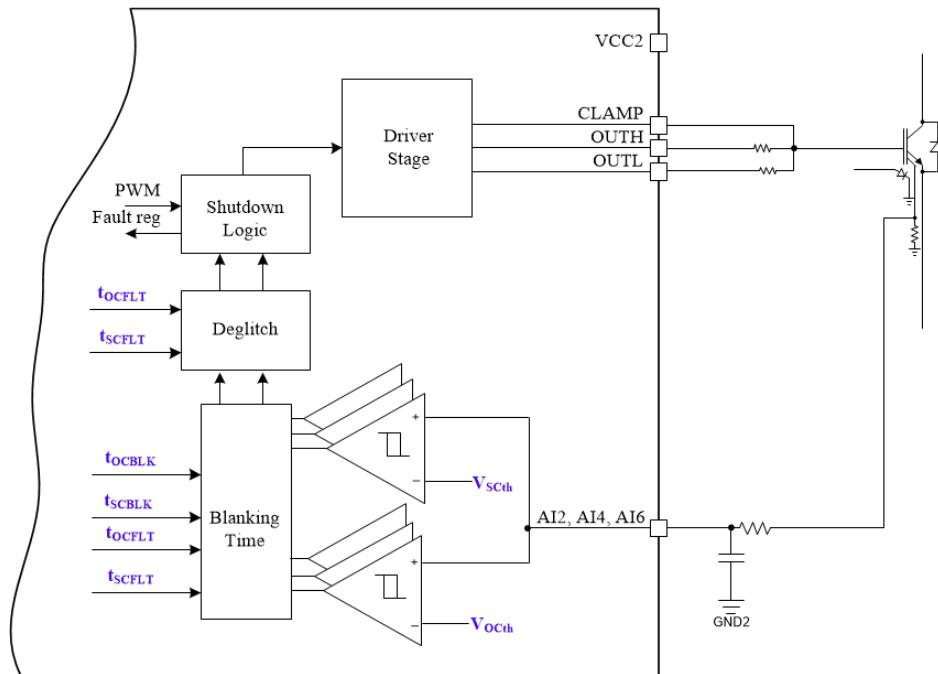

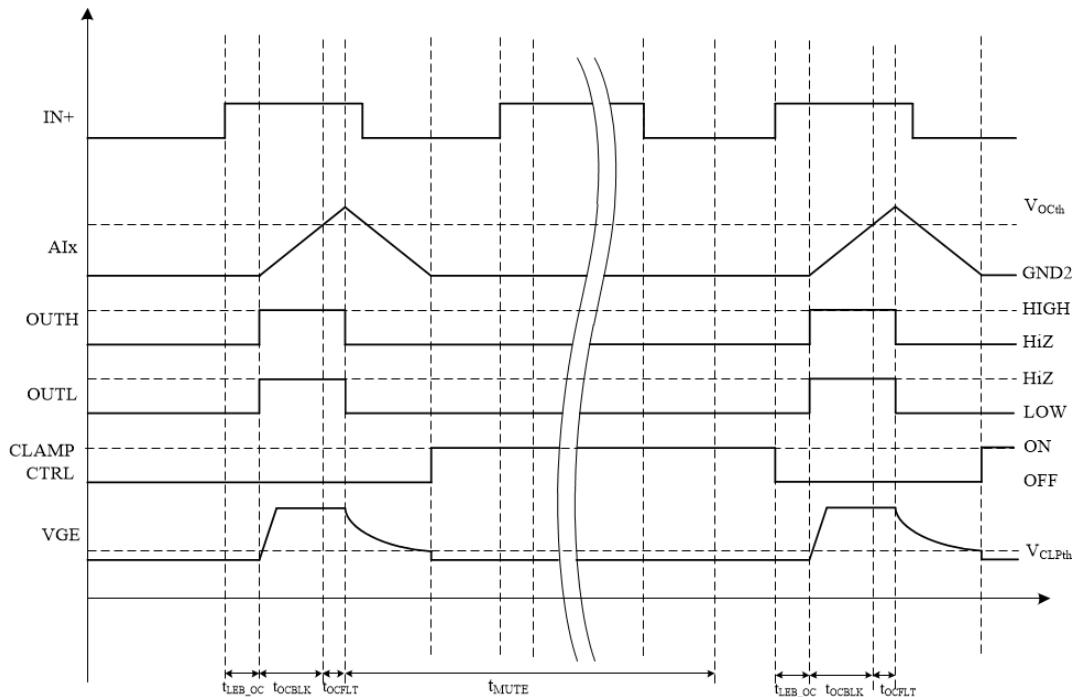

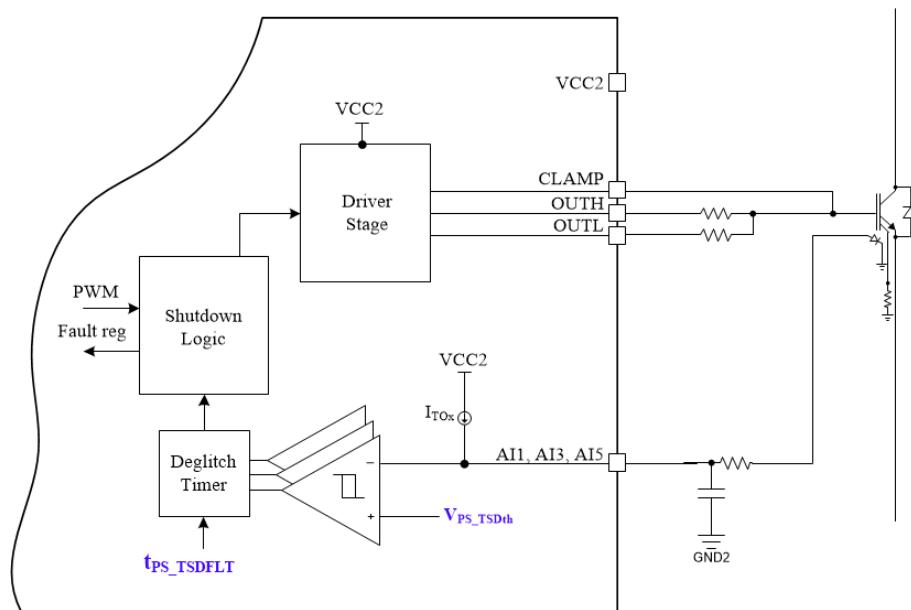

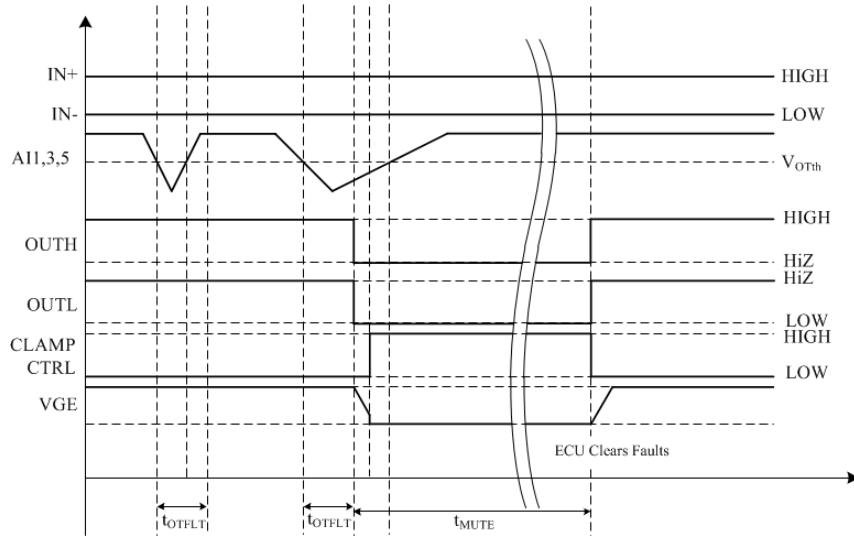

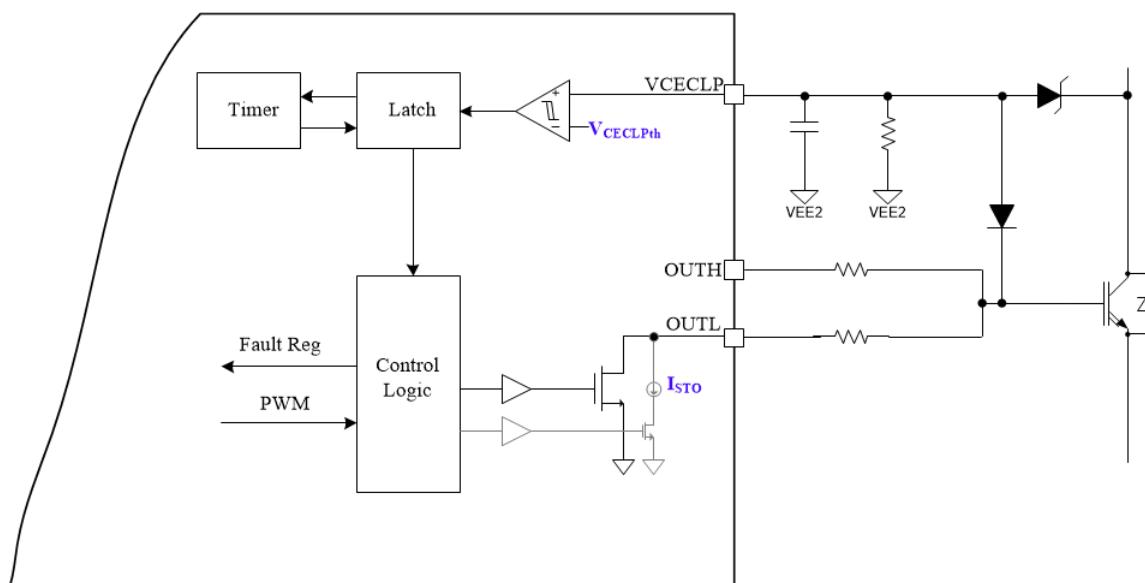

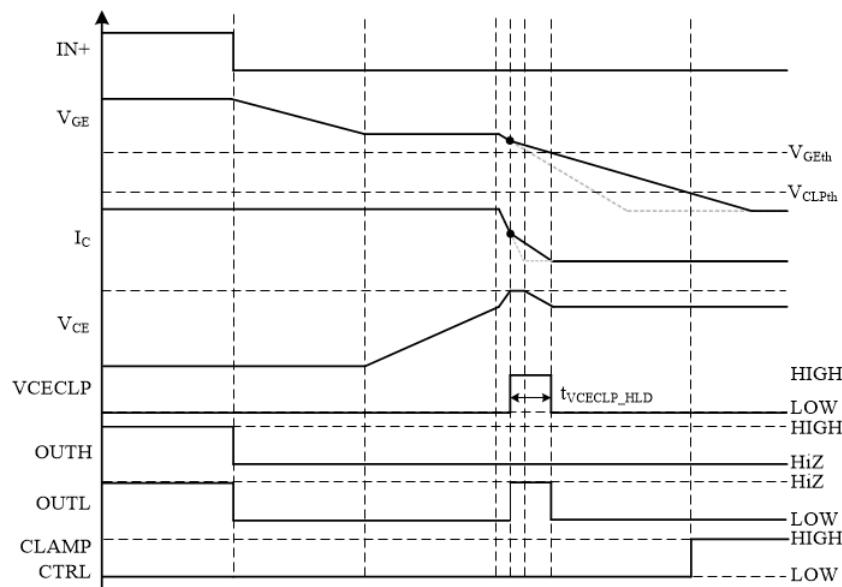

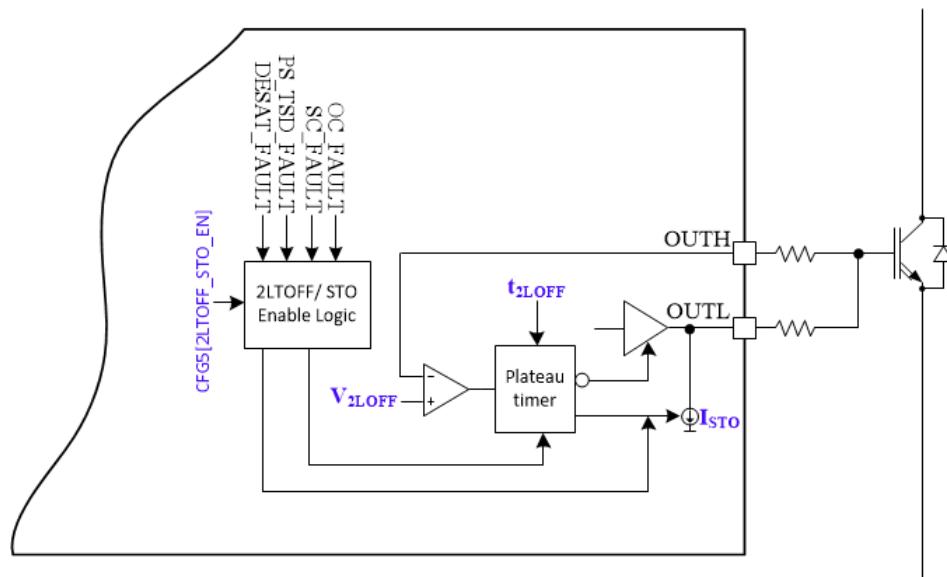

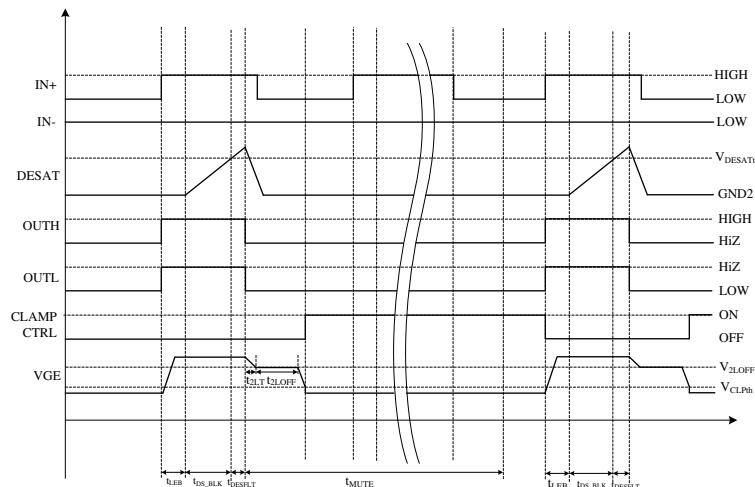

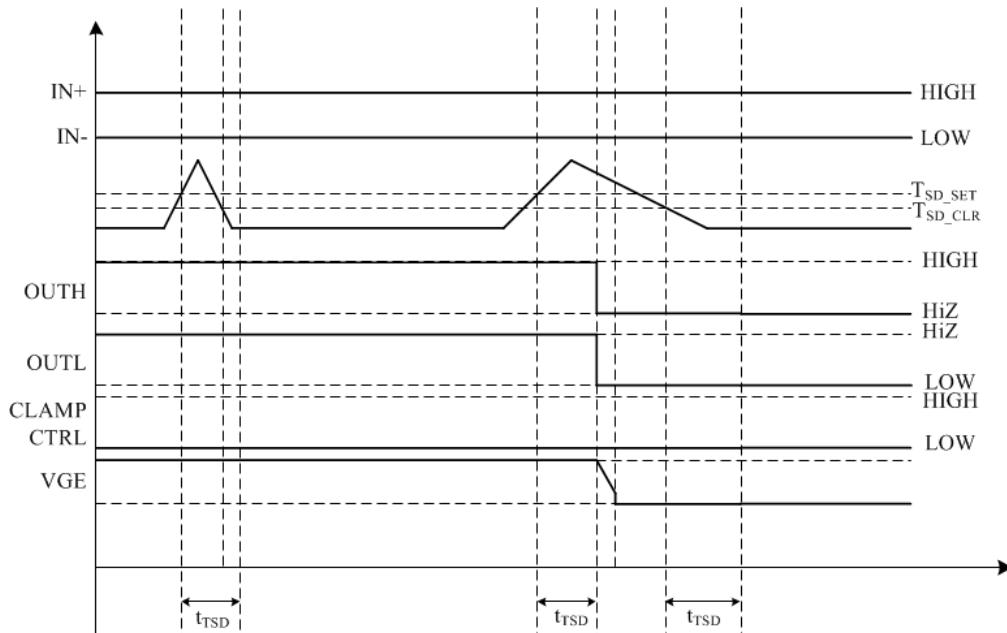

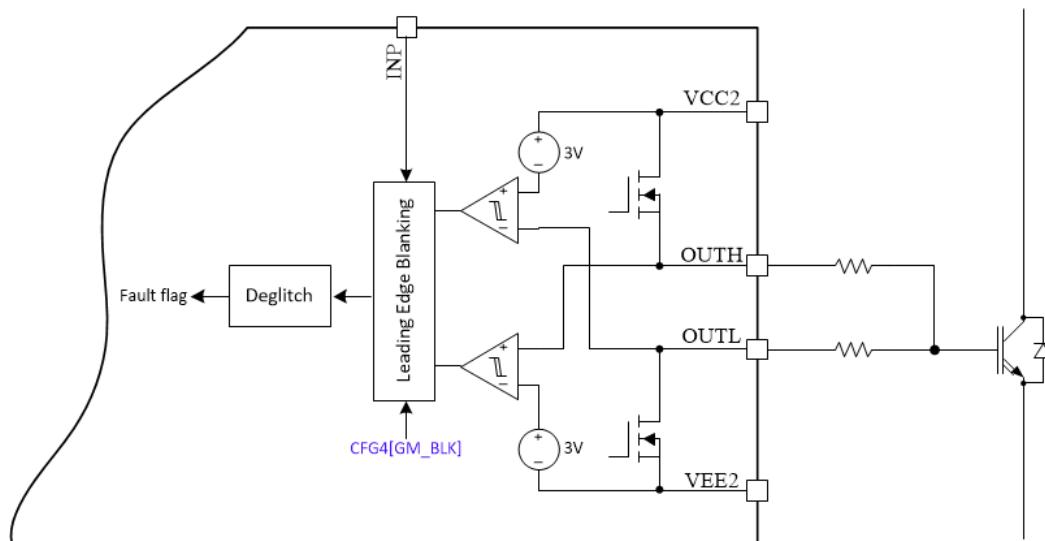

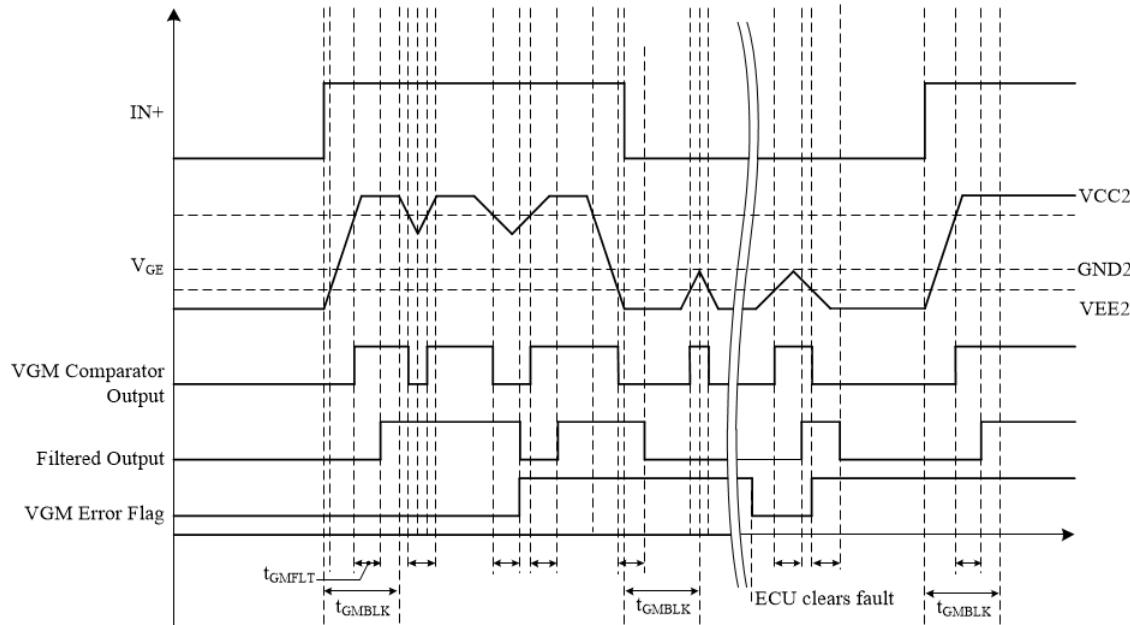

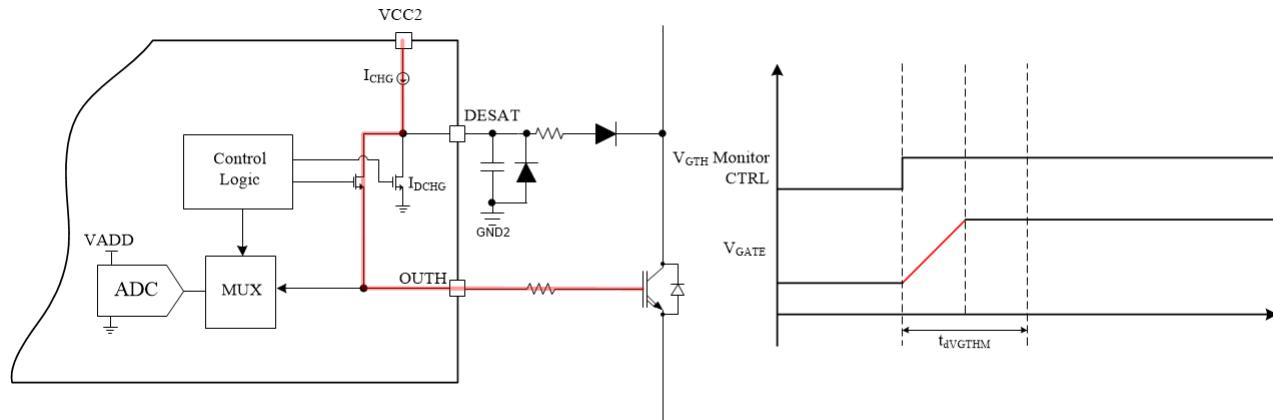

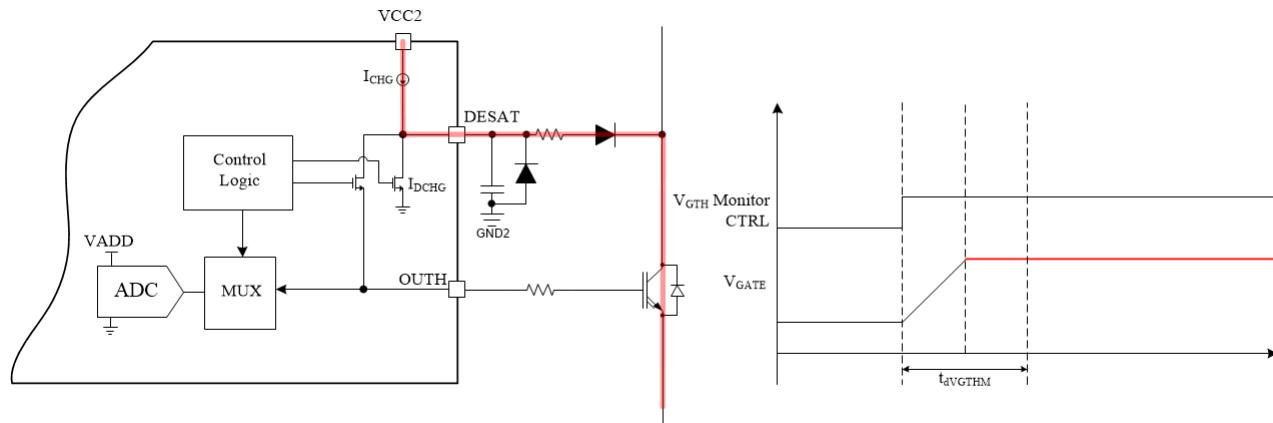

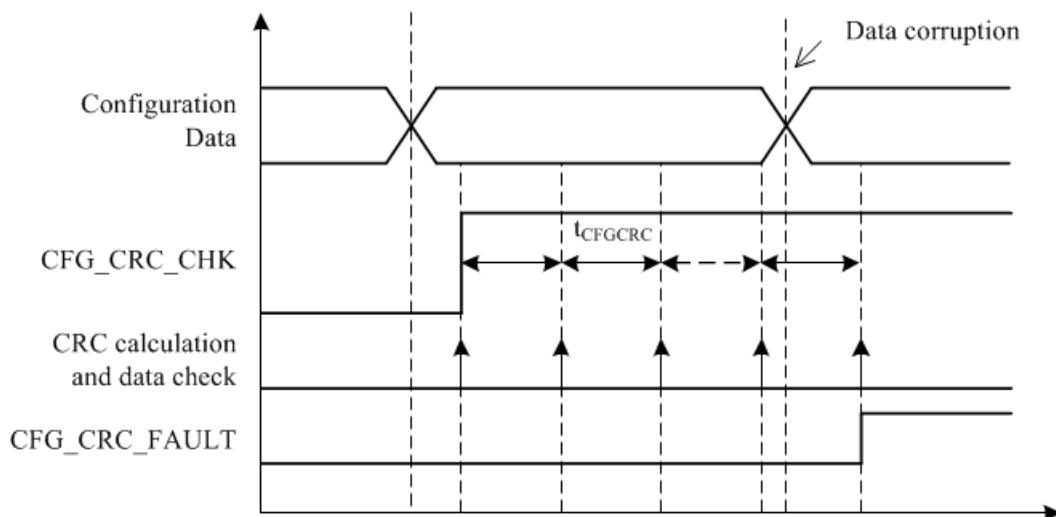

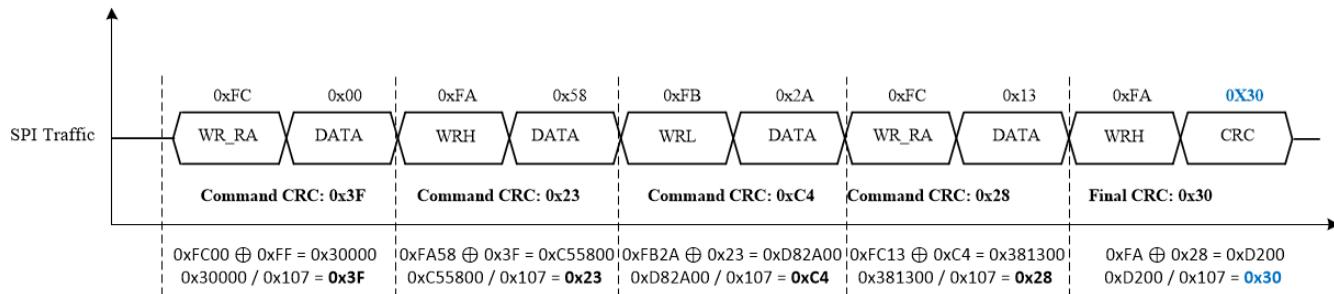

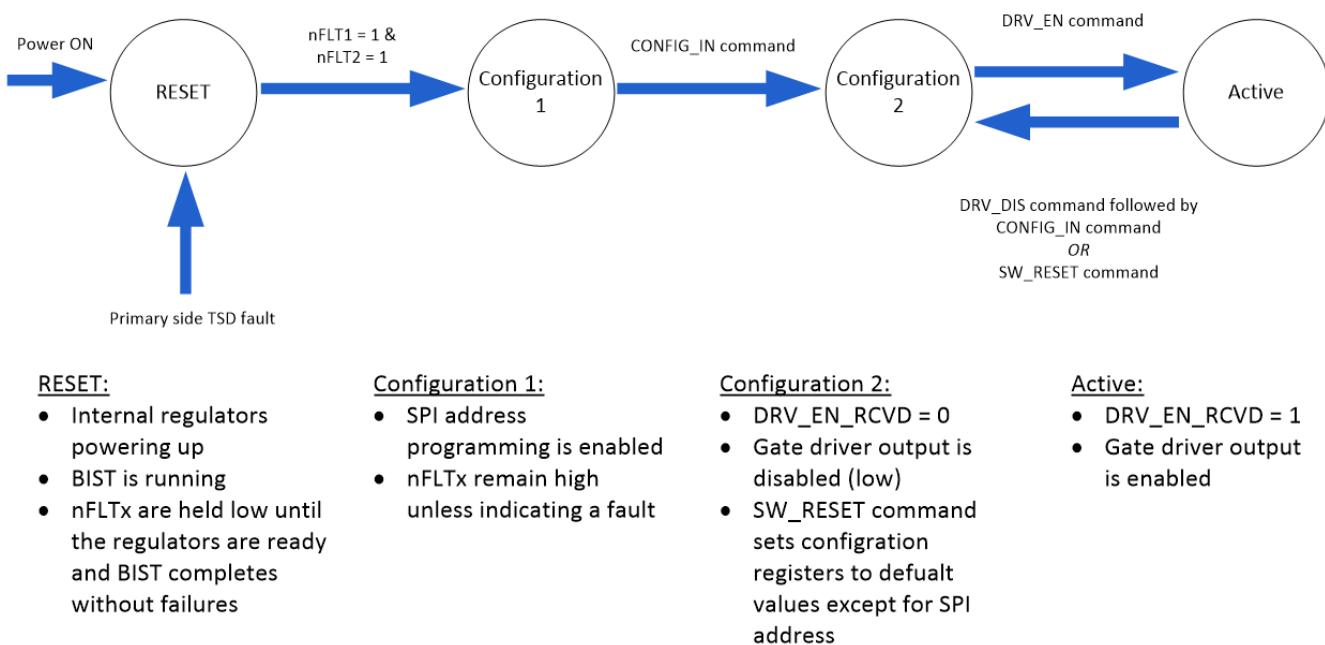

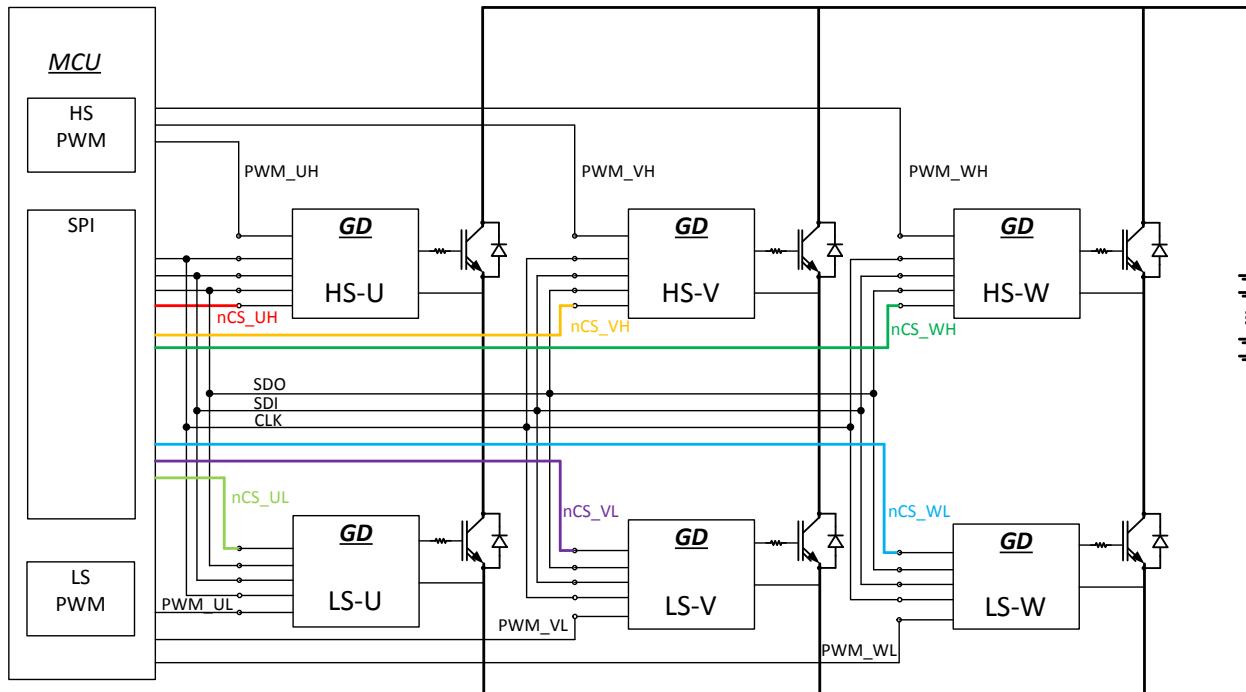

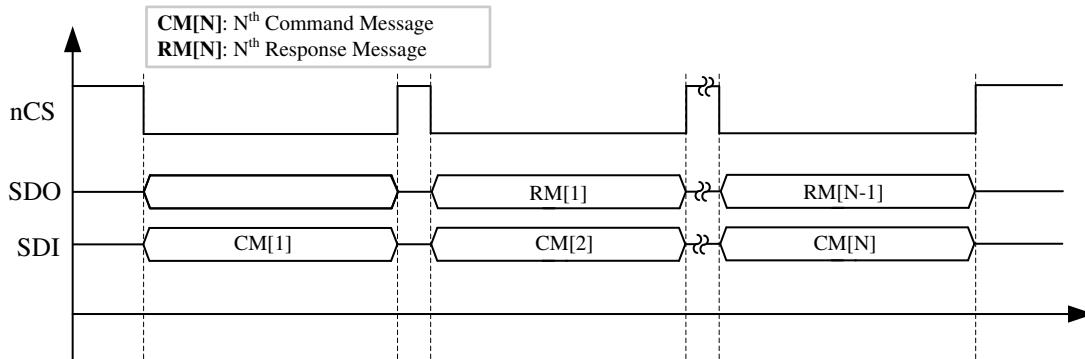

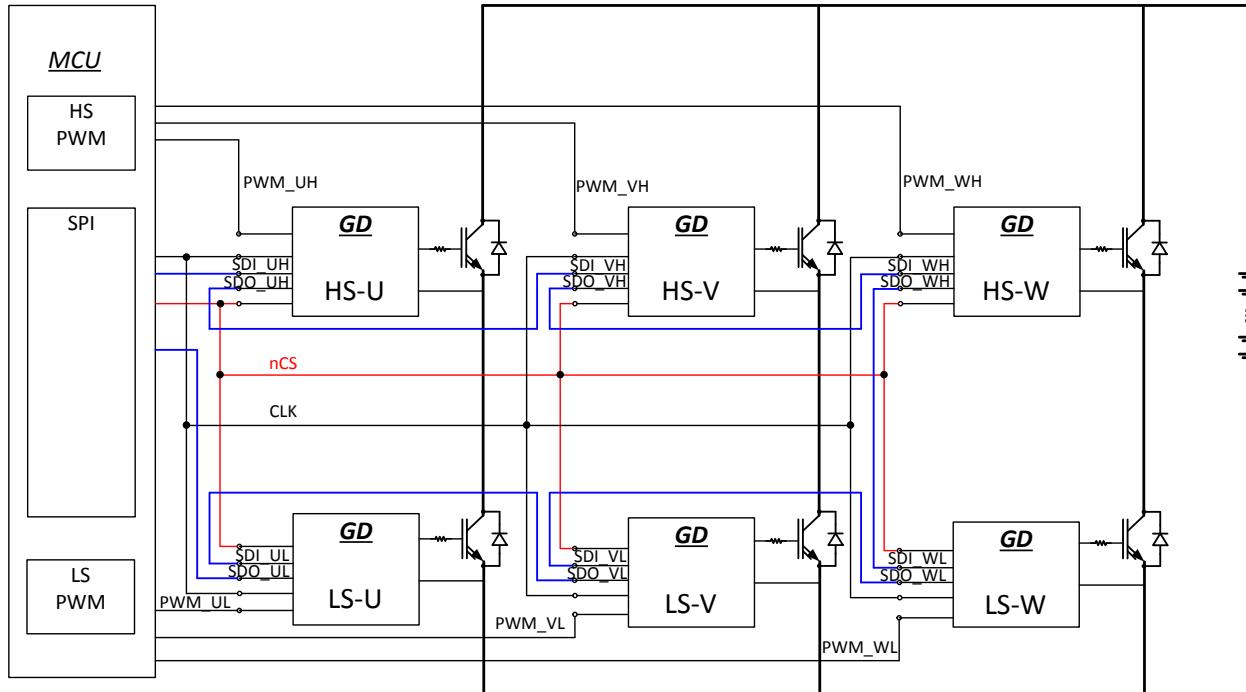

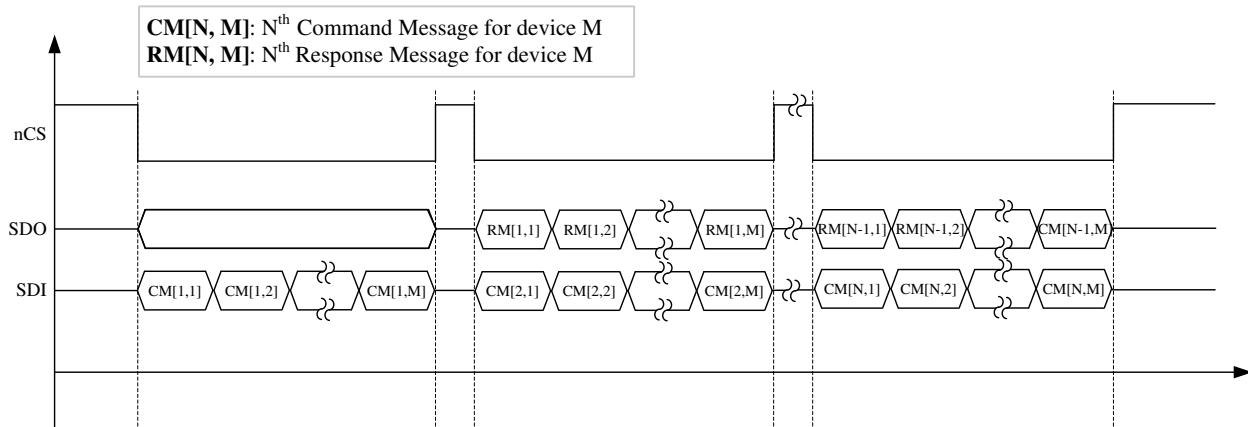

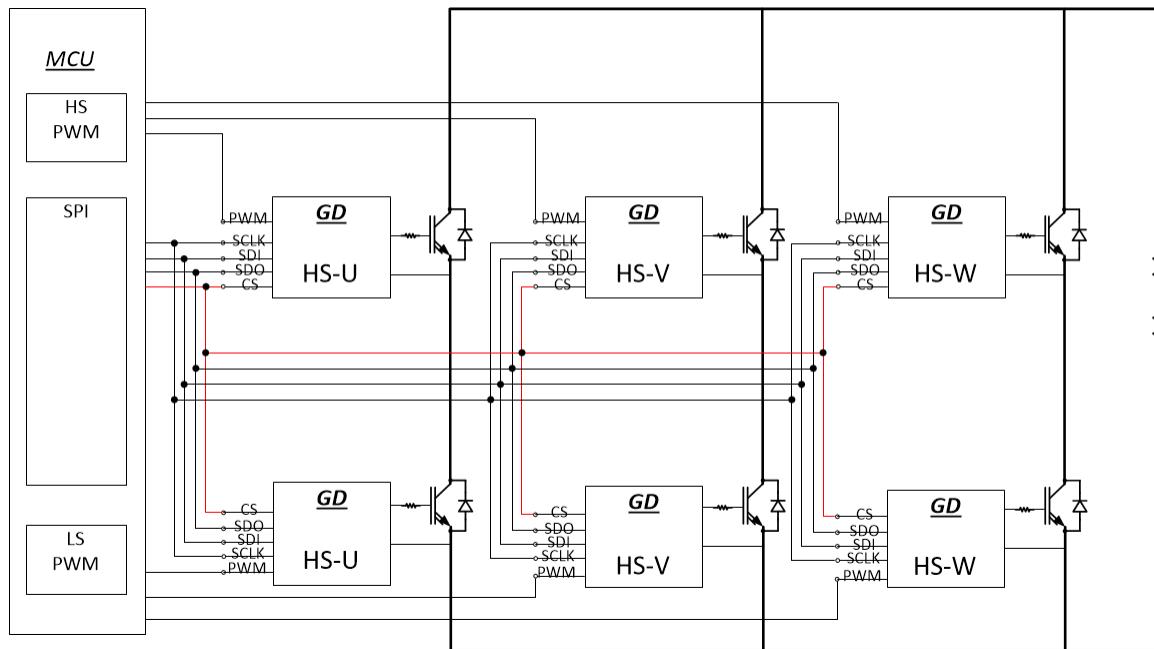

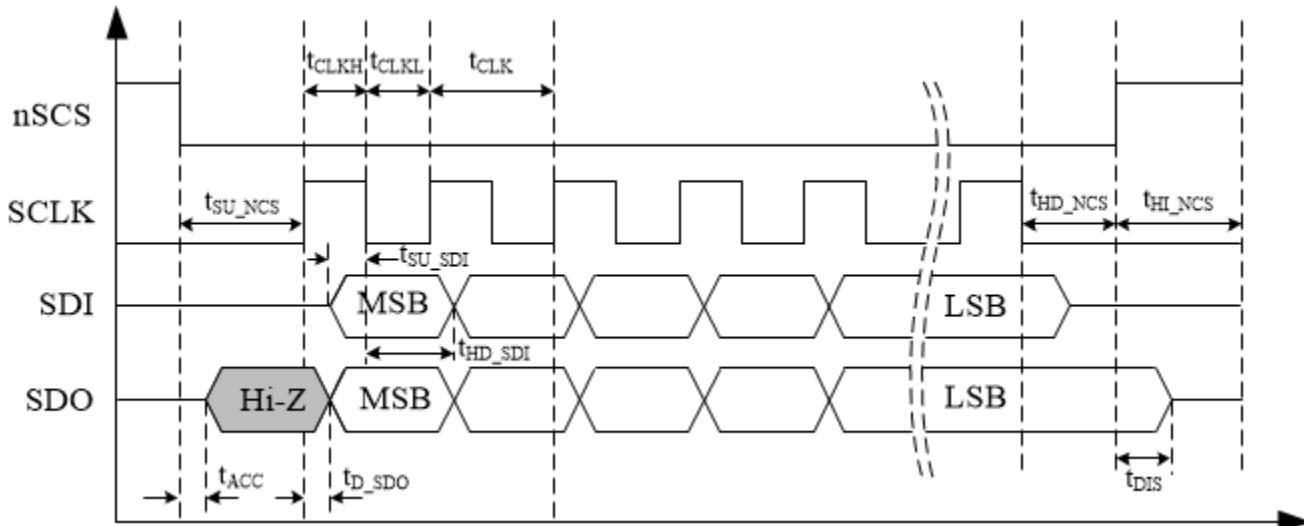

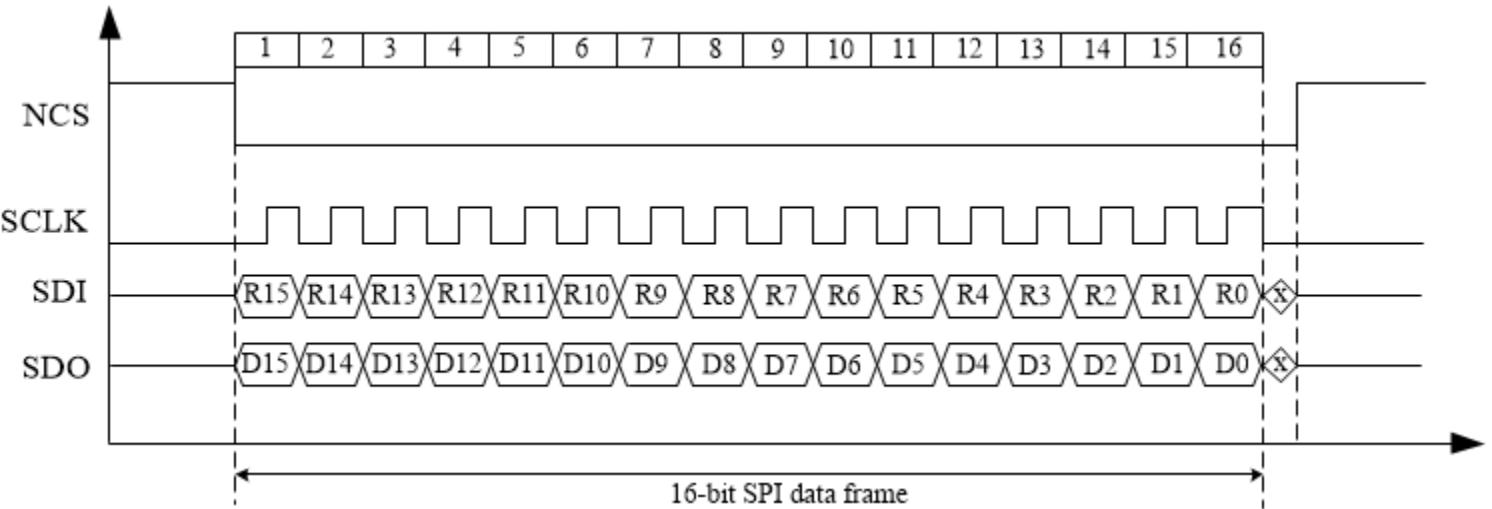

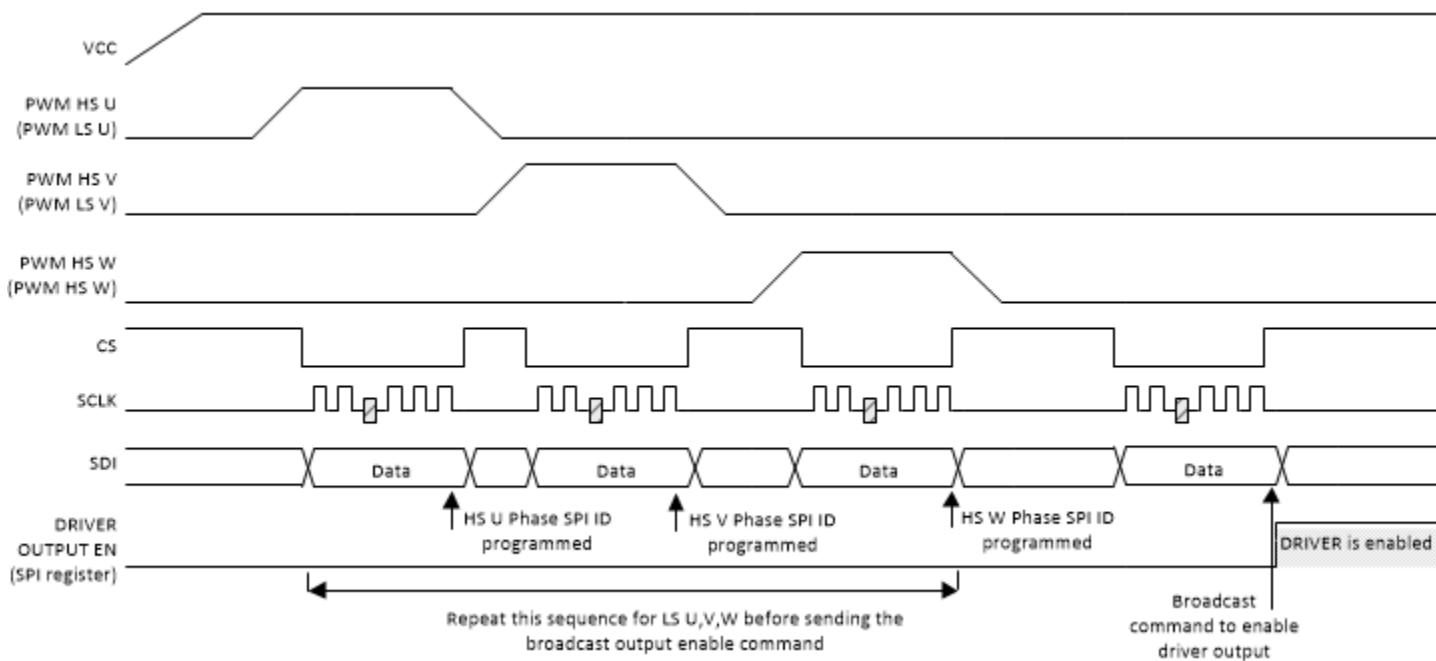

| DESAT SHORT-CIRCUIT PROTECTION |                                                                |                                                                                                               |      |     |       |          |