# PCI2040 PCI-DSP Bridge Controller

# Data Manual

2006 PCIBus Solutions

# PCI2040 PCI-DSP Bridge Controller Data Manual

Literature Number: SCPS048A September 2006

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products           |                        | Applications       |                           |

|--------------------|------------------------|--------------------|---------------------------|

| Amplifiers         | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters    | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP                | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface          | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic              | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt         | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers   | microcontroller.ti.com | Security           | www.ti.com/security       |

| Low Power Wireless | www.ti.com/lpw         | Telephony          | www.ti.com/telephony      |

|                    |                        | Video & Imaging    | www.ti.com/video          |

|                    |                        | Wireless           | www.ti.com/wireless       |

|                    |                        |                    |                           |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2006, Texas Instruments Incorporated

## **Contents**

| Se | ection |          | Title                                              | Page |

|----|--------|----------|----------------------------------------------------|------|

| 1  | Introd | uction . |                                                    | 1–1  |

|    | 1.1    | Descript | tion                                               | 1–1  |

|    | 1.2    | Feature  | s                                                  | 1–1  |

|    | 1.3    | Related  | Documents                                          | 1–1  |

|    | 1.4    | Ordering | g Information                                      | 1–1  |

| 2  | Termi  | nal Desc | riptions                                           | 2–1  |

| 3  | PCI20  | 40 Funct | tional Description                                 | 3–1  |

|    | 3.1    | PCI Inte | erface                                             | 3–1  |

|    | 3.2    | Accessi  | ng Internal PCI2040 Registers                      | 3–2  |

|    | 3.3    | PCI_LO   | OCK                                                | 3–2  |

|    | 3.4    |          | OM Interface                                       |      |

|    | 3.5    |          | 0 Host Port Interface                              |      |

|    |        | 3.5.1    | Identifying Implemented Ports and DSP Types        |      |

|    |        | 3.5.2    | DSP Chip Selects                                   | 3–4  |

|    |        | 3.5.3    | HPI Register Access Control                        |      |

|    |        | 3.5.4    | Mapping HPI DSP Memory to the Host                 |      |

|    |        | 3.5.5    | Read/Write Procedure                               |      |

|    |        | 3.5.6    | HPI Interface Specific Notes                       |      |

|    | 3.6    |          | I-Purpose I/O Interface                            |      |

|    | 3.7    |          | ts                                                 |      |

|    |        | 3.7.1    | Interrupt Event and Interrupt Mask Registers       |      |

|    |        | 3.7.2    | DSP-to-Host Interrupts                             |      |

|    |        | 3.7.3    | HPI Error Interrupts and HPI Error Reporting       |      |

|    |        | 3.7.4    | General-Purpose Interrupts                         |      |

|    |        | 3.7.5    | Interrupts Versus PME                              |      |

|    | 3.8    |          | 0 Power Management                                 |      |

|    |        | 3.8.1    | PCI Power Management Register Interface            |      |

|    |        | 3.8.2    | PCI Power Management Device States and Transitions |      |

|    | 3.9    |          | ct PCI Hot-Swap                                    | 3–9  |

|    | 3.10   |          | I-Purpose Bus                                      |      |

|    | 3.11   | -        | e Transactions on the General-Purpose Bus          |      |

|    |        | 3.11.1   | General-Purpose Bus Word Write                     |      |

|    |        | 3.11.2   | General-Purpose Bus Word Read                      | 3–11 |

| Se | ection | Title                                     | Page |

|----|--------|-------------------------------------------|------|

| 4  | PCI20  | 940 Programming Model                     | 4–1  |

|    | 4.1    | PCI Configuration Registers               |      |

|    | 4.2    | Vendor and Device ID Register             |      |

|    | 4.3    | PCI Command Register                      |      |

|    | 4.4    | PCI Status Register                       |      |

|    | 4.5    | Revision ID                               | 4-4  |

|    | 4.6    | Class Code                                |      |

|    | 4.7    | Cache Line Size Register                  | 4–5  |

|    | 4.8    | Latency Timer Register                    |      |

|    | 4.9    | Header Type Register                      |      |

|    | 4.10   | BIST Register                             |      |

|    | 4.11   | HPI CSR Memory Base Address Register      | 4–7  |

|    | 4.12   | Control Space Base Address Register       | 4–8  |

|    | 4.13   | GP Bus Base Address Register              | 4–9  |

|    | 4.14   | Subsystem Vendor ID Register              | 4-9  |

|    | 4.15   | Subsystem ID Register                     | 4–10 |

|    | 4.16   | Capability Pointer Register               | 4-10 |

|    | 4.17   | Interrupt Line Register                   | 4-10 |

|    | 4.18   | Interrupt Pin Register                    | 4-11 |

|    | 4.19   | MIN_GNT Register                          | 4–11 |

|    | 4.20   | MAX_LAT Register                          | 4–11 |

|    | 4.21   | GPIO Select Register                      | 4–12 |

|    | 4.22   | GPIO Input Data Register                  | 4–13 |

|    | 4.23   | GPIO Direction Control Register           | 4–13 |

|    | 4.24   | GPIO Output Data Register                 | 4–14 |

|    | 4.25   | GPIO Interrupt Event Type Register        | 4–14 |

|    | 4.26   | Miscellaneous Control Register            | 4–15 |

|    | 4.27   | Diagnostic Register                       | 4–16 |

|    | 4.28   | PM Capability ID Register                 | 4–16 |

|    | 4.29   | PM Next-Item Pointer Register             | 4–17 |

|    | 4.30   | Power Management Capabilities Register    | 4–17 |

|    | 4.31   | Power Management Control/Status Register  | 4–18 |

|    | 4.32   | HPI CSR I/O Base Address Register         | 4–19 |

|    | 4.33   | HS Capability ID Register                 | 4–19 |

|    | 4.34   | HS Next-Item Pointer Register             | 4-20 |

|    | 4.35   | CPCI Hot Swap Control and Status Register | 4–20 |

| 5  | HPI C  | ontrol and Status Registers (HPI CSR)     | 5–1  |

|    | 5.1    | Interrupt Event Register                  | 5–2  |

|    | 5.2    | Interrupt Mask Register                   | 5–3  |

|    | 5.3    | HPI Error Report Register                 | 5–4  |

|    | 5.4    | HPI Reset Register                        | 5–4  |

|    | 5.5    | HPI DSP Implementation Register           | 5–5  |

|    | 5.6    | HPI Data Width Register                   | 5–5  |

| Se | ction   |            | Title                                                 | Page |

|----|---------|------------|-------------------------------------------------------|------|

| 6  | DSP H   | IPI Overvi | iew                                                   | 6–1  |

|    | 6.1     | C54X Ho    | st Port Interface                                     | 6–1  |

|    |         | 6.1.1      | Modes of Operation                                    | 6–1  |

|    |         | 6.1.2      | HPI Functional Description                            | 6–1  |

|    |         | 6.1.3      | HPI Registers                                         | 6–1  |

|    | 6.2     | C54X HF    | PI Control Register                                   | 6–3  |

|    |         | 6.2.1      | Auto Increment Feature                                | 6–3  |

|    |         | 6.2.2      | Interrupts                                            | 6–3  |

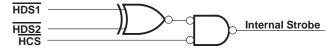

|    |         | 6.2.3      | Four Strobes (HDS1, HDS2, HR/W, HAS)                  | 6–4  |

|    |         | 6.2.4      | Wait States                                           | 6–4  |

|    |         | 6.2.5      | Host Read/Write Access to HPI                         | 6–4  |

|    |         | 6.2.6      | HPI Memory Access During Reset                        | 6–5  |

|    |         | 6.2.7      | Examples of Transactions Targeting the C54X           | 6–5  |

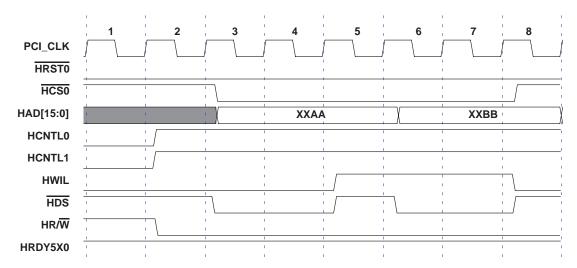

|    |         |            | 6.2.7.1 PCI Word Write                                | 6–5  |

|    |         |            | 6.2.7.2 PCI Word Read                                 | 6–6  |

|    |         |            | 6.2.7.3 PCI Double Word Write                         | 6–7  |

|    |         |            | 6.2.7.4 PCI Double Word Read                          | 6–8  |

|    | 6.3     | C6X HPI    | Interface                                             | 6–8  |

|    |         | 6.3.1      | No SAM or HOM Modes                                   | 6–8  |

|    |         | 6.3.2      | Address/Data Bus                                      | 6–9  |

|    |         | 6.3.3      | Byte Enables (HBE0 and HBE1)                          | 6–9  |

|    |         | 6.3.4      | Wait States                                           | 6–9  |

|    |         | 6.3.5      | C6X HPI Registers                                     |      |

|    |         | 6.3.6      | Software Handshaking Using HRDY and FETCH             | 6–11 |

|    |         | 6.3.7      | Host Access Sequence                                  | 6–12 |

|    |         | 6.3.8      | Single Half-Word Cycles                               | 6–12 |

|    |         | 6.3.9      | Memory Access Through HPI During Reset                | 6–12 |

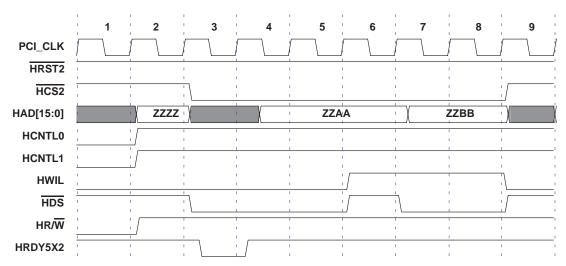

|    |         | 6.3.10     | Examples of Transactions Targeting the C6X            | 6–12 |

| 7  | Electri |            | acteristics                                           | 7–1  |

|    | 7.1     | Absolute   | Maximum Ratings Over Operating Temperature Ranges .   | 7–1  |

|    | 7.2     |            | ended Operating Conditions                            |      |

|    | 7.3     |            | Characteristics Over Recommended Operating Conditions | 7–3  |

| 8  | Mecha   | nical Info | ormation                                              | 8–1  |

## **List of Illustrations**

| Figure | Title                                                      | Page |

|--------|------------------------------------------------------------|------|

| 2–1    | PCI2040 Pin Diagram                                        | 2–1  |

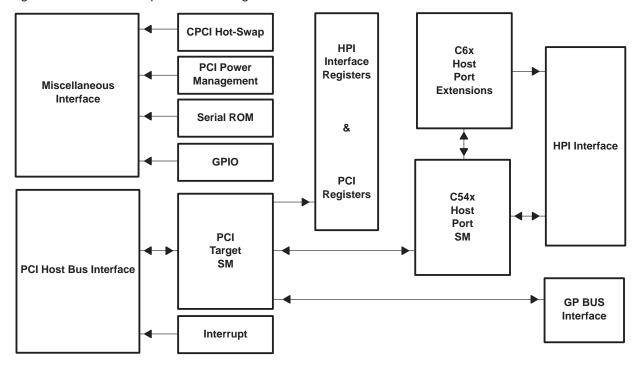

| 3–1    | PCI2040 System Block Diagram                               | 3–1  |

| 3–2    | PCI2040 Serial ROM Data Format                             | 3–3  |

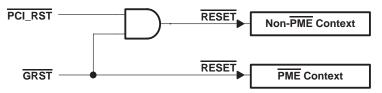

| 3–3    | PCI2040 Reset Illustration                                 | 3–9  |

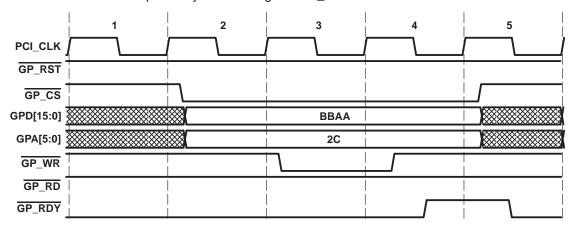

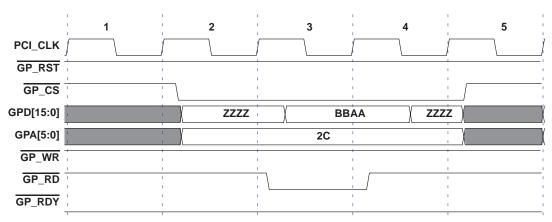

| 3–4    | General-Purpose Bus Word Write                             | 3–11 |

| 3–5    | General-Purpose Bus Word Read                              | 3–12 |

| 6–1    | C54X Select Input Logic                                    | 6–4  |

| 6–2    | Word Write To HPID Without Auto-Increment Enabled          | 6–6  |

| 6–3    | Word Write From HPID Without Auto-Increment Enabled        | 6–7  |

| 6–4    | Doubleword Write To HPID Without Auto-Increment Enabled    | 6–8  |

| 6–5    | Doubleword Read Trom HPID Without Auto-Increment Enabled   | 6–8  |

| 6–6    | Double Word Write To HPID Without Auto-Increment Selected  | 6–13 |

| 6–7    | Double Word Read From HPID Without Auto-Increment Selected | 6-13 |

## **List of Tables**

| Table | Title                                     | Page |

|-------|-------------------------------------------|------|

| 2–1   | Card Signal Names by GGU/PGE Pin Number   | 2-2  |

| 2–2   | Card Signal Names Sorted Alphabetically   | 2–3  |

| 2–3   | Power Supply                              |      |

| 2-4   | PCI System Terminal Functions             | 2-5  |

| 2–5   | Miscellaneous Terminal Functions          | 2-6  |

| 2-6   | Host Port Interface Terminal Functions    | 2–7  |

| 2–7   | Compact PCI Hot Swap Interface            | 2-8  |

| 2–8   | General-Purpose Bus Interface             | 2-8  |

| 3–1   | PCI2040 Chip Select Decoding              | 3–4  |

| 3–2   | HPI Interface Features                    | 3–5  |

| 3–3   | PMC Changes for PCI PM 1.1 Register Model | 3–8  |

| 3–4   | General-Purpose Bus Signals               | 3-10 |

| 4–1   | PCI Configuration Registers               | 4–1  |

| 4–2   | Bit Field Access Tag Descriptions         | 4–2  |

| 4–3   | PCI Command Register                      | 4–3  |

| 4–4   | PCI Status Register                       | 4–4  |

| 4–5   | HPI CSR Memory Base Address Register      | 4–7  |

| 4–6   | Control Space Base Address Register       | 4–8  |

| 4–7   | General-Purpose Bus Base Address Register | 4–9  |

| 4–8   | GPIO Select Register                      | 4–12 |

| 4–9   | GPIO Input Data Register                  | 4–13 |

| 4–10  | GPIO Direction Control Register           | 4–13 |

| 4–11  | GPIO Output Data Register                 | 4–14 |

| 4–12  | GPIO Interrupt Event Type Register        | 4–14 |

| 4–13  | Miscellaneous Control Register            | 4–15 |

| 4–14  | Diagnostic Register                       | 4–16 |

| 4–15  | Power Management Capabilities Register    | 4–17 |

| 4–16  | Power Management Control/Status Register  | 4–18 |

| 4–17  | HPI CSR I/O Base Address Register         | 4–19 |

| 4–18  | CPCI Hot Swap Control and Status Register | 4–20 |

| 5–1   | HPI Configuration Register Map            | 5–1  |

| 5–2   | Interrupt Event Register                  | 5–2  |

| 5–3   | Interrupt Mask Register                   | 5–3  |

| 5-4   | HPI Error Report Register                 | 5-4  |

| 5–5   | HPI Reset Register                        | 5–4  |

| 5-6   | HPI DSP Implementation Register           | 5–5  |

| 5–7   | HPI Data Width Register                   | 5–5  |

| Table | Title                                 | Page |

|-------|---------------------------------------|------|

| 6–1   | C54X HPI Registers Access Control     | 6–2  |

| 6–2   | C54X HPI Control Register Description | 6–3  |

| 6–3   | HCNTL0 and HCNTL1 in C6X              | 6–10 |

| 6–4   | C6X HPI Control Register              | 6-11 |

#### 1 Introduction

#### 1.1 Description

The TI PCI2040 is a PCI-DSP bridge that provides a glueless connection between the 8-bit host port interface (HPI) port on the TMS320C54X or the 16-bit HPI port on TMS320C6X to the high performance PCI bus. It provides a PCI bus target interface compliant with the *PCI Local Bus Specification*.

The PCI2040 provides several external interfaces: the PCI bus interface with compact PCI support, the HPI port interface with support for up to four DSPs, a serial ROM interface, a general-purpose input/output interface (GPIOs), and a 16-bit general-purpose bus to provide a glueless interface to TI JTAG test bus controller (TBC). The PCI2040 universal target-only PCI interface is compatible with 3.3-V or 5-V signaling environments.

The PCI2040 interfaces with DSPs via a data bus (HPI port). The PCI2040 also provides a serial ROM interface for preloading several registers including the subsystem ID and subsystem vendor ID.

The PCI2040, compliant with the latest *PCI Bus Power Management Interface Specification*, provides several low-power features that reduce power consumption. Furthermore, an advanced CMOS process achieves low system power consumption.

Unused PCI2040 inputs must be pulled to a valid logic level using a pullup resistor.

#### 1.2 Features

The PCI2040 supports the following features:

- PCI bus target only, supporting both single-word reads and writes

- Write transaction posting for improved PCI bus performance

- Provides glueless interface to host port interface (HPI) port of C54x and/or C6x

- Up to four DSP devices on HPI

- Allows direct access to program and control external devices connected to PCI2040

- Serial ROM interface for loading subsystem ID and subsystem vendor ID

- A 16-bit general-purpose bus (GPB) that provides glueless interface to TI JTAG TBC

- 3.3-V core logic with universal PCI interface compatible with 3.3-V or 5-V signaling environments

- Advanced submicron, low-power CMOS technology

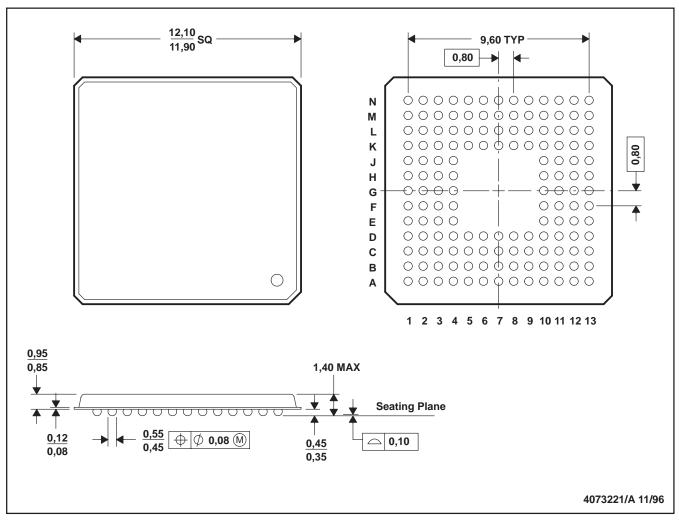

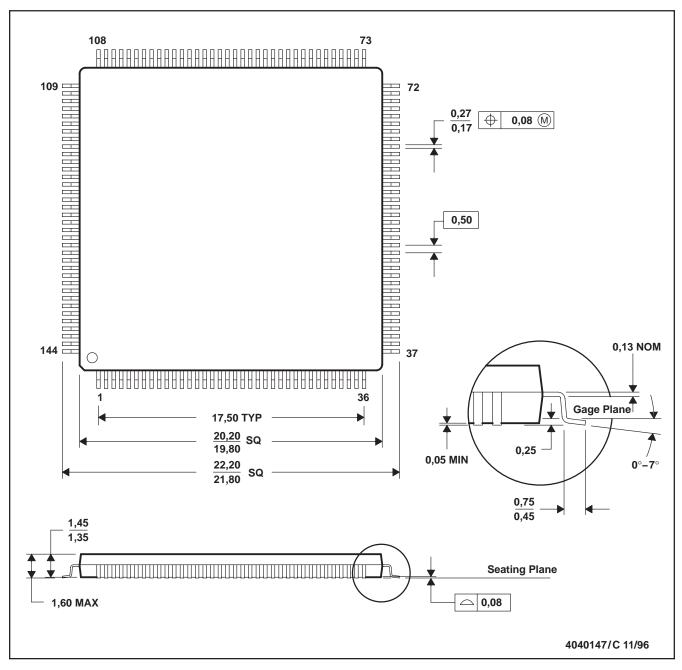

- 144-pin device and choice of surface mount packaging: TQFP or 12 mm x 12 mm MicroStar BGA

- Up to 33 MHz PCI bus frequency

#### 1.3 Related Documents

- Compact PCI Hot Swap Specification PICMG 2.1 (Revision 1.0)

- PCI Bus Power Management Interface Specification (Revision 1.1)

- PCI Local Bus Specification (Revision 2.2)

- PC 98/99

#### 1.4 Ordering Information

| ORDERING NUMBER | NAME                      | VOLTAGE                  | PACKAGE                       |

|-----------------|---------------------------|--------------------------|-------------------------------|

| PCI2040         | PCI-DSP Bridge Controller | 3.3 V, 5-V Tolerant I/Os | 144-pin LQFP<br>144-ball PBGA |

#### **2 Terminal Descriptions**

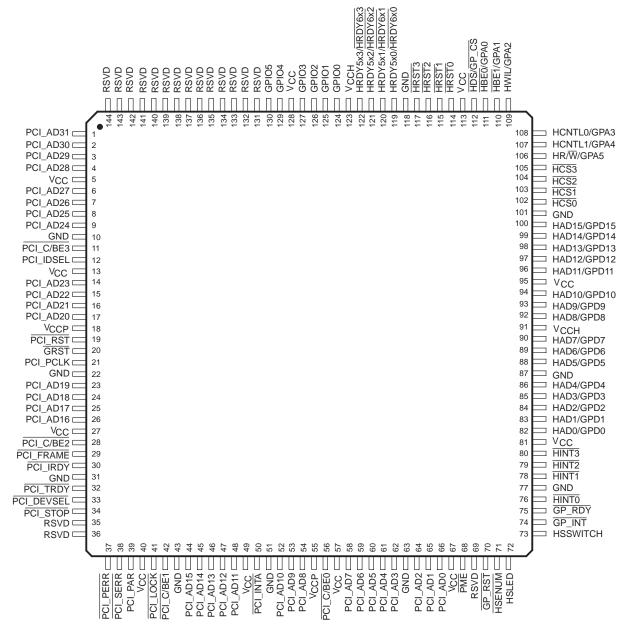

Figure 2-1. PCI2040 Pin Diagram

Table 2–1 shows the card signal names and their terminal assignments sorted alphanumerically by the associated GGU package terminal number. Table 2–2 shows the card signal names sorted alphabetically by the signal name and its associated terminal numbers.

Table 2–1. Card Signal Names by GGU/PGE Pin Number

| PIN NO. |     |                 | PIN NO. |     |                  | PIN NO. |     | SIGNAL          | PIN | NO. | SIGNAL          |

|---------|-----|-----------------|---------|-----|------------------|---------|-----|-----------------|-----|-----|-----------------|

| GGU     | PGE | SIGNAL NAME     | GGU     | PGE | SIGNAL NAME      | GGU     | PGE | NAME            | GGU | PGE | NAME            |

| A1      | 1   | PCI_AD31        | C11     | 106 | HR/W/GPA5        | G10     | 92  | HAD8/GPD8       | L4  | 42  | PCI_C/BE1       |

| A2      | 143 | RSVD            | C12     | 105 | HCS3             | G11     | 91  | Vссн            | L5  | 46  | PCI_AD13        |

| А3      | 140 | RSVD            | C13     | 104 | HCS2             | G12     | 89  | HAD6/GPD6       | L6  | 50  | PCI_INTA        |

| A4      | 137 | RSVD            | D1      | 8   | PCI_AD25         | G13     | 90  | HAD7/GPD7       | L7  | 55  | VCCP            |

| A5      | 133 | RSVD            | D2      | 7   | PCI_AD26         | H1      | 21  | PCI_PCLK        | L8  | 59  | PCI_AD6         |

| A6      | 129 | GPIO4           | D3      | 6   | PCI_AD27         | H2      | 22  | GND             | L9  | 63  | GND             |

| A7      | 126 | GPIO2           | D4      | 5   | V <sub>CC</sub>  | НЗ      | 23  | PCI_AD19        | L10 | 67  | V <sub>CC</sub> |

| A8      | 124 | GPIO0           | D5      | 136 | RSVD             | H4      | 24  | PCI_AD18        | L11 | 70  | GP_RST          |

| A9      | 120 | HRDY5x1/HRDY6x1 | D6      | 132 | RSVD             | H10     | 85  | HAD3/GPD3       | L12 | 75  | GP_RDY          |

| A10     | 116 | HRST2           | D7      | 128 | VCC              | H11     | 86  | HAD4/GPD4       | L13 | 76  | HINT0           |

| A11     | 112 | HDS/GP_CS       | D8      | 121 | HRDY5x2/HRDY6x2  | H12     | 87  | GND             | M1  | 35  | RSVD            |

| A12     | 110 | HBE1/GPA1       | D9      | 117 | HRST3            | H13     | 88  | HAD5/GPD5       | M2  | 36  | RSVD            |

| A13     | 109 | HWIL/GPA2       | D10     | 113 | V <sub>CC</sub>  | J1      | 25  | PCI_AD17        | М3  | 39  | PCI_PAR         |

| B1      | 2   | PCI_AD30        | D11     | 103 | HCS1             | J2      | 26  | PCI_AD16        | M4  | 43  | GND             |

| B2      | 144 | RSVD            | D12     | 102 | HCS0             | J3      | 27  | VCC             | M5  | 47  | PCI_AD12        |

| В3      | 141 | RSVD            | D13     | 101 | GND              | J4      | 28  | PCI_C/BE2       | M6  | 51  | GND             |

| В4      | 138 | RSVD            | E1      | 12  | PCI_IDSEL        | J10     | 81  | VCC             | M7  | 53  | PCI_AD9         |

| B5      | 134 | RSVD            | E2      | 11  | PCI_C/BE3        | J11     | 82  | HAD0/GPD0       | M8  | 58  | PCI_AD7         |

| В6      | 130 | GPIO5           | E3      | 10  | GND              | J12     | 83  | HAD1/GPD1       | M9  | 62  | PCI_AD3         |

| В7      | 125 | GPIO1           | E4      | 9   | PCI_AD24         | J13     | 84  | HAD2/GPD2       | M10 | 66  | PCI_AD0         |

| B8      | 123 | Vссн            | E10     | 100 | HAD15/GPD15      | K1      | 29  | PCI_FRAME       | M11 | 69  | RSVD            |

| В9      | 119 | HRDY5x0/HRDY6x0 | E11     | 99  | HAD14/GPD14      | K2      | 30  | PCI_IRDY        | M12 | 72  | HSLED           |

| B10     | 115 | HRST1           | E12     | 98  | HAD13/GPD13      | K3      | 31  | GND             | M13 | 74  | GP_INT          |

| B11     | 111 | HBE0/GPA0       | E13     | 97  | HAD12/GPD12      | K4      | 41  | PCI_LOCK        | N1  | 37  | PCI_PERR        |

| B12     | 108 | HCNTL0/GPA3     | F1      | 16  | PCI_AD21         | K5      | 45  | PCI_AD14        | N2  | 38  | PCI_SERR        |

| B13     | 107 | HCNTL1/GPA4     | F2      | 15  | PCI_AD22         | K6      | 49  | V <sub>CC</sub> | N3  | 40  | V <sub>CC</sub> |

| C1      | 4   | PCI_AD28        | F3      | 14  | PCI_AD23         | K7      | 56  | PCI_C/BE0       | N4  | 44  | PCI_AD15        |

| C2      | 3   | PCI_AD29        | F4      | 13  | VCC              | K8      | 60  | PCI_AD5         | N5  | 48  | PCI_AD11        |

| C3      | 142 | RSVD            | F10     | 96  | HAD11/GPD11      | K9      | 64  | PCI_AD2         | N6  | 52  | PCI_AD10        |

| C4      | 139 | RSVD            | F11     | 95  | VCC              | K10     | 77  | GND             | N7  | 54  | PCI_AD8         |

| C5      | 135 | RSVD            | F12     | 94  | HAD10/GPD10      | K11     | 78  | HINT1           | N8  | 57  | VCC             |

| C6      | 131 | RSVD            | F13     | 93  | HAD9/GPD9        | K12     | 79  | HINT2           | N9  | 61  | PCI_AD4         |

| C7      | 127 | GPIO3           | G1      | 18  | V <sub>CCP</sub> | K13     | 80  | HINT3           | N10 | 65  | PCI_AD1         |

| C8      | 122 | HRDY5x3/HRDY6x3 | G2      | 17  | PCI_AD20         | L1      | 32  | PCI_TRDY        | N11 | 68  | PME             |

| C9      | 118 | GND             | G3      | 19  | PCI_RST          | L2      | 33  | PCI_DEVSEL      | N12 | 71  | HSENUM          |

| C10     | 114 | HRST0           | G4      | 20  | GRST             | L3      | 34  | PCI_STOP        | N13 | 73  | HSSWITCH        |

Table 2–2. Card Signal Names Sorted Alphabetically

|             | PIN | NO. |                 | PIN | NO. | -           | PIN | NO. |                 | PIN | NO. |

|-------------|-----|-----|-----------------|-----|-----|-------------|-----|-----|-----------------|-----|-----|

| SIGNAL NAME | GGU | PGE | SIGNAL NAME     | GGU | PGE | SIGNAL NAME | GGU | PGE | SIGNAL NAME     | GGU | PGE |

| GRST        | G4  | 20  | HBE0/GPA0       | B11 | 111 | PCI_AD10    | N6  | 52  | PCI_SERR        | N2  | 38  |

| GND         | E3  | 10  | HBE1/GPA1       | A12 | 110 | PCI_AD11    | N5  | 48  | PCI_STOP        | L3  | 34  |

| GND         | H2  | 22  | HCNTL0/GPA3     | B12 | 108 | PCI_AD12    | M5  | 47  | PCI_TRDY        | L1  | 32  |

| GND         | K3  | 31  | HCNTL1/GPA4     | B13 | 107 | PCI_AD13    | L5  | 46  | PME             | N11 | 68  |

| GND         | M4  | 43  | HCS0            | D12 | 102 | PCI_AD14    | K5  | 45  | RSVD            | M1  | 35  |

| GND         | M6  | 51  | HCS1            | D11 | 103 | PCI_AD15    | N4  | 44  | RSVD            | M2  | 36  |

| GND         | L9  | 63  | HCS2            | C13 | 104 | PCI_AD16    | J2  | 26  | RSVD            | M11 | 69  |

| GND         | K10 | 77  | HCS3            | C12 | 105 | PCI_AD17    | J1  | 25  | RSVD            | C6  | 131 |

| GND         | H12 | 87  | HDS/GP_CS       | A11 | 112 | PCI_AD18    | H4  | 24  | RSVD            | D6  | 132 |

| GND         | D13 | 101 | HINT0           | L13 | 76  | PCI_AD19    | НЗ  | 23  | RSVD            | A5  | 133 |

| GND         | C9  | 118 | HINT1           | K11 | 78  | PCI_AD20    | G2  | 17  | RSVD            | B5  | 134 |

| GP_INT      | M13 | 74  | HINT2           | K12 | 79  | PCI_AD21    | F1  | 16  | RSVD            | C5  | 135 |

| GP_RDY      | L12 | 75  | HINT3           | K13 | 80  | PCI_AD22    | F2  | 15  | RSVD            | D5  | 136 |

| GP_RST      | L11 | 70  | HR/W/GPA5       | C11 | 106 | PCI_AD23    | F3  | 14  | RSVD            | A4  | 137 |

| GPIO0       | A8  | 124 | HRDY5x0/HRDY6x0 | В9  | 119 | PCI_AD24    | E4  | 9   | RSVD            | В4  | 138 |

| GPIO1       | В7  | 125 | HRDY5x1/HRDY6x1 | A9  | 120 | PCI_AD25    | D1  | 8   | RSVD            | C4  | 139 |

| GPIO2       | A7  | 126 | HRDY5x2/HRDY6x2 | D8  | 121 | PCI_AD26    | D2  | 7   | RSVD            | АЗ  | 140 |

| GPIO3       | C7  | 127 | HRDY5x3/HRDY6x3 | C8  | 122 | PCI_AD27    | D3  | 6   | RSVD            | В3  | 141 |

| GPIO4       | A6  | 129 | HRST0           | C10 | 114 | PCI_AD28    | C1  | 4   | RSVD            | C3  | 142 |

| GPIO5       | В6  | 130 | HRST1           | B10 | 115 | PCI_AD29    | C2  | 3   | RSVD            | A2  | 143 |

| HAD0/GPD0   | J11 | 82  | HRST2           | A10 | 116 | PCI_AD30    | B1  | 2   | RSVD            | B2  | 144 |

| HAD1/GPD1   | J12 | 83  | HRST3           | D9  | 117 | PCI_AD31    | A1  | 1   | VCC             | D4  | 5   |

| HAD2/GPD2   | J13 | 84  | HSENUM          | N12 | 71  | PCI_C/BE0   | K7  | 56  | VCC             | F4  | 13  |

| HAD3/GPD3   | H10 | 85  | HSLED           | M12 | 72  | PCI_C/BE1   | L4  | 42  | V <sub>CC</sub> | J3  | 27  |

| HAD4/GPD4   | H11 | 86  | HSSWITCH        | N13 | 73  | PCI_C/BE2   | J4  | 28  | VCC             | N3  | 40  |

| HAD5/GPD5   | H13 | 88  | HWIL/GPA2       | A13 | 109 | PCI_C/BE3   | E2  | 11  | VCC             | K6  | 49  |

| HAD6/GPD6   | G12 | 89  | PCI_AD0         | M10 | 66  | PCI_DEVSEL  | L2  | 33  | VCC             | N8  | 57  |

| HAD7/GPD7   | G13 | 90  | PCI_AD1         | N10 | 65  | PCI_FRAME   | K1  | 29  | VCC             | L10 | 67  |

| HAD8/GPD8   | G10 | 92  | PCI_AD2         | K9  | 64  | PCI_IDSEL   | E1  | 12  | VCC             | J10 | 81  |

| HAD9/GPD9   | F13 | 93  | PCI_AD3         | M9  | 62  | PCI_INTA    | L6  | 50  | VCC             | F11 | 95  |

| HAD10/GPD10 | F12 | 94  | PCI_AD4         | N9  | 61  | PCI_IRDY    | K2  | 30  | V <sub>CC</sub> | D10 | 113 |

| HAD11/GPD11 | F10 | 96  | PCI_AD5         | K8  | 60  | PCI_LOCK    | K4  | 41  | V <sub>CC</sub> | D7  | 128 |

| HAD12/GPD12 | E13 | 97  | PCI_AD6         | L8  | 59  | PCI_PAR     | МЗ  | 39  | Vссн            | G11 | 91  |

| HAD13/GPD13 | E12 | 98  | PCI_AD7         | M8  | 58  | PCI_PCLK    | H1  | 21  | Vссн            | B8  | 123 |

| HAD14/GPD14 | E11 | 99  | PCI_AD8         | N7  | 54  | PCI_PERR    | N1  | 37  | VCCP            | G1  | 18  |

| HAD15/GPD15 | E10 | 100 | PCI_AD9         | M7  | 53  | PCI_RST     | G3  | 19  | VCCP            | L7  | 55  |

The terminals are grouped in tables by functionality, such as PCI system function, power-supply function, etc. The terminal numbers are also listed for convenient reference.

Table 2–3. Power Supply

|      | TERMINAL                                          | -                                                       |                                                                                                                                                       |  |  |  |  |

|------|---------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|      | NO                                                | O.                                                      | DESCRIPTION                                                                                                                                           |  |  |  |  |

| NAME | PGE                                               | GGU                                                     |                                                                                                                                                       |  |  |  |  |

| GND  | 10, 22, 31, 43,<br>51, 63, 77, 87,<br>101, 118    | C9, D13, E3,<br>H2, H12, K3,<br>K10, L9, M4,<br>M6      | Device ground terminals                                                                                                                               |  |  |  |  |

| Vcc  | 5, 13, 27, 40,<br>49, 57, 67, 81,<br>95, 113, 128 | D4, D7, D10,<br>F4, F11, J3,<br>J10, K6, L10,<br>N3, N8 | Power supply terminal for core logic (3.3 V)                                                                                                          |  |  |  |  |

| Vссн | 91, 123                                           | G11, B8                                                 | HPI interface signaling voltage. The $V_{\mbox{CCH}}$ input indicates the signaling level for the HPI interface and is nominally either 3.3 V or 5 V. |  |  |  |  |

| VCCP | 18, 55                                            | G1, L7                                                  | PCI interface signaling voltage. The $V_{\mbox{CCP}}$ input indicates the signaling level for the PCI interface and is nominally either 3.3 V or 5 V. |  |  |  |  |

Table 2-4. PCI System Terminal Functions

| TERMINAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                        |                                                                                                                     | -           |                                                                                         |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------|-----------------------------------------------------------------------------------------|--|--|--|--|

| NO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                        | I/O                                                                                                                 | DESCRIPTION |                                                                                         |  |  |  |  |

| NAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | PGE                                                                                    | GGU                                                                                                                 |             |                                                                                         |  |  |  |  |

| PCI_AD31 PCI_AD30 PCI_AD29 PCI_AD28 PCI_AD26 PCI_AD25 PCI_AD24 PCI_AD23 PCI_AD22 PCI_AD21 PCI_AD20 PCI_AD19 PCI_AD16 PCI_AD15 PCI_AD15 PCI_AD15 PCI_AD11 PCI_AD11 PCI_AD10 PCI_AD2 | PGE  1 2 3 4 6 7 8 9 14 15 16 17 23 24 25 26 44 45 46 47 48 52 53 54 58 59 60 61 62 64 | GGU  A1  B1  C2  C1  D3  D2  D1  E4  F3  F2  F1  G2  H3  H4  J1  J2  N4  K5  N5  N6  M7  N7  M8  L8  K8  N9  M9  K9 | I/O         | 32-bit multiplexed address/data bus                                                     |  |  |  |  |

| PCI_AD1<br>PCI_AD0<br>PCI_C/BE3<br>PCI_C/BE2<br>PCI_C/BE1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 65<br>66<br>11<br>28<br>42                                                             | N10<br>M10<br>E2<br>J4<br>L4                                                                                        | ı           | PCI command and byte enable                                                             |  |  |  |  |

| PCI_C/BE0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 56                                                                                     | K7                                                                                                                  |             |                                                                                         |  |  |  |  |

| PCI_PCLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 21                                                                                     | H1                                                                                                                  | 1           | PCI clock. Provides timing for all PCI transactions with a maximum frequency of 33 MHz. |  |  |  |  |

| PCI_DEVSEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 33                                                                                     | L2                                                                                                                  | 0           | Device select                                                                           |  |  |  |  |

| PCI_FRAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 29                                                                                     | K1                                                                                                                  | ı           | PCI cycle frame                                                                         |  |  |  |  |

| PCI_IDSEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12                                                                                     | E1                                                                                                                  | I           | Initialization and device select                                                        |  |  |  |  |

| PCI_INTA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 50                                                                                     | L6                                                                                                                  | 0           | Interrupt A. INTA indicates to the host that PCI2040 requires attention.                |  |  |  |  |

| PCI_IRDY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 30                                                                                     | K2                                                                                                                  | I           | Initiator ready                                                                         |  |  |  |  |

| PCI_LOCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 41                                                                                     | K4                                                                                                                  | ı           | PCI lock                                                                                |  |  |  |  |

| PCI_PAR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 39                                                                                     | M3                                                                                                                  | I/O         | PCI parity                                                                              |  |  |  |  |

| PCI_PERR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 37                                                                                     | N1                                                                                                                  | I/O         | Parity error                                                                            |  |  |  |  |

| PCI_RST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 19                                                                                     | G3                                                                                                                  | I           | PCI reset. Assertion forces PCI2040 non-PME context to a predetermined state.           |  |  |  |  |

| PCI_SERR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 38                                                                                     | N2                                                                                                                  | 0           | System error                                                                            |  |  |  |  |

| PCI_STOP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 34                                                                                     | L3                                                                                                                  | 0           | PCI stop                                                                                |  |  |  |  |

| PCI_TRDY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 32                                                                                     | L1                                                                                                                  | 0           | Target ready                                                                            |  |  |  |  |

Table 2-5. Miscellaneous Terminal Functions

| TERMINAL                         |                           |                                                         |     |                                                                                                                                                                                                                                                        |  |  |  |  |                                                                                                                                                                                 |

|----------------------------------|---------------------------|---------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                             | NO                        | <b>)</b> .                                              | I/O | DESCRIPTION                                                                                                                                                                                                                                            |  |  |  |  |                                                                                                                                                                                 |

| NAME                             | PGE                       | GGU                                                     |     |                                                                                                                                                                                                                                                        |  |  |  |  |                                                                                                                                                                                 |

| GRST                             | 20                        | G4                                                      | I   | Global reset. This is a power-on reset to PCI2040 that indicates that a power has been applied to the V <sub>CC</sub> terminals. GRST resets all register bits in PCI2040.                                                                             |  |  |  |  |                                                                                                                                                                                 |

| PME                              | 68                        | N11                                                     | 0   | Power management event. This output indicates PCI power management wake-up events to the host, and requires open-drain, fail-safe signaling per the <i>PCI Bus Power Management Interface Specification</i> .                                          |  |  |  |  |                                                                                                                                                                                 |

|                                  |                           |                                                         |     | General-purpose inputs/output. With some exceptions, these terminals provide basic general-purpose input and output functionality programmable through the PCI2040.                                                                                    |  |  |  |  |                                                                                                                                                                                 |

| GPIO5                            | 130                       | B6                                                      |     | The GPIO3 and GPIO2 inputs may be programmed to generate generic interrupt events. See Section 3.7.4, <i>General-Purpose Interrupts</i> , for details.                                                                                                 |  |  |  |  |                                                                                                                                                                                 |

| GPIO4<br>GPIO3<br>GPIO2<br>GPIO1 | 126 A7                    |                                                         | I/O | GPIO0 is sampled on GRST to determine if a serial ROM is implemented. If GPIO0 is sampled high on GRST assertions, then the serial ROM clock (SCL) is routed to the GPIO0 terminal and the serial ROM data line (SDA) is routed to the GPIO1 terminal. |  |  |  |  |                                                                                                                                                                                 |

| GPIO0                            | 124                       | 125 B7<br>124 A8                                        |     |                                                                                                                                                                                                                                                        |  |  |  |  | GPIO4. GP write strobe. This active low signal is used to indicate a read from a device on the bus. The data on the bus is valid on the rising edge of $\overline{\text{WR}}$ . |

|                                  |                           |                                                         |     | GPIO5. GP read strobe. This active low signal is used to indicate a write to a device on the bus. The data on the bus is valid on the rising edge of $\overline{\text{RD}}$ .                                                                          |  |  |  |  |                                                                                                                                                                                 |

| RSVD                             | 35, 36,<br>69,<br>131–144 | A2-A5,<br>B2-B5,<br>C3-C6,<br>D5, D6,<br>M1, M2,<br>M11 | NC  | Reserved. These terminals are not connected in PCI2040 implementations.                                                                                                                                                                                |  |  |  |  |                                                                                                                                                                                 |

Table 2-6. Host Port Interface Terminal Functions

| TERMINA                                                                               | AL                                                                                            |                                                                                                              |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                       | N                                                                                             | 0.                                                                                                           | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| NAME                                                                                  | PGE                                                                                           | GGU                                                                                                          |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| HAD15 HAD14 HAD13 HAD12 HAD11 HAD10 HAD9 HAD8 HAD7 HAD6 HAD5 HAD4 HAD3 HAD2 HAD1 HAD0 | 100<br>99<br>98<br>97<br>96<br>94<br>93<br>92<br>90<br>89<br>88<br>86<br>85<br>84<br>83<br>82 | E10<br>E11<br>E12<br>E13<br>F10<br>F12<br>F13<br>G10<br>G13<br>G12<br>H13<br>H11<br>H10<br>J13<br>J12<br>J11 | I/O | Data. A 16-bit parallel, bidirectional, and 3-state data bus used to access registers on external devices controlled by PCI2040. HAD15 is MSB and HAD0 is LSB.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| HR/W/GPA5                                                                             | 106                                                                                           | C11                                                                                                          | 0   | Read/Write. The PCI2040 drives this signal to 0 on a host port interface for a write and to 1 on a host port interface for a read.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| HDS/GP_CS                                                                             | 112                                                                                           | A11                                                                                                          | 0   | Read strobe/data strobe. Active low signal that controls the transfer of data during an HPI cycle, and indicates to the DSP that the data on HAD15–HAD0 is valid. This signal must be connected to HDS1 or HDS2 on the DSP. Unused DSP HDSx inputs must be tied high.                                                                                                                                                                                                                                                                                                                 |

| HINT3<br>HINT2<br>HINT1<br>HINT0                                                      | 80<br>79<br>78<br>76                                                                          | K13<br>K12<br>K11<br>L13                                                                                     | I   | HPI Interrupts. These four interrupts from the DSPs are connected point-to-point between PCI2040 and each implemented DSP. The PCI2040 may be programmed to assert a PCI interrupt when the DSPs assert any HINT3—HINT0. From the DSP perspective, these signals are controlled by the HINT bit in the HPI control register and are driven high when the DSPs are being reset (and placed in high impedance when EMU1/OFF is asserted).                                                                                                                                               |

| HBE1/GPA1<br>HBE0/GPA0                                                                | 110<br>111                                                                                    | A12<br>B11                                                                                                   | 0   | Byte enables. These active low signals are only used when communicating with the C6x DSP. They indicate which bytes of the data bus are valid when writing to the C6x HPI data register and are not meaningful in any other conditions.                                                                                                                                                                                                                                                                                                                                               |

| HWIL/GPA2                                                                             | 109                                                                                           | A13                                                                                                          | 0   | Half-word identification select. Identifies first or second half-word of transfer. HWIL is low for the first half-word and high for the second half-word. This is not to be confused with the BOB bit in the DSP HPI control register which controls MSB/LSB from the DSP perspective.                                                                                                                                                                                                                                                                                                |

| HCNTL1/GPA4<br>HCNTL0/GPA3                                                            | 107<br>108                                                                                    | B13<br>B12                                                                                                   | 0   | Control signals for DSP access mode. Selects an access to DSP HPI address register, HPI control register, or HPI data register (and controls auto-increment). The HCNTL1 and HCNTL0 combinations are different for C54x and C6x DSPs.                                                                                                                                                                                                                                                                                                                                                 |

| HCS3<br>HCS2<br>HCS1<br>HCS0                                                          | 105<br>104<br>103<br>102                                                                      | C12<br>C13<br>D11<br>D12                                                                                     | 0   | Chip selects. These four chip selects to the DSPs are connected point-to-point between PCI2040 and each implemented DSP. The input to the DSP serves as an enable input for the HPI and must be low during an access and may stay low between accesses.                                                                                                                                                                                                                                                                                                                               |

| HRDY5x3/HRDY6x3<br>HRDY5x2/HRDY6x2<br>HRDY5x1/HRDY6x1<br>HRDY5x0/HRDY6x0              | 122<br>121<br>120<br>119                                                                      | C8<br>D8<br>A9<br>B9                                                                                         | ı   | Host ready signals. These ready signals from the DSPs are connected point-to-point between PCI2040 and each implemented DSP. This ready signal is active high for C54x DSPs and active low for C6x DSPs. When asserted, it indicates that the DSP is ready for a transfer to be performed, and is deasserted when the DSP is busy completing the internal portion of the previous transaction. HCS enables HRDY for the DSP; that is, HRDY is always asserted when the chip selects are deasserted. The DSP places this ready signal in high impedance when EMU1/OFF is active (low). |

| HRST3<br>HRST2<br>HRST1<br>HRST0                                                      | 117<br>116<br>115<br>114                                                                      | D9<br>A10<br>B10<br>C10                                                                                      | 0   | Host-to-DSP resets. These active low reset signals to the DSPs are connected point-to-point between PCl2040 and each implemented DSP. The PCl2040 resets the DSPs when GRST is asserted. It is software's responsibility to deassert HRSTn.                                                                                                                                                                                                                                                                                                                                           |

Table 2-7. Compact PCI Hot Swap Interface

| TERMINAL |        |     |   |                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|----------|--------|-----|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|          |        | NO. |   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| NAME     | GGU    |     |   |                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| HSENUM   | 71 N12 |     | 0 | Hot swap ENUM. This is an active low open drain signaling output that is asserted when either bit 7 (INS) or bit 6 (EXT) are set and bit 1 (EIM) is cleared in the CPCI hot swap control and status register (see Section 4.35). This output indicates to the system that an insertion event occurred or that a removal event is about to occur.                                                          |  |  |  |  |  |

| HSLED    | 72 M12 |     | 0 | Hot swap LED. This output is controlled via bit 3 (LOO) in the CPCI hot swap control and status register (see Section 4.35) and is provided to indicate when a hot-swap device is about to be removed. When PCI_RST is asserted to PCI2040, it drives this LED output until the serial ROM has completed preload and the ejector switch has been closed indicated by the HSSWITCH input.                  |  |  |  |  |  |

| HSSWITCH | 73     | N13 | ı | Hot swap handle switch. This input provides status of the ejector handle state and is used in the bit 7 (INS) and bit 6 (EXT) logic in the CPCI hot swap control and status register (see Section 4.35). The status of HSSWITCH is not directly read via CPCI hot swap control and status register but can be read through bit 8 (HSSWITCH_STS) in the miscellaneous control register (see Section 4.26). |  |  |  |  |  |

Table 2–8. General-Purpose Bus Interface

| TERM                                                                                                                                       | INIAI                                                                                   |                                                                                                              |     |                                                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IERIVI                                                                                                                                     | INAL<br>N                                                                               | <u> </u>                                                                                                     | I/O | DESCRIPTION                                                                                                                                                                                          |

| NAME                                                                                                                                       | PGE                                                                                     | GGU                                                                                                          | 1/0 | DESCRIPTION                                                                                                                                                                                          |

| GPD15<br>GPD14<br>GPD13<br>GPD12<br>GPD11<br>GPD10<br>GPD9<br>GPD8<br>GPD7<br>GPD6<br>GPD5<br>GPD5<br>GPD4<br>GPD3<br>GPD3<br>GPD2<br>GPD1 | 100<br>99<br>98<br>97<br>96<br>94<br>93<br>92<br>90<br>89<br>88<br>86<br>85<br>84<br>83 | E10<br>E11<br>E12<br>E13<br>F10<br>F12<br>F13<br>G10<br>G13<br>G13<br>G12<br>H13<br>H11<br>H10<br>J13<br>J12 | I/O | GP data bus. 16-bit data bus.                                                                                                                                                                        |

| GPD0  GPA5 GPA4 GPA3 GPA2 GPA1 GPA0                                                                                                        | 82<br>106<br>107<br>108<br>109<br>110<br>111                                            | J11<br>C11<br>B13<br>B12<br>A13<br>A12<br>B11                                                                | I/O | GP address lines. 6-bit address bus.                                                                                                                                                                 |

| GP_CS                                                                                                                                      | 112                                                                                     | A11                                                                                                          | 0   | GP chip select                                                                                                                                                                                       |

| GP_INT                                                                                                                                     | 74                                                                                      | M13                                                                                                          | I/O | GP interrupt. Interrupt from a device on the GP bus.                                                                                                                                                 |

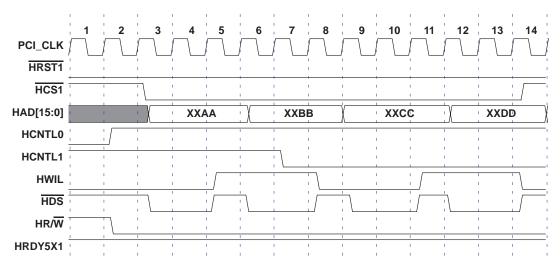

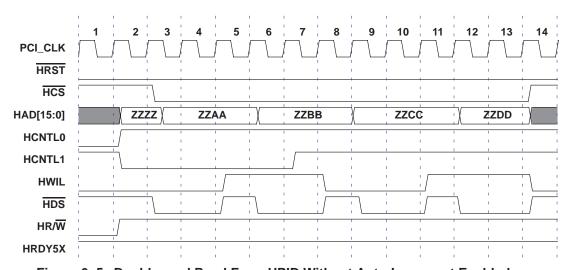

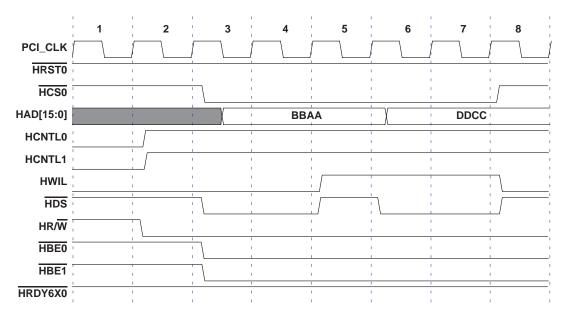

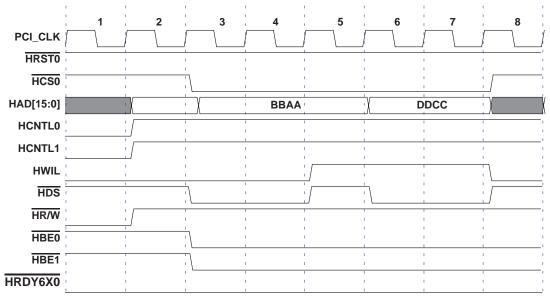

| GP_RD                                                                                                                                      | 130                                                                                     | B6                                                                                                           | I/O | GP read.                                                                                                                                                                                             |