SLVSAD1B - JUNE 2010 - REVISED JANUARY 2016

**TPS80010**

# TPS80010 PMU for Alkaline Battery-Powered Applications

#### **Features**

- 1.8-V Buck DC-DC Converter

- 3.1-V Boost DC-DC Converter with 3-V Post-Regulation LDO

- Over 91% Conversion Efficiency

- Current-Limited Start-Up for Both DC-DC Converters

- Load Switch With Current-Limited Turnon

- Battery-Level Monitor Switch

- 32-Pin, 4-mm x 4-mm x 1-mm VQFN Package

- ESD Performance Tested per JESD 22

- 2000-V Human-Body Model (A114-B, Class II)

- 500-V Charged-Device Model (C101)

# 2 Applications

- Wireless Mice

- Wireless Keyboards

- **Game Controllers**

# 3 Description

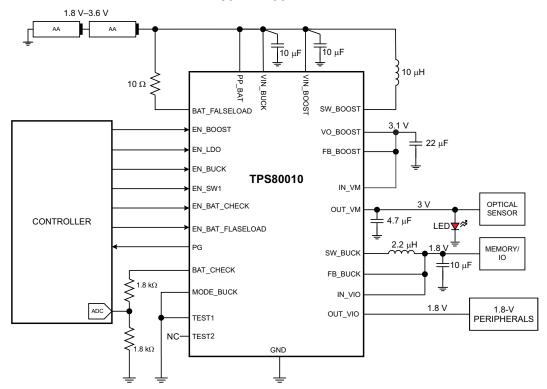

The TPS80010 device provides an integrated powermanagement solution for 2-cell alkaline battery applications such as wireless mice, keyboards, and video game controllers. The VBUCK 1.8-V output is powered by a buck converter with a load capacity of 100 mA. A Power Good (PG) signal is generated when VBUCK is greater than 90% of its target output voltage. Integrated in the TPS80010 is an  $80\text{-m}\Omega$ load switch that can be connected to the VBUCK output, allowing more system design flexibility when connecting to multiple loads. The 3.1-V VBOOST output is powered by a boost converter. The VBOOST output voltage is post-regulated by the integrated 3-V LDO. This post-regulation provides a low-noise supply level through the specified battery range.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| TPS80010    | VQFN (32) | 4.00 mm × 4.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

# **Typical Application**

# **Table of Contents**

| 3 Description                                | Il Modes                 |

|----------------------------------------------|--------------------------|

| 3 Description 1 8 Application and            | nlamantation 4           |

| -                                            | piementation 1           |

| 4 Revision History                           | nation1                  |

|                                              | on 1                     |

| 6 Specifications                             | ommendations1            |

| 6.1 Absolute Maximum Ratings                 | <u>2</u>                 |

| 6.2 ESD Ratings                              | es 2                     |

| 0.2 EOD Ratingo                              | · 2                      |

| 6.4 Thermal Information 5 11 Device and Doct | entation Support2        |

|                                              | 2                        |

|                                              | ources 2                 |

|                                              | 2                        |

|                                              | charge Caution2          |

| 7.1 Overview                                 | 2                        |

| 7.2 Functional Block Diagram                 | ging, and Orderable<br>2 |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

# Changes from Revision A (June 2010) to Revision B

**Page**

- Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section

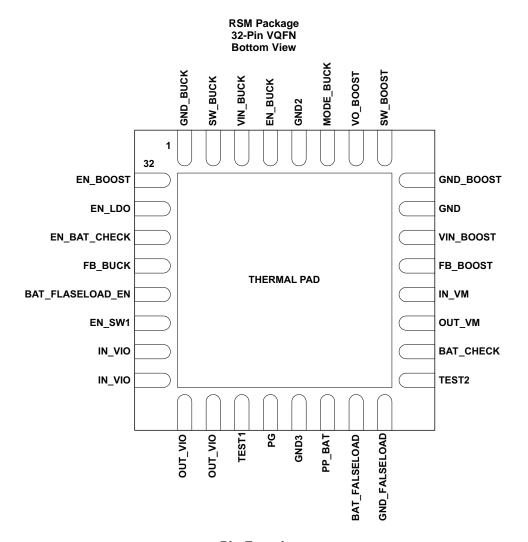

# 5 Pin Configuration and Functions

# **Pin Functions**

| PIN              |     | 1/0 | DECODINE                                                               |  |  |

|------------------|-----|-----|------------------------------------------------------------------------|--|--|

| NAME             | NO. | 1/0 | DESCRIPTION                                                            |  |  |

| BAT_CHECK        | 15  | 0   | Battery monitor switch output. Connect to ADC for battery-level check. |  |  |

| BAT_FALSELOAD    | 18  | I   | Battery monitor input for false-load check                             |  |  |

| BAT_FALSELOAD_EN | 28  | I   | Battery false load switch enable                                       |  |  |

| EN_BAT_CHECK     | 30  | I   | Battery-check path enable                                              |  |  |

| EN_BOOST         | 32  | I   | Boost converter enable                                                 |  |  |

| EN_BUCK          | 4   | I   | Buck converter enable                                                  |  |  |

| EN_LDO           | 31  | I   | Boost post-regulation LDO enable                                       |  |  |

| EN_SW1           | 27  | I   | Buck-load switch (SW1) enable                                          |  |  |

| FB_BOOST         | 12  | I   | Boost-converter feedback input                                         |  |  |

| FB_BUCK          | 29  | I   | Buck converter feedback input                                          |  |  |

| GND              | 10  | _   | Ground                                                                 |  |  |

| GND2             | 5   | _   | Device ground                                                          |  |  |

| GND3             | 20  | _   | Device ground                                                          |  |  |

| GND_BOOST        | 9   | _   | Boost converter ground                                                 |  |  |

| GND_BUCK         | 1   | _   | Buck converter ground                                                  |  |  |

Copyright © 2010–2016, Texas Instruments Incorporated

Submit Documentation Feedback

# Pin Functions (continued)

| PIN           |        | 1/0 | DESCRIPTION                                                                       |

|---------------|--------|-----|-----------------------------------------------------------------------------------|

| NAME          | NO.    | 1/0 | DESCRIPTION                                                                       |

| GND_FALSELOAD | 17     | 0   | False load ground                                                                 |

| IN_VIO        | 25, 26 | _   | Internal I/O power supply. Load switch 1 input. Connect externally to buck output |

| IN_VM         | 13     | 1   | Boost post-regulation LDO input. Connect externally to VO_BOOST.                  |

| MODE_BUCK     | 6      | - 1 | Buck converter mode control. High for PWM, low for PFM.                           |

| OUT_VIO       | 23, 24 | 0   | Load switch 1 output                                                              |

| OUT_VM        | 14     | 0   | Boost post-regulation LDO output                                                  |

| PG            | 21     | 0   | Buck Power Good indication output. High when V <sub>BUCK</sub> > 1.7 V.           |

| PP_BAT        | 19     | I   | Battery input for level check                                                     |

| SW_BOOST      | 8      | I/O | Boost converter switching node. Inductor connection.                              |

| SW_BUCK       | 2      | 0   | Buck converter switching output. Inductor connection.                             |

| TEST1         | 22     | I/O | Test pin1 (tie to GND)                                                            |

| TEST2         | 16     | 0   | Test pin 2 (do not connect)                                                       |

| VIN_BOOST     | 11     | -   | Boost-converter power supply                                                      |

| VIN_BUCK      | 3      | _   | Buck converter power supply                                                       |

| VO_BOOST      | 7      | 0   | Boost converter regulated output                                                  |

Submit Documentation Feedback

Copyright © 2010–2016, Texas Instruments Incorporated

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                  |                           | MIN  | MAX | UNIT |

|------------------|---------------------------|------|-----|------|

| $V_{I}$          | Input voltage (all pins)  | -0.3 | 3.6 | V    |

| Vo               | Output voltage (all pins) | -0.3 | 3.6 | V    |

| $T_{J}$          | Junction temperature      | -40  | 125 | °C   |

| T <sub>stg</sub> | Storage temperature       | -65  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                    |                         |                                                                               | MAX   | UNIT |

|--------------------|-------------------------|-------------------------------------------------------------------------------|-------|------|

| V                  | Floatrootatia dioabaraa | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>   | ±2000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins (2) | ±500  | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

$T_A = 0$ °C to 85°C; typical values are at  $T_A = 25$ °C

|                          |                                                 | MIN  | NOM | MAX       | UNIT |

|--------------------------|-------------------------------------------------|------|-----|-----------|------|

| $V_{BAT}$                | Input voltage, VIN BOOST, VIN_BUCK, PP_BAT pins | 1.95 |     | 3.6       | V    |

| V <sub>IO</sub> (IN_VIO) | Digital I/O operating voltage                   |      | 1.8 | $V_{BAT}$ | V    |

| T <sub>A</sub>           | Ambient temperature                             | 0    | 25  | 85        | °C   |

## 6.4 Thermal Information

|                       |                                              | TPS80010   |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RSM (VQFN) | UNIT |

|                       |                                              | 32 PINS    |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 37.4       | °C/W |

| $R_{\theta JC(top)}$  | Junction-to-case (top) thermal resistance    | 31.8       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 8.2        | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 0.4        | °C/W |

| Ψјв                   | Junction-to-board characterization parameter | 8.2        | °C/W |

| R <sub>θJC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 2.5        | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

# 6.5 Electrical Characteristics

$T_A = 0$ °C to 85°C; typical values are at  $T_A = 25$ °C (unless otherwise noted)

|                       | PARAMETER                       | TEST CONDITIONS                                                                                        | MIN                   | TYP   | MAX                              | UNIT |

|-----------------------|---------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------|-------|----------------------------------|------|

| SUPPLY CU             | IRRENT                          |                                                                                                        |                       |       |                                  |      |

| IQ                    | Quiescent current               | V <sub>BAT</sub> = 3 V, all modules enabled                                                            |                       | 51    |                                  | μА   |

| loff                  | Off current                     | V <sub>BAT</sub> = 3 V                                                                                 |                       | 1     |                                  | μA   |

| DIGITAL I/O           |                                 |                                                                                                        |                       |       |                                  | •    |

| R <sub>PULLDOWN</sub> | Internal pulldown resistor      | EN_BOOST, EN_LDO, EN_SW1,<br>EN_BAT_CHECK, EN_BAT_FALSELOAD                                            | 157                   | 275   | 383                              | kΩ   |

| V <sub>IH</sub>       | Input logic-high voltage        | EN_BOOST, EN_LDO, EN_SW1,<br>EN_BAT_CHECK, EN_BAT_FALSELOAD                                            | 0.7 × V <sub>IO</sub> |       |                                  | V    |

|                       |                                 | EN_BUCK, BUCK_MODE                                                                                     | $0.7 \times V_{BAT}$  |       |                                  |      |

| V <sub>IL</sub>       | Input logic-low voltage         | EN_BOOST, EN_LDO, EN_SW1,<br>EN_BAT_CHECK, EN_BAT_FALSELOAD                                            |                       |       | 0.3 × V <sub>IO</sub>            | V    |

| VIL                   | input logic-low voltage         | EN_BUCK, BUCK_MODE                                                                                     |                       |       | 0.7 <b>×</b><br>V <sub>BAT</sub> | V    |

| V <sub>OH</sub>       | Output logic-high voltage       | PG                                                                                                     | V <sub>IO</sub> - 0.2 |       |                                  | V    |

| V <sub>OL</sub>       | Output logic-low voltage        | PG                                                                                                     |                       |       | 0.2                              | V    |

| I <sub>L_DIG</sub>    | Logic-output load current       |                                                                                                        |                       |       | 1                                | mA   |

| V <sub>IN</sub>       | Input voltage at VIN BUCK       |                                                                                                        | 1.95                  |       | 3.6                              | V    |

| Io                    | Output current                  |                                                                                                        |                       |       | 100                              | mA   |

| V <sub>FB</sub>       | Feedback voltage (output        | PWM, $I_O = 0$ mA to 100 mA,<br>$V_{IN} \ge 1.85$ V to 3.6 V, $V_{BUCK} = 1.8$ V                       | -1.5%                 |       | 1.5%                             |      |

| . 5                   | accuracy)                       | PFM                                                                                                    |                       | 1     |                                  |      |

| V <sub>BUCK</sub>     | Buck output voltage             |                                                                                                        |                       | 1.8   |                                  | V    |

| $I_{SW}$              | Switch current limit            |                                                                                                        | 0.56                  | 0.7   | 0.84                             | Α    |

| I <sub>RUSH</sub>     | Inrush current                  | $V_{IN} = 2 V$                                                                                         |                       | 150   |                                  | mA   |

|                       | Line regulation                 | PWM, $I_O = 100 \text{ mA}$                                                                            |                       | 0.9%  |                                  |      |

|                       | Line regulation                 | PFM, I <sub>O</sub> = 100 mA                                                                           |                       | 0.9%  |                                  |      |

|                       | Load regulation                 | PWM, $V_{IN} = 2.4 \text{ V}$ , $I_O = 0 \text{ mA}$ to 100 mA                                         |                       | -0.5% |                                  |      |

|                       | Load regulation                 | PFM, $V_{IN} = 2.4 \text{ V}$ , $I_O = 0 \text{ mA to } 100 \text{ mA}$                                |                       | 0.5%  |                                  |      |

|                       | Efficiency                      | PFM , $I_O = 100$ mA, $V_{IN} = 2.4$ V, $V_{BUCK} = 1.8$ V                                             |                       | 92%   |                                  |      |

|                       | Lindency                        | PWM, $I_O = 100$ mA, $V_{IN} = 2.4$ V, $V_{BUCK} = 1.8$ V                                              |                       | 90%   |                                  |      |

|                       |                                 | PFM, $I_O = 0$ mA, no switching                                                                        |                       | 21    |                                  | μА   |

|                       | Quiescent current               | PFM, $I_O = 0$ mA, switching                                                                           |                       | 25    |                                  | μΛ   |

| lo                    |                                 | PWM, $I_O = 0 \text{ mA}$                                                                              |                       | 5     |                                  | mA   |

| 'Q                    | Shutdown current                |                                                                                                        |                       | 0.005 | 0.15                             | μΑ   |

|                       | Leakage current into SW_BUCK    |                                                                                                        |                       | 0.01  | 1                                | μА   |

| R <sub>REC</sub>      | Rectifier on-resistance         | $V_{GS} = 3.6 \text{ V}$                                                                               |                       | 185   | 380                              | mΩ   |

| R <sub>MAIN</sub>     | Main SW on-resistance           | V <sub>GS</sub> = 3.6 V                                                                                |                       | 240   | 480                              | mΩ   |

| $\Delta V_{LN}$       | Line transient output variation | PFM, $I_O = 50$ mA, $V_{IN} = 2$ V $\rightarrow 3.6$ V, $\Delta t = 25$ $\mu s$                        |                       | 10    | 20                               | mV   |

| $\Delta V_{LD}$       | Load transient output variation | PFM, $V_{IN}$ = 2.4 V, $V_{BUCK}$ = 1.8 V, $I_{O}$ = 1 mA $\rightarrow$ 100 mA, $\Delta t$ = 1 $\mu s$ |                       | 30    | 40                               | mV   |

| V                     | Output ripple                   | PWM, $I_0 = 100 \text{ mA}$ , $V_{IN} = 2.4 \text{ V}$                                                 |                       | 1     | 10                               | mVpp |

| $V_{RIP}$             | Output rippie                   | PFM, $I_0 = 10 \text{ mA}$ , $V_{IN} = 3.6 \text{ V}$                                                  |                       | 10    | 20                               | mypp |

| $f_{SW}$              | Switching frequency             |                                                                                                        | 2                     | 2.25  | 2.5                              | MHz  |

| UVLO                  | Undervoltage lockout threshold  |                                                                                                        |                       | 1.7   |                                  | V    |

| C <sub>L</sub>        | Load capacitance                |                                                                                                        |                       | 10    |                                  | μF   |

| L                     | Inductor                        |                                                                                                        |                       | 2.2   |                                  | μН   |

# **Electrical Characteristics (continued)**

$T_A = 0$ °C to 85°C; typical values are at  $T_A = 25$ °C (unless otherwise noted)

| 1 <sub>A</sub> – 0 C lC | · · · · · · · · · · · · · · · · · · · | \(\) = 25°C (unless otherwise noted)                                                              |      | T)/D | B# 4 37 |        |

|-------------------------|---------------------------------------|---------------------------------------------------------------------------------------------------|------|------|---------|--------|

|                         | PARAMETER                             | TEST CONDITIONS                                                                                   | MIN  | TYP  | MAX     | UNIT   |

| LOAD SWI                | ТСН                                   |                                                                                                   |      |      |         |        |

| R <sub>ON</sub>         | Switch on-resistance                  | V <sub>GS</sub> = 1.8 V                                                                           |      | 80   | 120     | mΩ     |

|                         | Maximum load current                  |                                                                                                   |      |      | 360     | mA     |

|                         | Turnon inrush current                 |                                                                                                   |      |      | 100     | mA     |

| I <sub>OFF</sub>        | Off-state current                     | Switch turned off, I <sub>O</sub> = 0 mA                                                          |      |      | 1       | μΑ     |

| POWER GO                | OOD RESET                             |                                                                                                   |      |      |         |        |

| $V_{THRESH}$            | Power good threshold voltage          |                                                                                                   | 1.68 | 1.7  | 1.72    | V      |

| $V_{HYS}$               | Power good hysteresis                 |                                                                                                   |      | 10   | 15      | mV     |

| BOOST CO                | ONVERTER                              |                                                                                                   |      |      |         | •      |

| V                       | land with an at VINL DOOST            | Boost mode                                                                                        | 1.8  |      | 3.1     |        |

| $V_{IN}$                | Input voltage at VIN_BOOST            | $V_{IN} > V_{BOOST}$ mode, $V_{BOOST} = V_{IN}$                                                   | 3.1  |      | 3.6     | V      |

| V <sub>BOOST</sub>      | Output voltage                        | $T_A = 0$ °C-50°C, $V_{IN} = 1.8$ V to 3.1 V, $I_O = 0$ mA to 50 mA                               | 3    | 3.1  | 3.2     | V      |

| lo                      | Output current                        | V <sub>IN</sub> = 1.8 V to 3.6 V                                                                  |      |      | 50      | mA     |

| I <sub>SW</sub>         | Switch current limit                  |                                                                                                   | 200  | 350  | 475     | mA     |

| I <sub>RUSH</sub>       | Inrush current                        | V <sub>IN</sub> = 2 V                                                                             |      | 150  |         | mA     |

| R <sub>REC</sub>        | Rectifier on-resistance               | V <sub>BOOST</sub> = 3.1 V                                                                        |      | 1    |         | Ω      |

| R <sub>MAIN</sub>       | Main SW on-resistance                 | 50001                                                                                             |      | 1    |         | Ω      |

| IVIZIIN                 | Line regulation                       | V <sub>IN</sub> = 2 V to 3 V, I <sub>O</sub> = 50 mA                                              |      | 0.5% |         |        |

|                         | Load regulation                       | $V_{IN} = 2 \text{ V}, I_{O} = 0-50 \text{ mA}$                                                   |      | 0.5% |         |        |

|                         | Boost efficiency                      | V <sub>IN</sub> = 2.4 V, I <sub>O</sub> = 5 mA                                                    |      | 91%  |         |        |

|                         |                                       | V <sub>IN</sub> = 2.4 V, I <sub>O</sub> = 50 mA                                                   |      | 91   |         |        |

| $f_{SW}$                | Oscillator frequency                  | 1114                                                                                              |      | 625  |         | kHz    |

|                         |                                       | From $V_{IN}$ supply, $I_O = 0$ mA, $V_{IN} = 1.8$ V, $V_{BOOST} = 3.1$ V                         |      | 1    | 2.5     |        |

| IQ                      | Quiescent current                     | From $V_{BOOST}$ , $I_{O}$ = 0 mA, $V_{IN}$ = 1.8 V, $V_{BOOST}$ = 3.1 V                          |      | 4    | 6.5     | μА     |

| u.                      | Shutdown current                      |                                                                                                   |      | 0.1  | 1       |        |

|                         | Leakage current into SW_BOOST         |                                                                                                   |      | 0.1  | 1       |        |

| V <sub>UVLO</sub>       | V <sub>IN</sub> decreasing            |                                                                                                   |      | 0.5  | 0.7     | V      |

| $\Delta V_{LN}$         | Line transient output variation       | $I_O$ = 10 mA, $V_{IN}$ = 1.8 V $\rightarrow$ $V_{BOOST}$ , $\Delta T$ = 25 $\mu s$               |      | 10   |         | mV     |

| $\Delta V_{LD}$         | Load transient output variation       | $V_{IN}$ = 2.4 V, $V_{BOOST}$ = 3.1 V, $I_{O}$ = 1 mA $\rightarrow$ 50 mA, $\Delta t$ = 1 $\mu s$ |      | 5    | 10      | mV     |

| V <sub>RIP</sub>        | Output ripple                         | V <sub>IN</sub> = 1.8 V, I <sub>O</sub> = 50 mA                                                   |      | 4    | 10      | mVpp   |

| I <sub>OFF</sub>        | Off-mode current                      |                                                                                                   |      | 0.1  | 1       | μА     |

| C <sub>L</sub>          | Load capacitance                      |                                                                                                   | 6    | 10   | 22      | μF     |

| L                       | Inductance                            |                                                                                                   |      | 10   |         | μH     |

|                         | SULATION LDO                          |                                                                                                   |      |      |         | F." .  |

| V <sub>IN</sub>         | Input voltage at IN_VM                |                                                                                                   | 3.1  |      | 3.6     | V      |

| V <sub>LDO</sub>        | Output voltage                        | 10 μA ≤ I <sub>O</sub> ≤ I <sub>OMAX</sub>                                                        | 2.91 | 3    | 3.09    | V      |

| I <sub>O</sub>          | Output current                        | Normal mode                                                                                       |      |      | 50      | mA     |

| I <sub>LIMIT</sub>      | Current limit                         | V <sub>LDO</sub> > 1 V                                                                            | 300  | 400  | 500     | mA     |

| I <sub>SHORT</sub>      | Short circuit current                 | Output shorted to ground                                                                          | 30   | 60   | 150     | mA     |

| VREG                    | Line regulation                       | $dV_{LDO}/dV_{IN}$ at $I_O = Max$                                                                 | 30   | 00   | 0.2%    | 111/5  |

| LREG                    | Load regulation                       | V <sub>LDO</sub> (I <sub>OMIN</sub> ) - V <sub>LDO</sub> (I <sub>OMAX</sub> )                     |      |      | 40      | mV     |

|                         |                                       |                                                                                                   |      | 50   | 100     |        |

| $\Delta V_{LN}$         | Load transient response               | $I_O = 20 \text{ mA/}\mu\text{s}, V_{IN} = 3.1 \text{ V}$                                         |      |      |         | mV<br> |

| $I_Q$                   | Quiescent current                     | $I_O = 0 \text{ mA}$                                                                              |      | 16   | 17.6    | μΑ     |

Submit Documentation Feedback

# **Electrical Characteristics (continued)**

$T_A = 0$ °C to 85°C; typical values are at  $T_A = 25$ °C (unless otherwise noted)

|                       | PARAMETER                         | TEST CONDITIONS                                                             | MIN | TYP | MAX             | UNIT |

|-----------------------|-----------------------------------|-----------------------------------------------------------------------------|-----|-----|-----------------|------|

| PSRR                  | Power-supply ripple rejection     | $f = 120 \text{ Hz to 1 kHz at I}_{O} = I_{OMAX}/2, V_{IN} = 3.1 \text{ V}$ | 40  |     |                 | dB   |

| V <sub>RIP_NORM</sub> | Output ripple                     | $V_{BAT}$ < 3.1 V, $I_{O}$ = 50 mA, $V_{IN}$ = $V_{BOOST}$                  |     | 0.1 | 1               | mVpp |

| $V_{RIP\_HIBAT}$      | Output ripple                     | $V_{BAT} > 3.1 \text{ V}, I_{O} = 50 \text{ mA}, V_{IN} = V_{BOOST}$        |     | 4   | 10              | mVpp |

|                       | Paget plus LDO officiancy         | $V_{BAT} = 2.4 \text{ V}, I_O = 5 \text{ mA}, V_{IN} = V_{BOOST}$           |     | 87% |                 |      |

|                       | Boost plus LDO efficiency         | $V_{BAT} = 2.4 \text{ V}, I_O = 50 \text{ mA}, V_{IN} = V_{BOOST}$          |     | 88% |                 |      |

| $C_L$                 | Load capacitance                  | Ceramic capacitor, ESR = 10 m $\Omega$ to 150 m $\Omega$                    | 4.7 | 10  | 22              | μF   |

| BATTERY I             | LOAD MONITOR                      |                                                                             |     |     |                 |      |

| $V_{OP}$              | Operating voltage                 |                                                                             |     | 1.8 | 3.6             | V    |

| V <sub>IN</sub>       | Input voltage at PP_BAT           |                                                                             | 1.8 |     | 3.6             | V    |

| V <sub>OUT</sub>      | Output voltage at BAT_CHECK       |                                                                             |     |     | V <sub>IN</sub> | V    |

| I <sub>LOAD</sub>     | Load current                      |                                                                             |     |     | 10              | mA   |

| R <sub>ON</sub>       | Switch on-resistance              | V <sub>IN</sub> = 1.8 V to 3.6 V                                            |     | 12  | 15              | Ω    |

| BATTERY I             | LOAD SWITCH                       | •                                                                           |     |     |                 |      |

| $V_{OP}$              | Operating voltage                 |                                                                             |     | 1.8 | 3.6             | V    |

| V <sub>IN</sub>       | Input voltage at<br>BAT_FALSELOAD |                                                                             |     |     | 3.6             | ٧    |

| I <sub>IN</sub>       | Input current                     |                                                                             |     | 240 | 360             | mA   |

| R <sub>ON</sub>       | Switch on-resistance              |                                                                             |     |     | 500             | mΩ   |

# 6.6 Timing Requirements

|                    |                                                                   | MIN | NOM  | MAX | UNIT |

|--------------------|-------------------------------------------------------------------|-----|------|-----|------|

| BUCK CC            | ONVERTER                                                          | 1   |      |     |      |

| t <sub>START</sub> | Start-up time                                                     |     |      | 10  | ms   |

| LOAD SW            | VITCH                                                             |     |      |     |      |

|                    | Output rise time; 10%–90% of final $V_O$ , $C_L = 100 \mu F$      |     | 2    | 4   | ms   |

| t <sub>ON</sub>    | Turnon time; $C_L = 100 \mu F$                                    |     |      | 6   | ms   |

| t <sub>OFF</sub>   | Turnoff time; $C_L = 100 \mu F$                                   |     |      | 10  | ms   |

| POWER (            | GOOD RESET                                                        | •   |      | •   |      |

| $\Delta t_{PG}$    | Power good time-out delay                                         | 100 | 150  | 200 | ms   |

| BOOST C            | ONVERTER                                                          |     |      |     |      |

| t <sub>START</sub> | Start-up time; from enable, V <sub>BOOST</sub> = 10% → 90%        |     | 0.25 | 10  | ms   |

| POST RE            | GULATION LDO                                                      |     |      |     |      |

| t <sub>ON</sub>    | Turn-on time; $I_O = 0$ mA, $V_{LDO} = 90\%$ , $C_L = 2.9 \mu F$  |     | 130  | 500 | μs   |

| t <sub>OFF</sub>   | Turn-off time; $I_O = 0$ mA, $V_{LDO} < 0.5$ V, $C_L = 2.9 \mu F$ |     | 3.9  | 5   | ms   |

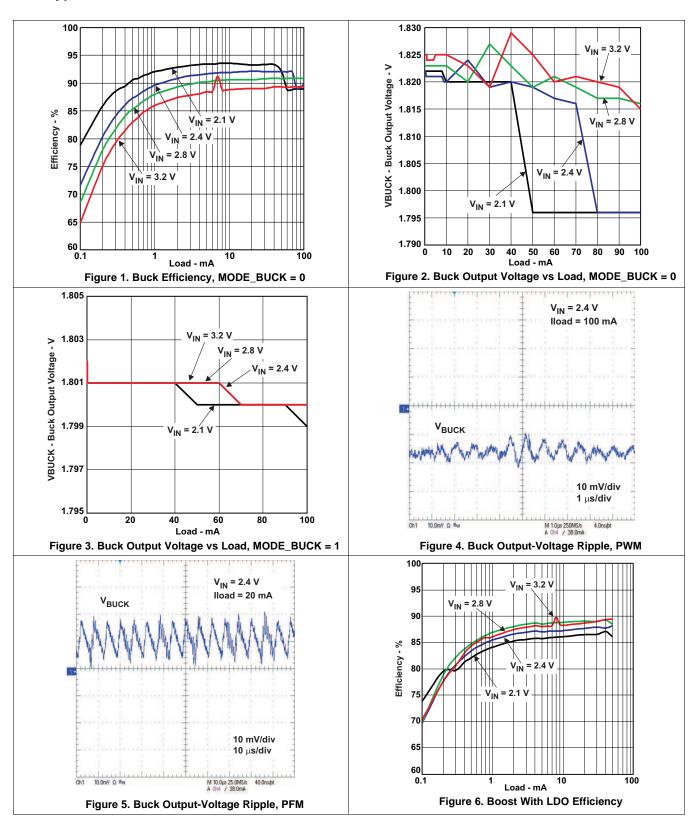

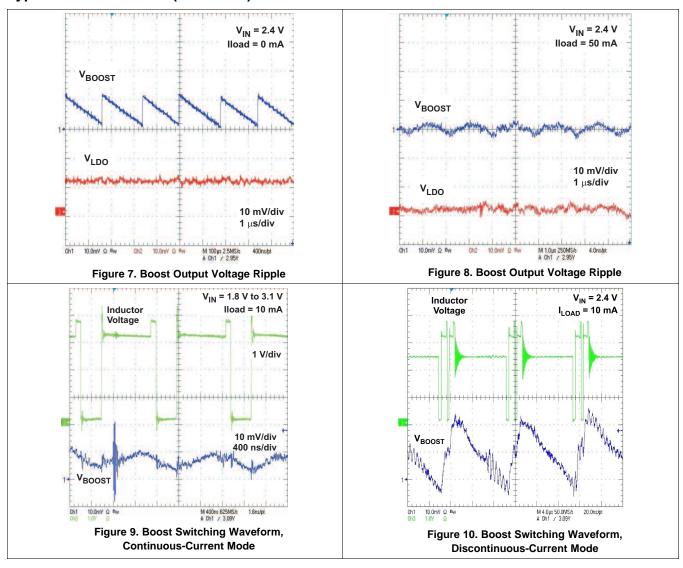

# 6.7 Typical Characteristics

# TEXAS INSTRUMENTS

# **Typical Characteristics (continued)**

Submit Documentation Feedback

Copyright © 2010–2016, Texas Instruments Incorporated

# 7 Detailed Description

#### 7.1 Overview

The TPS80010 provides a system level solution for 2-cell alkaline battery applications. Popular applications include handheld devices including wireless mice, keyboards, and video game controllers. The TPS80010 provides two DC-DC converters, a load switch, post-regulation LDO, and battery monitoring switch—each with their own enable pins to allow for maximum flexibility.

The buck converter operates at a fixed voltage, 1.8 V, and can provide up to 150 mA load. Automatic switching is implemented to maximize power efficiency. In moderate to heavy loads the converter operates in PWM mode; as load current decreases it switches to PFM mode. PWM can be forced regardless of load size by disabling this power save mode (PFM mode). The buck allows for several loads to be connected to its output, due to the power distributing load switch connected externally to the output of the buck.

The boost converter regulates at a fixed voltage of 3.1 V, and can provide up to 50 mA load current. It contains a discontinuous current mode to maintain efficiency at low load currents. The boost provides a low noise supply at low input voltages due to a post regulation LDO.

The battery monitoring switch is used to check battery lifetime. Using a false load implementation and the battery voltage it can determine the battery impedance and therefore health.

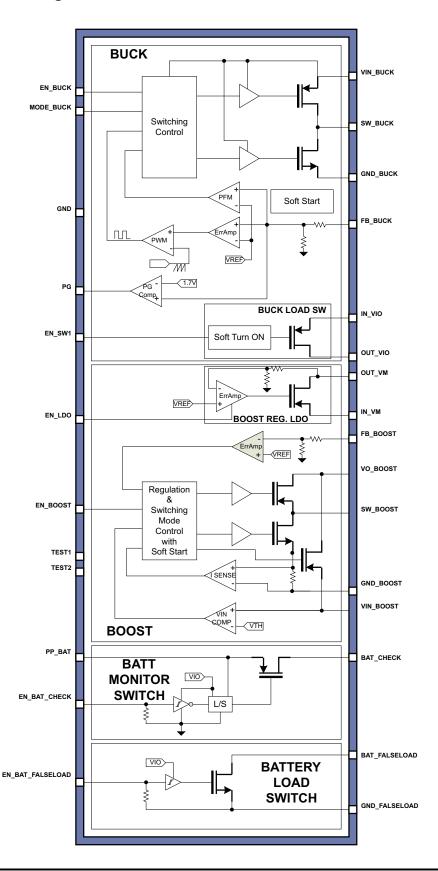

# 7.2 Functional Block Diagram

#### 7.3 Feature Description

#### **7.3.1** Enable

The TPS80010 includes two DC-DC converters, a load switch, post-regulation LDO, and battery monitoring switch. Each of these circuits has a dedicated enable pin with an internal pulldown resistor, R<sub>PULLDOWN</sub>, that can be driven by standard logic or by an open-drain driver. The EN\_BUCK pin not only enables the buck converter, but also serves as the master enable for the device. No other circuitry in the TPS80010 can operate without EN\_BUCK set high.

#### 7.3.2 Buck DC-DC Converter and Load Switch

The synchronous step-down (buck) converter in the TPS80010 provides a fixed 1.8-V output with a load capacity of 150 mA. This converter operates with a fixed switching frequency of 2.25 MHz during pulse-width-modulation (PWM) operation at moderate to heavy loads. As the load current decreases, the converter automatically switches to a power-save mode and operates in pulse-frequency-modulation (PFM) mode to maximize power efficiency. During PFM operation, the converter positions the output at a voltage about 1% greater than the nominal output voltage. This feature minimizes the output voltage drops during sudden load transients. The power-save mode can be disabled by setting the MODE BUCK pin high.

The buck converter has internal soft-start circuitry that limits the inrush current during startup to 150 mA, allowing a slow and controlled output-voltage ramp. Once the output voltage reaches 1.7 V, the output monitoring circuitry generates a Power Good (PG) output signal.

The TPS80010 also includes a load switch that is to be connected externally to the buck output voltage. This switch provides flexibility in the design and power distribution of the end application by allowing several loads (such as memory, I/O, Bluetooth, and so forth) to be connected to the same supply while being able to power down or disconnect some of these loads selectively when the end application goes to a low-power mode of operation. This switch has a controlled turnon to limit the inrush current caused by the load, and hence the load transient to the buck converter.

#### 7.3.3 Boost DC-DC Converter and Post-Regulation LDO

The TPS80010 includes a synchronous step-up (boost) converter that provides a 3.1-V fixed output at 50-mA load current. The boost converter is controlled by a hysteretic current-mode controller. This controller regulates the output voltage by keeping the inductor ripple current constant and adjusting the offset of this inductor current depending on the output load. If the required average input current is lower than the average inductor current defined by this constant ripple, the converter goes into discontinuous-current mode (DCM) to keep the efficiency high at low-load conditions. The boost also has a soft-start circuit that limits the inrush current to 150 mA.

To provide a clean, low-noise supply when  $V_{BAT} > 3.1$  V, the output of the boost is post-regulated by a 3-V LDO. This post-regulation allows the TPS80010 to provide a solid 3-V supply rail to the end application across the full input or battery-voltage range while minimizing the number of external components. To minimize power loss through the power path, the LDO allows for 100-mV input-voltage headroom at 50-mA load.

## 7.3.4 Battery Monitoring Switch and False Load

The TPS80010 implements a battery-voltage monitor switch to briefly check battery lifetime. The integrated false-load switch connects a specified load to the battery. When this *false* load is applied, the battery monitor switch is turned on, gating the sensed battery voltage to the ADC in the system. Based on this measurement, the system can determine the battery impedance and, therefore, battery health.

#### 7.4 Device Functional Modes

The step-down converter has two modes of operations to maximize efficiency: Pulse frequency modulation (PFM) and pulse width modulation (PWM).

#### PFM mode is for:

- Light loads

- Automatic transition from this mode to PWM mode automatically when MODE\_BUCK pin is pulled low

- Increasing output voltage setting by 1%

- Better accuracy

#### PWM mode is for:

- · Moderate to heavy loads

- Small output ripple

- Pulling MODE\_BUCK pin high to result in PWM mode over all load range

# 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 8.1 Application Information

The TPS80010 is ideal for dual-cell alkaline battery-powered and noise-sensitive applications. The application controller has the ability to enable resources on the power management IC to allow for maximum flexibility. The device resources are often used to power memory, IO, and optical sensors. These devices are common in wireless keyboards and video game controllers.

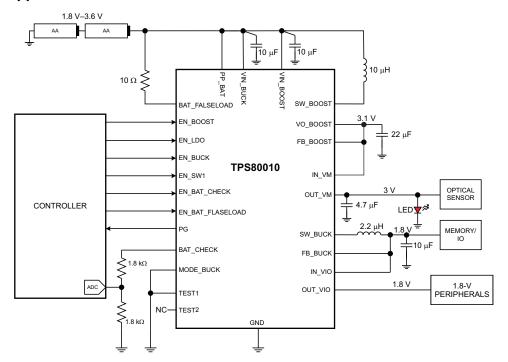

#### 8.2 Typical Application

Figure 11. TPS80010 Typical Application Diagram

#### 8.2.1 Design Requirements

The design requirements for TPS80010 are located in Table 1.

Table 1. TPS80010 Design Requirements

| RESOURCE | VOLTAGE |

|----------|---------|

| Buck     | 1.8 V   |

| Boost    | 3.1 V   |

#### 8.2.2 Detailed Design Procedure

#### 8.2.2.1 Buck Output Filter Design

The TPS80010 buck regulator is designed to operate with inductors in the range of 1.5  $\mu$ H to 4.7  $\mu$ H and with output capacitors in the range of 4.7  $\mu$ F to 22  $\mu$ F. The part is optimized for operation with a 2.2- $\mu$ H inductor and 10- $\mu$ F output capacitor.

Larger or smaller inductor values can be used to optimize the performance of the device for specific operation conditions. For stable operation, the L and C values of the output filter must not be less than 1-µH effective inductance and 3.5-µF effective capacitance.

#### 8.2.2.2 Buck Inductor Selection

The inductor value has a direct effect on the ripple current. The selected inductor must be rated for its DC resistance and saturation current. The inductor ripple current ( $\Delta I_L$ ) decreases with higher V<sub>IN</sub> or V<sub>BUCK</sub>.

The inductor selection also has an impact on the output-voltage ripple in PFM mode. Higher inductor values lead to lower output-voltage ripple and higher PFM frequency; lower inductor values lead to a higher output-voltage ripple but lower PFM frequency.

Equation 1 calculates the maximum inductor current in PWM mode under static load conditions. The saturation current of the inductor must be rated higher than the maximum inductor current, as calculated with Equation 2. This is recommended because during heavy load transients, the inductor current rises above the calculated value.

$$\Delta I_{L} = V_{BUCK} \times \frac{1 - \frac{V_{BUCK}}{V_{IN}}}{L \times f}$$

$$I_{Lmax} = I_{Omax} + \frac{\Delta I_{L}}{2}$$

(1)

where

- f = Switching frequency (2.25 MHz typical)

- L = Inductor value

- $\Delta I_1$  = Peak-to-peak inductor ripple current

A more conservative approach is to select the inductor current rating just for the switch current limit,  $I_{LIMF}$ , of the converter.

Accepting larger values of ripple current allows the use of lower inductance values, but results in higher output voltage ripple, greater core losses, and lower output current capability.

The total losses of the coil have a strong impact on the efficiency of the DC-DC conversion and consist of both the losses in the DC resistance ( $R_{(DC)}$ ) and the following frequency-dependent components:

- The losses in the core material (magnetic hysteresis loss, especially at high switching frequencies)

- Additional losses in the conductor from the skin effect (current displacement at high frequencies)

- Magnetic field losses of the neighboring windings (proximity effect)

- · Radiation losses

#### 8.2.2.3 Buck Output Capacitor Selection

The advanced fast-response voltage mode control scheme of the TPS80010 buck regulator allows the use of tiny ceramic capacitors. Ceramic capacitors with low ESR values have the lowest output voltage ripple and are recommended. The output capacitor requires either an X7R or X5R dielectric. Y5V- and Z5U-dielectric capacitors, aside from their wide variation in capacitance over temperature, become resistive at high frequencies. At nominal load current, the device operates in PWM mode and the RMS ripple current is calculated with Equation 3.

$$I_{RMSCout} = V_{BUCK} \times \frac{1 - \frac{V_{BUCK}}{V_{IN}}}{L \times f} \times \frac{1}{2 \times \sqrt{3}}$$

(3)

At nominal load current, the device operates in PWM mode and the overall output voltage ripple is the sum of the voltage spike caused by the output capacitor ESR plus the voltage ripple caused by charging and discharging the output capacitor in Equation 4.

$$\Delta V_{\text{BUCK}} = V_{\text{BUCK}} \times \frac{1 - \frac{V_{\text{BUCK}}}{V_{\text{IN}}}}{L \times f} \times \left( \frac{1}{8 \times C_{\text{OUT}} \times f} + \text{ESR} \right)$$

(4)

At light-load currents, the converter operates in power-save mode, and the output-voltage ripple depends on the output-capacitor and inductor values. Larger output-capacitor and inductor values minimize the voltage ripple in PFM mode and tighten DC output accuracy in PFM mode.

#### 8.2.2.4 Buck Input Capacitor Selection

An input capacitor is required for best input voltage filtering and for minimizing the interference with other circuits caused by high input-voltage spikes. For most applications, a  $4.7-\mu F$  to  $10-\mu F$  ceramic capacitor is recommended. Because a ceramic capacitor loses up to 80% of its initial capacitance at 5 V, TI recommends that  $10-\mu F$  input capacitors be used for input voltages > 4.5 V. The input capacitor can be increased without any limit for better input-voltage filtering. Take care when using only small ceramic input capacitors. When a ceramic capacitor is used at the input and the power is being supplied through long wires, such as from a wall adapter, a load step at the output or  $V_{IN}$  step on the input can induce ringing at the VIN\_BUCK pin. This ringing can couple to the output and be mistaken as loop instability or could even damage the part by exceeding the maximum ratings.

COMPONENT **VALUE PART SUPPLIER** SIZE 2.5 mm × 2 mm × 1.2 mm LQM2HPN2R2MJ0L Murata (1008)Inductor 2.2 μΗ  $3 \text{ mm} \times 3 \text{ mm} \times 1.5 \text{ mm}$ LPS3015-222ML Coilcraft Murata 0603 Cacitor (IN) 10 μF GRM188R60J106ME47D Capacitor (OUT) 10 μF GRM188R60J106ME47D Murata 0603

**Table 2. Recommended Component List for Buck Converter**

#### 8.2.2.5 Boost Inductor Selection

To ensure proper operation of the TPS80010 boost DC-DC converter, a suitable inductor must be connected between pins VIN\_BOOST and SW\_BOOST. Inductor values of 4.7  $\mu$ H show good performance over the whole input and output voltage range.

Choosing other inductance values affects the switching frequency f proportional to 1/L as shown in Equation 5.

$$L = \frac{1}{f \times 200 \text{ mA}} \times \frac{V_{IN} \times (V_{BOOST} - V_{IN})}{V_{BOOST}}$$

(5)

Choosing inductor values higher than 4.7  $\mu H$  can improve efficiency due to reduced switching frequency and correspondingly reduced switching losses. Using inductor values less than 2.2  $\mu H$  is not recommended.

Having selected an inductance value, the peak current for the inductor in steady-state operation can be calculated. Equation 6 gives the peak current estimate.

$$I_{L,MAX} = \left\{ \frac{V_{BOOST} \times I_{BOOST}}{0.8 \times V_{IN}} + 100 \text{ mA} \right\}$$

continuous current operation

$$I_{L,MAX} = 200 \text{ mA}$$

discontinuous current operation (6)

$I_{L,MAX}$  is the required minimum inductor-current rating. The load-transient or overcurrent conditions may require an even higher current rating.

The condition in Equation 7 provides an easy way to determine whether the device is in continuous or discontinuous operation. As long as the condition is true, the device operates in continuous-current mode. If the condition becomes false, discontinuous-current operation is established.

$$\frac{V_{\text{BOOST}} \times I_{\text{O}}}{V_{\text{IN}}} > 0.8 \times 100 \text{ mA}$$

(7)

Due to the use of current hysteretic control in the TPS80010 boost, the series resistance of the inductor can impact the operation of the main switch. There is a simple calculation that can ensure proper operation of the TPS80010 boost converter. The relationship between the series resistance ( $R_{IN}$ ), the input voltage ( $V_{IN}$ ), and the switch current limit ( $I_{SW}$ ) is shown in Equation 8.

$$R_{IN} < \frac{V_{IN}}{I_{SW}} \tag{8}$$

Examples include Equation 9 and Equation 10.

$$I_{SW} = 400 \text{ mA}, V_{IN} = 2.5 \text{ V}$$

(9)

In Equation 9,  $R_{\text{IN}}$  < 2.5 V / 400 mA; therefore,  $R_{\text{IN}}$  must be less than 6.25  $\Omega.$

$$I_{SW} = 400 \text{ mA}, V_{IN} = 1.8 \text{ V}$$

(10)

In Equation 10,  $R_{IN}$  < 1.8 V / 400 mA; therefore,  $R_{IN}$  must be less than 4.5  $\Omega$ .

#### 8.2.2.6 Boost Input Capacitor

The input capacitor must be at least 10  $\mu$ F to improve transient behavior of the regulator and EMI behavior of the total power-supply circuit. The input capacitor must be a ceramic capacitor and be placed as close as possible to the VIN\_BOOST and GND pins of the IC. These capacitors must be X7R or X5R ceramic capacitors.

#### 8.2.2.7 Boost Output Capacitor

For the output capacitor  $C_{OUT}$ , TI recommends using small X7R or X5R ceramic capacitors placed as close as possible to the VO\_BOOST and GND pins of the IC. If, for any reason, the application requires the use of large capacitors which cannot be placed close to the IC, the use of a small ceramic capacitor with a capacitance value of around 4.7  $\mu$ F in parallel with the larger one is recommended. This small capacitor must be placed as close as possible to the VO\_BOOST and GND pins of the IC.

A minimum effective capacitance value of 6  $\mu$ F must be used; 10  $\mu$ F is recommended. If the inductor value exceeds 4.7  $\mu$ H, the value of the effective output capacitance value must be half the inductance value or higher for stability reasons; see Equation 11.

$$C_{OUT} \ge \frac{L}{2} \times \frac{\mu F}{\mu H} \tag{11}$$

#### **NOTE**

When choosing the output capacitor, be aware of the effects of bias voltage, temperature, and tolerance on the effective capacitance of the component. A capacitor in a 0603 package size suffers more capacitance degradation than a 0805 package at a similar bias voltage. For example, either a 22- $\mu$ F 0603-sized capacitor or a 10- $\mu$ F 0805-sized capacitor is required to work with a nominal 10- $\mu$ H inductor.

The TPS80010 boost is not sensitive to ESR in terms of stability. Using low-ESR capacitors, such as ceramic capacitors, is recommended to minimize output-voltage ripple. If heavy load changes are expected, the output capacitor value must be increased to avoid output voltage drops during fast load transients.

**Table 3. Recommended Component List for Boost Converter**

| COMPONENT | VALUE | PART          | SUPPLIER    | SIZE                               |

|-----------|-------|---------------|-------------|------------------------------------|

| Inductor  | 10 μΗ | CBC3225T100MR | Taiyo Yuden | 3.2 mm × 2.5 mm × 2.5 mm<br>(1210) |

|           | •     | DO3314-103ML  | Coilcraft   | 3.3 mm × 3.3 mm × 1.4 mm           |

Table 3. Recommended Component List for Boost Converter (continued)

| COMPONENT       | VALUE | PART               | SUPPLIER    | SIZE |

|-----------------|-------|--------------------|-------------|------|

| Capacitor (IN)  | 10 μF | GRM188R60J106ME47D | Murata      | 0603 |

| Capacitor (OUT) | 22 μF | AMK107BJ226MA-T    | Taiyo Yuden | 0603 |

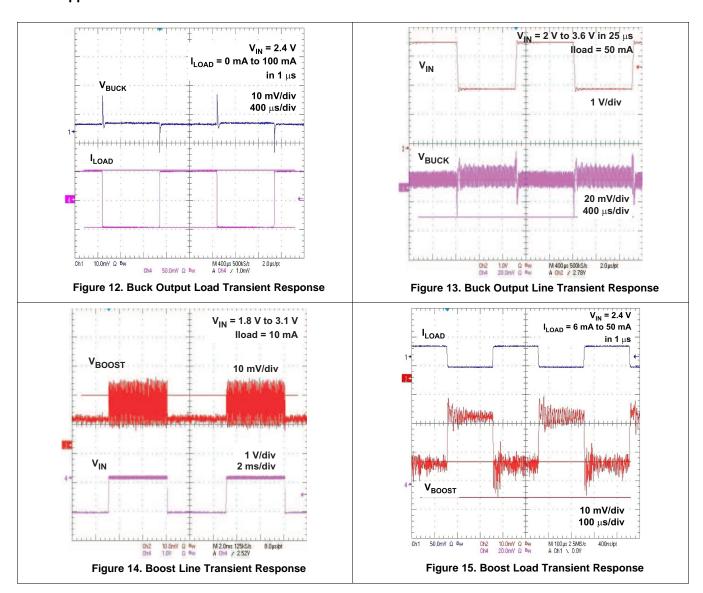

## 8.2.3 Application Curves

# 9 Power Supply Recommendations

The TPS80010 was originally designed for dual-cell alkaline battery applications. Therefore, the device has working input voltage ranges from 1.95 V to 3.6 V. As long as the input voltage range is followed, the input supply can be from other regulated supplies.

# 10 Layout

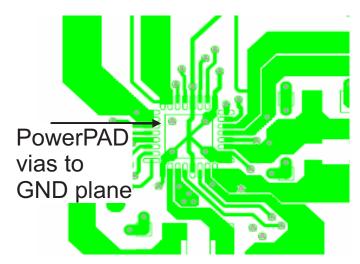

#### 10.1 Layout Guidelines

The VIN\_BOOST and VIN\_BUCK pins must be bypassed to ground with a low-ESR ceramic bypass capacitor. Texas Instruments recommends the typical bypass capacitance is 10 μF.

- The optimum placement is closest to the VIN\_BUCK and VIN\_BOOST pins of the device. Minimize the loop area formed by the bypass capacitor connection, the VINDCDC and VINLDO pins, and the thermal pad of the device.

- The thermal pad must be tied to the PCB ground plane with multiple vias.

- The FB \_BOOST, FB\_BUCK, SW\_BOOST, SW\_BCUK, and OUT\_VM pins (feedback and output pins) traces

must be routed away from any potential noise source to avoid coupling.

- Output capacitance must be placed immediately at the output pins. Excessive distance from the capacitance to output pins may cause poor converter performance.

#### 10.2 Layout Example

Figure 16. TPS80010 Layout

# 11 Device and Documentation Support

# 11.1 Device Support

#### 11.1.1 Third-Party Products Disclaimer

TI'S PUBLICATION OF INFORMATION REGARDING THIRD-PARTY PRODUCTS OR SERVICES DOES NOT CONSTITUTE AN ENDORSEMENT REGARDING THE SUITABILITY OF SUCH PRODUCTS OR SERVICES OR A WARRANTY, REPRESENTATION OR ENDORSEMENT OF SUCH PRODUCTS OR SERVICES, EITHER ALONE OR IN COMBINATION WITH ANY TI PRODUCT OR SERVICE.

### 11.2 Community Resources

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™ Online Community TI's Engineer-to-Engineer (E2E) Community. Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support** *TI's Design Support* Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 11.3 Trademarks

E2E is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

#### 11.4 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### 11.5 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

## 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

www.ti.com 19-Dec-2023

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|--------------------|--------------|-------------------------|---------|

|                  |        |              |                    |      |                |              | (6)                           |                    |              |                         |         |

| TPS80010ARSMR    | ACTIVE | VQFN         | RSM                | 32   | 3000           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | TPS<br>80010A           | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 20-Apr-2023

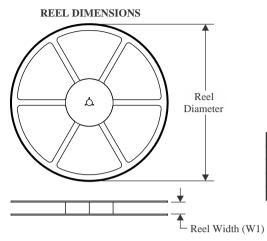

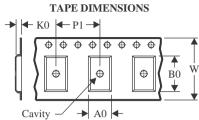

# TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

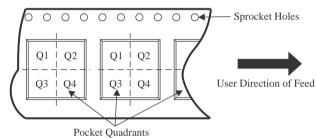

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device        | U    | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS80010ARSMR | VQFN | RSM                | 32 | 3000 | 330.0                    | 12.4                     | 4.25       | 4.25       | 1.15       | 8.0        | 12.0      | Q2               |

**PACKAGE MATERIALS INFORMATION**

www.ti.com 20-Apr-2023

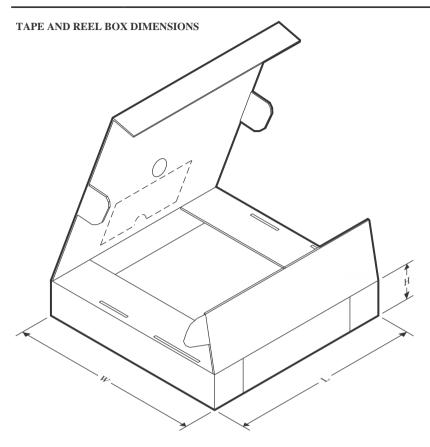

# \*All dimensions are nominal

| Device        | Package Type | Package Type Package Drawing |    | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|---------------|--------------|------------------------------|----|------|-------------|------------|-------------|--|

| TPS80010ARSMR | VQFN         | RSM                          | 32 | 3000 | 346.0       | 346.0      | 33.0        |  |

4 x 4, 0.4 mm pitch

PLASTIC QUAD FLATPACK - NO LEAD

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

# **IMPORTANT NOTICE AND DISCLAIMER**

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated