# PCMデバイスの基本接続とPCレイアウト設計

# 概要

このアプリケーションノートは、バー・ブラウンのオーディオ用PCMデバイス(DAC、ADC、CODEC)について、その基本的接続、PCパターン・レイアウト設計、出力回路設計等に関し、その理論的背景といくつかの実測データをもとに詳しく解説しています。このアプリケーションノートで掲げた各項目は、実設計に際し非常に有益であるはずですので、各設計者の十分な理解と実践をお願いいたします。

# 電源およびグランドの接続

まず最初に、オーディオ用DAC、CODEC、ADC等のデバイスはCMOS リニアICであり、アナログICとして扱わなければならないことを理解して下さい。このセクションでは、ICの各電源およびグランドの最適な接続方法について、ICの内部構造や実測データを用いて説明しています。

# CMOSプロセスとフィードスルー

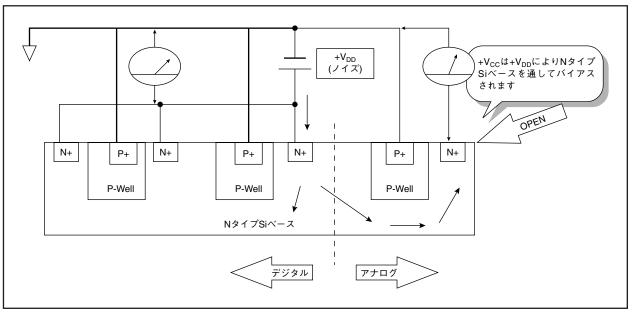

バー・ブラウンで用いているCMOSプロセスの簡易構造図を図1に示します。標準的には、ICデバイスはデジタル系およびアナログ系、2つの電源  $(+V_{CC}, +V_{DD})$ 、グランド

(AGND、DGND) がそれぞれあります。これは、IC内部の動作により区別していますが、デジタル部もアナログ部も全く同一のプロセス上にあり、図1に示す通り、N型シリコンのベース上に生成されています。

この構造原理により、例えば、デジタル系  $(+V_{DD})$  に電圧を加え、アナログ系  $(+V_{CC})$  側をオープンにしている場合、デジタル系の電圧はN型シリコン・ベースを介してアナログ電源  $(+V_{CC})$  にも現れます。この逆の場合も同様で、電源をいずれかの電源ピンに加えれば、電源を接続していない電源ピンにも電圧が発生します。このことは非常に重要で、電源上に乗っている "ノイズ" もこれと同じようにデジタル側からアナログ側へ伝達されることを意味しています。つまり、デジタル系電源  $(+V_{DD})$  を外部デジタル回路に接続してしまうと、外部デジタル回路の電源ノイズが直接ICデバイスに加わることになります。

#### 電源デジタルノイズのフィールドスルー

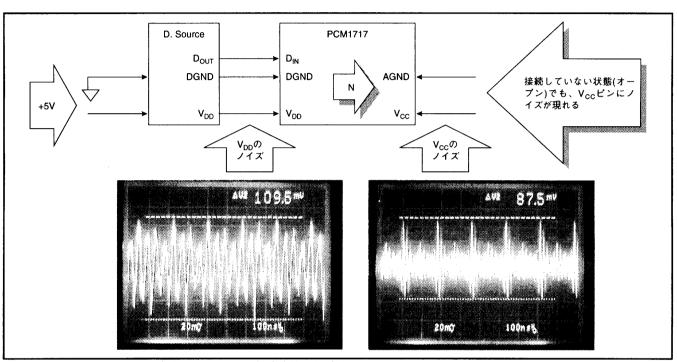

図2に電源デジタルノイズの伝達特性の実測例をPCM1717をモデルに示します。ここでは、外部デジタル信号源からシステム・クロック、PCMデータをDACに供給し、同時に

図1.CMOSプロセスの簡易構造

デジタル電源をDACのデジタル電源 $(+V_{DD})$ に供給しています。 DACのアナログ側電源 $(+V_{CC})$ はオープンです。

この図から明らかなように、アナログ側には何も接続していないのにも関わらず、非常に大きなデジタルノイズが+Vccピンに発生しています。つまり、デジタルノイズを回避しようとDACのデジタル電源を外部デジタル電源に接続するのは逆効果であることを示しています。したがって、DACの各電源は、デジタル系であっても外部デジタル回路に接続するとデジタルノイズを直接DACに加えているのと同じことになるので、DAC電源は外部デジタル系に接続してはなりません。

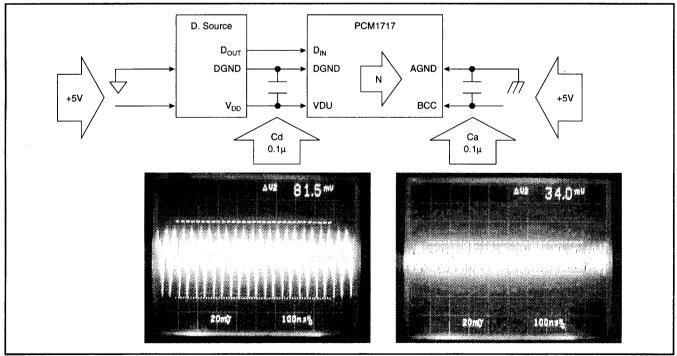

## バイパス・コンデンサ

図3に、電源デカップリング・バイパス・コンデンサのデジタルノイズのデカップリング効果を示します。ここでは、 $0.1\mu$ Fのセラミック・コンデンサをバイパス・コンデンサとして電源ピンに接続したもので、 $+V_{DD}$ および  $+V_{CC}$ 上のデジタルノイズは抑圧されますが、まだ無視できないレベルで残っています。この電源ピンのバイパス・コンデンサは非常に重要であり、ICデバイスの特性に直接影響するので最優先で接続しなければなりません。

図2. PCM1717をモデルにした電源デジタルノイズ伝達特性の実測例

図3. 電源デカップリング・バイパス・コンデンサのデジタルノイズのデカップリング効果

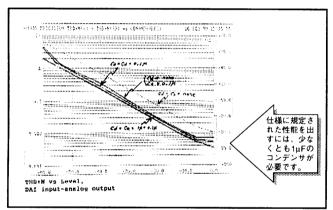

#### THD + N 特性とバイパス・コンデンサ

図4にPCM1717による電源バイパス・コンデンサ容量対THD+N特性の実測例を示します。この特性傾向は、若干の差はありますが、他のPCMモデルPCM17xx、PCM1800、PCM300x等にも適用されます。図4から明らかなように、バイパス・コンデンサはTHD+N特性に大きく影響し、少なくとも容量1µF以上のバイパス・コンデンサを接続しないと期待する性能は出せないと言えます。一般的なアプリケーションでは、電源条件はテストベンチでの電源ソースに比べて不利ですので、このバイパス・コンデンサの役割は非常に重要になり、実設計においては、このバイパス・コンデンサの接続を優先して行う必要があります。理想的には、全周波数帯域で低インピーダンスを保つため、10µF以上のアルミ電解コンデンサと0.1µF程度の積層セラミック・コンデンサを並列接続することを推奨します。

また、これらのコンデンサは、ICピンにできる限り近づけて接続しなければなりません。ICピンからの距離が長くなるとバイパス効果が低下し、性能劣化につながりますので、レイアウト設計時にはこのバイパス・コンデンサの配置を優先させなければなりません。

**図4.** PCM1717による電源バイパス·コンデンサ容量対THD + N特 性の実測例

# ラッチアップ

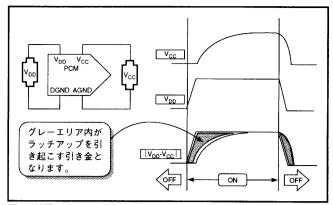

PCMデバイスは前述の通り、デジタル系とアナログ系の電源をもっていますが、図5に示すように別電源からそれぞれ +V<sub>CC</sub>、+V<sub>DD</sub>に電源を供給すると、各電源インピーダンスが異なるため、電源ON/OFF時の過渡状態において両電源間に電圧差が発生します(図中のグレーエリア)。CMOS構造では、この電圧差はラッチアップを起こすトリガとなり、ICデバイスにおいては極めて危険な状態となります。また、過渡時に関わらずスパイク状のノイズ等もラッチアップのトリガとなり、別電源接続で使用することはICデバイスの破壊に繋がります。

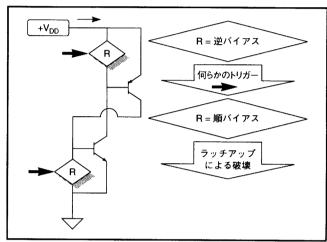

図6(A)は、CMOS構造におけるラッチアップの原理を示したものです。PNP、NPNの各トランジスタは、通常遊バイアスされているためOFF状態ですが、電源電圧差やスパイク・ノイズにより何らかのトリガがかかると、これらのトランジスタは順バイアスとなり、大きな電流が流れます。この状態は電源をOFFにしない限り回復しないため、これをラッチアップと言います。この場合、ほとんどのICデバイスは過電流により破壊されてしまうか、ストレスにより機能不良、性能劣化を起こします。

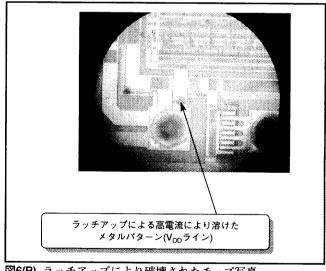

図6(B)に、ラッチアップにより破壊されたチップ写真を示しま

図5. 別電源での電源シーケンス

図6(A). CMOS構造におけるラッチアップの原理

図6(B). ラッチアップにより破壊されたチップ写真

す。ここでは、電源パッドからのアルミ配線パターンが過電流により溶断されています。したがって、PCMデバイスをデジタル、アナログ別電源で使用することはラッチアップを引き起こすことになるため、必ず、共通接続で使用しなければなりません。

#### **Short Summary**

今までの解説で、PCMデバイスを別電源で使用することは百 害あって一利無しだと理解されたと思いますが、それでも別電源 にしたいという設計者はいますか? ここでは、今までの解説の簡単なSummaryをします。

- \*PCMデバイスのデジタル電源(+V<sub>DD</sub>)を外部デジタル電源(回路)に接続することは、外部デジタル電源のノイズを直接PCMデバイスに加えていることになり、特性に大きく影響します。

- \*PCMデバイスをアナログ系、デジタル系別電源で使用することは、ラッチアップにつながりICデバイスの破壊または、機能、性能不良を起こします。

したがって、

- \*PCMデバイスの各電源 $(+V_{CC}, +V_{DD})$ および各グランド(AGND, DGND)は共通接続とし、システムのアナログ電源、グランドに接続します。

- \*バイパス·コンデンサはできる限りICピンに最短距離で接続し、容量は少なくとも1uF以上とします。

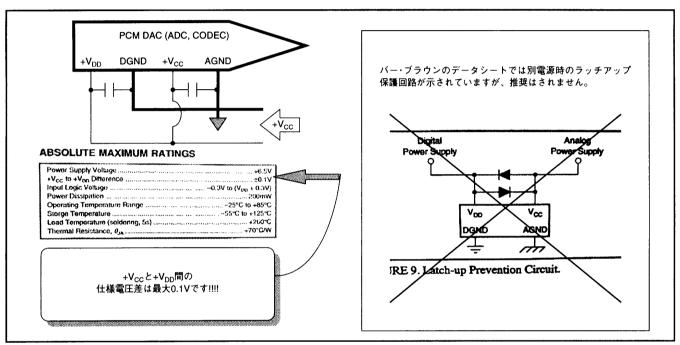

図7に、ここでのShort Summaryを示します。PCMデバイスの各電源、GNDは共通接続で、バイパス・コンデンサを最短距離で接続します。また、PCMデバイスのデータシートで規定している電源電圧差は、絶対最大定格で±0.1Vです。すなわち、電源電圧差が0.1Vを超えた場合の保証はされていません。電源電圧差が0.1Vを超えて発生した不良は使用者側の責任になります。

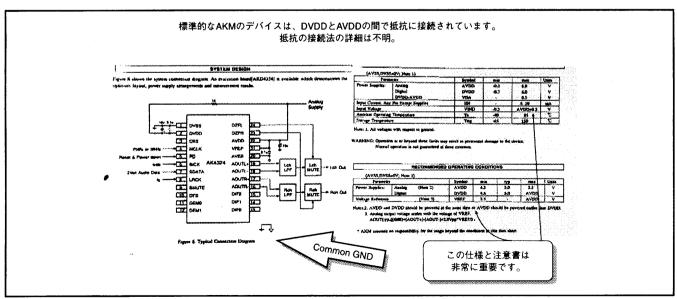

#### 他社での規定

この電源電圧差に関しては、特にバーブラウンだけが規定しているものではなく、他社の同様のデバイスでも同様の規定がされています。図8にAKM社のAK4324のデータシートの抜粋を示します。ここでは、±0.3Vが定格となっており、グランドは完全に共通、電源も同一電源から供給することとしています。別電源での使用については一切触れていません。

図7. Short Summary

図8. AK4324のデータシート(抜粋)

#### ロジック・インターフェース

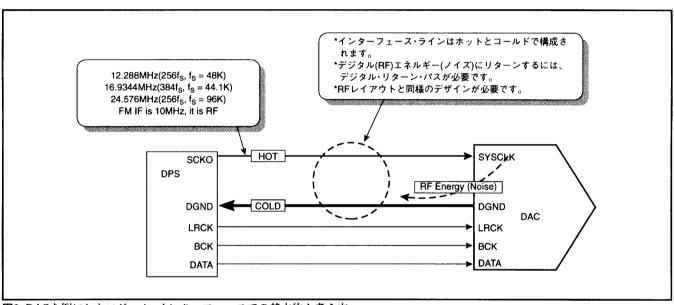

PCMデバイスを使用する際に、電源、GND接続の他は、デジ タル信号のインターフェースが重要になってきます。図9にDAC を例にしたロジック・インターフェースでの基本的な考え方を示 します。TTL、CMOSのインターフェース・レベルの合致は当然 として、ここで考えなければならないのは、各デジタル信号は RF信号と同様の高い周波数であるということです。例えば、FM チューナーのIF(中間増幅周波数)は10.7MHzで、DACに供給する システム·クロック周波数は、f<sub>s</sub>=44.1kHz、384f<sub>s</sub>では、16.9344MHz であり、パターン・レイアウトにおいては少なくともRF(高周波) 設計と同様の考慮が必要だと考えるべきです。具体的には、とに かく最短距離で接続することが重要です。また、デジタル信号の もつエネルギーはDAC内部の他の部分の特性に影響を与えること になりますので、デジタル信号のリターン・ラインを必要としま す。いかなる信号もホットとコールド(グランド)があり、信号伝 送での基本となっていますが、DACとの接続時にこれが例外とな る理由はありません。したがって、デジタル信号の中でも一番周 波数の高いシステム・クロックに対しては、信号のガード、シールド、デジタル・リターンについて十分考察する必要があります。

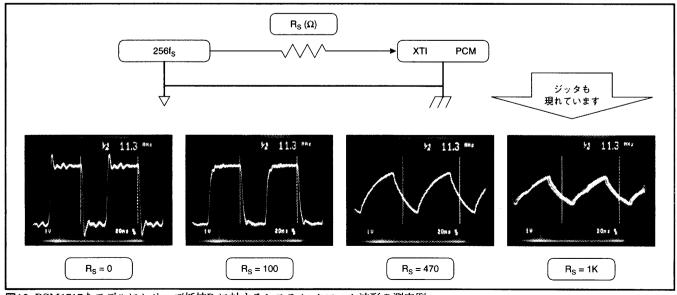

# シリーズ抵抗接続

実アプリケーションにおいては、RFI、EMI対策を主目的としてロジック・インターフェース・ラインに抵抗を挿入するケースがしばしば見られます。この処置は、抵抗値を間違えなければPCMデバイス側からは大きな問題となることはありません。インターフェース・クロック波形のオーバー/アンダー・シュートを補正し、リンキング・ノイズを抑圧する意味でも有効ですが、抵抗値が大きくなると短形波が三角波になり、ジッタを生成してしまうケースもあるので抵抗値の設定には十分な考察と実機での確認が必要です。

図10に、PCM1717をモデルにシリーズ抵抗 $R_s$ に対するシステム・クロック波形の測定例を示します。ここでのシステム・クロックは、11.288MHz(256 $f_s$ 、 $f_s$  = 44.1kHz)です。この波形変化は、測定条件、特にインターフェース方法、グランディング、プロー

図9. DACを例にしたロジック・インターフェースでの基本的な考え方

図10. PCM1717をモデルにシリーズ抵抗R。に対するシステム・クロック波形の測定例

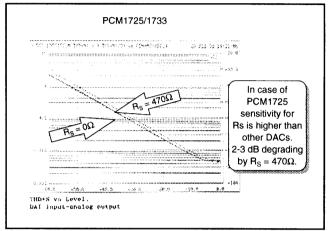

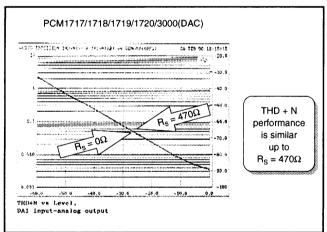

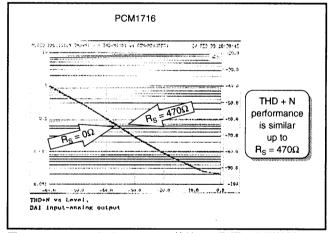

ブ容量等により影響されますから、あくまでも参考として考えて下さい。 図10より、 $R_{\rm S}$  = 470 $\Omega$ が最大許容レベルで、1k $\Omega$ ではジッタまで発生しています。図11、12、13にそれぞれ、PCM1717、PCM1725、PCM1716におけるTHD + N特性への影響を実測した結果を示します。

これらの実測結果から、PCM1725が最も波形変化に対する感度が敏感であり、ついでPCM1716、最も感度が低いのがPCM1717という結果になっています。

# デジタル・リターン

前述の通り、DACへの入力デジタル信号エネルギー(ノイズ)は、そのデジタル信号源に返してあげなければなりません。実際のアプリケーションから見ると、一般的にこのデジタル・リターンをきちんと行っているケースは少なく、その影響度の認識が低いように思われます。PCMデバイスのダイナミック特性は、このデジタル・リターンの有無により影響されることをここでは理解して下さい。

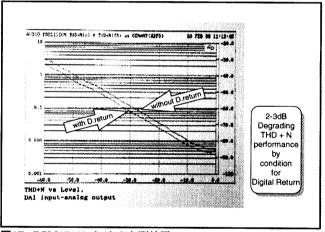

図14にデジタル・リターンの有無による特性差の測定ブロック 図を示します。システム・クロックは384f<sub>s</sub>で、このシステム・クロックを長さ約15cmのシールド・ケーブルでPCM評価ボードに供給し、シールド側のON/OFFでの特性差を実測します。もちろん信号源の電源とPCM評価ボードのグランドは共通であり、一応両グランドは接続されており、単にインターフェース・ラインに

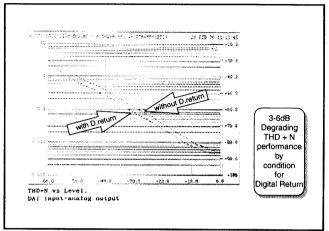

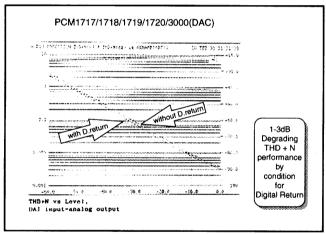

デジタル・リターンが有るか否かの評価になります。図15、16、17に、PCM1717、PCM1725、PCM1716における実測結果をそれぞれ示します。

PCM1717では、1-3dB、PCM1725では、3-6dB、PCM1716では、1-2dBの差がそれぞれ確認できています。これは、微少なジッタ、波形の変化も含んでいますが、それらも含めて、デジタル・リターンの有無による差であり、無視することはできません。したがって、実際のPCレイアウト設計に際しては、このデ

図12. PCM1725におけるTHD + N特性への影響の実測結果

図11. PCM1717におけるTHD + N特性への影響の実測結果

図13. PCM1716におけるTHD + N特性への影響の実測結果

図14. デジタル・リターンの有無による特性差の測定

ジタル・リターンを考慮した設計を行う必要があります。

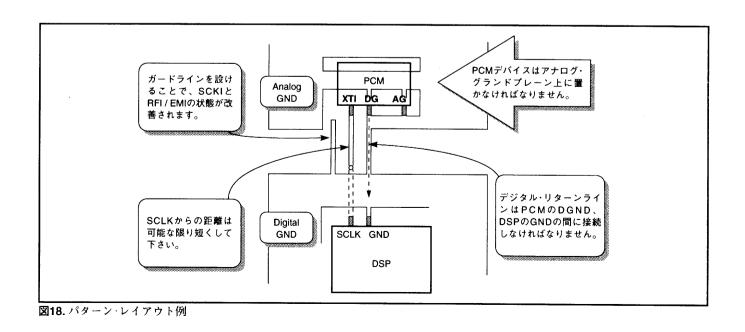

図18に、これらを考慮したパターン・レイアウト例を示します。実際にデジタル・リターンを設定する場合は、PCMデバイスのデジタル系グランド(DGND)ピンから、デジタル信号源のGNDにリターン・ラインを接続します。PCMデバイスのDGND、AGNDは共通にアナログ・グランドに接続されていますが、PCMデバイスのDGNDピンからリターン・ラインを接続することにより、デジタルノイズはアナログ側には行かず、デジタル信号側にリターンされます。

# ロジック・インターフェースのShort Summary

今まで解説した通り、PCMデバイスの特性は、デジタル信号のインターフェース方法によりかなり影響されることが解ったと思います。ここでのShort Summaryは、

- \*システム・クロックは最短距離で接続する。

- \*シリーズ抵抗の挿入はRFI、EMIに有効。ただし、抵抗値は 470Ω以下、実機での確認をすべきです。

- \*デジタル・リターンは絶対必要。ガードラインもできれば設けるべきです。

# アナログ出力回路

DACの出力回路は、一般的にはポスト・ローパスフィルタ、ゲイン・アンプ(LPFで兼用の場合や、無しの場合もあり)、出力MUTE回路で構成されています。せっかく今まで解説した電源接続、バイパス・コンデンサ接続、インターフェース接続を完璧に

図16. PCM1725における実測結果

図15. PCM1717における実測結果

図17. PCM1716における実測結果

行っても、このアナログ出力回路の不出来で特性が取れなければ 意味がありません。ここでは、アナログ出力回路に関して、特に バー・ブラウンでの推奨に関して解説します。

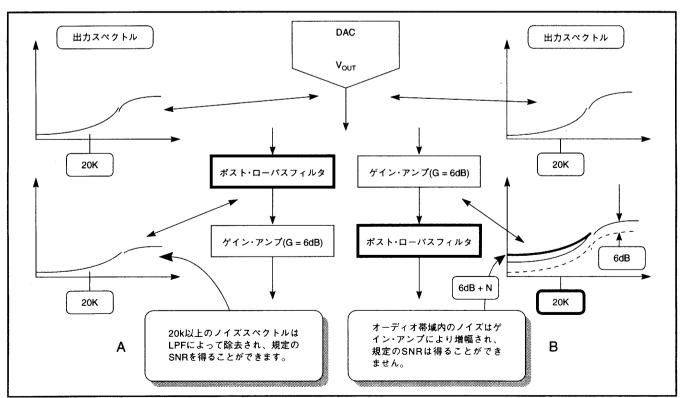

#### ポスト・ローパスフィルタの位置

ポスト・ローパスフィルタの目的はオーディオ帯域外のノイズスペクトルの除去で、その回路構成(フィルタの種類、次数、カットオフ周波数等)は設計者の意図、設計指針により異なります。ポスト・ローパスフィルタの設計に関する説明はこのアプリケーションノートでは特に行いませんが、アナログ出力回路におけるポスト・ローパスフィルタの位置と特性の関係をここでは解説します。図19(A、B)は、ゲイン・アンプとポスト・ローパスフィルタの構成法(位置)の違いによる特性への影響を示したものです。DACの出力は20kHz以上のオーディオ帯域外にフルスケールに対して約-60dBのレベルのノイズシェーピング・スペクトル(以下、帯域外ノイズと称す)を含んでいます。この帯域外ノイズは、まず最初にポスト・ローパスフィルタである程度除去されなければなりませんが、構成(位置)を間違えると性能を悪化させる(帯域内ノイズの増加)ことになります。図19(A、B)において、

構成(A) は、DAC出力 → ポスト·ローパスフィルタ

**→** ゲイン·アンプ

構成(B) は、DAC出力→ ゲイン・アンプ

→ ポスト・ローパスフィルタ

でそれぞれ構成されています。ここで、構成(A)は、まず最初にポスト・ローパスフィルタで帯域外ノイズが除去されるため、次段のゲイン・アンプはそのままゲイン・アンプとして動作し、何ら問題なく動作します。

ところが、構成(B)では、大きな帯域外ノイズを含んだ信号が ゲイン・アンプに入力されるため、アンプが何らかの飽和動作ま たは帯域外ノイズによる相互変調動作を起こし、所定の設定ゲイン以上に帯域内のノイズや信号も増幅してしまったり、帯域内に新たなノイズを発生させることがあります。この場合、ゲイン・アンプの出力はすでに帯域内ノイズが所定ゲイン以上に増加しているため、次段のポスト・ローパスフィルタではこのノイズを除去できません。すなわち、結果的にはTHD+N、ダイナミック・レンジ、S/N比の悪化を起こします。したがって、DAC出力にはまず最初にポスト・ローパスフィルタを接続し、帯域外ノイズを除去してから、ゲイン等のアナログ信号処理を行う構成にしなければなりません。

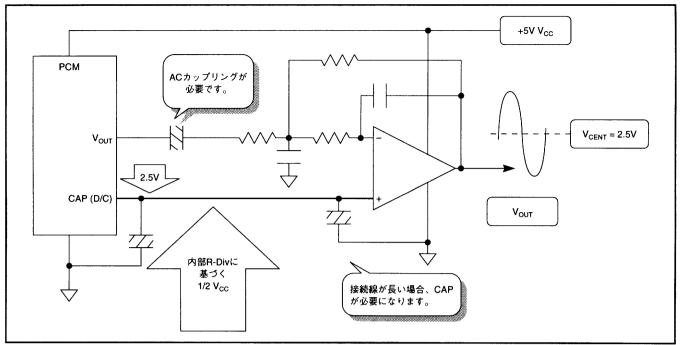

#### 単一電源用ポスト・ローパスフィルタ回路

図20に、+5V単一電源でも簡単に構成できる2次アクティブ フィルタの回路例を示します。通常、+5V単一電源では1/2 V<sub>cc</sub> (+2.5V)のバイアスを外部で生成しますが、これが面倒でポスト・ ローパスフィルタを省略してしまう場合もあります。バー・ブラ ウンのPCM DACの場合、この1/2V<sub>cc</sub>バイアス点のデカップリン グ端子(D/C L、EXT L、CAP等の名称)が設けてあり、この端 子をそのままフィルタ回路のオペアンプのバイアス基準として使 用することができるので、DAC出力には必ずここで示したポス ト·ローパスフィルタを加えることを推奨します。DACの1/2Vcc ピンは外部へこのリファレンス電圧を供給するようには設計され ていませんが、オペアンプの入力端子のように入力インピーダン スが非常に高ければ、特に問題はありません。バイパス・コンデ ンサはレイアウトによっては、DAC側、オペアンプ側の両方に接 続すると良いと思われます。このアクティブ・ローパス・フィルタ は多重帰還、反転型で、次数は2次です。カットオフ周波数は、 30kHzから40kHzに設定するのが推奨されます。

図19. ゲイン・アンプとポスト・ローパスフィルタの構成法(位置)の違いによる特性への影響

図20. +5V単一電源で構成する2次アクティブフィルタの回路例

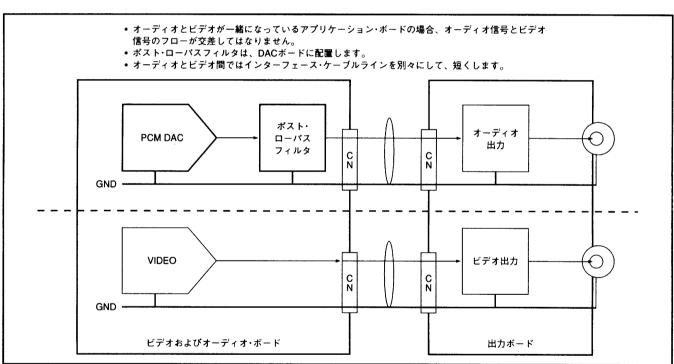

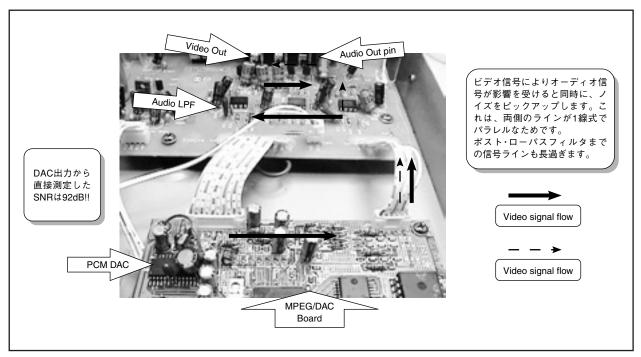

図21. ビデオCDプレーヤを例にした注意点

#### 実機での実装位置とインターフェース

実際のアプリケーション・セット、実機においては、特にDAC のみに注意して他の全ての部品、基板構成および位置が決定しているわけではありませんが、特性の悪化を防ぐために最低限必要な実機での注意点についてここで掲げます。図21にビデオCDプレーヤを例にした注意点を示します。実機での構成において、一般的にビデオCDではMPEGデコーダとオーディオDAC、ビデオ信号処理回路が同一基板に構成されます。また、オーディオ出力回路とビデオ出力回路が別の同一基板に構成されており、こちらの両出力基板は実機のバック・パネル側に(出力RCAピンと一緒に)取り付けられる場合が多くあります。このような構成を行う場合の注意点としては、

- \*オーディオ信号フローとビデオ信号フローを分離し、信号を交差させない。

- \*基板間のインターフェースにフラット·ケーブルを用いている場合、オーディオ、ビデオ両信号が干渉しないようにインターフェースする。

- \*ポスト・ローパスフィルタの位置を出力回路基板にすると、帯域外ノイズを含んだ信号が引き回され、DAC出力からポスト・ローパスフィルタの間で干渉を受けることがあるので、ポスト・ローパスフィルタは必ずDAC基板に取り付ける。

等があげられます。実機の設計においては、これらの点に注意した配置とインターフェースを行って下さい。

# アナログ出力回路のShort Summary

- \*ポスト・ローパスフィルタの接続はDACと最短距離でDAC出力に直接(Cカップルは必要)する。

- \*+5V単一電源でも推奨ポスト·ローパスフィルタを簡単に用いる ことができる。

- \*ビデオ等の信号とオーディオが混在している場合、相互干渉を 避ける配置、インターフェースを行う。

## PCレイアウト設計例およびケース・スタディ

ここまでは、PCMデバイスの基本接続に関し、理論的背景と数々の実測データをもとに解説してきましたが、これらの各項目は非常に重要なものであり、完全な理解と実践を願ってやみません。

これらの理解を深める意味と実設計の参考として、ここでは代

表的モデルに関してのPCレイアウト・パターンの設計例といくつかの項目に関しての実例、ケース・スタディを示します。

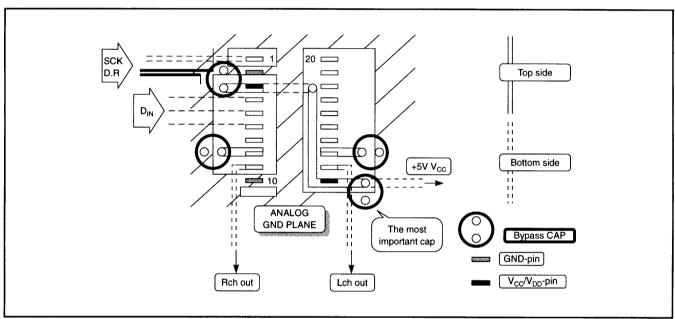

### PCM1717のレイアウト例

図22に、PCM1717のパターン・レイアウト設計例を示します。 他のモデルにも共通ですが、基本事項として、2層両面基板、電源、GND、ロジック・インターフェースの各主要部分のみについて示しています。バイパス・コンデンサについては、最も性能面で影響のあるものを示していますので、このコンデンサについては、そのままこの設計例通りに使用することを推奨します。

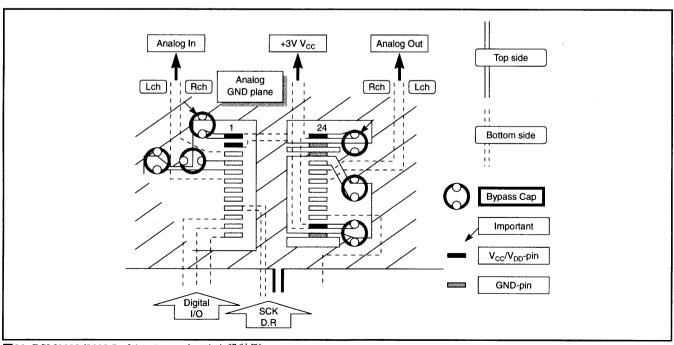

# PCM3002/3003のレイアウト例

図23にPCM3002/3003におけるパターン·レイアウト設計例を示します。

図22. PCM1717のパターン·レイアウト設計例

図23. PCM3002/3003のパターン・レイアウト設計例

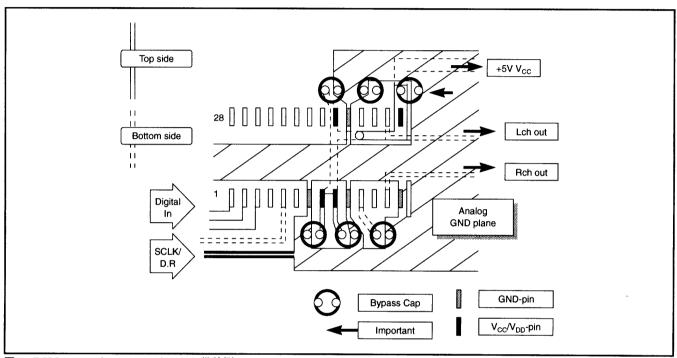

#### PCM1716のレイアウト例

図24にPCM1716におけるパターン·レイアウト設計例を示します。

これら図22、23、24においての共通基本設計要点はいままで述べた解説と全く同じで、

- \*アナログ電源、デジタル電源共通接続

- \*AGND、DGND共通接続、広いアナログ・ベタグランド

- \*バイパス·コンデンサはICピンに最短距離で接続。

- \*システム·クロックラインに平行してDGNDピンからデジタル・ リターン·ラインを接続(ガード効果も含めて)となります。

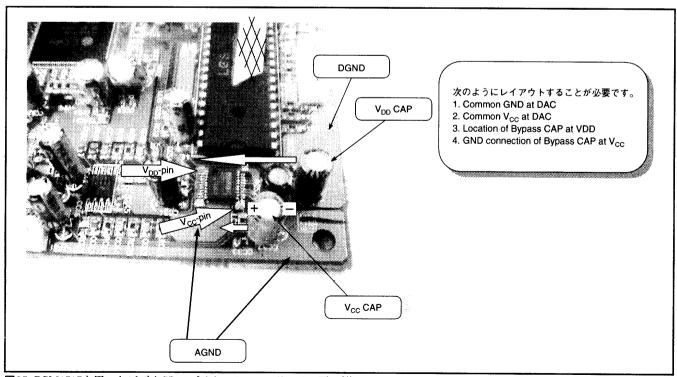

# ケース・スタディ1(良くないPCレイアウト例)

図25にPCM1717を用いたビデオCDアプリケーション・ボードの例を示します。このボードでは、DACの各GNDがボードのデジタルGNDとアナログGNDに接続されていることがまずいけません。また、 $V_{\rm DD}$ ピンのバイパス・コンデンサが $V_{\rm DD}$ ピンから離れており、 $V_{\rm CC}$ ピンのバイパス・コンデンサは+側はICピンの近くですが、-側がICから離れたGNDに接続されており、これは、IC真下側のGNDに接続すべきです。

**図24.** PCM1716のパターン·レイアウト設計例

図25. PCM1717を用いたビデオCDアプリケーション・ボードの悪い例

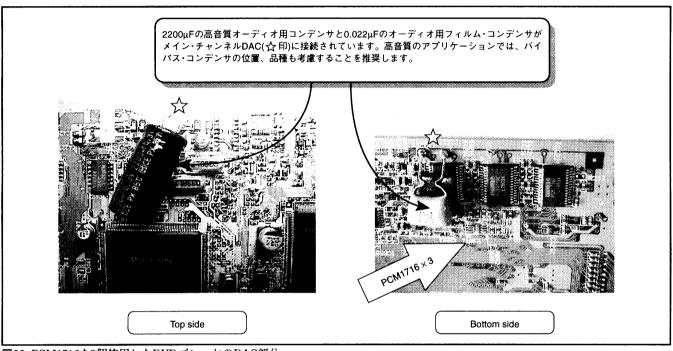

#### ケース・スタディ2(バイパス・コンデンサの良い例)

図26は、PCM1716を3個使用したDVDプレーヤのDAC部分を示したものです。写真からは分かりにくいかもしれませんが、チップ・コンデンサによるバイパス・コンデンサの他に、メインチャンネルDACには2000 $\mu$ Fの高音質オーディオ用コンデンサと0.022 $\mu$ Fのオーディオ用フィルム・コンデンサがそれぞれICピンに最短距離で接続されています。

この処置は、性能面はもとより音質的にも極めて優れていると言えます。特に音質にこだわるアプリケーションでは、バイパス・コンデンサの取り付け位置、品種にまでこだわるべきです。

#### ケース・スタディ3(良くないアナログ出力回路構成例)

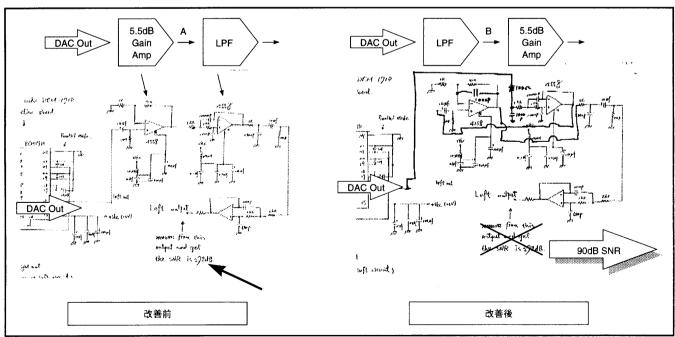

図27(A)はPCM DACの出力回路のある設計例を示しています。この回路では、結果的に72dBのS/N比しか得ることができず、何らかの対応を必要としました。原因は、DAC出力がまずゲイン・アンプに接続されているため、ゲイン・アンプが帯域外ノイズにより正常に動作せず、帯域内に設定ゲイン以上のノイズを発生させてしまうことによります。このため、後段のポスト・ローパスフィルタでは帯域内ノイズはカットできません。この例では、図27(B)に示すように、DAC出力をまずポスト・ローパスフィルタに接続し、その後段にゲイン・アンプをおく構成に変更することにより、S/N比は90dBに改善されました。

**図26.** PCM1716を3個使用したDVDプレーヤのDAC部分

図27. PCM DACの出力回路の設計例

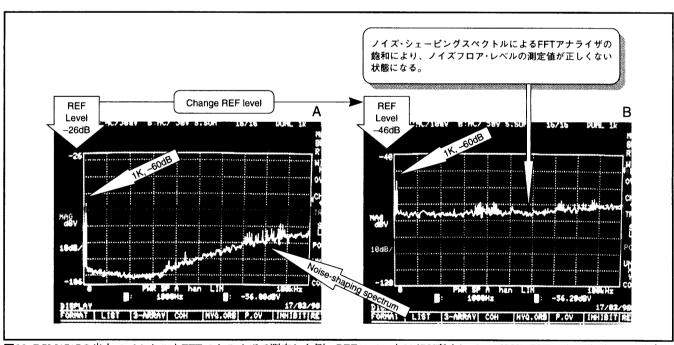

#### ケース・スタディ4(FFT測定での誤動作例)

DACの出力スペクトルは、一般的にはFFTアナライザで測定しますが、PCM DACの場合、帯域外ノイズレベルが比較的大きいためFFTのゲイン・リファレンス設定によってFFTアナライザが誤動作することがあります。

図28(A)は、PCM1717の出力スペクトルをFFTアナライザで測定した例です。信号周波数は1kHz、DAC出力レベルは-60dB、測定帯域は100kHzです。また、FFTアナライザのREF入力レベルを-26dBVに設定しています。DACの-60dB出力レベルに対しFFTアナライザは、まだ20dB以上大きな信号を入力可能なREFレベル設定になっているので、ここで、REFレベルを20dBV高くして-46dBVにFFTアナライザのREF入力レベル設定にしたのが図28(B)です。

図28(B)では、本来図28(A)がそのまま20dBシフトした形でスペクトルが測定されるべきところを、完全に飽和したような測定結果となってしまっています。すなわち、FFTアナライザでさえもDACの帯域外ノイズにより誤動作することがあることを示しており、したがって、ポスト・ローパスフィルタの役割が重要だということをここでは再認識して下さい。

# ケース・スタディ5(良くないアナログ回路構成、インターフェース例)

図29にあるビデオCDプレーヤのオーディオおよびビデオの構成例を示します。ここでは、MPEGデコーダとDACは同一基板上に構成されており、この構成については特に問題ではありません。この例での問題は、オーディオDACのポスト・ローパスフィルタの位置が確かに回路図上ではDAC出力に接続されています

が、実際には別の基板上にあり、この間ビデオ信号とオーディオ 信号がクロスし、なおかつ、細いフラットケーブルでビデオ信号 と一緒にポスト・ローパスフィルタも基板にインターフェースさ れていることです。

このため、この例ではDAC出力信号がビデオ信号との相互干渉でS/N比が84dBと、DACの所定の92dBに比べて8dBもの劣化を起こしています。事実、DAC出力でS/N比を測定すると92dBと所定の性能が得られていますが、回路構成(位置)の悪さと貧弱なインターフェースにより性能の劣化を起こしています。

# Summary

このアプリケーションノートでは、PCMデバイスの基本的な接続方法について、その動作原理、規格、多くの特性実測例、またいくつかのケース・スタディで示してきました。PCMデバイスの基本性能を実機で発揮させるために、ここで示した項目は絶対的に必要な項目ですが、決して難しいことを要求しているものではなく、それに従った設計を行うことが余計なトラブルの回避になり、スムーズな製品生産への一番の近道だと言えます。

ここで、特に絶対的要求項目をもう一度Summaryとして掲げます。

- \*電源(+V<sub>DD</sub>、+V<sub>CC</sub>)およびGND(AGND、DGND)の共通接続

- \*電源、GNDはシステムのアナログ電源、GNDへ接続

- \*少なくとも1µF以上のバイパス·コンデンサをICピンにできる 限り最短距離で接続

- \*ICのDGNDと外部デジタル信号源のGND間にデジタルリターンを接続

- \*ポスト・ローパスフィルタはDAC出力に直接接続(回路的にも物

図28. PCM1717の出力スペクトルをFFTアナライザで測定した例。REFレベルを20dBV高くして-46dBVにFFTアナライザのREF入力レベル設定にする。

図 29. ビデオCDプレーヤのオーディオおよびビデオの構成例

#### 理的にも)

PCMデバイスのアプリケーションは、従来のCDプレーヤを始めとするデジタル・オーディオから、ビデオCD、DVD、PCサウンド、通信ネットワーク、デジタル放送等のマルチメディアに急速に広がっています。実設計エンジニアもオーディオ DACを扱うのは初めてという人も増えている傾向の中、このアプリケーションノートで掲げた基本的な接続法とPCレイアウト例さえ実践していただければ、誰でも簡単かつ確実にPCMデバイスの応用回路を作成できますので、十分な理解と実務への実践を最後にお願いします。

# ご注意

日本テキサス・インスツルメンツ株式会社(以下TIJといいます)及びTexas Instruments Incorporated(TIJの親会社、以下TIJおよびTexas Instruments Incorporatedを総称してTIといいます)は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIの標準契約約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。TI製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI製部品を使用したお客様の製品及びアプリケーションについて想定されうる危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路

配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならない場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、且つその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの黙示的保証を無効にし、且つ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任もありません。

なお、日本テキサス・インスツルメンツ株式会社半導体集積回路製品販売用標準契約約款もご覧下さい。

http://www.tij.co.jp/jsc/docs/stdterms.htm

Copyright © 2006, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社

# 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点 を遵守して下さい。

#### 1. 静電気

- 素手で半導体製品単体を触らないこと。どうしても触る必要がある場合は、リストストラップ等で人体からアースをとり、導電性手袋等をして取り扱うこと。

- 弊社出荷梱包単位(外装から取り出された内装及び個装) 又は製品単品で取り扱いを行う場合は、接地された導 電性のテーブル上で(導電性マットにアースをとったも の等)、アースをした作業者が行うこと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる 全ての装置類は、静電気の帯電を防止する措置を施す こと。

- 前記のリストストラップ・導電性手袋・テーブル表面 及び実装装置類の接地等の静電気帯電防止措置は、常 に管理されその機能が確認されていること。

#### 2. 温·湿度環境

■ 温度:0~40℃、相対湿度:40~85%で保管・輸送 及び取り扱いを行うこと。(但し、結露しないこと。)

- 直射日光があたる状態で保管・輸送しないこと。

- 3. 防湿梱包

- 防湿梱包品は、開封後は個別推奨保管環境及び期間に 従い基板実装すること。

#### 4. 機械的衝撃

● 梱包品(外装、内装、個装)及び製品単品を落下させたり、 衝撃を与えないこと。

# 5. 熱衝撃

● はんだ付け時は、最低限260°C以上の高温状態に、10 秒以上さらさないこと。(個別推奨条件がある時はそれ に従うこと。)

# 6. 汚染

- はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。 (不純物含有率が一定以下に保証された無洗浄タイプの フラックスは除く。)

以上