# C672x DSPを用いたシステム開発のナビゲータ

アプリケーション技術統括部

## アブストラクト

本資料は、C672x DSP (C6722 / C6726 / C6727) を使用したシステム開発のための有用な情報を紹介しています。

この資料は日本テキサス・インスツルメンツ(日本TI)が、お客様がTIおよび日本TI製品を理解するための一助としてお役に立てるよう、作成しております。製品に関する情報は随時更新されますので最新版の情報を取得するようお勧めします。

TIおよび日本TIは、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。また、TI及び日本TIは本ドキュメントに記載された情報により発生した問題や障害等につきましては如何なる責任も負いません。

## 目次

|                                                                 |           |

|-----------------------------------------------------------------|-----------|

| <b>1 はじめに .....</b>                                             | <b>4</b>  |

| <b>2 最新資料について .....</b>                                         | <b>5</b>  |

| 2.1 資料のアップデート情報 .....                                           | 5         |

| 2.2 最新資料の入手方法 .....                                             | 5         |

| 2.3 この資料に記載されているWebアドレス .....                                   | 5         |

| <b>3 ソフトウェア開発のためのナビゲータ .....</b>                                | <b>6</b>  |

| 3.1 開発環境のセットアップ .....                                           | 6         |

| 3.2 統合開発環境 Code Composer Studio IDEの使い方 .....                   | 6         |

| 3.3 Code Composer Studio のバージョン・アップについて .....                   | 6         |

| 3.4 Code Composer Studio の便利なHelp機能 .....                       | 6         |

| 3.5 Code Composer Studio を使ってお客様のボードをデバッグするためには .....           | 6         |

| 3.6 XDS510USBを使用する場合の注意点 .....                                  | 7         |

| 3.7 DSP/BIOSの使い方 .....                                          | 7         |

| 3.8 ペリフェラルを使用する方法（チップ・サポート・ライブラリ） .....                         | 7         |

| 3.9 プログラム最適化の資料 .....                                           | 7         |

| 3.10 最適化ライブラリ (DSP Lib/Imaging Lib/Floating Run-time Lib) ..... | 7         |

| 3.11 システムパッチ .....                                              | 8         |

| 3.12 ブートローダ .....                                               | 8         |

| <b>4 ハードウェア開発のためのナビゲータ .....</b>                                | <b>9</b>  |

| 4.1 データシート/シリコン・エラッタ最新情報 .....                                  | 9         |

| 4.2 CADのシンボル情報/フットプリント情報 .....                                  | 9         |

| 4.3 IBISモデルを使用するボード設計 .....                                     | 9         |

| 4.4 ブルアップ/ブルダウンについて .....                                       | 9         |

| 4.5 入力クロックについて .....                                            | 9         |

| 4.6 PLL回路について .....                                             | 9         |

| 4.7 リセット回路について .....                                            | 10        |

| 4.8 電源について .....                                                | 10        |

| 4.9 コンデンサについて .....                                             | 10        |

| 4.10 電源回路について .....                                             | 10        |

| 4.11 SDRAMを接続する場合の注意点 .....                                     | 11        |

| 4.12 非同期メモリを接続する場合の注意点 .....                                    | 11        |

| 4.13 UHPI経由で外部ホストと接続する方法 .....                                  | 11        |

| 4.14 動作周囲温度について .....                                           | 11        |

| 4.15 JTAG回路について .....                                           | 11        |

| 4.16 バウンダリ・スキャンについて .....                                       | 12        |

| 4.17 ボードをデバッグするときのために .....                                     | 12        |

| <b>5 サービス/サポートについて .....</b>                                    | <b>13</b> |

| 5.1 最新情報の配信サービスについて .....                                       | 13        |

| 5.2 DSPワークショップ/セミナーについて .....                                   | 13        |

| 5.3 TI製品のサポートについて .....                                         | 13        |

| <b>更新履歴 .....</b>                                               | <b>14</b> |

## 図

|                             |           |

|-----------------------------|-----------|

| <b>図 1 RESET回路の一例 .....</b> | <b>10</b> |

|-----------------------------|-----------|

## 表

|                      |    |

|----------------------|----|

| 表 1 ブートモード .....     | 8  |

| 表 2 EMIフィルタの型名 ..... | 9  |

| 表 3 TIの電源ICの一部 ..... | 10 |

## 1 はじめに

本資料は、C672x DSP (C6722 / C6726 / C6727) を使用したシステム開発のために必要な情報を紹介しています。

本資料に記載されている内容は、TI が保証しているものではありませんので、参考資料としてご覧ください。また、他社製品の型名も記載されていますが、TI が推奨しているものではありませんのでご注意ください。

システム開発には、最新のデータシート、最新のシリコン・エラッタ、最新のユーザーズ・ガイドを参照してください。

## 2 最新資料について

設計開発時には、必ず、最新のデータシート、最新のシリコン・エラッタ、最新のユーザーズ・ガイドを参照してください。

### 2.1 資料のアップデート情報

英文資料に関しては、更新履歴（90日間）のページがあります。

<http://www.ti.com/sc/docs/pssheets/newdocs/techmenu.htm>

データシートやエラッタなどが更新された場合には、上記Webに掲載されます。

### 2.2 最新資料の入手方法

データシート、シリコン・エラッタ、ユーザーズ・ガイドなどの最新資料は、TI USサイトの Product Folderまたは日本TIサイトのDSP技術資料ページからダウンロードすることができます。

TMS320C6722 Product Folder (英語)

<http://focus.ti.com/docs/prod/folders/print/tms320c6722.html>

TMS320C6726 Product Folder (英語)

<http://focus.ti.com/docs/prod/folders/print/tms320c6726.html>

TMS320C6727 Product Folder (英語)

<http://focus.ti.com/docs/prod/folders/print/tms320c6727.html>

C67x/C67x+ コア技術資料 (日本語)

<http://www.tij.co.jp/jsc/docs/dspss/support/download/c6000/c67x.htm>

### 2.3 この資料に記載されている Web アドレス

この資料に記載されているアプリケーション・ノート、ユーザーズ・ガイドなどが更新された場合、Webアドレスのリンクが切れてしまいます。リンク切れの場合、Product Folderまたは C67x/C67x+ コア技術資料ページからダウンロードしてください。

### 3 ソフトウェア開発のためのナビゲータ

この章ではソフトウェア開発のための有用な情報をご紹介します。

#### 3.1 開発環境のセットアップ

C672xのソフトウェア開発を行うためには、以下の環境が必要です。

- Code Composer Studio v3.1

- CCSStudio v3.1 Service Pack 1 Rev2

- C672x Chip Support Package

CCStudio v3.1 Service Pack 1 Rev2 および C672x Chip Support Package はアップデート・アドバイザからダウンロードすることができます。アップデート・アドバイザに関しては、3.3 節を参照してください。

以下の手順でインストールを実行してください。

1. Code Composer v3.1

2. C672x Chip Support Package

3. CCSStudio v3.1 Service Pack 1

4. C672x Chip Support Package (再インストール)

上記の手順でインストールを行わない場合、C672xのソフトウェア開発環境を正常にインストールすることができませんのでご注意ください。

Spectrum Digital社製のエミュレータを使用するためには、上記の他にエミュレータのドライバをインストールする必要があります。エミュレータのドライバは以下のURLからダウンロードすることができます。

<http://emulators.spectrumdigital.com/c6000/>

#### 3.2 統合開発環境 Code Composer Studio IDE の使い方

C6000 DSP のソフトウェア開発は、統合開発環境 Code Composer Studio (CCS) を使用して行います。CCSの使い方については、以下の資料を参照してください。

Code Composer Studio 入門マニュアル (英語版) [SPRU509]

<http://focus.ti.com/lit/ug/spru509g/spru509g.pdf>

Code Composer Studio 入門マニュアル (日本語版) [SPRU567]

<http://www.tij.co.jp/jsc/docs/dspssupport/download/tools/toolspdf5000/SPRU567D.pdf>

Code Composer Studio User's Guide (英語版) [SPRU328]

<http://focus.ti.com/lit/ug/spru328b/spru328b.pdf>

また、CCSのCコンパイラに関しては、以下の資料を参照してください。

TMS320C6000オプティマイジング(最適化) C/C++コンパイラ (日本語版) [SPRU419]

<http://www.tij.co.jp/jsc/docs/dspssupport/download/tools/toolspdf6000/spru419b.pdf>

TMS320C6000オプティマイジング(最適化) C/C++コンパイラ (英語版) [SPRU187]

<http://focus.ti.com/lit/ug/spru187n/spru187n.pdf>

C6000開発ツール (CCS) のエラッタ (不具合) は、下記Webからご覧ください。

<http://focus.ti.com/general/docs/buglist/bugsearch.tsp?templateId=5121&navigationId=11278>

#### 3.3 Code Composer Studio のバージョン・アップについて

統合開発環境 Code Composer Studioは、アップデート・アドバイザからバージョン・アップを行います。CCSの最新バージョンはアップデート・アドバイザにアップロードされます。アップデート・アドバイザを開くためには、CCS上のメニューの Help->Update Advisor->Check for Update を選択してください。

アップデート有効期間が過ぎてしまうと、アップデート・アドバイザからアップデート・ファイルをダウンロードできなくなります。このため、アップデート有効期間中には、頻繁にアップデート・アドバイザをチェックして、最新版ファイルをダウンロードしておくことをお勧めします。アップデート期間が過ぎてしまった場合、アップデート版を購入してください。

#### 3.4 Code Composer Studio の便利な Help 機能

CCSには便利なHelp機能が搭載されています。CCSのHelpには、CCSの機能、DSP/BIOS、Chip Support Library、C6000コアの命令セットなど、ソフトウェア開発に役立つ情報が記載されています。CCSのHelpは、CCS上のメニューの Help->Contentsで立ち上がります。

#### 3.5 Code Composer Studio を使ってお客様のボードをデバッグするためには

お客様の作成したボード上でプログラムの実行やデバッグを行うためには、CCSの他にエミュレータが必要です。CCSでデバッグするためには、以下の手順を実行します。

1. ボード上の JTAG ヘッダ (ハードウェアの章で説明) とエミュレータを接続します。

2. Setup CCS で使用するエミュレータのドライバを選択します。

3. CCS を起動します。

4. CCS メニューの Debug->Connect を選択します。

CCSのセットアップ方法に関する詳細は、Code Composer Studio User's Guide（英語版）を参照してください。

### 3.6 XDS510USB を使用する場合の注意点

XDS510USB を使用して C672x のエミュレーションを行うためには、`sdocts.cfg` というファイルの内容を修正する必要があります。`sdocts.cfg` は、以下のフォルダにあります。

C:\Windows\system32\

```

sdocts.cfg の

#EmuFirmware=sdxds510usb_v10_1.out

を

EmuFirmware=sdxds510usb_v10_1.out

に変更 (#を削除) してください。

```

上記に関する詳細は以下のサイトを参照してください。

[http://support.spectrumdigital.com/ccs31/Release-30104C/ReadMe\\_C672x.htm](http://support.spectrumdigital.com/ccs31/Release-30104C/ReadMe_C672x.htm)

### 3.7 DSP/BIOS の使い方

DSP/BIOSは、統合開発環境CCSに付属しているリアルタイムOSであり、ライセンス・フリーで使用できます。DSP/BIOSを利用すると、割り込み処理やタスク管理などを容易に行うことが可能です。DSP/BIOSの使い方に関しては、下記の資料をご参照ください。

TMS320 DSP/BIOS User's Guide（英語版）[SPRU423]

<http://focus.ti.com/lit/ug/spru423b/spru423b.pdf>

TMS320C6000 DSP/BIOS Application Programming Interface (API) Reference Guide [SPRU403]

<http://focus.ti.com/lit/ug/spru403f/spru403g.pdf>

DSP/BIOS 5.20 Textual Configuration (Tconf) User's Guide [SPRU007]

<http://focus.ti.com/lit/ug/spru007g/spru007g.pdf>

### 3.8 ペリフェラルを使用する方法（チップ・サポート・ライブラリ）

ペリフェラルに簡単にアクセスするために、チップ・サポート・ライブラリが提供されています。C672x チップ・サポート・ライブラリは以下のURLからダウンロードすることができます。チップ・サポート・ライブラリのドキュメントおよびサンプル・コードも同時にダウンロードすることができます。

<http://focus.ti.com/docs/toolsw/folders/print/sprc223.html>

ペリフェラルの機能やレジスタに関しては、ユーザーズ・ガイドをご参照ください。ペリフェラルのユーザーズ・ガイドは Product Folder からダウンロードすることができます。

### 3.9 プログラムの最適化

プログラムの最適化の方法に関しては、以下のアプリケーション・ノート、およびDSP Forum 内の「システム全体から見たプログラム最適化時の注意点」をご参照ください。

TMS320C6000 Optimization Technique（日本語アプリケーション・ノート）

[http://www.tij.co.jp/jsc/docs/dspss/support/download/c6000/c6000pdf/c6000\\_application\\_note.pdf](http://www.tij.co.jp/jsc/docs/dspss/support/download/c6000/c6000pdf/c6000_application_note.pdf)

TMS320C6000 オプティマイジング（最適化）C/C++コンパイラ（第3章）

[http://www.tij.co.jp/jsc/docs/dspss/support/download/tools/toolspdf6000/CJ\\_spru419a.pdf](http://www.tij.co.jp/jsc/docs/dspss/support/download/tools/toolspdf6000/CJ_spru419a.pdf)

TMS320C6000 Programmer's Guide [SPRU198]

<http://focus.ti.com/lit/ug/spru198i/spru198i.pdf>

DSP Forum（閲覧するためにはユーザー登録が必要です）

<http://www.tij.co.jp/DSPForum/Default.asp>

### 3.10 最適化ライブラリ (DSP Lib / Imaging Lib / FastRts Lib)

最適化された以下の3つのライブラリ、デジタル信号処理ライブラリ (DSP Lib)、画像処理ライブラリ (Imaging Lib)、浮動小数点演算高速ランタイム・サポート・ライブラリ (FastRts Lib) が無償で提供されています。ライブラリおよびユーザーズ・ガイドは、以下のURLからダウンロードすることができます。

C67x デジタル信号処理ライブラリ (FFT/FIR/IIRなど)

<http://focus.ti.com/docs/toolsw/folders/print/sprc121.html>

C62x 画像処理ライブラリ

<http://focus.ti.com/docs/toolsw/folders/print/sprc093.html>

C67x 浮動小数点演算高速ランタイム・サポート・ライブラリ

<http://focus.ti.com/docs/toolsw/folders/print/sprc060.html>

デジタル信号処理ライブラリと浮動小数点演算高速ランタイム・サポート・ライブラリは C672x の内蔵ROM にマスクされています。内蔵ROM 内のライブラリを使用する方法は、3.11 節を参照してください。

### 3.11 システムパッチ

C672x の内蔵 ROM には、DSP/BIOS、DSP Lib、FastRTS Lib がマスクされています。これらを使用するためには、システムパッチを適用する必要があります。システムパッチの適用方法、および内蔵 ROM の DSP/BIOS と各ライブラリの使用方法に関しては、以下のアプリケーション・ノートを参照してください。

C9230C100 TMS320C672x Floating-Point Digital Signal Processor ROM

<http://focus.ti.com/lit/an/sprs277b/sprs277b.pdf>

システムパッチは以下のURLからダウンロードすることができます。

<http://focus.ti.com/docs/toolsw/folders/print/sprc203.html>

また、バージョン 2.00 以降のシステムパッチを適用すると、dMAX の SPI スレーブ転送および 1 次元バースト転送を使用することができるようになります。

Using the TMS320C672x Bootloader [SPRAA69]

<http://focus.ti.com/lit/an/spraa69c/spraa69c.pdf>

ブートローダ・ユーティリティは以下のURLからダウンロードすることができます。

<http://www-s.ti.com/sc/psheets/sprc203/sprc203.zip>

また、Parallel Flashブートで必要な 2ndブートローダの作成方法については、以下の資料をご参照ください。

Creating a Second-Level Bootloader for FLASH Bootloading on TMS320C6000 Platform With Code Composer Studio [SPRA999]

<http://focus.ti.com/lit/an/spra999a/spra999a.pdf>

実行ファイル (\*.out) をHex形式に変換するために、Hex変換ユーティリティを使用することができます。Hex変換ユーティリティの使用方法については、以下の資料をご参照してください。

TMS320C6000 Assembly Language Tools User's Guide [spru186]

Chapter 11 Hex Conversion Utility Description

<http://focus.ti.com/lit/ug/spru186p/spru186p.pdf>

### 3.12 ブートローダ

C672x DSPには、以下のブートモードがあります。

表1 ブートモード

| ブートモード         | 説明                                                                            |

|----------------|-------------------------------------------------------------------------------|

| HPI (C6727のみ)  | UHPI経由で、ホストCPUがプログラムをダウンロードします。                                               |

| Parallel Flash | FlashからEMIF経由でプログラムをダウンロードします。Parallel Flashブートでは、ユーザーが2ndブートローダを作成する必要があります。 |

| SPIマスタ         | EEPROMからSPI経由でプログラムをダウンロードします。プログラムはAIS形式にする必要があります。                          |

| SPIスレーブ        | ホストCPUがSPI経由でプログラムをダウンロードします。プログラムはAIS形式にする必要があります。                           |

| I2Cマスタ         | EEPROMからI2C経由でプログラムをダウンロードします。プログラムはAIS形式にする必要があります。                          |

| I2Cスレーブ        | ホストCPUがI2C経由でプログラムをダウンロードします。プログラムはAIS形式にする必要があります。                           |

AISとは、C672x ブートローダ用のスクリプトの形式です。ブートローダ・ユーティリティを使用すると、実行ファイル (.out) を AIS形式に変換することができます。ブートローダとブートローダ・ユーティリティに関する詳細は、以下の資料をご参照ください。

## 4 ハードウェア開発のためのナビゲータ

この章では、ハードウェア開発のための有用な情報を紹介します。本書は、ボード回路設計/レイアウトなどのハードウェア開発をサポートするために作られた資料であり、TIが保証しているものではありません。あくまで、参考資料としてお使いください。また、ボード構成はお客様のシステムによって異なります。DSPを含んだシステム全体として正常動作するかどうか、お客様の責任で評価/確認してください。

### 4.1 データシート/シリコン・エラッタ最新情報

設計を始める場合、必ず最新のデータシートおよび最新のシリコン・エラッタを参照してください。最新資料の入手方法は、この資料の 2.2 節をご参照ください。

### 4.2 CAD のシンボル情報/フットプリント情報

各種CADツール用のシンボル情報/フットプリント情報を入手できます。これらは、各デバイスの「Product Folder」ページ内にあるPricing/Packaging テーブルの CAD Design Tools カラムからダウンロードすることができます。

### 4.3 IBIS モデルを使用するボード設計

IBISとは、「I/O Buffer Information Specification」の略で、ANSI/EIA-656-Aで規定されています。

<http://www.eigroup.org/ibis/ibis.htm>

IBISモデルは、すべてのプロセス・コンディションでの出入力ピンのバッファのふるまいを正しくモデリングしたものです。IBISモデルを使用してボード・レベルのシミュレーションを行うことにより、クロック/コントロール/データ・ラインなどの各ラインの最適な引き回し、およびデバイスの最適なレイアウトを行うことが可能です。以上の理由から、IBISモデルを使用してタイミング特性を正しく解析することをお勧めします。C672x DSPのIBISモデルは、Product Folder からダウンロード可能です。IBISモデルを使用するためには、下記ベンダーなどからシミュレーション・パッケージなどを購入する必要があります。

- 図研 <http://www.zuken.co.jp/>

- パッズ・ジャパン株式会社 HyperLynx

<http://www.padsjapan.co.jp/>

- Mentor Graphics HyperLynx

<http://www.mentor.com/pads/highspeed.html>

IBISを使ったタイミング解析に関しては、以下のアプリケーション・ノートをご参照ください。

Using IBIS Models for Timing Analysis (英語)

<http://focus.ti.com/lit/an/spra839a/spra839a.pdf>

Using IBIS Models for Timing Analysis (日本語)

<http://www.tij.co.jp/jsc/docs/dspssupport/download/c6000/c6000pdf/spraae2.pdf>

また、高速ボード設計が得意なサード・パーティもあります。詳細は、下記サード・パーティのページをご参照ください。

<http://www.tij.co.jp/jsc/docs/dspssupport/3rd/corp/index.htm>

### 4.4 プルアップ/プルダウンについて

内部プルアップ/プルダウンされていない未使用ピンは、外部でプルアップまたはプルダウンすることを推奨しています。また、/TRSTピンは内部プルダウンされていますが、高ノイズ環境下では、外部でプルダウンすることを推奨しています。

### 4.5 入力クロックについて

入力クロック回路については、データシートの 4.17 External Clock Input From Oscillator or CLKIN Pin をご参照ください。

発振器とCLKINの配線に関しては、一般的に以下の点に注意してください。

- できるだけ短く、配線はまっすぐ、引き回しは最小限に。複数のレイヤをまたぐ配線は極力避けてください。

- TOP レイヤに配線してください。内層にいれる場合、クロストークを抑えるため、GND/電源層などではさむか、保護トレース・ラインを追加するようにしてください。

- シリーズ抵抗などを挿入して正しく終端してください。インピーダンスの整合がとれない場合、波形割れなどが発生することが考えられます。

- 発振器の DVdd と DSP の DVdd を同じ平面にしてください。

- 発振器は、ソケットにせずに直接ボードに接続してください。

### 4.6 PLL 回路について

C672x には PLL 用の電源入力ピン (PLLHV) があります。PLLHV と DVdd の間には、EMI フィルタを含む回路を作成する必要があります。推奨EMI フィルタは以下の通りです。

表 2 EMI フィルタの型名

| 会社名                                                               | 型名         |

|-------------------------------------------------------------------|------------|

| TDK ( <a href="http://www.tdk.co.jp/">http://www.tdk.co.jp/</a> ) | ACF451832- |

|                                                                                                                            |                               |

|----------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| Panasonic<br>( <a href="http://industrial.panasonic.com/jp/index.html">http://industrial.panasonic.com/jp/index.html</a> ) | 333,223,153,103<br>EXCCET103U |

|----------------------------------------------------------------------------------------------------------------------------|-------------------------------|

EMI フィルタに関する詳細は、データシートの 4.18 Phase-Locked Loop (PLL) をご参照ください。

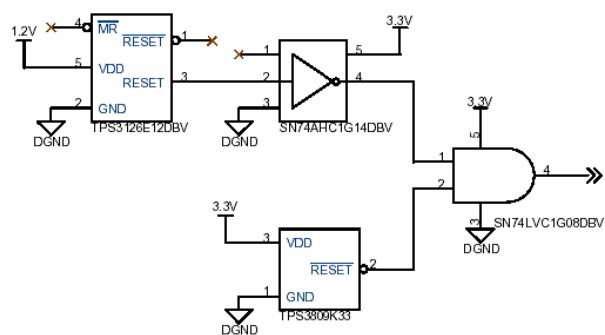

#### 4.7 リセット回路について

/RESET (ハードウェア・リセットピン) は、電源投入中 (電源電圧投入開始から動作電圧に到達する間) には Low に保つことを推奨しています。/RESET ピンをデアサート (Low → High) する前に、CVdd および DVdd は動作電圧範囲に到達している必要があります。

CVdd : 1.2V、DVdd : 3.3V の電源監視の回路例をいかに示します。

図 1 RESET回路の一例

また、リセット回路に関しては、以下のアプリケーション・ノートを参考にしてください。

TMS320C6000 Board Design: Considerations for Debug

<http://focus.ti.com/lit/an/spra523c/spra523c.pdf>

Reset Circuit for the TMS320C6000 DSP

<http://focus.ti.com/lit/an/spra431a/spra431a.pdf>

#### 4.8 電源について

電源電圧は、DSPの電源端子上で CVdd/DVdd の仕様を満たすようにしてください。レギュレータのピン付近では仕様を満たしている場合でも、DSPの端子付近では仕様を満たしていない場合があります。

電源およびGNDプレーンについては、以下の内容に注意してください。

- レギュレータと DSP との間を細い線幅で接続すると、電圧降下が起こりやすくなり、電源のゆれに対する応答も悪くなります。

- 電源プレーンは、GND プレーンよりも一回り小さくして

ください。

- 電源ラインのインダクタンスと抵抗の個数を最小限にするために、CVdd と DVdd の電圧を作成するレギュレータは DSP に近くに配置してください。多数の DSP を使用する場合、電源プレーンを分けて複数個の電源を使用してください。可能であれば、CVdd プレーンを他のデバイスの電源プレーンと共有せずに、1 つの DSP 専用にしてください。

#### 4.9 コンデンサについて

電源ICから生じる低周波数 (<1kHz) のノイズを削減するために、またデバイス・ピンが同時にスイッチングした場合に電源電圧レベルを安定化するために、電源IC出力部分に極性付き (タンタル) コンデンサ (約47uF) を置いてください。また、GND/CVdd/DVdd プレーンの電圧を極力ゆれないようにするために、また高周波ノイズも削減できるようにするために、ESL/ESRが小さいコンデンサ (パス・コン) を DSP にできるだけ近い位置に挿入してください。高品質のコンデンサを使っていても、DSPから離して配置してしまった効果は小さくなってしまいます。

パス・コンの容量や個数の推奨値に関しては、データシートの 4.7.2 Power-Supply Decoupling をご参照ください。

#### 4.10 電源回路について

C672x DSPは、2電源電圧 (CVdd/DVdd) のデバイスとなっています。電源の立ち上げに関しては、以下の点に注意してください。

- 片方の電源のみを立ち上げたまま、そのまま (1 秒以上) にしないでください。

- DVdd を先に立ちあげる場合には、バス衝突が起こらないような設計をする必要があります。CVdd が立ち上がる前は、DSP の I/O 端子は不定状態であるため、外部デバイスとバスの衝突が起こる可能性があります。

電源ICは出力電流に多少余裕があるものを使用してください。DSPの消費電流は、以下のスプレッド・シートで見積もりすることができます。

TMS320C672x Power Consumption Summary [SPRAAA4]

<http://focus.ti.com/lit/an/spraaa4a/spraaa4a.pdf>

電源ICとDSP間で電圧降下が起こる可能性がありますので、電圧を調整できる電源ICを使用することをお勧めします。電圧調整可能な電源ICを使用すると、デバイスのプロセス・シミュリンクによるコア電圧変更にも対応しやすくなります。以下に、コア電圧1.2V～1.4Vが出力できる TI の電源ICの例を示します。

表 3 TIの電源ICの一部

| 種類          | 型名       | 入力   | 出力                 | 出力電流 | シーケンス |

|-------------|----------|------|--------------------|------|-------|

| DC/DC Conv. | TPS54310 | 3-6V | Adj.(0.9-4.5V)[1%] | 3A   | -     |

|                   |          |         |                          |        |           |

|-------------------|----------|---------|--------------------------|--------|-----------|

|                   | TPS54312 | 3-6V    | 1.2V[1%]                 | 3A     | -         |

|                   | TPS54380 | 3-6V    | Adj.(0.9-4.5V)[1%]       | 3A     | Adj.      |

|                   | TPS54610 | 3-6V    | Adj.(0.9-4.5V)[1%]       | 6A     | -         |

|                   | TPS54612 | 3-6V    | 1.2V[1%]                 | 6A     | -         |

| Dual LDO          | TPS70402 | 5V      | 3.3V/Adj.(1.22-3.3V)[2%] | 1A/2A  | Adj.      |

| DC/DC Cont.       | TPS5110  | 2.5-28V | 3.3V/Adj.(0.9-2.5V)[1%]  | (FET)  |           |

|                   | TPS5120  | 4.5-28V | Adj/Adj.(0.9-3.3V)       | (FET)  |           |

| DualPlugin Module | PTS6938  | 3.3-5V  | 3.3V/1.2V                | 7/1.6A | Same time |

|                   | PTS6944  | 3.3-5V  | 3.3V/1.2V                | 6A     | Same time |

TIの電源ICの製品情報は以下のページをご参照ください。

<http://www.tij.co.jp/jsc/docs/msp/analog/pmp/pmp.html>

#### 4.11 SDRAM を接続する場合の注意点

SDRAM を接続する場合には、以下の点に注意してください。

- SDRAM を接続する場合は、IBIS Model で評価することをお勧めします。

- 等長配線にしてください。

- SDRAM は、配線の遅延などを考慮すると非常にタイミングが厳しいため、実際に動作させる周波数より高い周波数のデバイスを選択することをお勧めします。

- Bus Buffer はできるだけ使用しないでください。どうしても必要な場合には、Bus Buffer ではなく Cross Bus Switch を使用してください。ただし、Switch の場合、Buffer と違い配線を伸ばすことはできません。

- アドレス/データ線などのオーバー・シート、アンダー・シートを抑えるために、ダンピング抵抗をいれて、受信部の波形をきれいにするように調整してください。（IBIS Model にて評価してください。）

- C6000 DSP のドライブ能力は、それほど高くありません。このため、一つの DSP に多くの I/O やメモリを接続することはできません。多数のメモリを接続する場合には、Cross Bus Switch を使用してください。

SDRAMとの接続例/設定例は、以下のアプリケーション・ノートをご参照ください。

TMS320C6000 EMIF-to-External SDRAM Interface [SPRA433]

<http://focus.ti.com/lit/an/spra433d/spra433d.pdf>

#### 4.12 非同期メモリを接続する場合の注意点

C672x のアドレスピンの本数は、BGAパッケージで13本、QFPパッケージで12本となっています。このため、BGAでは32kバイト、QFPでは16kバイトの領域までしかアクセスすることが

できません。より大きなメモリを接続するためには、アドレスの上位ピンをGPIOピン等で補う必要があります。上位アドレスをGPIOピンで代用する場合、かつ Parallel Flashポートを使用する場合、そのGPIOピンは必ずプルダウンしてください。

#### 4.13 UHPI 経由で外部ホストと接続する方法

UHPI（ホストポート・インターフェイス）経由で外部のホストと接続する場合は、以下のアプリケーション・ノートおよび UHPI のリファレンスガイドをご参照ください。UHPI のリファレンスガイドは Product Folder からダウンロードできます。

TMS320C6000 EMIF to TMS320C6000 Host Port Interface [SPRA536]

<http://focus.ti.com/lit/an/spra536b/spra536b.pdf>

#### 4.14 動作周囲温度について

C672x DSPは、動作保証範囲をDSPのケース温度で規定しています。動作周囲温度は計算で求めることができます。動作周囲温度を計算するためには、DSPの消費電力、風の流れに対応するパッケージのThermal Resistance（熱抵抗）の値が必要です。計算の方法の詳細は以下のアプリケーション・ノートをご参照ください。

TMS320C6x Thermal Design Considerations [SPRA432]

<http://focus.ti.com/lit/an/spra432/spra432.pdf>

パッケージの Thermal Resistance（熱抵抗）の値は、データシートの

7.1 Package Thermal Resistance Characteristics をご参照ください。

#### 4.15 JTAG 回路について

JTAG周回路は、JTAGヘッダとDSP間が6インチ（約15cm）以内の場合、6インチより離れている場合、複数のデバイスを接続する場合によって異なります。詳細は下記リファレンスガイドをご参照ください。

TMS320C6000 DSP Designing for JTAG Emulation Reference Guide [SPRU641]

<http://focus.ti.com/lit/ug/spru641/spru641.pdf>

TMS320C6000: Board Design for JTAG [SPRA584]

<http://focus.ti.com/lit/an/spra584c/spra584c.pdf>

CCSが立ち上がらない場合、またはDSPの動作が不安定な場合には、以下のことを試してみてください。

- ノイズの多い環境であれば、/TRST ピンを Pull-down してください。

- TCK のクロックを遅くしてみてください。TI XDS510 エ

ミュレータを使用する場合、TCKは約10MHzとなります。

XDS560エミュレータを使用する場合、TCKのクロック

はSetup CCS内でユーザーが設定できます。

#### 4.16 バウンダリ・スキャンについて

バウンダリ・スキャンを実行すると、デバイスの接続試験を行なうことができます。バウンダリ・スキャンを実行するためには、BSDLファイルが必要です。BSDLファイルはProduct Folderからダウンロードすることができます。

バウンダリ・スキャンを実行するためには、EMU0/EMU1ピンをLowにする必要があります。詳細は、データシートおよび下記アプリケーション・ノートをご参照ください。

TMS320C6000: Board Design for JTAG [SPRA584]

<http://focus.ti.com/lit/an/spra584c/spra584c.pdf>

バウンダリ・スキャンを行う場合、特にDSPと他のデバイスを組み合わせて行なう場合、以下の処理を行なったほうがよい場合があります。

電源立ち上げ時は、/TRST、/RESETとともにLowにする

/RESETを解除する、また、EMU0/EMU1をLowの状態にする

そのまま、TCLKを10クロック以上いれる

/TRSTをHighにして、10クロック以上いれる

(/TRST Low-to-HighでEMU0/EMU1の値をラッ

チする)

(TMSをHighにして、5クロック以上いれる)

#### 4.17 ボードをデバッグするときのために

以下のような点を考慮して設計を行うと、デバッグするときに便利です。

- 重要な信号ラインには波形計測用にTest Pointをつける

- マニュアル・リセット（リセット・ボタン）をつける

- ブートモードの変更を可能にする

- クロック・モードの変更を可能にする

- 電源電圧の変更を可能にする

量産ボードでもJTAGのパターンを出しておく

## 5 サービス／サポートについて

### 5.1 最新情報の配信サービスについて

日本TIおよびTI USでは、以下のような情報を提供しております。ユーザー登録制になっておりますので、Webにて、ご登録ください。

#### e-NewsLetter

TI Japanから日本語にて最新の情報をE-Mailにて提供。

<http://www.tij.co.jp/jsc/docs/dspdocs/newsletter/index.htm?eNL=46840>

#### TI&ME

TI USから、英文で最新の情報をE-Mailにて提供。お客様が必要な情報をカスタマイズして表示。

<https://my.ti.com/>

#### DSP Forum

ユーザー同士の意見交換をするための会議室があります。

<http://www.tij.co.jp/DSPForum/Default.asp>

### 5.2 DSP ワークショップ／セミナーについて

TI が開催するDSPのワークショップ／セミナーは以下Webをご覧ください。

<http://www.tij.co.jp/jsc/docs/dspws/wshome.htm>

### 5.3 TI 製品のサポートについて

DSPに関する技術的な質問がある場合、お取引頂いております販売特約店、弊社担当営業、または日本TIプロダクト・インフォメーション・センター（PIC）にお問い合わせください。

#### 弊社特約店一覧

<http://www.tij.co.jp/jsc/docs/distmenu.htm>

#### 日本TI プロダクト・インフォメーション・センター (PIC)

<http://www.tij.co.jp/jsc/docs/pic/pichome.htm>

DSPの技術的な質問以外（納期や価格など）については、販売特約店または弊社担当営業にお問い合わせください。

## 更新履歴

| 版            | ページ | 追加/変更/削除項目         |

|--------------|-----|--------------------|

| 初版<br>Jun/06 |     | 初版リリース             |

| 第2版          | 6   | 3.1 開発環境のセットアップを修正 |

# ご注意

日本テキサス・インスツルメンツ株式会社(以下TIJといいます)及びTexas Instruments Incorporated(TIJの親会社、以下TIJおよびTexas Instruments Incorporatedを総称してTIといいます)は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIの標準契約約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。TI製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI製部品を使用したお客様の製品及びアプリケーションについて想定される危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾することは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならぬ場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、且つその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの黙示的保証を無効にし、且つ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任もありません。

なお、日本テキサス・インスツルメンツ株式会社半導体集積回路製品販売用標準契約約款をご覧下さい。

<http://www.tij.co.jp/jsc/docs/stdterms.htm>

Copyright © 2006, Texas Instruments Incorporated

日本語版 日本テキサス・インスツルメンツ株式会社

## 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。

### 1. 静電気

- 素手で半導体製品単体を触らないこと。どうしても触る必要がある場合は、リストストラップ等で人体からアースをとり、導電性手袋等をして取り扱うこと。

- 弊社出荷梱包単位(外装から取り出された内装及び個装)又は製品単品で取り扱いを行う場合は、接地された導電性のテーブル上で(導電性マットにアースをとったもの等)、アースをした作業者が行うこと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

- 前記のリストストラップ・導電性手袋・テーブル表面及び実装装置類の接地等の静電気帯電防止措置は、常に管理されその機能が確認されていること。

### 2. 溫・湿度環境

- 温度：0～40°C、相対湿度：40～85%で保管・輸送及び取り扱いを行うこと。(但し、結露しないこと。)

- 直射日光があたる状態で保管・輸送しないこと。

- 3. 防湿梱包

- 防湿梱包は、開封後は個別推奨保管環境及び期間に従い基板実装すること。

- 4. 機械的衝撃

- 梱包品(外装、内装、個装)及び製品単品を落させたり、衝撃を与えないこと。

- 5. 熱衝撃

- はんだ付け時は、最低限260°C以上の高温状態に、10秒以上さらさないこと。(個別推奨条件がある時はそれに従うこと。)

- 6. 汚染

- はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。(不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。)

以上

# ご注意

IMPORTANT NOTICE

日本テキサス・インスツルメンツ株式会社（以下TIJといいます）及びTexas Instruments Incorporated(TIJの親会社、以下TIJないしTexas Instruments Incorporatedを総称してTIといいます）は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIJとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIJの標準販売契約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIJとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。TI製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI製部品を使用したお客様の製品及びアプリケーションについて想定される危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならぬ場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、かつその情報と結び付いた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの黙示的保証を無効にし、かつ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任も負いません。

TIは、TIの製品が、安全でないことが致命的となる用途ないしアプリケーション（例えば、生命維持装置のように、TI製品に不良があった場合に、その不良により相当な確率で死傷等の重篤な事故が発生するようなもの）に使用されることを認めめておりません。但し、お客様とTIの双方の権限ある役員が書面でそのような使用について明確に合意した場合は除きます。たとえTIがアプリケーションに関連した情報やサポートを提供了としても、お客様は、そのようなアプリケーションの安全面及び規制面から見た諸問題を解決するために必要とされる専門的知識及び技術を持ち、かつ、お客様の製品について、またTI製品をそのような安全でないことが致命的となる用途に使用することについて、お客様が全ての法的責任、規制を遵守する責任、及び安全に関する要求事項を満足させる責任を負っていることを認め、かつそのことに同意します。さらに、もし万一、TIの製品がそのような安全でないことが致命的となる用途に使用されたことによって損害が発生し、TIないしその代表者がその損害を賠償した場合は、お客様がTIないしその代表者にその全額の補償をするものとします。

TI製品は、軍事的用途もしくは宇宙航空アプリケーションないし軍事的環境、航空宇宙環境にて使用されるようには設計もされていませんし、使用されることを意図されておりません。但し、当該TI製品が、軍需対応グレード品、もしくは「強化プラスティック」製品としてTIが特別に指定した製品である場合は除きます。TIが軍需対応グレード品として指定した製品のみが軍需品の仕様書に合致いたします。お客様は、TIが軍需対応グレード品として指定していない製品を、軍事的用途もしくは軍事的環境下で使用することは、もっぱらお客様の危険負担においてなされるということ、及び、お客様がもっぱら責任をもって、そのような使用に関して必要とされる全ての法的要件及び規制上の要求事項を満足させなければならないことを認め、かつ同意します。

TI製品は、自動車用アプリケーションないし自動車の環境において使用されるようには設計されていませんし、また使用されることを意図されておりません。但し、TIがISO/TS16949の要求事項を満たしていると特別に指定したTI製品は除きます。お客様は、お客様が当該TI指定品以外のTI製品を自動車用アプリケーションに使用しても、TIは当該要求事項を満たしていなかったことについて、いかなる責任も負わないことを認め、かつ同意します。

Copyright 2008, Texas Instruments Incorporated

日本語版 日本テキサス・インスツルメンツ株式会社

## 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。

### 1. 静電気

- 素手で半導体製品単体を触らないこと。どうしても触る必要がある場合は、リストストラップ等で人体からアースをとり、導電性手袋等をして取り扱うこと。

- 弊社出荷梱包単位（外装から取り出された内装及び個装）又は製品単品で取り扱いを行う場合は、接地された導電性のテーブル上で（導電性マットにアースをとったもの等）、アースをした作業者が行うこと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

- 前記のリストストラップ・導電性手袋・テーブル表面及び実装装置類の接地等の静電気帯電防止措置は、常に管理されその機能が確認されていること。

### 2. 温・湿度環境

- 温度：0～40°C、相対湿度：40～85%で保管・輸送及び取り扱いを行うこと。（但し、結露しないこと。）

- 直射日光があたる状態で保管・輸送しないこと。

### 3. 防湿梱包

- 防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装すること。

### 4. 機械的衝撃

- 梱包品（外装、内装、個装）及び製品単品を落下させたり、衝撃を与えないこと。

### 5. 熱衝撃

- はんだ付け時は、最低限260°C以上の高温状態に、10秒以上さらさないこと。（個別推奨条件がある時はそれに従うこと。）

### 6. 汚染

- はんだ付けを損なう、又はアルミ配線腐食の原因となるような汚染物質（硫黄、塩素等ハロゲン）のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。（不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。）

以上