# 多入力ADC回路のセトリング測定とメモリー効果

中村黄三

営業・技術本部 マーケッティング／応用技術統括部

## 概要

マルチチャネル入力のA/D変換システムを試作した際に、チャンネル切り替えにおけるシステム全体のセトリング時間（以下、総合セトリング時間）を、ハードウェアだけ

で定量的に測定したい場合があります。本アプリケーションノートでは、身近にある測定器や材料でこれを実現する方法を紹介します。

## 目次

|                      |    |

|----------------------|----|

| 1.はじめに.....          | 1  |

| 2.測定システムのブロック図 ..... | 2  |

| 3.タイミング.....         | 3  |

| 4.試作したボード.....       | 4  |

| 5.データの前処理.....       | 5  |

| 6.セトリング時間の分析.....    | 7  |

| 7.セトリング時間の比較.....    | 9  |

| 8.メモリー効果の再現実験.....   | 10 |

| 9.まとめ .....          | 11 |

| 10.参考文献.....         | 11 |

## 1. はじめに

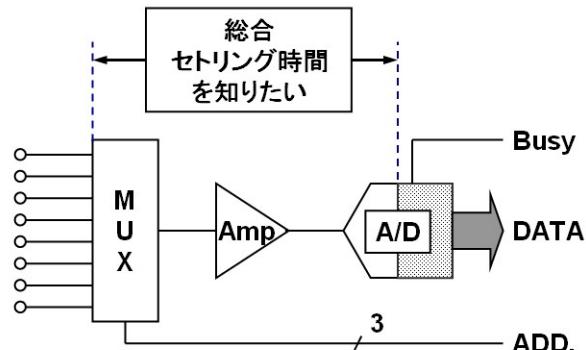

図1のようなマルチチャネル入力のA/D変換システムの重要な要素の一つとして、チャンネル切り替えにおける総合セトリング時間があります。これを正確に把握して適切な待ち（アクイジョン）時間を設定することで、A/D変換データの精度を確保できるからです。

初めてこの手のシステムを設計する場合は、中身であるアナログマルチプレクサ（以下、MUX）、バッファアンプ、A/Dコンバータ（以下、ADC）等のセトリング時間に関するスペックを、それぞれのデータシートから拾い集めて集計しようと試みます。しかし、スペックの値と規定条件が目的のシステムに合致しないことに気づきます。

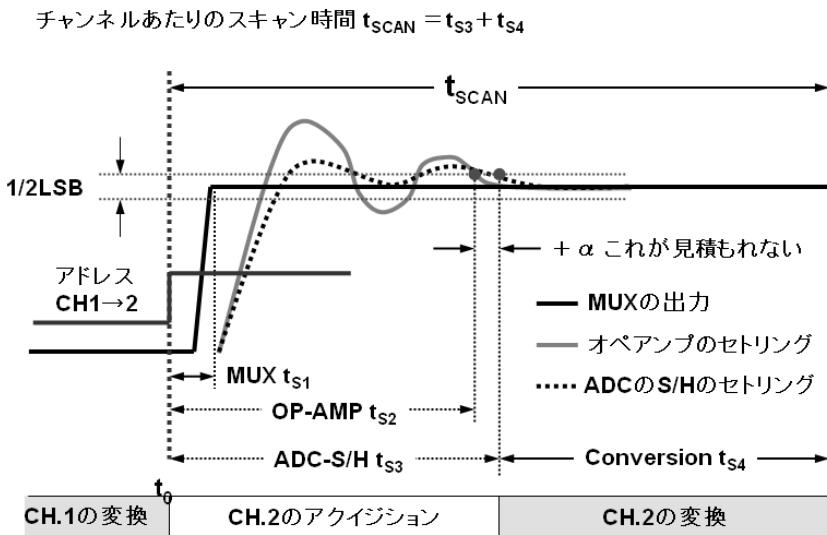

例えば、使用するADCが16ビットの場合では、ADCのフルスケールと1 LSBのパーセンテージは0.0015%となります。図2のように、オペアンプのセトリング時間を1/2 LSB（0.00076%）までの条件で求めようとしても、多分そのような条件でのスペック記載はないでしょう。更には、オペアンプが1/2 LSBまでセトリングしたとして、ADCの

図1 マルチ・チャネル入力のA/D変換システム

サンプル／ホールド（S/H）回路のセトリング時間（図中の $\alpha$ ）も見積もれません。

この資料は日本テキサス・インストゥルメンツ(日本TI)が、お客様がTIおよび日本TI製品を理解するための一助としてお役に立てるよう、作成しております。製品に関する情報は随時更新されますので最新版の情報を取得するようお勧めします。

TIおよび日本TIは、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。また、TI及び日本TIは本ドキュメントに記載された情報により発生した問題や障害等につきましては如何なる責任も負いません。

そこで、実測で把握することになりますが、16ビット以上のADCを使用したシステムでは、実測した総合セッティング時間の再現性の問題にしばしばつきあたります。これは、ADCの1 LSBあたりの電圧の重みが数  $\mu$ V～数十  $\mu$ Vのオーダであるため、外来ノイズとADCを含むアナログ系の内部ノイズにより変換データがばらつくことに起因します。

この解決には、エッジシフト法と呼ばれる測定方法が有効です。詳細は後述しますが、このエッジシフト法の測定システムを、身近にある測定器、タイミングジェネレータ、そして被測定回路で構成して結果を評価することが本アプリケーションノートの目的です。

## 2. 測定システムのブロック図

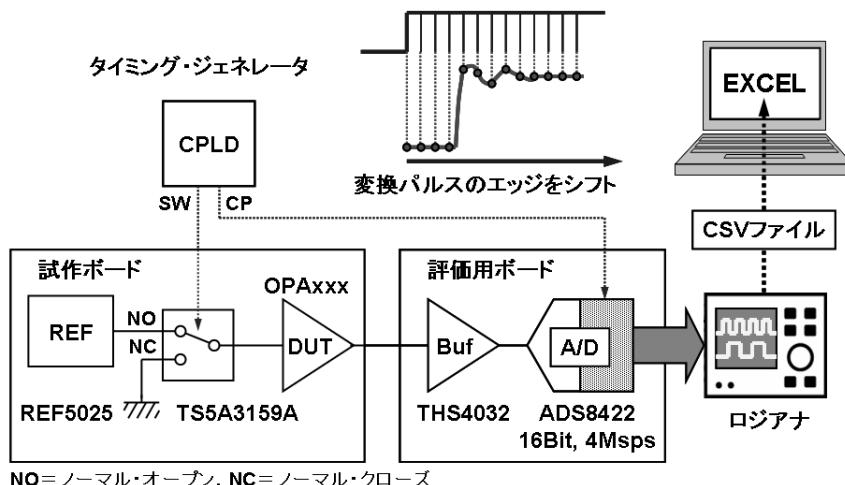

図3にエッジシフト法による測定システムのブロック図とその原理を示します。機能ブロックは大きく分けると、タイミング・ジェネレータ、被試験回路（試作ボード）、ADCボードとなります。

今回は、中速オペアンプのセッティング時間を高精度に測定することも主眼において、ADCには4MspsのADS8422を採用し、ボードはTIが提供しているADS8422の評価用ボード（TIではEVMと呼んでいる）をそのまま使っています。残りは、ロジックアナライザ、そしてパソコン上の表計算ソフトです。

次に信号の流れですが、スイッチ（TS5A3159A）の入力“NO”にREF（基準電圧）を、他方“NC”をグランドに接続しています。

REF電圧は2.5V（REF5025）なので、スイッチを切り替えることで、ベースラインが0Vで振幅2.5Vのパルスが被試験オペアンプ（以下、DUT=Device Under the Test）に与えられます。

DUTの出力（ステップ波形）は、ADS8422のEVMによりデジタルデータに変換され、これをCSVファイルが吐き出せるロジックアナライザでモニタします。ちなみにCSVファイルとは、数値と数値の間をカンマ“,”で区切った

図2 各ステージのセッティング時間

図3 測定システムのブロック図

テキストファイルのことです。このファイルをUSBステッキメモリなどのメディアに吸い取り、パソコン上の表計算ソフトで開いて最終処理（グラフの作成）を行います。

今回は、タイミングパルスをCPLD（FPGAの小規模版）で発生させており、手持ちにプログラマブル・マルチチャネル・タイミング・ジェネレータがある場合は、この部分は不要です。CPLDからは、周期の異なる2系統のタイミングパルスが出力され、スイッチの開閉制御（以下、SW）とADC用の変換パルス（以下、CP）に使用されます。

SWの開閉タイミングを基準にCPの発生タイミングを右方向へ少しづつシフトさせることから、このような測定方法

### 3. タイミング

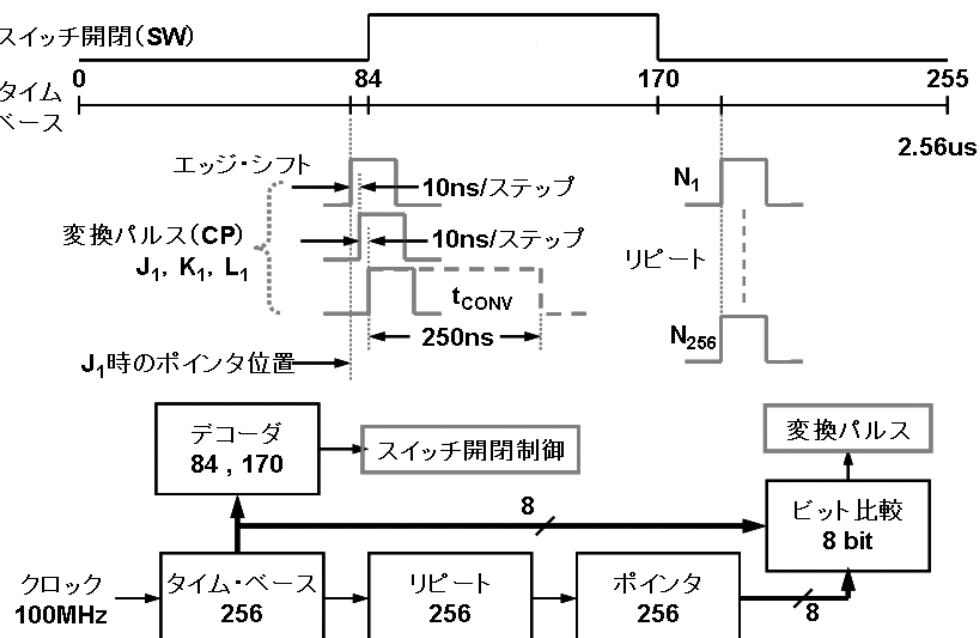

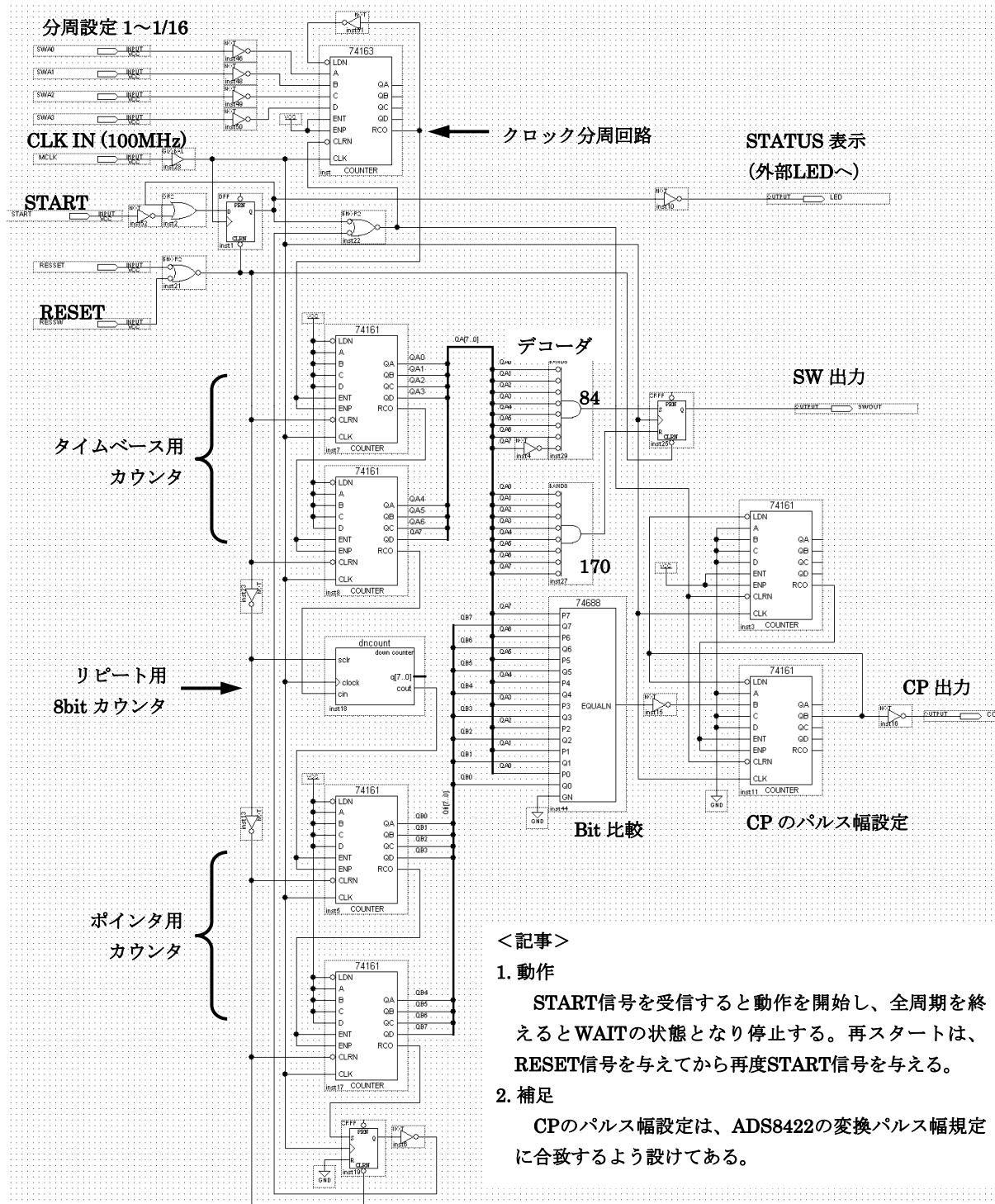

図4はSWの開閉制御とCPのタイミングを示したもので、図中にはCPLD内の論理ブロックも記載されています。

先ず、図の上部のタイムベースですが、同名の8進カウンタの計数値0~255（10進表記）に対応しており、これは1フレームのタイミング・シーケンス全体を管理しています。

SWの開閉は84と170で行われ、CPはタイムベースとポイント（8進カウンタ）の値をビット比較し、等しくなったときに発生します。すなわち、タイムベース上のポイントの位置がCPの発生タイミングとなり、SWのタイミングと合わせて以降はパターンと呼びます。

全てのカウンタの初期値は0なので、最初のパターンにおけるCPの位置はタイムベース上で0になります。その後CPの位置はJ<sub>1</sub>、K<sub>1</sub>、L<sub>1</sub>のように、タイムベース上で1ステップずつエッジがシフトしたパターンで推移します。

こうするとADCは、繰り返しのステップ波形に対して、1ステップずつ時間がずれた時点でのアナログ・レベルを取り込むことになります。

更に、タイムベースとポイントの間にはリピート（8進カウンタ）があるため、1つのパターンはN<sub>1</sub>~N<sub>256</sub>のように

をエッジシフト法と呼びます。

256回繰り返され、同一時点のアナログ・レベルを256回取り込むことになります。

この256（4の4乗）個の変換データの平均値を求める、ランダム・ノイズの振幅は1/16に減り、総合セトリング時間の再現性が4ビット分（16倍）向上します。

データタイムベースは100MHzのクロックで駆動されており、CPのシフト量は最小10ns/ステップです。パターンの総数は、タイムベース上の0~255に対応したCPの位置として256種類（255ステップ）となります。

つまり、1つのパターンを256フレーム分繰り返して256種類のパターンを発生させるので、タイムベース上の255まで到達する時間は2.56μsとなります。

CPLDの内部回路を、次ページの図5に示します。セトリングの遅いDUTを測定できるように、実際にはクロックの分周機能を設けてあります。

分周率は1~1/16まで設定できるので、最も分周した場合は、タイムベース上の255まで到達する時間は40.96μsとなります。

図4 スイッチの開閉 (SW) と変換パルス (CP) のタイミング図

図5 CPLDの内部回路

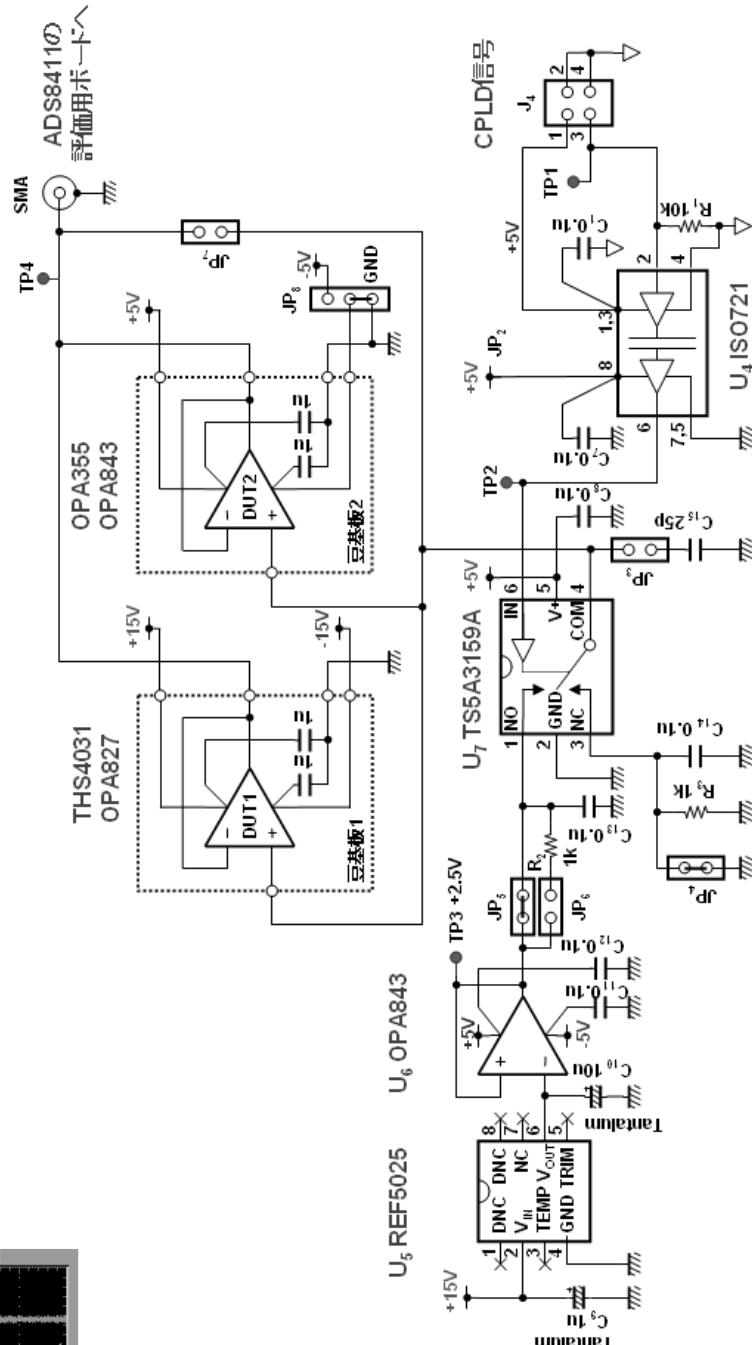

#### 4. 試作したボード

図5はセトリング時間を測定するために試作した回路基板（以下、ヘッダー）で、REF、SWおよび各種のDUTを搭載しています。DUTは独立したピン付の豆基板に実装し、ヘッダー上のソケットへ差し込む方式を探っています。これにより、いろいろなDUTがテストできます。

SWの開閉制御は、CPLDからの制御信号“SW”を、100Mbpsまで通過するU<sub>7</sub>のデジタル絶縁カプラー（ISO721）

で絶縁分離して与えています。これは、ロジック部とアナログのグランドを完全に分離して、アナログ部をクリーンな環境に置くための処置です。ちなみに、この部分に低速なフォトカプラを使用すると、その伝播遅延がボトルネックとなるので要注意です。

図中のJP<sub>3</sub>～JP<sub>6</sub>は、後述するメモリー効果の再現実験を行うためのオプションです。通常のセトリング時間の測定

は、JP<sub>5</sub>=ショート（JP<sub>6</sub>=オープン）、JP<sub>4</sub>=ショート、そしてJP<sub>3</sub>=オープンのジャンパ設定で行います。

DUTへの入力信号は、U<sub>6</sub>（OPA843）でバッファされたU<sub>5</sub>（REF5025）の2.5V出力をSWであるU<sub>7</sub>（TS5A3159）を介して与えます。

TS5A3159AはS P D T（単極双投）のアナログスイッチです。SWのピン3（NC：ノーマルクローズ）をJP<sub>4</sub>経由でグランドへ、ピン1（NO：ノーマルオープン）をREFのバッファアンプU<sub>6</sub>に接続し、これらを切り替えることで、0V～2.5Vのステップ波形をDUTへ供給します。

このSWのターンオンとターンオフ時間はそれぞれ30ns／20nsなので、ターゲットの中速オペアンプ（セトリング時間が1～10μs程度）のテスト用には十分な速度です。

最終的にDUTのステップ出力波形は、SMAコネクタを介してADCボードへ送られます。ちなみにJP<sub>7</sub>は、SWからの出力波形をオシロスコープでモニタするもので、DUTを差し込んだ状態ではオープンにしておきます。

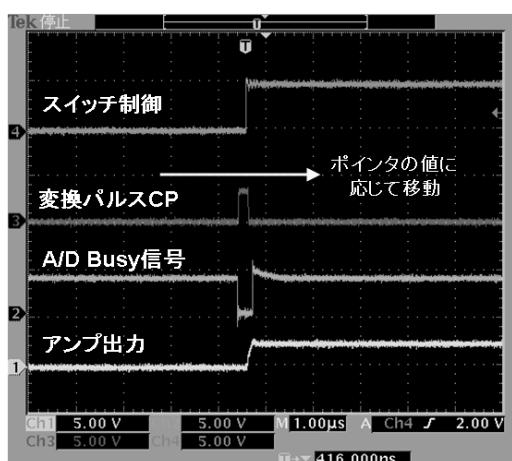

ではここで、オシロスコープで撮った実際の波形を写真1に示しておきます。

写真1 システムの主要な波形

図5 試作したボード

## 5. データの前処理

図6は、今回使用したロジックアナライザの出力データ（以下、生データファイル）をメモ帳で開いたものです。スペースの関係で部分的に抜き取ったものを図としておりタイトルなどのヘッダーも短く編集しています。

データは時系列順に、1つのCPステップに対応する256行のデータが256ステップ分ならんでいます。1行はサンプル番号、16ビットを一つに束ねたBus1（ADCの変換デー

タ)、Bus2は未使用、経過時間データの順に“,”で区切られた各要素で構成されています。これをもとに、Y軸を電圧値、X軸をC Pの位置に対応した時間軸として散布図のグラフを書きます。

このためには、生データの各行から要素を分離して時系列順にソーティングを行い、それぞれ必要な処理をグラフを書く前に行う必要があります。

しかし、これらを表計算ソフト上で手動により集計するにはかなり根気が要ります。そこで、なんらかの

### 手順1：データファイルの読み書きの準備

先ず、生データファイルを読み込む仕組みと、処理したデータを別のファイル（以下、グラフ用ファイル）に書き込む仕組みを作ります。両者はいずれもシーケンシャル・ファイル形式で、データは数字を含めて文字データとして扱います。また、処理過程で使う必要な数のデータバッファも事前に用意します。

### 手順2：全体のシーケンスを決める

タイムベース上の1つのCPの位置に対応した256個のデータの平均値求め、タイムベース0～255までの各平均値のブロックを得るために、 $256 \times 256$ の処理を繰り返します。

ここでは以下の文例で示すように、For～Next文をメインとサブの2重構造でネスティングして、この中で局部的なプロセスを並べた形であります。

```

For H=0 to 255

```

```

Process1

```

```

For I=0 to 255

```

```

Process2

```

```

Process3

```

### 手順2：ヘッダー行の処理

目的の生データファイルを開き、最初のヘッダー行は空読みします。このときついでに、グラフ用ファイルに、自分で分かりやすいヘッダーネームを書き込みます。ここでは...

“SPL #, Time (us), Conv (Hex), Conv (V)”として、要素名と並べる順番を変更しています。Conv (Hex)と名付けた

### 手順3：データ行の分解

ヘッダー行に後続するデータ行を1行ずつ読み込み、“,”を区切りとした5の要素データに分解し“Temp\_Data\$ (4)”などと名付けたバッファに一時保存し

### 手順4：電圧値データの作成

Temp\_Data\$ (4)の16進文字データを10進の数値に変換し、例えば“Dec\_Data”などの変数に...

```

DEC_Data=Val("&H"+Temp_Data$(4))

```

...のように代入します。

これを256個の平均値を求める変数、例えば“Ave”を使って、Ave=Ave+Dec\_Dataのように累計した後、Ave=Ave/256として平均値を変数Aveに再代入します。

方法（例えば、V B Aによるマクロや独立系言語ソフト）でデータの前処理が必要になりますが、ここではB A S I C系言語による処理の要約を解説します。

| Start Part                 | Waveform's Pre-edge Part | Waveform's Post-edge Part | End Part |

|----------------------------|--------------------------|---------------------------|----------|

| 48425,0004,0,123.202012 ms | ス                        |                           |          |

| 48426,0003,0,123.204572 ms | テ                        |                           |          |

| 48427,0003,0,123.207132 ms | ップ                       |                           |          |

| 48428,0003,0,123.209692 ms | 波                        |                           |          |

| 48429,0002,0,123.212262 ms | 形                        |                           |          |

| 48430,FFF3,0,123.214822 ms | の                        |                           |          |

| 48431,FFF4,0,123.217382 ms | 後                        |                           |          |

| 48432,FFF4,0,123.219942 ms | 縁                        |                           |          |

| 48433,FFF5,0,123.222502 ms | 部                        |                           |          |

| 48434,FFF4,0,123.225062 ms | 分                        |                           |          |

| 65526,FFEE,0,166.896754 ms | ス                        |                           |          |

| 65527,FFEE,0,166.899314 ms | テ                        |                           |          |

| 65528,FFEF,0,166.901876 ms | ップ                       |                           |          |

| 65529,FFED,0,166.904436 ms | 波                        |                           |          |

| 65530,FFEE,0,166.906996 ms | 形                        |                           |          |

| 65531,FFEE,0,166.909556 ms | の                        |                           |          |

| 65532,FFEE,0,166.912116 ms | 前                        |                           |          |

| 65533,FFEF,0,166.914676 ms | 縁                        |                           |          |

| 65534,FFEE,0,166.917236 ms | 部                        |                           |          |

| 65535,FFEE,0,166.919796 ms | 分                        |                           |          |

図6 ロジックアナライザの出力データ

Next I

Process4

Next H

Process5

End

最終的なグラフ用ファイルへの書き込みは、Process5あたりでまとめて行えば効率的です。

16進の変換データは参考用で、グラフを書くために必ず必要というものではありません。

ここでは、上記の要素の数に準じてBuffer\$ (4,256)と宣言した、サイズ $4 \times 256$ のデータバッファを手順1で用意しています。

ます。このとき、要素“Bus2”は空読みし、残りをSPL#、Time (us)、Conv (Hex)、Conv (V)の順にTemp\_Data\$ (1)～Temp\_Data\$ (4)に保存します。

ここで気をつける点としては、ADCであるADS8411の変換データのフォーマットはB T Cコードなので、以下の文例で示すようにS B（ストレートバイナリ）形式の重み付けに変換する必要があることです。

```

If DEC_Data>&H7FFF then

DEC_Data=DEC_Data-&H10000

End If

```

以上の処理が終わった後で、Conv (V)に対応するデータバッファ…

```

Buffer$(4,H)=Str$(Ave*Bit_Weight*2)

```

…として保存すれば良いでしょう。

### 手順5：時間軸データの作成

生データファイルから取得した時間データ（以下、時間データ）は、変換データと時間データのペアが時系列順に連なったものなので、そのまま時間軸データとしては使えません。

つまり、タイムベース上で同じCP位置の変換データであっても、生データファイルでは行ごとに時間が加算されたものとなっています。

そこで、256個の平均データごとにタイムベース上の時間と一致した値を、時間データをもとに作成します。

方法として先ず、Forで回すループ変数“*I*”が*I*=0と*I*=255のときの時間データの差分を $255 \times 256$ で割って時間差の変数、例えば“*T\_Delta*”に保存します。

次に、時間軸データの変数、例えば“*T\_Axis*”に“*T\_Delta*”の累積を保存することで時間軸データが得られます。

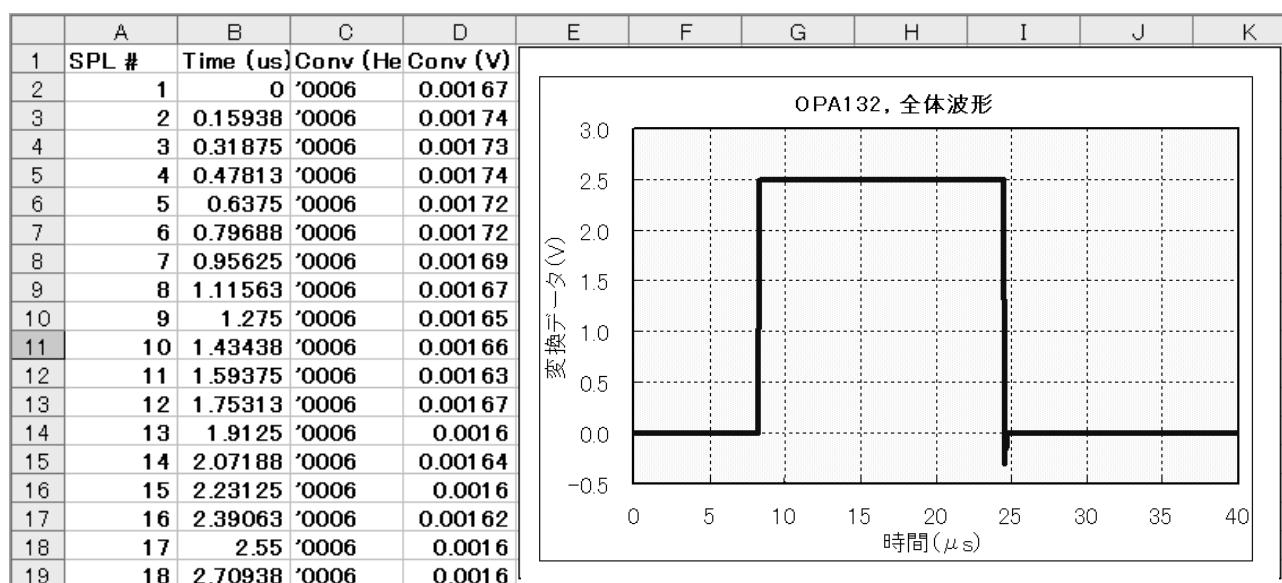

### 手順6：グラフの作成

最後に、作成したグラフ用データを表計算ソフトで読み込みグラフを作成します。使用するデータは、B列（時間）と

ここで変数“*Bit\_Weight*”は、ADCに使用しているREFの電圧4.096Vを7FFF(hex)で割ったものです。

また、後尾の2はADC8411の入力レンジが±REF電圧=2×REFからきています。

この文例を以下に示します。

```

If H=1 then

```

```

T_Axsis=0

```

```

Else

```

```

T_Delta=(T_Buf2-T_Buf1)/(255*256)

```

```

T_Axsis=T_Axsis+T_Delta

```

```

End If

```

ここでT\_Buf2は*I*=255、T\_Buf1は*I*=1のときの時間データです。

但し時間データは、図6を見ると分かるように、数字データの右に“us”や“ms”の単位文字を追加した構造です。

そこで、数字データと単位文字を一度分離して、単位文字を1E-6あるいは1E-3のように浮動小数データに変換して、数字データ+浮動小数データとして再結合の処理をします。

D列（電圧換算の変換データ）です。グラフが完成すると図7のようになります。

図7 表計算ソフトで作成したグラフ

## 6. セトリング時間の分析

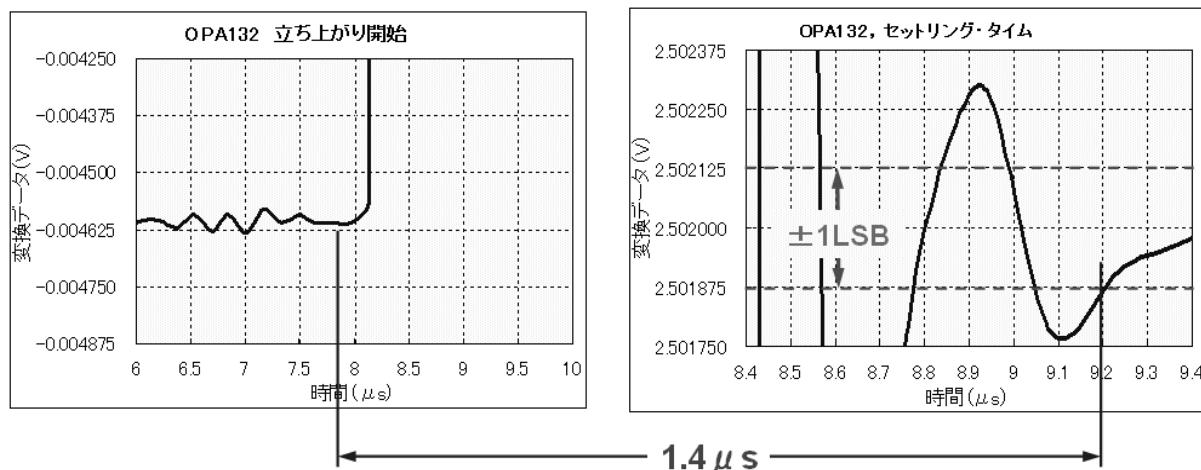

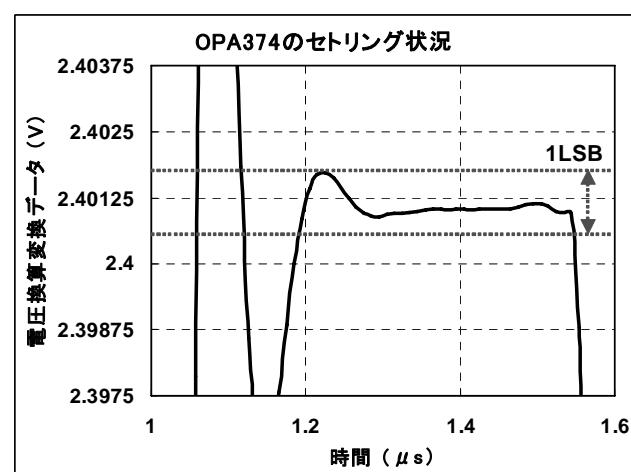

作成したグラフを部分的に拡大して、このシステムのセトリング時間を分析します。使用したADCやSWの応答速度からすると、オペアンプのセトリング時間が支配的なので、ここではDUT（オペアンプ）のセトリング時間としてデータを提示します。

拡大する部分は、ステップ波形の前縁を中心とした前後の部分です。図7のグラフを2回コピー・アンド・ペーストして、各々のグラフのY軸とX軸を調整してズームアップ波形に仕上げます。すると、8ビットADCを使用したデジタル・オシロスコープと比べて、元データは16ビット分解能な

ので、遙かに細かい波形が見えます。これら2つのグラフを1つにまとめて、図8として示します。

また、データの実質分解能は256個のデータの平均値なので4ビット分増大します。前出の図7で見るとY軸がボルトオーダーなので、ステップ波形の上部が平らなように見えますが、拡大するとリンギングがはつきり見えます。

システムの分解能に合わせて、ここでは16ビットの1 LSB (0.0015%)までに安定する時間をセッティング時間とします。

セッティング時間をグラフからの読み取る方法ですが、図の

ようにDUT出力の変化が始まって、その後1 LSBの誤差幅にリンギングが収まるまでの時間をY軸から読み取ります。この結果、このDUT (OPA132) のセッティング時間は  $1.4 \mu\text{s}$  であることが分かります。

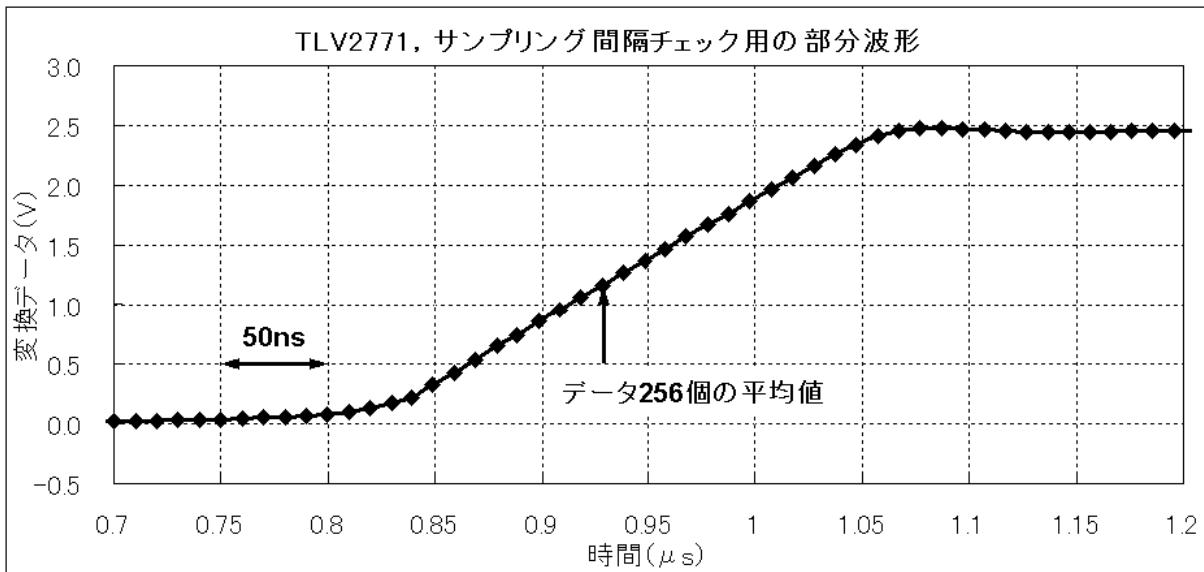

図9のグラフは、作成した本システムの時間軸方向の分解能を検証したときのもので、参考までに掲載します。

使用したDUTは比較的高速なTLV2771で、CPLDを最高速100MHzのクロックで動作させて測定したのですが、プロットポイントが分かるようにマーカを入れてあります。

図8 セッティング時間の読み取り方

図9 作成したシステムの時間分解能検証用グラフ

## 7. セトリング時間の比較

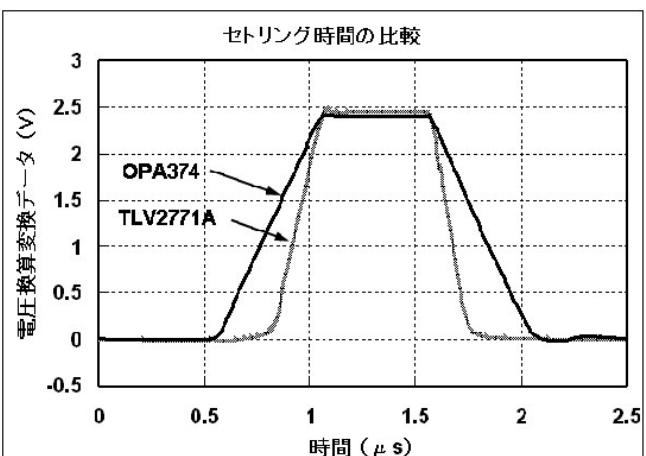

CPLDに与えるクロック周波数を同一条件にすると、異なるアンプのセトリング時間を精密に比較できます。

表1はTLV2771AとOPA374のスルーレートおよびセトリングに関する特性・条件を、それぞれのデータシートから抜き出しました。表1のデータで見る限り、スルーレートについてはTLV2771の方が約2倍高速で、セトリング

時間はOPA374の方がTLV2771Aを基準に約24%高速です。他の特性・条件はほぼ同じと見ることができます。

図10は、これら2つのDUTのステップ応答を1つのグラフに重ね書きしたもので、データシートを見比べただけでは分からぬ情報が明確に見えてきます。

| 型番       | $A_{OL}$ (dB) | GB積(MHz) | ゲイン条件  | $R_L$ (kΩ) | $C_L$ (pF) | スルーレート(V/ $\mu$ s) | セトリング(μs)          |

|----------|---------------|----------|--------|------------|------------|--------------------|--------------------|

| TLV2771A | 113           | 5.1      | $G=-1$ | 10         | 100        | 10.5               | 1.97 0.01%, 2Vステップ |

| OPA374   | 110           | 6.5      | $G=+1$ | 10         | 100        | 5                  | 1.5 0.01%, 2Vステップ  |

表1 データシート上の比較

先ずスルーレートの比較ですが、TLV2771Aの方が明らかに早いことが見て取れます。しかし、応答の開始がOPA374よりも遅いことも判明しました。

このような遅れを、ロジック部品ではプロパーゲーション・ディレイと呼びます。リニア增幅用のアンプであっても、パルス状の波形を信号として扱う回路では、プロパーゲーション・ディレイはパルス幅歪に直結するため歓迎できません。

TLV2771Aの応答グラフを良く見ると、出力の変化が0V近傍( $G=+1$ でテストしているので入力も0V近傍)で遅くなっています。TLV2771Aのデータシートではレール・ツー・レール出力は明記されていますが、同相モード入力範囲の規定が無いので、入力の差動段の飽和が応答遅れの原因と考えられます。

ちなみに、OPA374では入力・出力ともレール・ツー・レールであることが明記されており同相モード入力範囲が規定されています。

従って、単一電源で入出力ともに大振幅を扱う回路か、あるいは、高スルーレートを利用して高周波信号をできるだけ

図10 ステップ応答波形の重ね書き

低歪で増幅する回路かによって、オペアンプの選択を行います。

オールマイティなオペアンプは存在しないので、このような比較・解析は実用上で有益です。

図11 TLV2771Aのステップ応答

図12 OPA374のステップ応答

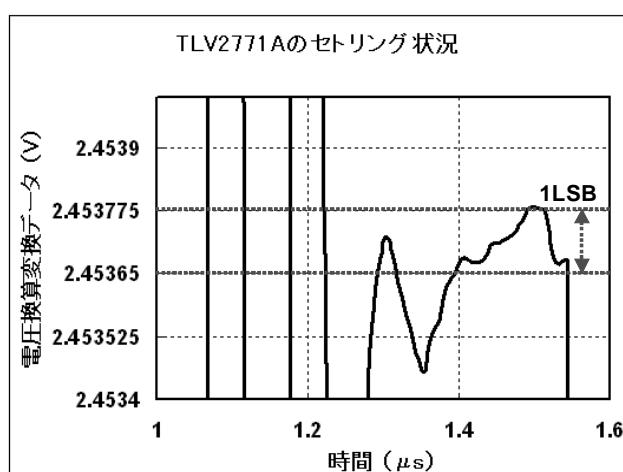

次にセトリングの状況を、図11と図12とで見てみましょう。2つのグラフは、今回使った表計算ソフトのコピー機能を利用したもので、図10のグラフを2回コピーして不要なグラフ要素を削除したものです。

両者のステップ応答の前縁をズームアップして、Y軸の最小目盛を本システムで使用している16ビットADCの1 LSBに相当する電圧 ( $125\mu V$ )まで拡大しています。

ここで2つのグラフを比較すると、TLV2771Aでは大きなリンギングと小さなリンギングを合わせると3つあり、3つめのリンギングの谷から1 LSBの誤差幅への収束に時間を要

## 8. メモリー効果の再現実験

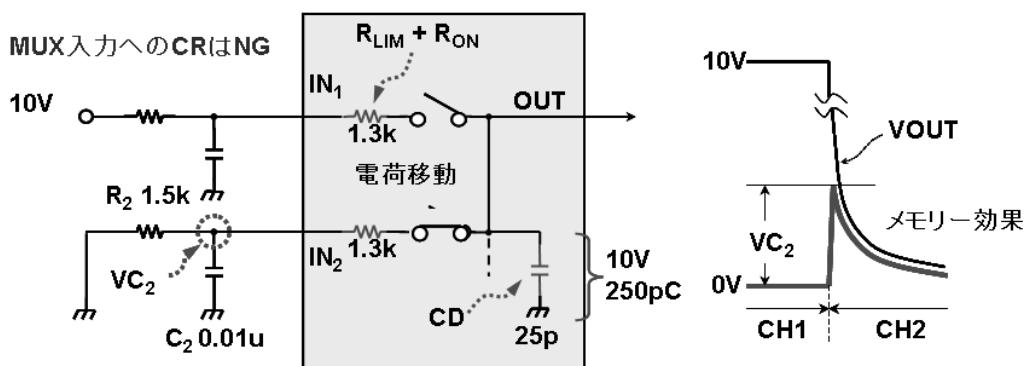

メモリー効果とはMUXのDC的チャンネル間干渉のことです。メモリー効果はMUXの内外に存在する複数のコンデンサ間の電荷移動がその原因で、そのメカニズムを図13により解説します。

同図において、スイッチの切り替えシーケンスが最初はIN<sub>1</sub>（入力は+10V）で、次がIN<sub>2</sub>（入力は0V）であったとします。

先ずIN<sub>1</sub>のスイッチがオンの期間（IN<sub>2</sub>はオフ）に、MUXのOUT側に位置する内部寄生容量“CD (25pF)”が10Vまでチャージアップされ、結果として250pCの電荷が蓄積されます。このときIN<sub>2</sub>の入力に接続されたC<sub>2</sub>には残留電荷はなく、ノード“VC<sub>2</sub>”も0Vが保持されています。

この状態でIN<sub>2</sub>のスイッチがオンの期間（IN<sub>1</sub>はオフとなる）に移行すると、同図の右側の波形で示すように、寄生

しています。一方OPA374では、2つ目のリンギングの頂点が既に1 LSBの誤差幅に収まっていることが分かります。

一般なオペアンプのステップ応答は、自身の開ループゲインが0dBになる周波数において、位相シフトが小さい（=位相余裕が大きい）ほど、リンギングの収束は早くなります。

それに対してGB積が同じなら、スルーレートの方は遅くなります。つまり、オペアンプ自体の設計は、スルーレート優先かセトリング時間優先かで位相余裕を決めるので、高スルーレートなオペアンプはセトリング時間も短いということにはならない点に留意して下さい。

容量“CD”的電荷がIN<sub>2</sub>のC<sub>2</sub>に移動してVC<sub>2</sub>の電圧を押し上げます。ちなみに、このような状況を電荷の再配分と呼びます。

このとき、MUXのOUT側は通常、高インピーダンスなボルテージフォロアによるバッファで受けているので、C<sub>2</sub>に溜まった電荷の放電経路はR<sub>2</sub> (1.5kΩ)だけとなります。放電時間はR<sub>2</sub>とC<sub>2</sub>の積である時定数で決まり、図のようにエクスポーネンシャルな放電カーブを描きます。

C<sub>2</sub>の電荷が完全に放電しない内にA/D変換すると、変換結果は真値となりません。誤差はIN<sub>1</sub>に入力される信号電圧に依存するので、このようなDC的干渉をメモリー効果と呼んでいます。

図13 メモリー効果の発生メカニズム

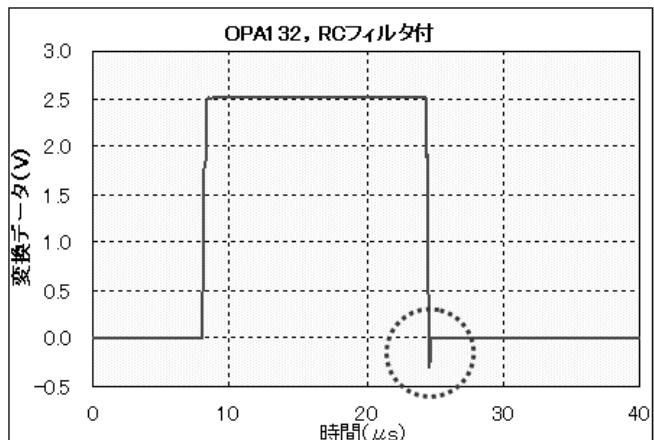

ではここで、前述した第3項“試作したボード”的ジャンパ設定を変更して、RCフィルタ有効にした本システムによる実測波形を図14に示します。

同図のステップ波形後縁において、0V近傍へたち下がる期間（点線で記した丸のあたり）にメモリー効果は発生します。この図では詳細が分からないので、次ページの図15に、丸の部分を拡大したグラフを示します。

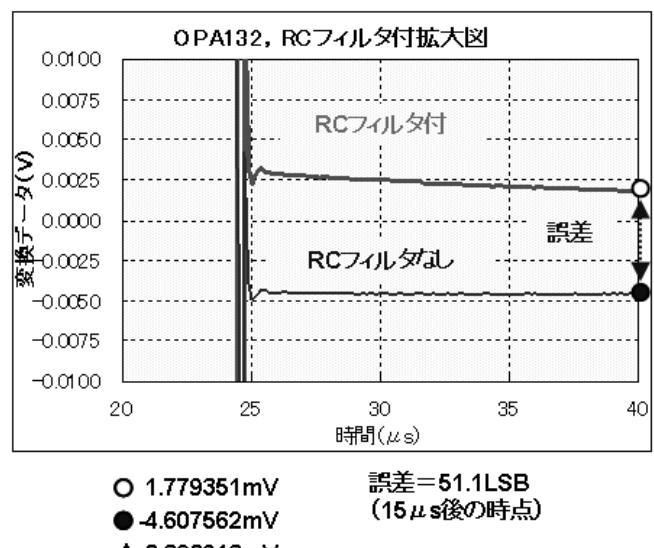

拡大された図15を見ると、重ねがきされた2つのグラフ（R C フィルタ有りと無し）の比較から、メモリー効果が明確に分かります。R C フィルタ無しでは、ただちに $-4.61\text{mV}$ （回路のオフセット分だけ負にずれてい る）で安定していますが、R C フィルタ有りでは、 $25\mu\text{s}$ から $15\mu\text{s}$ 経過後（時間軸 $40\mu\text{s}$ ）において $1.78\text{mV}$ と、RC フィルタ無しに対して $6.39\text{mV}$ ほど高い値となっています。

このシステムで使っている16ビットADCの入力レンジは $\pm 4.098\text{V}$ （スパンで $8.192\text{V}$ ）なので、 $6.39\text{mV}$ のデルタは LSB換算で $51.1\text{LSB}$ と巨大な誤差です。

すなわち、このシステムがチャンネル切り替えから $15\mu\text{s}$ 後にA/D変換を開始するタイミング設計であるとすれば、変換データに $6.39\text{mV}$ もの誤差を含むということです。

このままの回路で図13のC<sub>2</sub>の電荷が放電するまで待つとすれば、いくら高速のADCを使ってもチャンネルのスキャン速度は大幅に制限されることは明白です。

対策としては、R C フィルタとMUX入力の間にボルテージフォロアによるバッファアンプ入れます。R<sub>2</sub> ( $1.5\text{k}\Omega$ ) の代わりに、オペアンプ出力がこの電荷を吸い取るので、MUXの出力はフィルタ無しの場合と同じカーブになります。

もしもMUXの入力チャネルに空きがあれば、そのチャネルを放電経路に使うのも良いでしょう。ここでは、これをIN<sub>3</sub>とします。IN<sub>3</sub>はダイレクトにグランドへ落とし、IN<sub>1</sub> → IN<sub>3</sub> → IN<sub>2</sub>のように、チャネル切り替えのたびに、放電経路用チャネルへの切り替えを間にれます。また、IN<sub>3</sub>の変換結果をMPUなどのレジスタに保存し、MUX以降のオフセット電圧の校正用に使用するのも良いでしょう。

## 9. まとめ

実際の設計現場では、第3項の“試作したボード”は、マルチ・チャネル入力A/D変換システムの試作基板であり、ADC回路を含んだものとなります。従って、エッジシフト法でシステムの評価をするのであれば、CPLDなどで構成するタイミングジェネレータだけ用意すれば済みます。

## 10. 参考文献

- (1) ADS8422 データシート (JAJS188A)

- (2) ADS8422EVM ユーザーズガイド (SLAU192-September 2006)

- (3) その他の関連したデータシート

図14 MUXの入力にR C フィルタを付けた全体波形

図15 ステップ波形の後縁を拡大したグラフ

MUXやオペアンプを含めたセトリング時間を、データシートだけで見積もるのは困難であることは既に解説しました。

必要な回答を得るためにあれこれ悩むより、身近にあるものを利用したエッジシフト法による評価がいかに有用であるかがこれでお分かり頂けたかと思います。

# ご注意

日本テキサス・インスツルメンツ株式会社（以下TIJといいます）及びTexas Instruments Incorporated（TIJの親会社、以下TIJないしTexas Instruments Incorporatedを総称してTIといいます）は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIJとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIJの標準販売契約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIJとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。TI製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI製部品を使用したお客様の製品及びアプリケーションについて想定される危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明しておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならぬ場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、かつその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの默示的保証を無効にし、かつ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任も負いません。

TIは、TIの製品が、安全でないことが致命的となる用途ないしアプリケーション（例えば、生命維持装置のように、TI製品に不良があった場合に、その不良により相当な確率で死傷等の重篤な事故が発生するようなもの）に使用されることを認めておりません。但し、お客様とTIの双方の権限有る役員が書面でそのような使用について明確に合意した場合は除きます。たとえTIがアプリケーションに関連した情報やサポートを提供したとしても、お客様は、そのようなアプリケーションの安全面及び規制面から見た諸問題を解決するために必要とされる専門的知識及び技術を持ち、かつ、お客様の製品について、またTI製品をそのような安全でないことが致命的となる用途に使用することについて、お客様が全ての法的責任、規制を遵守する責任、及び安全に関する要求事項を満足させる責任を負っていることを認め、かつそのことに同意します。さらに、もし万一、TIの製品がそのような安全でないことが致命的となる用途に使用されたことによって損害が発生し、TIないしその代表者がその損害を賠償した場合は、お客様がTIないしその代表者にその全額の補償をするものとします。

TI製品は、軍事的用途もしくは宇宙航空アプリケーションないし軍事的環境、航空宇宙環境にて使用されるようには設計もされていませんし、使用されることを意図されておりません。但し、当該TI製品が、軍需対応グレード品、若しくは「強化プラスティック」製品としてTIが特別に指定した製品である場合は除きます。TIが軍需対応グレード品として指定した製品のみが軍需品の仕様書に合致いたします。お客様は、TIが軍需対応グレード品として指定していない製品を、軍事的用途もしくは軍事的環境下で使用することは、もっぱらお客様の危険負担においてなされるということ、及び、お客様がもっぱら責任をもって、そのような使用に関して必要とされる全ての法的要件及び規制上の要求事項を満足させなければならないことを認め、かつ同意します。

TI製品は、自動車用アプリケーションないし自動車の環境において使用されるようには設計もされていませんし、また使用されることを意図されておりません。但し、TIがISO/TS 16949の要求事項を満たしていると特別に指定したTI製品は除きます。お客様は、お客様が当該TI指定品以外のTI製品を自動車用アプリケーションに使用しても、TIは当該要求事項を満たしていなかったことについて、いかなる責任も負わないことを認め、かつ同意します。

Copyright © 2011, Texas Instruments Incorporated

日本語版 日本テキサス・インスツルメンツ株式会社

## 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。

### 1. 静電気

- 素手で半導体製品単体を触らないこと。どうしても触る必要がある場合は、リストストラップ等で人体からアースをとり、導電性手袋等をして取り扱うこと。

- 弊社出荷梱包単位（外装から取り出された内装及び個装）又は製品単品で取り扱いを行う場合は、接地された導電性のテーブル上で（導電性マットにアースをとったもの等）、アースをした作業者が行うこと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

- 前記のリストストラップ・導電性手袋・テーブル表面及び実装装置類の接地等の静電気帯電防止措置は、常に管理されその機能が確認されていること。

### 2. 溫・湿度環境

- 温度：0～40°C、相対湿度：40～85%で保管・輸送及び取り扱いを行うこと。（但し、結露しないこと。）

- 直射日光があたる状態で保管・輸送しないこと。

### 3. 防湿梱包

- 防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装すること。

### 4. 機械的衝撃

- 梱包品（外装、内装、個装）及び製品単品を落下させたり、衝撃を与えないこと。

### 5. 熱衝撃

- はんだ付け時は、最低限260°C以上の高温状態に、10秒以上さらさないこと。（個別推奨条件がある時はそれに従うこと。）

### 6. 汚染

- はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質（硫黄、塩素等ハロゲン）のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。（不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。）

以上