***AN-558 Introduction to Power MOSFETs and Their Applications***

Literature Number: JAJA244

# パワー MOSFET と アプリケーションの概要

National Semiconductor

Application Note 558

Ralph Locher

1988 年 12 月

## はじめに

今日流通している高耐圧パワー MOSFET は N チャネル・エンハンスマント・モード型の二重拡散型金属酸化シリコン (MOS) 電界効果トランジスタが一般的です。パワー MOSFET を NPN 型バイポーラ接合トランジスタと比べると、電流制御型のバイポーラ・デバイスに対して MOSFET は電圧制御型である点を除き、機能的には同じです。MOSFET は現在、入力インピーダンスが高いことと、少数キャリア蓄積時間効果や熱暴走、二次降伏が問題となるない多数キャリア型のため、かつてないほど普及が進んでいます。

## MOSFET の動作原理

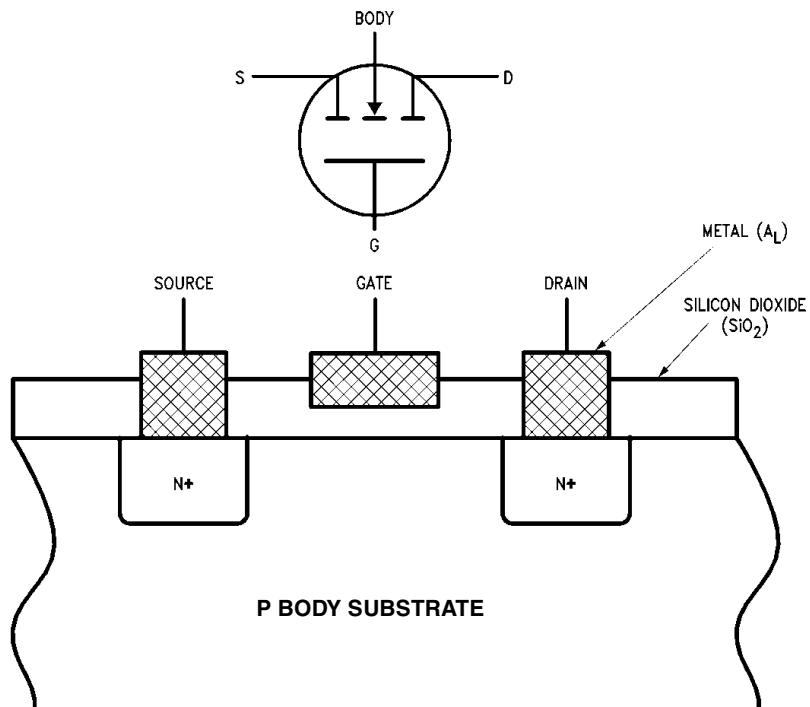

MOSFET の動作を理解するために、まず始めに Figure 1 に示す従来型 MOSFET を取り上げます。

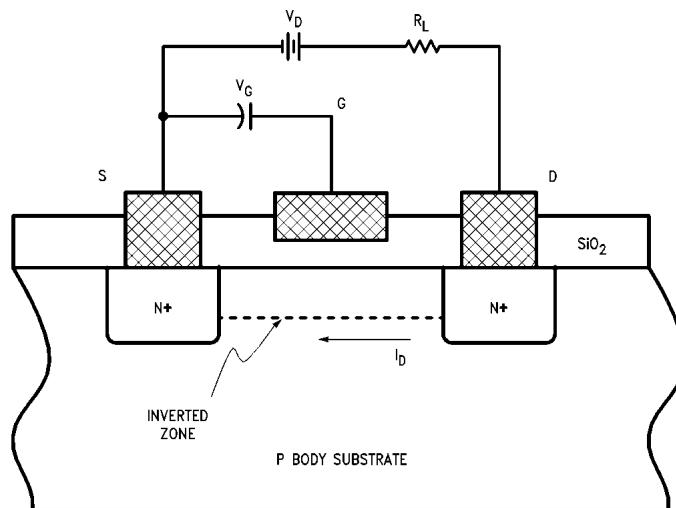

ゲート “ G ” に電気的にバイアスが印加されていない場合、PN 接合で遮断されているため、いずれの方向にもゲート直下を電流が流れることはできません。ゲートに、ソースに対して順方向となるバイアスを Figure 2 のように印加すると、p エピタキシャル層にある自由正孔キャリアはゲート領域から排除され、ソースからドレインへと電子を流すチャネルが形成されます。ゲート・チャネルから正孔が排除されるため、原理的に電子が「多数キャリア」になります。この動作モードは「エンハンスマント」と呼ばれます。エンハンスマント・モードの動作はデバイスが「通常オフ」の状態にあると考えれば理解が容易です。すなわち、ターンオン信号を受けてからまでスイッチが電流を遮断します。エンハンスマント・モードの反対は、デバイスが「通常オン」となるデブリーザン・モードです。

FIGURE 1. Lateral N-Channel MOSFET Cross-Section

ラテラル MOSFET の特長は次のとおりです。

1. ゲート信号の電力要件が小さい。ゲート酸化膜の微小容量の充電以外はゲートには電流が流れません。

2. チャネルが開いた瞬間にドレインからソースへと電子が流れ始めるためスイッチングが高速。チャネルの厚さはゲート電圧に比例し、またゲート電圧がゼロとなった瞬間に閉じるため、バイポーラ・トランジスタで起こるような蓄積時間の影響はありません。

主な欠点は次のとおりです。

1. チャネルが高抵抗である。通常はソースは電気的にサブストレートに接続されています。ゲート・バイアスが印加されていない状態では空乏層はN+ドレインから半球形に似た形状で伸びています。チャネル長  $L$  はデバイスの定格電圧を満たすために必要な最小空乏層幅より短くなっています。

2. チャネルを広くすればチャネル抵抗を小さくできる可能性はあるものの、シリコン上の貴重な面積を占有するためコストに跳ね返ってしまいます。また、ゲート容量が増えるためスイッチング速度が低下します。

そこでパーティカル MOSFET の登場となります。

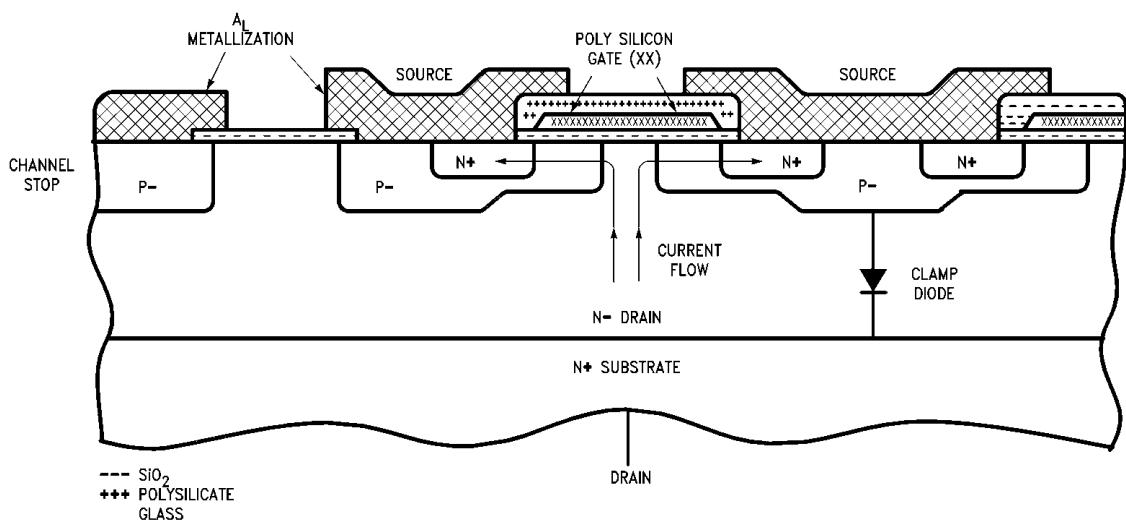

高耐圧 MOSFET (DMOS とも呼ばれる) の構造を Figure 3 に示します。

**FIGURE 2. Lateral MOSFET Transistor Biased for Forward Current Conduction**

**FIGURE 3. Vertical DMOS Cross-Sectional View**

電流経路はラテラル FET 同じ原理でゲート直下の p 層の反転によって形成されます。ソース電流はまずゲート領域の下を流れ、次にドレインを垂直に広がりながら流れています。代表的なパワー MOSFET は数多くの N+ ソースを並列に接続してパワーを確保しています。パーティカル構造はラテラル構造に比べて、ブロッキング電圧が同じならばオン状態抵抗 ( $R_{DS(ON)}$ ) が小さく、またスイッチングが高速です。

パーティカル MOSFET にはさまざまな構造が考えられます。たとえば V 溝型や U 溝型であるとか、あるいはソース形状には正方形、三角形、六角形などがあります。ブロッキング電圧が 300V 超のすべての市販パワー MOSFET は Figure 3 と同様の構造で製造されています。ソース形状は、 $R_{DS(on)}$ 、入力容量、スイッチング時間、トランスクンダクタンスなどの要因で決定します。

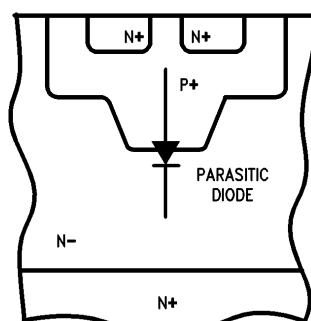

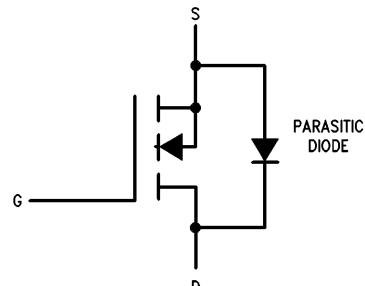

### 寄生ダイオード

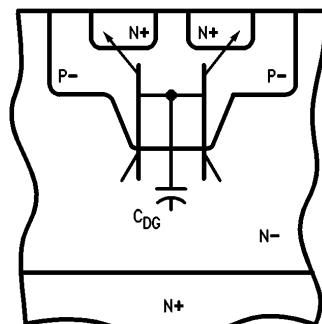

以前の MOSFET は、電圧遷移による電圧降伏に敏感で、またドレン=ソース間電圧が急峻な立ち上がり遷移 ( $dV/dt$ ) を見せた場合にターンオンする性質を持っていました。どちらも致命的な障害に至る現象です。 $dV/dt$  により起こるターンオンは、MOSFET 内に固有に存在する寄生 NPN パラジスタを原因とするもので、回路を Figure 4a に示します。接合容量  $C_{DG}$  の充電電流が、寄生 NPN をターンオンさせるベース電流の役割を果たします。

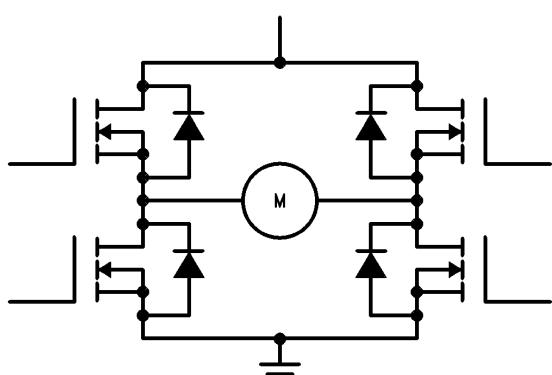

現在の MOSFET は、ソース・メタライゼーションによって N+ ソースから P+ 本体への距離を短くして、寄生 NPN の動作を抑えています。そうすると、MOSFET パラジスタに対してアンチパラレル・ダイオードとなる固有 PN ダイオードが形成されます (Figure 4b 参照)。このダイオードは接合部面積が広いため、定格と熱抵抗はパワー MOSFET 本体と同じです。寄生ダイオードは N- ドレン層での少数キャリアの寿命が長いため、逆方向リカバリ時間が長く逆方向リカバリ電流が大きい性質を持ち、そのため、Figure 5 に示すモーター制御回路のようなさわめて低い周波数のアプリケーションを除いては、このダイオードは利用できません。高周波アプリケーションでは寄生ダイオードのターンオンを抑止するために、寄生ダイオードに対して超高速ダイオードを外付けに並列接続しなければなりません。寄生ダイオードのターンオンを許すと、ダイオードの逆方向リカバリ損失によってデバイスの消費電力が過度に増加し、また大きな逆方向リカバリ電流によって過大な電圧遷移が発生してしまうからです。

### MOSFET の制御

パワー MOSFET の大きな特長の 1 つはスイッチングが高速である点です。ドレン電流は厳密にゲート電圧に比例するので、理論的に完璧なデバイスであれば、キャリアがソースからドレンまで流れる時間の 50ps ~ 200ps でスイッチします。多数キャリア・デバイスの MOSFET が性能でバイポーラ接合パラジスタを上回るもう一つの理由は、ベースでの少数キャリア蓄積時間によるターンオフ遅延が存在しない点です。MOSFET はゲート電圧がスレッシュホールド電圧を下回った瞬間にターンオフを始めます。

a. MOSFET Transistor Construction

Showing Location of the

Parasitic NPN Transistor

b. Parasitic Diode

c. Circuit Symbol

FIGURE 4

FIGURE 5. Full-Wave Motor Control Circuit

## スイッチングの挙動

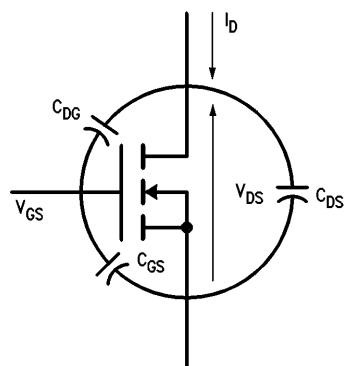

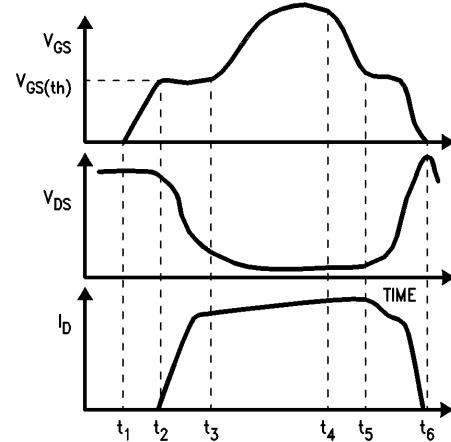

パワー MOSFET の寄生容量を単純化したモデルと抵抗性負荷に対するスイッチング電圧波形を Figure 6 に示します。

ターンオン中には異なる複数の現象が発生します。同じ図を参照しながら進んでください。

時間区間  $t_1 < t < t_2$ :

初期ターンオン遅延時間  $t_{d(on)}$  は  $V_{GS}$  がスレッショルド電圧  $V_{GS(th)}$  に指数関数的に上昇するまでの時間で決まります。Figure 6 から時定数は  $R_S \times C_{GS}$  とわかります。ナショナル セミコンダクター社の IRF330 の代表的なターンオン遅延時間は次のとおりです。

$$t_{d(on)} = R_S \times C_{GS} \times \ln(1 - V_{GS(th)}/V_{PK}) \quad (1)$$

ゲート信号ジェネレータのソース・インピーダンス  $R_S$  を 50 Ω、また  $C_{GS}$  を 600pF と仮定すると、 $t_d$  は 11ns になります。ゲート信号のソース・インピーダンスが  $t_d$  の式に現れるため、スイッチング時間の測定に適用するテスト条件には注意が必要です。

物理的に測定できる入力容量は  $C_{DG}$  と  $C_{GS}$  の並列容量である  $C_{iss}$ だけです。 $C_{GS} \gg C_{DG}$  の場合でも、後者には大きな電圧遷移が印加されるためスイッチング時間に対する影響を無視できません。

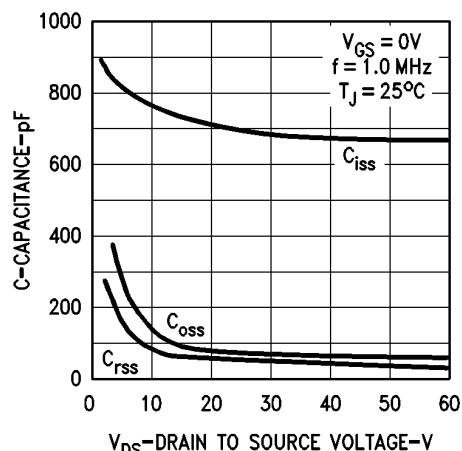

ナショナル セミコンダクター社の IRF330 の  $C_{iss}$ 、 $C_{rss}$ 、 $C_{oss}$  のグラフを Figure 7 に示します。 $C_{DG}$  の充放電は、真空管で最初に発見され、次に説明するスイッチング期間で支配的となるミラー効果に似ています。

時間区間  $t_2 < t < t_3$ :

$V_{GS}$  はスレッショルド電圧に達しているため、MOSFET を流れる負荷電流は増加し、一方で  $V_{DS}$  は低下します。 $C_{DG}$  は放電を始め、同時に  $V_{DG}$  に反比例して容量が大きくなります。すなわち、

$$C_{DG} = C_{DG}(0)/(V_{DG})^n \quad (2)$$

ゲート・ドライバが  $C_{DG}$  の放電に必要な電流を速やかに供給できない限り、電圧低下は遅くなり結果としてターンオン時間が長くなります。

時間区間  $t_3 < t < t_4$ :

MOSFET はオンし、ゲート電圧はオーバードライブ・レベルにまで上昇します。

時間区間  $t_4 < t < t_6$ :

ターンオフはターンオン時の逆です。 $V_{GS}$  がスレッショルド近くまで低下すると  $R_{DS(on)}$  が増加を始めます。 $V_{DS}$  が上昇を始めると  $C_{DG}$  によるミラー効果が再び発生し、 $C_{DG}$  の再充電中に  $V_{CC}$  に達しようとする  $V_{DS}$  の上昇を妨げます。

個別のアプリケーションに適したさまざまなゲート・ドライブ回路は図と合わせて後述します。

a. MOSFET Capacitance Model for Power MOSFET

b. Switching Waveforms for Resistive Load

FIGURE 6

FIGURE 7. Typical Capacitances of the National IRF330

## MOSFET の特性評価

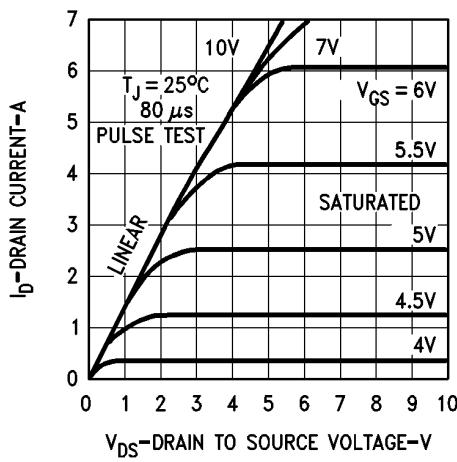

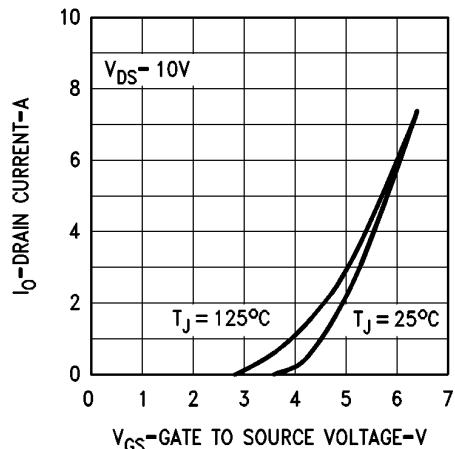

ナショナルセミコンダクター社のIRF330の出力特性( $I_D$ と $V_{DS}$ の関係)をFigure 8、9に示します。

Figure 8 からわかるように動作領域は大きく2つに分かれており、それぞれ「線形(linear)領域」と「飽和(saturated)領域」と呼ばれます。両者の違いを理解するために、MOSFETの実際の電流は、ゲート酸化膜の下に形成されたチャネルを横に流れ、次にドレインに対して垂直に流れることを思い出してください。線形領域とは、MOSFETのチャネル間電圧がキャリアに最大のドリフト速度または最大電流密度を与えるほどには高くない状態です。 $R_{DS(on)}$ は静的で、単純に $V_{DS}/I_D$ で定義され一定です。

$V_{DS}$ が上昇するに連れてキャリアは最大ドリフト速度に達し、電流はそれ以上増加しなくなります。デバイスは電流源のように振る舞うため、出力インピーダンスは高くなります。これを「飽和」領域と呼びます。MOSFETの動作をバイポーラ・トランジスタと比較した場合、バイポーラでの線形領域と飽和領域はMOSFETとちょうど逆になります。 $V_{GS}$ を一定間隔で変化させたときに出力 $I_D$ 曲線の間隔が等しければ、Figure 9の伝達特性は飽和領域でリニアであることを意味します。

## スレッショルド電圧の重要性

スレッショルド電圧 $V_{GS(th)}$ とはドレイン電流が流れ始めるために必要となる最小ゲート電圧です。ゲートをドレインに接続し、250 μAまたは1 μAの規定ドレイン電流に必要なドレイン電圧をTektronix 576カーブ・トレーサを使って記録すれば、 $V_{GS(th)}$ を簡単に測定できます(Figure 9で $V_{GS(th)}$ は3.5Vです)。 $V_{GS(th)}$ が高いと明らかにターンオン遅延時間が長くなますが、一方で低いスレッショルド電圧はパワーMOSFETでは次の理由により望ましくありません。

1.  $V_{GS(th)}$ は-7mV/の負の温度ドリフト係数を持っている。

2. MOSFETのゲート・インピーダンスは高いため、ゲート・ノイズによって誤ったターンオンを生じるおそれがある。

3. 共通して見られる故障モードの一つが電圧によるゲート酸化膜のパンチスルーである。低い $V_{GS(th)}$ を実現するには酸化膜を薄くする必要があり、ゲート酸化膜の電圧定格を低くしてしまう。

FIGURE 8. Output Characteristics

FIGURE 9. Transfer Characteristics

## パワー MOSFET の熱モデル

他のパワー半導体デバイスと同じように MOSFET は接合部温度が上昇した状態で動作します。所望の性能と信頼性を得るために熱の上限を把握しておくことが重要です。データシートには、最大接合部温度( $T_{J(max)}$ )と、動作安全領域、電流定格、電気的特性の各情報が対象となる場合は $T_J$ の関数として、それぞれ記載されています。ただし、すべての動作状態を対象にするのは基本的に不可能なので、仕様範囲内でのデバイスの動作を保証する目的で、接合部に関する程度の計算が必要です。

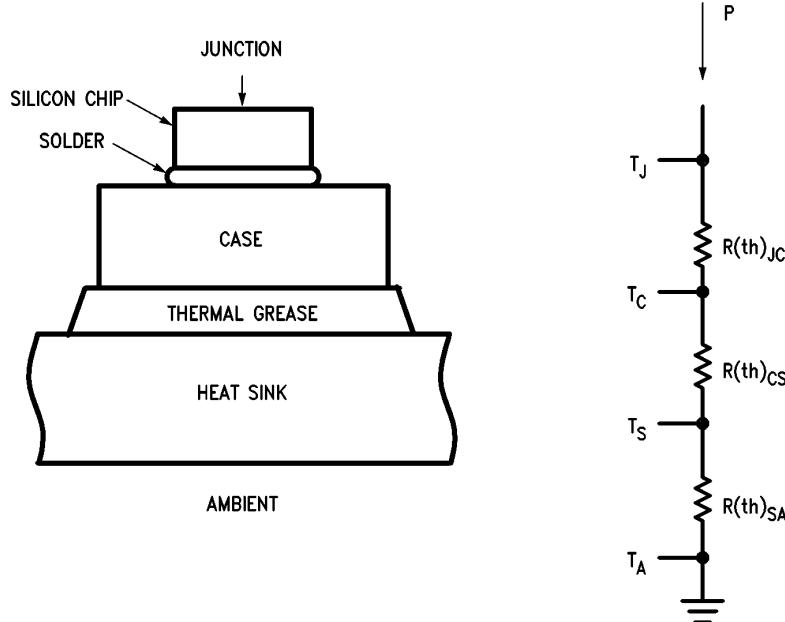

Figure 10に、すべてのパワー半導体に適用される安定状態での基本的な熱モデルと電気的な相似回路を示します。接合部で発生した熱はシリコン・ペレットをとおしてケースまたはタブに伝わり、その後ヒートシンクに伝わっていきます。周囲環境に対する接合部温度の上昇は、熱フローと接合部=周囲熱抵抗に直接比例します。次の式は安定状態でのxとyの2点間の熱抵抗 $R_{(th)JC}$ を定義しています。

$$R_{(th)JC} = (T_y - T_x)/P \quad (3)$$

$T_x$  = x点での平均温度( )

$T_y$  = y点での平均温度( )

P = 単位をワットとする平均熱フロー

熱抵抗を意味あるものとするには2つの温度参照点が指定されなければならない点に注意してください。 $R_{(th)JC}$ の単位は /Wです。

熱モデルは、接合部温度、ケース温度、ヒートシンク温度、周囲温度の参照点の位置を概念的に表わしたものです。これらの温度参照から、次の熱参照が定義されます。

$R_{(th)JC}$ : 接合部=ケース熱抵抗

$R_{(th)CS}$ : ケース=ヒートシンク熱抵抗

$R_{(th)SA}$ : ヒートシンク=周囲熱抵抗

全体の熱抵抗は直列なので、

$$R_{(th)JA} = R_{(th)JC} + R_{(th)CS} + R_{(th)SA}. \quad (4)$$

FIGURE 10. MOSFET Steady State Thermal Resistance Model

デバイスの設計と製造から  $R_{(th)JC}$  が決まるため、 $R_{(th)JC}$  はデバイスごとにばらつきがありますが、 $R_{(th)JC}$  の最大値はメーカーの責任で保証されなければなりません。 $R_{(th)CS}$  を許容可能な最大値に収めるにはユーザーとメーカーの両者の努力が必要ですが、外部ヒートシンクの装着はすべてユーザーの責任で判断されなければなりません。

Figure 10 から  $T_J$  に関して次の式が得られます。

$$T_J = T_A + P \times [R_{(th)JC} + R_{(th)CS} + R_{(th)SA}] \quad (5)$$

この式は見た目こそ単純ですが、MOSFET の消費電力は  $T_J$  に依存するので、実際の計算は簡単ではありません。すなわち、安定性維持に必要となる最大  $R_{(th)SA}$  を求めるには、反復法または図式的解法のいずれかを使用しなければなりません。一方、パルス波形アプリケーションを取り扱う場合には、熱抵抗は変化するものとして考えなければなりません。

パルス波形アプリケーションで接合部のピーク温度を求めるには、安定状態での熱抵抗だけでは十分ではありません。ピーク・パワー値をあてはめると接合部温度を過大に評価することになり、一方で平均パワー値を使用すると、パワー・パルスの終わり時点でのピーク接合部温度を過小評価することになってしまいます。矛盾が生じる理由は、半導体と筐体は熱容量を持っていて、次のパルスの前に熱を蓄え放熱する能力があるためです。

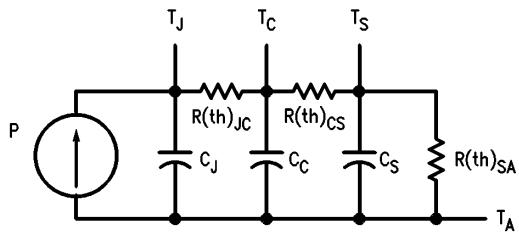

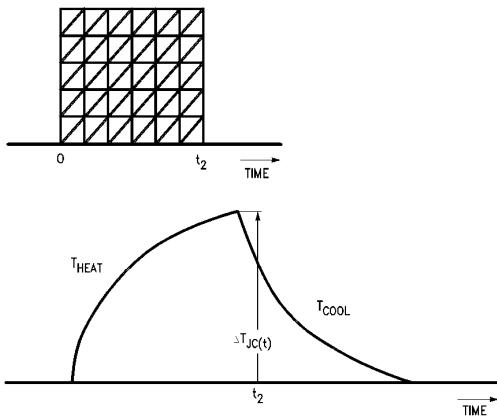

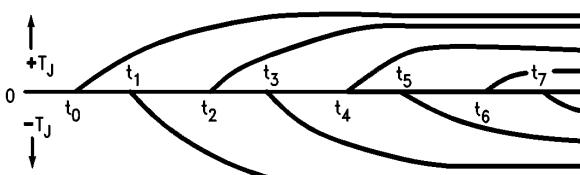

MOSFET の変更した熱モデルを Figure 11 に示します。分布している熱容量を、 $C_J$ ,  $C_C$ ,  $C_S$  と記載した単一のコンデンサとして扱います。この単純化にあたっては、電流は均等にシリコン・チップを流れ、大きな電力損失は接合部のみで発生すると仮定しています。熱を発生させるパワー  $P$  のステップ・パルスが接合部に注入されると、Figure 12a に示すように、 $T_J$  は熱ネットワークの応答で決まる安定状態値に向けて指数関数の上昇率で上昇していきます。パワー入力が時間  $t_2$  で終わると、 $T_J$  は Figure 12a の  $T_{COOL}$  で示される曲線に沿って最初の値まで下がっていきます。つまり、時刻  $t$  における熱抵抗の変化は次のように定義されます。

$$Z_{(th)JC} = \frac{\Delta T_{JC}(t)}{P} \quad (6)$$

熱抵抗の変化曲線は、長期的には安定状態に到達し、短期的な傾きは  $C_J$  に反比例します。この曲線が製品の製造ばらつきから見込まれる  $Z_{(th)JC}$  の最大値を各時間間隔に対して表わすものでない限り、信頼性をもって使用できません。

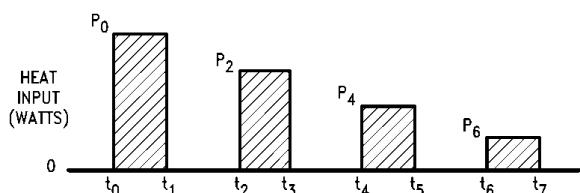

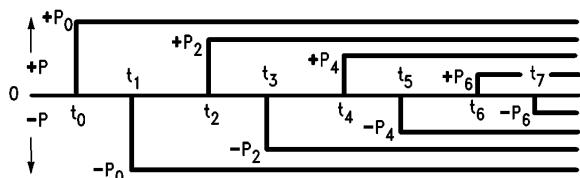

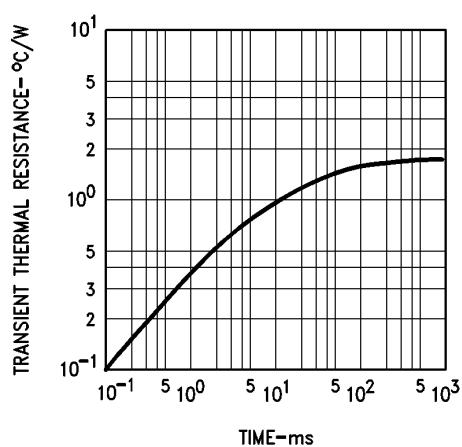

連続したパワー・パルスの応答に対して  $T_J$  を見積もる作業はとても複雑ですが、一方、パワー・パルスの重ね合わせでは、確実な解を得る手段として熱抵抗の変化曲線を使用すれば厳格な算出が可能です。重ね合わせの場合、連続する正と負のステップ関数を重ね合わせたものを入力関数として、ネットワークの応答を調べます。各ステップ関数はゼロから始まり  $T_J$  が計算される時間まで続かなければなりません。たとえば、Figure 13 に熱発生パルス列の一例を示します。

FIGURE 11. Transient Thermal Resistance Model

a. Heat Input

a. Junction Temperature Response to a Step Pulse of Heating Power

b. Equivalent Heat Input by Superposition of Power Pulses

c. Junction Temperature Response to Individual Power Pulses of b

b. Transient Thermal Resistance Curve for National Semiconductor IRF330 MOSFET

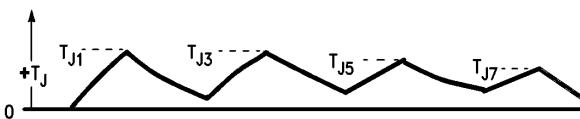

FIGURE 12d. Actual  $T_J$

FIGURE 13. Use of Superposition to Determine Peak  $T_J$

時刻  $t$  での  $T_J$  は次の式で与えられます。

$$T_J(t) = T_J(0) + \sum_{i=0}^n P_i \quad (7)$$

$$[Z_{(th)JC}(t_n - t_i) - Z_{(th)JC}(t_n - t_{i+1})]$$

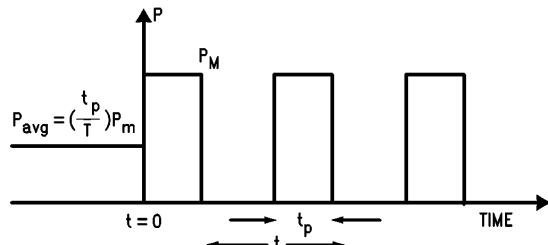

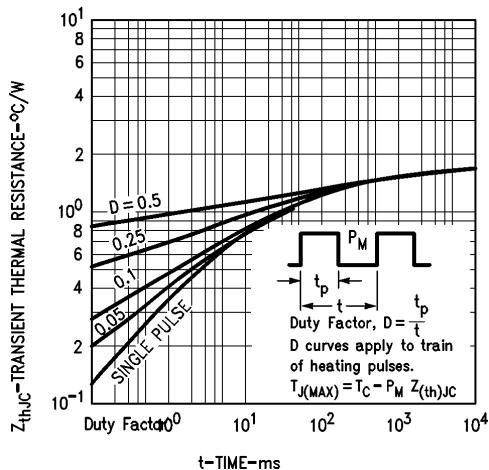

通常の使用条件では、Figure 14 に示すように、振幅が等しい連続したパワー・パルス列を与えた場合の熱均衡状態から接合部のピーク温度を求めます。

この計算をさらに単純化するために、Figure 14b の  $Z_{(th)JC}$  のグラフに示すように、式 (7) の括弧の項をナショナルセミコンダクター社のすべての MOSFET に対してプロットしました。このグラフと次の式から、 $P_M$ 、 $Z_{(th)JC}$ 、 $T_C$  がわかれれば  $T_J$  は簡単に求められます。

$$T_J = T_C + P_M \times Z_{(th)JC} \quad (8)$$

例：25W で幅 200μs の熱発生パルスを 2ms ごとに繰返したパルス列を与えた場合の最大接合部温度を計算します。ケース温度を 95 と仮定します。

デューティ比 = 0.1

Figure 14b から：

$$Z_{(th)JC} = 0.55 \text{ } ^\circ\text{C/W}$$

式 (8) に代入して：

$$T_{J(\text{Max})} = 95 + 25 \times 0.55 = 108.75 \text{ } ^\circ\text{C}$$

a. Train of Power Pulses

b. Normalized  $Z_{(th)JC}$  for National Semiconductor IRF330 for Power Pulses Typified in Figure 14a

FIGURE 14

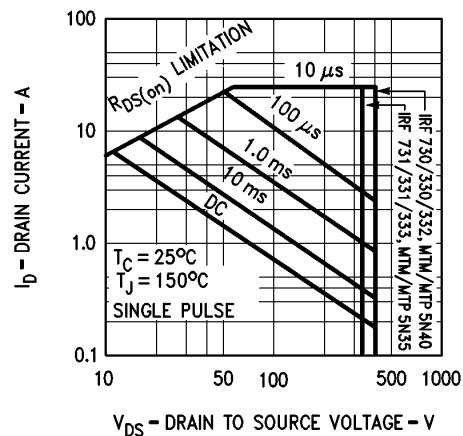

## 安全動作領域

バイポーラ接合トランジスタでは容易に起こり得る順方向または逆方向バイアスの二次降伏はパワー MOSFET では発生しません。二次降伏とはトランジスタのオンとオフに伴なって発生するシリコンの熱的なホットスポットがバイポーラ・トランジスタを破壊する現象です。一方の MOSFET の場合は、0.6% の正の温度ドリフト係数を持つパルク半導体を流れるように、キャリアがデバイスを流れています。仮に電流が局所的な領域に集中しても、パルク・シリコンの温度ドリフト係数は正なので、そのスポットの温度上昇によってスポット抵抗は大きくなります。そのため電圧降下が発生し電流はホット・スポットを迂回して流れるようになります。Figure 15 はナショナルセミコンダクター社の IRF330 デバイスの安全動作領域を表わしています。

安全動作領域の境界は熱のみによって決まり、二次降伏による劣化はありません。この図は MOSFET トランジスタがきわめて丈夫であることを示していますが、過大な電力消費を強いれば熱的に破壊に至るのには変わりありません。

FIGURE 15. Safe Area of Operation of the National Semiconductor IRF330 MOSFET Transistor

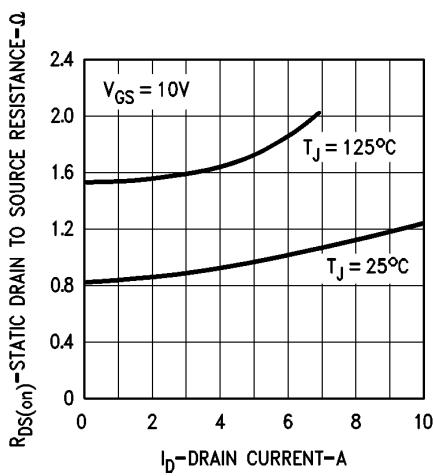

## オン抵抗 $R_{DS(on)}$

パワー MOSFET のオン抵抗は、低周波から中程度の周波数 (200kHz 未満) のアプリケーションで、デバイスが流せる電流量を決める重要なパラメータです。ターンオンによってオン状態となった MOSFET は両端電圧が低下し、 $R_{DS(on)}$  は単純にオン状態電圧をオン状態電流で除した値として表されます。MOSFET にスイッチとして電流が流れる場合、導通損失  $P_C$  は、

$$P_C = I_D^2 R_{DS(on)} \quad (9)$$

$R_{DS(on)}$  を下げるには、Figure 8 に示す線形領域またはオーム領域で動作するように、十分に高いゲート電圧を印加しなければなりません。ナショナルセミコンダクター社のすべての MOSFET は、 $V_{GS} = 10V$  で定格電流が定められています。ナショナルセミコンダクター社の IRF330 の  $R_{DS(on)}$  と  $I_D$  の特性を  $T_J$  に対して示した Figure 16 のグラフでも  $V_{GS} = 10V$  を使用しています。 $R_{DS(on)}$  は  $T_J$  に伴なって増加するため、Figure 16 では室温と高温の両方に對して、電流の関数として  $R_{DS(on)}$  をプロットしています。

FIGURE 16.  $R_{DS(on)}$  of the National Semiconductor IRF330

ドレン電流  $I_D$  が定格電流値を超えるまで増大すると、 $R_{DS(on)}$  が増大する点に注意が必要です。MOSFET は多数キャリア・デバイスであるため、 $R_{DS(on)}$  を構成するドレン領域の N-シリコンのパリク抵抗が温度とともに増大することがその理由です。熱暴走を防ぐにはこの点を考慮に入れる必要があり、MOSFET の並列動作が推奨される理由にもなります。MOSFET 間ではデバイス同士がバランスしていくなくても、電流が多く流れるデバイスは温度が上昇し、結果的にオン電圧が高くなつて電流は他の並列デバイスを迂回するようになるため、電流の集中化は発生しません。

### トランジスタ

MOSFET は電圧制御型のため、真空管の時代には共通的に使用されていたトランジスタ  $g_{fs}$  の項を復活させる必要があります。Figure 8 を参照してください。 $g_{fs}$  は、ドレン電圧を一定としたときに、ドレン電流の変化をゲート電圧の変化で除した値に相当します。数学的には

$$g_{fs} (\text{Siemens}) = \frac{dI_D(\text{A})}{dV_{GS}(\text{V})} \quad (10)$$

トランジスタは動作条件によって変化し、 $V_{GS} < V_{GS(th)}$  でゼロとなり、デバイスが完全に飽和した状態で有限のピーカー値に達します。デバイスはそれ以上の電流を流せないオーム領域では、トランジスタ  $g_{fs}$  を除いて小さくなります。一般に  $g_{fs}$  は、定格電流の 1/2、 $V_{DS} = 20\text{V}$  に対して規定されます。トランジスタ  $g_{fs}$  はリニアアンプの設計には有用ですが、スイッチング電源ではそれほど重要ではありません。

### パワー MOSFET 用のゲート・ドライブ回路

パワー MOSFET のゲート・ドライブ回路はスイッチング動作と消費電力に影響を与えます。そのため、ドライブ回路の種類はアプリケーションから決定します。 $R_{DS(on)}$  で生じるオン状態の電力損失が支配的であれば、高価なドライブ回路を用いても意味はほとんどありません。スレッショルド電圧より数ボルト程度高いゲート=ソース電圧を与えれば、消費電力はゲート・ドライブにはあまり依存せず、スイッチング時間を短くしようと手の込んだドライブ回路を用いても余計な EMI と電圧リンクを増やすだけしかありません。それに対して、200kHz 以上のデバイス・スイッチングのためのドライブ回路は、スイッチング損失が総消費電力のかなりの部分を占めるため消費電力に影響を与えます。

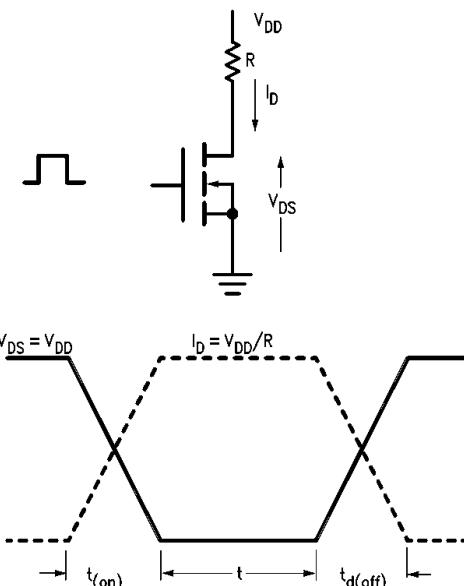

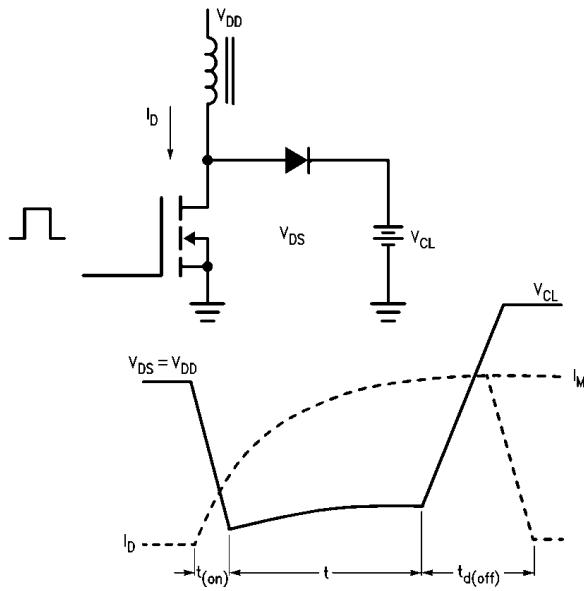

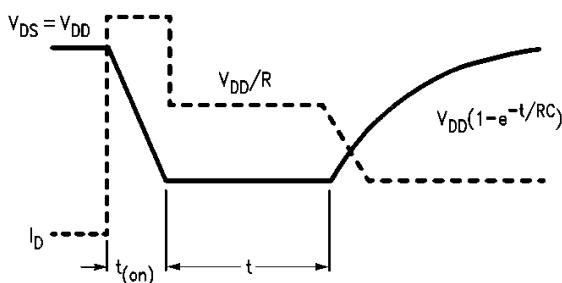

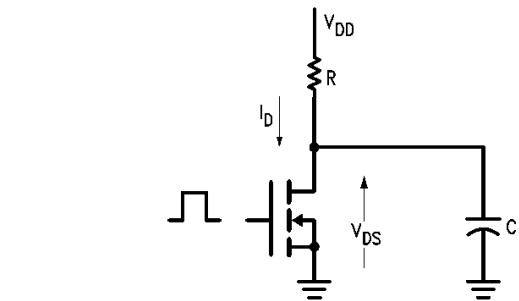

バイポーラ接合トランジスタと比較して MOSFET のスイッチング損失は十分に小さい値ですが、損失項を無視できません。理想的なスイッチング波形をゲート・ドライブに使用した代表的な負荷に対する出力波形の例と消費電力の式を Figure 17 から Figure 19 に示します。

各回路の電力損失は一般的な式を用いて求められます。

$$P_D = \left( \frac{1}{\tau} \int_0^\tau I_D(t) \cdot V_{DS}(t) dt \right) \cdot f_s \quad (11)$$

$f_s$  = スイッチング周波数

図に示す理想的な波形の場合、積分項は三角形の面積計算で近似可能です。

抵抗性負荷 :

$$P_D = \frac{V_{DD}^2}{R} \left[ \frac{t_{on} + t_{off}}{6} + R_{DS(on)} \cdot T \right] \cdot f_s$$

誘導性負荷 :

$$P_D = \frac{V_{CL} I_m t_{off} f_s}{2} + P_C$$

$P_C$  = 時間区間  $T$  での導通損失

容量性負荷 :

$$P_D = \left( \frac{CV_{DD}^2}{2} + \frac{V_{DD}^2 R_{DS(on)}}{R^2} T \right) f_s$$

ゲート損失とプロッキング損失は通常は無視可能です。これらから必要なヒートシンクを求めます。熱安定性を確認するために、制御された温度環境下で最終的なヒートランを行ってください。

FIGURE 17. Resistive Load Switching Waveforms

**FIGURE 18. Clamped Inductive Load Switching Waveforms**

**FIGURE 19. Capacitive Load Switching Waveforms**

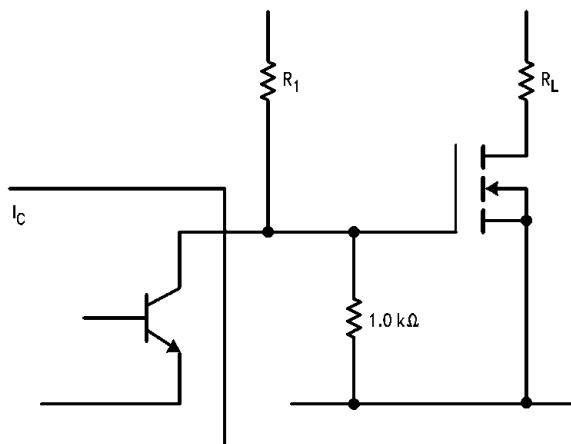

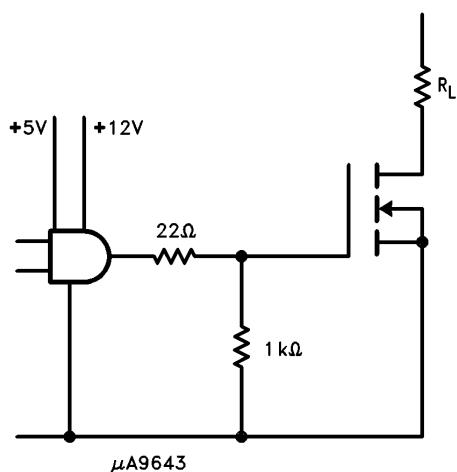

MOSFETは本質的に電圧制御なので、入力容量  $C_{iss}$  の充電電流以外のゲート電流は必要ありません。10Aのバイポーラ・トランジスタでは飽和状態を維持するために2Aのベース電流を必要としますが、パワー MOSFET の場合は、Figure 20 に示すように、CMOS またはオープンコレクタ TTL ロジック回路から直接ゲートをドライブできます。

ドライブ IC の電流シンク定格から最小値が決まる抵抗  $R_1$  の選択によって、MOSFET のターンオン時間が決まります。ゲートに印加する電圧は MOSFET のスレッショルド電圧 5V を上回る電圧でなければならぬため、オープンコレクタ TTL バッファを使用しなければなりません。15V 電源で動作する CMOS デバイスであれば、パワー MOSFET を直接ドライブできます。

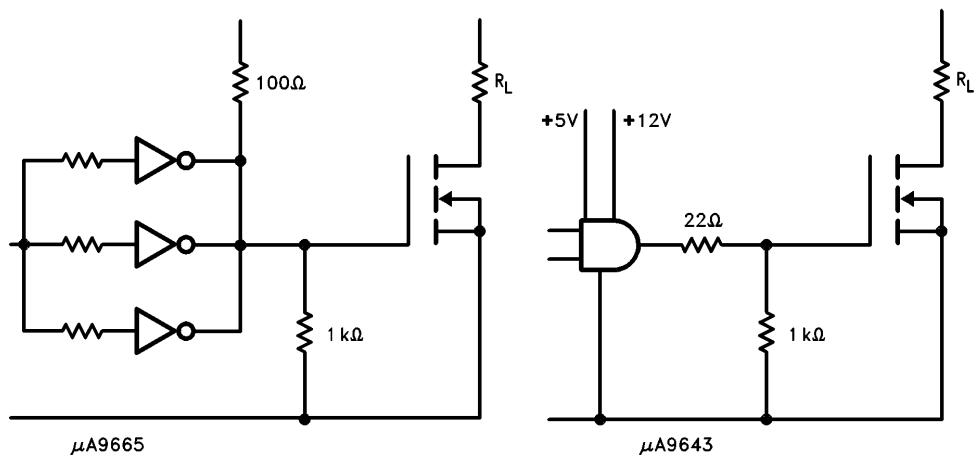

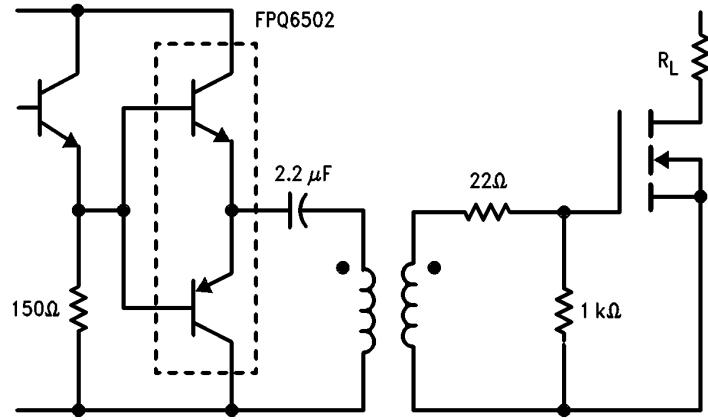

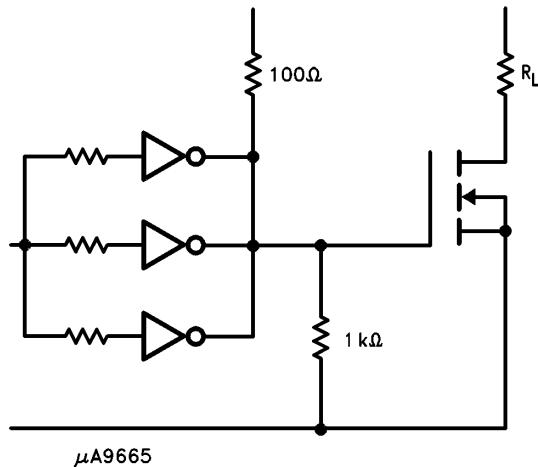

Figure 21 に示すように、他のアプリケーションを目的としたインタフェース IC もパワー MOSFET のドライブに利用可能です。

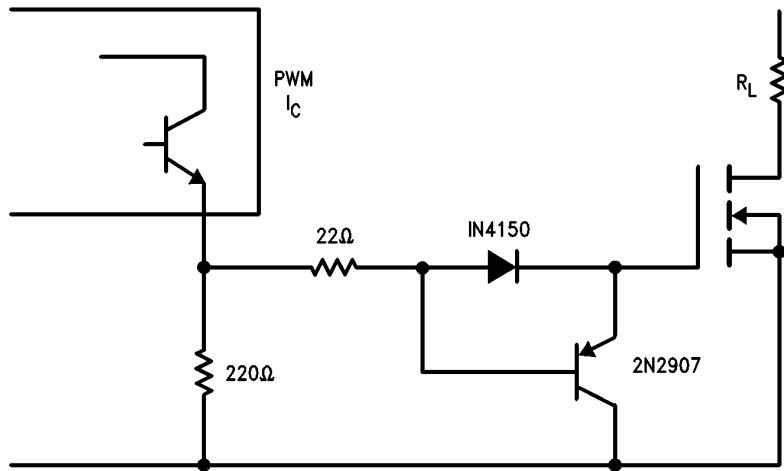

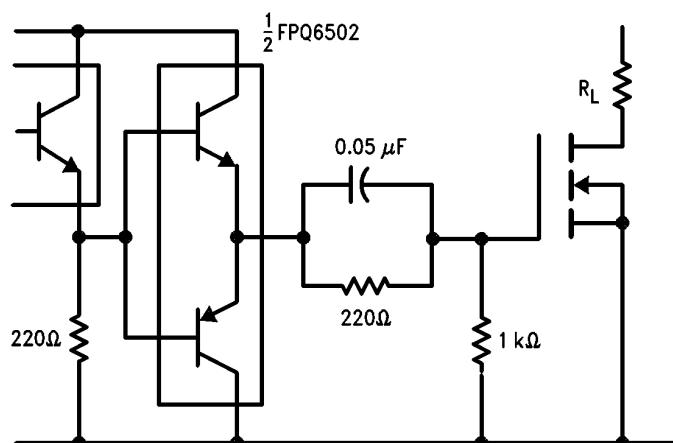

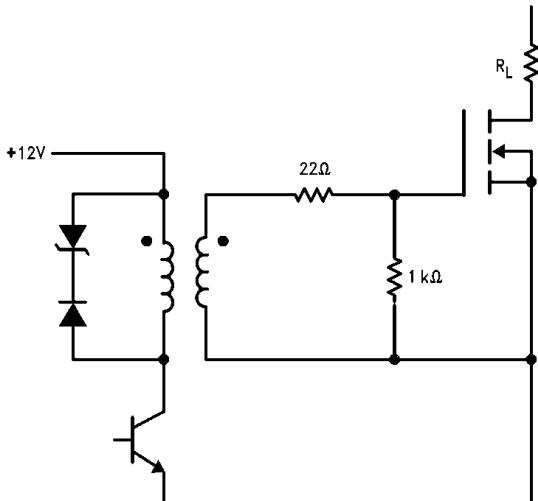

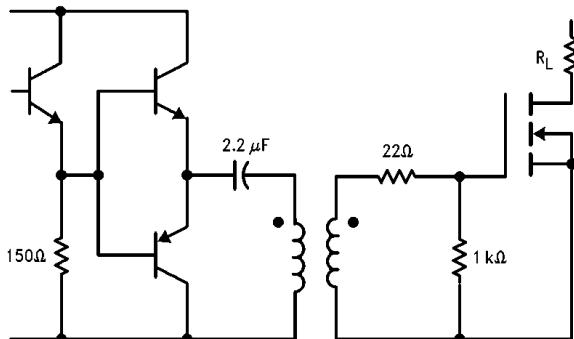

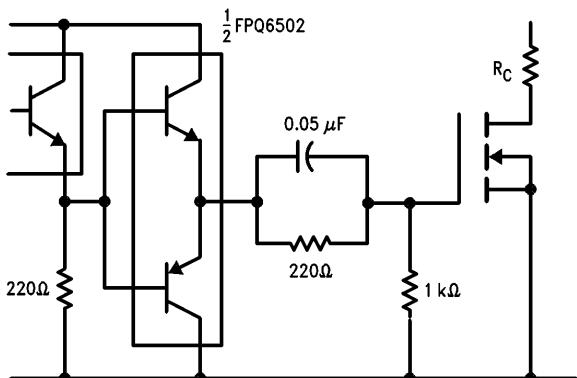

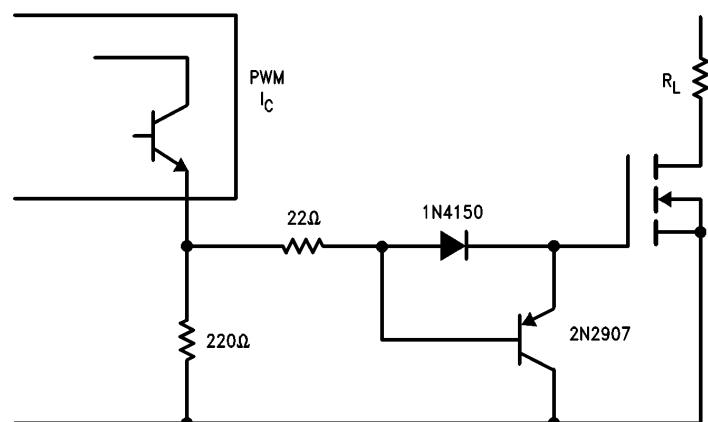

スイッチングが頻繁に発生する電源アプリケーションでは、NPN トランジスタ出力段を備えたパルス幅変調 IC を採用します。MOSFET をオンにすべきときに出力トランジスタがオンになるため、オープンコレクタ TTL デバイスで使用したようなドライブ回路は使用できません。Figure 22、23 に PWM IC を使ったドライブ回路の代表例を示します。

**FIGURE 20. Open Collector TTL Drive Circuit**

FIGURE 21. Interface ICs Used to Drive Power MOSFETs

FIGURE 22. Circuit for PWM IC Driving MOSFET.

The PNP Transistor Speeds Up Turn-Off

FIGURE 23. Emitter Follower with Speed-Up Capacitor

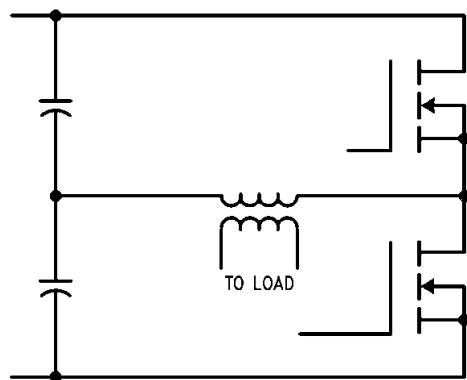

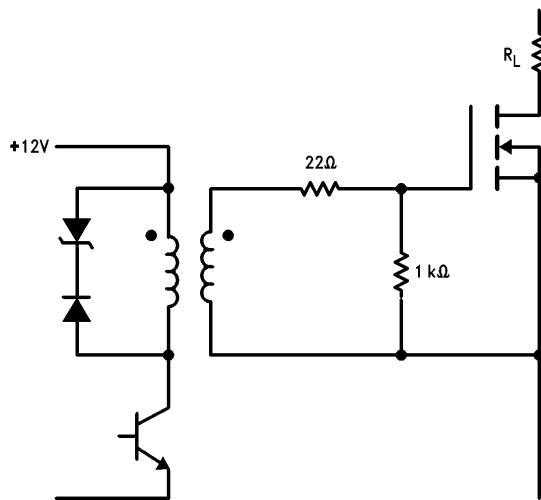

絶縁：商用電源を直接平滑化するオフライン型のスイッチング電源では、低  $R_{DS(on)}$  の安価な高耐圧デバイスがないため、パワー MOSFET をハーフブリッジ構成にして使用するのが一般的です。

パワー・デバイスの一端が正電源レールに接続されるため、ドライブ回路も同様に高電位にフローティングしなければなりません。ドライブ回路の最も汎用的なカップリング方法はパルス・トランスを使用することです。パルス・トランスは、MOSFET の故障から保護するために、高耐圧で動作する MOSFET と論理回路とを絶縁するためにも使われます。

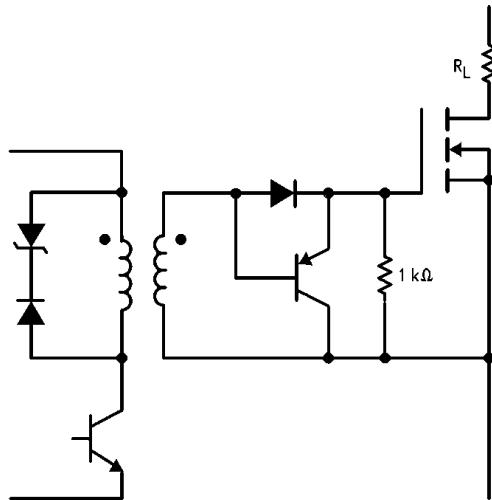

Figure 25 に示すツエナー・ダイオードはパルス・トランスを速やかにリセットする目的で設けられています。12V ツエナー・ダイオードを使用すると、デューティ・サイクルは 50% に達する場合があります。ターンオフの性能を高めるには PNP トランジスタを Figure 26 のように追加します。

Figure 27 は、パルス・トランスにコンデンサを直列に挿入してターンオフ時の MOSFET に逆バイアスを与える回路方式です。コンデンサは DC バイアスを遮断するため、パルス・トランスを飽和させない働きも担っています。

FIGURE 24. Half-Bridge Configuration

FIGURE 25. Simple Pulse Transformer Drive Circuit. The Transistor May Be a Part of a PWM IC if Applicable.

FIGURE 26. Improved Performance at Turn-Off with a Transistor

FIGURE 27. Emitter Follower Driver with Speed-Up Capacitor

オプト・アイソレータもパワー MOSFET のドライブに使用可能ですが、スイッチング時間が長いため低周波アプリケーション以外には適しません。

#### ドライブ回路の選択

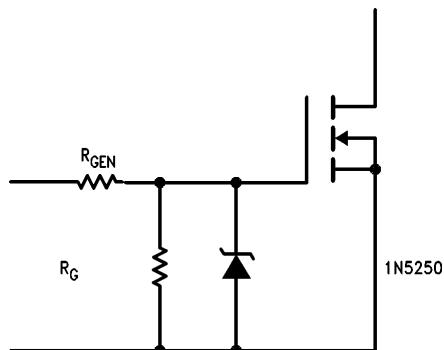

図示した回路はいずれもパワー MOSFET のターンオンとターンオフが可能です。ドライブ回路のタイプはアプリケーションに依存します。ドライブ回路の電流シンクと電流ソース能力からパワー・デバイスのスイッチング時間とスイッチング損失が決まります。法則としてターンオンとターンオフ時のゲート電流が大きいとスイッチング損失は小さくなります。しかし高速なドライブ回路はゲートヒドレイン回路にリンクを生む可能性があります。ターンオン時にゲート回路にリンクが発生すると、最大  $V_{GS}$  定格を超えた電圧遷移が生じるおそれがあり、ゲート酸化膜の破壊につながります。このような問題を防ぐには、適切な電圧定格のツエナー・ダイオードを Figure 28 のように追加します。なお、ツエナー・ダイオードはデバイスのできる限り近くに配置してください。

ターンオフ時もゲート電圧にリンクが発生する可能性があり、スレッショルド電圧まで達した場合はデバイスは短時間にわたってターンオンしてしまいます。ドレイン回路にリンクが発生すればドレイン=ソース電圧が最大定格電圧を超える可能性もあります。保護用の RC スナバー回路またはツエナー・ダイオードを追加して、ドレイン電圧を安全なレベルに維持してください。

Figure 29 ~ Figure 34 にはそれぞれのドライブ回路の代表的なターンオンとターンオフ時間が併記されています。テスト回路の条件は次のとおりです。

デバイス：ナショナル セミコンダクター社 IRF450、 $V_{DD} = 200V$ 、負荷 = 33 抵抗

**FIGURE 28. Zener Diode to Prevent Excessive Gate-Source Voltages**

ドライブ回路のターンオン / ターンオフ時間

Note : 電圧立ち下がり時間 = 17ns、電圧立ち上がり時間 = 20ns

**FIGURE 29. Emitter Follower PWM**

Note : 電圧立ち下がり時間 = 50ns、電圧立ち上がり時間 = 112ns

**FIGURE 30. Simple Pulse Transformer**

Note : 電圧立ち下がり時間 = 50ns、電圧立ち上がり時間 = 16ns

**FIGURE 31. Pulse Width Modulator**

Note : 電圧立ち下がり時間 = 63ns、電圧立ち上がり時間 = 74ns

**FIGURE 32. Pulse Transformer with Speed-Up Capacitor**

Note : 電圧立ち下がり時間 = 200ns、電圧立ち上がり時間 = 84ns

**FIGURE 33. Interface Drive**

Note : 電圧立ち下がり時間 = 70ns、電圧立ち上がり時間 = 30ns

**FIGURE 34. Interface Drive**

## 生命維持装置への使用について

弊社の製品はナショナルセミコンダクター社の書面による許可なくしては、生命維持用の装置またはシステム内の重要な部品として使用することはできません。

1. 生命維持用の装置またはシステムとは (a) 体内に外科的に使用されることを意図されたもの、または (b) 生命を維持あるいは支持するものをいい、ラベルにより表示される使用法に従って適切に使用された場合に、この不具合が使用者に身体的障害を与えると予想されるものをいいます。

2. 重要な部品とは、生命維持にかかわる装置またはシステム内のすべての部品をいい、これの不具合が生命維持用の装置またはシステムの不具合の原因となりそれらの安全性や機能に影響を及ぼすことが予想されるものをいいます。

## ナショナルセミコンダクタージャパン株式会社

本社 / 〒135-0042 東京都江東区木場 2-17-16 TEL.(03)5639-7300

技術資料（日本語／英語）はホームページより入手可能です。

<http://www.national.com/jpn/>

その他のお問い合わせはフリーダイヤルをご利用下さい。

0120-666-116

# ご注意

日本テキサス・インスツルメンツ株式会社（以下TIJといいます）及びTexas Instruments Incorporated（TIJの親会社、以下TIJないしTexas Instruments Incorporatedを総称してTIといいます）は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIJとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIJの標準販売契約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIJとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。TI製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI製部品を使用したお客様の製品及びアプリケーションについて想定される危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明しておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならぬ場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、かつその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの默示的保証を無効にし、かつ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任も負いません。

TIは、TIの製品が、安全でないことが致命的となる用途ないしアプリケーション（例えば、生命維持装置のように、TI製品に不良があった場合に、その不良により相当な確率で死傷等の重篤な事故が発生するようなもの）に使用されることを認めておりません。但し、お客様とTIの双方の権限有る役員が書面でそのような使用について明確に合意した場合は除きます。たとえTIがアプリケーションに関連した情報やサポートを提供したとしても、お客様は、そのようなアプリケーションの安全面及び規制面から見た諸問題を解決するために必要とされる専門的知識及び技術を持ち、かつ、お客様の製品について、またTI製品をそのような安全でないことが致命的となる用途に使用することについて、お客様が全ての法的責任、規制を遵守する責任、及び安全に関する要求事項を満足させる責任を負っていることを認め、かつそのことに同意します。さらに、もし万一、TIの製品がそのような安全でないことが致命的となる用途に使用されたことによって損害が発生し、TIないしその代表者がその損害を賠償した場合は、お客様がTIないしその代表者にその全額の補償をするものとします。

TI製品は、軍事的用途もしくは宇宙航空アプリケーションないし軍事的環境、航空宇宙環境にて使用されるようには設計もされていませんし、使用されることを意図されておりません。但し、当該TI製品が、軍需対応グレード品、若しくは「強化プラスティック」製品としてTIが特別に指定した製品である場合は除きます。TIが軍需対応グレード品として指定した製品のみが軍需品の仕様書に合致いたします。お客様は、TIが軍需対応グレード品として指定していない製品を、軍事的用途もしくは軍事的環境下で使用することは、もっぱらお客様の危険負担においてなされるということ、及び、お客様がもっぱら責任をもって、そのような使用に関して必要とされる全ての法的要件及び規制上の要求事項を満足させなければならないことを認め、かつ同意します。

TI製品は、自動車用アプリケーションないし自動車の環境において使用されるようには設計もされていませんし、また使用されることを意図されておりません。但し、TIがISO/TS 16949の要求事項を満たしていると特別に指定したTI製品は除きます。お客様は、お客様が当該TI指定品以外のTI製品を自動車用アプリケーションに使用しても、TIは当該要求事項を満たしていなかったことについて、いかなる責任も負わないことを認め、かつ同意します。

Copyright © 2011, Texas Instruments Incorporated

日本語版 日本テキサス・インスツルメンツ株式会社

## 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。

### 1. 静電気

- 素手で半導体製品単体を触らないこと。どうしても触る必要がある場合は、リストストラップ等で人体からアースをとり、導電性手袋等をして取り扱うこと。

- 弊社出荷梱包単位（外装から取り出された内装及び個装）又は製品単品で取り扱いを行う場合は、接地された導電性のテーブル上で（導電性マットにアースをとったもの等）、アースをした作業者が行うこと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

- 前記のリストストラップ・導電性手袋・テーブル表面及び実装装置類の接地等の静電気帯電防止措置は、常に管理されその機能が確認されていること。

### 2. 溫・湿度環境

- 温度：0～40°C、相対湿度：40～85%で保管・輸送及び取り扱いを行うこと。（但し、結露しないこと。）

- 直射日光があたる状態で保管・輸送しないこと。

### 3. 防湿梱包

- 防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装すること。

### 4. 機械的衝撃

- 梱包品（外装、内装、個装）及び製品単品を落下させたり、衝撃を与えないこと。

### 5. 熱衝撃

- はんだ付け時は、最低限260°C以上の高温状態に、10秒以上さらさないこと。（個別推奨条件がある時はそれに従うこと。）

### 6. 汚染

- はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質（硫黄、塩素等ハロゲン）のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。（不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。）

以上