# LM27262

***Application Note 1380 Design Challenges in 5 Gbps Copper Backplanes***

Literature Number: JAJA287

# 5Gbps に対応したカッパー・バックプレーンの設計課題と対策

## 1.0 はじめに

ギガビット Ethernet がデスクトップ PC にも普及し、同時に、ポート密度の向上とポートあたりコストの削減が強く求められている現在、ネットワーク・スイッチやルーターの設計ではライン・カードやスイッチ・ファブリック・カードのトラフィックが走るバックプレーンの容量向上が急務になっています。すべてを新規に設計すれば高速なバックプレーンの実現は難しくありませんが、開発コストの増加によって高価格となつたシステムはエンドユーザーに歓迎されません。新規設計を行うのではなく、既存シャシーを流用してスイッチ・ファブリック・カードを高速なタイプにアップグレードしておき、エンドユーザーは必要に応じてライン・カードを新しいものにアップグレードする方法もあります。この場合、コスト効率は高くなりますが、低速システムを前提に設計された旧世代のバックプレーンを高速なバックプレーンにアップグレードすることは、技術的には大きな課題です。

現在のほとんどのバックプレーンは 600Mbps から 2.5Gbps の速度で動作します。5Gbps 以上を実現しようとすると、シグナル・インテグリティ、システム設計、さらには IC 設計の各分野でさまざまな課題が浮かび上がります。2.5Gbps と 5Gbps との違いは、データレートだけで見れば 2 倍ですが、伝送に伴なう問題の複雑さは指数関数的に増大します。そこでこのアプリケーション・ノートでは、5Gbps に対応するバックプレーンの設計課題と、その課題に対する解決策の一端を紹介します。

## 2.0 バックプレーン設計のハードル

高速バックプレーンには伝送上のハードルが数多く存在します。たとえば、伝送損失、バックプレーンに使われるめっきスルーホールから生まれる寄生容量、隣接チャネルからのクロストークなどがハードルの一例です。これらハードルと、伝送に対するそれらの影響を、以下のセクションで説明します。

### 2.1 伝送損失

バックプレーンの伝送損失は、2.5Gbps 以下であれば、表皮損失や誘電体損失などプリント回路板の特性に依存します。一方 2.5Gbps を超えると、バックプレーンの伝送損失は、信頼性の観点から用いられることが多い高密度プレス・フィット型に代表されるバックプレーン・コネクタに大きく影響を受けます。高密度コネクタはピルピッチが狭いため、利用できるルーティング領域の幅は通常 5 ~ 8mil に制限され、伝送損失をさらに増やす要因となります。

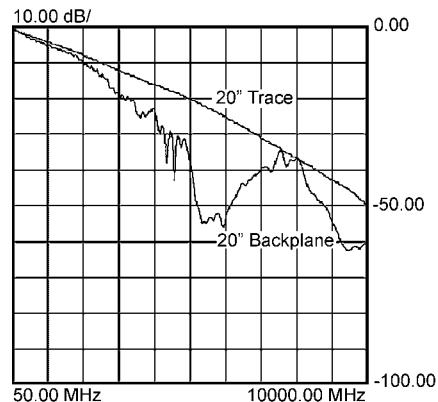

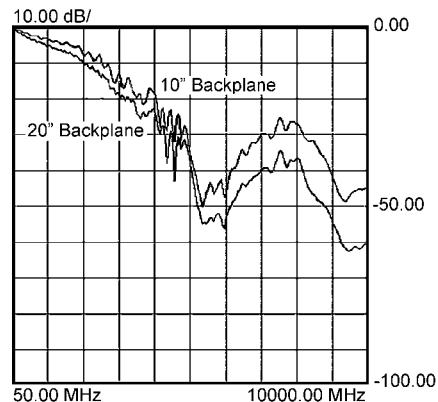

Figure 1 に、トレース幅 6mil で 50cm (20 インチ) の FR4 ボード・トレースと、トレース幅 8mil で 50cm (20 インチ) のバックプレーンの伝送損失を示します。また Figure 2 に、50cm (20 インチ) バックプレーンと 25cm (10 インチ) バックプレーンを比較したバックプレーン・コネクタの影響を示します。

National Semiconductor

Application Note 1380

TK Chin

2005 年 4 月

2

FIGURE 1. Comparing a 20-inch FR4 Board Trace versus a 20-inch Backplane

FIGURE 2. Comparing a 20-inch versus a 10-inch FR4 Backplane

5Gbps に対応したカッパー・バックプレーンの設計課題と対策

AN-1380

## 2.0 バックプレーン設計のハードル (つづき)

### 2.2 コネクタ・ピアとピア・スタブ

これまでの実績や信頼性が高いといった理由で、現在のほとんどのコネクタはプレスフィット技術で作られています。プレスフィット・コネクタは比較的大きなめつきスリーホール・ピアを必要とします。めつきスリーホールは、多層バックプレーンの電源層やグラウンド層と作用して、大きな寄生容量を形成します。バックプレーンの代表的な厚みはおよそ 200mil で、ライン・カードの厚みはおよそ 100mil です。差動信号がルーティングされている内層までの距離がスタブとして現れます。信号層がボード表面に近ければスタブ距離は長くなり、結果として寄生容量は増え、ボード裏面に近い信号層より先伝送損失が大きくなります。

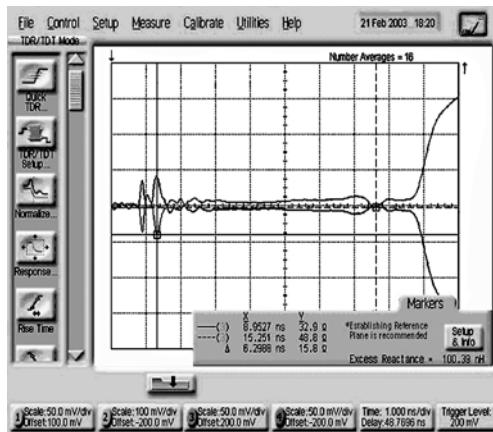

Figure 3 はバックプレーンのインピーダンス・プロファイルを表した差動 TDR 波形です。波形左側の 2 か所の落ち込みが、ライン・カード・コネクタのピアとバックプレーンのピアによるインピーダンス低下を示します。このインピーダンス低下は、コネクタに 0.5pF ~ 1.5pF の寄生容量が付加されている状態に相当します。

FIGURE 3. Impedance Profile of a Backplane

### 2.3 シンボル間干渉 (ISI)

伝送損失によってシリアル・ビットストリーム上には大量の確定ジッタが現れます。帯域が十分ではない伝送チャネルはローパス・フィルタとして振る舞い、データ・ビットストリームの高周波成分に対して減衰歪みを招きます。Figure 4 に K28.5 ビットストリームに与える伝送損失の影響を示します。この波形から、5 ビットの連続する 1 で構成される周波数の低いビットストリームのほうが、周波数の高い 1 ビット・パルスよりも、振幅が大きいことがあります。データ遷移時点のレベルによってその後の波形振幅が異なり、その結果、波形のレベルは公称位置から変動します。データ遷移

位置に依存したこのような変動はデータ・パターンに応じたジッタを招きます。この種のジッタを一般にデータ依存ジッタと呼びます。

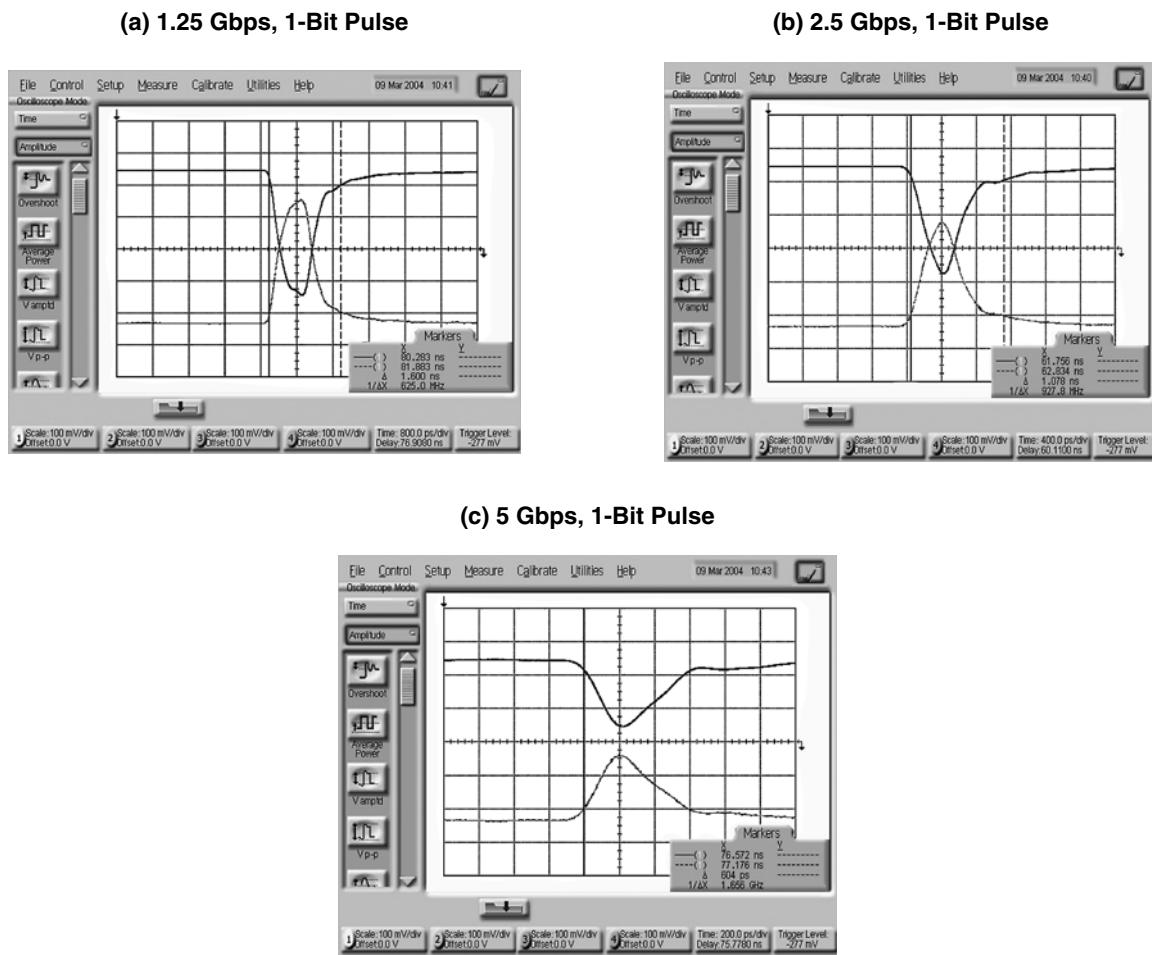

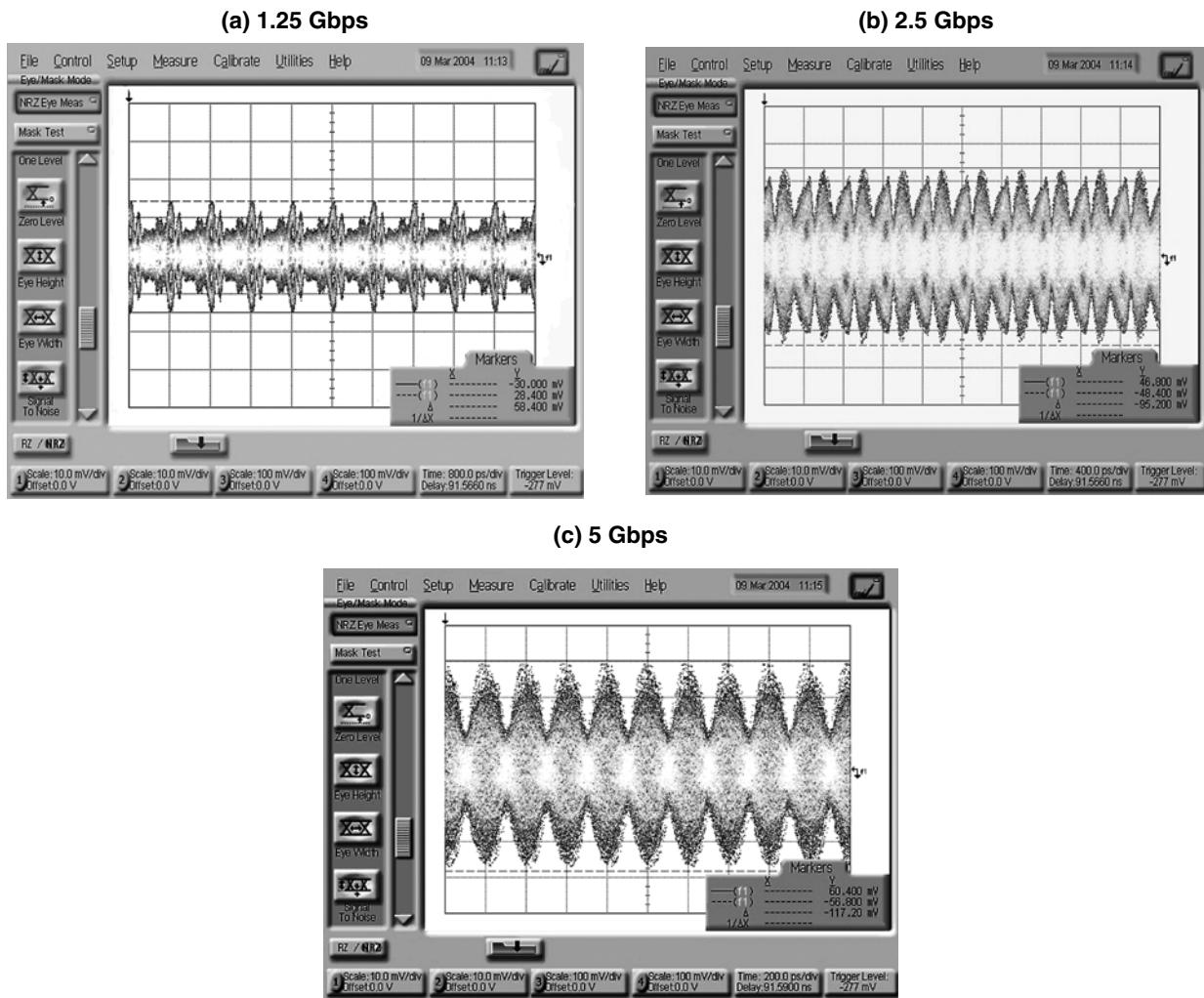

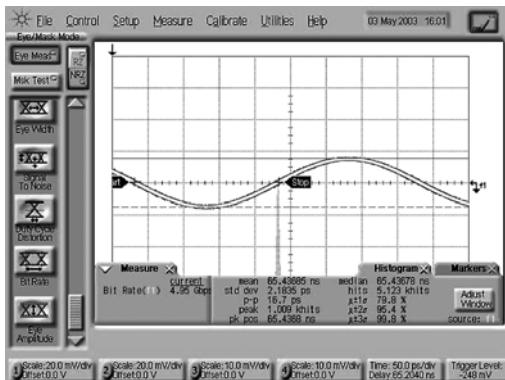

Figure 5 に、バックプレーン遠端における 1 ビット・パルス波形を、1.25Gbps、2.5Gbps、5Gbps のそれぞれで示します。転送レートが高いほど、また伝送損失が大きいほど、パルス振幅は減少します。5Gbps では差動の相補信号は互いに交差することなく、結果としてアイ・オープニングが存在しません。バックプレーンによってエッジレートが鈍化するため、パルス幅も 1 ビット周期より先長くなっています。次のシンボルにまで延びているひとつ前の伝送の残存電圧が、次のデータ遷移に影響を与えています。

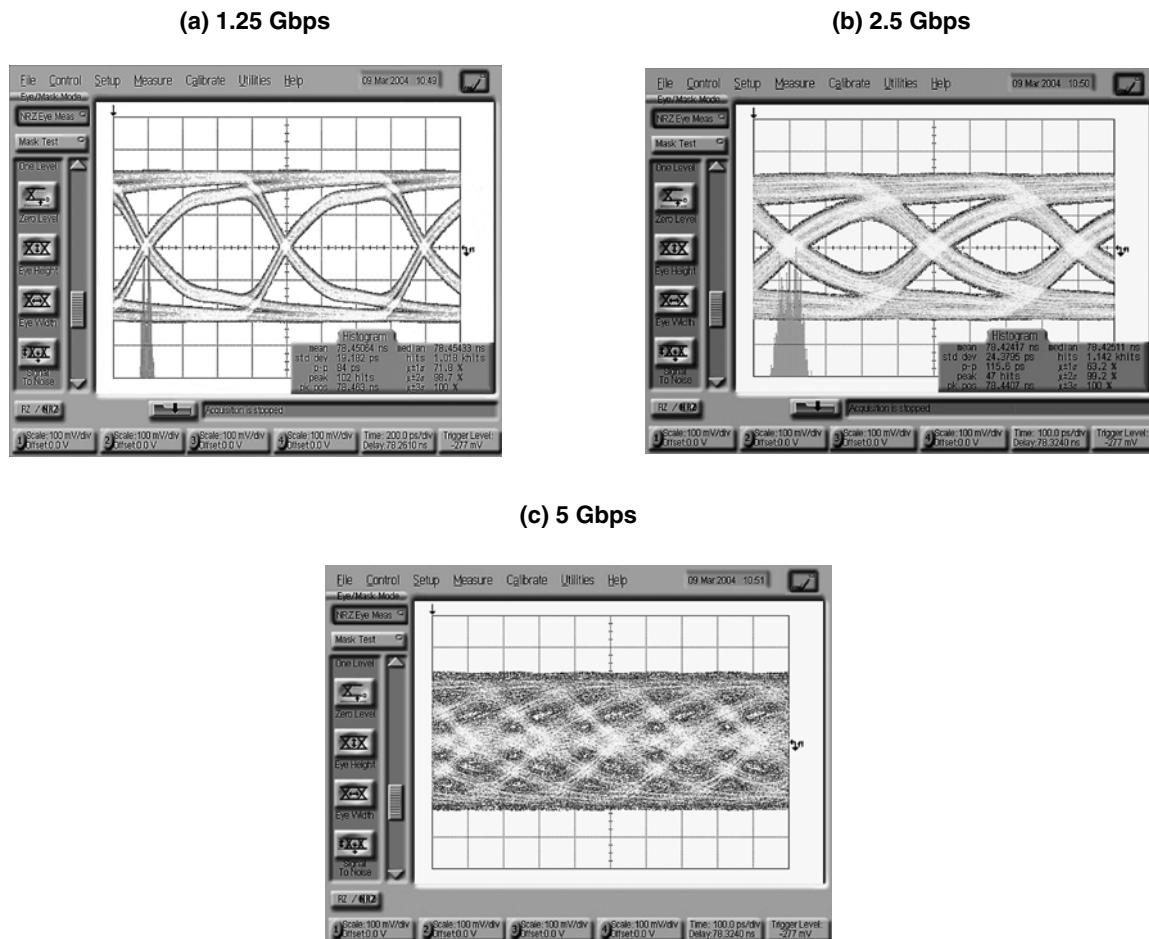

パッシブ・バックプレーンで生じるデータ遷移時の変動はデータ・パターンに依存します。パターン依存ジッタ量には上限があり、通常は確定ジッタと呼ばれます。ジッタが増大すると下流側のレシーバがデータを正しく復元できなくなります。Figure 6 に、バックプレーン通過後の擬似ランダム・ビットストリームのアイパターンを 1.25Gbps、2.5Gbps、5Gbps のそれぞれで示します。5Gbps ではアイ・オープニングが存在しないため、システム設計者は大きな課題を抱えることになります。

FIGURE 4. Waveform of a K28.5 Bit Stream at 2.5 Gbps

Table 1. Summary of 1-Bit Pulse Duration As Shown in Figure 5

|           | Symbol Width (1 UI) | Approximate Pulse Duration |

|-----------|---------------------|----------------------------|

| 1.25 Gbps | 800 ps              | 1600 ps (2.0 UI)           |

| 2.5 Gbps  | 400 ps              | 1100 ps (2.75 UI)          |

| 5 Gbps    | 200 ps              | 604 ps (3 UI)              |

## 2.0 バックプレーン設計のハードル (つづき)

FIGURE 5. 1-Bit Pulses at 1.25, 2.5 and 5 Gbps

## 2.0 バックプレーン設計のハードル (つづき)

FIGURE 6. Eye Diagrams of Pseudo-Random Bit Stream at 1.25, 2.5 and 5 Gbps Running ( $2^{10}-1$ ) Pattern

### 2.4 クロストーク

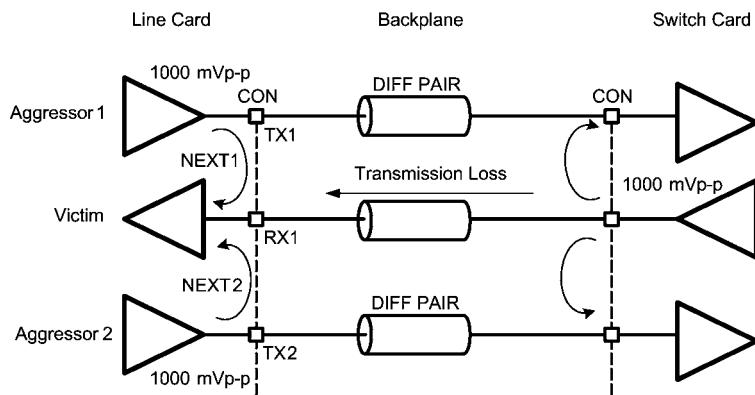

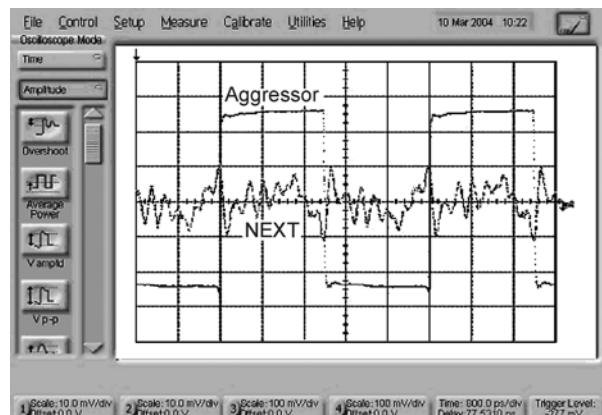

伝送損失に続いて、2.5Gbps 以上で動作する高速バックプレーンのデータ・インテグリティに影響を与える要因が、近接 (ニアエンド) クロストーク (NEXT) です。コネクタ内部に存在する導体エレメントは電界を生み、隣接ペアの導体に結合します。同様に、隣接の円筒形のビアにも結合します。

ライン・カード上のトランシミッタは、通常は  $1000\text{mV}_{\text{pp}}$  を超えるフル振幅でバックプレーンを駆動します。送信信号はバックプレーンを伝わる途中で大幅に減衰し、遠端にあるレシーバに到着する時

点では微弱な信号に変わります。遠端のレシーバ近くにある駆動能力の強いローカル・ドライバから、微弱な受信信号にニアエンド・クロストークが重畳し、結果として S/N 比が悪化します。5Gbps にて、データバスの伝送損失が 20dB でニアエンド・クロストークが 28dB 程度になることは珍しくなく、その場合 S/N 比はわずか 8dB になります。Figure 7 に NEXT の影響が及ぶシグナル・バスを示します。

## 2.0 バックプレーン設計のハードル (つづき)

FIGURE 7. Signal Paths of Victim and Aggressors

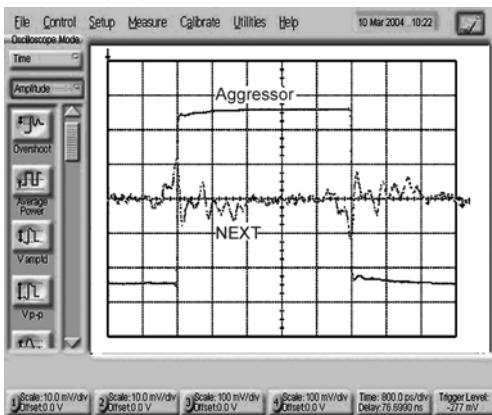

### 2.4.1 スピードに比例するクロストークの振幅

アグレッサ (攻撃側) ドライバのデータ遷移によってピクティム (犠牲側) チャネルに非対称のクロストーク・パルスが発生します。クロストークのパルス幅は一般に数百 ps です。データレートが低ければクロストーク・パルスは単位シンボル幅の中に埋もれてしまいます。ピット幅が短くなる高データレートでは、クロストーク・パルスの幅は単位シンボル幅以上になります。10 個の 1 と 10 個の 0 で繰り返されるパターンを使った 2.5Gbps で動作するアグレッサを Figure 8a に示します。アグレッサのデータ遷移で発生したクロストークは、次のクロストーク・パルスが発生する前に消滅していま

す。Figure 8b は同じアグレッサですが 5Gbps で動作しています。クロストーク・パルスが消滅する前に次のクロストーク・パルスが到来して、前のクロストーク・パルスに重畳しています。このようにパルスが重ね合わさる作用によって、動作速度が高く、シンボル幅が狭いほど、クロストークの振幅は大きくなります。ピクティム・チャネルの伝送損失増大とアグレッサ・チャネルからのクロストーク増大に対処しなければならない 5Gbps のような高データレートでは、NEXT の影響は致命的な問題です。Figure 9 にデータレートに伴う NEXT 振幅の増大を示します。

(a) At 2.5 Gbps

(b) At 5 Gbps

FIGURE 8. Cumulative Effect of NEXT Pulses as Bit Width Shrinks

## 2.0 バックプレーン設計のハードル (つづき)

FIGURE 9. NEXT Amplitude at 1.25, 2.5 and 5 Gbps, Running ( $2^{10}-1$ ) Pattern

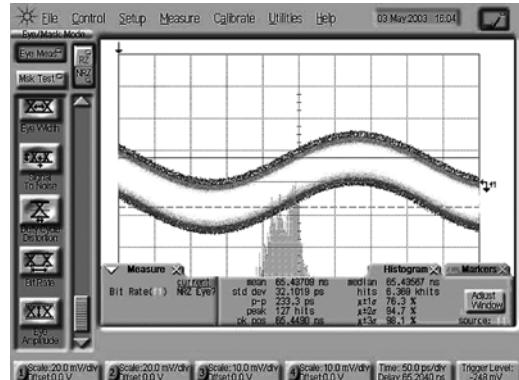

### 2.4.2 クロストークによるタイミング・マージンの減少

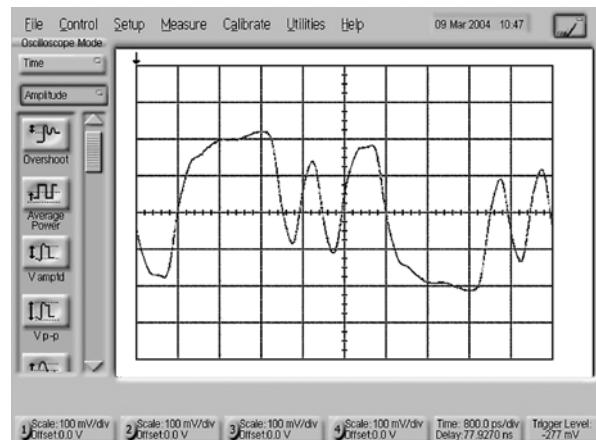

クロストークによってピクティム・チャネルに高周波ジッタが付加されます。微弱な受信信号の遷移タイミングはクロストークによって乱れます。アグレッサ・チャネルが 5Gbps の ( $2^{10}-1$ ) パターンで動作しているとき、5Gbps の繰り返し 1-0 パターンに重畠した大量のク

ロストークを Figure 10 に示します。クロストークはデータ復元を行う過程でレシーバのタイミング・マージンを減少させます。クロストークが大量に存在する状況下では、データを正しくサンプリングすることは困難です。結果としてエラーレートが高くなり、システム性能が損なわれます。

## 2.0 バックプレーン設計のハードル (つづき)

(a) No crosstalk

(b) With crosstalk

FIGURE 10. Alternating-1-0-Pattern at 5 Gbps With and Without Crosstalk

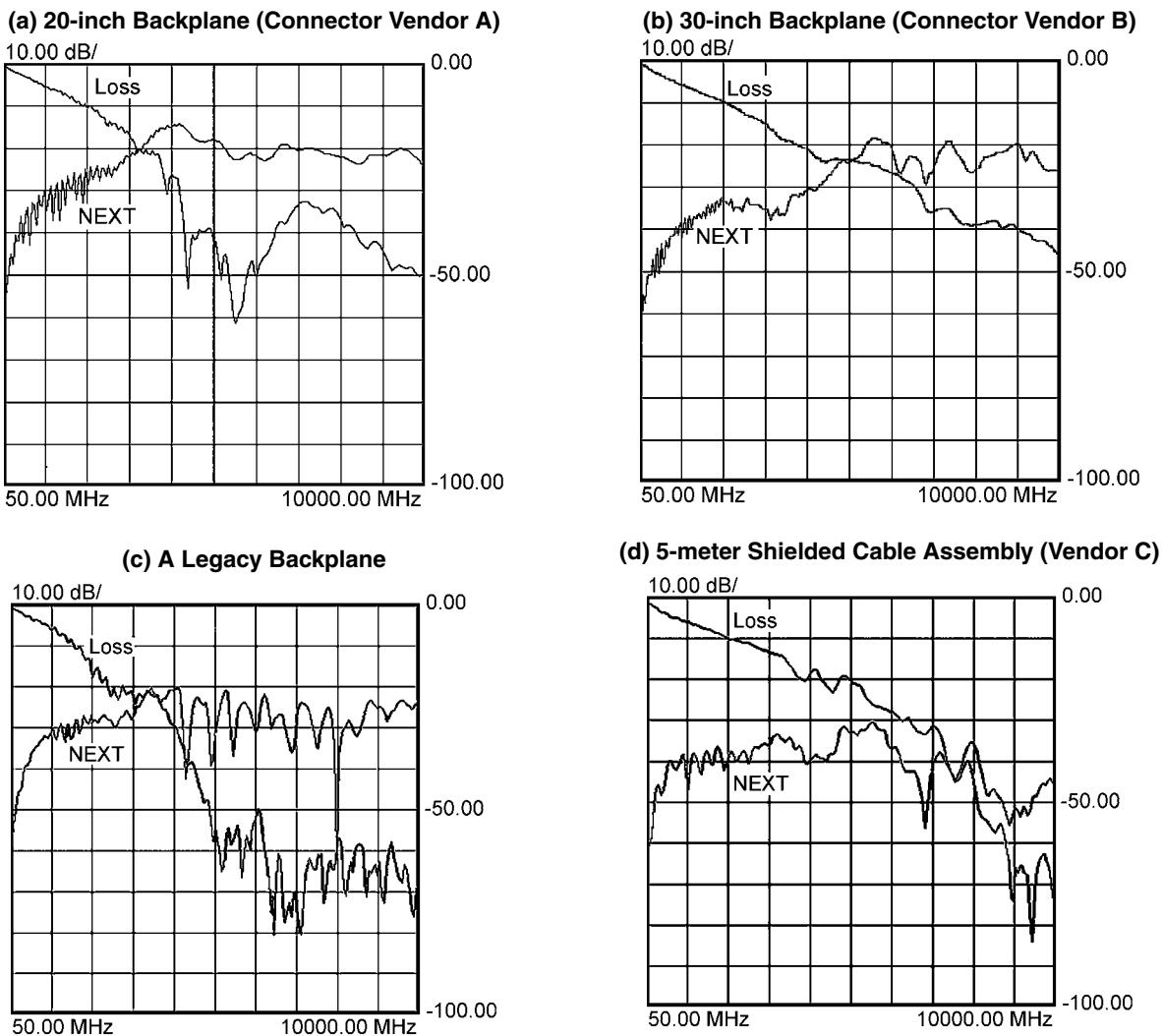

### 2.5 バックプレーンごとに異なる特性

伝送線路に存在するハードルの高さは、コネクタの性能、バックプレーン設計に用いられるボードの物理的形状 (ビア構造、トレス幅、ボード厚み、ボード層構成、ボード材料など)、あるいは差動ペアの割り当て方法などに直接左右されます。最近のバックプレーン設計には、インピーダンス不整合が小さくクロストークの小さな、新しいタイプの高速対応コネクタが採用されています。このようなコネクタの採用と高速プリント基板設計テクニックの適用により、コネクタ・インターフェース部分のルーティング制約は緩和されま

す。古くに設計された従来のバックプレーンには低速動作用に開発された旧世代のコネクタが採用されていました。従来のバックプレーンは、インピーダンス不整合が大きく、クロストーク結合も大きいため、高速動作には向いていません。5Gbpsに対応したバックプレーンを実現するには、伝送上のハードルをクリアする高性能トランシーバ IC が必要です。Figure 11に伝送損失とクロストークの観点から見たチャネル特性の例をいくつか示します。5Gbpsの実現にあたって着目すべき点は、伝送損失と、2.5GHzでのNEXTと伝送損失の比です。

## 2.0 バックプレーン設計のハードル (つづき)

FIGURE 11. Loss and NEXT of Several Types of Transmission Channels

## 3.0 数 Gbps に対応したバックプレーンが実用化へ

5Gbps バックプレーン設計の成否は、厳格なジッタ管理と、高性能バックプレーン・トランシーバ部品の採用にかかっています。バックプレーンを新しく設計する場合、高速ボード設計テクニックと最新の高速伝送対応コネクタを用いることで、伝送損失を抑えることが可能です。8b/10b コーディングのようなコード化されたビットストリームを採用することで、スペクトル成分の拡散を抑え ISI 歪み量を制御します。最新の高性能 SerDes デバイスや信号調整 IC によって、5Gbps への移行が現実のものとなります。

5Gbps のカッパー・バックプレーンを実現するテクニックのいくつかを、以下のセクションで説明します。

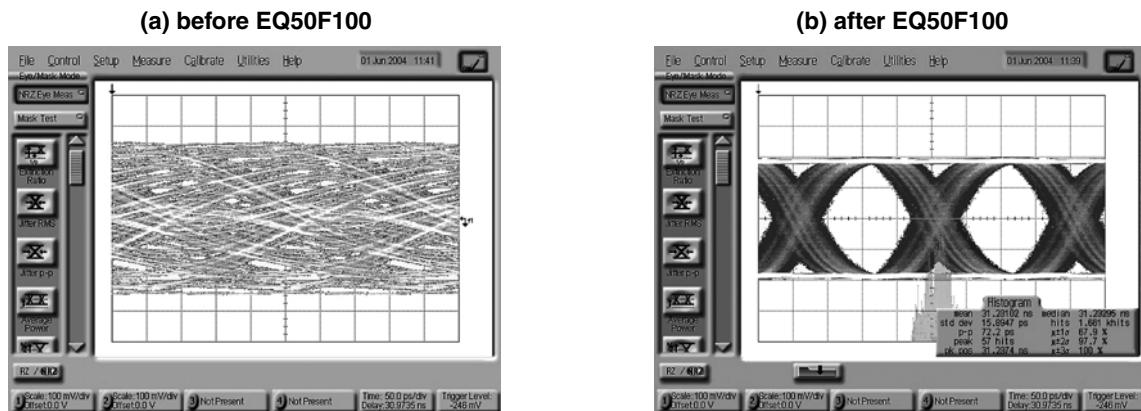

### 3.1 受信イコライズ

レシーバでイコライズを行う設計テクニックを適用すれば、新規設計の高性能バックプレーンだけでなく、従来の設計手法によるバックプレーン・ボードでも、5Gbps 動作が実現されます。伝送線路が最も短いチャネルと最長のチャネルは数 dB しか伝送損失に差がないため、イコライザの適用量を固定して最長チャネルのイコライズを行えば、最短チャネルに与える影響はありません。バックプレーンのレシーバ端に配置されたイコライザが、信号の高周波成分を昇圧して伝送損失を補償し、ビットストリーム内の低周波成分と高周波成分の振幅差を狭めます。イコライズ処理によって、バックプレーンで生じる ISI は小さくなり、データ復元に必要なアイ・オープニングが確保されます。ナショナル セミコンダクターの EQ50F100 のような単体イコライザ・デバイスを使用すれば、イコライザをライン・カード・コネクタの近くに配置することができます。EQ50F100 はバックプレーン・チャネルの信号をイコライズし、波形を整形して、データ復元を行う SerDes に信号を供給します。単体のイコライザ・デバイスであれば、チャネルの特性に応じて異なる品種を選択することで最適化が可能です。

### 3.0 数 Gbps に対応したバックプレーンが実用化へ (つづき)

FIGURE 12. Eye diagrams Before and After EQ50F100 Used In a Legacy Backplane

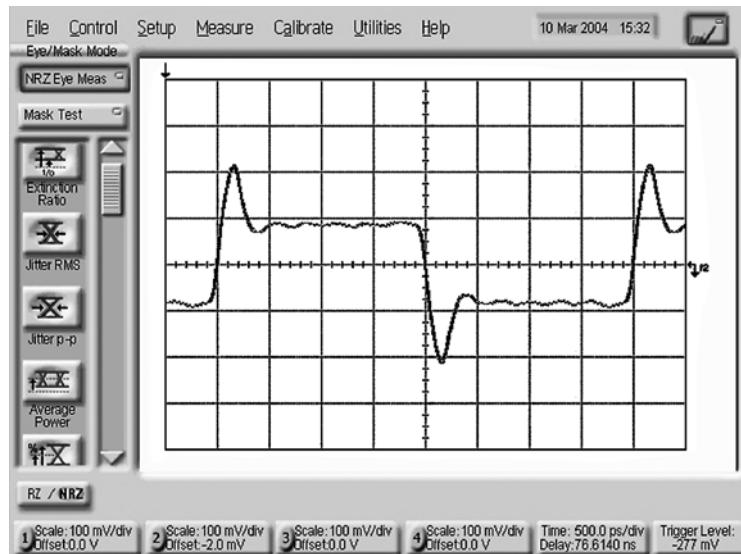

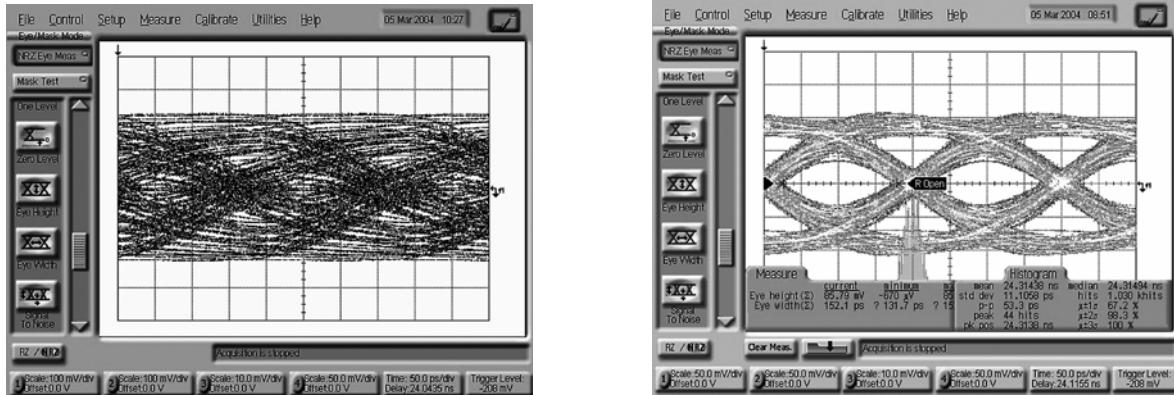

### 3.2 ドライバのデエンファシス

損失がそれほど大きくなりバックプレーンで、アイ・オープニングが問題となるほどには減衰していない場合は、わずかな量のイコライズを適用して ISI 歪みを低減してやる必要があります。送信ドライバにデエンファシスを実装して、ビットストリームの低周波成分の駆動振幅を、チャネル損失後の高周波成分と同等のレベルになるように抑えて出力します。Figure 13 にデエンファシスを用いたドライ

バ波形を示します。このテクニックはクロストークの抑制に適します。低速 SerDes で使われる従来のプリエンファシス・テクニックとは異なり、デエンファシスは駆動振幅を高めません。したがって、高データレートでもクロストークを悪化させません。

FIGURE 13. De-Emphasis Waveform from Driver

### 3.0 数 Gbps に対応したバックプレーンが実用化へ (つづき)

FIGURE 14. Eye Diagrams with and Without De-Emphasis after a 30-inch Backplane

#### 3.3 クロストークの管理

クロストークによってレシーバの入力データ・ビットストリームには高周波ジッタが加わります。レシーバ PLL は PLL 帯域を超える高周波ジッタには追従できないため、データ復元に必要なレシーバのタイミング・マージンが減少します。タイミング・マージンの減少に対処するには、入力ジッタ許容度が高いレシーバが必要です。このほか、送信レベルをダウンストリーム・レシーバが受信できる最小レベルに設定する方法でもクロストークを抑えられます。また、コネクタの信号割り当てで、送信信号ピンと受信信号ピンを隣接させない限り、クロストークが大幅に増えることはありません。送信ペアと受信ペアをそれぞれ隣接させると信号が結合してクロストークが増大します。

#### 3.4 ノイズの多い電源の排除

電源に重畳するノイズのうち、SerDes トランシーバの送信 PLL の帯域に該当するノイズを抑える必要があります。PLL のパスバンドのノイズは送信出力の周期的ジッタに直接影響を与えます。周期ジッタで生じるノイズがダウンストリーム・レシーバの PLL 帯域内であれば、PLL はジッタに追従するため問題は起いません。しかし、ネットワーク機器内のカードに搭載されるレシーバが複数のサプライヤで構成されている環境では、どのようなレシーバが対象となるかわからず、根本的にはジッタを招く電源ノイズを抑えることが有効です。ナショナルセミコンダクターは低ノイズ降圧スイッチング・レギュレータ LM27262 を供給しています。LM27262 はおよそ 300KHz のスイッチング周波数で動作しスイッチング・ノイズは数 mV 未満です。LM27262 のようなクリーンな電源を使うことで、ジッタ性能全体が向上し、システムのエラーレート性能を高めます。

## 4.0まとめ

数ギガビットに対応したバックプレーンの設計にはさまざまな課題が存在します。そのような課題の解決には、ナショナルセミコンダクターのシグナル・コンディショニング製品が最適です。システム設計に気を配りクロストークとジッタを適切にコントロールすることで、開発期間とコストを抑えながら、従来のバックプレーンを 5Gbps 動作にアップグレードすることが可能です。

## 5.0 参考資料

EQ50F100 1 ~ 6.25Gbps PCB イコライザのデータシート、ナショナルセミコンダクター

LM27262 電圧レギュレータ・コントローラのデータシート、ナショナルセミコンダクター

このドキュメントの内容はナショナルセミコンダクター社製品の関連情報として提供されます。ナショナルセミコンダクター社は、この発行物の内容の正確性または完全性について、いかなる表明または保証もいたしません。また、仕様と製品説明を予告なく変更する権利を有します。このドキュメントはいかなる知的財産権に対するライセンスも、明示的、黙示的、禁反言による惹起、またはその他を問わず、付与するものではありません。

試験や品質管理は、ナショナルセミコンダクター社が自社の製品保証を維持するために必要と考える範囲に用いられます。政府が課す要件によって指定される場合を除き、各製品のすべてのパラメータの試験を必ずしも実施するわけではありません。ナショナルセミコンダクター社は製品適用の援助や購入者の製品設計に対する義務は負いかねます。ナショナルセミコンダクター社の部品を使用した製品および製品適用の責任は購入者にあります。ナショナルセミコンダクター社の製品を用いたいかなる製品の使用または供給に先立ち、購入者は、適切な設計、試験、および動作上の安全手段を講じなければなりません。

それら製品の販売に関するナショナルセミコンダクター社との取引条件で規定される場合を除き、ナショナルセミコンダクター社は一切の義務を負わないものとし、また、ナショナルセミコンダクター社の製品の販売が使用、またはその両方に関連する特定目的への適合性、商品の機能性、ないしは特許、著作権、または他の知的財産権の侵害に関連した義務または保証を含むいかなる表明または黙示的保証も行いません。

### 生命維持装置への使用について

ナショナルセミコンダクター社の製品は、ナショナルセミコンダクター社の最高経営責任者(CEO)および法務部門(GENERAL COUNSEL)の事前の書面による承諾がない限り、生命維持装置または生命維持システム内のきわめて重要な部品に使用することは認められていません。

ここで、生命維持装置またはシステムとは (a) 体内に外科的に使用されることを意図されたもの、または (b) 生命を維持あるいは支持するものをいい、ラベルにより表示される使用法に従って適切に使用された場合に、この不具合が使用者に身体的障害を与えると予想されるものをいいます。重要な部品とは、生命維持にかかわる装置またはシステム内のすべての部品をいい、これの不具合が生命維持用の装置またはシステムの不具合の原因となりそれらの安全性や機能に影響を及ぼすことが予想されるものをいいます。

National Semiconductor とナショナルセミコンダクターのロゴはナショナルセミコンダクター コーポレーションの登録商標です。その他のブランドや製品名は各権利所有者の商標または登録商標です。

Copyright © 2006 National Semiconductor Corporation

製品の最新情報については [www.national.com](http://www.national.com) をご覧ください。

ナショナルセミコンダクター ジャパン株式会社

本社 / 〒 135-0042 東京都江東区木場 2-17-16 TEL.(03)5639-7300

技術資料(日本語/英語)はホームページより入手可能です。

[www.national.com/jpn/](http://www.national.com/jpn/)

# ご注意

日本テキサス・インスツルメンツ株式会社（以下TIJといいます）及びTexas Instruments Incorporated（TIJの親会社、以下TIJないしTexas Instruments Incorporatedを総称してTIといいます）は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIJとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIJの標準販売契約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIJとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。TI製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI製部品を使用したお客様の製品及びアプリケーションについて想定される危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならぬ場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、かつその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

Copyright © 2011, Texas Instruments Incorporated

日本語版 日本テキサス・インスツルメンツ株式会社

## 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。

### 1. 静電気

- 素手で半導体製品単体を触らないこと。どうしても触る必要がある場合は、リストストラップ等で人体からアースをとり、導電性手袋等をして取り扱うこと。

- 弊社出荷梱包単位（外装から取り出された内装及び個装）又は製品単品で取り扱いを行う場合は、接地された導電性のテーブル上で（導電性マットにアースをとったもの等）、アースをした作業者が行うこと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

- 前記のリストストラップ・導電性手袋・テーブル表面及び実装装置類の接地等の静電気帯電防止措置は、常に管理されその機能が確認されていること。

### 2. 湿度環境

- 温度：0～40°C、相対湿度：40～85%で保管・輸送及び取り扱いを行うこと。（但し、結露しないこと。）

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの黙示的保証を無効にし、かつ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任もありません。

TIは、TIの製品が、安全でないことが致命的となる用途ないしアプリケーション（例えば、生命維持装置のように、TI製品に不良があった場合に、その不良により相当な確率で死傷等の重篤な事故が発生するようなもの）に使用されることを認めておりません。但し、お客様とTIの双方の権限有る役員が書面でそのような使用について明確に合意した場合は除きます。たとえTIがアプリケーションに関連した情報やサポートを提供したとしても、お客様は、そのようなアプリケーションの安全面及び規制面から見た諸問題を解決するために必要とされる専門的知識及び技術を持ち、かつ、お客様の製品について、またTI製品をそのような安全でないことが致命的となる用途に使用することについて、お客様が全ての法的責任、規制を遵守する責任、及び安全に関する要求事項を満足させる責任を負っていることを認め、かつそのことに同意します。さらに、もし万一、TIの製品がそのような安全でないことが致命的となる用途に使用されたことによって損害が発生し、TIないしその代表者がその損害を賠償した場合は、お客様がTIないしその代表者にその全額の補償をするものとします。

TI製品は、軍事的用途もしくは宇宙航空アプリケーションないし軍事的環境、航空宇宙環境にて使用されるようには設計もされていませんし、使用されることを意図されておりません。但し、当該TI製品が、軍需対応グレード品、若しくは「強化プラスティック」製品としてTIが特別に指定した製品である場合は除きます。TIが軍需対応グレード品として指定した製品のみが軍需品の仕様書に合致いたします。お客様は、TIが軍需対応グレード品として指定していない製品を、軍事的用途もしくは軍事的環境下で使用することは、もっぱらお客様の危険負担においてなされるということ、及び、お客様がもっぱら責任をもって、そのような使用に関して必要とされる全ての法的要件及び規制上の要求事項を満足させなければならないことを認め、かつ同意します。

TI製品は、自動車用アプリケーションないし自動車の環境において使用されるようには設計もされていませんし、また使用されることを意図されておりません。但し、TIがISO/TS 16949の要求事項を満たしていると特別に指定したTI製品は除きます。お客様は、お客様が当該TI指定品以外のTI製品を自動車用アプリケーションに使用しても、TIは当該要求事項を満たしていなかったことについて、いかなる責任も負わないことを認め、かつ同意します。

- 直射日光があたる状態で保管・輸送しないこと。

- 3. 防湿梱包

- 防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装すること。

- 4. 機械的衝撃

- 梱包品（外装、内装、個装）及び製品単品を落下させたり、衝撃を与えないこと。

- 5. 熱衝撃

- はんだ付け時は、最低限260°C以上の高温状態に、10秒以上さらさないこと。（個別推奨条件がある時はそれに従うこと。）

- 6. 汚染

- はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質（硫黄、塩素等ハロゲン）のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。（不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。）

以上