BTL ?????????????

Literature Number: JAJA390

### **BTL Power Dissipation** Calculation

National Semiconductor Application Note 839 Joel Martinez, Stephen Kempainen July 1992

#### INTRODUCTION

Futurebus+ systems designed today have bus widths of 32 or 64. To support higher bandwidths in the future, Futurebus+ provides a data width extension of up to 256 bits. BTL (Backplane Transceiver Logic) is the electrical signaling environment for Futurebus+. The number of BTL transceivers in a system will increase as the bus width is extended to accommodate higher bandwidths. A total of 16 transceivers is required to implement a 64-bit data bus. Four 6-bit Handshake Transceivers (DS3884A) are used for the handshake, central arbitration, capability and serial bus lines. One 9-bit Arbitration Transceiver (DS3885) is used for the arbitration competition lines. Three 9-bit Data Transceivers (DS3883A or DS3886A) are used for the command, status and tag lines. A 64 wide bus with byte parity requires 8 data transceivers for the multiplexed address and data lines alone. A 256 wide bus requires 32 data transceivers. Including the other lines, the total number of transceivers on single board for a 256-bit data bus is 40. The power required and dissipated by these transceivers must be fully understood to design an efficient cooling and power supply system for the backplane. Power calculations differ depending on the assumptions made concerning supply and output power. This application note illustrates how to use graphs provided by manufacturers to obtain accurate power calculations. Power is calculated for these conditions; worst case, driver outputs high, driver outputs low and outputs switching.

### CALCULATING BTL POWER USING THE STANDARD

The power equation may be divided into two parts. One part is the supply power (Ps) which is derived from the quiescent current flowing into the power pins. The other is output power (Po) derived from current flowing into or out of the input and output pins. The standard method to calculate P<sub>S</sub> and Po is to use specifications available in the DC Electrical Characteristics of datasheets.  $I_{\text{CC}}(\text{typ})$  and  $I_{\text{CC}}(\text{max})$  are typical and maximum supply current which may be found directly within the DC Electrical Characteristics. Typical power dissipation ( $P_{S\_Typ}$ ) is equal to  $I_{CC}(typ)$  x  $V_{CC}(typ)$ . Maximum power dissipation (P<sub>S\_max</sub>) is equal to I<sub>CC</sub>(max) x V<sub>C</sub>c(max). Output power is different when the output is low and when it is high. With the output high (the device is in high impedance) essentially zero current flows in or out of the device and Po equals zero. With the output low, Po is equal to  $V_{OL}(max) \times I_{OL}(max)$ .  $P_O$  is worst case when the output is low or asserted. Typical and Maximum power calculations are shown in Table 2 for DS3886A.  $V_{\rm OL}$  and  $I_{\rm OL}$  will differ depending on the termination resistor and voltage used on the backplane which is not taken into account. Actual Po for Futurebus+ is less and an accurate calculation of power dissipation is presented later.

#### **POWER CALCULATION EQUATIONS AND DEFINITIONS**

Table 1 summarizes the equations and terms used in following discussions.

**TABLE 1. Power Calculation Equations and Terms**

| Parameter       | Equation                                                                                                                    | Description                                                                                                              |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|

| V <sub>CC</sub> | 4.5V < V <sub>CC</sub> < 5.5V                                                                                               | Supply Voltage                                                                                                           |  |

| I <sub>cc</sub> | See DC Electrical Characteristics, Typical I <sub>CC</sub> vs<br>Temperature Curves or Typical I <sub>CC</sub> vs Frequency | Supply Current                                                                                                           |  |

| V <sub>OL</sub> | See Typical I <sub>OL</sub> vs V <sub>OL</sub> Curves                                                                       | Output Low Voltage                                                                                                       |  |

|                 |                                                                                                                             | For the BTL Driver $V_{OL}$ will Depend on the Termination Resistance Used                                               |  |

| I <sub>OL</sub> | See Typical I <sub>OL</sub> vs V <sub>OL</sub> Curves                                                                       | Output Low Current                                                                                                       |  |

|                 |                                                                                                                             | For the BTL Driver I <sub>OL</sub> will Depend on the Termination Resistance Used                                        |  |

| V <sub>t</sub>  | 2.1V                                                                                                                        | Termination Voltage                                                                                                      |  |

| Ps              | I <sub>cc</sub> x V <sub>cc</sub>                                                                                           | Supply Power                                                                                                             |  |

|                 |                                                                                                                             | Power Dissipated Due to Quiescent Current Flowing into Power Pins                                                        |  |

| Po              | V <sub>OL</sub> x I <sub>OL</sub>                                                                                           | Output Power                                                                                                             |  |

|                 |                                                                                                                             | Power Dissipated per Channel at the Driver or Receiver Output when the Output is Low                                     |  |

|                 | (V <sub>CC</sub> – V <sub>OH</sub> ) x I <sub>OH</sub>                                                                      | Power Dissipated per Channel at the Driver or Receiver Output when the Output is High; For BTL $I_{\mathrm{OH}}$ is Zero |  |

| TABLE 2. Standard Power Calculations for the DS3886A |                                                   |  |  |  |

|------------------------------------------------------|---------------------------------------------------|--|--|--|

| Typical                                              | Max                                               |  |  |  |

| P <sub>S</sub> = 5.0V x 55 mA = 275 mW               | P <sub>S</sub> = 5.5V x 62 mA = 341 mW            |  |  |  |

| P <sub>O</sub> = 1.0V x 65 mA = 65 mW                | P <sub>O</sub> = 1.1V x 80 mA = 88 mW             |  |  |  |

| P <sub>total</sub> = 275 mW + (65 mW x 9) = 860 mW   | P <sub>total</sub> = 341 mW + (88 mW x 9) = 1.13W |  |  |  |

## REVIEW OF BTL — BACKPLANE TRANSCEIVER LOGIC

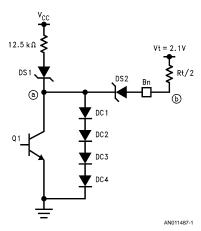

A brief review of BTL is given to help the reader understand how the driver operates. A schematic of the BTL output stage is shown in Figure 1. The driver output is composed of a Schottky diode — DS2 in series with the collector of transistor Q1. DS2 shields the capacitance of Q1 from the bus to reduce capacitive loading. When the driver is asserted Q1 is "on", node a is approximately 0.4V, and node b is approximately 1V. Current flows from the 2.1V termination voltage through Rt/2, through DS2 and into the collector of Q1. When the driver is released Q1 is "off", a 12.5 k $\Omega$  resistor pulls node a which is clamped to 3V by four diode clamps (DC1 to DC4) in series. DS2 is reversed biased (node a is at a higher potential than node b), with node b at 2.1V which is equal to the termination voltage. Essentially zero current flows into or out of the driver output.

FIGURE 1. Futurebus+ BTL Driver Output Schematic

www.national.com

# CALCULATION OF OUTPUT POWER USING LOAD LINES

IEEE 1194.1 BTL Electrical Characteristics define  $I_{OL}$  and  $V_{OL}.$  BTL devices are required to sink 80 mA ( $I_{OL}$ ) within a specified  $V_{OL}$  range of 0.75V to 1.1V. This requirement was established to maintain compatibility between vendors offering BTL devices. The BTL devices offered by National conform to this specification. The actual  $I_{OL}$  flowing into the output is dependent on the termination resistor and voltage on the backplane. National's datasheets specify 12.5 $\Omega$  in series with 2.1V to test AC and DC requirements which conform to an  $I_{OL}$  of 80 mA. The equivalent representation of a 12.5 $\Omega$  at opposite ends. The Thevenin equivalent of two 25 $\Omega$  resistors is 12.5 $\Omega$ . Fu

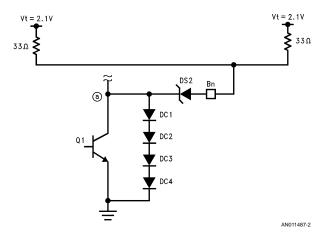

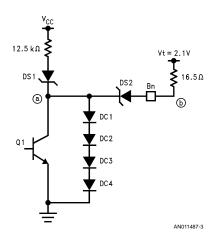

turebus+ requires  $33\Omega$  termination resistors in series with 2.1V at each end of the backplane as shown on Figure 2. The Thevenin equivalent for the Futurebus+ termination of  $33\Omega$  is  $16.5\Omega$  in series with 2.1V which is shown in Figure 3.  $\rm I_{OL}$  for a Futurebus+ termination will be less than 80 mA.

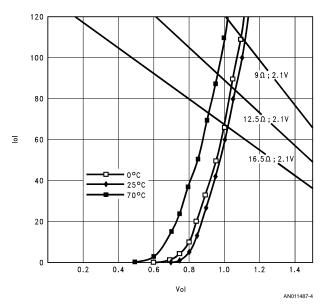

$l_{OL}$  for a Futurebus+ termination is equal to the intersection point between the output  $V_{OL}$  vs  $l_{OL}$  curve and the resistor load line as shown on Figure 4. The intersection point for a Futurebus+ load line of 16.5 $\Omega$  in series with 2.1V at 25°C, is 65 mA and 1.025V. The intersection point for 12.5 $\Omega$  in series with 2.1V is 83 mA and 1.075V. The intersection point for 9 $\Omega$  in series with 2.1V is 110 mA and 1.125V.  $l_{OL}$  and  $V_{OL}$  may be obtained for any termination resistor and voltage using the load line intersection point.

FIGURE 2. Futurebus+ Backplane Termination

FIGURE 3. Thevenin Equivalent of Futurebus+ Backplane

FIGURE 4.  $\rm I_{OL}$  vs  $\rm V_{OL}$  and Load Line

Output power ( $P_O$ ) per channel is equal to the product of  $I_{OL}$  vs  $V_{OL}$  at the intersection point. For Futurebus+ with the driver asserted, the point of intersection is 65 mA and 1.025V which yields 66.6 mW for output power. Output power for a transceiver is directly proportional to the number of bits. A 9-bit transceiver (like the DS3886A, DS3883A or DS3885) with all outputs low will need to dissipate 599 mW, which is 66 mW times 9 bits. In addition to  $P_O$ ,  $P_S$  must also be included for the total power. Calculations for  $P_S$  will be given later. Output power for different loads is shown on Table 3. Output power almost doubles when the resistor is reduced from 16.5 $\Omega$  to  $9\Omega$ . When all drivers are released, the outputs are in a high impedance state and pulled high by the termination. At this state, essentially zero power is dissipated at the outputs.

Output power is also dependent on the duty cycle. The power dissipated at the output will equal the average power between the asserted and the released state. Assume that in a normal operation the drivers are high half of the time and low half of the time. This condition may be approximated to

a 50% duty cycle. Power is calculated for a 50% duty cycle in *Table 3*. To calculate power for other duty cycles the equation below may be used:

$$P_{O(k)} = P_O$$

(asserted) x k

where k is equal to the duty cycle.

For example,  $\rm P_{O}$  is calculated for a 9-bit device terminated according to Futurebus+ specification with a 60% duty cycle.

$$P_{O(60\%)} = 600 \text{ mW x } 0.60 = 360 \text{ mW}$$

#### **CALCULATION OF TOTAL BTL TRANSCEIVER POWER**

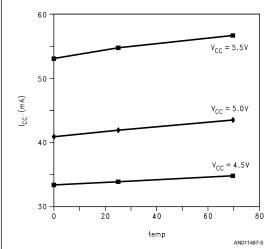

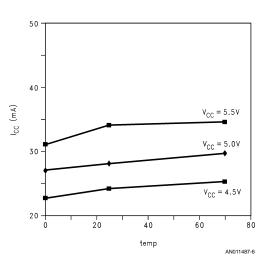

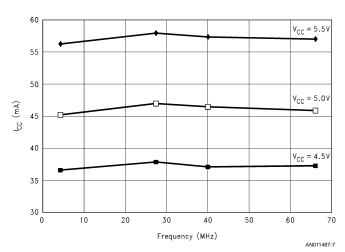

Total Power is equal to the sum of P $_{\rm O}$  and P $_{\rm S}$ . Using P $_{\rm O}$  from Table 3 and P $_{\rm S}$  derived from Figure 5, Figure 6, Figure 7, Table 4 shows total typical power for different conditions; all outputs high, all outputs low, 10 MHz and 20 MHz with 50% duty cycles. Supply power is equal to I $_{\rm CC}$  x V $_{\rm CC}$ , where V $_{\rm CC}$  and I $_{\rm CC}$  were taken from Figure 5, Figure 6, Figure 7. Table 5 shows Maximum power using I $_{\rm CC}$ (max) x V $_{\rm CC}$ (max) from the datasheet.

TABLE 3. Calculation of BTL Output Power (T = 25°C)

| Termination                                                | Termination         | Output Low                | Output Low                | Output | Output       | Output       |

|------------------------------------------------------------|---------------------|---------------------------|---------------------------|--------|--------------|--------------|

| Voltage                                                    | in Parallel         | Current — I <sub>OL</sub> | Voltage — V <sub>OL</sub> | Power  | Power 6-Bits | Power 9-Bits |

| (V)                                                        | <b>(</b> Ω <b>)</b> | (mA)                      | (V)                       | (mW)   | (mW)         | (mW)         |

| BTL OUTPUT P                                               | OWER PER CHANNEL    | WHEN DRIVERS              | ARE ASSERTED              |        |              |              |

| 2.1                                                        | 16.5                | 65                        | 1.025                     | 66.6   | 400          | 600          |

| 2.1                                                        | 12.5                | 83                        | 1.050                     | 87.2   | 523          | 784          |

| 2.1                                                        | 9                   | 110                       | 1.125                     | 123.8  | 743          | 1,114        |

| BTL OUTPUT POWER PER CHANNEL WHEN DRIVERS ARE RELEASED     |                     |                           |                           |        |              |              |

| 2.1                                                        | 16.5, 12.5 or 9     | 0                         | 2.1V                      | 0      | 0            | 0            |

| BTL OUTPUT POWER PER CHANNEL WHEN DRIVERS @ 50% DUTY CYCLE |                     |                           |                           |        |              |              |

| 2.1                                                        | 16.5                | 65                        | 1.025                     | 66.6/2 | 200          | 300          |

|                                                            | 1                   |                           |                           |        | I            |              |

www.national.com

| TABLE 3. Calculation of BTL Output Power (T = 25°C) (Continued)                                                                                                  |      |     |       |         |      |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-------|---------|------|-----|

| Termination Termination Output Low Output Low Output Output  Voltage in Parallel Current—I <sub>OL</sub> Voltage—V <sub>OL</sub> Power Power 6-Bits Power 9-Bits |      |     |       |         |      |     |

| $oxed{(V)} oxed{(\Omega)} oxed{(mA)} oxed{(V)} oxed{(mW)} oxed{(mW)} oxed{(mW)}$                                                                                 |      |     |       |         | (mW) |     |

| BTL OUTPUT POWER PER CHANNEL WHEN DRIVERS @ 50% DUTY CYCLE                                                                                                       |      |     |       |         |      |     |

| 2.1                                                                                                                                                              | 12.5 | 83  | 1.050 | 87.2/2  | 262  | 392 |

| 2.1                                                                                                                                                              | 9    | 110 | 1.125 | 123.8/2 | 372  | 557 |

TABLE 4. DS3886 Typical Power with Futurebus+ Termination

| Parameter                         | Supply Power | Output Power | Total Power |

|-----------------------------------|--------------|--------------|-------------|

| All Outputs Low (25°C and 5V)     | 210 mW       | 600 mW       | 810 mW      |

| All Outputs High (25°C and 5V)    | 140 mW       | 0 mW         | 140 mW      |

| Switching at 10 MHz (25°C and 5V) | 230 mW       | 300 mW       | 530 mW      |

| Switching at 20 MHz (25°C and 5V) | 235 mW       | 300 mW       | 535 mW      |

TABLE 5. DS3886 Maximum Power with Futurebus+ Termination

| Parameter       | Supply Power | Output Power | Total Power |  |

|-----------------|--------------|--------------|-------------|--|

| All Outputs Low | 341 mW       | 600 mW       | 941 mW      |  |

FIGURE 5. DS3886A  $I_{\rm CC}$  vs Temperature (All Bn Outputs Low)

FIGURE 6. DS3886A  $I_{\rm CC}$  vs Temperature (All Bn Outputs High)

FIGURE 7. DS3886A  $I_{CC}$  vs Switching Frequency ( $A_n$  to  $B_n$ ) (All Channels Switching at Room Temperature)

The maximum power dissipation result shown in Table 5 is 1.315W compared to 1.51W in Table 2 derived from the standard method. Power calculated using the standard method is 15% higher than actual maximum of 1.315W.  $I_{OL}$  of 80 mA and V<sub>OI</sub> of 1.1V was used in the standard method yielding the higher Po. The results derived in Table 5 take into account the Futurebus+ termination specification in the calculation of Po. There are four typical power calculations in Table 4 reflecting different conditions. Typical power varied from 325 mW when all outputs are high to 990 mW when all outputs are low. The typical power calculated in Table 2 is 1.08W which is 10% higher than that calculated in Table 4. These different power calculations are important when determining the total power of a system. A Futurebus+ backplane may contain several modules. Only one module may transmit data on the bus while others receive. It is important to know how to calculate power dissipation for modules in the transmit mode as well as modules in the receive mode to derive accurate system power.

#### CALCULATION OF SYSTEM POWER REQUIREMENTS

In a backplane, one board will normally be active and driving the bus while other modules are receiving or in standby. If all lines were asserted, the termination voltage must be able to supply enough current to all the lines. To determine the current requirement from the termination voltage, use this equation;

I<sub>OL</sub> x Number of Lines = Termination Current

In a 32-bit Futurebus+ backplane the total number of lines will be 89 which includes all the required lines in addition to the 32-bit address/data lines. The current requirement from the termination supply will be;

65 mA x 89 Lines = 5.79A

A 64-bit Futurebus+ backplane requires;

$$65 \text{ mA} \times (89 + 32 + 4) = 8.13A$$

Calculation of typical system power is shown below. Two assumptions are made for the given equation. First, one module transmits while others receive. Second, the transmitting module will have an average duty cycle equal to 50% and running at 20 MHz. Power per bit allows easy calculation of total power for different number of lines. Dividing the total transceiver power by the number of bits on the transceiver will yield power/bit. The total number of modules on the backplane minus one gives the number of receiving modules. The receiving modules will have their outputs in a high state

(Power/bit with 50% Duty Cycle @ 20 MHz x # of Lines) + (# Boards – 1) (Power/Bit with all Outputs High x # of Lines) = Transceiver System Power

For a 32-bit Futurebus+ Interface with 14 boards the transceiver system power required will be;

(725 mW/9 x 89) + (14 - 1) (325 mW/9 x 89) = 49W

#### CONCLUSION

There are several ways of calculating power dissipation. The results of these calculations will greatly vary depending on the assumptions. An error in calculating output power will be multiplied when extending the results to determine overall system power. A thorough understanding of how to calculate power will yield accurate power calculations. A preferred method of calculating output power is to use the load line intersection point. Typical power dissipation calculation should use duty cycle approximation. Typical device curves are provided with datasheets. Refer to individual datasheets for most up to date information. With this background, the designer will be able to make accurate thermal and power analysis of the interface which may ultimately reduce cost.

| 7 |   |   |

|---|---|---|

|   |   |   |

|   |   |   |

|   |   |   |

|   |   |   |

|   |   |   |

|   |   |   |

|   |   |   |

|   |   |   |

|   |   |   |

|   |   |   |

|   |   |   |

|   |   |   |

|   |   |   |

|   |   |   |

|   |   |   |

|   |   |   |

|   |   |   |

|   |   |   |

|   |   |   |

|   |   |   |

|   |   |   |

|   |   |   |

|   |   |   |

|   |   |   |

|   |   |   |

| 7 |   |   |

| 7 |   |   |

| 7 |   |   |

| 7 |   |   |

| 7 |   |   |

| 7 |   |   |

| 7 |   |   |

| 7 |   |   |

| 7 |   |   |

| 7 |   |   |

| 7 |   |   |

| 7 |   |   |

| 7 |   |   |

| 7 |   |   |

| 7 |   |   |

| 7 |   |   |

| 7 |   |   |

| 7 |   |   |

| 7 |   |   |

| 7 |   |   |

| 7 |   |   |

| 7 |   |   |

| 7 |   |   |

| 7 |   |   |

| 7 |   |   |

| 7 |   |   |

| 7 |   |   |

| 7 |   |   |

| 7 |   |   |

| 7 |   |   |

| 7 |   |   |

| 7 |   |   |

| 7 |   |   |

| 7 |   |   |

| 7 |   |   |

| 7 |   |   |

| 7 |   |   |

| 7 |   |   |

| 7 |   |   |

|   | ١ | 7 |

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DE-VICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMI-CONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation Americas

Tel: 1-800-272-9959 Fax: 1-800-737-7018 Email: support@nsc.com

www.national.com

**National Semiconductor** Europe

Fax: +49 (0) 1 80-530 85 86 Fax: +49 (0) 1 80-530 85 86

Email: europe support@nsc.com

Deutsch Tel: +49 (0) 1 80-530 85 85

English Tel: +49 (0) 1 80-532 78 32

Français Tel: +49 (0) 1 80-532 93 58

Italiano Tel: +49 (0) 1 80-534 16 80

National Semiconductor Asia Pacific Customer Response Group

Fax: 65-2504466 Email: sea.support@nsc.com National Semiconductor Japan Ltd. Tel: 81-3-5620-6175 Fax: 81-3-5620-6179

**AN-839**

# ご注意

日本テキサス・インスツルメンツ株式会社(以下TIJといいます)及びTexas Instruments Incorporated(TIJの親会社、以下TIJないしTexas Instruments Incorporatedを総称してTIといいます)は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIJとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIJの標準販売契約約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIJとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。TI製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI製部品を使用したお客様の製品及びアプリケーションについて想定されうる危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならない場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、かつその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの黙示的保証を無効にし、かつ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任もありません。

TIは、TIの製品が、安全でないことが致命的となる用途ないしアプリケーション(例えば、生命維持装置のように、TI製品に不良があった場合に、その不良により相当な確率で死傷等の重篤な事故が発生するようなもの)に使用されることを認めておりません。但し、お客様とTIの双方の権限有る役員が書面でそのような使用について明確に合意した場合は除きます。たとえTIがアプリケーションに関連した情報やサポートを提供したとしても、お客様は、そのようなアプリケーションの安全面及び規制面から見た諸問題を解決するために必要とされる専門的知識及び技術を持ち、かつ、お客様の製品について、またTI製品をそのような安全でないことが致命的となる用途に使用することについて、お客様が全ての法的責任、規制を遵守する責任、及び安全に関する要求事項を満足させる責任を負っていることを認め、かつそのことに同意します。さらに、もし万一、TIの製品がそのような安全でないことが致命的となる用途に使用されたことによって損害が発生し、TIないしその代表者がその損害を賠償した場合は、お客様がTIないしその代表者にその全額の補償をするものとします。

TI製品は、軍事的用途もしくは宇宙航空アプリケーションないし軍事的環境、航空宇宙環境にて使用されるようには設計もされていませんし、使用されることを意図されておりません。但し、当該TI製品が、軍需対応グレード品、若しくは「強化プラスティック」製品としてTIが特別に指定した製品である場合は除きます。TIが軍需対応グレード品として指定した製品のみが軍需品の仕様書に合致いたします。お客様は、TIが軍需対応グレード品として指定して収ない製品を、軍事的用途もしくは軍事的環境下で使用することは、もっぱらお客様の危険負担においてなされるということ、及び、お客様がもっぱら責任をもって、そのような使用に関して必要とされる全ての法的要求事項及び規制上の要求事項を満足させなければならないことを認め、かつ同意します。

TI製品は、自動車用アプリケーションないし自動車の環境において使用されるようには設計されていませんし、また使用されることを意図されておりません。但し、TIがISO/TS 16949の要求事項を満たしていると特別に指定したTI製品は除きます。お客様は、お客様が当該TI指定品以外のTI製品を自動車用アプリケーションに使用しても、TIは当該要求事項を満たしていなかったことについて、いかなる責任も負わないことを認め、かつ同意します。

Copyright © 2011, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社

### 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。 1. 熱電気

- 素手で半導体製品単体を触らないこと。どうしても触る必要がある場合は、リストストラップ等で人体からアースをとり、導電性手袋等をして取り扱うこと。

- 弊社出荷梱包単位(外装から取り出された内装及び個装)又は製品単品で取り扱いを行う場合は、接地された導電性のテーブル上で(導電性マットにアースをとったもの等)、アースをした作業者が行うこと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

- 前記のリストストラップ・導電性手袋・テーブル表面及び実装装置 類の接地等の静電気帯電防止措置は、常に管理されその機能が確認 されていること。

#### 2. 温·湿度環境

● 温度:0~40℃、相対湿度:40~85%で保管・輸送及び取り扱いを行うこと。(但し、結露しないこと。)

- 直射日光があたる状態で保管・輸送しないこと。

- 3. 防湿梱包

- 防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装すること。

#### 4. 機械的衝擊

● 梱包品(外装、内装、個装)及び製品単品を落下させたり、衝撃を 与えないこと。

#### 5. 熱衝撃

はんだ付け時は、最低限260℃以上の高温状態に、10秒以上さら さないこと。(個別推奨条件がある時はそれに従うこと。)

#### 6. 汚染

- はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。(不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。)

以上