# **LP5550,LP5551,LP5552**

Literature Number: JAJA411

# POWER | designer

*Expert tips, tricks, and techniques for powerful designs*

No. 118

特集記事 ..... 1-7

デジタル・プログラミング

可能なエナジー・マネジメント・

ユニット (EMU) ..... 2

使いやすいパワーマネジメント・

ユニット (PMU) ..... 4

DVSでデジタル・プロセッサの

パワーマネジメントを強化 ..... 6

電源回路設計ツール ..... 8

## スマート・パワーマネジメントによる省電力化

— Michael Drake, Applications Engineer

パワーマネジメントの技法が急速な広がりをみせています。政治や環境および消費者側からの圧力で、市場は機能強化と省電力化を同時に達成する必要に迫られています。とりわけポータブル・アプリケーションの成長は目覚しく、これを支える原動力がワイヤレス機器の普及とその周辺機器の拡充です。携帯電話、PDA、MP3プレーヤ、デジタルカメラ、携帯ゲーム機などは、小型化、高速化、高機能化の一途をたどっており、市場に対し許容レベルの「通話可能時間」(バッテリ寿命)を維持するため、電源サブシステムの設計には多くの努力が払われています。

携帯機器のバッテリ寿命に影響を与える2つの重要分野が、電力変換とシステム・エナジー・マネジメントです。電力変換はバッテリ電圧を必要な電源電圧に効率よく変換する役割を担い、システム・エナジー・マネジメントは、アプリケーションのリアルタイムな要求に合わせてシステム全体を最適化することでエネルギー節約をはかる方法です。

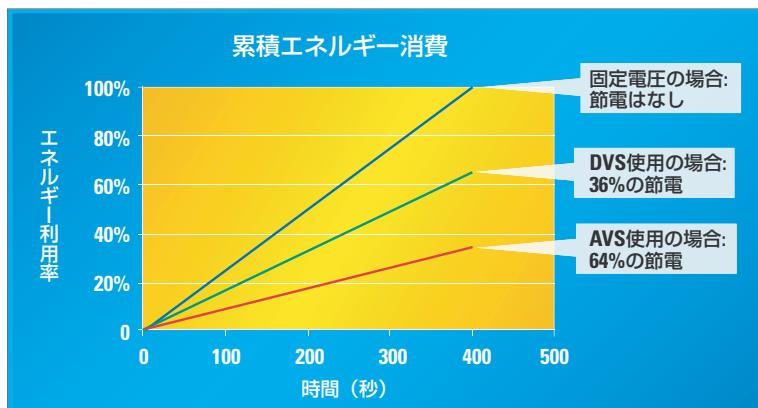

Figure 1. DVSやAVSを用いた節電

## レギュレーションの最適化による省エネ化

電力変換では、レギュレータの効率を最大限に引き出すことが課題になっています。レギュレータの効率は入力電力に対する出力電力の比率で表され、次式のパーセント値になります。

次号予告

携帯機器向けライティング

National

Semiconductor

*The Sight & Sound of Information*

# PowerWise®技術で消費電力を低減

デジタル・プログラミング機能を備えたLP5552エナジー・マネジメント・ユニット(EMU)は、バッテリ寿命延長と新機能搭載を実現します。

| 製品名               | 出力数 | 出力電圧と出力電流                                                                                                           | 入力電圧範囲    | インターフェース | パッケージ        |

|-------------------|-----|---------------------------------------------------------------------------------------------------------------------|-----------|----------|--------------|

| LP5550            | 4   | 降圧型 1個: 0.6V～1.2V、300mA<br>LDO 3個: 0.6V～3.3V、最大250mA                                                                | 3V～5.5V   | PWI 1.0  | LLP-16       |

| LP5551            | 8   | 降圧型 2個: 0.6V～1.2V、300mA<br>LDO 4個: 0.6V～3.3V、最大250mA<br>N-ウェル・バイアス: -0.3V～+1V (対電源)<br>P-ウェル・バイアス: -1V～+0.3V (対GND) | 2.7V～5.5V | PWI 1.0  | LLP-36       |

| <b>NEW</b> LP5552 | 7   | 降圧型 2個: 0.6V～1.235V、800mA<br>LDO 5個: 0.6V～3.3V、最大250mA                                                              | 2.7V～4.8V | PWI 2.0  | micro SMD-36 |

デュアル・コア・プロセッサ、携帯電話、携帯ラジオ、PDA、バッテリ駆動機器、ポータブル計器などに最適です。

LP5550、LP5551、LP5552の製品サンプル、データシートはホームページから入手できます。

[power.national.com/jpn](http://power.national.com/jpn)

## スマート・パワーマネジメントによる省電力化

$$\eta = P_{\text{OUT}} / P_{\text{IN}} = (V_{\text{OUT}} * I_{\text{OUT}}) / (V_{\text{IN}} * I_{\text{IN}})$$

電力変換効率はいまや90パーセントの域まで達していますが、それ以上の効率を得ることはなかなか困難です。変換効率が頭打ち状態なので、システムレベルで省エネをはかる新しい工夫が必要になっています。そのためにはエナジー・マネジメントの適応を検討する必要があります。

次の2つの式は、システム・エナジー・マネジメントを行う上で必要な式です。この式には、回路容量C、供給電圧 $V_{\text{DD}}$ およびクロック周波数fが関与する動的な要素があります。2項目は静的な要素があり、デジタル・ゲートのリーク電流に支配されます。大型の機器では動的な要素が電力利用率を支配しますが、機器の小型化と半導体プロセスの微細化により、静的な要素の重要性が増しています。

デジタル・システムでは、消費電力は次式で近似されます:

$$P = (C * V_{\text{DD}}^2 * f) + (V_{\text{DD}} * I_{\text{LEAK}})$$

従って、消費エネルギーの近似は次式で求められます。

$$E = (C * V_{\text{DD}}^2) + ((V_{\text{DD}} * I_{\text{LEAK}}) * t)$$

### 設計向上のためのさまざまな技術

大型のデジタル・システムのほとんどは、不要なクロックのトグルを回避するためのクロック・ゲーティング手段を1つまたは複数採用しており、また、多くのシステムでは、不使用のセクションができるだけパワーダウンさせる方式を用いています。プロセッシング・エンジンの場合も、アイドル・モードやスリープ・モードによる節電を採用していますが、この方法は在来型のエナジー・マネジメント技術であり、プロセッサが周期的に動作するか、使用しない場合は待ち状態とし必要に応じて動作を実行した後で低消費電力状態に戻します。これらの技術は省電力化に対し効果的ですが、設計コストが高くなるという代償を伴います。回路が待ち状態から動作を実行する度に、パワーアップや同期の際に若干の遅延が生じます。これらの方は、何も実行しない時（すなわち、プロセッサがスリープ状態にある時）にだけ節電を行うこととなります。

最近の新しい技術では、プロセッシング・エンジンの周波数や電圧の調整によって省エネを達成します。バッテリ駆動システムの場合、オン時間増加にとってキーポイントとなるのがエネルギー消費です。単に周波数を下げるだけで平均消費電力は低減しますが、ある特定の演算タスクを完了するのに必要な総エネルギー量は減りません。省エネをはかるには、システム内の供給電圧を下げる必要があります。ダイナミック・ボルテージ・スケーリング (DVS) やアダプティブ・ボルテージ・スケーリング (AVS) を用いると、このシステム内の電圧を低減できます。(Figure 1のDVSやAVSを用いた節電を参照)

DVSでは、各周波数に対応した電圧を予め設定し、その組み合わせ値を基にして調整します。ナショナルは、DVSモードをサポートするLP3906やLP3907、AVSとDVS両モードをサポートするLP5550、LP5551、LP5552といったパワーマネジメントIC(PMIC)を提供しています。DVSは、使用されるあらゆるシステムのプロセスや温度変動の全範囲を考慮する必要があり、予め設定される電圧に若干の余裕を持たせる必要があります。したがってある程度の電力およびエネルギーの節約を提供しますが、ワーストケースを考慮したこの余力は、非理想的なシステムでは余分なエネルギーの浪費になります。システムレベルで電源ループを閉ループにすることが可能であれば、制御ループを用いて電圧を必要最低限の電圧にまでアダプティブにスケーリングすることで、DVSでの余分なエネルギー消費を含めた大半のエネルギーを節約できます。PowerWise®技術はそれが可能です。

### スマートなエナジー・マネジメントを実現する PowerWiseインタフェース (PWI®)

PowerWise仕様は、AVSやバッテリ駆動機器のステータス制御を可能にする、システム・レベルのエナジー・マネジメント方式です。PowerWise方式では、システム内でプロセッシング・エンジンが常にどんな動作周波数の時でも必要最低限の電圧を使えるようにする、高速シリアル・パワーマネジメント・バス付きの閉ループAVSを採用しており、これによって動的なエネルギー消費低減を可能にします。

# デジタル・サブシステムに最適 使いやすさに優れたパワーマネジメント・ユニット (PMU)

96%の高効率を持つLP3906は、デジタル・プログラム機能により

フレキシビリティを向上します。

## LP3906の特長

- コアおよびその他の大電流レールをサポートする2個のプログラム可能な降圧型レギュレータ

- 内部のプロセッサ機能および周辺ユニットへの補助電圧をそれぞれ供給する2個のプログラム可能なLDO

- LP3906および周辺機能を個別に制御するI<sup>2</sup>C

サイズや効率が重視されるアプリケーション・プロセッサ、FPGA、DSPなどの電源に最適です。

| 製品名    | デジタル・<br>プログラム機能 | 最大効率 | レギュレータ<br>出力電流 | LDO出力電流       | パッケージ  | ソリューション・<br>サイズ |

|--------|------------------|------|----------------|---------------|--------|-----------------|

| LP3906 | I <sup>2</sup> C | 96%  | 1.5 A          | 300 mA        | LLP-24 | 20 mm x 20 mm   |

| LP3905 | N/A              | 90%  | 600 mA         | 150 mA (低ノイズ) | LLP-14 | 15 mm x 10 mm   |

LP3906の製品サンプル、データシートは

ホームページから入手できます。

[power.national.com/jpn](http://power.national.com/jpn)

## スマート・パワーマネジメントによる省電力化

PowerWise技術は、プロセッシング・エンジンのトランジスタのウェル電圧に対するバイアス機能も備えています。動的な損失を最小に抑えるため $V_{DD}$ を下げる所以、高い駆動レベルを維持するにはトランジスタのスレッショルド電圧も下げる必要があります。このため、リーク電流と静的な電力損失が増えます。このリーク電流は、ウェルにバック・バイアスをかけることで低減できます。また、順方向バイアスをかけることによって、 $V_{DD}$ が同じまま駆動レベルを上げる方法も可能です。PowerWiseループ & ウェル・バイアス方式は、マルチ $V_T$ 設計と組み合わせて使用できます。

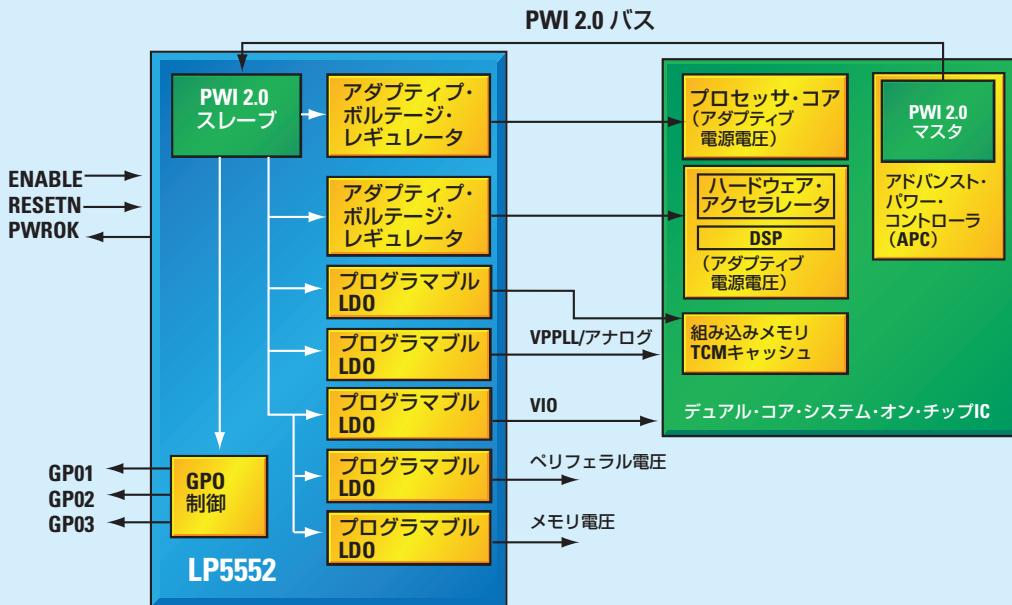

PowerWise閉ループAVSを使用できる環境として標準的なシステム構成は、プロセッシング・エンジンに内蔵されるアドバンスト・パワー・コントローラ（APC）、PWIスレーブ付きのPMIC、2つの部品間接続に使用される2線式PWIシリアル・バスからなっています。PMICは、プロセッサに様々な電圧を供給します。PMICからの供給電圧レベルは、APC内のPWIマスターからPWIスレーブにコマンドが送られることで調整されます。

APCは、ホスト・プロセッサからコマンドを受け取り、CPUから独立した電圧制御メカニズムを用いてロジック動作速度をリアルタイムで監視する役割を担います。APCは常にアクティブ状態にあり、全パラメータにわたってシステムを連続的に監視します。特にシステム温度や負荷、過渡、プロセス変動は重要で、これらをすべて監視します。APCは周波数変化を検知すると、その周波数に対応したシステム動作を確保できる必要最低限の電圧を決定します。この操作は閉ループ内で行われ、PWIインターフェースを介してAPCからPWIスレーブに電圧調整コマンドを送って、電圧を適切なレベルにサーボ制御します。

### さまざまな電力課題に対応するための各種オプション

PowerWise AVS技術では、2種のAPCバージョンを使用できます。APC1は単純な単一電圧ドメイン設計に、APC2は複雑なマルチドメイン・システムにそれぞれ適しています。APC1はポイント・ツー・ポイントPWI 1.0インターフェースを用い、APC2はマスター/スレーブ間にPWI 2.0バス・インターフェースを使用します。

ナショナルは、APC1用のエナジー・マネジメント・ユニット（EMU）としてLP5550、LP5551の両デバイスを提供しています。LP5550は、AVS DC/DCスイッチャ1個とLDO3個を内蔵しています。LP5551はそれに加えて、DVS型のDC/DCスイッチャ1個、追加のLDO1個と、スレッショルド・スケーリング・アプリケーションでのN-ウェル/P-ウェルに対するバイアス・レギュレータを内蔵しています。

LP5552 EMUは、APC2/PWI 2.0 IPパッケージとの互換性を持ったデバイスです。LP5552は、AVSまたはDVSアプリケーション向けの高性能スイッチング・レギュレータ2個とLDO5個を内蔵しており、7個のレギュレータはすべて、小型の36ピンmicro SMDパッケージに収納されています。各レギュレータは、ターンオン/ターンオフを独立して行えるほか、所望の電圧へのプログラミングが可能です。

### 高いスイッチング周波数により、消費電力低減と回路の小型化を実現

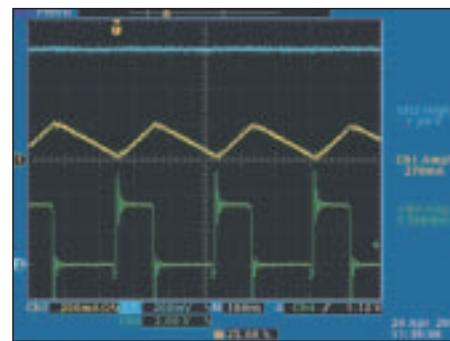

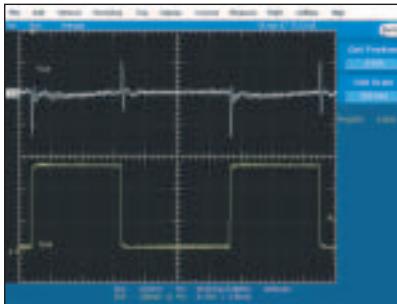

Figure 2.  $V_{IN} = 3.6V$ 、 $V_{OUT} = 1.235V$ 、 $I_{LOAD} = 400mA$ の負荷時のスイッチャ出力

LP5552に内蔵されたスイッチング・レギュレータは、3.6MHzのスイッチング周波数で動作します（Figure 2を参照）。スイッチング周波数が高いので、出力フィルタに小さい定数の部品を使用できます。代表値は、インダクタが $1\mu H$ 、セラミック・コンデンサが $10\mu F$ です。これらの定数が小さいので、高速な過渡特性を維持しながら、実装面積が少なく薄い部品を使用できます。

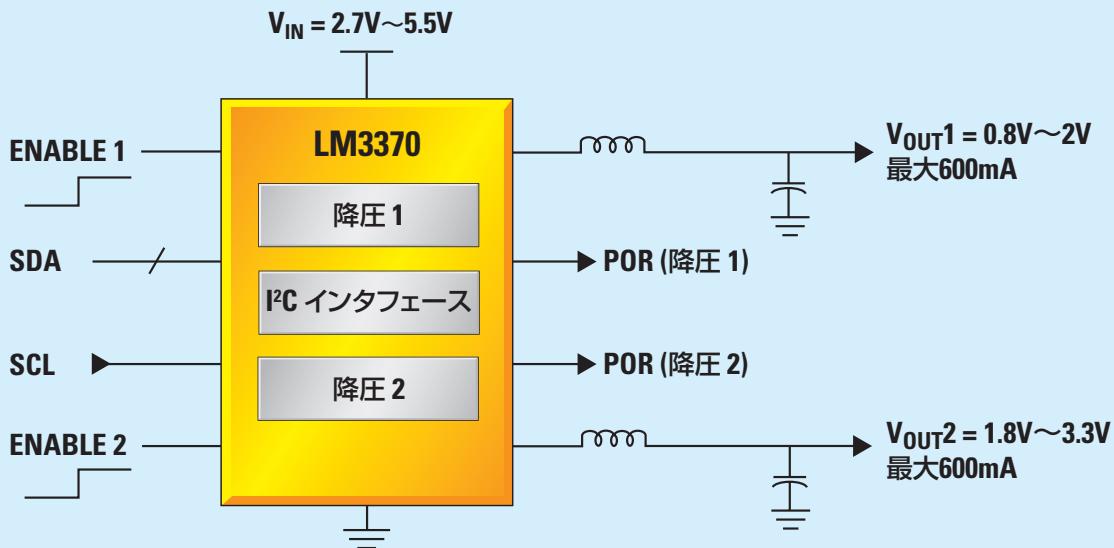

# ダイナミック・ボルテージ・スケーリング (DVS) により デジタル・プロセッサのパワーマネジメントをさらに強化

LM3370デュアル降圧型レギュレータはFPGAやマルチメディア・プロセッサ用電源として最高の効率を提供します。

## LM3370の特長

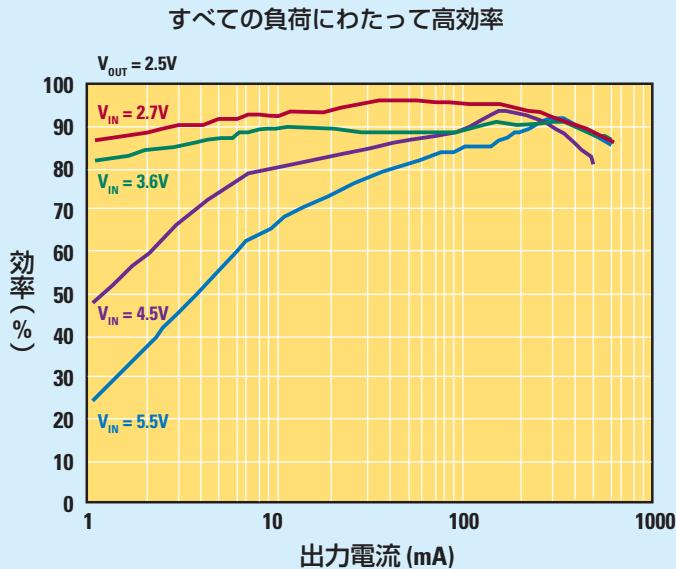

- すべての負荷において高効率を提供する、自動PFM/PWMモード・スイッチング

- プロセッサのクロック周波数に適した電圧スケーリングのためのI<sup>2</sup>C対応インターフェース

- バッテリ寿命を延長する、極めて低い自己消費電流 ( $<20\mu A$ )

- 外付け部品の小型化と実装面積の最小化を可能にする2MHzのスイッチング動作

- プロセッサの誤動作防止のためのパワーオン・リセット機能

- 拡散スペクトル機能によるノイズ低減 (RFシステムに最適)

低電力のFPGA、CPLD、アプリケーション・プロセッサなどに最適です。

LM3370の製品サンプル、評価ボード、データシート

およびオンライン設計ツールは、ホームページから入手できます。

[power.national.com/jpn](http://power.national.com/jpn)

## スマート・パワーマネジメントによる省電力化

Figure 3は、このスイッチャの過渡特性です。電源システム全体は高さが0.85 mmを切る薄さに作られており、製品設計において低背の実装が可能です。

Figure 3. 出力電流が $50\text{mA} \rightarrow 560\text{mA} \rightarrow 50\text{mA}$ と変化する時の負荷過渡特性 =  $300\text{mA}/\mu\text{s}$

### 主な特長

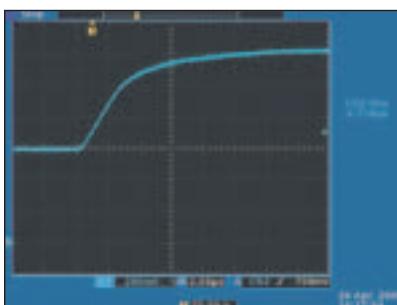

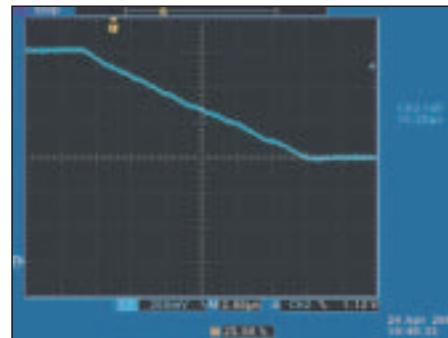

このスイッチャは、最大800mAのDC電流で動作可能で、ピーク効率は88%に達します。出力電圧は、0.6V～1.235Vの範囲内で5mV刻みでデジタル・プログラミングできます。Figure 4とFigure 5は、最小0.6V、最大1.235Vにプログラミングした出力電圧のセトリング時間です。また、各スイッチャはそれぞれが固定電圧のLDO1個と連携しており、このLDOは、電圧スケーリング・アプリケーションでスイッチャの電圧追従のためのプログラミングが可能なほか、独立した50mA LDOとしても使えます。この2つのLDO（固定電圧）は、0.6V～1.35Vの範囲内で50mV刻みでプログラミングできます。

残りの3つのLDOは、別の領域への給電用に使用され、設計時のフレキシビリティを提供します。このうち2つは300mA出力LDOで、LP5552自身へのI/O電圧環境の設定用とシステム側への電圧供給が可能です。

Figure 4. 無負荷時の最小 $V_{\text{OUT}}$ →最大 $V_{\text{OUT}}$ のセトリング時間

Figure 5. 無負荷時の最大 $V_{\text{OUT}}$ →最小 $V_{\text{OUT}}$ のセトリング時間

残り1つのLDOは、PLL機能やアナログ機能への給電に使用され、連続出力電流100mAの性能を持っています。これらのLDOもすべて、デジタル・プログラミングが可能です。

LP5552は、ターゲット・システムへのシームレスな組み込みを可能にする付加的な信号を多く持っています。ENABLE/RESETN信号は、システム内における電源シーケンシング、レジスタ・スペース・リセットおよびグローバル・パワーオン/オフに用いられます。PWROK信号は、電源シーケンシングやパワーオン・リセット生成に使用できるインジケータです。LP5552はさらに、システム内で追加のデジタル・ドライバとして自由に使えるGPO（汎用出力）3つを備えており、これらはオープンドレイン出力またはLP5552 のI/O電圧を基準とするプッシュプル出力としてプログラミングできます。

LP5552は、システム設計の大幅な簡素化、コストの最小化、PCBスペースの低減を実現し、ポータブル電力システムの大半のニーズを満たせる非常に高密度のパッケージ製品です。閉ループAVS内で動作するPWI 2.0マスターと併用すると、携帯機器で極めて大きい省エネ効果を発揮します。また、閉ループDVSアプリケーションにも利用でき、APCを使わずに、プロセッシング・エンジン上でPWIをGPIO（汎用入出力）からビット・バンジング（bit-bang）モードで使用することができます。PWI仕様は、[www.pwistandard.org](http://www.pwistandard.org)から無償でダウンロードできます。PowerWise技術を含むナショナルのパワー・マネジメント・ソリューションについては、[power.national.com/jpn](http://power.national.com/jpn)をご覧ください。■

# 電源回路設計ツール

## オンライン・セミナー

オンライン・セミナー「FPGAへの電源供給:設計課題、ICソリューション、ツール類」をご覧ください。

[www.national.com/JPN/onlineseminar](http://www.national.com/JPN/onlineseminar)

## Analog Edge/ アプリケーション・ノート

月刊のAnalog Edgeに掲載されるアプリケーション・ノートをご覧ください。

[edge.national.com/jpn](http://edge.national.com/jpn)

## リファレンス・デザイン

ナショナルの電源設計専用のリファレンス・デザイン・ライブラリは、システム設計を迅速化し、製品の市場投入までの期間を短縮する実用的なリファレンス・デザインの総合的なライブラリを提供します。

[www.national.com/JPN/Reference\\_Designs](http://www.national.com/JPN/Reference_Designs)

ナショナルの

パワー製品サイト:

[power.national.com/jpn](http://power.national.com/jpn)

お問い合わせ:

[JPN.Feedback@nsc.com](mailto:JPN.Feedback@nsc.com)

## どの号もお見逃しなく！

Power Designerのバックナンバーは

ナショナルのサイトでご覧いただけます。

[power.national.com/jpndesigner](http://power.national.com/jpndesigner)

Signal Path Designerもオンラインで

提供しています。ぜひお読みください。

[signalpath.national.com/jpndesigner](http://signalpath.national.com/jpndesigner)

ナショナル セミコンダクター ジャパン株式会社

〒135-0042 東京都江東区木場2-17-16

TEL 03-5639-7300 (大代表) [www.national.com/jpn/](http://www.national.com/jpn/)

The Sight & Sound of Information

©2007, National Semiconductor Corporation. National Semiconductor, **N**, PowerWise, PWI, and Signal Path Designer are registered trademarks and Analog Edge is a service mark of National Semiconductor. All other brand or product names are trademarks or registered trademarks of their respective holders. All rights reserved.

550263-018-JP

# ご注意

日本テキサス・インスツルメンツ株式会社（以下TIJといいます）及びTexas Instruments Incorporated（TIJの親会社、以下TIJないしTexas Instruments Incorporatedを総称してTIといいます）は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIJとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIJの標準販売契約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIJとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。TI製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI製部品を使用したお客様の製品及びアプリケーションについて想定される危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明しておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならぬ場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、かつその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの默示的保証を無効にし、かつ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任も負いません。

TIは、TIの製品が、安全でないことが致命的となる用途ないしアプリケーション（例えば、生命維持装置のように、TI製品に不良があった場合に、その不良により相当な確率で死傷等の重篤な事故が発生するようなもの）に使用されることを認めておりません。但し、お客様とTIの双方の権限有る役員が書面でそのような使用について明確に合意した場合は除きます。たとえTIがアプリケーションに関連した情報やサポートを提供したとしても、お客様は、そのようなアプリケーションの安全面及び規制面から見た諸問題を解決するために必要とされる専門的知識及び技術を持ち、かつ、お客様の製品について、またTI製品をそのような安全でないことが致命的となる用途に使用することについて、お客様が全ての法的責任、規制を遵守する責任、及び安全に関する要求事項を満足させる責任を負っていることを認め、かつそのことに同意します。さらに、もし万一、TIの製品がそのような安全でないことが致命的となる用途に使用されたことによって損害が発生し、TIないしその代表者がその損害を賠償した場合は、お客様がTIないしその代表者にその全額の補償をするものとします。

TI製品は、軍事的用途もしくは宇宙航空アプリケーションないし軍事的環境、航空宇宙環境にて使用されるようには設計もされていませんし、使用されることを意図されておりません。但し、当該TI製品が、軍需対応グレード品、若しくは「強化プラスティック」製品としてTIが特別に指定した製品である場合は除きます。TIが軍需対応グレード品として指定した製品のみが軍需品の仕様書に合致いたします。お客様は、TIが軍需対応グレード品として指定していない製品を、軍事的用途もしくは軍事的環境下で使用することは、もっぱらお客様の危険負担においてなされるということ、及び、お客様がもっぱら責任をもって、そのような使用に関して必要とされる全ての法的要件及び規制上の要求事項を満足させなければならないことを認め、かつ同意します。

TI製品は、自動車用アプリケーションないし自動車の環境において使用されるようには設計もされていませんし、また使用されることを意図されておりません。但し、TIがISO/TS 16949の要求事項を満たしていると特別に指定したTI製品は除きます。お客様は、お客様が当該TI指定品以外のTI製品を自動車用アプリケーションに使用しても、TIは当該要求事項を満たしていなかったことについて、いかなる責任も負わないことを認め、かつ同意します。

Copyright © 2011, Texas Instruments Incorporated

日本語版 日本テキサス・インスツルメンツ株式会社

## 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。

### 1. 静電気

- 素手で半導体製品単体を触らないこと。どうしても触る必要がある場合は、リストストラップ等で人体からアースをとり、導電性手袋等をして取り扱うこと。

- 弊社出荷梱包単位（外装から取り出された内装及び個装）又は製品単品で取り扱いを行う場合は、接地された導電性のテーブル上で（導電性マットにアースをとったもの等）、アースをした作業者が行うこと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

- 前記のリストストラップ・導電性手袋・テーブル表面及び実装装置類の接地等の静電気帯電防止措置は、常に管理されその機能が確認されていること。

### 2. 溫・湿度環境

- 温度：0～40°C、相対湿度：40～85%で保管・輸送及び取り扱いを行うこと。（但し、結露しないこと。）

- 直射日光があたる状態で保管・輸送しないこと。

### 3. 防湿梱包

- 防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装すること。

### 4. 機械的衝撃

- 梱包品（外装、内装、個装）及び製品単品を落下させたり、衝撃を与えないこと。

### 5. 熱衝撃

- はんだ付け時は、最低限260°C以上の高温状態に、10秒以上さらさないこと。（個別推奨条件がある時はそれに従うこと。）

### 6. 汚染

- はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質（硫黄、塩素等ハロゲン）のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。（不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。）

以上