**DS15BA101,DS15EA101,DS25BR110**

Literature Number: JAJA430

# SIGNAL PATH *designer*

*Tips, tricks, and techniques from the analog signal-path experts*

No. 110

|                      |     |

|----------------------|-----|

| 特集記事 .....           | 1-7 |

| LVDSバッファ .....       | 2   |

| 高速差動アンプおよびADC .....  | 4   |

| ビデオ・ケーブル・イコライザ ..... | 6   |

| 設計支援ツール .....        | 8   |

## データ伝送ラインにおけるシグナルパスの延長

— Lee Sledjeski, Applications Engineer

大抵のRF信号は、A/Dコンバータ（ADC）でデジタル変換した後、追加処理のためにバックプレーンやケーブルを通じてFPGAに転送する必要があります。サンプリング速度はますます上がり続けており、ビット・エラーなしでこの信号の駆動距離を数十cm延長するのは容易ではありません。本稿では、FR-4配線やケーブル上での高速シグナルパスの伝送距離延長問題を解決する方法を紹介します。

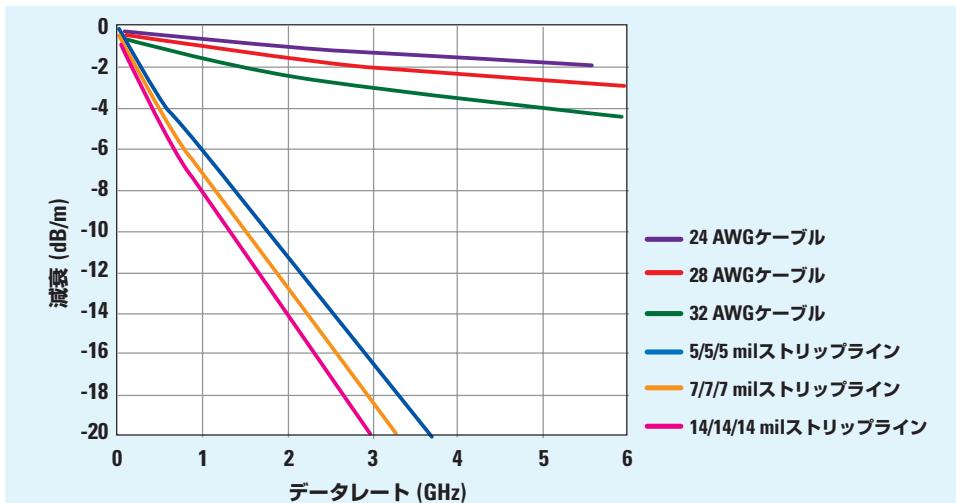

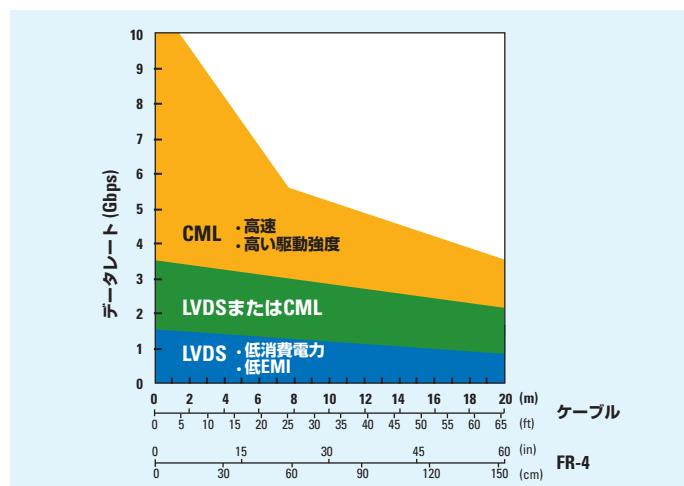

Figure 1. 伝送媒体損失（差動伝送時）はローパス・フィルタからの影響が原因

この高速信号問題を、Figure 1に示されるグラフを例にとって説明します。2.5Gbps NRZ信号が1ビット・サイクル進むごとに、1.25GHzクロック信号と等価な成分が生成されます。2.5Gbps信号のこの成分は、長さ1mの100Ω差動FR-4ストリップラインを通過した後、最大10dBまでの損失を生じさせます。二芯同軸ケーブルの場合、伝送距離が最短10mでこれと同様の損失が発生します。この伝送損失は、やがて信号「アイ」またはサンプリング・ウインドウを閉じてしまうほどのジッタを発生します（Figure 2aを参照）。

高速信号の場合、伝送媒体はローパス・フィルタ（Figure 1を参照）に相当します。ここを減衰量3dB未満で通過する信号周波数の最高値がフィルタ帯域幅を規定します。この帯域幅以内の信号成分は、最小の減衰量でフィルタを通過します。さらに、-3dBポイントまたは伝送ラインの帶

# 「LVDS」 + 「シグナル・コンディショニング」機能により シグナル・インテグリティの問題をすべて解決

ナショナルの3.125Gbps LVDSバッファはプリエンファシス機能とイコライザ機能を集積しました。

## DS25BR100/110/120/150の特長

- ・ジッタ代表値: 17ps (2.5 Gbps、2<sup>23</sup>-1パターン)

- ・プログラマブル・プリエンファシス/イコライザ機能を搭載

- ・幅広い入力レンジでLVDS/CML/LVPECLに対応

- ・100Ω入出力終端抵抗を集積

- ・7kV耐量ESD保護のLVDSピンを装備

シグナル・コンディショニング

| 製品名       | LVDS<br>バッファ<br>機能 | 入力<br>チャネル | 出力<br>チャネル | 入力互換性           | 出力   | プリエン<br>ファシス (dB) | レシーバ・<br>イコライゼー<br>ション (dB) | チャネルあたり<br>最大速度<br>(Mbps) | パッケージ              | 備考             |

|-----------|--------------------|------------|------------|-----------------|------|-------------------|-----------------------------|---------------------------|--------------------|----------------|

| DS25BR100 | シングル               | 1          | 1          | LVDS/LVPECL/CML | LVDS | 0/6               | 3/6                         | 3125                      | LLP-8              | 内部終端、8 kV ESD  |

| DS25BR110 | シングル               | 1          | 1          | LVDS/LVPECL/CML | LVDS | —                 | 0/3/6/9                     | 3125                      | LLP-8              | 内部終端、8 kV ESD  |

| DS25BR120 | シングル               | 1          | 1          | LVDS/LVPECL/CML | LVDS | 0/3/6/9           | —                           | 3125                      | LLP-8              | 内部終端、8 kV ESD  |

| DS90LV804 | クワッド               | 4          | 4          | LVDS/LVPECL/CML | LVDS | —                 | —                           | 800                       | LLP-32             | 内部終端、15 kV ESD |

| DS90LV004 | クワッド               | 4          | 4          | LVDS/LVPECL/CML | LVDS | 0/2/4/6           | —                           | 1500                      | TQFP-48            | 内部終端、15 kV ESD |

| DS15BR400 | クワッド               | 4          | 4          | LVDS/LVPECL/CML | LVDS | 0/6               | —                           | 2000                      | LLP-32,<br>TQFP-48 | 内部終端、15 kV ESD |

| DS15BR401 | クワッド               | 4          | 4          | LVDS/LVPECL/CML | LVDS | 0/6               | —                           | 2000                      | LLP-32,<br>TQFP-48 | 15 kV ESD      |

ルータ、スイッチ、ストレージ、医療画像処理、ビデオ・セキュリティ、イメージ・キャプチャ/プロセッシングなどに最適です。

DS25BR100/110/120/150の製品サンプル、データシートはホームページから入手できます。

[lvds.national.com/jpn](http://lvds.national.com/jpn)

## データ伝送ラインにおけるシグナルパスの延長

域幅を超える信号成分および高調波は、このフィルタ通過時に振幅が減衰します。この非線形の周波数依存性損失から、シンボル間干渉 (ISI) に起因するデータ依存性ジッタ (DDJ) が発生します。このため、シグナル・コンディショニングでは、高周波伝送損失の影響を軽減するための補償技術が欠かせません。入出力信号のコンディショニングは、伝送特性を向上させ、シグナルパスの伝送距離延長を可能にします。

### 入出力信号のシグナル・コンディショニング

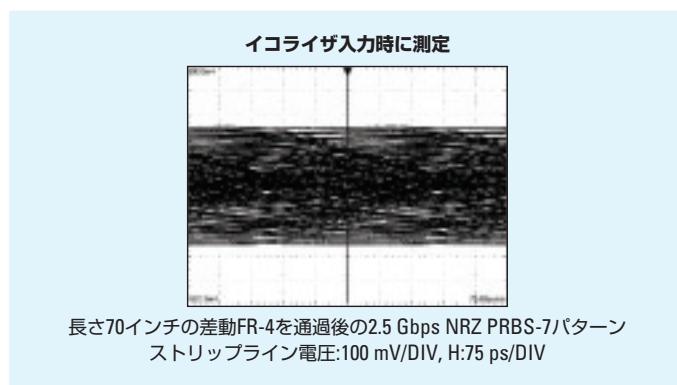

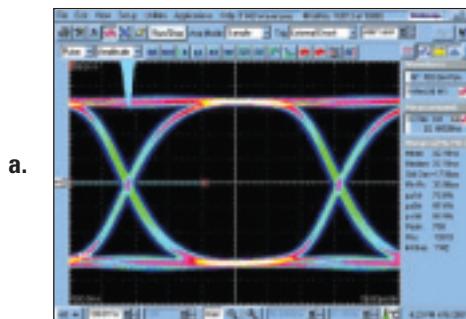

Figure 2a. 長さ70インチのFR-4通過後の2.5Gbps NRZ信号

— 非イコライズ時

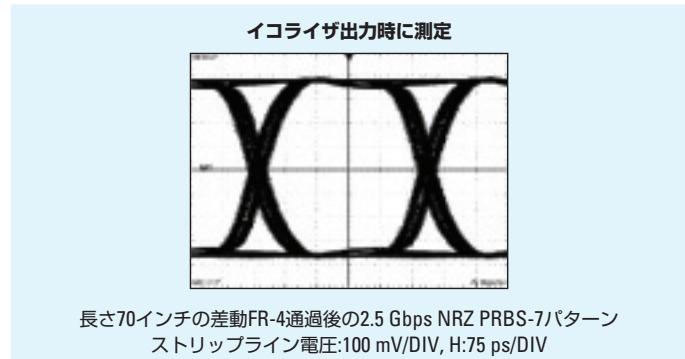

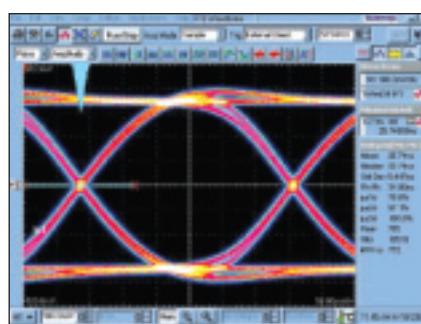

シグナル・インテグリティ (信号の整合性) の設計では、入力信号のコンディショニングにイコライザを用います。イコライザ回路の目的は、システムの周波数応答を「平坦化」して信号の歪みや「スミヤリング」を低減することで、伝送時の信号損失を抑えることがあります。イコライザはハイパス・フィルタとして機能し、伝送時の周波数応答を平坦化することによって、信号の周波数帯域幅内でローパス・フィルタの影響をほぼ相殺します。経験則によれば、イコライゼーション (EQ) では、極力高い伝送密度を持ったデータ・パターンでつくるられる周波数までに対して、周波数応答を平坦化する必要があります。たとえば1-0-1-0 NRZ パターンでの2.5Gbps信号の場合、最大2.5GHzまでの周波数に対して平坦な周波数応答を必要とします (Figure 1を参照)。適切に調整すれば、EQによって伝送媒体からの ISI の影響を大幅に低減できます (Figure 2bを参照)。長さ29.5インチのストリップライン上でさえ、2.5Gbps時の減衰量は-6dBに近づきます。伝送リンクで信頼性の高いデータ伝送を行うには、何らかのEQが必要といえます。

Figure 2b. 長さ70インチのFR-4通過後の2.5Gbps NRZ信号

— イコライズ時 (b)

ナショナルのDS25BR110のような高速デバイスは、伝送媒体に起因する周波数依存性損失の影響を低減するためのレシーバ入力EQ回路を内蔵しています (Figure 2を参照)。減衰範囲が0dB～16dBの4レベルEQ制御を用いれば、通常の伝送路の長さで、広いレンジにわたって容易に信号品質を最適化できます。

トランスマッタ出力信号のコンディショニングは、伝送路全体にわたってEQと同様な効果を發揮します。入力EQは、周波数依存性損失を除去する役割をします。これに対し出力プリエンファシス (PE) は、ドライバに接続された伝送媒体に起因する信号減衰を想定して、クリーンな減衰しない信号が確保されるよう周波数コンテンツを変更します。この結果、伝送ラインの遠端部にあるレシーバではクリーンな信号が得られます。出力波形へのPE適用によって、信号内の最も高い周波数成分がドライブ側デバイスで強調されます。データレートが高速化するほどシグナル・コンディショニングの必要性が増し、このため高速デバイスでは、通常の大半のPCBや銅ケーブルの伝送距離でレシーバ側のシグナル・インテグリティを最適化するために、0dBから9dBまでの複数のレベルを選択できるようになっています (Figure 3を参照)。

### プリエンファシスとイコライゼーションの設定

シグナル・コンディショニングは、ローパス・フィルタからの影響を補償するように設計します。まず、設定レベルを問題となる一次周波数で発生する伝送ラインの損失にマッチさせるよう調整し、そして1レベルごとに増減させて、受信波形のアイ・パターンの質を最適化します。シグナル・コンディショニングでは通常、問題となる一次周波

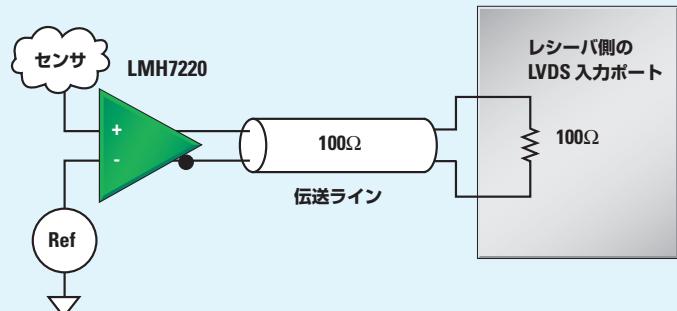

# LVDS出力機能を内蔵した 高速コンパレータと高帯域幅A/Dコンバータ

ナショナルは高いIF周波数のサンプリング・システム向けに

最適な低消費電力コンパレータとADC製品を提供しています。

## LMH7220の特長

- ・伝搬遅延時間: 2.9ns (100mVオーバードライブ時)

- ・立ち上がり/立ち下がり時間: 0.6ns

- ・入力電源電圧範囲: 2.7V ~ 12V

- ・消費電流: 6.8mA

- ・動作温度範囲: -40°C ~ 125°C

- ・LVDS出力

- ・TSOT-6 パッケージ

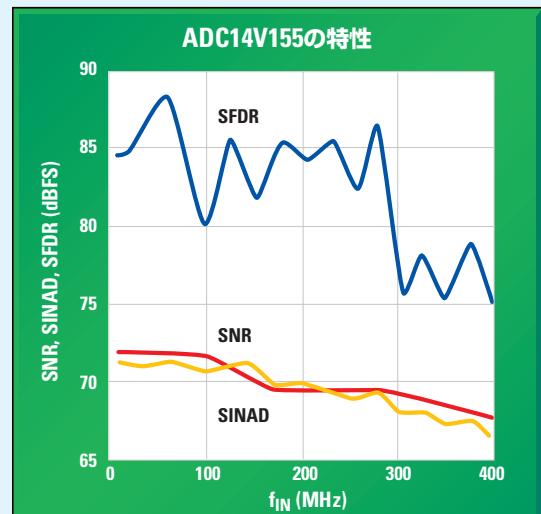

## ADC12V170/ADC14V155の特長

- ・フルパワー入力帯域幅: 1.1GHz

- ・デュアル電源電圧: 3.3Vと1.8V

- ・デュアル・データレート (DDR) パラレルLVDS出力

- ・ADC12C170とADC14V155はCMOS出力ではピン互換

- ・クロック・デューティ・サイクル・スタビライザ

- ・内部サンプル/ホールド (S/H) 回路

- ・内部高精度1.0V基準電圧源

- ・LLP-48/パッケージ (7 x 7 x 0.8mm)

| 製品名       | 分解能 (ビット) | 速度 (MSPS) | 出力形式        | 消費電力 (mW) | SNR (dB) | SFDR (dB) | パッケージ  |

|-----------|-----------|-----------|-------------|-----------|----------|-----------|--------|

| ADC14V155 | 14        | 155       | DDRパラレルLVDS | 951       | 71.7     | 86.9      | LLP-48 |

| ADC12V170 | 12        | 170       | DDRパラレルLVDS | 781       | 67.2     | 85.8      | LLP-48 |

| ADC14V155 | 14        | 155       | CMOS        | 967       | 71.3     | 87.0      | LLP-48 |

| ADC12C170 | 12        | 170       | CMOS        | 715       | 67.2     | 85.4      | LLP-48 |

LMH7220およびADC14V155、ADC12V170、ADC14V155、ADC12C170の

製品サンプル、データシートはホームページから入手できます。

[signalpath.national.com/jpn](http://signalpath.national.com/jpn)

## データ伝送ラインにおけるシグナルパスの延長

a.

DS25BR120のプリエンファシス: OFF

PRBS7パターンで3.125 Gbps

出力負荷: 4インチFR-4 100Ω差動パターン

b.

DS25BR120のプリエンファシス: ON (6dB設定)

PRBS7パターンで3.125 Gbps

出力負荷: 20インチFR-4 100Ω差動パターン

**Figure 3.** プリエンファシスした長さ4インチのFR-4通過後の3.125Gbps LVDS出力 (a) とプリエンファシスしない長さ20インチのFR-4通過後の3.125Gbps LVDS出力 (b)

数はデータレートの1/2です（たとえば2.5Gbps信号では $2.5 \div 2 = 1.25$ GHz、1Gbps信号では500MHzになります）。これは、データ・パターンで減衰量が最高レベルになる周波数です。ネットワーク・アナライザは、Figure 1のような伝送損失のグラフを得るために最も簡単な手段です。ネットワーク・アナライザを使えない場合は、伝送ライン上で正弦波を問題となる一次周波数で送信し、この時の減衰量を伝送損失値とみなすことができます。

入力EQ、出力シグナル・コンディショニング、または両者の組み合わせを用いて、損失が発生しがちな伝送ラインの補償を行うことができます。いずれも一長一短があり、どれを採用するかはアプリケーションや個人的好みによります。出力PEは、測定が簡単なのが長所です。この効果はレシーバ側で視認でき、監視や調整も容易です。

レシーバEQは、伝送ラインに余分なエネルギーを加えないため、クロストークの影響を受けやすい低電力アプリケーションに使用されます。EQのみまたはPEのみでは不十分な、損失が非常に発生しやすいアプリケーションでは、入力と出力双方のシグナル・コンディショニングを組み合わせて使用する必要があるでしょう。たとえば、9dBのPEを9dBのレシーバEQと組み合わせるといった方法があります。

### LVDS、CMLのいずれを選択すべきか？

ディスクリートLVDS方式は、データレートが3Gbpsを超える場合に効果的です。CML（カレント・モード・ロジック）方式は、伝送速度が3.5Gbps (Figure 4を参照) 以上の場合に有効なI/Oです。LVDSは総じて、低消費電力かつ低EMIの周到に定義されたインターフェース標準です。CMLはLVDSと比べて、伝送速度がより高速で、一般的により高い駆動強度を持っています。どちらの方式も、大抵は1Gbpsから3.125Gbpsのデータレートに使用できます。したがって、最適なシグナル・インテグリティを得るためにどちらの変換方式を用いるかが重要です。

**Figure 4.** LVDSとCMLの代表的なアプリケーション

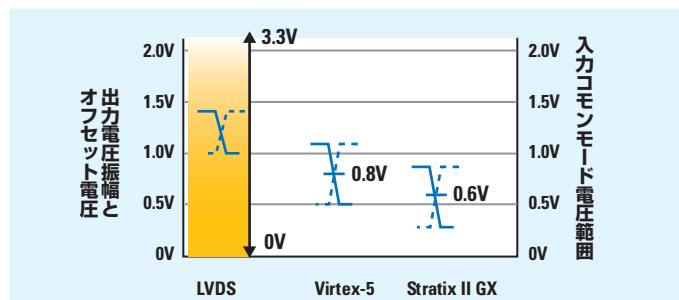

レベル変換を正しく行うには、ドライバの差動出力電圧 ( $V_{OD}$ ) とコモンモード電圧 ( $V_{CM}$ ) の値はレシーバの入力電圧範囲内に収まらなければなりません。LVDSの場合、 $V_{OD}$  (EIA/TIA-644A標準の定義に準拠) は100Ω抵抗性負荷を接続したドライバ出力の電圧です。他の差動標準の場合は、出力電圧振幅をピーク・ツー・ピーク

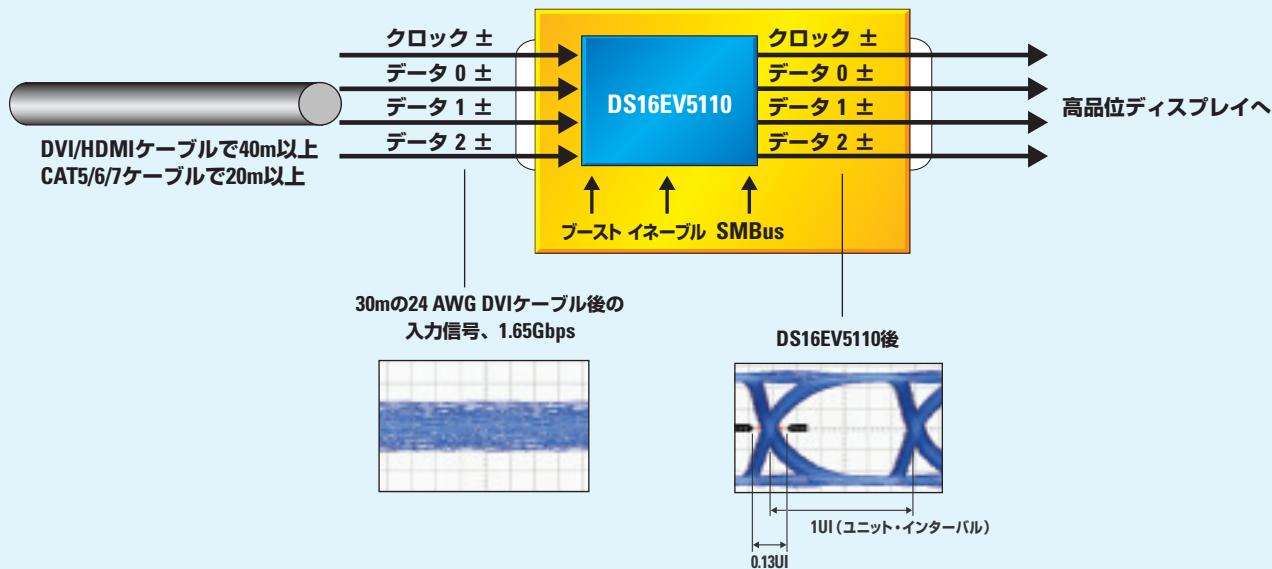

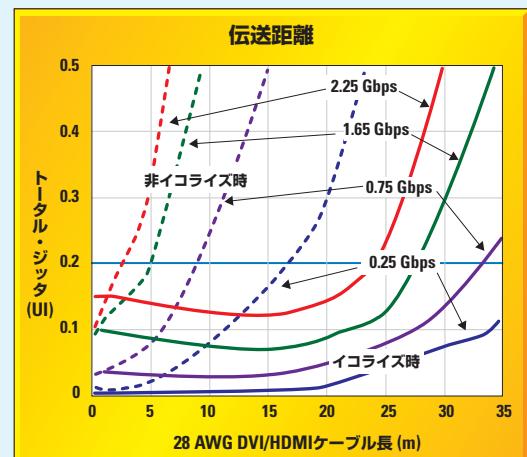

# 30mの24AWG DVIケーブル上で0.13UI 超低ジッタのビデオ・ケーブル・イコライザ

ナショナルのDS16EV5110は1080p高品位ビデオの画質を向上。

さらに、HDMI/DVIケーブル上で40mを超える伝送距離を実現します。

## DS16EV5110の特長

- HDMI、DVI、CAT5/6/7ケーブル上で伝送距離を大幅に延長

- 最適なイコライゼーションのための8段階ブースト設定が可能

- 超低ジッタ:30mの24AWGDVIケーブル上で0.13UI (ユニット・インターバル)

- 低消費電力: 475mW

- 節電のためのクロック・チャネル・シグナル・ディテクト (SD) 機能と出力イネーブル端子

- 設計の自由度を高めるシリアル・マネジメント・バス (SMBus)

- 小型LTPS-48パッケージ (7mm×7mm)

HDMI/DVI/CAT5/6/7ケーブル・エクステンダ、スイッチャ、デジタル・ルータ/スイッチ、プロジェクタ、HD (高品位) ディスプレイに最適です。

DS16EV5110の製品サンプル、データシートは

ホームページから入手できます。

[lvds.national.com/jpn](http://lvds.national.com/jpn)

## Analog by Design Show

「DVI/HDMI/PCI-Expressケーブル標準に準拠した

長距離伝送アプリケーションの設計」

[www.national.com/nationaltv](http://www.national.com/nationaltv)

## データ伝送ラインにおけるシグナルパスの延長

値と規定しています。たとえば $\pm 400\text{mV}$ のLVDS  $V_{\text{OD}}$ は振幅が $800\text{mV}$ のピーク・ツー・ピークCML出力とちょうど同じになりますが、GNDに対するオフセット電圧は異なります。

LVDSレシーバ・デバイスは、入力コモンモード電圧範囲が広く、1.2V/1.5V/2.5VのCMLおよびLVPECL差動I/Oの信号振幅を容易に受け入れるので、差動技術のなかではフレキシビリティの点で最も優れています。このため大半の差動出力とLVDS入力間で直接のDC接続が可能であり、回路基板面積の増加やACカップリング・コンデンサのコストを最小限に抑えられます。

Figure 5. 標準型およびFPGA一体型差動I/Oのシグナリング・レベル

LVDSトランスマッタ出力  $V_{\text{OD}}$  は、高性能かつ低EMI、低消費電力を実現するために、最小値が $\pm 250\text{mV}$  ( $500\text{mV}$ ピーク・ツー・ピーク)と規定されています。これに出力シグナル・コンディショニングを追加すると、延長したケーブルや大きいバックプレーンを駆動できます。このLVDS出力は、内部バンドギャップ基準電圧から得られた1.2Vのコモンモード電圧に重畠され、多くのLVPECL入力とのDCカップリングが可能です。ただし、LVDS出力の電圧振幅は大半のCML入力に求められる最低限のコモンモード要件を満たしていないため、コモンモード電圧範囲が制限されたCML入力の場合、ACカップリング・インターフェースが必要になります。

LVDSおよびCMLバッファ・チップの多くは、ADC、DAC、FPGAおよびDSPからの信号をブーストするためのPE機能やレシーバEQ機能を内蔵しており、なかにはスイッチング・アプリケーションや冗長性のあるアプリケーション向けのマルチプレクシング機能を搭載しているものもあります。高性能LVDSクロスポイント・スイッチと高速FPGA CML I/Oを組み合わせると、冗長性付与、マルチプレクシ

ングおよび信号分配アプリケーション向けの低消費電力ソリューションを実現できます。CML出力を $600\text{mV}$ ~ $800\text{mV}$ 対応にプログラムすると、FPGA一体型SerDesでのトランスマット消費電力が低減し、インターフェースの全体的なEMIシグネチャが減り、EQ付きLVDS入力にとって最適となる信号が得られます。

最新世代のCML I/O付きFPGAは、LVDS標準で規定された公称電圧1.2Vより低いコモンモード出力電圧を持っています (Figure 5を参照)。入力コモンモード電圧範囲を広げると、高速FPGA I/OとLVDSデバイス間のインターフェース (相互接続性) が可能になります。

### 伝送距離が20mを超える信号駆動

LVDSおよびCMLのシグナル・コンディショナは、マルチギガビット級速度での信号伝送距離を最大20mまで延長可能です。伝送距離をもっと延ばす場合はイーサネットを使用できますが、シグナルパスの生データをイーサネット・パケットに適合させるための追加のプロトコルとタイミング・オーバーヘッドが必要になります。また別の方法として、ケーブル・ドライバとアダプティプ・イコライザを使って、シリアル・データ伝送距離を最大数100mまで延長することも可能です。ナショナルのDS15BA101/EA101は、最長100mまでの $100\Omega$ ツイストペア・ケーブル (低速用) と $50\Omega$ 同軸ケーブル (低速・高速用) をサポートしている1.5Gbpsケーブル・エクステンダ・チップセットです。このチップセットは、他の多くのEQ付きシグナル・コンディショナと異なり、さまざまなケーブル長やケーブル・タイプに対応できる自動補償機能を備えています。長距離のケーブル駆動にはイコライザのアダプティブ性が不可欠で、これによって高周波のエネルギー増幅時に発生する付加ノイズや付加ジッタが低減します。ナショナルの評価用リファレンス・デザインDriveCable02EVKを使えば、こうした評価および設計を迅速に行うことができます。

### まとめ

現在、多くのシグナルパスでは信号アクイジョンと各種のプロセッシング・モジュールが別々の構成になっています。サンプリング速度が高速化するにつれ、伝送媒体の損失が原因で、各モジュール間のシグナルパス・データ伝送はさらに難しくなっています。実際、伝送距離が一定の場合でも、シグナリング速度が速まると、損失およびそれに起因するジッタが増えます。PEおよびEQ機能を搭載したシグナル・コンディショナを採用することで、これらの損失の影響を予測し、問題を克服することができます。■

# 設計支援ツール

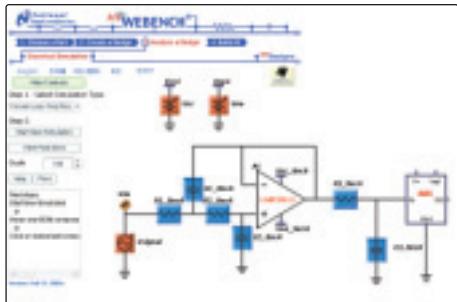

## WEBENCH® Signal Path Designer 回路設計ツール

ナショナルは、簡単な操作で回路設計を加速するSignal-Path DesignerをWEBENCHプラットフォーム上で提供しています。

### 機能

- アンチ・エイリアシング・フィルタの合成

- アンプの選択、A/Dコンバータとの最適な組み合わせを選定

- SNR、SDFR、電源電圧にもとづくトレードオフ

- SPICEを使用した実際の動作環境でのシミュレーション

- 短期間でサンプルを入手可能

[webench.national.com/jpn](http://webench.national.com/jpn)

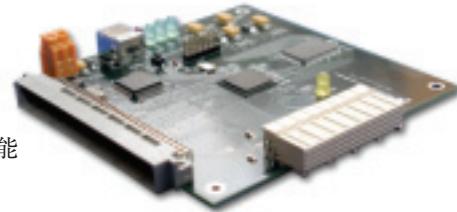

## WaveVision 4.0評価ボード

A/Dコンバータのテストと評価には、使いやすいナショナルのWaveVision 4.0評価ボードを。各評価ボードはUSBインターフェースを備え、ソフトウェアが同梱されています。

### 特長と利点

- プラグ・アンド・プレイなADC評価ボード

- パソコンと接続するUSBインターフェース

- パソコン上で動作するデータ・キャプチャ機能

- データ・キャプチャと評価が容易

- 高調波とSFDR周波数を表示

- 波形確認が容易

- FFTグラフの生成と表示

- FFTと合わせてダイナミック性能パラメータを表示

- ヒストグラムの生成と表示

ナショナルの

シグナルバス製品サイト:

[signalpath.national.com/jpn](http://signalpath.national.com/jpn)

お問い合わせ:

[jpn.feedback@nsc.com](mailto:jpn.feedback@nsc.com)

## どの号もお見逃しなく！

Signal Path Designerのバックナンバーは

ナショナルのサイトでご覧いただけます。

[signalpath.national.com/jpndesigner](http://signalpath.national.com/jpndesigner)

Power Designerもぜひお読みください。

オンラインで提供しています。

[power.national.com/jpndesigner](http://power.national.com/jpndesigner)

## ナショナル セミコンダクター ジャパン株式会社

〒135-0042 東京都江東区木場2-17-16

TEL 03-5639-7300 (大代表) [www.national.com/jpn/](http://www.national.com/jpn/)

© National Semiconductor Corporation, 2007. National Semiconductor, **N**, LLP, LMH, Signal Path Designer, and WEBENCH are registered trademarks of National Semiconductor. All other brand or product names are trademarks or registered trademarks of their respective holders.

570088-010-JP

# ご注意

日本テキサス・インスツルメンツ株式会社（以下TIJといいます）及びTexas Instruments Incorporated（TIJの親会社、以下TIJないしTexas Instruments Incorporatedを総称してTIといいます）は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIJとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIJの標準販売契約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIJとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。TI製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI製部品を使用したお客様の製品及びアプリケーションについて想定される危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならぬ場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、かつその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

Copyright © 2011, Texas Instruments Incorporated

日本語版 日本テキサス・インスツルメンツ株式会社

## 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。

### 1. 静電気

- 素手で半導体製品単体を触らないこと。どうしても触る必要がある場合は、リストストラップ等で人体からアースをとり、導電性手袋等をして取り扱うこと。

- 弊社出荷梱包単位（外装から取り出された内装及び個装）又は製品単品で取り扱いを行う場合は、接地された導電性のテーブル上で（導電性マットにアースをとったもの等）、アースをした作業者が行うこと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

- 前記のリストストラップ・導電性手袋・テーブル表面及び実装装置類の接地等の静電気帯電防止措置は、常に管理されその機能が確認されていること。

### 2. 湿度環境

- 温度：0～40°C、相対湿度：40～85%で保管・輸送及び取り扱いを行うこと。（但し、結露しないこと。）

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの黙示的保証を無効にし、かつ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任もありません。

TIは、TIの製品が、安全でないことが致命的となる用途ないしアプリケーション（例えば、生命維持装置のように、TI製品に不良があった場合に、その不良により相当な確率で死傷等の重篤な事故が発生するようなもの）に使用されることを認めておりません。但し、お客様とTIの双方の権限有る役員が書面でそのような使用について明確に合意した場合は除きます。たとえTIがアプリケーションに関連した情報やサポートを提供したとしても、お客様は、そのようなアプリケーションの安全面及び規制面から見た諸問題を解決するために必要とされる専門的知識及び技術を持ち、かつ、お客様の製品について、またTI製品をそのような安全でないことが致命的となる用途に使用することについて、お客様が全ての法的責任、規制を遵守する責任、及び安全に関する要求事項を満足させる責任を負っていることを認め、かつそのことに同意します。さらに、もし万一、TIの製品がそのような安全でないことが致命的となる用途に使用されたことによって損害が発生し、TIないしその代表者がその損害を賠償した場合は、お客様がTIないしその代表者にその全額の補償をするものとします。

TI製品は、軍事的用途もしくは宇宙航空アプリケーションないし軍事的環境、航空宇宙環境にて使用されるようには設計もされていませんし、使用されることを意図されておりません。但し、当該TI製品が、軍需対応グレード品、若しくは「強化プラスティック」製品としてTIが特別に指定した製品である場合は除きます。TIが軍需対応グレード品として指定した製品のみが軍需品の仕様書に合致いたします。お客様は、TIが軍需対応グレード品として指定していない製品を、軍事的用途もしくは軍事的環境下で使用することは、もっぱらお客様の危険負担においてなされるということ、及び、お客様がもっぱら責任をもって、そのような使用に関して必要とされる全ての法的要件及び規制上の要求事項を満足させなければならないことを認め、かつ同意します。

TI製品は、自動車用アプリケーションないし自動車の環境において使用されるようには設計もされていませんし、また使用されることを意図されておりません。但し、TIがISO/TS 16949の要求事項を満たしていると特別に指定したTI製品は除きます。お客様は、お客様が当該TI指定品以外のTI製品を自動車用アプリケーションに使用しても、TIは当該要求事項を満たしていなかったことについて、いかなる責任も負わないことを認め、かつ同意します。

- 直射日光があたる状態で保管・輸送しないこと。

### 3. 防湿梱包

- 防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装すること。

### 4. 機械的衝撃

- 梱包品（外装、内装、個装）及び製品単品を落下させたり、衝撃を与えないこと。

### 5. 熱衝撃

- はんだ付け時は、最低限260°C以上の高温状態に、10秒以上さらさないこと。（個別推奨条件がある時はそれに従うこと。）

### 6. 汚染

- はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質（硫黄、塩素等ハロゲン）のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。（不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。）

以上