# High-Speed Operational Amplifier Layout Made Easy

Andy Hahn

AAP Power Supplies

### ABSTRACT

This application brief describes some general guidelines that can exploit the full performance characteristics of a THS-Series high-speed operational amplifier. The guidelines assist development engineers in quickly creating efficient board layouts for high-speed amplifiers.

#### Contents

| When Is a High-Speed Layout Necessary?    | 2 |

|-------------------------------------------|---|

| Guidelines for a Proper High-Speed Layout | 2 |

| References                                | 7 |

### **List of Figures**

| 1 | PCB With Proper Arrangement            | 2 |

|---|----------------------------------------|---|

|   | Impedance Behavior of a Real Capacitor |   |

| 3 | Sharing of Ground Lines                | 4 |

| 4 | Trace Width on Standard PCB's          | 5 |

| 5 | Correct Termination                    | 6 |

| 6 | PowerPAD™ Improves Heat Sinking        | 6 |

## When Is a High-Speed Layout Necessary?

Effects that can safely be ignored at lower frequencies become significant when processing signals with frequencies in the MHz range. The bandwidth for THS-Series high-speed operational amplifiers extends to well over 50 MHz. At these high frequencies the effects caused by electromagnetic waves must be taken into account when designing the printed-circuit board. Careful attention must be given to such factors as component selection, grounding, power supply bypassing, signal path layout, line termination, stray capacitance, and inductance. A PCB design following some general guidelines can exploit the full performance characteristics of a THS-Series high-speed operational amplifier. The following set of guidelines assists development engineers in quickly creating efficient board layouts for high-speed amplifiers.

# **Guidelines for a Proper High-Speed Layout**

- To achieve a good high-speed layout, a two-layer PCB is the minimum requirement. The bottom plane should be a large continuous ground plane to provide a low impedance ground path for return currents. In contrast, the supply voltage traces should be designed as large continuous planes next to the ground plane. This ensures a low Impedance for the supply voltages due to the distributed capacitance formed.

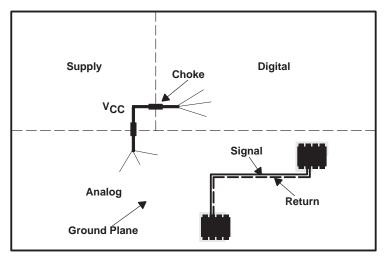

- If several functional modules are combined on a single PCB, the PCB should be partitioned into separate functional units. This is particularly important if analog and digital signals are being processed on the same PCB. A common error is to incorrectly position the analog circuit on the PCB and to route digital signal lines through the analog area of the board. Each individual functional unit should have its own power supply, as shown in Figure 1. A star-shaped distribution of the supply voltage to each stage through a choke leads to better decoupling between these stages.

Figure 1. PCB With Proper Arrangement

At high frequencies every component lead acts like an inductor. For high-speed designs it is always best to keep this inductance as low as possible. Surface-mounted devices (SMD) are ideal in meeting this requirement. SMD packages not only guarantee extremely low lead inductance, they also take up very little space on the PCB. A smaller and more compact layout simultaneously helps to keep the stray capacitance and inductance at low levels. Leaded components and sockets are not recommended for use in high-speed designs.

- In RF designs, low resistance values are required. This minimizes coupled interference voltages and avoids attenuation of the signals due to low cutoff frequencies caused by the low-pass formed by the signal trace and the stray capacitances. The feedback resistor requires careful attention. For optimum frequency response, settling time and minimum ringing recommended feedback resistor values are given in the related data sheets.

- The PCB design should preferably permit signal processing to take place along a line. This

means that the circuit input and output are kept well apart, providing the best possible

degree of decoupling within the circuit. The components located between input and output

should be placed along this line. Arranging components in such a way reduces signal

coupling between different stages of the signal processing. In general, the layout design

should be compact to ensure that all RF loops are small to decrease RF irradiation and

emission.

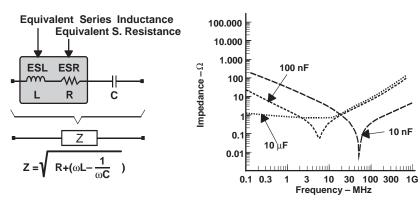

- The ideal supply voltage for an operational amplifier has a very low impedance. To achieve this on the PCB, the whole supply trace must have low impedance by a width trace. Additionally the supply voltage has to be stabilized by a bulk capacitor against rapid large changes of the supply current. The maximum supply current is determined by the output power of the amplifier. In most cases a  $6.8-\mu$ F to  $10-\mu$ F tantalum capacitor provides a good value for the output power of the THS series. When selecting capacitors it is important to ensure that they have a low equivalent series resistance (ESR) and a low equivalent series inductance (ESL). It may be possible to share the bulk capacitor among several devices. depending on the application. Figure 2 shows that at high frequencies the impedance of a capacitor increases. Depending on the quality of the bulk capacitor and the trace length, additional bypass capacitors are necessary to improve the impedance of the power supplies at high frequencies. Placing a ceramic bypass capacitor, in the range of 10 nF to 100 nF directly at the amplifier's supply pins bypasses RF currents and improves EMC characteristics of the circuit. The designer should strive for distances of less than 0.1 inches between the device supply pins and the ceramic capacitor. This additional ceramic capacitor can be improved by using a multilayer PCB, since large power supply planes on such a PCB act as capacitors themselves.

Figure 2. Impedance Behavior of a Real Capacitor

The most important signal trace design guideline concerns the length of the signal trace, which should be as short and as straight as possible. If the signal trace has to be significantly angled this should be done in a rounded fashion, or at least in 45° steps to ensure that the trace impedance remains constant. A ground plane takes care that every signal trace has its signal return path nearby. If signal traces run parallel due to shortage of

space, a gap of at least three times the signal trace width should be maintained. Better decoupling is provided if a grounding trace is routed between two signal traces.

- If shortage of space means that a signal trace has to switch between two layers of the PCB a connection, or via, must be used. At high frequencies, this via adds additional impedance into the signal trace. Accordingly, the number of vias should be kept to a minimum.

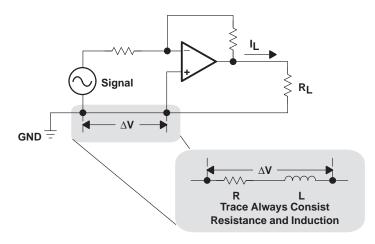

- The ground path of the input signal provides a potential for noise injection into the signal because the signal is typically referenced to ground. If the ground path is used by more than one signal they might interfere with each other. In Figure 3, the same ground trace is used by the input and the output signal. A high output current (*I<sub>L</sub>*) leads to a voltage drop of Δ*V* on the line impedance. In accordance with Ohm's Law, this increases proportionally to the load current. The voltage drop is an additional input signal for the amplifier, and with a high gain, the voltage drop can lead to positive feedback, causing the amplifier circuit to oscillate. Accordingly, it is advisable for circuit parts at high currents not to share signal traces with other parts. They should rather meet at a single point.

Figure 3. Sharing of Ground Lines

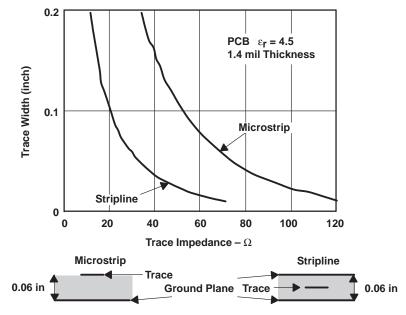

All connection traces on the PCB less then 2 inches can be considered as a lumped capacitive load. Stripline techniques should be used for longer distances of the connections. These traces should be designed with characteristic impedances as required by the application. The graph in Figure 4 shows the trace and PCB dimensions for different impedances and stripline techniques. Mismatching at the impedance transitions can lead to reflections with high signal levels. These reflections are added to the original signal, either making it erroneous or even erasing it entirely. The impedance for a cable (50 Ω for coaxial) is in general much lower than the impedance of a stripline on the PCB. The use of higher impedances for signal distribution on the PCB will improve signal quality.

Figure 4. Trace Width on Standard PCB's

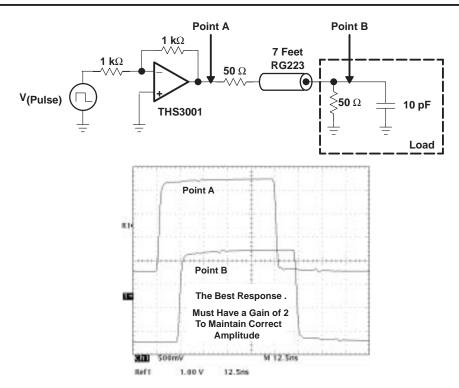

If a 6-dB signal reduction is acceptable for signal distribution, a transmission line can be made reflection free by adding a series resistor to the amplifier output and a terminating load resistor at the end of the transmission line at the destination device input. This is shown in Figure 5 with different values for the termination resistors. Output and series resistor together, also input and shunt resistor together, must be equal to the characteristic line impedance. The series resistor isolates capacitive loads from the amplifier output. Capacitive loading directly on the amplifier output will decrease the device's phase margin leading to high frequency ringing or oscillations. Therefore, it is recommended that a resistor be placed in series with the output of the amplifier. If the attenuation loss of the double termination is unacceptable, a termination at one end only might be the solution with the involved restricted signal quality.

- The amplifier output and inputs are sensitive to stray capacitance and inductance. The components connected at these pins should be placed as close as possible to the amplifier in order to keep the connecting signal traces short to reduce stray capacitances and inductances. Further reduction in stray capacitance is possible by removing the ground plane below these pins and the connected signal traces. This should be done in any case at the inverting input pin because this pin is most sensitive to stray capacitance. If the amplifier is used in inverting mode, stray capacitance has a minimized effect, because this pin is biased by a fixed potential.

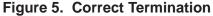

- High-speed amplifiers with high output capacity are fitted with a special PowerPAD<sup>™</sup> on the bottom of the SMD package to improve heat sinking, as illustrated in application brief SLMA004 and Figure 6. In this package a special contact pad is directly connected internally to the die. The PowerPAD<sup>™</sup> contact surface should be connected to the PCB's ground plane in order to further improve the heat sinking. Thus the PCB design should include a small copper area fitted between the pads of the amplifier package. This copper area should be suitably connected to the ground plane (through several vias). This provides an enlarged surface which improves the dissipation of heat to the ambient environment.

Figure 6. PowerPAD<sup>™</sup> Improves Heat Sinking

PowerPAD is a trademark of Texas Instruments.

### References

- 1. Application Report, Understanding Basic Analog Passive Devices, SLOA027, Texas Instruments, 1999

- 2. Application Brief, PowerPAD<sup>™</sup> Made Easy, SLMA004, Texas Instruments, 1999

- 3. The Bypass Capacitor In High-Speed Environments, SCBA007A, Texas Instruments, 1996

- 4. Application Report, *Effect of Parasitic Capacitance in Op Amp Circuits*, SLOA013, Texas Instruments, 1999

- 5. Mark I. Montrose, *Printed Circuit Board Design Techniques for EMC Compliance*, IEEE Press 1996

- 6. Johnson & Graham, High-Speed Digital Design, Prentice Hall PTR

- 7. Mark I. Montrose, EMC and the Printed Circuit Board, IEEE Press 1999

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated