# ADC10065

***ADC10065 10-Bit 65 MSPS 3V A/D Converter***

Literature Number: JAJSA60

2005年5月

ADC10065 10ビット、65MSPS、3V A/Dコンバータ

## ADC10065

10ビット、65MSPS、3V A/Dコンバータ

### 概要

ADC10065 は、アナログ入力信号を 65MSPS のサンプリング・レートで 10 ビットのデジタル・ワードに変換できるモノリシック CMOS A/D コンバータです。本デバイスはデジタル・エラー訂正機能とオンチップのサンプル / ホールド回路を備えた差動式パイプライン型アーキテクチャを採用しており、完全なコンバージョン・ソリューションを実現します。また、消費電力を最小限に抑えながら優れた動的性能を確保しています。独自のサンプル・ホールド段により、400MHz のフルパワー帯域幅を得ています。ADC10065 の消費電力は、基準電流も含めて単電源 3.0V、65MSPS 動作でわずか 68.4mW です。スタンバイ機能を使うと消費電力はわずか 14.1mWまで下がります。

差動入力の振幅範囲は 2.0V<sub>P-P</sub>、1.5V<sub>P-P</sub>、1.0V<sub>P-P</sub>から選択可能で、シングルエンド入力としても構成できます。ただし、本デバイスの性能を最大限に引き出すには差動入力を適切に使用することを推奨します。内蔵の高精度バンドギャップ・リファレンスによって ADC のフルスケール・レンジが確保されますが、より精度が必要なアプリケーションにも対応できるようにバッファしたリファレンス電位を外部から与えることも可能です。出力データ形式は、10 ビットのオフセット・バイナリ、または 2 の補数です。

28 ピンの TSSOP パッケージで供給可能で、動作温度範囲は、工業用機器に適用される -40 から +85 までです。

### 特長

- 单一 + 3V 電源で動作

- フルスケール入力振幅は 2.0 V<sub>P-P</sub>、1.5 V<sub>P-P</sub>、1.0 V<sub>P-P</sub> から選択可能

- 3 dB 入力帯域幅 400MHz

- 低消費電力

- スタンバイ・モード

- リファレンス電位生成回路とサンプル / ホールド・アンプを内蔵オフセット・バイナリまたは 2 の補数による出力データ形式

- 出力ドライバ電源の分離により 2.5V や 3.3V ロジックとのインターフェースに対応

- 28 ピン TSSOP パッケージ

### 主な仕様

|                           |                   |

|---------------------------|-------------------|

| 分解能                       | 10 ビット            |

| サンプリング・レート                | 65 MSPS           |

| フルパワー帯域幅                  | 400 MHz           |

| DNL                       | ± 0.3 LSB ( 代表値 ) |

| SN 比 ( $f_{IN} = 11$ MHz) | 59.6 dB ( 代表値 )   |

| SFDR ( $f_{IN} = 11$ MHz) | - 80 dB ( 代表値 )   |

| データ・レイテンシ                 | 6 クロック・サイクル       |

| 電源電圧                      | + 3.0V            |

| 消費電力 65MHz                | 68.4 mW           |

### アプリケーション

- 超音波映像装置

- 計測機器

- 携帯電話の基地局、受信機

- ソナー、レーダ

- xDSL

- 無線ローカル・ループ

- 業務用カメラ

- DSP のフロント・エンド

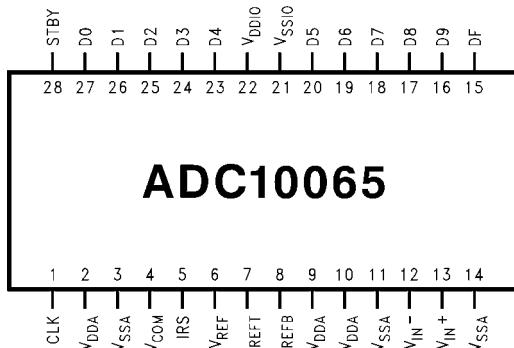

### ピン配置図

## 製品情報

| Industrial (-40°C ≤ T <sub>A</sub> ≤ +85°C) | NS Package               |

|---------------------------------------------|--------------------------|

| ADC10065CIMT                                | 28 Pin TSSOP             |

| ADC10065CIMTX                               | 28 Pin TSSOP Tape & Reel |

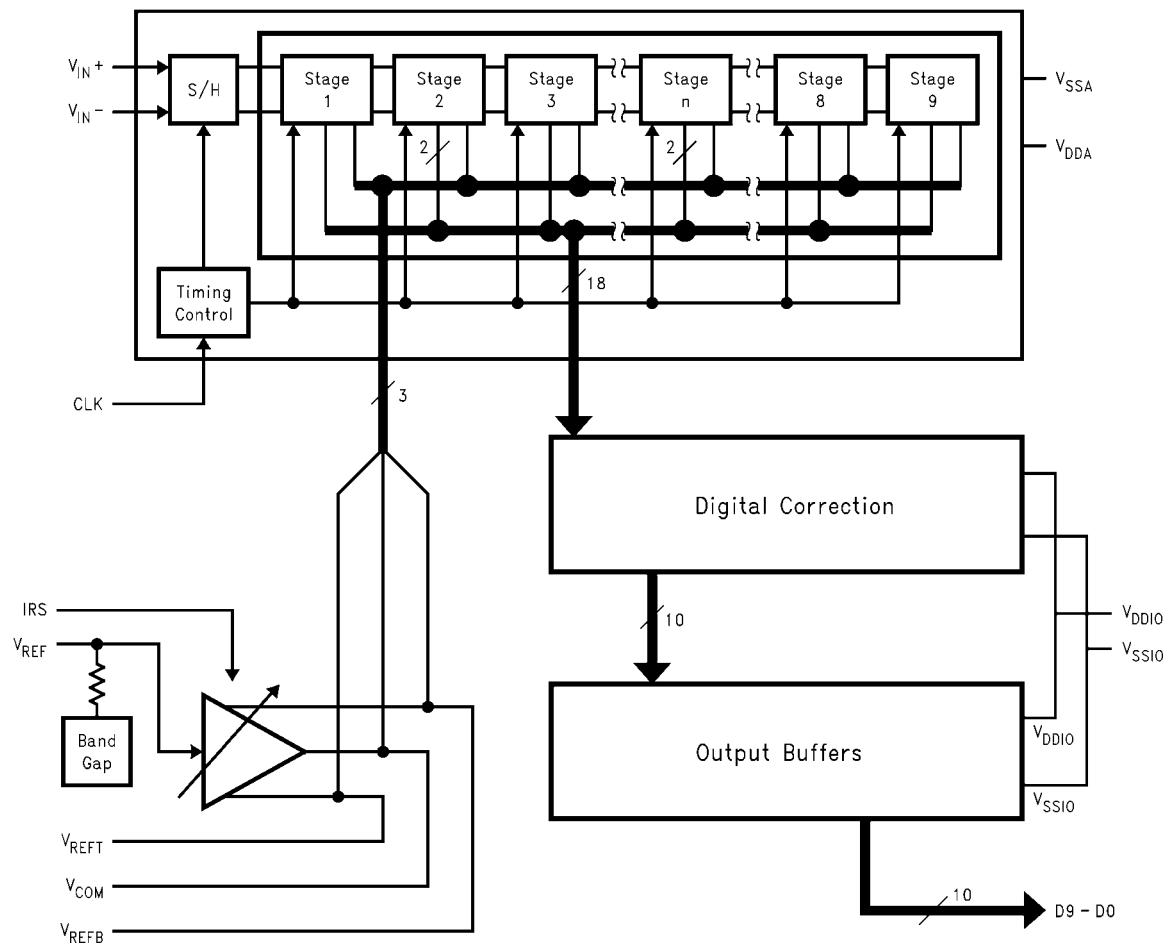

## ブロック図

## 端子説明および等価回路

| 端子番号                 | 記号                           | 等価回路                                                                                | 説明                                                                                                                                                                                                                                                                                                                                                  |

|----------------------|------------------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>アナログ入出力 (I/O)</b> |                              |                                                                                     |                                                                                                                                                                                                                                                                                                                                                     |

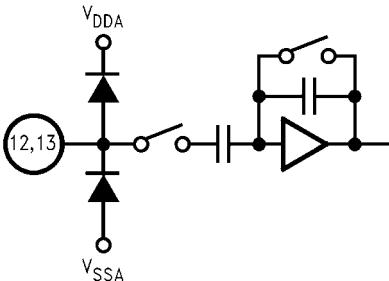

| 12                   | V <sub>IN</sub> <sup>-</sup> |    | 反転アナログ入力信号。リファレンス電圧が 1.2V の場合、フルスケール入力信号レベルは 1.0V <sub>P-P</sub> です。シングルエンドで動作させる場合はこのピンを V <sub>COM</sub> (4 ピン) に接続します。                                                                                                                                                                                                                           |

| 13                   | V <sub>IN</sub> <sup>+</sup> |    | 非反転アナログ入力信号。リファレンス電圧が 1.2V の場合、フルスケール入力信号レベルは 1.0V <sub>P-P</sub> です。                                                                                                                                                                                                                                                                               |

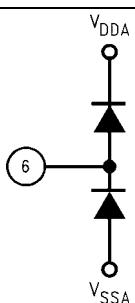

| 6                    | V <sub>REF</sub>             |    | 基準電圧入力端子。この端子と V <sub>SSA</sub> の間にバイパス・コンデンサとして 0.1 μF のモノリシック・コンデンサを 1 つ挿入してください。V <sub>REF</sub> は公称 1.20V です。必要であればこのピンを外部 1.20V リファレンス電圧で駆動することも可能です。                                                                                                                                                                                          |

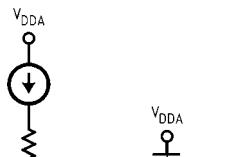

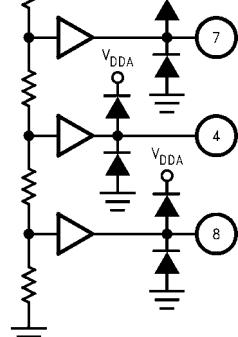

| 7                    | V <sub>REFT</sub>            |   |                                                                                                                                                                                                                                                                                                                                                     |

| 4                    | V <sub>COM</sub>             |  | これらの端子は高インピーダンスの基準電圧用バイパス端子。各端子と V <sub>SSA</sub> の間に 0.1 μF のコンデンサを 1 つずつ挿入してください。これらの端子に負荷を接続してはなりません。V <sub>COM</sub> を使って入力コモン電圧 V <sub>CM</sub> を設定できます。                                                                                                                                                                                       |

| 8                    | V <sub>REFB</sub>            |  |                                                                                                                                                                                                                                                                                                                                                     |

| <b>デジタル入出力 (I/O)</b> |                              |                                                                                     |                                                                                                                                                                                                                                                                                                                                                     |

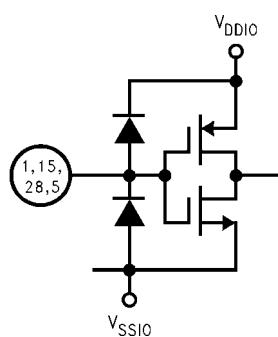

| 1                    | CLK                          |  | デジタル・クロック入力端子。入力周波数範囲は 20MHz ~ 65MHz です。このクロック・パルスの立ち上がり端でアナログ入力信号がサンプリングされます。                                                                                                                                                                                                                                                                      |

| 15                   | DF                           |  | DF = High のとき、2 の補数<br>DF = Low のとき、オフセット・バイナリ                                                                                                                                                                                                                                                                                                      |

| 28                   | STBY                         |  | スタンバイピン。このピンが High のとき、コンバータはスタンバイ・モードになります。Low レベルの時は、通常動作になります。                                                                                                                                                                                                                                                                                   |

| 5                    | IRS (Input Range Select)     |  | IRS = V <sub>DDA</sub> のとき、入力電圧範囲 2.0 V <sub>P-P</sub><br>IRS = V <sub>SSA</sub> のとき、入力電圧範囲 1.5 V <sub>P-P</sub><br>IRS = 開放のとき、入力電圧範囲 1.0 V <sub>P-P</sub><br>V <sub>IN</sub> <sup>+</sup> ピンと V <sub>IN</sub> <sup>-</sup> ピンの両方を使用する場合 (または差動モードの場合)、ピーク・ツー・ピーク電圧は差動電圧 (V <sub>IN</sub> <sup>+</sup> - V <sub>IN</sub> <sup>-</sup> ) での参照となります。 |

## 端子説明および等価回路(つづき)

| 端子番号                | 記号                | 等価回路                                                                              | 説明                                                                                                                                                                                   |

|---------------------|-------------------|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>デジタル入出力(I/O)</b> |                   |                                                                                   |                                                                                                                                                                                      |

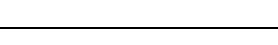

| 16-20,<br>23-27     | D0-D9             |  | デジタル・データ出力です。D0 がバイナリ出力ワードの LSB であり、D9 が同 MSB です。                                                                                                                                    |

| <b>アナログ電源</b>       |                   |                                                                                   |                                                                                                                                                                                      |

| 2, 9, 10            | V <sub>DDA</sub>  |                                                                                   | 正のアナログ電源電圧端子。この端子は 3 本とも共通の安定した 3.0V 電源に接続してください。各電源端子と AGND の間のバイパス・コンデンサとして、各端子から 1cm 以内の所で 0.1 μF のモリシック・コンデンサを 1 つずつ挿入してください。合わせて、4.7 μF のコンデンサを並列に接続してください。                     |

| 3, 11, 14           | V <sub>SSA</sub>  |                                                                                   | アナログ電源のグラウンド帰路端子。                                                                                                                                                                    |

| <b>デジタル電源</b>       |                   |                                                                                   |                                                                                                                                                                                      |

| 22                  | V <sub>DDIO</sub> |                                                                                   | ADC10065 の出力ドライバ用の正のデジタル電源端子。ビンから 1cm 以内に配置した 0.1 μF のモリシック・コンデンサを使って、このビンをデジタル・グラウンドにバイパスしてください。合わせて、4.7 μF のコンデンサを並列に接続してください。このビンには V <sub>DDA</sub> より先 300mV 以上高い電圧を印加してはなりません。 |

| 21                  | V <sub>SSIO</sub> |                                                                                   | 出力ドライバ用デジタル電源のグラウンド端子。デジタル・グラウンドに接続してください。また、アナログ・グラウンドとは離してください。                                                                                                                    |

**絶対最大定格 (Note 1、2)**

|                                     |                                                             |

|-------------------------------------|-------------------------------------------------------------|

| V <sub>DDA</sub> 、V <sub>DDIO</sub> | 3.9V                                                        |

| 任意のピンの対 GND 電圧                      | - 0.3V ~ V <sub>DDA</sub> 、<br>または V <sub>DDIO</sub> + 0.3V |

| 各端子の入力電流                            | ± 25 mA                                                     |

| パッケージ入力電流 (Note 3)                  | ± 50mA                                                      |

| T <sub>A</sub> = 25 °C でのパッケージ損失    | (Note 4) 参照                                                 |

| ESD 耐性                              |                                                             |

| 人体モデル (Note 5)                      | 2500V                                                       |

| マシン・モデル (Note 5)                    | 250V                                                        |

| ハンダ付け温度赤外線 (10 秒) (Note 6)          | 235                                                         |

| 保存温度範囲                              | - 65 ~ + 150                                                |

**動作定格**

|                                     |                              |

|-------------------------------------|------------------------------|

| 動作温度範囲                              | - 40 ~ T <sub>A</sub> ~ + 85 |

| V <sub>DDA</sub> (電源電圧)             | + 2.7V ~ + 3.6V              |

| V <sub>DDIO</sub> (出力ドライバ電源電圧)      | + 2.5V ~ V <sub>DDA</sub>    |

| V <sub>REF</sub>                    | 1.20V                        |

| V <sub>SSA</sub> -V <sub>SSIO</sub> | 100 mV                       |

| クロック・デューティ・サイクル                     | 30 ~ 70%                     |

**NOTE:** 「絶対最大定格」とは、個々に適用されるリミット値で、これを超えるとデバイスの有効性が損なわれるおそれがあります。絶対最大定格条件下では機能的な動作は想定されていません。最大定格でデバイスを長時間にわたって動作させると信頼性に影響を及ぼすおそれがあります。

**コンバータの電気的特性**

特記のない限り次の仕様が適用されます。V<sub>SSA</sub> = V<sub>SSIO</sub> = 0V、V<sub>DDA</sub> = + 3.0V、V<sub>DDIO</sub> = + 2.5V、V<sub>IN</sub> = 2 V<sub>P-P</sub>、STBY = 0V、V<sub>REF</sub> = 1.20V、(外部供給) f<sub>CLK</sub> = 65 MHz、デューティ・サイクル 50%、C<sub>L</sub> = 10pF/ピン。太文字表記のリミット値は T<sub>A</sub> = T<sub>MIN</sub> ~ T<sub>MAX</sub> にわたって適用され、その他のすべてのリミット値は T<sub>A</sub> = 25 °C に対して適用されます。

| Symbol                                     | Parameter                                                         | Conditions                                  | Min  | Typ   | Max         | Units  |

|--------------------------------------------|-------------------------------------------------------------------|---------------------------------------------|------|-------|-------------|--------|

| <b>STATIC CONVERTER CHARACTERISTICS</b>    |                                                                   |                                             |      |       |             |        |

|                                            | No Missing Codes Guaranteed                                       |                                             | 10   |       |             | Bits   |

| INL                                        | Integral Non-Linearity (Note 12)                                  | F <sub>IN</sub> = 500 kHz, -0 dB Full Scale | -1.0 | ±0.3  | +1.1        | LSB    |

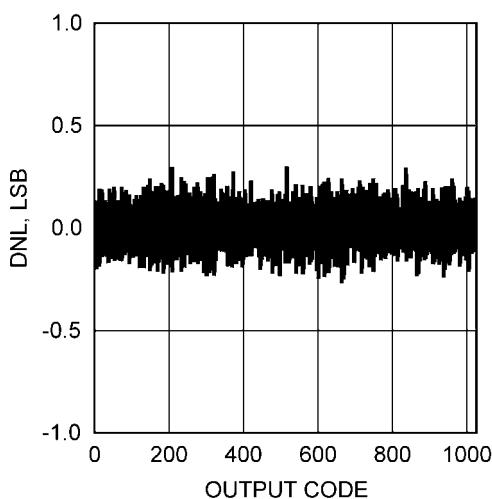

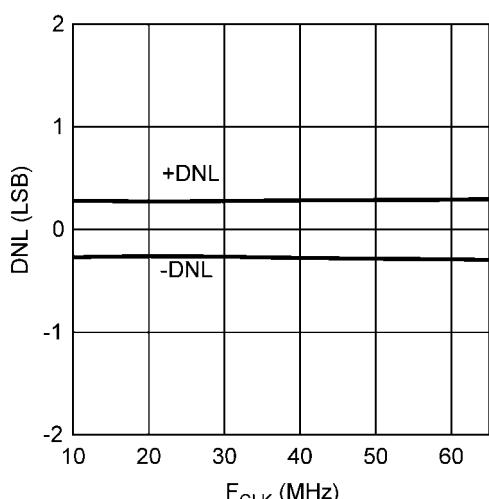

| DNL                                        | Differential Non-Linearity                                        | F <sub>IN</sub> = 500 kHz, -0 dB Full Scale | -0.9 | ±0.3  | +0.9        | LSB    |

| GE                                         | Gain Error                                                        | Positive Error                              | -1.5 | +0.4  | +1.9        | % FS   |

|                                            |                                                                   | Negative Error                              | -1.5 | +0.03 | +1.9        | % FS   |

| OE                                         | Offset Error (V <sub>IN+</sub> = V <sub>IN-</sub> )               |                                             | -1.4 | 0.2   | +1.7        | % FS   |

|                                            | Under Range Output Code                                           |                                             |      | 0     |             |        |

|                                            | Over Range Output Code                                            |                                             |      | 1023  |             |        |

| FPBW                                       | Full Power Bandwidth                                              |                                             |      | 400   |             | MHz    |

| <b>REFERENCE AND INPUT CHARACTERISTICS</b> |                                                                   |                                             |      |       |             |        |

| V <sub>CM</sub>                            | Common Mode Input Voltage                                         |                                             | 0.5  |       | 1.5         | V      |

| V <sub>COM</sub>                           | Output Voltage for use as an input common mode voltage (Note 7)   |                                             |      | 1.45  |             | V      |

| V <sub>REF</sub>                           | Reference Voltage                                                 |                                             |      | 1.2   |             | V      |

| V <sub>REFTC</sub>                         | Reference Voltage Temperature Coefficient                         |                                             |      | ±80   |             | ppm/°C |

| C <sub>IN</sub>                            | V <sub>IN</sub> Input Capacitance (each pin to V <sub>SSA</sub> ) |                                             |      | 4     |             | pF     |

| <b>POWER SUPPLY CHARACTERISTICS</b>        |                                                                   |                                             |      |       |             |        |

| I <sub>VDDA</sub>                          | Analog Supply Current                                             | STBY = 1                                    |      | 4.7   | <b>6.0</b>  | mA     |

|                                            |                                                                   | STBY = 0                                    |      | 22    | <b>29</b>   | mA     |

| I <sub>VDIO</sub>                          | Digital Supply Current                                            | STBY = 1, f <sub>IN</sub> = 0 Hz            |      | 0     |             | mA     |

|                                            |                                                                   | STBY 0, f <sub>IN</sub> = 0 Hz              |      | 0.97  | <b>1.2</b>  | mA     |

| PWR                                        | Power Consumption                                                 | STBY = 1                                    |      | 14.1  | <b>18.0</b> | mW     |

|                                            |                                                                   | STBY = 0                                    |      | 68.4  | <b>90</b>   | mW     |

## DC およびロジック電気的特性

特記のない限り次の仕様が適用されます。  $V_{SSA} = V_{SSIO} = 0V$ 、 $V_{DDA} = +3.0V$ 、 $V_{DDIO} = +2.5V$ 、 $V_{IN} = 2\text{ V}_{P-P}$ 、 $STBY = 0V$ 、 $V_{REF} = 1.20V$ 、(外部供給)  $f_{CLK} = 65\text{ MHz}$ 、デューティ・サイクル 50%、 $C_L = 10\text{ pF}/\text{ビン}$ 。太文字表記のリミット値は  $T_A = T_{MIN}$  ~  $T_{MAX}$  にわたって適用され、その他のすべてのリミット値は  $T_A = 25^\circ C$  に対して適用されます。

| Symbol                                   | Parameter                                                       | Conditions                 | Min               | Typ  | Max | Units   |

|------------------------------------------|-----------------------------------------------------------------|----------------------------|-------------------|------|-----|---------|

| <b>CLK, DF, STBY, SENSE</b>              |                                                                 |                            |                   |      |     |         |

|                                          | Logical "1" Input Voltage                                       |                            | 2                 |      |     | V       |

|                                          | Logical "0" Input Voltage                                       |                            |                   |      | 0.8 | V       |

|                                          | Logical "1" Input Current                                       |                            |                   |      | +10 | $\mu A$ |

|                                          | Logical "0" Input Current                                       |                            | -10               |      |     | $\mu A$ |

| <b>D0-D9 OUTPUT CHARACTERISTICS</b>      |                                                                 |                            |                   |      |     |         |

|                                          | Logical "1" Output Voltage                                      | $I_{OUT} = -0.5\text{ mA}$ | $V_{DDIO}-0.2$    |      |     | V       |

|                                          | Logical "0" Output Voltage                                      | $I_{OUT} = 1.6\text{ mA}$  |                   |      | 0.4 | V       |

| <b>DYNAMIC CONVERTER CHARACTERISTICS</b> |                                                                 |                            |                   |      |     |         |

| ENOB                                     | Effective Number of Bits                                        | $f_{IN} = 11\text{ MHz}$   | 9.4, <b>9.3</b>   | 9.6  |     | Bits    |

|                                          |                                                                 | $f_{IN} = 32\text{ MHz}$   | 9.3, <b>9.2</b>   | 9.5  |     | Bits    |

| SNR                                      | Signal-to-Noise Ratio                                           | $f_{IN} = 11\text{ MHz}$   | 58.6, <b>58</b>   | 59.6 |     | dB      |

|                                          |                                                                 | $f_{IN} = 32\text{ MHz}$   | 58.5, <b>57.9</b> | 59.3 |     | dB      |

| SINAD                                    | Signal-to-Noise Ratio + Distortion                              | $f_{IN} = 11\text{ MHz}$   | 58.3, <b>57.6</b> | 59.4 |     | dB      |

|                                          |                                                                 | $f_{IN} = 32\text{ MHz}$   | 58, <b>57.4</b>   | 59   |     | dB      |

| 2nd HD                                   | 2nd Harmonic                                                    | $f_{IN} = 11\text{ MHz}$   | -75.6,<br>-69.7   | -90  |     | dBc     |

|                                          |                                                                 | $f_{IN} = 32\text{ MHz}$   | -72.7,<br>-68.9   | -82  |     | dBc     |

| 3rd HD                                   | 3rd Harmonic                                                    | $f_{IN} = 11\text{ MHz}$   | -66.2,<br>-63     | -74  |     | dBc     |

|                                          |                                                                 | $f_{IN} = 32\text{ MHz}$   | -65.4,<br>-63.3   | -72  |     | dBc     |

| THD                                      | Total Harmonic Distortion (First 6 Harmonics)                   | $f_{IN} = 11\text{ MHz}$   | -66.2,<br>-63     | -74  |     | dB      |

|                                          |                                                                 | $f_{IN} = 32\text{ MHz}$   | -65.4,<br>-63.3   | -72  |     | dB      |

| SFDR                                     | Spurious Free Dynamic Range<br>(Excluding 2nd and 3rd Harmonic) | $f_{IN} = 11\text{ MHz}$   | -75.8,<br>-74.5   | -80  |     | dBc     |

|                                          |                                                                 | $f_{IN} = 32\text{ MHz}$   | -74.4,<br>-73.3   | -80  |     | dBc     |

## AC 電気的特性

特記のない限り次の仕様が適用されます。 $V_{SSA} = V_{SSIO} = 0V$ 、 $V_{DDA} = +3.0V$ 、 $V_{DDIO} = +2.5V$ 、 $V_{IN} = 2V_{P-P}$ 、 $STBY = 0V$ 、 $V_{REF} = 1.20V$ 、(外部供給) $f_{CLK} = 65MHz$ 、デューティ・サイクル50%、 $C_L = 10pF/\text{ピン}$ 。太文字表記のリミット値は $T_A = T_{MIN} \sim T_{MAX}$ にわたって適用され、その他のすべてのリミット値は $T_A = 25^\circ C$ に対して適用されます。

| Symbol                      | Parameter                                   | Conditions                                                                  | Min<br>(Note 12) | Typ<br>(Note 12) | Max<br>(Note 12) | Units       |

|-----------------------------|---------------------------------------------|-----------------------------------------------------------------------------|------------------|------------------|------------------|-------------|

| <b>CLK, DF, STBY, SENSE</b> |                                             |                                                                             |                  |                  |                  |             |

| $f_{CLK1}$                  | Maximum Clock Frequency                     |                                                                             |                  |                  | 65               | MHz (min)   |

| $f_{CLK2}$                  | Minimum Clock Frequency                     |                                                                             |                  | 20               |                  | MHz         |

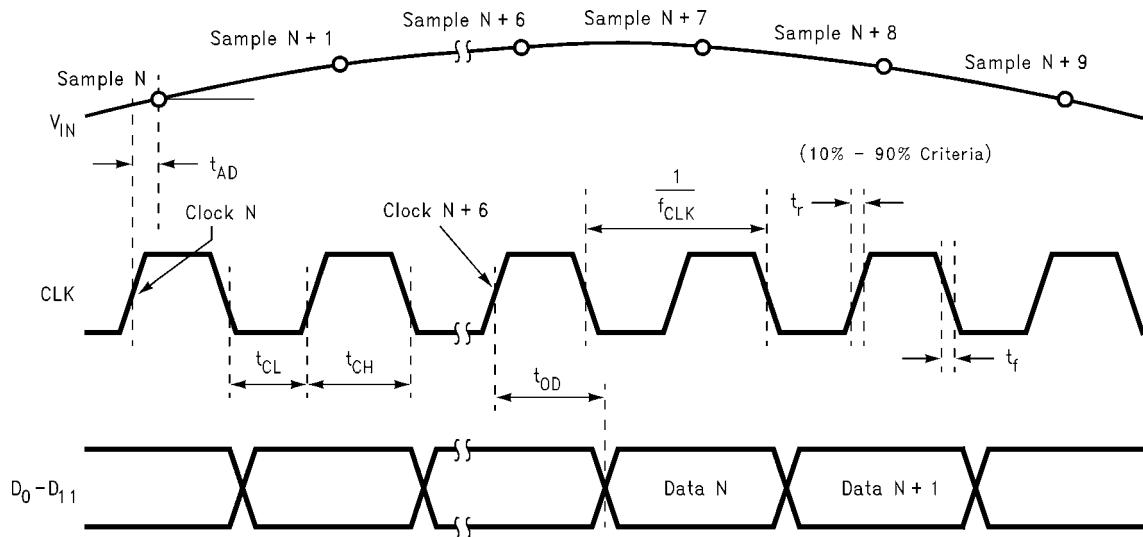

| $t_{CH}$                    | Clock High Time                             |                                                                             |                  | 7.69             |                  | ns          |

| $t_{CL}$                    | Clock Low Time                              |                                                                             |                  | 7.69             |                  | ns          |

| $t_{CONV}$                  | Conversion Latency                          |                                                                             |                  |                  | 6                | Cycles      |

| $t_{OD}$                    | Data Output Delay after a Rising Clock Edge | $T = 25^\circ C$                                                            | 2                | 3.4              | 5                | ns          |

|                             |                                             |                                                                             | 1                |                  | 6                | ns          |

| $t_{AD}$                    | Aperture Delay                              |                                                                             |                  | 1                |                  | ns          |

| $t_{AJ}$                    | Aperture Jitter                             |                                                                             |                  | 2                |                  | ps (RMS)    |

|                             | Over Range Recovery Time                    | Differential $V_{IN}$ step from $\pm 3V$ to $0V$ to get accurate conversion |                  |                  | 1                | Clock Cycle |

| $t_{STBY}$                  | Standby Mode Exit Cycle                     |                                                                             |                  | 20               |                  | Cycles      |

**Note 1:** 「絶対最大定格」とは、IC に破壊が発生する可能性のあるリミット値をいいます。「動作定格」とはデバイスが機能する条件を示しますが、特定の性能リミット値を示すものではありません。保証された仕様、試験条件については「電気的特性」を参照してください。保証された仕様はリストに示された試験条件でのみ適用されます。デバイスが記載の試験条件下で動作しない場合、いくつかの性能特性が低下することがあります。

**Note 2:** 特記のない限り、すべての電圧は  $GND = V_{SSA} = V_{SSIO} = 0V$  を基準にして測定されています。

**Note 3:** いずれかの端子で入力電圧 ( $V_{IN}$ ) が電源電圧を超えた場合 ( すなわち  $V_{IN} < V_{SSA}$ 、または  $V_{IN} > V_{DDA}$ 、 $V_{DDIO}$  のとき )、その端子の入力電流を  $25mA$  以下に制限しなければなりません。最大パッケージ入力定格電流 ( $50mA$ ) により、電源電圧を超えて  $25mA$  の電流を流せる端子数は 2 本に制限されます。

**Note 4:** 温度上昇時の動作では、最大消費電力の定格を  $T_{Jmax}$  ( 最大接合部温度 : このデバイスの場合、 $T_{Jmax}$  は  $150^\circ C$  )、 $J_A$  ( 接合部・周囲温度間熱抵抗 )、 $T_A$  ( 周囲温度 ) に従ってディレーティングしなければなりません。任意温度における最大許容消費電力は、 $P_{DMAX} = (T_{Jmax} - T_A) / J_A$  または「絶対最大定格」で示される値のうち、いずれか低い方の値です。ボード実装時におけるこのデバイスの代表的な熱抵抗  $J_A$  は 28 ピン TSSOP では  $96^\circ C/W$ 、25°C での最大許容消費電力は、 $P_{DMAX} = 1,302mW$ 、85°C の最大動作周囲温度では、 $677mW$  になります。通常動作時のこのデバイスの消費電力は代表値で約  $68.6mW$  になることに注意してください。上記の最大許容消費電力の値にまで上がる場合は、ADC10065 が何らかの異常な状態で動作しているときのみです。

**Note 5:** 人体モデルの場合、 $100pF$  のコンデンサから直列抵抗  $1.5k\Omega$  を通して各端子に放電させます。マシン・モデルの場合は、 $220pF$  のコンデンサから直接各端子に放電させます。

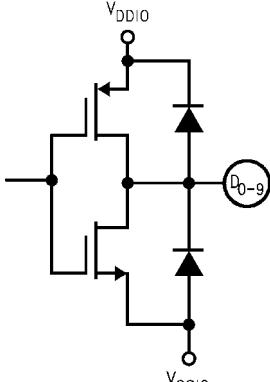

**Note 6:**  $235^\circ C$  のリフロー温度は赤外線リフローを指しています。気相リフロー (VPR: Vapor Phase Reflow) の場合は別の条件が適用されます。気相リフローの場合は最低 60 秒間はパッケージ本体の上面温度を  $183^\circ C$  より高く維持してください。パッケージ本体の表面温度は  $220^\circ C$  を超えてはなりません。 $183^\circ C$  を超えるのが許されるのはリフロー・サイクル 1 回につき 1 回だけです。アナログ入力は、以下に示されるように保護されています。入力電圧が電源電圧レールを超えて  $500mV$  まで振幅する場合にはデバイスが損傷を受けることはありません。ただし、差動入力のいずれかが  $V_{DDA}$  か  $V_{DDIO}$  より高く、かつ一方が  $V_{SSA}$  か  $V_{SSIO}$  より低い場合、入力誤差が生じます。

**Note 7:**  $V_{COM}$  は代表値で、室温で測定されています。試験によって保証されているわけではありません。

**Note 8:** 精度を保証するために、各電源電圧差を  $|V_{DDA} - V_{DDIO}| = 100mV$  にし、かつそれぞれの電源端子に別個のバイパス・コンデンサが必要となります。

**Note 9:**  $2V_{P-P}$  差動入力のテスト条件で、10 ピットの ILSB は  $1.95mV$  になります。

**Note 10:** 代表値 (Typical) は、 $T_A = T_J = 25^\circ C$  で得られる最も標準的な数値です。テスト・リミット値はナショナルセミコンダクター社の平均出荷品質レベル AOQL (Average Outgoing Quality Level)に基づき保証されます。

**Note 11:** 積分非直線性 (INL) は LSB で表され、正と負のフルスケールを通る直線からのアナログ値の偏差として定義されます。

**Note 12:** タイミング特性は、TTL ロジック・レベル (立ち下がりエッジが  $V_{IL} = 0.4V$ 、立ち上がりエッジが  $V_{IH} = 2.4V$ ) でテストされます。

**Note 13:** 最適なダイナミック性能は、リファレンス入力を  $1.2V$  に維持すると得られます。

**Note 14:**  $I_{DDIO}$  とは、出力ドライバのスイッチング処理に消費される電流のことです。この値を決める主な要素は、出力端子の負荷容量、電源電圧、 $V_{DR}$ 、出力信号のスイッチング・レートです。出力信号のスイッチング・レートは入力信号に左右されます。 $I_{DDR}$  は、 $I_{DDR} = V_{DR} \times (C_0 \times f_0 + C_1 \times f_1 + C_2 \times f_2 + \dots + C_{11} \times f_{11})$  の式で計算されます。 $V_{DR}$  は出力ドライバ用の電源電圧、 $C_n$  は当該出力端子の総負荷容量、 $f_n$  は当該出力端子の平均スイッチング周波数です。

**Note 15:** 消費電力には出力ドライバの電力も含まれています ( $f_{IN} = 0 MHz$ )。

**Note 16:** 入力帯域は  $V_{IN}^-$  と  $V_{IN}^+$  間に存在する容量分  $10pF$  によって制限されます。

## 用語の定義

**アーチャ・ディレイ (APERTURE DELAY)** は、クロック・パルスが立ち上がってから入力信号が取り込まれるか保持されるまでの時間です。

**アーチャ・ジッタ (APERTURE JITTER)** は「APERTURE UNCERTAINTY」(アーチャ・ディレイのばらつき)とも言います。サンプルとサンプルの間のアーチャ・ディレイのばらつきです。アーチャ・ジッタは出力のノイズとして現れます。

**同相電圧 (COMMON MODE VOLTAGE:  $V_{CM}$ )** とは、ADC の差動入力端子のいずれにも共通して現れる直流電位です。

**変換レイテンシ (CONVERSION LATENCY)** については「パイプライン・ディレイ」(PIPELINE DELAY)を参照ください。

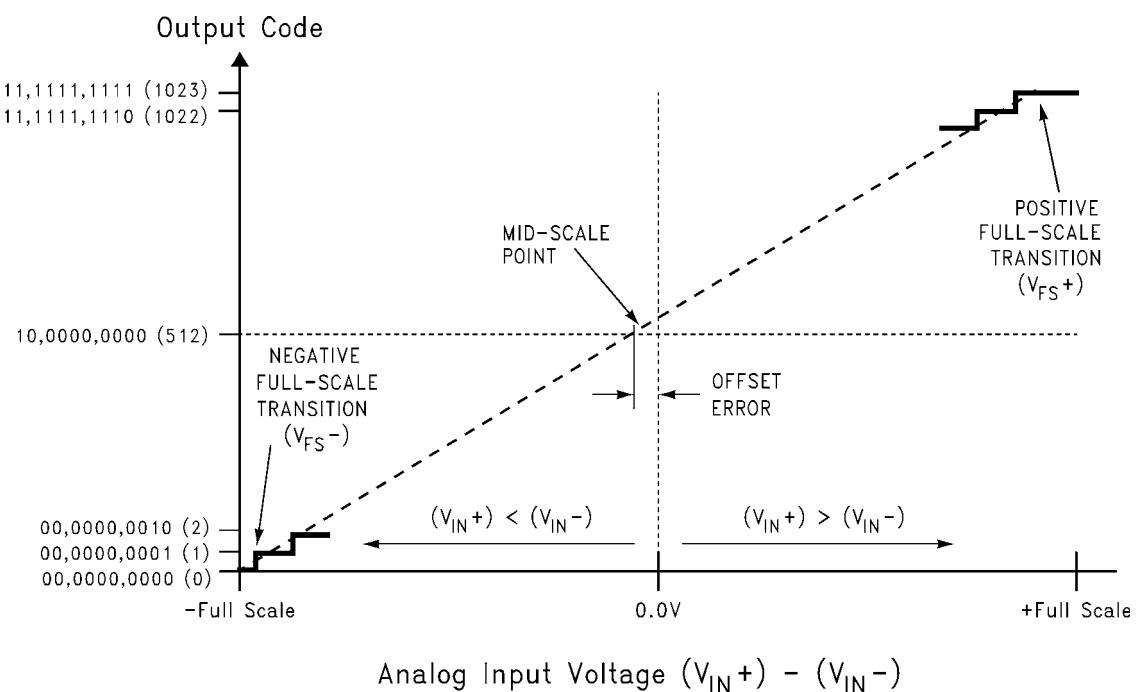

**微分非直線性 (DIFFERENTIAL NON-LINEARITY: DNL)** は、理想的なステップである1LSBからの最大偏差として表されます。

**デューティ・サイクル (DUTY CYCLE)** とは、繰り返し波形の周期に対する High 期間の割合です。本データシートに記載されているデューティ・サイクルの仕様は、ADC のクロック入力信号に対して適用されます。

**有効ビット (EFFECTIVE NUMBER OF BITS: ENOB)** は、信号/(ノイズ+歪み)比またはSINADの別の規定方法です。ENOBは(SINAD - 1.76)/6.02として定義され、この値のビット数をもつ理想的な A/D コンバータに等しいコンバータであることを意味します。

**フルパワー帯域幅 (FULL POWER BANDWIDTH)** は、フルスケール入力に対して再現される出力基本周波数特性で低周波数帯域に対して 3dB 落ちる周波数として測定されます。

**ゲイン誤差 (GAIN ERROR)** は、伝達関数の実測値と理想カープとの偏差です。次の式で計算できます。

ゲイン誤差 = 正側フルスケール誤差 - 負側フルスケール誤差

**積分非直線性 (INTEGRAL NON-LINEARITY: INL)** は、ゼロスケール(最初のコード遷移の 0.5LSB 下)から正のフルスケール(最後のコード遷移の 1.5LSB 上)まで引いた直線からそれぞれ個々のコードとの偏差として表されます。この直線から任意のコードとの偏差は、各コード値の中央から測定します。

**ミッシング・コード (MISSING CODES)** は、ADC から出力されない出力コードです。ADC10065 は、ミッシング・コードのないことが保証されています。

**負のフルスケール誤差 (NEGATIVE FULL SCALE ERROR)** は、負のフルスケール・コードから最初のコードに遷移を生じさせる入力電圧( $V_{IN}^+ - V_{IN}^-$ )の差で、理想値は 0.5LSB です。

**オフセット誤差 (OFFSET ERROR)** は、コード 01 1111 1111 からコード 10 0000 0000 への遷移を引き起こす入力電圧です。

**出力ディレイ (OUTPUT DELAY)** は、クロック入力の立ち上がりエッジから出力端子にアップデートされたデータが現われるまでの遅延時間です。

**パイプライン・ディレイ (PIPELINE DELAY: LATENCY)** は、変換開始からその変換結果が出力バスに有効になるまでの期間をクロックサイクル数で表したものです。任意に与えられたサンプリングに対するデータは、そのサンプリングが行われた後、パイプライン・ディレイおよび出力ディレイの出力ピン上で有効になります。新しいデータはクロック・サイクルごとに有効ですが、その出力データはパイプライン・ディレイ分の変換ラグがあります。

正のフルスケール誤差(POSITIVE FULL SCALE ERROR)は、最後のコード遷移点の実測値と(正側フルスケール - 1.5LSB)の理想値とのずれです。

信号 / ノイズ比 (SIGNAL TO NOISE RATIO: SNR) は、クロック信号の 1/2 以下の周波数における、歪みと DC 成分を除いたその他すべてのスペクトラル成分の実効値に対する入力信号の実効値の比で、dB で表されます。

信号 / (ノイズ + 歪み) 比 (SIGNAL TO NOISE PLUS DISTORTION RATIO: S/N + D) または SINAD) は、クロック信号の 1/2 以下の周波数における、歪みを含め DC 成分を除いたその他すべてのスペクトラル成分の実効値に対する入力信号の実効値の比として表されます。

**スピリアス・フリー・ダイナミック・レンジ (SPURIOUS FREE DYNAMIC RANGE: SFDR)** は、入力信号の実効値に対するピーク・スピリアス信号との差で、dB で表されます。ここで言うピーク・スピリアス信号は、出力スペクトラムに現われる任意のスピリアス信号で、入力に現れるものではありません。

**全高調波歪み (TOTAL HARMONIC DISTORTION: THD)** は、出力に現れる 2 次から 6 次までの高調波レベルの二乗和平方根と基本周波数のレベルとの比で、dBc で表されます。全高調波歪み THD は次式から求められます。

$$THD = 20 \times \log \sqrt{\frac{f_2^2 + f_3^2 + \dots + f_6^2}{f_1^2}}$$

$f_1$  は基本(出力)周波数の実効パワー、 $f_2$  から  $f_6$  は 2 次から 6 次までの高調波の実効パワーです。

**第 2 次高調波歪み (2nd Harm)** は、出力に現れる入力周波数の実効パワーと 2 次高調波のパワーとの差を、dB で表した値です。

**第 3 次高調波歪み (3rd HARM)** は、出力に現れる周波数の実行パワーと 3 次高調波のパワーとの差を、dB で表した値です。

## タイミング図

FIGURE 1. Clock and Data Timing Diagram

## 変換特性

FIGURE 2. Input vs. Output Transfer Characteristic

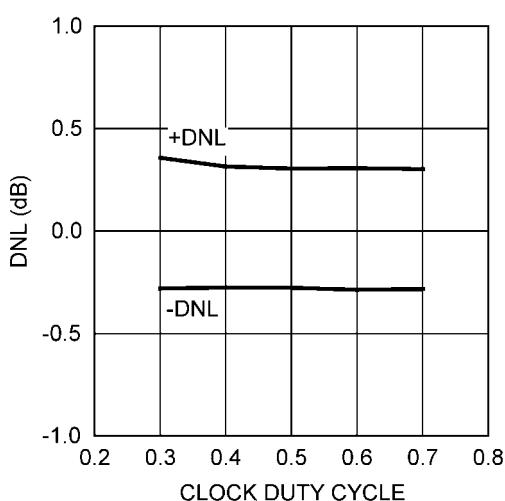

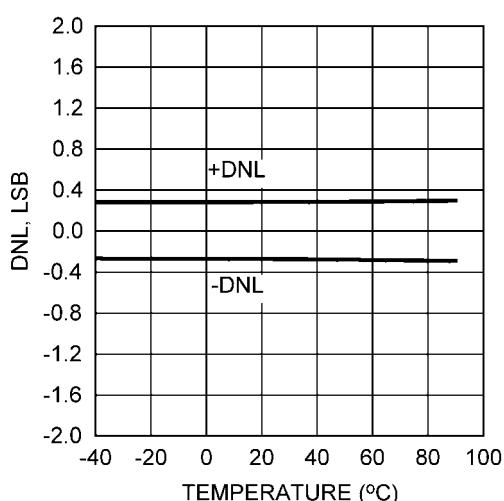

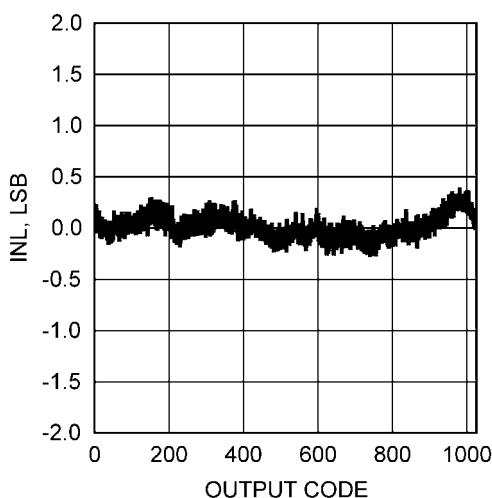

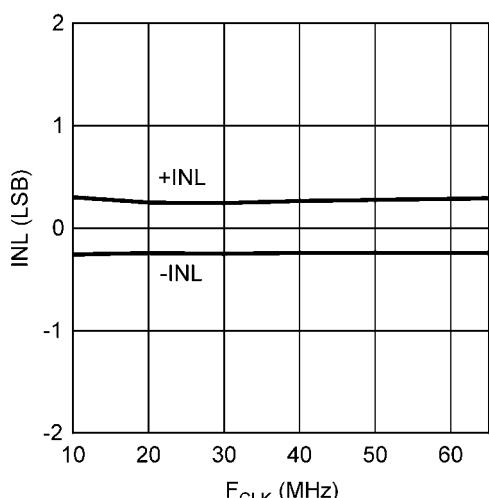

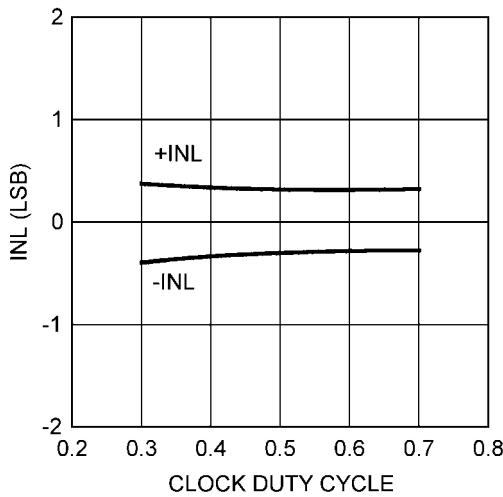

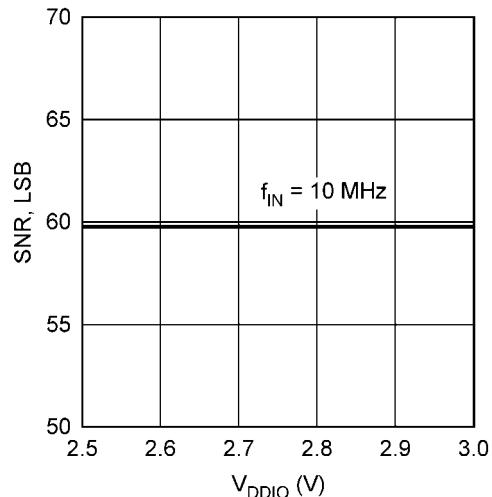

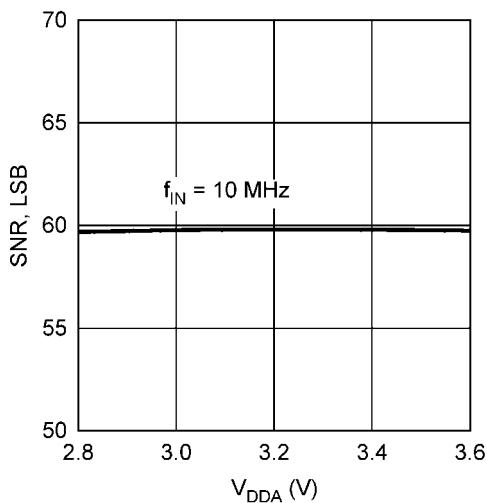

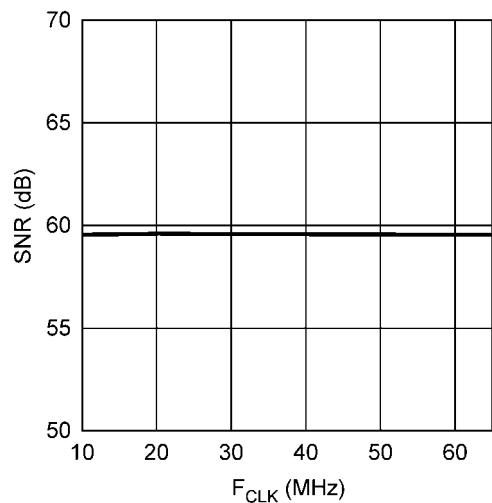

## 代表的な性能特性

特記のない限り次の仕様が適用されます。 $V_{SSA} = V_{SSIO} = 0V$ 、 $V_{DDA} = +3.0V$ 、 $V_{DDIO} = +2.5V$ 、 $V_{IN} = 2V_{P-P}$ 、 $STBY = 0V$ 、 $V_{REF} = 1.2V$ 、(外部供給)  $f_{CLK} = 65MHz$ 、 $f_{IN} = 11MHz$ 、デューティ・サイクル 50%。

### DNL

### DNL vs. $f_{CLK}$

### DNL vs. Clock Duty Cycle (DC input)

### DNL vs. Temperature

### INL

### INL vs. $f_{CLK}$

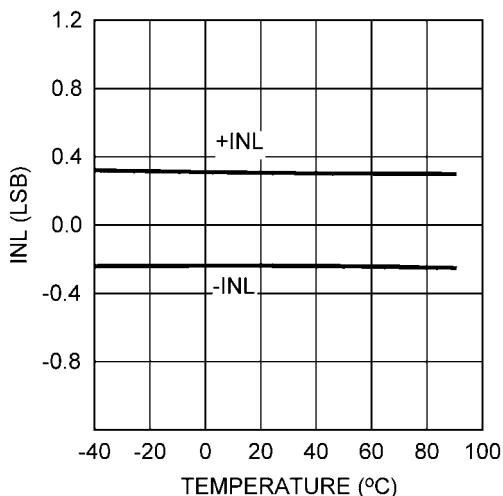

### 代表的な性能特性(つづき)

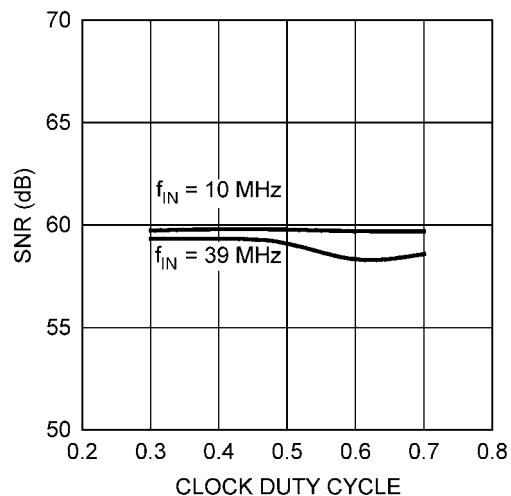

特記のない限り次の仕様が適用されます。 $V_{SSA} = V_{SSIO} = 0V$ 、 $V_{DDA} = +3.0V$ 、 $V_{DDIO} = +2.5V$ 、 $V_{IN} = 2V_{P-P}$ 、 $STBY = 0V$ 、 $V_{REF} = 1.2V$ 、(外部供給) $f_{CLK} = 65MHz$ 、 $f_{IN} = 11MHz$ 、デューティ・サイクル50%。

**INL vs. Clock Duty Cycle**

**SNR vs.  $V_{DDIO}$**

**SNR vs.  $V_{DDA}$**

**SNR vs.  $f_{CLK}$**

**INL vs. Temperature**

**SNR vs. Clock Duty Cycle**

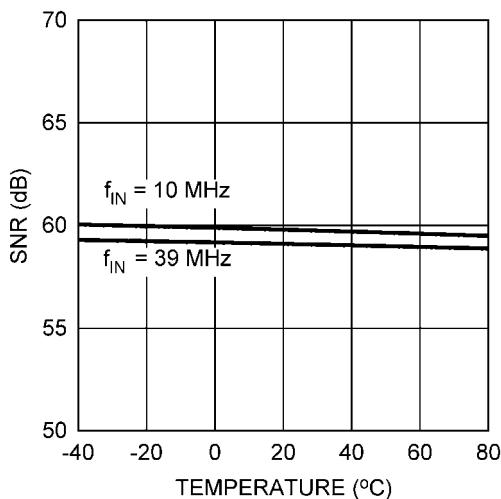

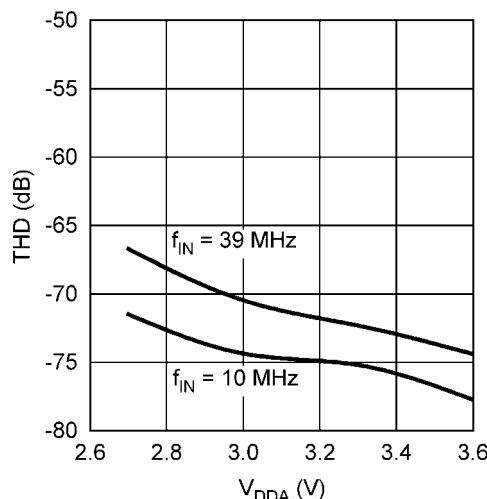

## 代表的な性能特性(つづき)

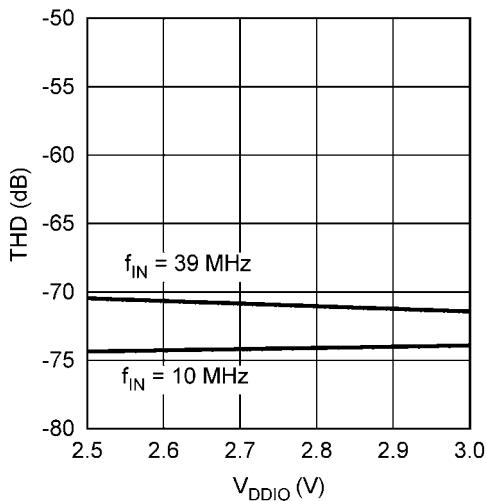

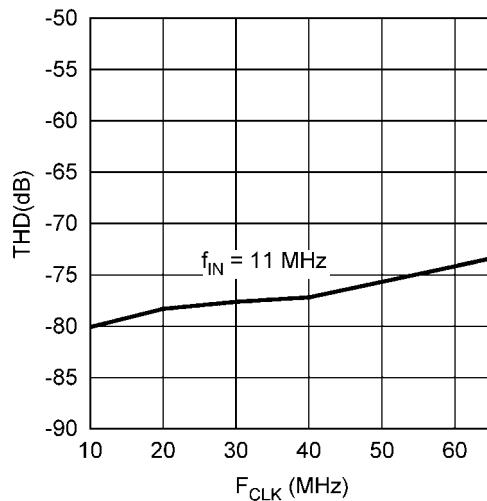

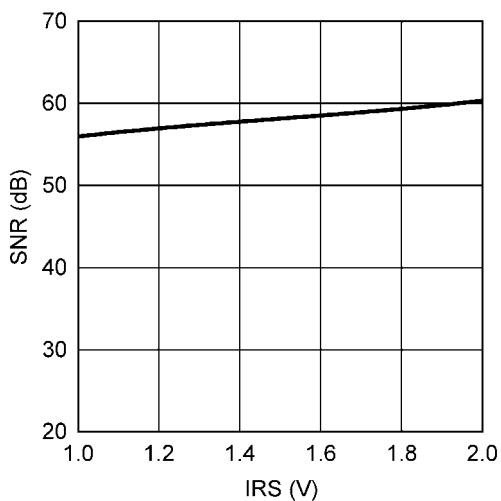

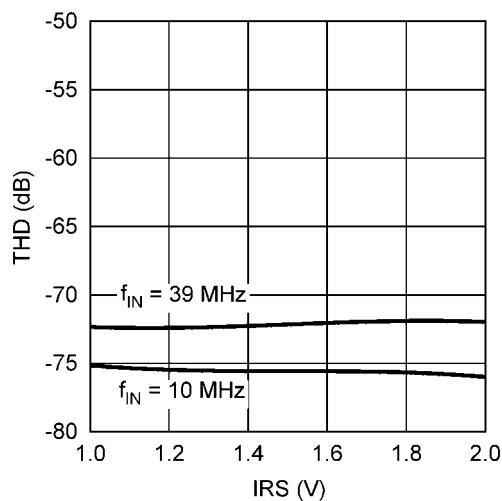

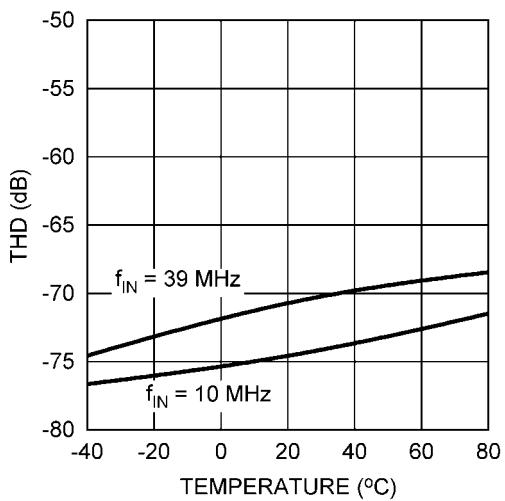

特記のない限り次の仕様が適用されます。 $V_{SSA} = V_{SSIO} = 0V$ 、 $V_{DDA} = +3.0V$ 、 $V_{DDIO} = +2.5V$ 、 $V_{IN} = 2V_{P-P}$ 、 $STBY = 0V$ 、 $V_{REF} = 1.2V$ 、(外部供給) $f_{CLK} = 65MHz$ 、 $f_{IN} = 11MHz$ 、デューティ・サイクル50%。

SNR vs. Temperature

THD vs.  $V_{DDA}$ THD vs.  $V_{DDIO}$ THD vs.  $f_{CLK}$

SNR vs. IRS

THD vs. IRS

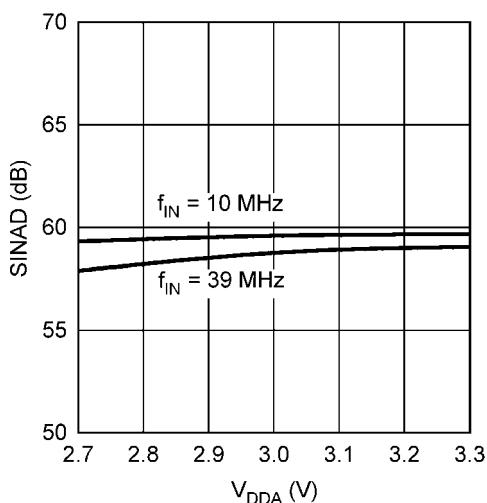

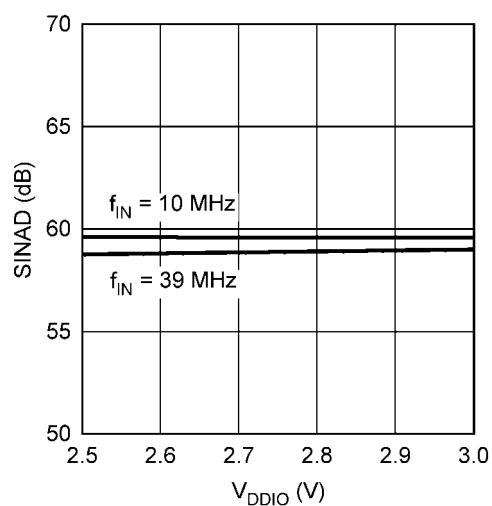

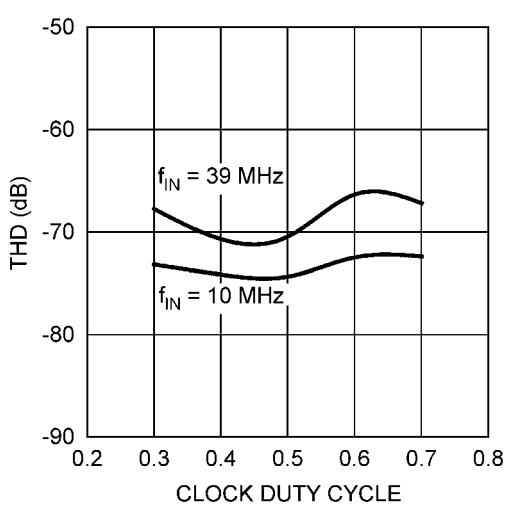

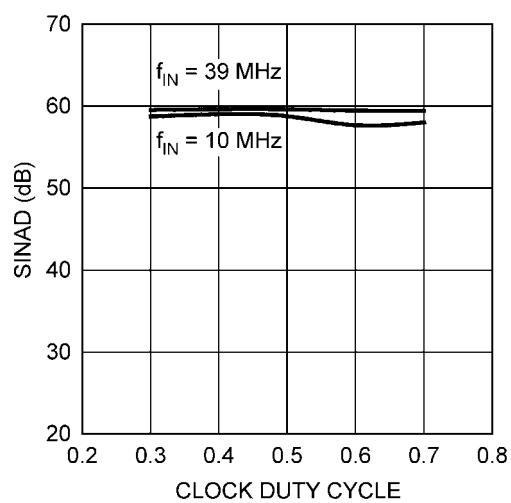

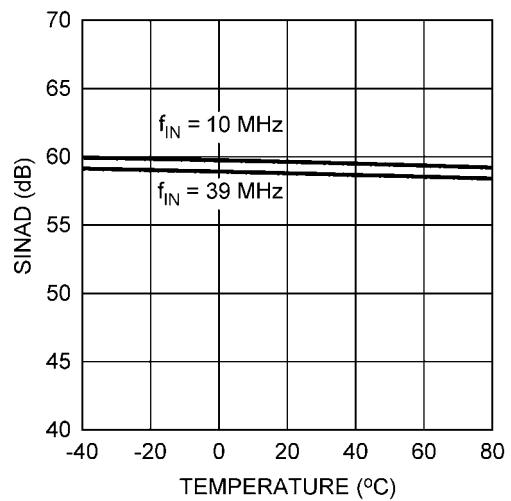

### 代表的な性能特性(つづき)

特記のない限り次の仕様が適用されます。 $V_{SSA} = V_{SSIO} = 0V$ 、 $V_{DDA} = +3.0V$ 、 $V_{DDIO} = +2.5V$ 、 $V_{IN} = 2V_{P-P}$ 、 $STBY = 0V$ 、 $V_{REF} = 1.2V$ 、(外部供給) $f_{CLK} = 65MHz$ 、 $f_{IN} = 11MHz$ 、デューティ・サイクル50%。

**SINAD vs.  $V_{DDA}$**

**SINAD vs.  $V_{DDIO}$**

**THD vs. Clock Duty Cycle**

**SINAD vs. Clock Duty Cycle**

**THD vs. Temperature**

**SINAD vs. Temperature**

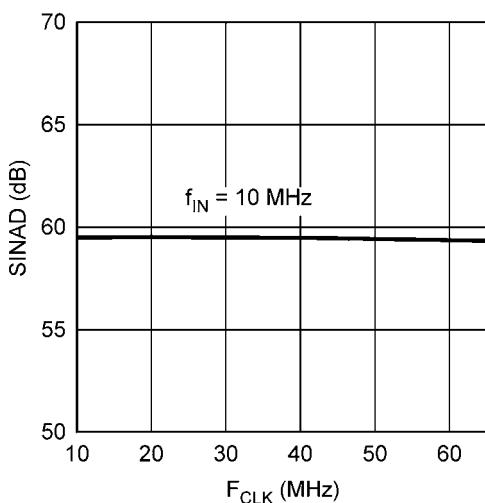

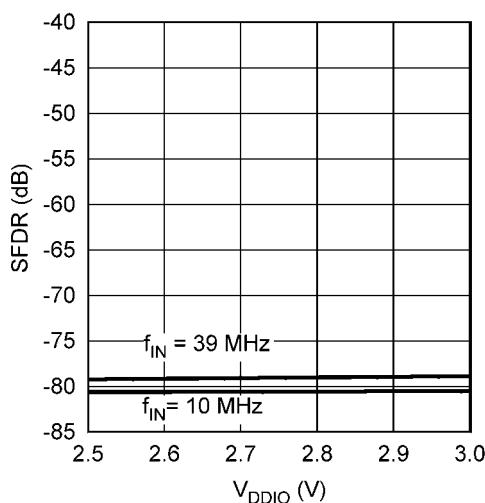

## 代表的な性能特性(つづき)

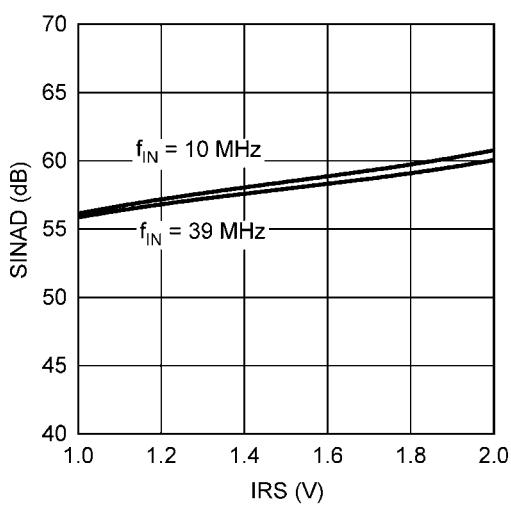

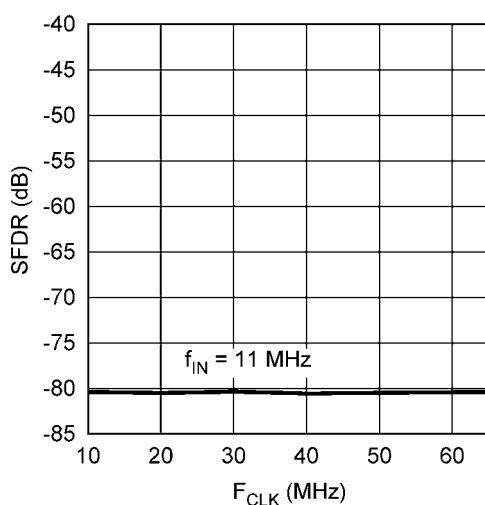

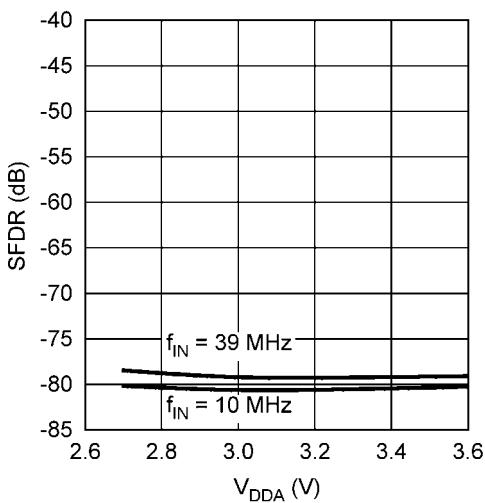

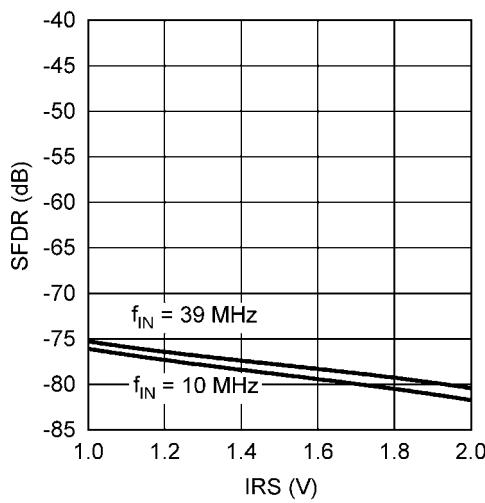

特記のない限り次の仕様が適用されます。 $V_{SSA} = V_{SSIO} = 0V$ 、 $V_{DDA} = +3.0V$ 、 $V_{DDIO} = +2.5V$ 、 $V_{IN} = 2V_{P-P}$ 、 $STBY = 0V$ 、 $V_{REF} = 1.2V$ 、(外部供給) $f_{CLK} = 65MHz$ 、 $f_{IN} = 11MHz$ 、デューティ・サイクル 50%。

SINAD vs.  $f_{CLK}$ SFDR vs.  $V_{DDIO}$

SINAD vs. IRS

SFDR vs.  $f_{CLK}$ SFDR vs.  $V_{DDA}$

SFDR vs. IRS

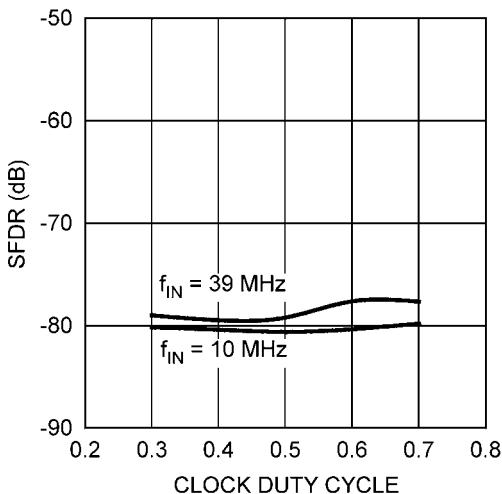

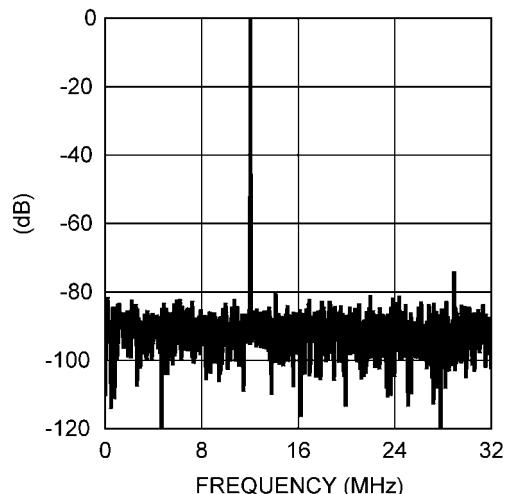

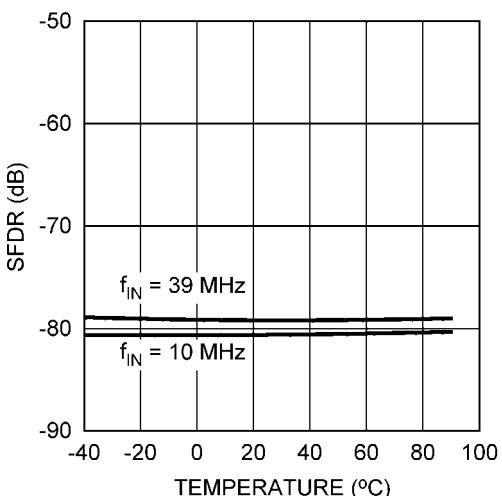

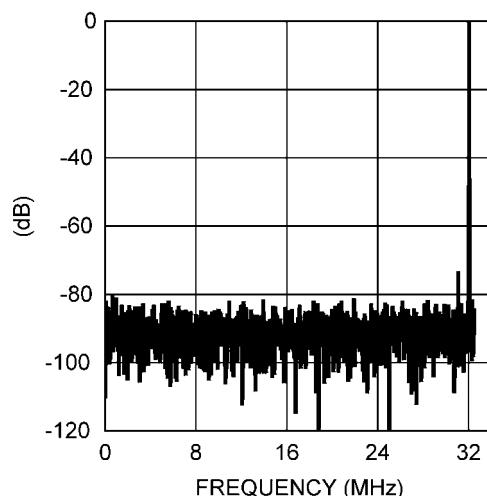

### 代表的な性能特性(つづき)

特記のない限り次の仕様が適用されます。 $V_{SSA} = V_{SSIO} = 0V$ 、 $V_{DDA} = +3.0V$ 、 $V_{DDIO} = +2.5V$ 、 $V_{IN} = 2V_{P-P}$ 、 $STBY = 0V$ 、 $V_{REF} = 1.2V$ 、(外部供給) $f_{CLK} = 65MHz$ 、 $f_{IN} = 11MHz$ 、デューティ・サイクル50%。

SFDR vs. Clock Duty Cycle

Spectral Response @ 11 MHz Input

SFDR vs. Temperature

Spectral Response @ 32 MHz Input

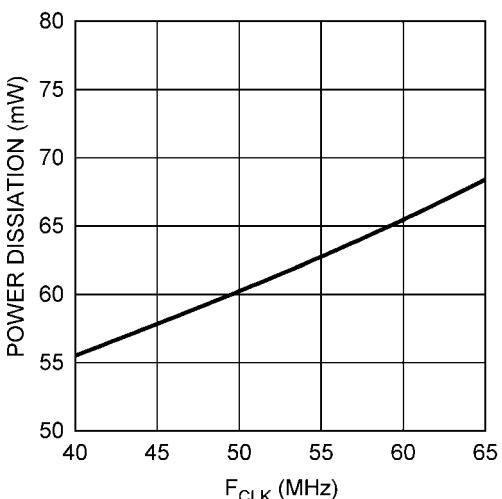

Power Consumption vs.  $f_{CLK}$

## 機能説明

ADC10065 はパイプライン型アーキテクチャを採用し、かつ誤差訂正回路を内蔵しているため、性能が最大限まで発揮されます。差動のアナログ入力信号は 10 ビットのデジタル信号に変換されます。差動モードの場合の各アナログ入力信号のピーク・ツー・ピーク電圧は IRS 端子 (5 ピン) の設定に応じて 1.0V、0.75V、または 0.5V でなければならず、また  $V_{CM}$  を中心電圧として、それぞれ位相を 180° ずらす必要があります。シングルエンド動作を望む場合は  $V_{IN+}$  を  $V_{COM}$  ピン (4 ピン) に接続します。その場合シングルエンド入力信号を  $V_{IN+}$  に印加し、また、電圧範囲の平均値は  $V_{CM}$  でなければなりません。信号振幅は、IRS 端子 (5 ピン) の設定に応じて、2.0V、1.5V、または 1.0V でなければなりません。

## アプリケーション情報

### 1.0 アナログ入力

ADC10065 は、 $V_{IN+}$  と  $V_{IN-}$  の 2 つのシングルエンド・アナログ入力を備えています。この 2 つの端子を組にして差動入力端子として使います。 $V_{COM}$  ピンを用いてコモンモード電圧を設定できます。

### 1.1 基準電圧端子

ADC10065 は基準電圧 1.2V で動作するよう設計されています。 $V_{COM}$ 、 $V_{REFT}$ 、 $V_{REFB}$  の各電圧は基準電圧から生成されています。また、入力信号の振幅が大きいほど THD も劣化します。基準電圧および入力信号に対するすべてのグラウンドは、グラウンド経路に流れるノイズ電流の影響を抑えるため、アナログ・グラウンド層に対して一点アースで接続するのが極めて重要になります。3 本の基準電圧バイパス端子 ( $V_{REF}$ 、 $V_{REFT}$ 、 $V_{REFB}$ ) はバイパス専用です。各端子とグラウンドの間に 0.1 μF のコンデンサを 1 つずつ挿入してください。この 3 本の端子には絶対に負荷を接続しないでください。

### 1.2 $V_{COM}$ 端子

この端子の電圧はコモンモード入力電圧を設定する電圧基準として働きます。また、この端子に  $V_{IN-}$  に接続すると、 $V_{IN+}$  をシングルエンド入力として使用できます。この端子は 0.1 μF 以上のコンデンサを用いたバイパスが必要です。

### 1.3 入力信号

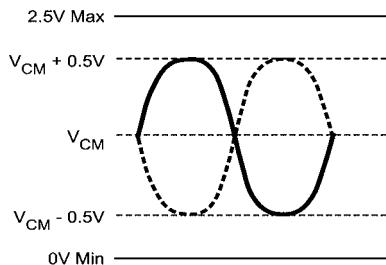

信号入力には  $V_{IN+}$  と  $V_{IN-}$  があります。入力信号振幅は  $V_{IN+} - V_{IN-}$  として定義され、図式的に表わすと Figure 3 のようになります。

FIGURE 3. Input Voltage Waveforms for a 2V<sub>p-p</sub> Input

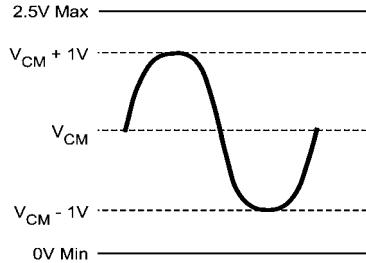

Figure 4 にシングルエンド入力信号を示します。

FIGURE 4. Input Voltage Waveform for a 2V<sub>p-p</sub> Single Ended Input

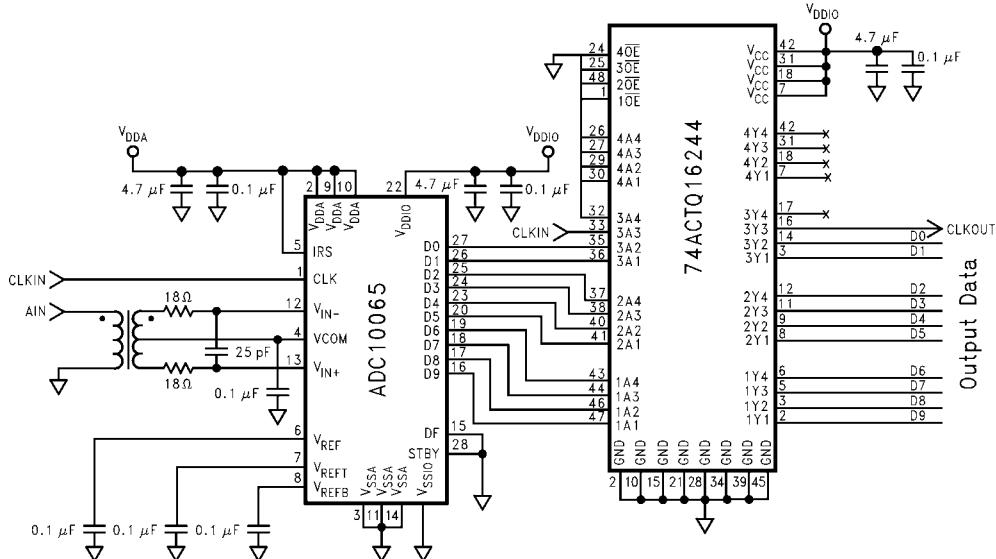

アナログ入力端子の内部回路ではスイッチングが行われるため、入力端子から電流が帰ってきます。この電流をアナログ入力信号の駆動源側で打ち消そうとすると入力信号にノイズが乗ります。これを防ぐには、Figure 5 に示したように、入力端子のそれぞれに 18 Ω の抵抗を 1 つずつ直列に挿入し、さらに入力端子同士を 1 つの 25pF コンデンサで接続してください。取り付ける位置は ADC のすぐ近くにしてください。その理由は、ADC の入力端子が全体の中でも最も敏感な部分であり、入力信号にフィルタをかけるには最後のポイントであるためです。オーバー・サンプリング・アプリケーション（信号周波数の 2 倍以上の周波数でのサンプリング）では 68pF を用いますが、アンダー・サンプリング・アプリケーション（ナイキスト周波数以下のサンプリング）では 10pF を使用してください。2 個の 18 Ω 抵抗と 25pF コンデンサは、-3dB 周波数が 177MHz のローパス・フィルタを形成します。

### 1.4 CLK ピン

CLK 信号はサンプリングのタイミングを決めます。このクロック入力端子は、安定した低ジッタのクロック信号源で駆動してください。クロック周波数の範囲は 20MHz ~ 65MHz まで、パルスの立ち上がり時間、立ち下がり時間はいずれも 2ns 未満とします。クロック信号の配線パターンは最短とし、アナログ、デジタルを問わず他の一切の信号線と交差しないようにしてください。CLK 信号は内部のステート・マシンのクロックとしても使われます。クロック入力が中断されたり周波数があまりにも低いと、出力データの精度が低下するポイントまで内部コンデンサの電荷を消失する可能性があります。この理由によりサンプリング・レートの下限は 20MSPS となっています。すべての A/D コンバータで、クロックのデューティ・サイクルは性能に影響します。しかし正確なデューティ・サイクルを維持するのは難しいため、ADC10065 では広い範囲のデューティ・サイクルに対して性能を発揮するように設計されています。性能の規定と保証はクロックのデューティ・サイクルが 50% の場合ですが、40% ~ 60% の範囲であれば通常は性能が維持されます。

### 1.5 STBY ピン

コンバータが使われない場合には、STBY 端子を High レベルにすると ADC10065 がパワーダウン・モードになります。これによって、未使用時の消費電力が抑えられます。この状態での消費電力は 15mW です。パワーダウン・モード時の出力データ端子の状態がどうなるかは決まっていません。パワーダウン・モード時の消費電力はクロック周波数の影響を受けず、またクロック信号が入力されても影响しません。パワーダウン中のパイプライン中のデータは、破壊されます。

### 1.6 DF ピン

DF ピンを High レベルにすると、ADC10065 の出力データ・フォーマットは 2 の補数になります。DF ピンを Low レベルにすると出力フォーマットはオフセット・バイナリになります。

## アプリケーション情報(つづき)

### 1.7 IRS ピン

IRS(入力範囲選択)ピンによってフルスケール出力を生む入力信号振幅を選択します。次の表に IRS ピンの機能を示します。

TABLE 1. IRS Pin Functions

| IRS Pin   | Full-Scale Input |

|-----------|------------------|

| $V_{DDA}$ | $2.0V_{PP}$      |

| $V_{SSA}$ | $1.5V_{PP}$      |

| Floating  | $1.0V_{PP}$      |

### 1.8 出力ピン

ADC10065には、TTL/CMOS互換のデジタル・データ出力端子が10本付いています。DF端子およびSTBY端子にLowレベルの電圧を印加している間は、この出力端子にオフセット・データがバイナリで出力されます。 $t_{OD}$ 時間も出力タイミングの情報はないですが、有効な出力データをとらえる簡単な方法の1つは、変換クロック・パルスの立ち上がり端でデータをラッチすることです。容量の多いバスを駆動するときは注意が必要です。変換のたび

に出力ドライバで充電しなければならない容量が増えるほど、 $V_{DDIO}$ と $V_{SSIO}$ に流れる瞬時デジタル電流の量が増えます。このような大きな充電電流スパイクは、チップ上でのグラウンド・ノイズの原因となり、またアナログ回路部にも結合するため、動的性能が劣化しかねません。適切なバイパス、負荷容量の低減、グラウンド層の適切な設計等によって、このような現象の軽減が図れます。また、バス・ラインの負荷容量が仕様値 $10\text{pF}/\text{pin}$ を超えると $t_{OD}$ が増え、その結果、ADCの出力データを正しくラッチするのが難しくなります。その場合、動的性能が劣化する恐れがあります。デジタル出力のスイッチングによるノイズを最小にするには、デジタル出力の負荷電流を最小にします。これを実現するには、ADCの出力端子とそれ以降の回路の間に、バッファICを設けます。ADCの出力を1バッファ入力にのみ接続すれば、配線容量や回路容量の遮断と出力電流の低減が図れ、性能低下を回避できます。

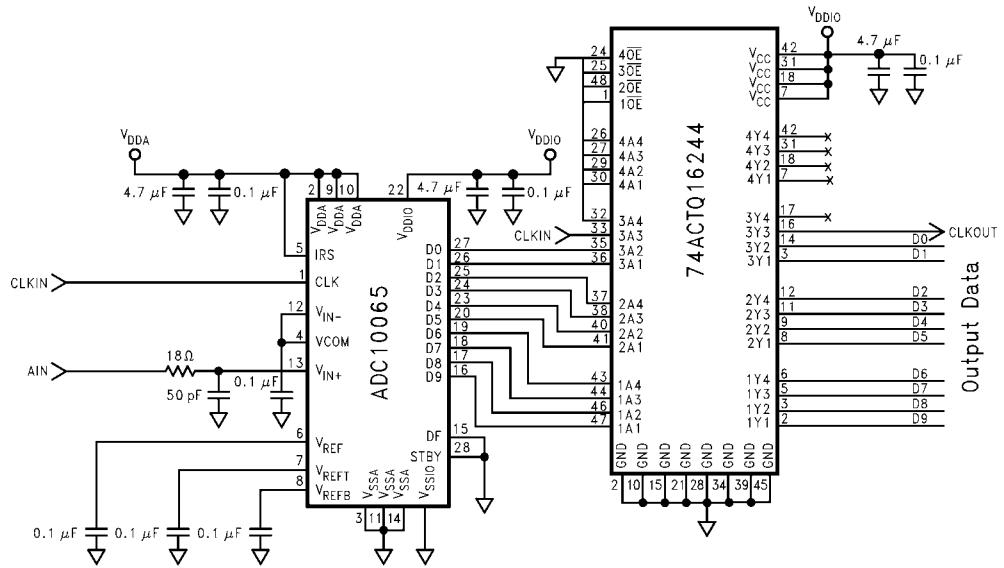

### 1.9 アプリケーション回路

ADC10065を使用した簡単な回路例を次に示します。Figure 5は差動入力の例、Figure 6はシングルエンド・アプリケーション回路の例です。

FIGURE 5. A Simple Application Using a Differential Driving Source

## アプリケーション情報(つづき)

FIGURE 6. A Simple Application Using a Single Ended Driving Source

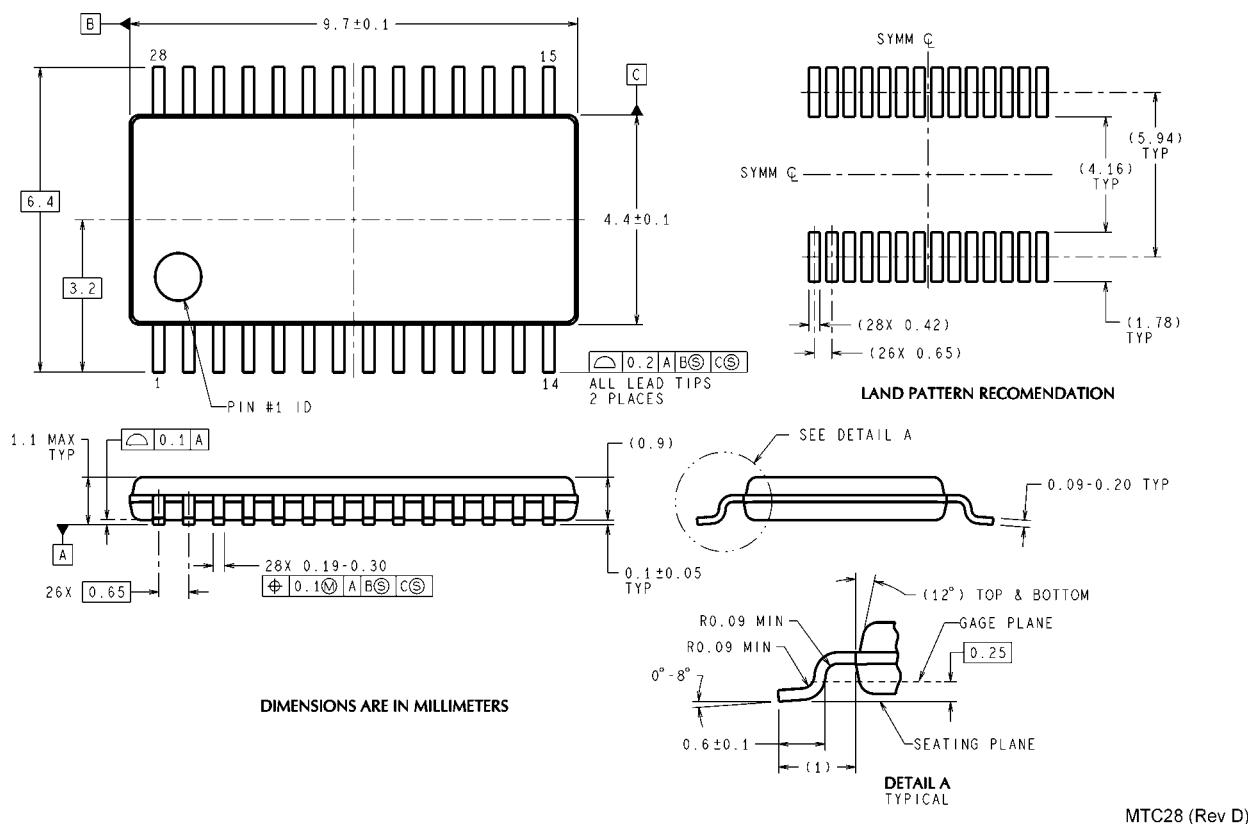

## 外形寸法図 単位は millimeters

**28-Lead TSSOP Package**

**Ordering Number ADC10065CIMT**

**NS Package Number MTC28**

MTC28 (Rev D)

このドキュメントの内容はナショナルセミコンダクター社製品の関連情報として提供されます。ナショナルセミコンダクター社は、この発行物の内容の正確性または完全性について、いかなる表明または保証もいたしません。また、仕様と製品説明を予告なく変更する権利を有します。このドキュメントはいかなる知的財産権に対するライセンスも、明示的、黙示的、禁反言による惹起、またはその他の問い合わせ、付与するものではありません。

試験や品質管理は、ナショナルセミコンダクター社が自社の製品保証を維持するために必要と考える範囲に用いられます。政府が課す要件によって指定される場合を除き、各製品のすべてのパラメータの試験を必ずしも実施するわけではありません。ナショナルセミコンダクター社は製品適用の援助や購入者の製品設計に対する義務は負いかねます。ナショナルセミコンダクター社の部品を使用した製品および製品適用の責任は購入者にあります。ナショナルセミコンダクター社の製品を用いたいかなる製品の使用または供給に先立ち、購入者は、適切な設計、試験、および動作上の安全手段を講じなければなりません。

それら製品の販売に関するナショナルセミコンダクター社との取引条件で規定される場合を除き、ナショナルセミコンダクター社は一切の義務を負わないものとし、また、ナショナルセミコンダクター社の製品の販売が使用、またはその両方に関連する特定目的への適合性、商品の機能性、ないしは特許、著作権、または他の知的財産権の侵害に関連した義務または保証を含むいかなる表明または默示的保証も行いません。

## 生命維持装置への使用について

ナショナルセミコンダクター社の製品は、ナショナルセミコンダクター社の最高経営責任者(CEO)および法務部門(GENERAL COUNSEL)の事前の書面による承諾がない限り、生命維持装置または生命維持システム内のきわめて重要な部品に使用することは認められていません。

ここで、生命維持装置またはシステムとは(a)体内に外科的に使用されることを意図されたもの、または(b)生命を維持あるいは支持するものをいい、ラベルにより表示される使用法に従って適切に使用された場合に、この不具合が使用者に身体的障害を与えると予想されるものをいいます。重要な部品とは、生命維持にかかわる装置またはシステム内のすべての部品をいい、これの不具合が生命維持用の装置またはシステムの不具合の原因となりそれらの安全性や機能に影響を及ぼすことが予想されるものをいいます。

National Semiconductor とナショナルセミコンダクターのロゴはナショナルセミコンダクターコーポレーションの登録商標です。その他のブランドや製品名は各権利所有者の商標または登録商標です。

Copyright © 2007 National Semiconductor Corporation

製品の最新情報については [www.national.com](http://www.national.com) をご覧ください。

ナショナルセミコンダクタージャパン株式会社

本社 / 〒135-0042 東京都江東区木場 2-17-16 TEL.(03)5639-7300

技術資料(日本語/英語)はホームページより入手可能です。

[www.national.com/jpn/](http://www.national.com/jpn/)

# ご注意

日本テキサス・インスツルメンツ株式会社（以下TIJといいます）及びTexas Instruments Incorporated（TIJの親会社、以下TIJないしTexas Instruments Incorporatedを総称してTIといいます）は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIJとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIJの標準販売契約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIJとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。TI製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI製部品を使用したお客様の製品及びアプリケーションについて想定される危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明しておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならぬ場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、かつその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの默示的保証を無効にし、かつ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任も負いません。

TIは、TIの製品が、安全でないことが致命的となる用途ないしアプリケーション（例えば、生命維持装置のように、TI製品に不良があった場合に、その不良により相当な確率で死傷等の重篤な事故が発生するようなもの）に使用されることを認めておりません。但し、お客様とTIの双方の権限有る役員が書面でそのような使用について明確に合意した場合は除きます。たとえTIがアプリケーションに関連した情報やサポートを提供したとしても、お客様は、そのようなアプリケーションの安全面及び規制面から見た諸問題を解決するために必要とされる専門的知識及び技術を持ち、かつ、お客様の製品について、またTI製品をそのような安全でないことが致命的となる用途に使用することについて、お客様が全ての法的責任、規制を遵守する責任、及び安全に関する要求事項を満足させる責任を負っていることを認め、かつそのことに同意します。さらに、もし万一、TIの製品がそのような安全でないことが致命的となる用途に使用されたことによって損害が発生し、TIないしその代表者がその損害を賠償した場合は、お客様がTIないしその代表者にその全額の補償をするものとします。

TI製品は、軍事的用途もしくは宇宙航空アプリケーションないし軍事的環境、航空宇宙環境にて使用されるようには設計もされていませんし、使用されることを意図されておりません。但し、当該TI製品が、軍需対応グレード品、若しくは「強化プラスティック」製品としてTIが特別に指定した製品である場合は除きます。TIが軍需対応グレード品として指定した製品のみが軍需品の仕様書に合致いたします。お客様は、TIが軍需対応グレード品として指定していない製品を、軍事的用途もしくは軍事的環境下で使用することは、もっぱらお客様の危険負担においてなされるということ、及び、お客様がもっぱら責任をもって、そのような使用に関して必要とされる全ての法的要件及び規制上の要求事項を満足させなければならないことを認め、かつ同意します。

TI製品は、自動車用アプリケーションないし自動車の環境において使用されるようには設計もされていませんし、また使用されることを意図されておりません。但し、TIがISO/TS 16949の要求事項を満たしていると特別に指定したTI製品は除きます。お客様は、お客様が当該TI指定品以外のTI製品を自動車用アプリケーションに使用しても、TIは当該要求事項を満たしていなかったことについて、いかなる責任も負わないことを認め、かつ同意します。

Copyright © 2011, Texas Instruments Incorporated

日本語版 日本テキサス・インスツルメンツ株式会社

## 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。

### 1. 静電気

- 素手で半導体製品単体を触らないこと。どうしても触る必要がある場合は、リストストラップ等で人体からアースをとり、導電性手袋等をして取り扱うこと。

- 弊社出荷梱包単位（外装から取り出された内装及び個装）又は製品単品で取り扱いを行う場合は、接地された導電性のテーブル上で（導電性マットにアースをとったもの等）、アースをした作業者が行うこと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

- 前記のリストストラップ・導電性手袋・テーブル表面及び実装装置類の接地等の静電気帯電防止措置は、常に管理されその機能が確認されていること。

### 2. 溫・湿度環境

- 温度：0～40°C、相対湿度：40～85%で保管・輸送及び取り扱いを行うこと。（但し、結露しないこと。）

- 直射日光があたる状態で保管・輸送しないこと。

### 3. 防湿梱包

- 防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装すること。

### 4. 機械的衝撃

- 梱包品（外装、内装、個装）及び製品単品を落下させたり、衝撃を与えないこと。

### 5. 熱衝撃

- はんだ付け時は、最低限260°C以上の高温状態に、10秒以上さらさないこと。（個別推奨条件がある時はそれに従うこと。）

### 6. 汚染

- はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質（硫黄、塩素等ハロゲン）のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。（不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。）

以上