# ADC12DS105

***ADC12DS105 Dual 12-Bit, 105 MSPS A/D Converter with Serial LVDS Outputs***

Literature Number: JAJSAO2

ご注意:この日本語データシートは参考資料として提供しており、内容が最新でない場合があります。製品のご検討およびご採用に際しては、必ず最新の英文データシートをご確認ください。

2008年2月

ADC12DS105

シリアル LVDS 出力付デュアル 12 ビット、105MSPS A/D コンバータ

概要

ADC12DS105 は、2 つのアナログ入力信号を最高 105MSPS のサンプリング・レートで、12 ビットのデジタル・ワードに変換できる、高性能 CMOS A/D コンバータです。デジタル出力はシリアル化されて、差動 LVDS 信号ペアとして提供されます。デジタル誤差補正機能とサンプル / ホールド回路を備えた差動パイプライン型アーキテクチャを採用し、消費電力と外付け部品を最小限に抑えながら優れた性能を発揮します。ADC12DS105 は +3.0V または +3.3V 単一電源で動作します。パワーダウン機能によって消費電力は非常に低いレベルに抑えられますが、わずかなウェイクアップ時間で通常動作に復帰できます。差動入力は 2V のフルスケール差動入力振幅に対応可能です。ADC12DS105 には、安定した 1.2V 内部リファレンスが用意され、また 1.2V の外部リファレンスでも動作できます。デューティ・サイクル・スタビライザは、広範囲なクロック・デューティ・サイクルで性能を保持します。シリアル・インターフェースによって内部レジスタへのアクセスが可能で、ADC12DS105 の機能を完全に制御できます。ADC12DS105 は 60 ピンの LLP パッケージで提供され、産業用温度範囲 (-40 ~ +85) で動作します。

特長

- クロック・デューティ・サイクル・スタビライザ

- + 3.0V または 3.3V 単一電源動作

- シリアル LVDS 出力

- シリアル制御インターフェース

- オーバーレンジ出力

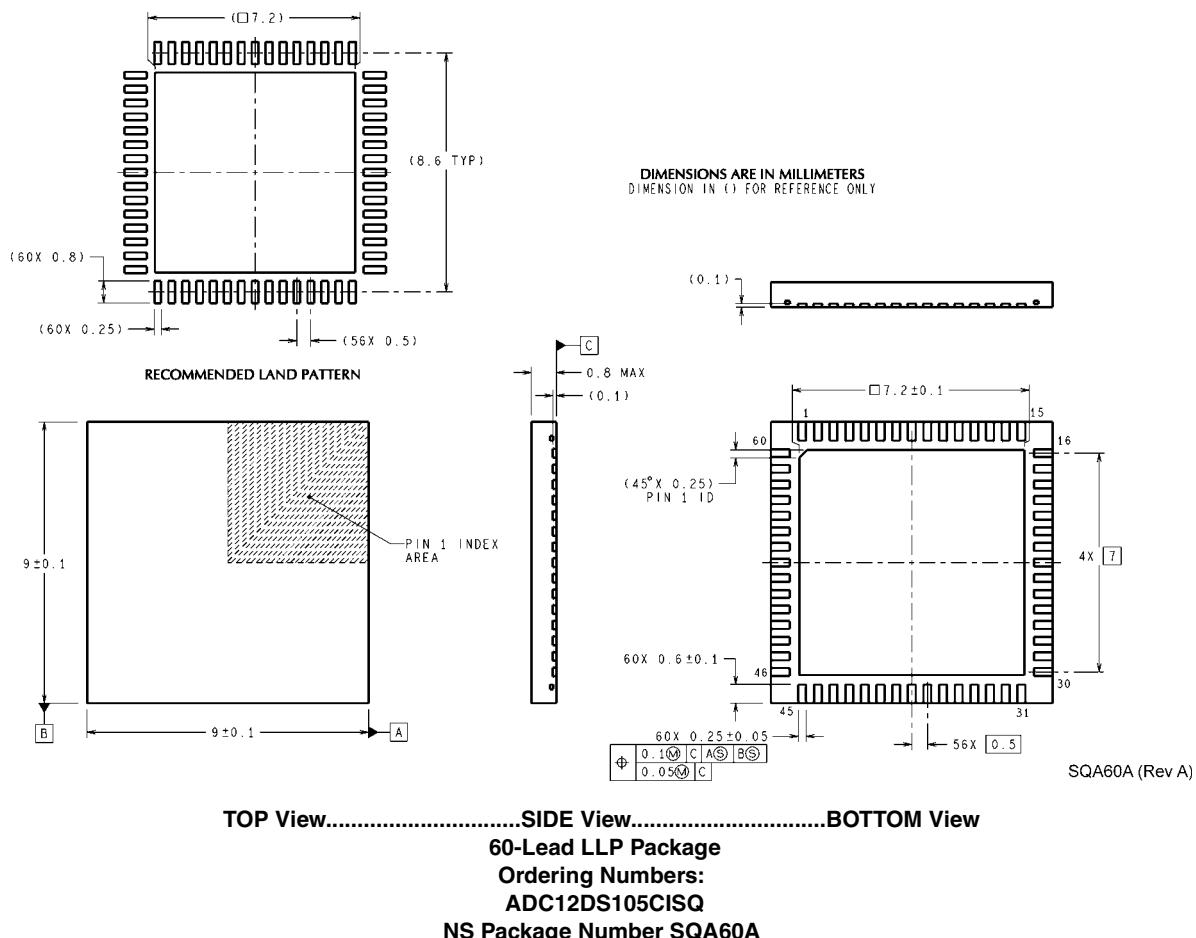

- 60 ピン LLP パッケージ ( $9 \times 9 \times 0.8\text{mm}$ 、 $0.5\text{mm}$  ピンピッチ)

### 主な仕様

|                                   |                |

|-----------------------------------|----------------|

| 分解能                               | 12 ピット         |

| 変換レート                             | 105MSPS        |

| SN 比 ( $f_{IN} = 240\text{MHz}$ ) | 68.5dBFS (typ) |

| SFDR ( $f_{IN} = 240\text{MHz}$ ) | 83dBFS (typ)   |

| フルパワー帯域幅                          | 1GHz (typ)     |

| 消費電力                              | 1 W (typ)      |

## アプリケーション

- 高 IF サンプリング・レシーバ

無線基地局レシーバ

試験装置および測定機器

通信機器

携帯機器

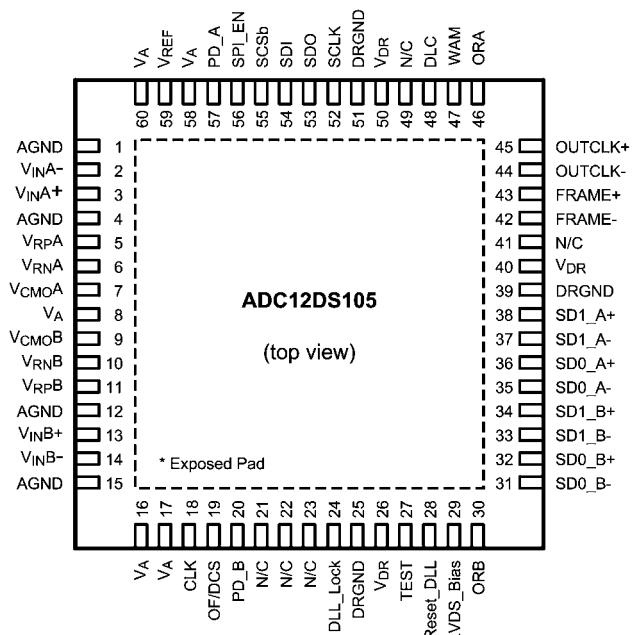

ピン配置図

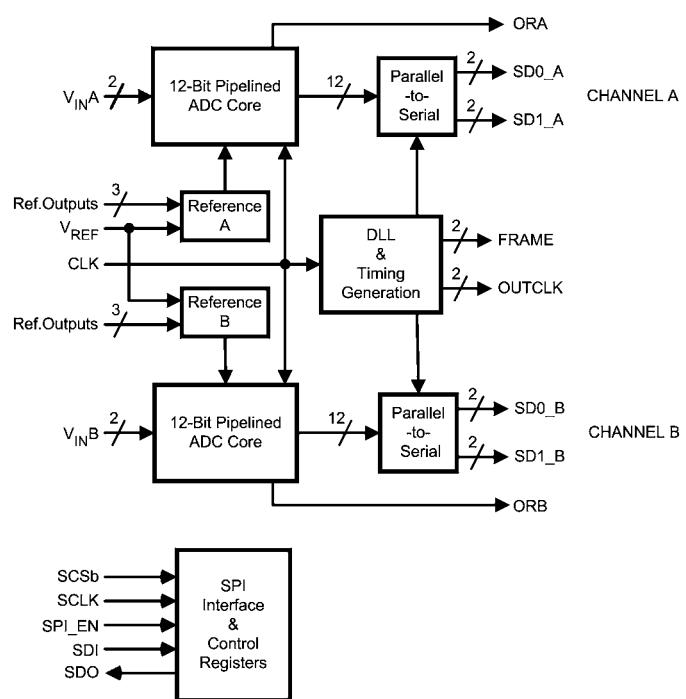

## ブロック図

## 製品情報

| Industrial ( $-40^{\circ}\text{C} \leq T_A \leq +85^{\circ}\text{C}$ ) | Package                                            |

|------------------------------------------------------------------------|----------------------------------------------------|

| ADC12DS105CISQ                                                         | 60 Pin LLP                                         |

| ADC12DS105LFEB                                                         | Evaluation Board for<br>Input Frequency $< 70$ MHz |

## ピン説明および等価回路

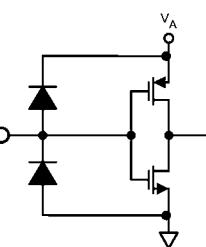

| ピン番号            | シンボル                         | 等価回路                                                                                | 説明                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------|------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>アナログ I/O</b> |                              |                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3<br>13         | $V_{IN A} +$<br>$V_{IN B} +$ |    |                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2<br>14         | $V_{IN A}-$<br>$V_{IN B}-$   |    | 差動アナログ入力ピン。差動フルスケール入力信号レベルは、各入力ピンの信号がコモンモード電圧 $V_{CM}$ を中心電圧として、 $2V_{P-P}$ です。                                                                                                                                                                                                                                                                                                                                                             |

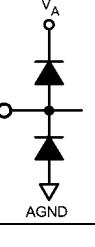

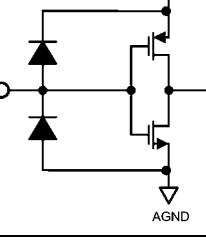

| 5<br>11         | $V_{RP A}$<br>$V_{RP B}$     |    |                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 7<br>9          | $V_{CMO A}$<br>$V_{CMO B}$   |   | これらのピンを、低 ESL (等価直列インダクタンス) の $0.1\mu F$ コンデンサにより、浮遊インダクタンスを最小にするためピンのごく近くで AGND にバイパスします。 $V_{RP}$ と $V_{RN}$ の間のできるだけピンの近くに 0201 サイズの $0.1\mu F$ のコンデンサを配置し、 $1\mu F$ のコンデンサを並列に接続します。 $V_{RP}$ と $V_{RN}$ には負荷を接続しないでください。 $V_{CMO}$ は温度的に安定した $1.5V$ リファレンスとして、 $1mA$ までの負荷に対応できます。                                                                                                                                                     |

| 6<br>10         | $V_{RN A}$<br>$V_{RN B}$     |   | 差動アナログ入力、 $V_{IN}$ に対するコモンモード電圧の供給のために $V_{CMO}$ の使用を推奨します。                                                                                                                                                                                                                                                                                                                                                                                 |

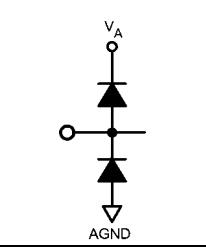

| 59              | $V_{REF}$                    |  | リファレンス電圧。本デバイスは内部で生成する $1.2V$ リファレンス電圧を備えています。内部リファレンスを使用する場合、 $V_{REF}$ は、低等価直列インダクタンス (ESL) の $0.1\mu F$ および $1\mu F$ コンデンサで AGND にデカップルする必要があります。<br>このピンは $1.2V$ 外部リファレンス電圧で駆動できます。<br>このピンは、電流をソースまたはシンクするために使用してはなりません。                                                                                                                                                                                                               |

| 29              | LVDS_Bias                    |                                                                                     | LVDS ドライバ用バイアス抵抗をこのピンとアナログ・グラウンド間に接続します。標準値は $3.6K$ です。                                                                                                                                                                                                                                                                                                                                                                                     |

| <b>デジタル I/O</b> |                              |                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                             |

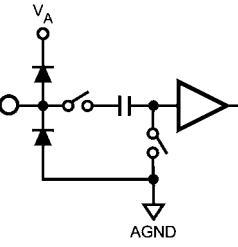

| 18              | CLK                          |  | クロック入力ピン。<br>アナログ入力は、クロック入力の立ち上がりエッジでサンプリングされます。                                                                                                                                                                                                                                                                                                                                                                                            |

| 28              | Reset_DLL                    |  | Reset_DLL 入力。このピンは通常動作では Low です。入力クロック周波数が突然変化すると、内部のタイミング回路のロックが外れる場合があります。このピンを $1\mu s$ だけ High にしてサイクルすると、DLL を再ロックすることができます。Reset_DLL をアサートした後、DLL がロックされるまでに数 $\mu s$ かかります。                                                                                                                                                                                                                                                          |

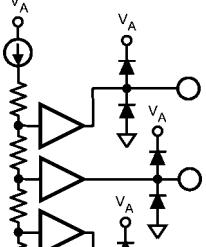

| 19              | OF/DCS                       |  | 入力クロック・モードと出力データ・フォーマットを制御する 4 ステート入力のピン。<br>OF/DCS = $V_A$ の場合、出力データのフォーマットは 2 の補数となり、入力クロックにデューティ・サイクル安定化機能が適用されません。<br>OF/DCS = AGND の場合、出力データのフォーマットはオフセット・バイナリとなり、入力クロックにはデューティ・サイクル安定化機能が適用されません。<br>OF/DCS = $(2/3)*V_A$ の場合、出力データのフォーマットは 2 の補数となり、入力クロックにはデューティ・サイクル安定化機能が適用されます。<br>OF/DCS = $(1/3)*V_A$ の場合、出力データのフォーマットはオフセット・バイナリとなり、入力クロックにはデューティ・サイクル安定化機能が適用されます。<br>Note: この信号は SPI_EN が High で SPI インタフェースがイネーブルの場合は無効です。 |

## ピン説明および等価回路(つづき)

| ピン番号     | シンボル                 | 等価回路                                                                                | 説明                                                                                                                                                                                                                                                                                                                                 |

|----------|----------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 57<br>20 | PD_A<br>PD_B         |                                                                                     | パワーダウンをコントロールする 2 ステート入力。<br>PD = $V_A$ でパワーダウン・モードになり、消費電力が低減されます。<br>PD = AGND では通常動作になります。<br>Note: この信号は SPI_EN が High で SPI インタフェースがイネーブルの場合は無効です。                                                                                                                                                                            |

| 27       | TEST                 |                                                                                     | テスト・モード。この信号を High にすると、固定のテスト・パターン (101001100011 MSB LSB の順序) がデータ出力に供給されます。<br>この信号を Low にするとデバイスは通常の動作モードになります。<br>Note: この信号は SPI_EN が High で SPI インタフェースがイネーブルの場合は無効です。                                                                                                                                                       |

| 47       | WAM                  |    | ワード整列モード。<br>シングル・レーン・モードにするには、このピンは論理 0 に設定しなければなりません。<br>この信号を論理 0 にした場合、デュアル・レーン・モードの場合にのみシリアル・データ・ワードは半ワードだけオフセットされます。この信号を論理 1 にすると、シリアル・データは相互に整列します。<br>Note: この信号は SPI_EN が High で SPI インタフェースがイネーブルの場合は無効です。                                                                                                              |

| 48       | DLC                  |                                                                                     | デュアル・レーン構成。デュアル・レーン・モードはこの信号を論理 0 にすると選択されます。この信号を論理 1 にすると、各チャネルのデータはすべてシングル・レーン (SD1_x) に供給されます。<br>Note: この信号は SPI_EN が High で SPI インタフェースがイネーブルの場合は無効です。                                                                                                                                                                       |

| 45<br>44 | OUTCLK +<br>OUTCLK - |  | シリアル・クロックこの差動 LVDS 信号ペアによってシリアル・データ出力と同期したシリアル・クロックが供給されます。このクロックの立ち上がりおよび立ち下がりでシリアル・データ・ビットは各シリアル・データ出力に供給されます。この差動出力はデバイスの電源がオンとなっていれば、常にイネーブルになります。パワーダウン・モードでは、この出力は論理 Low の状態に保持されます。この信号ペアに対しては伝送ラインの遠端に 100 Ω の終端抵抗を必ず使用しなければなりません。                                                                                         |

| 43<br>42 | FRAME +<br>FRAME -   |  | シリアル・データ・フレーム。この差動 LVDS 信号ペアはシリアル・データ・ワードの境界で遷移します。SD1_A + / - および SD1_B + / - 出力ワードは常にフレーム信号の立ち上がりエッジで始まります。デュアル・レーン・モードの場合は、フレーム信号の立ち下がりエッジが SD0_A + / - および SD0_B + / - 信号ペアに現れるシリアル・データ・ワードの開始を定めます。この差動出力はデバイスの電源がオンとなっていれば、常にイネーブルになります。パワーダウン・モードでは、この出力は論理 Low の状態に保持されます。この信号ペアに対しては伝送ラインの遠端に 100 Ω の終端抵抗を必ず使用しなければなりません。 |

## ピン説明および等価回路(つづき)

| ピン番号     | シンボル               | 等価回路                                                                                | 説明                                                                                                                                                                                                                                                                                                     |

|----------|--------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 38<br>37 | SD1_A +<br>SD1_A - |                                                                                     | チャネル A のシリアル・データ出力 1。この差動 LVDS 信号ペアにはチャネル A の ADC 出力がシリアル化されて現れます。このシリアル・データは OUTCLK 出力と同期して供給されます。シングル・レーン・モードでは、各サンプル出力が連続して供給されます。デュアル・レーン・モードではこの出力にはサンプル出力は 1 つおきに供給されます。この差動出力はデバイスの電源がオンとなっていれば、常にイネーブルになります。パワーダウン・モードでは、この出力には最後の論理状態が保持されます。この信号ペアに対しては伝送ラインの遠端に 100 Ω の終端抵抗を必ず使用しなければなりません。 |

| 34<br>33 | SD1_B +<br>SD1_B - |    | チャネル B のシリアル・データ出力 1。この差動 LVDS 信号ペアにはチャネル B の ADC 出力がシリアル化されて現れます。このシリアル・データは OUTCLK 出力と同期して供給されます。シングル・レーン・モードでは、各サンプル出力が連続して供給されます。デュアル・レーン・モードではこの出力にはサンプル出力は 1 つおきに供給されます。この差動出力はデバイスの電源がオンとなっていれば、常にイネーブルになります。パワーダウン・モードでは、この出力には最後の論理状態が保持されます。この信号ペアに対しては伝送ラインの遠端に 100 Ω の終端抵抗を必ず使用しなければなりません。 |

| 36<br>35 | SD0_A +<br>SD0_A - |                                                                                     | チャネル A のシリアル・データ出力 0。この差動 LVDS 信号ペアにはデュアル・レーン・モードでのシリアル化されたチャネル A の ADC サンプル出力が交互に現れます。このシリアル・データは OUTCLK 出力と同期して供給されます。シングル・レーン・モードではこの差動出力はハイ・インピーダンス状態に保持されます。この差動出力はデバイスの電源がオンとなっていれば、常にイネーブルになります。パワーダウン・モードでは、この出力には最後の論理状態が保持されます。この信号ペアに対しては伝送ラインの遠端に 100 Ω の終端抵抗を必ず使用しなければなりません。              |

| 32<br>31 | SD0_B +<br>SD0_B - |                                                                                     | チャネル B のシリアル・データ出力 0。この差動 LVDS 信号ペアにはデュアル・レーン・モードでのシリアル化されたチャネル B の ADC サンプル出力が交互に現れます。このシリアル・データは OUTCLK 出力と同期して供給されます。シングル・レーン・モードではこの差動出力はハイ・インピーダンス状態に保持されます。この差動出力はデバイスの電源がオンとなっていれば、常にイネーブルになります。パワーダウン・モードでは、この出力には最後の論理状態が保持されます。この信号ペアに対しては伝送ラインの遠端に 100 Ω の終端抵抗を必ず使用しなければなりません。              |

| 56       | SPI_EN             |  | SPI イネーブル : この信号を High にすると SPI インタフェースがイネーブルになります。この場合、直接制御されるピンは無効です。この信号を Low にすると、SPI インタフェースはディスエーブルとなり、直接制御ピンがイネーブルになります。                                                                                                                                                                        |

| 55       | SCSb               |  | シリアル・チップ選択 : この信号をアサートすると、SCLK は SDI 入力に現れるシリアル・データを受け取り、SDO 出力ではシリアル・データを供給するために使用されます。この信号をアサートしない場合は SDI 入力は無視され、SDO 出力は TRI-STATE モードになります。                                                                                                                                                        |

| 52       | SCLK               |                                                                                     | シリアル・クロック : シリアル・データはクロック信号に同期してデバイスにシフト入力およびシフト出力されます。                                                                                                                                                                                                                                                |

| 54       | SDI                |                                                                                     | シリアルデータ入力 : SCSb 信号がアサートされている場合、シリアル・データはこのピンからデバイスにシフト入力されます。                                                                                                                                                                                                                                         |

## ピン説明および等価回路(つづき)

| ピン番号     | シンボル       | 等価回路 | 説明                                                                                                                                                                          |

|----------|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 53       | SDO        |      | シリアルデータ出力 : SCSb 信号がアサートされている場合、シリアル・データはデバイスのこのピンからシフト出力されます。SCSb がアサートされていない場合、この出力は TRI-STATE モードになります。                                                                  |

| 46<br>30 | ORA<br>ORB |      | オーバーレンジ。これらの CMOS 出力は対応するチャネルのデータ出力が High または Low の方向に範囲外になると論理 High になります。                                                                                                 |

| 24       | DLL_Lock   |      | DLL_ロック出力。内部 DLL が入力 CLK にロックされると、このピン出力は論理 High になります。入力 CLK が突然変化すると、内部 DLL はロックが外れる可能性があり、その場合このピンは論理 Low になります。Reset_DLL (pin 28) をサイクルすると、入力 CLK に対して内部 DLL が再ロックされます。 |

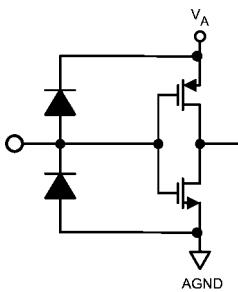

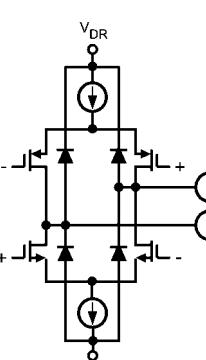

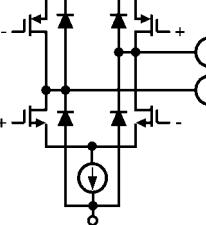

## アナログ電源

|                         |                |  |                                                                                    |

|-------------------------|----------------|--|------------------------------------------------------------------------------------|

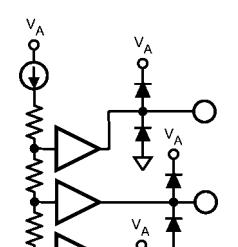

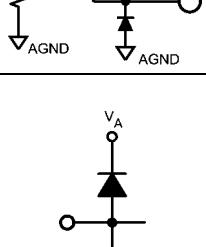

| 8, 16, 17,<br>58, 60    | V <sub>A</sub> |  | 正のアナログ電源ピン。これらのピンは、ノイズのない電源に接続する必要があり、電源ピンの近くに配置した 0.1 μF コンデンサで AGND にバイパスしてください。 |

| 1、4、12、<br>15、露出<br>パッド | AGND           |  | アナログ電源のグラウンド・ピン。                                                                   |

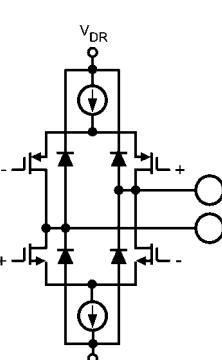

## デジタル電源

|            |                 |  |                                                                                             |

|------------|-----------------|--|---------------------------------------------------------------------------------------------|

| 26, 40, 50 | V <sub>DR</sub> |  | 出力ドライバ用の正のデジタル電源ピン。これらのピンは、ノイズのない電源に接続する必要があり、電源ピンの近くに配置した 0.1 μF コンデンサで DRGND にバイパスしてください。 |

| 25, 39, 51 | DRGND           |  | デジタル出力ドライバ電源のグラウンド・ピン。システムのデジタル・グラウンドに接続してください。ただし、A/D コンバータの AGND ピンの近くには接続しないでください。       |

**絶対最大定格 (Note 1、3)**

本データシートには軍用・航空宇宙用の規格は記載されていません。

関連する電気的信頼性試験方法の規格を参照ください。

|                            |                          |

|----------------------------|--------------------------|

| 電源電圧 ( $V_A$ 、 $V_{DR}$ )  | - 0.3V ~ 4.2V            |

| 各入出力ピン電圧<br>(4.2V を超えないこと) | - 0.3V ~ ( $V_A$ + 0.3V) |

| 電源ピン以外の全入力ピン電流<br>(Note 4) | ± 5mA                    |

| パッケージ入力電流 (Note 4)         | ± 50mA                   |

| 最大接合部温度 ( $T_J$ )          | + 150                    |

| 熱抵抗 ( $J_A$ )              | 30 /W                    |

| ESD 耐圧                     |                          |

| 人体モデル (Note 6)             | 2,500V                   |

マシン・モデル (Note 6)

250V

保存温度範囲

- 65 ~ + 150

ハンダ付けのプロセスは、National Semiconductor's Reflow Temperature Profile 規格に準拠してください。

www.national.com/JPN/packaging を参照してください (Note 7)。

**動作定格 (Note 1、3)**

|                                |             |          |      |

|--------------------------------|-------------|----------|------|

| 動作温度範囲                         | - 40        | $T_A$    | + 85 |

| 電源電圧 ( $V_A = V_{DR}$ )        | + 2.7V      | ~ + 3.6V |      |

| クロック・デューティ・サイクル<br>(DCS イネーブル) | 30/70 %     |          |      |

| (DCS ディスエーブル)                  | 45/55 %     |          |      |

| $V_{CM}$                       | 1.4V ~ 1.6V |          |      |

| AGND - DRGND                   | 100mV       |          |      |

**コンバータの電気的特性**

特記のない限り、 $AGND = DRGND = 0V$ 、 $V_A = + 3.3V$ 、 $V_{DR} = + 3.0V$ 、内部  $V_{REF} = + 1.2V$ 、 $f_{CLK} = 105MHz$ 、 $V_{CM} = V_{CMO}$ 、 $C_L = 5pF/ ピン$ 。標準値は  $T_A = 25^\circ C$  のときのものです。太字表記のリミット値は  $T_{MIN} \leq T_A \leq T_{MAX}$  に適用されます。その他のすべてのリミット値は  $T_A = 25^\circ C$  に対して適用されます。 (Note 8、9)

| Symbol                                  | Parameter                        | Conditions                              | Typical<br>(Note 10) | Limits                    | Units<br>(Limits)      |

|-----------------------------------------|----------------------------------|-----------------------------------------|----------------------|---------------------------|------------------------|

| <b>STATIC CONVERTER CHARACTERISTICS</b> |                                  |                                         |                      |                           |                        |

|                                         | Resolution with No Missing Codes |                                         |                      | <b>12</b>                 | Bits (min)             |

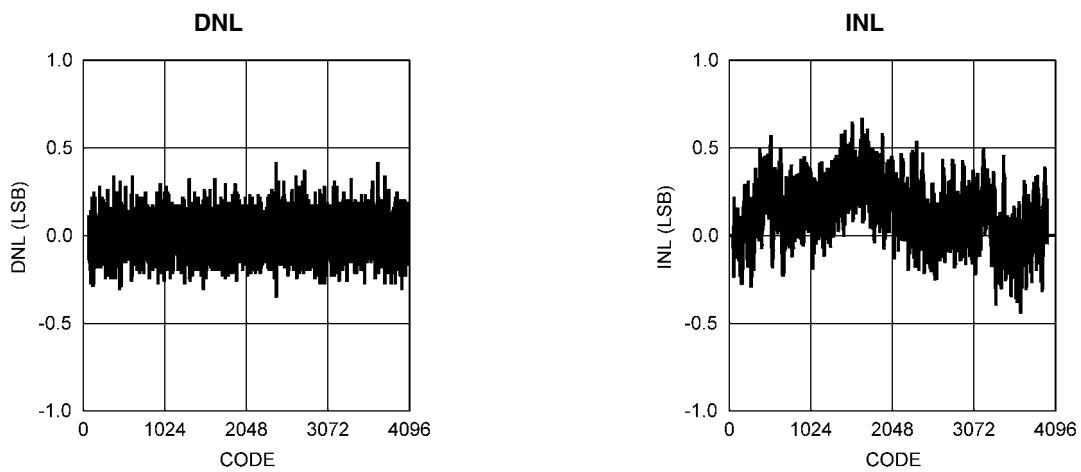

| INL                                     | Integral Non Linearity           |                                         | ±0.5                 | <b>2</b><br><b>-2</b>     | LSB (max)<br>LSB (min) |

| DNL                                     | Differential Non Linearity       |                                         | ±0.3                 | <b>0.8</b><br><b>-0.8</b> | LSB (max)<br>LSB (min) |

| PGE                                     | Positive Gain Error              |                                         | 0.15                 | <b>±1</b>                 | %FS (max)              |

| NGE                                     | Negative Gain Error              |                                         | 0.07                 | <b>±1</b>                 | %FS (max)              |

| TC PGE                                  | Positive Gain Error Tempco       | $-40^\circ C \leq T_A \leq +85^\circ C$ |                      |                           | ppm/°C                 |

| TC NGE                                  | Negative Gain Error Tempco       | $-40^\circ C \leq T_A \leq +85^\circ C$ |                      |                           | ppm/°C                 |

| $V_{OFF}$                               | Offset Error                     |                                         | 0.03                 | <b>±0.55</b>              | %FS (max)              |

| TC $V_{OFF}$                            | Offset Error Tempco              | $-40^\circ C \leq T_A \leq +85^\circ C$ |                      |                           | ppm/°C                 |

|                                         | Under Range Output Code          |                                         | 0                    | <b>0</b>                  |                        |

|                                         | Over Range Output Code           |                                         | 4095                 | <b>4095</b>               |                        |

**REFERENCE AND ANALOG INPUT CHARACTERISTICS**

|              |                                                           |                                         |                         |                          |                    |

|--------------|-----------------------------------------------------------|-----------------------------------------|-------------------------|--------------------------|--------------------|

| $V_{CMO}$    | Common Mode Output Voltage                                |                                         | 1.5                     | <b>1.4</b><br><b>1.6</b> | V (min)<br>V (max) |

| $V_{CM}$     | Analog Input Common Mode Voltage                          |                                         | 1.5                     | 1.4<br>1.6               | V (min)<br>V (max) |

| $C_{IN}$     | $V_{IN}$ Input Capacitance (each pin to GND)<br>(Note 11) | $V_{IN} = 1.5\text{ Vdc}$<br>± 0.5 V    | (CLK LOW)<br>(CLK HIGH) | 8.5<br>3.5               | pF<br>pF           |

| $V_{REF}$    | Internal Reference Voltage                                |                                         | 1.18                    | 1.17<br>1.21             | V (min)<br>V (max) |

| TC $V_{REF}$ | Internal Reference Voltage Tempco                         | $-40^\circ C \leq T_A \leq +85^\circ C$ | 18                      |                          | ppm/°C             |

| $V_{RP}$     | Internal Reference Top                                    |                                         | 2.0                     |                          | V                  |

| $V_{RN}$     | Internal Reference Bottom                                 |                                         | 1.0                     |                          | V                  |

## コンバータの電気的特性(つづき)

特記のない限り、AGND = DRGND = 0V、 $V_A = +3.3V$ 、 $V_{DR} = +3.0V$ 、内部  $V_{REF} = +1.2V$ 、 $f_{CLK} = 105MHz$ 、 $V_{CM} = V_{CMO}$ 、 $C_L = 5pF/\text{ビン}$ 。標準値は  $T_A = 25^\circ\text{C}$  のときのものです。太字表記のリミット値は  $T_{MIN} \leq T_A \leq T_{MAX}$  に適用されます。その他のすべてのリミット値は  $T_A = 25^\circ\text{C}$  に対して適用されます。(Note 8、9)

| Symbol        | Parameter                   | Conditions        | Typical<br>(Note 10) | Limits         | Units<br>(Limits)  |

|---------------|-----------------------------|-------------------|----------------------|----------------|--------------------|

|               | Internal Reference Accuracy | $(V_{RP}-V_{RN})$ | 0.97                 | 0.89<br>1.06   | V (min)<br>V (max) |

| EXT $V_{REF}$ | External Reference Voltage  |                   | 1.2                  | 1.176<br>1.224 | V (min)<br>V (max) |

## コンバータの電気的ダイナミック特性

特記のない限り、AGND = DRGND = 0V、 $V_A = +3.3V$ 、 $V_{DR} = +3.0V$ 、内部  $V_{REF} = +1.2V$ 、 $f_{CLK} = 105MHz$ 、 $V_{CM} = V_{CMO}$ 、 $C_L = 5pF/\text{ビン}$ 。標準値は  $T_A = 25^\circ\text{C}$  のときのものです。太字表記のリミット値は  $T_{MIN} \leq T_A \leq T_{MAX}$  に適用されます。その他のすべてのリミット値は  $T_A = 25^\circ\text{C}$  に対して適用されます。(Note 8、9)

| Symbol                                                                        | Parameter                            | Conditions                                                     | Typical<br>(Note 10) | Limits       | Units<br>(Limits)<br>(Note 2) |

|-------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------------------------|----------------------|--------------|-------------------------------|

| <b>DYNAMIC CONVERTER CHARACTERISTICS, <math>A_{IN} = -1\text{dBFS}</math></b> |                                      |                                                                |                      |              |                               |

| FPBW                                                                          | Full Power Bandwidth                 | -1 dBFS Input, -3 dB Corner                                    | 1.0                  |              | GHz                           |

| SNR                                                                           | Signal-to-Noise Ratio                | $f_{IN} = 10 \text{ MHz}$                                      | 71                   |              | dBFS                          |

|                                                                               |                                      | $f_{IN} = 70 \text{ MHz}$                                      | 70                   |              | dBFS                          |

|                                                                               |                                      | $f_{IN} = 240 \text{ MHz}$                                     | 68.5                 | <b>67.4</b>  | dBFS                          |

| SFDR                                                                          | Spurious Free Dynamic Range          | $f_{IN} = 10 \text{ MHz}$                                      | 88                   |              | dBFS                          |

|                                                                               |                                      | $f_{IN} = 70 \text{ MHz}$                                      | 85                   |              | dBFS                          |

|                                                                               |                                      | $f_{IN} = 240 \text{ MHz}$                                     | 83                   | <b>76.5</b>  | dBFS                          |

| ENOB                                                                          | Effective Number of Bits             | $f_{IN} = 10 \text{ MHz}$                                      | 11.5                 |              | Bits                          |

|                                                                               |                                      | $f_{IN} = 70 \text{ MHz}$                                      | 11.3                 |              | Bits                          |

|                                                                               |                                      | $f_{IN} = 240 \text{ MHz}$                                     | 11                   | <b>10.7</b>  | Bits                          |

| THD                                                                           | Total Harmonic Distortion            | $f_{IN} = 10 \text{ MHz}$                                      | -86                  |              | dBFS                          |

|                                                                               |                                      | $f_{IN} = 70 \text{ MHz}$                                      | -85                  |              | dBFS                          |

|                                                                               |                                      | $f_{IN} = 240 \text{ MHz}$                                     | -80                  | <b>-74</b>   | dBFS                          |

| H2                                                                            | Second Harmonic Distortion           | $f_{IN} = 10 \text{ MHz}$                                      | -90                  |              | dBFS                          |

|                                                                               |                                      | $f_{IN} = 70 \text{ MHz}$                                      | -88                  |              | dBFS                          |

|                                                                               |                                      | $f_{IN} = 240 \text{ MHz}$                                     | -83                  | <b>-76.5</b> | dBFS                          |

| H3                                                                            | Third Harmonic Distortion            | $f_{IN} = 10 \text{ MHz}$                                      | -88                  |              | dBFS                          |

|                                                                               |                                      | $f_{IN} = 70 \text{ MHz}$                                      | -85                  |              | dBFS                          |

|                                                                               |                                      | $f_{IN} = 240 \text{ MHz}$                                     | -83                  | <b>-76.5</b> | dBFS                          |

| SINAD                                                                         | Signal-to-Noise and Distortion Ratio | $f_{IN} = 10 \text{ MHz}$                                      | 70.8                 |              | dBFS                          |

|                                                                               |                                      | $f_{IN} = 70 \text{ MHz}$                                      | 69.9                 |              | dBFS                          |

|                                                                               |                                      | $f_{IN} = 240 \text{ MHz}$                                     | 68.2                 | <b>66.5</b>  | dBFS                          |

| IMD                                                                           | Intermodulation Distortion           | $f_{IN} = 19.5 \text{ and } 20.5 \text{ MHz}$ ,<br>each -7dBFS | -82                  |              | dBFS                          |

## ロジックおよび電源の電気的特性

特記のない限り、AGND = DRGND = 0V、 $V_A = +3.3V$ 、 $V_{DR} = +3.0V$ 、内部  $V_{REF} = +1.2V$ 、 $f_{CLK} = 105MHz$ 、 $V_{CM} = V_{CMO}$ 、 $C_L = 5pF/\text{ビン}$ 。標準値は  $T_A = 25^\circ\text{C}$  のときのものです。太字表記のリミット値は  $T_{MIN} \leq T_A \leq T_{MAX}$  に適用されます。その他のすべてのリミット値は  $T_A = 25^\circ\text{C}$  に対して適用されます。(Note 8、9)

| Symbol                                                                                  | Parameter                 | Conditions      | Typical<br>(Note 10) | Limits     | Units<br>(Limits) |

|-----------------------------------------------------------------------------------------|---------------------------|-----------------|----------------------|------------|-------------------|

| <b>DIGITAL INPUT CHARACTERISTICS (CLK, PD_A,PD_B,SCSb,SPI_EN,SCLK,SDI,TEST,WAM,DLC)</b> |                           |                 |                      |            |                   |

| $V_{IN(1)}$                                                                             | Logical "1" Input Voltage | $V_D = 3.6V$    |                      | <b>2.0</b> | V (min)           |

| $V_{IN(0)}$                                                                             | Logical "0" Input Voltage | $V_D = 3.0V$    |                      | <b>0.8</b> | V (max)           |

| $I_{IN(1)}$                                                                             | Logical "1" Input Current | $V_{IN} = 3.3V$ | 10                   |            | $\mu\text{A}$     |

| $I_{IN(0)}$                                                                             | Logical "0" Input Current | $V_{IN} = 0V$   | -10                  |            | $\mu\text{A}$     |

## ロジックおよび電源の電気的特性 (つづき)

特記のない限り、AGND = DRGND = 0V、 $V_A = + 3.3V$ 、 $V_{DR} = + 3.0V$ 、内部  $V_{REF} = + 1.2V$ 、 $f_{CLK} = 105MHz$ 、 $V_{CM} = V_{CMO}$ 、 $C_L = 5pF/\text{ビット}$ 。標準値は  $T_A = 25^\circ\text{C}$  のときのものです。太字表記のリミット値は  $T_{MIN} \leq T_A \leq T_{MAX}$  に適用されます。その他のすべてのリミット値は  $T_A = 25^\circ\text{C}$  に対して適用されます。(Note 8、9)

| Symbol                                                       | Parameter                           | Conditions                 | Typical<br>(Note 10) | Limits      | Units<br>(Limits) |

|--------------------------------------------------------------|-------------------------------------|----------------------------|----------------------|-------------|-------------------|

| $C_{IN}$                                                     | Digital Input Capacitance           |                            | 5                    |             | pF                |

| <b>DIGITAL OUTPUT CHARACTERISTICS (ORA,ORB,SDO,DLL_Lock)</b> |                                     |                            |                      |             |                   |

| $V_{OUT(1)}$                                                 | Logical "1" Output Voltage          | $I_{OUT} = -0.5\text{ mA}$ |                      | <b>1.2</b>  | V (min)           |

| $V_{OUT(0)}$                                                 | Logical "0" Output Voltage          | $I_{OUT} = 1.6\text{ mA}$  |                      | <b>0.4</b>  | V (max)           |

| $+I_{SC}$                                                    | Output Short Circuit Source Current | $V_{OUT} = 0V$             | -10                  |             | mA                |

| $-I_{SC}$                                                    | Output Short Circuit Sink Current   | $V_{OUT} = V_{DR}$         | 10                   |             | mA                |

| $C_{OUT}$                                                    | Digital Output Capacitance          |                            | 5                    |             | pF                |

| <b>POWER SUPPLY CHARACTERISTICS</b>                          |                                     |                            |                      |             |                   |

| $I_A$                                                        | Analog Supply Current               | Full Operation             | 240                  | <b>270</b>  | mA (max)          |

| $I_{DR}$                                                     | Digital Output Supply Current       | Full Operation             | 70                   | <b>80</b>   | mA                |

|                                                              | Power Consumption                   |                            | 1000                 | <b>1130</b> | mW (max)          |

|                                                              | Power Down Power Consumption        | Clock disabled             | 33                   |             | mW                |

## タイミング仕様と AC 特性

特記のない限り、AGND = DRGND = 0V、 $V_A = + 3.3V$ 、 $V_{DR} = + 3.0V$ 、内部  $V_{REF} = + 1.2V$ 、 $f_{CLK} = 105MHz$ 、 $V_{CM} = V_{CMO}$ 、 $C_L = 5pF/\text{ビット}$ 。代表値は  $T_A = 25^\circ\text{C}$  の場合の値です。タイミング測定は信号振幅の 50% で行われます。太字表記のリミット値は  $T_{MIN} \leq T_A \leq T_{MAX}$  に適用されます。その他のすべてのリミット値は  $T_A = 25^\circ\text{C}$  に対して適用されます。(Note 8、9)

| Symb       | Parameter               | Conditions                                                                 | Typical<br>(Note 10) | Limits                   | Units<br>(Limits) |

|------------|-------------------------|----------------------------------------------------------------------------|----------------------|--------------------------|-------------------|

|            | Maximum Clock Frequency | In Single-Lane Mode<br>In Dual-Lane Mode                                   |                      | <b>65</b><br><b>105</b>  | MHz (max)         |

|            | Minimum Clock Frequency | In Single-Lane Mode<br>In Dual-Lane Mode                                   |                      | <b>25</b><br><b>52.5</b> | MHz (min)         |

| $t_{CONV}$ | Conversion Latency      | Single-Lane Mode<br>Dual-Lane, Offset Mode<br>Dual-Lane, Word Aligned Mode |                      | 7.5<br>8<br>9            | Clock Cycles      |

| $t_{AD}$   | Aperture Delay          |                                                                            | 0.6                  |                          | ns                |

| $t_{AJ}$   | Aperture Jitter         |                                                                            | 0.1                  |                          | ps rms            |

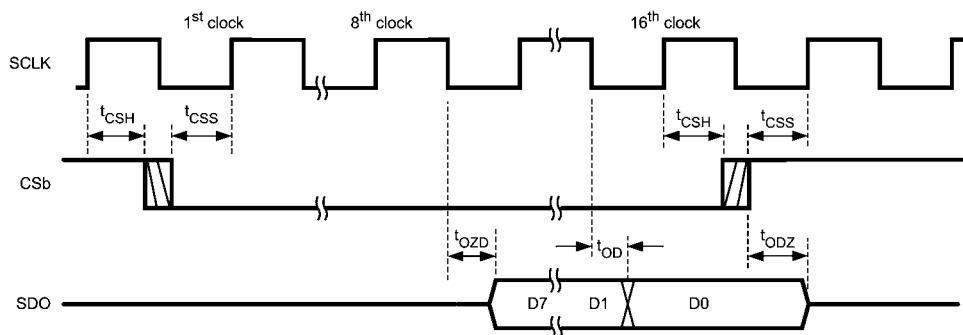

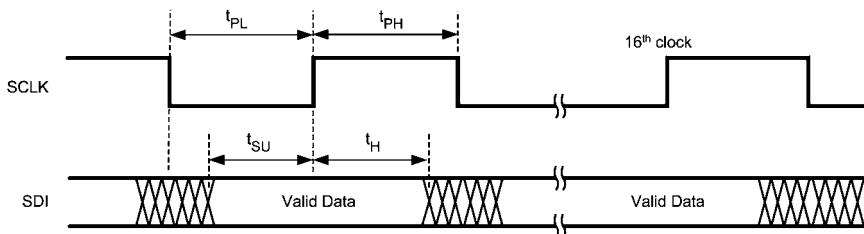

## シリアル制御インターフェースのタイミングと AC 特性

特記のない限り、AGND = DRGND = 0V、 $V_A = + 3.3V$ 、 $V_{DR} = + 3.0V$ 、内部  $V_{REF} = + 1.2V$ 、 $f_{CLK} = 105MHz$ 、 $V_{CM} = V_{CMO}$ 、 $C_L = 5pF/\text{ビット}$ 。代表値は  $T_A = 25^\circ\text{C}$  の場合の値です。タイミング測定は信号振幅の 50% で行われます。太字表記のリミット値は  $T_{MIN} \leq T_A \leq T_{MAX}$  に適用されます。その他のすべてのリミット値は  $T_A = 25^\circ\text{C}$  に対して適用されます。(Note 8、9)

| Symb       | Parameter                    | Conditions                                            | Typical<br>(Note 10) | Limits   | Units<br>(Limits)  |

|------------|------------------------------|-------------------------------------------------------|----------------------|----------|--------------------|

| $f_{SCLK}$ | Serial Clock Frequency       | $f_{SCLK} = f_{CLK}/10$                               |                      | 10.5     | MHz (max)          |

| $t_{PH}$   | SCLK Pulse Width - High      | % of SCLK Period                                      |                      | 40<br>60 | % (min)<br>% (max) |

| $t_{PL}$   | SCLK Pulse Width - Low       | % of SCLK Period                                      |                      | 40<br>60 | % (min)<br>% (max) |

| $t_{SU}$   | SDI Setup Time               |                                                       |                      | 5        | ps (min)           |

| $t_H$      | SDI Hold Time                |                                                       |                      | 5        | ns (min)           |

| $t_{ODZ}$  | SDO Driven-to-Tri-State Time |                                                       | 40                   | 50       | ns (max)           |

| $t_{OZD}$  | SDO Tri-State-to-Driven Time |                                                       | 15                   | 20       | ns (max)           |

| $t_{OD}$   | SDO Output Delay Time        |                                                       | 15                   | 20       | ns (max)           |

| $t_{CSS}$  | SCSb Setup Time              |                                                       | 5                    | 10       | ns (min)           |

| $t_{CSH}$  | SCSb Hold Time               |                                                       | 5                    | 10       | ns (min)           |

| $t_{IAG}$  | Inter-Access Gap             | Minimum time SCSb must be deasserted between accesses | 3                    |          | Cycles of SCLK     |

## LVDS 電気的特性

特記のない限り、AGND = DRGND = 0V、 $V_A = +3.3V$ 、 $V_{DR} = +3.0V$ 、内部  $V_{REF} = +1.2V$ 、 $f_{CLK} = 105MHz$ 、 $V_{CM} = V_{CMO}$ 、 $C_L = 5pF/\text{pin}$ 。代表値は  $T_A = 25^\circ\text{C}$  の場合の値です。タイミング測定は信号振幅の 50% で行われます。太字表記のリミット値は  $T_{MIN}$   $T_A$   $T_{MAX}$  に適用されます。その他のすべてのリミット値は  $T_A = 25^\circ\text{C}$  に対して適用されます。(Note 8、9)

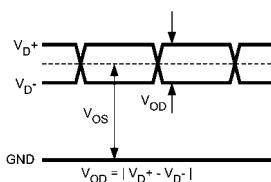

| Symbol                                                  | Parameter                                                   | Conditions                               | Typical<br>(Note 10) | Limits         | Units<br>(Limits)    |

|---------------------------------------------------------|-------------------------------------------------------------|------------------------------------------|----------------------|----------------|----------------------|

| <b>LVDS DC CHARACTERISTICS</b>                          |                                                             |                                          |                      |                |                      |

| $V_{OD}$                                                | Output Differential Voltage (SDO+) - (SDO-)                 | $R_L = 100\Omega$                        | 350                  | 250<br>450     | mV (min)<br>mV (max) |

| delta $V_{OD}$                                          | Output Differential Voltage Unbalance                       | $R_L = 100\Omega$                        |                      | $\pm 25$       | mV (max)             |

| $V_{OS}$                                                | Offset Voltage                                              | $R_L = 100\Omega$                        | 1.25                 | 1.125<br>1.375 | V (min)<br>V (max)   |

| delta $V_{OS}$                                          | Offset Voltage Unbalance                                    | $R_L = 100\Omega$                        |                      | $\pm 25$       | mV (max)             |

| IOS                                                     | Output Short Circuit Current                                | $DO = 0V, V_{IN} = 1.1V,$                | -10                  |                | mA (max)             |

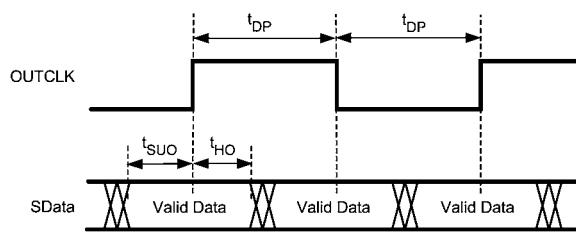

| <b>LVDS OUTPUT TIMING AND SWITCHING CHARACTERISTICS</b> |                                                             |                                          |                      |                |                      |

| $t_{DP}$                                                | Output Data Bit Period                                      | Dual-Lane Mode                           | 1.59                 |                | ns                   |

| $t_{HO}$                                                | Output Data Edge to Output Clock Edge Hold Time (Note 12)   | Dual-Lane Mode                           | 750                  | <b>450</b>     | ps                   |

| $t_{SUO}$                                               | Output Data Edge to Output Clock Edge Set-Up Time (Note 12) | Dual-Lane Mode                           | 800                  | <b>500</b>     | ps                   |

| $t_{FP}$                                                | Frame Period                                                | Dual-Lane Mode                           | 19.05                |                | ns                   |

| $t_{FDC}$                                               | Frame Clock Duty Cycle (Note 12)                            |                                          | 50                   | 45<br>55       | % (min)<br>% (max)   |

| $t_{DFS}$                                               | Data Edge to Frame Edge Skew                                | 50% to 50%                               | 15                   |                | ps                   |

| $t_{ODOR}$                                              | Output Delay of OR output                                   | From rising edge of CLK to ORA/ORB valid | 4                    |                | ns                   |

**Note 1:** 絶対最大定格とは、デバイスに破壊が発生する可能性のある制限値をいいます。動作定格とはデバイスが機能する条件を示しますが、特定の性能リミット値を保証するものではありません。保証された仕様、および試験条件については「電気的特性」を参照してください。保証された仕様はリストに示された試験条件でのみ適用されます。リストに示されている試験条件の下で動作していない場合には、いくつかの性能特性は低下することがあります。最大動作定格を超えた状態でデバイスを動作させることはできません。

**Note 2:** dBFS で指定されたパラメータは、フルスケール入力信号で達成される値を示しています。

**Note 3:** 特記のない限り、すべての電圧は GND = AGND = DRGND = 0V に対して測定された値です。

**Note 4:** いずれかのピンで入力電圧 ( $V_{IN}$ ) が電源電圧を超えた場合 ( $V_{IN} < AGND$  または  $V_{IN} > V_A$ )、そのピンの入力電流を  $\pm 5mA$  以下に制限しなければなりません。 $\pm 50mA$  の最大パッケージ入力定格電流によって、電源電圧を超えて  $\pm 5mA \sim 10mA$  の電流を流せるピン数が制限されます。

**Note 5:** 最大許容消費電力 ( $T_{J,max}$ ) は、接合部周囲間熱抵抗 ( $J_A$ ) および周囲温度 ( $T_A$ ) によって決まり、 $P_{D,max} = (T_{J,max} - T_A) / J_A$  で表されます。上記の最大許容消費電力の値にまで上がる場合は、デバイスが何らかの異常な状態で動作しているときのみです(例えば、入力ピンまたは出力ピンを電源電圧を超えて駆動させている場合や電源の極性を逆転させている場合など)。このような条件での動作は必ず避けるようにしてください。

**Note 6:** 使用した試験回路は人体モデルに基づき、100pF のコンデンサから直列抵抗 1.5kΩ を通して、各ピンに放電させます。マシン・モデルでは 220pF のコンデンサから直列抵抗 0Ω を通して、各ピンに放電させます。

**Note 7:** リフロー温度プロファイルは、鉛フリー・パッケージの場合と非鉛フリー・パッケージの場合で異なります。

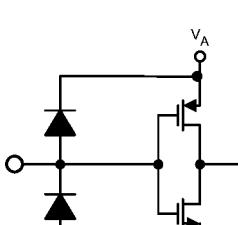

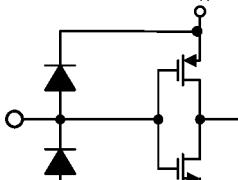

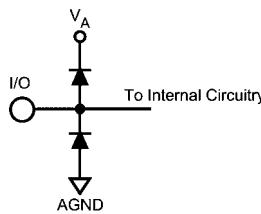

**Note 8:** 以下に示すように、各入出力ピンは 1 個のツエナーダイオードで保護されています。Note 4 に従って電流制限を行うことで、入力電圧が  $V_A$  を上回った場合や GND を下回った場合でも本デバイスがダメージを受けることはありません。しかし、動作定格で記載されたように入力が 2.6V 以上または GND より低い場合、A/D 変換のエラーが発生します。

**Note 9:** 2V<sub>P-P</sub> のフルスケールの差動入力では 12 ピットの LSB は 488μV です。

**Note 10:** 代表的性能値は、 $T_A = 25^\circ\text{C}$  のときのものであり、製品特性試験の時点でとり得る最適なパラメータの基準を表しています。この代表的な仕様は保証されているわけではありません。

**Note 11:** 入力容量は、パッケージ/ピン・キャパシタンスとサンプル/ホールド回路キャパシタンスの合計です。

**Note 12:** このパラメータは設計と特性評価によって保証されています。製造時の試験は行っていません。

## 用語の定義

**アーチャ・ディレイ (APERTURE DELAY)** は、クロック・パルスが立ち下がってから入力信号が取り込まれるか保持されるまでの時間です。

**アーチャ・ジッタ (アーチャ不確定性) (APERTURE JITTER: APERTURE UNCERTAINTY)** は、サンプルとサンプルの間のアーチャ・ディレイのばらつきです。アーチャ・ジッタは、それ自身は出力のノイズとして現れます。

**クロック・デューティ・サイクル (CLOCK DUTY CYCLE)** は、繰り返しデジタル波形の周期に対する High の時間の比です。本データシートに記載されているデューティ・サイクルの仕様は、ADC のクロック入力信号に対して適用されます。

**コモンモード電圧 (COMMON MODE VOLTAGE:  $V_{CM}$ )** とは A/D コンバータの両方の入力ピンに印加されるコモン DC 電圧です。

**変換レイテンシ (CONVERSION LATENCY)** は、変換開始からその変換結果が出力ドライバで得られるまでの期間をクロック・サイクル数で表したものです。任意に与えられたサンプリングに対するデータは、そのサンプリングが行われた後、パイプライン・ディレイや出力ディレイの出力ピン上で有効になります。新しいデータはクロック・サイクル毎に有効ですが、その出力データはパイプライン・ディレイ分の変換ラグがあります。

**クロストーク (CROSSTALK)** とは、1 つのチャネルから別のチャネルへエネルギーが結合することです。

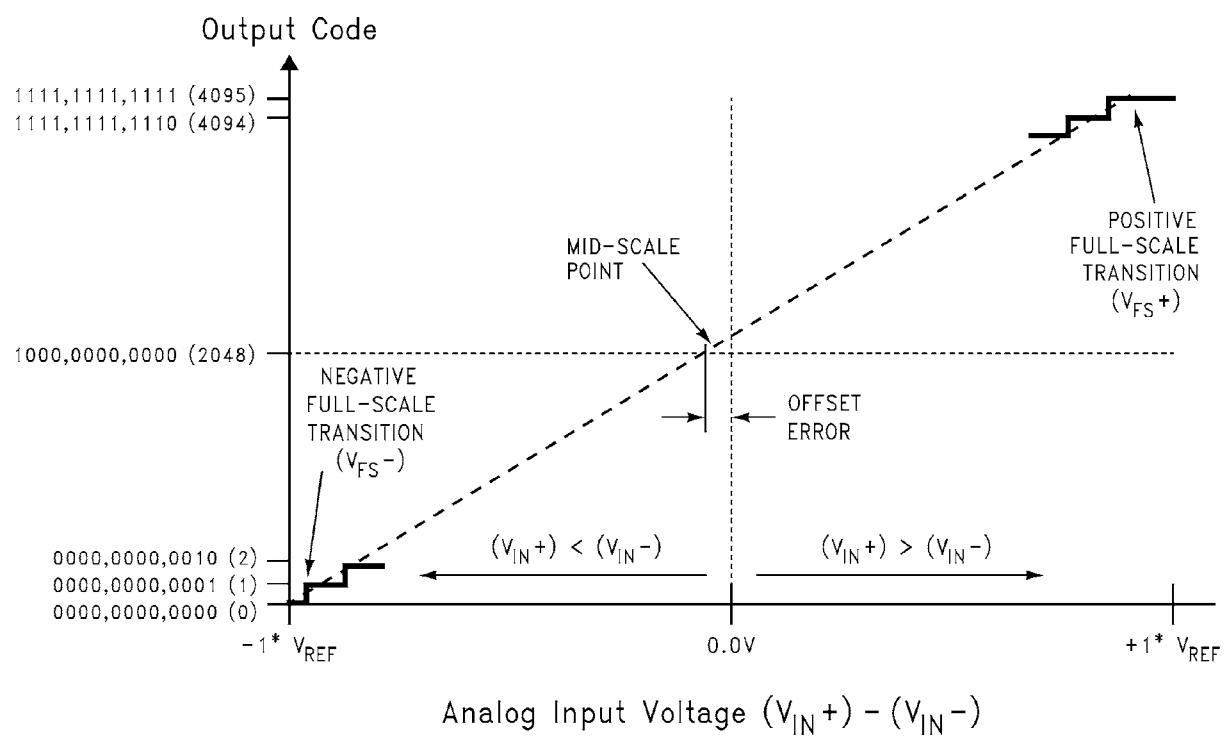

**微分非直線性 (DIFFERENTIAL NON-LINEARITY: DNL)** は、理想的なステップである 1LSB からの最大偏差として表されます。

**有効ビット (EFFECTIVE NUMBER OF BITS: ENOB)** は、信号 / (ノイズ + 歪み) または SINAD の別の規定方法です。ENOB は (SINAD - 1.76) / 6.02 として定義され、この値のビット数をもつ完全な A/D コンバータに等しいコンバータであることを意味します。

**フルパワー入力帯域 (FULL POWER BANDWIDTH)** は、フルスケール入力に対して再現される出力の基本周波数が低周波数における値に対して 3dB 低下した部分の帯域幅です。

**ゲイン誤差 (GAIN ERROR)** は、伝達関数の実測値と理想カーブとの偏差のことです。次の式で計算できます。

$$\text{ゲイン誤差} = \text{正側フルスケール誤差} - \text{負側フルスケール誤差}$$

正側ゲイン誤差と負側ゲイン誤差によって次のように表すことができます。

$$\text{正側ゲイン誤差} = \text{正側フルスケール誤差} - \text{オフセット誤差}$$

$$\text{負側ゲイン誤差} = \text{オフセット誤差} - \text{負側フルスケール誤差}$$

**積分非直線性 (INTEGRAL NON LINEARITY: INL)** は、バストフィットさせた直線と各個別コードとの偏差を表します。この直線と任意のコードとの偏差は、各コード値の中央から測定します。

**混変調歪み (INTERMODULATION DISTORTION: IMD)** は、A/D コンバータの入力に 2 つの近接した周波数を同時に投入し、結果として作り出される別のスペクトラル成分です。元の周波数のトータル・パワーに対する混変調成分のパワーの比として定義されます。IMD は通常 dBFS で表されます。

**LSB (LEAST SIGNIFICANT BIT)** は、全ビットのうち、最も小さな値、または最も小さな重みを持ったビットです。この値は  $V_{FS}/2^n$  として表されます。 " $V_{FS}$ " はフルスケール入力電圧、" $n$ " は ADC の分解能 (ビット) です。

**LVDS 差動出力電圧 (LVDS DIFFERENTIAL OUTPUT VOLTAGE:  $V_{OP}$ )** は、それぞれグラウンドを基準として測定した差動出力電圧 ( $V_D^+$  + 電圧と  $V_D^-$  ) の絶対値です。

**ミッシング・コード (MISSING CODES)** は、A/D コンバータから出力されない出力コードです。ADC12DS105 は、ミッシング・コードのないことが保証されています。

**MSB (MOST SIGNIFICANT BIT)** は、全ビットのうち、最も大きな値、または最も大きな重みを持ったビットです。MSB の値はフルスケールの 1/2 に相当します。

**負のフルスケール誤差 (NEGATIVE FULL SCALE ERROR)** は、最初のコード遷移点の実測値と(負側フルスケール + 0.5LSB)の理想値とのずれです。

**オフセット誤差 (OFFSET ERROR)** とは、コード 2047 から 2048 への遷移を発生させるために必要な、2 つの入力電圧の差 [ $(V_{IN+}) - (V_{IN-})$ ] です。

**出力ディレイ (OUTPUT DELAY)** は、クロック入力の立ち下がりエッジから出力ピンにアップデートされたデータが現われるまでの遅延時間です。

**パイプライン・ディレイ (PIPELINE DELAY : LATENCY)** については「変換レイテンシ」(CONVERSION LATENCY)をご覧ください。

**正のフルスケール誤差(POSITIVE FULL SCALE ERROR)** は、最後のコード遷移点の実測値と(正側フルスケール - 1.5LSB)の理想値とのずれのことです。

**電源電圧変動除去比 (POWER SUPPLY REJECTION RATIO : PSRR)** は、電源電圧の変動を ADC でどの程度除去できるかを表したものです。PSRR は、最大 DC 電源限界値の電源での A/D コンバータのフルスケールの出力に対する、最小 DC 電源限界値の電源での A/D コンバータのフルスケールの出力の比であり、dB で表されます。

**信号 / ノイズ比 (SIGNAL TO NOISE RATIO: SNR)** は、クロック信号の 1/2 以下の周波数における、歪みと DC 成分を除いたその他すべてのスペクトラル成分の実効値に対する入力信号の実効値の比で、dB で表されます。

**信号 / (ノイズ + 歪み) 比 (SIGNAL TO NOISE PLUS DISTORTION RATIO: S/(N + D) または SINAD)** は、クロック信号の 1/2 以下の周波数における、歪みを含め DC 成分を除いたその他すべてのスペクトラル成分の実効値に対する入力信号の実効値の比として表されます。

**スピリアス・フリー・ダイナミック・レンジ (SPURIOUS FREE DYNAMIC RANGE : SFDR)** は、入力信号の実効値に対するピーク・スピリアス信号との差で、dB で表されます。ここで言うピーク・スピリアス信号とは、出力スペクトラムに現われる任意のスピリアス信号であり、入力に現われるものではありません。

**全高調波歪み (TOTAL HARMONIC DISTORTION: THD)** は、最初から第 6 番目までの歪み成分の実効値の総和に対する入力信号の実効値 (rms 値) の比で、dB で表されます。全高調波歪み THD は次式から求めます。

$$\text{THD} = 20 \times \log \sqrt{\frac{f_2^2 + \dots + f_7^2}{f_1^2}}$$

$f_1$  は基本周波数 (出力) パワーの実効値 (RMS 値)、 $f_2$  から  $f_7$  は出力スペクトラムに現れる高調波のうち最初から第 6 番目までの高調波のパワーです。

**二次高調波歪み (SECOND HARMONIC DISTORTION (2ND HARM))** とは、出力に現れる入力基本周波数の RMS パワーと二次高調波のパワーとの差を dB で表した値です。

**三次高調波歪み (THIRD HARMONIC DISTORTION (3RD HARM))** とは、出力に現れる入力基本周波数の RMS パワーと三次高調波のパワーとの差を dB で表した値です。

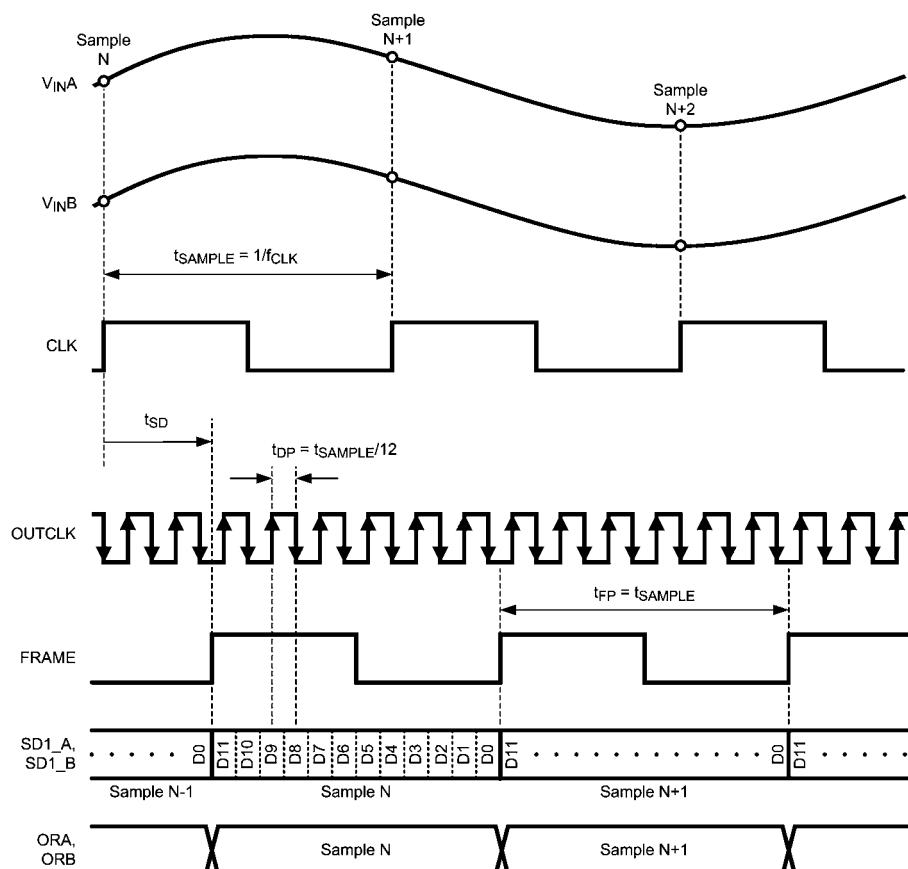

## タイミング図

Serial Output Data Timing

FIGURE 1.

FIGURE 2. Serial Output Data Format in Single-Lane Mode

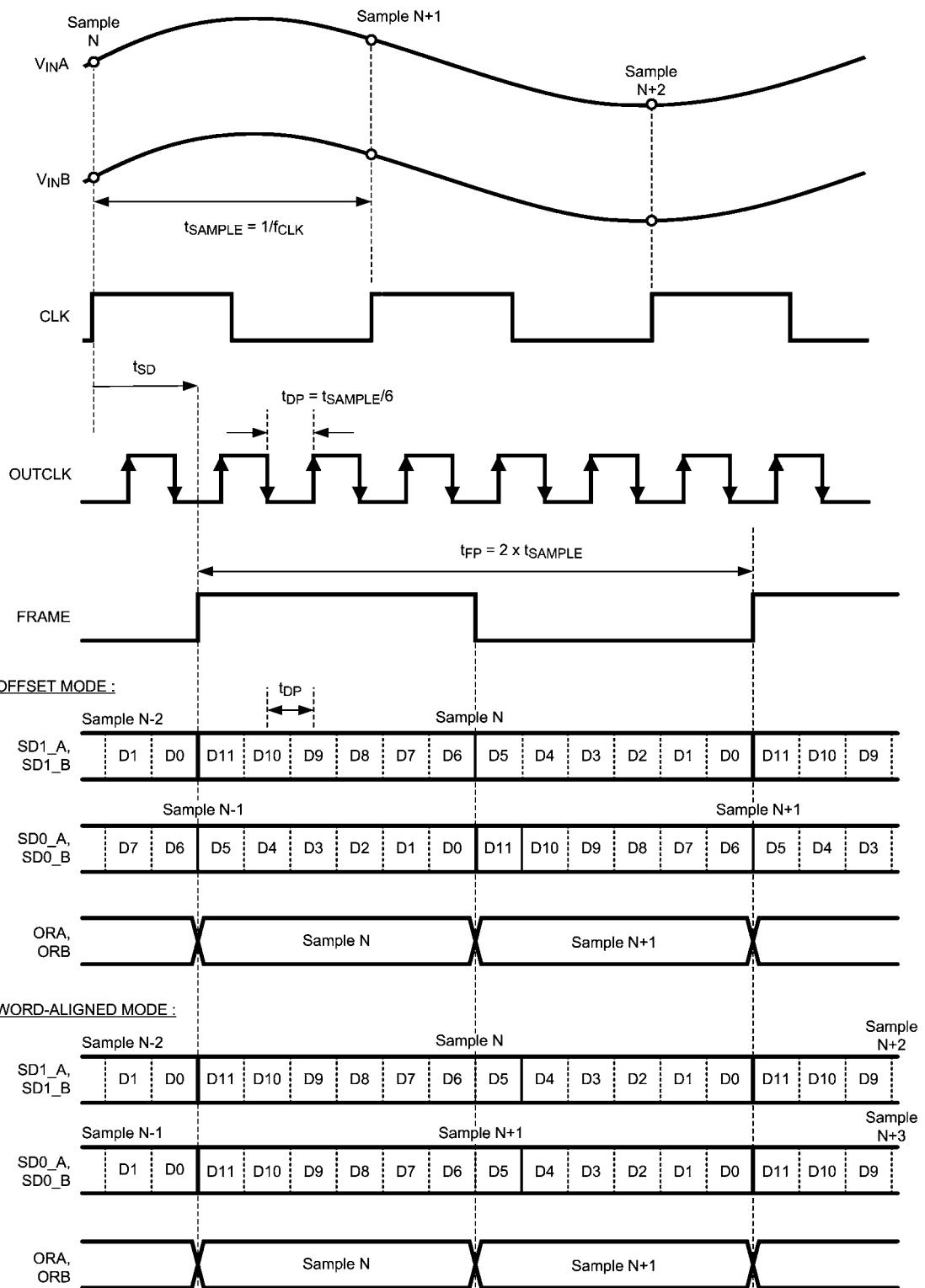

## タイミング図 (つづき)

FIGURE 3. Serial Output Data Format in Dual-Lane Mode

## 変換特性

FIGURE 4. Transfer Characteristic

## 代表的な性能特性 DNL、INL

特記のない限り、AGND = DRGND = 0V、 $V_A = 3.3V$ 、 $V_{DR} = + 3.0V$ 、内部  $V_{REF} = + 1.2V$ 、 $f_{CLK} = 105MHz$ 、50% デューティーサイクル、DCS ディスエーブル、 $V_{CM} = V_{CMO}$ 、 $T_A = 25^{\circ}C$ 。

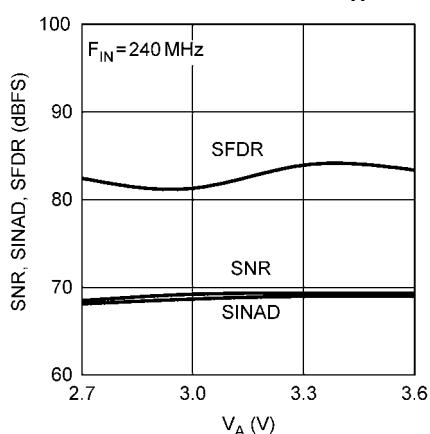

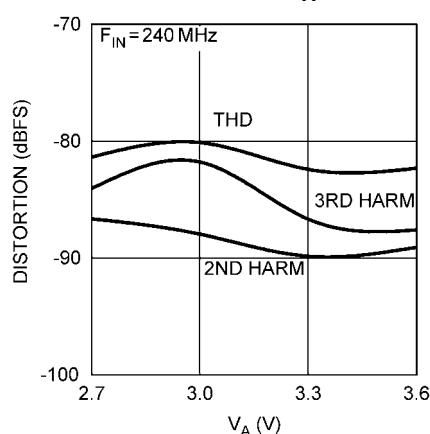

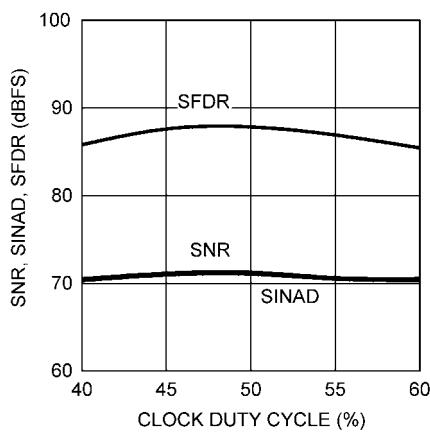

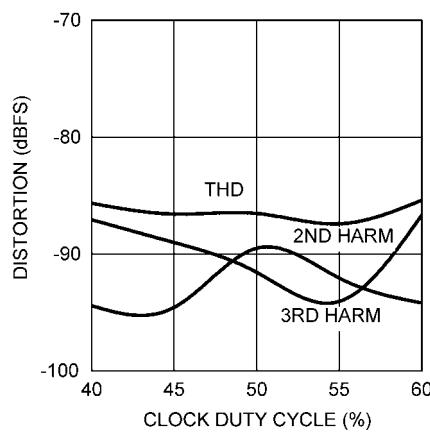

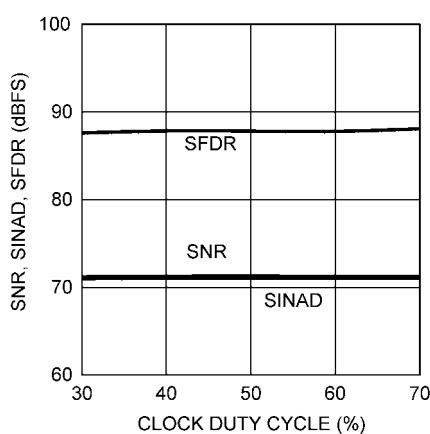

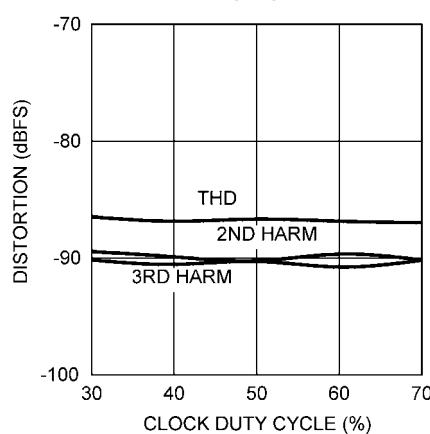

## 代表的な性能特性

特記のない限り、AGND = DRGND = 0V、 $V_A = 3.3V$ 、 $V_{DR} = +3.0V$ 、内部  $V_{REF} = +1.2V$ 、 $f_{CLK} = 105MHz$ 、50% デューティーサイクル、DCS ディスエーブル、 $V_{CM} = V_{CMO}$ 、 $f_{IN} = 10MHz$ 、 $T_A = 25^\circ C$ 。

**SNR, SINAD, SFDR vs.  $V_A$**

**Distortion vs.  $V_A$**

**SNR, SINAD, SFDR vs. Clock Duty Cycle**

**Distortion vs. Clock Duty Cycle**

**SNR, SINAD, SFDR vs. Clock Duty Cycle, DCS Enabled**

**Distortion vs. Clock Duty Cycle, DCS Enabled**

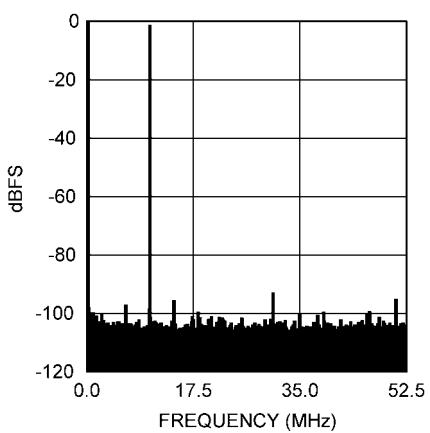

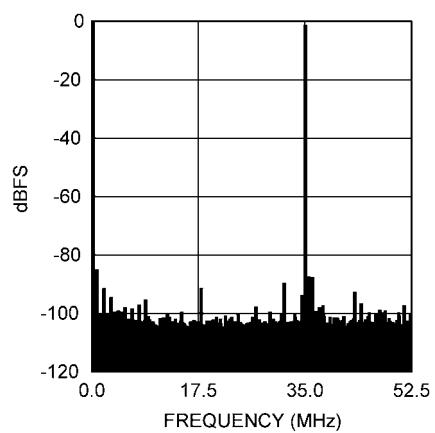

### 代表的な性能特性(つづき)

特記のない限り、AGND = DRGND = 0V、 $V_A = 3.3V$ 、 $V_{DR} = +3.0V$ 、内部  $V_{REF} = +1.2V$ 、 $f_{CLK} = 105MHz$ 、50% デューティー・サイクル、DCS ディスエーブル、 $V_{CM} = V_{CMO}$ 、 $f_{IN} = 10MHz$ 、 $T_A = 25^\circ C$ 。

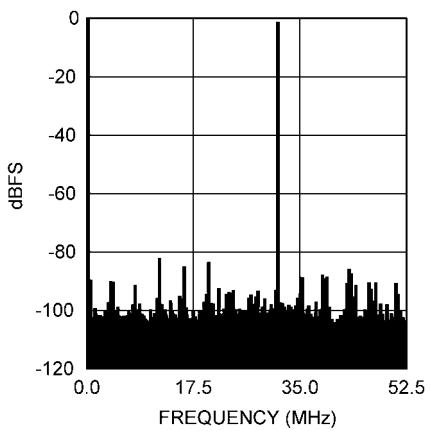

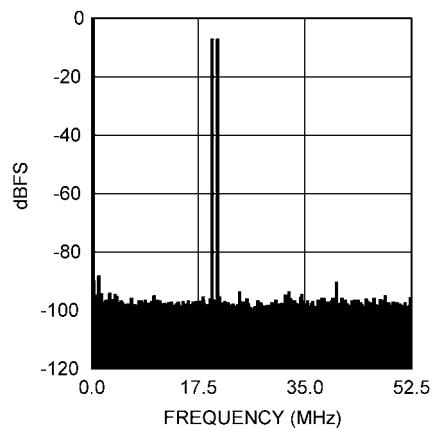

Spectral Response @ 10 MHz Input

Spectral Response @ 70 MHz Input

Spectral Response @ 240 MHz Input

IMD,  $f_{IN1} = 20 \text{ MHz}$ ,  $f_{IN2} = 21 \text{ MHz}$

## 機能説明

ADC12DS105 は、+ 3.3V 電源で動作し差動パイプライン・アーキテクチャと誤差補正回路とオンチップ・サンプル / ホールド回路を使用して差動アナログ入力信号を 12 ビットにデジタル化し、最大性能を確保しています。リファレンス電圧には安定した 1.2V 内部リファレンスか 1.2V の外部リファレンスを使います。外部リファレンス・ピンは駆動が簡単になるように内部でバッファされています。デューティ・サイクル安定化および出力データのフォーマットは、4 ステートの機能ピン OF/DCS (ピン 19) によって選択可能です。出力データは、オフセット・バイナリまたは 2 の補数のいずれかに設定できます。

## アプリケーション情報

### 1.0 動作条件

ADC12DS105 の動作条件としては次の各値を推奨します。

$$2.7V \quad V_A \quad 3.6V$$

$$2.7V \quad V_{DR} \quad V_A$$

$$25MHz \quad f_{CLK} \quad 105MHz$$

1.2V 内部リファレンス

$V_{REF} = 1.2V$  (外部リファレンス)

$V_{CM} = 1.5V$  ( $V_{CMO}$  より)

### 2.0 アナログ入力

#### 2.1 信号入力

##### 2.1.1 差動アナログ入力ピン

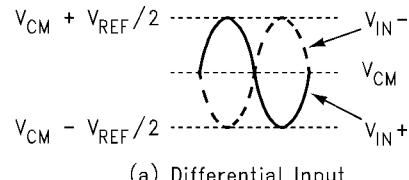

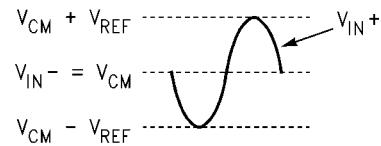

ADC12DS105 は、2 つのチャネルのそれぞれについて 1 対のアナログ信号入力ピンを備えています。 $V_{IN+}$  と  $V_{IN-}$  を差動入力ピンとして使います。入力信号  $V_{IN}$  は次のように定義されます。

$$V_{IN} = (V_{IN+}) - (V_{IN-})$$

Figure 5 は、入力信号として予想される範囲を示したもので、コモン・モード入力電圧 ( $V_{CM}$ ) は 1.5V でなければならぬことに注意してください。 $V_{CM}$  に対して  $V_{CMO}$  (ピン 7, 9) を使用すると、アナログ入力信号として最適な入力コモンモード・レベルになります。個々の入力信号のピークは、決して 2.6V を超えてはなりません。差動ペアの各アナログ入力ピンは、最大ピーク・ツー・ピーク電圧が 1V であり、互いに 180° 位相がずれた状態で、 $V_{CM}$ を中心とする必要があります。各アナログ入力ピンにおけるピーク・ツー・ピーク電圧振幅は 1V を超えないようしてください。1V を超えると出力データはクリッピングされます。

(a) Differential Input

(b) Single-Ended Input

FIGURE 5. Expected Input Signal Range

单一周波数の正弦波で、フルスケール誤差は次式で計算できます (単位 : LSB)。

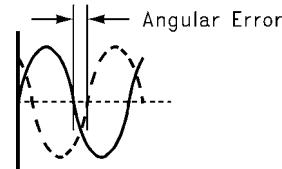

$$E_{FS} = 4096 (1 - \sin(90^\circ \text{ dev}))$$

"dev" は、互いに 180° の相対位相差を持つとした場合の 2 つの信号間の位相誤差です (Figure 6 を参照)。入力信号の周波数が 1 つだけのときは、位相差があると (つまり差動信号の位相差が正確に 180° になっていないと)、実効フルスケール入力の範囲が狭くなってしまいます。複雑な波形の場合は位相差があると歪みが生じます。

FIGURE 6. Angular Errors Between the Two Input Signals Will Reduce the Output Level or Cause Distortion

アナログ入力ピンを駆動する信号源のソース・インピーダンスは 100Ω 未満にしてください。差動入力のソース・インピーダンス・マッチングを行うと、偶数次高調波特性が改善されます (特に第二高調波)。

Table 1 は、ADC12DS105 の入力と出力との関係を示したものです。

## アプリケーション情報(つづき)

TABLE 1. Input to Output Relationship

| $V_{IN+}$            | $V_{IN-}$            | Binary Output  | 2's Complement Output |                     |

|----------------------|----------------------|----------------|-----------------------|---------------------|

| $V_{CM} - V_{REF}/2$ | $V_{CM} + V_{REF}/2$ | 0000 0000 0000 | 1000 0000 0000        | Negative Full-Scale |

| $V_{CM} - V_{REF}/4$ | $V_{CM} + V_{REF}/4$ | 0100 0000 0000 | 1100 0000 0000        |                     |

| $V_{CM}$             | $V_{CM}$             | 1000 0000 0000 | 0000 0000 0000        | Mid-Scale           |

| $V_{CM} + V_{REF}/4$ | $V_{CM} - V_{REF}/4$ | 1100 0000 0000 | 0100 0000 0000        |                     |

| $V_{CM} + V_{REF}/2$ | $V_{CM} - V_{REF}/2$ | 1111 1111 1111 | 0111 1111 1111        | Positive Full-Scale |

## 2.1.2 アナログ入力の駆動

ADC12DS105 の  $V_{IN+}$ 、 $V_{IN-}$  の入力は、アナログ・スイッチとそれに続くスイッチ・キャパシタ・アンプから構成されています。

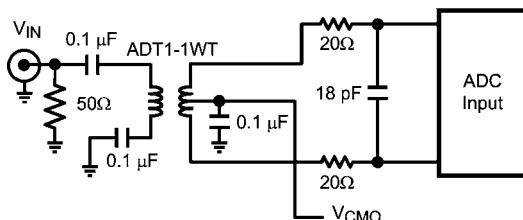

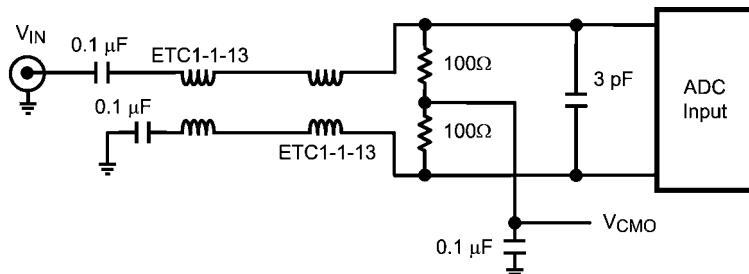

Figure 7 と Figure 8 に、シングルエンド入力を差動入力に変換する回路の例を示します。Figure 7 の回路は、約 70MHz までの入力周波数で正常に動作しますが、Figure 8 の回路は 70MHz を超える入力周波数でも正常に動作します。

FIGURE 7. Low Input Frequency Transformer Drive Circuit

FIGURE 8. High Input Frequency Transformer Drive Circuit

トランスを使用してシングルエンドから差動に変換を行う際の弱点は、ほとんどの RF トランスの低周波側の性能が低いことです。差動アンプは、低周波アプリケーションのアナログ入力の駆動に使用できます。アンプは、サンプル / ホールド動作によりアナログ入力に生ずるチャージグリッチに対して、クロックが High になりサンプル電圧が A/D コンバータのコアへ通過する前にセトリングするように充分高速である必要があります。

## 2.1.3 入力コモンモード電圧

入力コモンモード電圧  $V_{CM}$  は 1.4V ~ 1.6V の範囲とし、アナログ信号のピーク電圧がグラウンドを下回らないように、かつ、2.6V を上回らないように設定しなければなりません。入力コモンモード電圧として  $V_{CMO}$  (ピン 7、9) の使用を推奨します。

## 2.2 リファレンス電圧ピン

ADC12DS105 は、1.2V の内部または外部リファレンス電圧で動作するように設計されています。外部リファレンス入力が  $V_{REF}$  ピンに加えられないときは、1.2V の内部リファレンス電圧がデフォルト条件です。 $V_{REF}$  ピンに電圧を印加した場合は、その電圧がリファレンスとして使用されます。 $V_{REF}$  ピンは、リファレンス電圧入

力ピンの近くに 0.1 μF コンデンサを配置して常にグラウンドにバイパスしてください。

また、入力信号の振幅が大きいほど THD も劣化します。リファレンス電圧およびアナログ入力信号に対するすべてのグラウンドは、グラウンド経路に流れるノイズ電流の影響を抑えるため、グラウンド・プレーンに対して一点アースで接続するのが極めて重要になります。

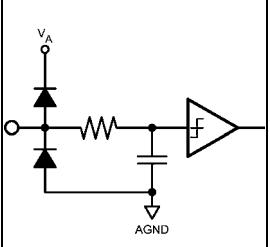

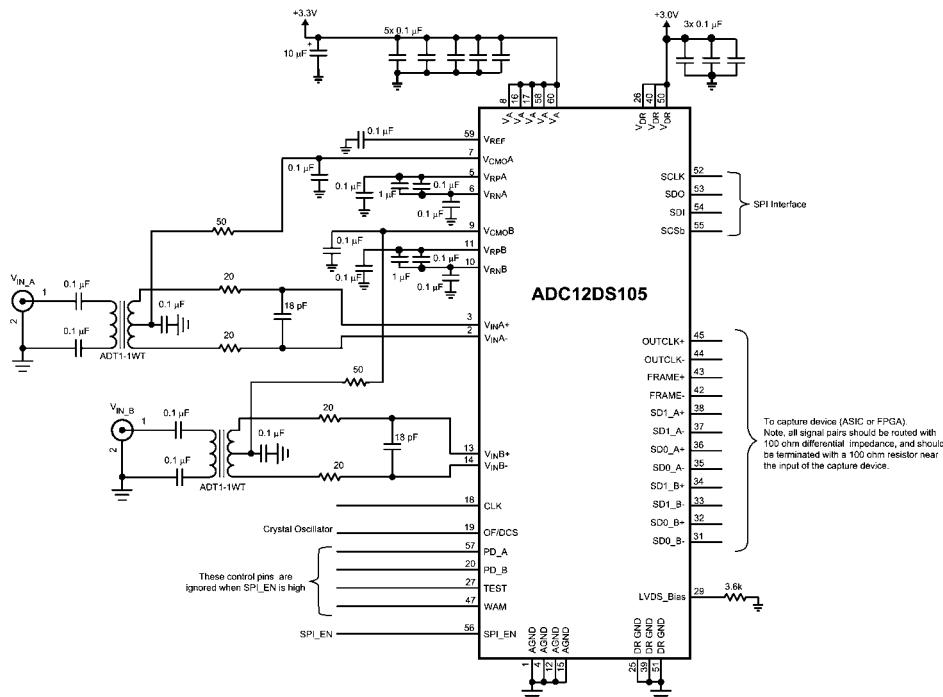

バイパス用にリファレンス電圧バイパス・ピン ( $V_{RP}$ 、 $V_{CMO}$ 、 $V_{RN}$ ) を備えています。これらのピンを、低 ESL (等価直列インダクタンス) の 1 μF コンデンサで AGND にバイパスし、それは浮遊インダクタンスを最小にするためピンの近くに配置する必要があります。0.1 μF コンデンサと 1 μF コンデンサを並列にして、 $V_{RP}$  と  $V_{RN}$  の間のできるだけピンの近くに配置する必要があります。この設定を Figure 9 に示します。この回路は、SFDL や SNR、またはその両方を悪化させる可能性のあるリファレンスの発振を防ぐために必要です。 $V_{CMO}$  は温度的に安定した 1.5V リファレンスとして、1mA までの負荷に対応できます。他のピンには負荷を接続しないでください。

## アプリケーション情報 (つづき)

上記で規定した容量より小容量のコンデンサを使用すると、パワーダウン・モードからの復帰時間は短くなりますが、ノイズ性能は低下します。 $V_{CMO}$  を除くこれらのピンに負荷を接続すると性能劣化を引き起こす場合があります。

リファレンス・バイパス・ピンの公称電圧は次のとおりです。

$$V_{CMO} = 1.5V$$

$$V_{RP} = 2.0V$$

$$V_{RN} = 1.0V$$

### 2.3 OF/DCS ピン

デューティ・サイクル安定化および出力データのフォーマットは、この4ステートの機能ピンによって選択可能です。デューティ・サイクル安定化回路を有効にすると、デューティ・サイクル 30% ~ 70% のクロック入力が補償され、安定した内部クロックが生成されるため、デバイスの性能が向上します。OF/DCS =  $V_A$  の場合、出力データのフォーマットは2の補数となり、入力クロックにはデューティ・サイクル安定化機能が適用されません。OF/DCS = AGND の場合、出力データのフォーマットはオフセット・バイナリとなり、入力クロックにはデューティ・サイクル安定化機能が適用されません。OF/DCS = (2/3)\* $V_A$  の場合、出力データのフォーマットは2の補数となり、入力クロックにデューティ・サイクル安定化機能が適用されます。OF/DCS = (1/3)\* $V_A$  の場合、出力データのフォーマットはオフセット・バイナリとなり、入力クロックにデューティ・サイクル安定化機能が適用されます。このピンのロジック・レベルは動作中に変更することも可能ですが、切り換え後数クロック・サイクルにわたって正しくないデータが出力される可能性があるため、そのような使い方は推奨しません。

Note: この信号は SPI\_EN が High でシリアル制御インターフェースがイネーブルの場合は無効です。

### 3.0 デジタル入力

デジタル CMOS 互換入力は、CLK、PD\_A、PD\_B、Reset\_DLL、DLC、TEST、WAM、SPI\_EN、SCSb、SCLK、SDI で構成されます。

#### 3.1 クロック入力

CLK はサンプリングのタイミングを決めます。最適のノイズ特性を実現するために、クロック入力は電気的特性表で示される範囲で、安定した低ジッタ・クロック信号で駆動してください。また、クロック入力信号は、遷移時間が短くなければなりません。これは、低ジッタ・サイン波クロック信号源を高速バッファ・ゲートに通すことによって得られます。クロック信号の配線パターンは最短とし、アナログ、デジタルを問わず他の一切の信号線と交差しないようにしてください。

また、クロック信号は内蔵ステート・マシンを駆動します。CLK が途切れると、内部キャパシタに充電されていた電位が徐々に下がってきます。この電位が一定値以下になると出力データの精度が低下します。サンプリング・レートの下限が規定されているのはこのためです。

クロック・ラインはラインの特性インピーダンスによってソース端で終端しなければなりません。ラインの全長にわたってインピーダンスが一定になるように注意してください。特性インピーダンスの求め方はアプリケーション・ノート AN-905 を参照してください。

A/D コンバータのクロック・ピンを駆動するクロック源で他の負荷を駆動しないようにしてください。クロック源から他の入力負荷も駆動している場合は、クロック・ラインの特性インピーダンスに等しい抵抗と次に示す容量のコンデンサを用いた直列 RC 回路を用いて、グラウンドに AC 終端を行ってください。

$$C \geq \frac{4 \times t_{PD} \times L}{Z_0}$$

ここで  $t_{PD}$  はクロック配線の信号伝搬遅延時間、"L" は配線長、 $Z_0$  はクロック配線の特性インピーダンスです。この終端回路は ADC クロック・ピンのできるだけ近くに、かつ、クロック・ソースから見て遠い側に配置してください。 $t_{PD}$  の代表値は、FR-4 を使用した基板でよそ 150ps/inch (60ps/cm) です。"L" の単位と  $t_{PD}$  の単位は一致させてください (cm またはインチ)。

クロック信号のデューティ・サイクルは A/D コンバータの性能に影響を与えることがあります。正確なデューティ・サイクルの達成が困難なので、ADC12DS105 ではデューティ・サイクル・スタビライザを備えています。

#### 3.2 パワーダウン (PD\_A、PD\_B)

コンバータを使用しない場合に PD\_A ピンと PD\_B ピンを High レベルにすれば、ADC12DS105 の対応するチャネルはパワーダウン・モードになり消費電力が抑えられます。チャネルはすべて同時にまたは個別にパワーダウンさせることができます。パワーダウン中のバイオペイント中のデータは、破壊されます。

"Power Down Mode Exit Cycle" 時間の長さは、リファレンス・バイパス・ピン ( $V_{RP}$ 、 $V_{CMO}$ 、 $V_{RN}$ ) に接続したコンデンサの値によって決まります。これらのコンデンサはパワーダウン・モード中に放電されますが、正確な変換を再び行う前にオンチップ回路によって再充電されなければなりません。容量が小さいほどパワーダウン・モードからの復帰は少し高速になりますが、SNR、SINAD、ENOB 性能は低下します。

Note: この信号は SPI\_EN が High でシリアル制御インターフェースがイネーブルの場合は無効です。

#### 3.3 Reset\_DLL

このピンは通常動作では Low です。入力クロック周波数が突然変化すると、内部のタイミング回路がロックが外れる場合があります。このピンを 1μs だけ High にしてサイクルすると、DLL を再ロックすることができます。Reset\_DLL をアサートした後、DLL がロックされるまでに数 μs かかります。

#### 3.4 DLC

このピンで出力データ構成を設定します。この信号を論理 1 にすると、各チャネルのデータはすべてシングル・レーン (SD1\_x) に供給されます。この信号を論理 0 にすると、各チャネルのデータはすべてシングル・レーン (SD0\_x および SD1\_x) に供給されます。これにより、高速データレートでのデータの読み出しが容易になります。

Note: この信号は SPI\_EN が High で SPI インタフェースがイネーブルの場合は無効です。

#### 3.5 TEST

この信号を High にすると、固定のテスト・パターン (101001100011 MSB ~ LSB の順序) がデータ出力に供給されます。データ出力に供給されます。Low にすると、ADC は通常の動作モードになります。シリアル制御インターフェースを通じてカスタム・テスト・パターンを指定することもできます。

Note: この信号は SPI\_EN が High で SPI インタフェースがイネーブルの場合は無効です。

## アプリケーション情報 (つづき)

### 3.6 WAM

この信号を論理 0 にした場合、デュアル・レーン・モードの場合にのみシリアル・データ・ワードは半ワードだけオフセットされます。この信号を論理 1 にすると、シリアル・データは相互に整列します。シングル・レーン・モードにするには、このピンは論理 0 に設定しなければなりません。

Note: この信号は SPI\_EN が High で SPI インタフェースがイネーブルの場合は無効です。

### 3.7 SPI\_EN

この信号を High にすると SPI インタフェースがイネーブルになります。この場合、直接制御されるピン (OF/DCS、PD\_A、PD\_B、DLC、WAM、TEST) は無効です。この信号を Low にすると、SPI インタフェースはディスエーブルとなり、直接制御ピンがイネーブルになります。

### 3.8 SCSb、SDI、SCLK

これらのピンは、SPI インタフェースで使用します。詳細はセクション 5.0 を参照してください。

## 4.0 デジタル出力

デジタル出力には、6 つの LVDS 信号ペア (SD0\_A、SD1\_A、SD0\_B、SD1\_B、OUTCLK、FRAME)、および CMOS 論理出力 ORA、ORB、DLL\_Lock、SDO があります。

### 4.1 LVDS 出力

各チャネルのデジタル・データはシリアル形式で供給されます。シリアル・データ・フォーマットには 2 種類の動作モードがあります。シングル・レーン・シリアル・フォーマット (Figure 2 を参照) はチャネルごとに差動データ信号の 1 セットを使用します。デュアル・レーン・シリアル・フォーマット (Figure 3 参照) はチャネルごとに差動データ信号の 2 セットを使用して、データクロック周波数を 2 分の 1 に低速化します。動作速度が遅い場合 (代表値で 65MSPS 未満) はシングル・レーン・モードの方が使用効率はよくなります。変換レートが速い場合はデュアル・レーン方式の方が望れます。いずれにしても DDR タイプのクロック法が使われます。各データ・チャネルに対して、オーバーレンジ表示が用意されています。OR 信号はデータのフレームごとに更新されます。

### 4.2 ORA、ORB

これらの CMOS 出力は対応するチャネルのデータ出力が High または Low の方向に範囲外になると論理 High になります。

### 4.3 DLL\_Lock

内部 DLL が入力 CLK にロックされると、このピン出力は論理 High になります。入力 CLK が突然変化すると、内部 DLL はロックが外れる可能性があり、その場合このピンは論理 Low になります。Reset\_DLL (28 ピン) をサイクルすると、入力 CLK に対して内部 DLL が再ロックされます。

### 4.4 SDO

このピンは、SPI インタフェースで使用します。詳細はセクション 5.0 を参照してください。

FIGURE 9. Application Circuit

### 5.0 シリアル制御インターフェース

ADC12DS105 は制御レジスタへのアクセスを可能とするシリアル・インターフェースを備えています。このシリアル・インターフェースは多くのマイクロコントローラや DSP コントローラで使用されている SPI タイプのインターフェースと互換の汎用 4 線式同期インターフェースです。

シリアル・コントロール・インターフェースを動作させるには ADC に入力クロックを与える必要があります。SPI\_EN (56 ピン) 信号を High にすると SPI インタフェースがイネーブルになります。この場合、直接制御されるピン (OF/DCS、PD\_A、PD\_B、DLC、WAM、TEST) は無効です。この信号を Low にすると、SPI インタフェースはディスエーブルとなり、直接制御ピンがイネーブルになります。

## アプリケーション情報(つづき)

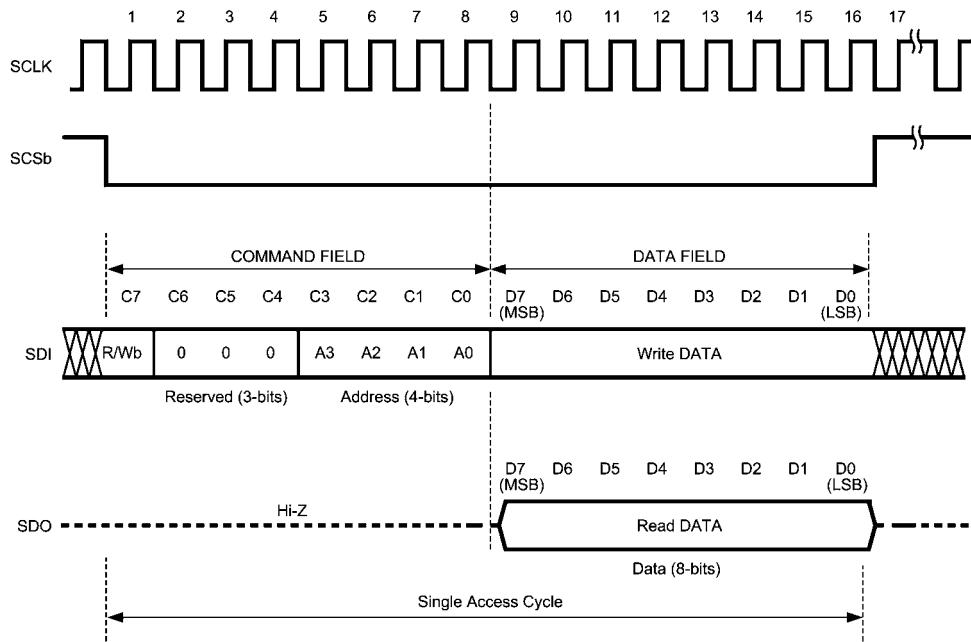

各シリアル・インターフェース・アクセス・サイクルは正確に 16 ビット長です。Figure 10 はこのインターフェースで使用されるアクセス・プロトコルが示されています。各信号の機能を次に説明します。読み取りタイミングは Figure 11 に、書き込みタイミングは Figure 12 に示されています。

FIGURE 10. Serial Interface Protocol

**SCLK:** 入力データ (SDI) をその立ち上がりエッジでレジスタ入力し、出力データ (SDO) をその立ち下がりエッジで出力します。クロックがイネーブルまたはディスエーブルされたとき、クロックのパルス幅の最小仕様値に違反しない限り、ユーザーはクロックをディスエーブルしてそれを Low 状態に保持することができます。

**SCSb:** シリアル・インターフェースのチップ選択。この信号がアサートされるたびに、新しいレジスタ・アクセスが始まります。つまり、SDATA フィールドのプロトコルが必要です。この信号は 16 番目のクロックごとに、アサートを解除する必要があります。SCSb が 16 番目のクロックよりも早くアサート解除されたらアドレスまたはデータの書き込みは起いません。書き込み動作の場合は、この立ち上がりエッジでちよびシフト入力されたアドレスが捕捉され、アドレスされたレジスタに書き込まれます。アサート解除するために必要なパルス幅の最小値があり、「電気的特性」に規定されています。

**SDI:** シリアル・データ。SCLK 対してセットアップ / ホールド要件満たさなければなりません。各サイクルは 16 ビット長です。

R/Wb:

この値が '1' は読み取り動作、'0' は書き込み動作を示します。

予備:

将来のための予備です。0 に設定してください。

ADDR:

最大 3 レジスタまでアドレス可能です。

DATA:

書き込み動作では、このフィールドの値は SCSb がアサート解除されたとき、このサイクルでアドレスされたレジスタに書き込まれます。読み取り動作ではこのフィールドは無視されます。

**SDO:** この出力は通常 TRI-STATE であり、SCSb がアサートされた場合にのみ駆動されます。SCSb がアサートされると、最初のパルス時にアドレスされたレジスタ内容が 2 番目の 8 個の SCLK の立ち下がりエッジでシフト出力されます。電源投入時にはアドレスのデフォルト値は 00h です。

## アプリケーション情報(つづき)

FIGURE 11. Read Timing

FIGURE 12. Write Timing

## デバイス制御レジスタ、アドレス 0h

|    |     |     |    |     |      |      |   |

|----|-----|-----|----|-----|------|------|---|

| 7  | 6   | 5   | 4  | 3   | 2    | 1    | 0 |

| OM | DLC | DCS | OF | WAM | PD_A | PD_B |   |

リセット状態 : 08h

## Bits (7:6) 動作モード

0 0 通常動作。

0 1 テスト出力モード。固定のテスト・パターン (10100110001111, MSB &gt; LSB) がデータ出力に供給されます。

1 0 テスト出力モード。データ・パターンはレジスタ 01h とレジスタ 02h でユーザーによって定義され、データ出力に供給されます。

1 1 予備。

Bit 5 データ・レーン構成このビットを '0' に設定すると、シリアル・データ・インターフェースはデュアル・レーン・モードに構成され、データ・ワードは 2 つのデータ出力 (SD1 と SDO) にシングルレーン・インターフェースの場合の半分の速度で出力されます。このビットを '1' に設定するとシリアル・データは SD1 にのみ出力され、SD0 出力はハイ・インピーダンス状態に保持されます。

Bit 4 デューティ・サイクル・スタビライザ。このビットを '0' に設定すると、DCS はオフになります。このビットを '1' に設定すると DCS がオンになります。

Bit 3 出力データ・フォーマット。このビットを '1' に設定すると、データ出力は「2 の補数」形式になります。このビットを '0' に設定すると、データ出力は「オフセット・バイナリ」形式になります。

Bit 2

ワード整列モード。

このビットはシングル・レーン・モード動作では '0' に設定しなければなりません。

デュアル・レーン・モードではこのビットが '0' に設定されると、シリアル・データには半ワードだけオフセットが加わります。これによって、デバイスのレイテンシが最小になります。このビットが '1' に設定されると、シリアル・データ・ワードはワード整列モードになります。このモードでは、SD1 レーン上のシリアル・データは 1 CLK サイクルだけ、さらに遅れます。(Figure 3 を参照)。

Bit 1

チャネル A のパワーダウン。このビットを '1' に設定すると、チャネル A はパワーダウン状態になり、通常動作が保留されます。

Bit 0

チャネル B のパワーダウン。このビットを '1' に設定すると、チャネル B はパワーダウン状態になり、通常動作が保留されます。

## ユーザー・テスト・パターン・レジスタ 0、アドレス 1h

|          |                          |   |   |   |   |   |   |

|----------|--------------------------|---|---|---|---|---|---|

| 7        | 6                        | 5 | 4 | 3 | 2 | 1 | 0 |

| Reserved | User Test Pattern (13:6) |   |   |   |   |   |   |

## アプリケーション情報 (つづき)

リセット状態 : 00h

Bits (7:6) 予備。0に設定してください。

Bits (5:0) ユーザー・テスト・パターン。テスト出力モードでは12ビット・パターンの内の上位6ビットがデータ出力に供給されます。

ユーザー・テスト・パターン・レジスタ1、アドレス2h

|                         |   |   |   |   |   |          |   |

|-------------------------|---|---|---|---|---|----------|---|

| 7                       | 6 | 5 | 4 | 3 | 2 | 1        | 0 |

| User Test Pattern (5:0) |   |   |   |   |   | Reserved |   |

リセット状態 : 00h

Bits (7:2) ユーザー・テスト・パターン。テスト出力モードでは12ビット・パターンの内の下位6ビットがデータ出力に供給されます。

Bits (1:0) 予備。0に設定してください。

## 6.0 電源構成

いずれの電源ビンも当該ピンの近くにバイパス・コンデンサとして0.1μFコンデンサと10pFセラミック・コンデンサを1つずつ挿入してください。直列インダクタンスが小さいリードレス・チップコンデンサを推奨します。

あらゆる高速コンバータと同じように、ADC12DS105も電源ノイズに敏感です。また、アナログ電源ピンに乗るノイズ・レベルは100mV<sub>P-P</sub>より先低く抑えてください。

どのピンも、電源電圧より高い電圧を加えることは、たとえ瞬時であっても許されません。特に電源の投入時、遮断時には注意してください。

## 7.0 レイアウトとグラウンド

適切なグラウンド処理とすべての信号ラインの適切な配線は、正確な変換を確保するには必須の条件です。ADC12DS105はアナログ領域とデジタル領域とのあいだに挟まれる形になります。仕様どおりの性能を発揮するには、この2つの領域を分離しておく必要があります。

ノイズの多いデジタル回路とノイズに敏感なアナログ回路との間の容量性カップリングにより、変換性能が低下する可能性があります。解決方法として、アナログ回路をデジタル回路から十分に分離させたレイアウトを行い、クロック信号の配線パターンを最短にします。

デジタル・スイッチング・トランジエント（デジタル回路の瞬間的スイッチング電圧によるオーバーシュート/アンダーシュート）は高周波成分を大きく発生します。表皮効果があるためグラウンド・プレーンの総銅箔重量は、ロジック回路の生成するノイズにはあまり影響がありません。グラウンド・プレーンの体積よりも、全表面積の方が重要です。

一般に、アナログとデジタルの配線パターンどうしのクロストークを防ぐには、両者の配線パターンを互いに90°交差させるのが望ましいとされています。高周波 / 高分解能のシステムで精度を最大限にするためには、アナログ信号ラインとデジタル信号ラインが互いに交差する配線は避けなければなりません。クロック・ラインは最短にし、他のデジタル・ラインを含むすべてのその他のラインから分離することが重要です。一般的に受け入れられているクロック・ラインが90°互いに交差させる方法は、高周波でのちょっとしたカップリングによる問題が起こる可能性があるので避けるべきです。これは、他のラインがクロック・ラインにジッタを招き、

結果的にSN比の劣化につながります。また、クロックが高速だとアナログ回路にノイズが生じる場合もあります。

高周波 / 高分解能で最大限の性能を得るには、信号経路をまっすぐに配線すると実現できます。これは、すべての部品を通る信号経路をできるだけまっすぐな直線に配線することです。

インダクタとトランジスタのレイアウトには特に注意してください。相互インダクタンスにより、インダクタを使用する回路の特性が変わります。複数のインダクタを使用する場合には、決して並べて配置しないでください。たとえインダクタ部品全長の一部であっても並べて配置してはなりません。例えば、アナログ入力用とクロック入力用のトランジスは互いに90°に配置して磁気結合を避けるようにしてください。

スプリアス信号が入力にカップリングするのを避けるために、アナログ入力は、ノイズの多い信号経路から十分に分離してください。コンバータの入力ピンとグラウンドの間、またはリファレンス入力ピンとグラウンドに接続される任意の外部回路（例えば、フィルタ用のコンデンサ）は、グラウンド・プレーン中の非常にクリーンなノイズの少ない1点で接続してください。

すべてのアナログ回路（入力アンプ、フィルタ、リファレンス電圧回路など）はボード上のアナログ領域に配置してください。すべてのデジタル回路とデジタル入出力（I/O）は、デジタル領域に配置してください。ADC12DS105は両者の中間に配置してください。さらに、リファレンス電圧回路と入力信号に関連する回路に含まれているすべての部品については、そのリターン側どうしを短い配線でノイズのない一点に接続してからグラウンド・プレーンに落としてください。すべてのグラウンドへの接続は、グラウンドへの経路が低インダクタンスになるように配線してください。

## 8.0 ダイナミック特性

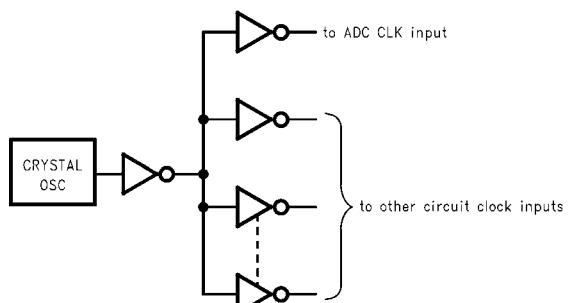

最高のダイナミック特性を実現するために、CLK入力をドライブするクロック信号源は遷移時間が短くジッタのないものでなければなりません。Figure 13に示されるようなバッファを用いてクロック・ツリーを構成して、A/Dのクロック信号をその他のデジタル回路から分離しなければなりません。クロック・ツリーに使用するゲートの動作周波数は、発生したジッタを阻止する場合に使用するゲートの動作周波数よりも大幅に高い値にする必要があります。

セクション7.0で述べたように、A/Dクロック・ラインをできる限り短くかつその他の任意の信号から十分に離して置くのは、良い手段です。別の信号はクロック信号にジッタを招く可能性があり、SNRの性能劣化につながる場合や、クロック信号が原因でほかの配線にノイズを生じることもあります。信号ラインが互いに90°交わっているときでも容量性のカップリングが起こりますので、クロック・ラインは90°の交差もしないようにしてください。

FIGURE 13. Isolating the ADC Clock from other Circuitry with a Clock Tree

# ADC12DS105シリアル LVDS 出力付デュアル 12 ビット、105MSPS A/D コンバータ

外形寸法図 単位は millimeters

このドキュメントの内容はナショナルセミコンダクター社製品の関連情報として提供されます。ナショナルセミコンダクター社は、この発行物の内容の正確性または完全性について、いかなる表明または保証もいたしません。また、仕様と製品説明を予告なく変更する権利を有します。このドキュメントはいかなる知的財産権に対するライセンスも、明示的、黙示的、禁反言による惹起、またはその他を問わず、付与するものではありません。

試験や品質管理は、ナショナルセミコンダクター社が自社の製品保証を維持するために必要と考える範囲に用いられます。政府が課す要件によって指定される場合を除き、各製品のすべてのパラメータの試験を必ずしも実施するわけではありません。ナショナルセミコンダクター社は製品適用の援助や購入者の製品設計に対する義務は負いかねます。ナショナルセミコンダクター社の部品を使用した製品および製品適用の責任は購入者にあります。ナショナルセミコンダクター社の製品を用いたいかなる製品の使用または供給に先立ち、購入者は、適切な設計、試験、および動作上の安全手段を講じなければなりません。

それら製品の販売に関するナショナルセミコンダクター社との取引条件で規定される場合を除き、ナショナルセミコンダクター社は一切の義務を負わないものとし、また、ナショナルセミコンダクター社の製品の販売が使用、またはその両方に関連する特定目的への適合性、商品の機能性、ないしは特許、著作権、または他の知的財産権の侵害に関連した義務または保証を含むいかなる表示または默示的保証も行いません。

## 生命維持装置への使用について

ナショナルセミコンダクター社の製品は、ナショナルセミコンダクター社の最高経営責任者(CEO)および法務部門(GENERAL COUNSEL)の事前の書面による承諾がない限り、生命維持装置または生命維持システム内のきわめて重要な部品に使用することは認められていません。

ここで、生命維持装置またはシステムとは(a)体内に外科的に使用されることを意図されたもの、または(b)生命を維持あるいは支持するものをいい、ラベルにより表示される使用法に従って適切に使用された場合に、この不具合が使用者に身体的障害を与えると予想されるものをいいます。重要な部品とは、生命維持にかかわる装置またはシステム内のすべての部品をいい、これの不具合が生命維持用の装置またはシステムの不具合の原因となりそれらの安全性や機能に影響を及ぼすことが予想されるものをいいます。

National Semiconductor とナショナルセミコンダクターのロゴはナショナルセミコンダクターコーポレーションの登録商標です。その他のブランドや製品名は各権利所有者の商標または登録商標です。

Copyright © 2007 National Semiconductor Corporation

製品の最新情報については [www.national.com](http://www.national.com) をご覧ください。

**ナショナルセミコンダクター ジャパン株式会社**

本社 / 〒135-0042 東京都江東区木場 2-17-16 TEL.(03)5639-7300

技術資料(日本語/英語)はホームページより入手可能です。

[www.national.com/jpn/](http://www.national.com/jpn/)

# ご注意

日本テキサス・インスツルメンツ株式会社（以下TIJといいます）及びTexas Instruments Incorporated（TIJの親会社、以下TIJないしTexas Instruments Incorporatedを総称してTIといいます）は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIJとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIJの標準販売契約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIJとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。TI製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI製部品を使用したお客様の製品及びアプリケーションについて想定される危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明しておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならぬ場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、かつその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの默示的保証を無効にし、かつ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任も負いません。

TIは、TIの製品が、安全でないことが致命的となる用途ないしアプリケーション（例えば、生命維持装置のように、TI製品に不良があった場合に、その不良により相当な確率で死傷等の重篤な事故が発生するようなもの）に使用されることを認めておりません。但し、お客様とTIの双方の権限有る役員が書面でそのような使用について明確に合意した場合は除きます。たとえTIがアプリケーションに関連した情報やサポートを提供したとしても、お客様は、そのようなアプリケーションの安全面及び規制面から見た諸問題を解決するために必要とされる専門的知識及び技術を持ち、かつ、お客様の製品について、またTI製品をそのような安全でないことが致命的となる用途に使用することについて、お客様が全ての法的責任、規制を遵守する責任、及び安全に関する要求事項を満足させる責任を負っていることを認め、かつそのことに同意します。さらに、もし万一、TIの製品がそのような安全でないことが致命的となる用途に使用されたことによって損害が発生し、TIないしその代表者がその損害を賠償した場合は、お客様がTIないしその代表者にその全額の補償をするものとします。

TI製品は、軍事的用途もしくは宇宙航空アプリケーションないし軍事的環境、航空宇宙環境にて使用されるようには設計もされていませんし、使用されることを意図されておりません。但し、当該TI製品が、軍需対応グレード品、若しくは「強化プラスティック」製品としてTIが特別に指定した製品である場合は除きます。TIが軍需対応グレード品として指定した製品のみが軍需品の仕様書に合致いたします。お客様は、TIが軍需対応グレード品として指定していない製品を、軍事的用途もしくは軍事的環境下で使用することは、もっぱらお客様の危険負担においてなされるということ、及び、お客様がもっぱら責任をもって、そのような使用に関して必要とされる全ての法的要件及び規制上の要求事項を満足させなければならないことを認め、かつ同意します。

TI製品は、自動車用アプリケーションないし自動車の環境において使用されるようには設計もされていませんし、また使用されることを意図されておりません。但し、TIがISO/TS 16949の要求事項を満たしていると特別に指定したTI製品は除きます。お客様は、お客様が当該TI指定品以外のTI製品を自動車用アプリケーションに使用しても、TIは当該要求事項を満たしていなかったことについて、いかなる責任も負わないことを認め、かつ同意します。

Copyright © 2011, Texas Instruments Incorporated

日本語版 日本テキサス・インスツルメンツ株式会社

## 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。

### 1. 静電気

- 素手で半導体製品単体を触らないこと。どうしても触る必要がある場合は、リストストラップ等で人体からアースをとり、導電性手袋等をして取り扱うこと。

- 弊社出荷梱包単位（外装から取り出された内装及び個装）又は製品単品で取り扱いを行う場合は、接地された導電性のテーブル上で（導電性マットにアースをとったもの等）、アースをした作業者が行うこと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

- 前記のリストストラップ・導電性手袋・テーブル表面及び実装装置類の接地等の静電気帯電防止措置は、常に管理されその機能が確認されていること。

### 2. 溫・湿度環境

- 温度：0～40°C、相対湿度：40～85%で保管・輸送及び取り扱いを行うこと。（但し、結露しないこと。）

- 直射日光があたる状態で保管・輸送しないこと。

### 3. 防湿梱包

- 防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装すること。

### 4. 機械的衝撃

- 梱包品（外装、内装、個装）及び製品単品を落下させたり、衝撃を与えないこと。

### 5. 熱衝撃

- はんだ付け時は、最低限260°C以上の高温状態に、10秒以上さらさないこと。（個別推奨条件がある時はそれに従うこと。）

### 6. 汚染

- はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質（硫黄、塩素等ハロゲン）のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。（不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。）

以上