# ADS5474-SP、Class V、14 ビット、400MSPS、アナログ デジタル コンバータ

## 1 特長

- サンプル レート 400MSPS

- 14 ビット分解能、10.9 ビットの有効ビット数 (ENOB)

- 5962R13208:

- 放射線耐性保証 (RHA): TID 最大 100krad (Si)

- 吸収線量: 100krad (Si)

- ELDRS フリー: 100krad (Si)

- SEL/SEU 特性評価済み

- 入力帯域幅: 1.28GHz

- 230MHz および 400MSPS での SFDR = 78dBc

- 230MHz および 400MSPS での SNR = 69.8dBFS

- 差動入力電圧: 2.2V<sub>PP</sub>

- LVDS 互換出力

- 全消費電力: 2.5W

- パワーダウン モード: 50mW

- オフセット バイナリ出力フォーマット

- 出力データは、ハーフレート出力クロックの立ち上がりエッジおよび立ち下がりエッジで遷移します

- オンチップ アナログ バッファ、トラック アンド ホールド、基準回路

- 84 ピンのセラミック非導電性タイバー パッケージ (HFG) で供給されます

- 軍用温度範囲: -55°C ~ 125°C T<sub>case</sub>

- エンジニアリング評価 (IEM) サンプルが利用可能です。<sup>1</sup>

- 12 ビットおよび 14 ビットのファミリとピン類似および互換性: [ADS5463-SP](#) および [ADS5444-SP](#)

## 2 アプリケーション

- テストおよび計測機器

- ソフトウェア無線

- データ アクイジション

- パワー アンプ 直線化

- 通信機器

- レーダー

## 3 説明

ADS5474 は、14 ビット、400MSPS の A/D コンバータ (ADC) で、5V 電源と 3.3V 電源の両方で動作し、LVDS 互換のデジタル出力を供給します。この ADC は、210MSPS ~ 500MSPS で動作する 12、13、14 ビット ADC ファミリの 1 つです。ADS5474 の入力バッファにより、高インピーダンスの入力を実現し、またオンチップのトラック アンド ホールドの内部スイッチングを分離し、信号ソースからの干渉を防止します。システム設計を簡略化するため、基準電圧ジェネレータも提供されています。

ADS5474 は、400MSPS の入力周波数の 400MHz を超える広帯域信号の変換用に 1.4GHz の入力帯域幅を持つよう設計されており、広い入力周波数範囲にわたって優れた低ノイズ特性とスプリアスフリー ダイナミック範囲を実現します。

ADS5474 は、84 ピンのセラミック非導電性タイバー パッケージ (HFG) で供給されます。デバイスはテキサス インスツルメンツの相補型バイポーラプロセス (BiCom3) に基づいて製造され、軍用温度範囲全体 (-55°C ~ 125°C T<sub>case</sub>) で動作が規定されています。

## パッケージ情報

| 部品番号       | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|------------|----------------------|--------------------------|

| ADS5474-SP | CFP (HFG, 84)        | 19.05mm × 19.05mm        |

(1) 供給されているすべてのパッケージについては、[セクション 10](#) を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピッチも含まれます。

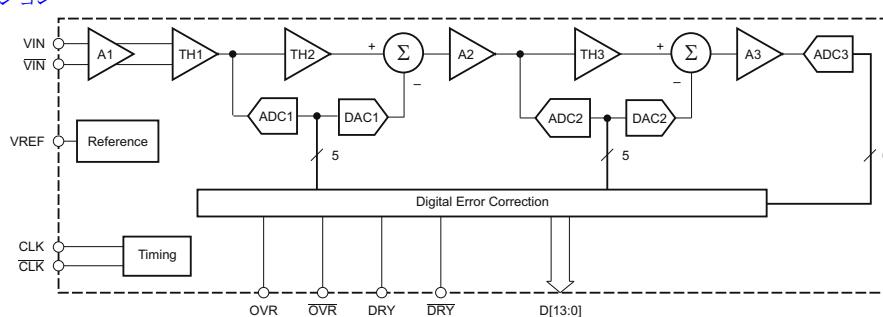

概略回路図

<sup>1</sup> これらのユニットは、エンジニアリング評価のみを目的としています。標準とは異なるフロー (バーンインがないなど) に従って処理され、25°C の温度定格のみがテストされています。これらのユニットは、認定、量産、放射線テスト、航空での使用には適していません。部品は、MIL に規定されている温度範囲全体 (-55°C ~ 125°C) にわたる性能も動作寿命全体にわたる性能も保証されていません。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあります。TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|             |    |                        |    |

|-------------|----|------------------------|----|

| 1 特長        | 1  | 6.1 概要                 | 16 |

| 2 アプリケーション  | 1  | 7 アプリケーションと実装          | 23 |

| 3 説明        | 1  | 7.1 電源に関する推奨事項         | 23 |

| 4 ピン構成および機能 | 3  | 8 デバイスおよびドキュメントのサポート   | 25 |

| 5 仕様        | 5  | 8.1 デバイスサポート           | 25 |

| 5.1 絶対最大定格  | 5  | 8.2 ドキュメントのサポート        | 26 |

| 5.2 ESD 定格  | 5  | 8.3 ドキュメントの更新通知を受け取る方法 | 26 |

| 5.3 推奨動作条件  | 5  | 8.4 サポート・リソース          | 26 |

| 5.4 熱に関する情報 | 6  | 8.5 商標                 | 26 |

| 5.5 電気的特性   | 6  | 8.6 静電気放電に関する注意事項      | 27 |

| 5.6 タイミング特性 | 10 | 8.7 用語集                | 27 |

| 5.7 代表的特性   | 11 | 9 改訂履歴                 | 27 |

| 6 詳細説明      | 16 | 10 メカニカル、パッケージ、および注文情報 | 27 |

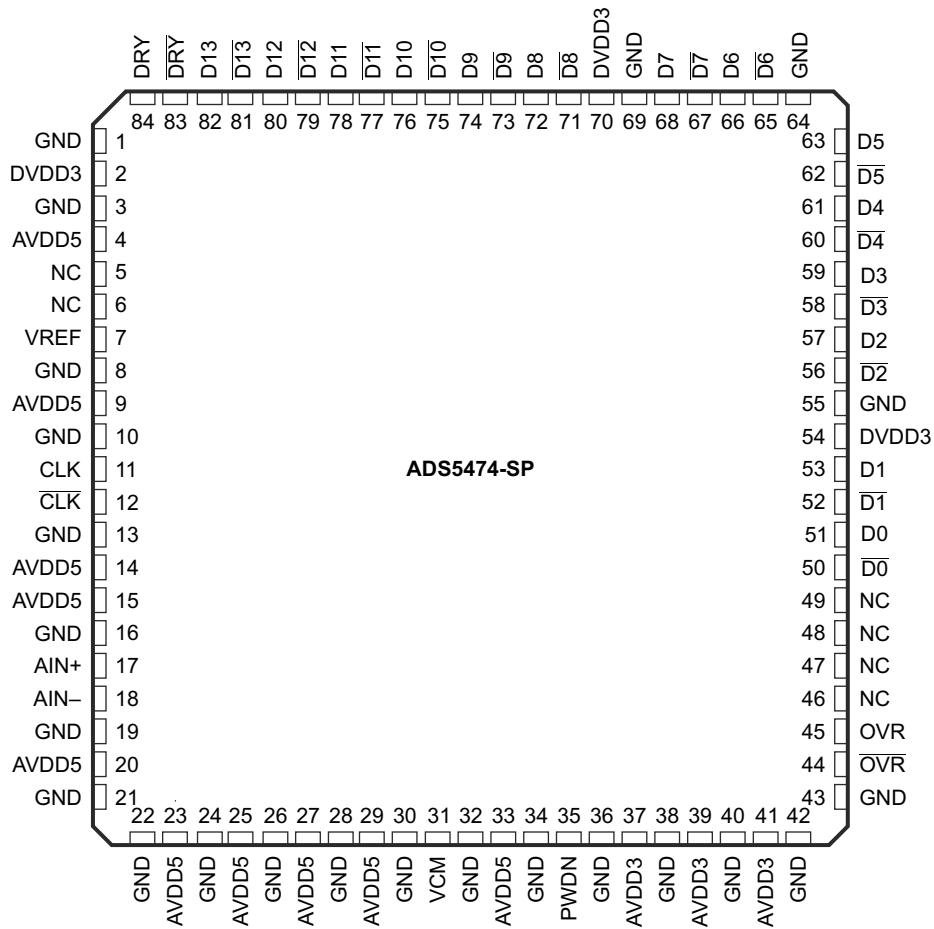

## 4 ピン構成および機能

図 4-1. HFG パッケージ、84 ピン CFP (上面図)

表 4-1. ピンの機能

| ピン                           |                                      | タイプ <sup>(1)</sup> | 説明                                   |

|------------------------------|--------------------------------------|--------------------|--------------------------------------|

| 名称                           | 番号                                   |                    |                                      |

| AIN                          | 17                                   | I                  | 差動入力信号 (ポジティブ)                       |

| AIN                          | 18                                   | I                  | 差動入力信号 (ネガティブ)                       |

| AVDD3                        | 37, 39, 41                           | P                  | アナログ電源 (3.3V)                        |

| AVDD5                        | 4, 9, 14, 15, 20, 23, 25, 27, 29, 33 | P                  | アナログ電源 (5V)                          |

| CLK                          | 11                                   | I                  | 差動入力クロック (ポジティブ)。変換は立ち上がりエッジで開始されます。 |

| CLK                          | 12                                   | I                  | 差動入力クロック (ネガティブ)                     |

| D0, D0                       | 50, 51                               | O                  | LVDS デジタル出力ペア、最下位ビット (LSB)           |

| D1, D1, D2-D5, D6-D7, D8-D12 | 52, 53, 56-63, 65-68, 71-82          | O                  | LVDS デジタル出力ペア                        |

| D13, D13                     | 81, 82                               | O                  | LVDS デジタル出力ペア、最上位ビット (MSB)           |

| DRY, DRY                     | 84, 83                               | O                  | データレディ LVDS 出力ペア                     |

| DVDD3                        | 2, 54, 70                            | P                  | デジタルおよび出力ドライバ電源 (3.3V)               |

表 4-1. ピンの機能 (続き)

| ピン               |                                                                   | タイプ <sup>(1)</sup> | 説明                                                                                                                                                                                           |

|------------------|-------------------------------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称               | 番号                                                                |                    |                                                                                                                                                                                              |

| GND              | 1、3、8、10、13、16、19、21、22、24、26、28、30、32、34、36、38、40、42、43、55、64、69 | GND                | グランド                                                                                                                                                                                         |

| NC               | 5、6、46、47、48、49                                                   | 該当なし               | 無接続                                                                                                                                                                                          |

| OVR、 $\bar{OVR}$ | 45、44                                                             | O                  | オーバー レンジ インジケータ LVDS 出力。ロジック high は、フルスケール範囲を超える範囲でアナログ入力を信号として接続します。                                                                                                                        |

| PDWN             | 35                                                                | I                  | パワーダウン (アクティブ high)。PDWN ピンがロジック HIGH のとき、デバイスはスリープ モードになります。PDWN がロジック LOW (グラウンド) のとき、ADC コンバータはウェークアップします。<br>(このピンは <a href="#">ADS5463-SP</a> および <a href="#">ADS5444-SP</a> では使用しません。) |

| VCM              | 31                                                                | O                  | 同相電圧出力 (標準 3.1V)。入力信号を正しい同相電圧に設定するために、DC 結合アプリケーションで一般に使用されます。<br>(このピンは <a href="#">ADS5463-SP</a> および <a href="#">ADS5444-SP</a> では使用しません。)                                                |

| VREF             | 7                                                                 | I/O                | 入出力基準電圧 (公称 2.4V)                                                                                                                                                                            |

(1) I = 入力、O = 出力、GND = グランド、P = 電源、I/O = 双方向、N/A = 該当なし

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                      |                | 最小値  | 最大値         | 単位 |

|----------------------|----------------|------|-------------|----|

| 電源電圧                 | AVDD5 から GND へ |      | 6           | V  |

|                      | AVDD3 から GND へ |      | 5           | V  |

|                      | DVDD3 から GND へ |      | 5           | V  |

| アナログ入力から GND へ       |                | -0.3 | AVDD5 + 0.3 | V  |

| クロック入力から GND へ       |                | -0.3 | AVDD5 + 0.3 | V  |

| CLK から $\bar{CLK}$ へ |                | -2.5 | 2.5         | V  |

| GND へのデジタルデータ出力      |                | -0.3 | DVDD3 + 0.3 | V  |

| 動作時のケース温度 $T_C$      |                | -55  | 125         | °C |

| 最大接合部温度 $T_J$        |                |      | 150         | °C |

| 保存温度 $T_{stg}$       |                | -65  | 150         | °C |

- (1) 「絶対最大定格」外での操作は、デバイスに恒久的な損傷を引き起こす可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用した場合、本デバイスは完全に機能するとは限らず、このことが本デバイスの信頼性、機能、性能に影響を及ぼし、本デバイスの寿命を縮める可能性があります。

### 5.2 ESD 定格

|                  |                                                      | 値    | 単位 |

|------------------|------------------------------------------------------|------|----|

| $V_{(ESD)}$ 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup> | 2000 | V  |

- (1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

### 5.3 推奨動作条件

|                               |            | 最小値               | 公称値 | 最大値  | 単位       |

|-------------------------------|------------|-------------------|-----|------|----------|

| <b>供給電圧</b>                   |            |                   |     |      |          |

| AVDD5                         | アナログ電源電圧   | 4.75              | 5   | 5.25 | V        |

| AVDD3                         | アナログ電源電圧   | 3.1               | 3.3 | 3.6  | V        |

| DVDD3                         | 出力ドライバ電源電圧 | 3                 | 3.3 | 3.6  | V        |

| <b>アナログ入力</b>                 |            |                   |     |      |          |

| 差動入力範囲                        |            |                   | 2.2 |      | $V_{PP}$ |

| VCM                           | 入力同相モード    |                   | 3.1 |      | V        |

| <b>デジタル出力 (DRY、DATA、OVR)</b>  |            |                   |     |      |          |

| 最大差動出力負荷                      |            |                   | 10  |      | pF       |

| <b>クロック入力 (CLK)</b>           |            |                   |     |      |          |

| CLK 入力サンプルレート (正弦波)           |            | 20 <sup>(1)</sup> | 400 |      | MSPS     |

| クロック振幅、差動正弦波 <sup>(1)</sup>   |            | 0.5               | 5   |      | $V_{PP}$ |

| クロック デューティサイクル <sup>(1)</sup> |            | 40%               | 50% | 60%  |          |

| $T_C$                         | 動作ケース温度範囲  | -55               | 125 |      | °C       |

- (1) パラメータは特性評価によって保証されますが、出荷時のテストは行っていません。

## 5.4 热に関する情報

(1)

| 热評価基準           |                | テスト条件                  | 標準値   | 単位   |

|-----------------|----------------|------------------------|-------|------|

| $R_{\theta JA}$ | 接合部から周囲空気への热抵抗 | 接合部からケースへの热抵抗          | 21.81 |      |

| $R_{\theta JC}$ | 接合部からケースへの热抵抗  | MIL-STD-883 テスト方法 1012 | 0.849 | °C/W |

(1) この CQFP パッケージには、ダイの底面をパッケージの底面にあるパッドに電気的および热的に接続するビアが組み込まれています。热を効率的に除去し、低インピーダンスのグランドパスを提供するため、パッケージの本体の直下にある PCB 表面にサーマル ランドが必要です。通常の表面実装フローの半田付け操作では、パッケージの底面にあるヒート パッドをこのサーマル ランドに半田付けすることで、効率的な热パスを実現します。通常、PCB のサーマル ランドには多数のサーマル ビアがあり、内部の铜領域（または PCB の反対側）への热パスを提供し、より効率的に热を除去します。通常、TI は  $11.9\text{mm}^2$  基板実装のサーマル パッドを推奨します。これにより、放熱を可能にすると同時に、リードをパッドの領域から遠ざけることで、半田ブリッジを防ぐことができます。デバイスを推奨動作条件内に維持するには、十分な量のサーマル/電気ビアを用意する必要があります。このパッドは、グランド電位に電気的に接続する必要があります。

## 5.5 電気的特性

$T_C = 25^\circ\text{C}$  での標準値:特に記述のない限り、全温度範囲にわたって最小値および最大値  $T_{C,\text{MIN}} = -55^\circ\text{C} \sim T_{C,\text{MAX}} = 125^\circ\text{C}$ 、サンプリングレート = 400MSPS、50% クロック デューティ サイクル、AVDD5 = 5V、AVDD3 = 3.3V、DVDD3 = 3.3V、-1dBFS 差動入力、3V<sub>PP</sub> 差動クロック、特に記述のない限り。

| パラメータ                                       | テスト条件                                                                                        | 最小値   | 標準値   | 最大値 | 単位              |

|---------------------------------------------|----------------------------------------------------------------------------------------------|-------|-------|-----|-----------------|

| 分解能                                         |                                                                                              |       | 14    |     | ビット             |

| <b>アナログ入力</b>                               |                                                                                              |       |       |     |                 |

| 差動入力範囲                                      |                                                                                              | 2.2   |       |     | V <sub>PP</sub> |

| アナログ入力同相電圧                                  | 自己バイアス、以下の VCM 仕様を参照してください                                                                   | 3.1   |       |     | V               |

| 入力抵抗 (dc)                                   | 各入力から VCM へ                                                                                  | 500   |       |     | Ω               |

| 入力容量                                        | 各入力から GND へ                                                                                  | 2.8   |       |     | pF              |

| アナログ入力帯域幅 (-3dB)                            |                                                                                              | 1.28  |       |     | GHz             |

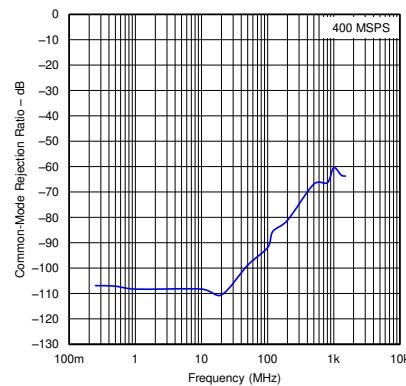

| CMRR 同相除去比                                  | 同相信号 < 50Mhz<br>(図 5-28 を参照)                                                                 | 100   |       |     | dB              |

| <b>内部リファレンス電圧</b>                           |                                                                                              |       |       |     |                 |

| VREF リファレンス電圧                               |                                                                                              | 2.4   |       |     | V               |

| VCM アナログ入力同相電圧リファレンス出力                      | 内部 VREF 搭載。DC 結合アプリケーションでは、VCM ピン経由で出力として供給されます。                                             | 2.9   | 3.1   | 3.3 | V               |

| VCM の温度係数                                   |                                                                                              | -0.8  |       |     | mV/°C           |

| <b>動的精度</b>                                 |                                                                                              |       |       |     |                 |

| ミッキング コードなし                                 |                                                                                              | 保証    |       |     |                 |

| DNL 微分直線性誤差                                 | $f_{\text{IN}} = 10\text{MHz}$                                                               | -0.99 | ±0.7  | 2.5 | LSB             |

| INL 積分直線性誤差                                 | $f_{\text{IN}} = 10\text{MHz}$                                                               | -7.0  | ±1.5  | 7.0 | LSB             |

| オフセット誤差                                     |                                                                                              | -16   |       | 16  | mV              |

| オフセット温度係数                                   |                                                                                              | 0.02  |       |     | mV/°C           |

| ゲイン誤差                                       |                                                                                              | -5    |       | 5   | %FS             |

| ゲイン温度係数                                     |                                                                                              | -0.02 |       |     | %FS/°C          |

| <b>電源</b>                                   |                                                                                              |       |       |     |                 |

| $I_{\text{AVDD5}}$ 5V アナログ電源電圧              | $V_{\text{IN}} = \text{フルスケール}, f_{\text{IN}} = 70\text{MHz}, f_{\text{S}} = 400\text{MSPS}$ | 338   | 380   |     | mA              |

| $I_{\text{AVDD3}}$ 3.3V アナログ電源電圧            |                                                                                              | 185   | 210   |     | mA              |

| $I_{\text{DVDD3}}$ 3.3V デジタル電源電流 (LVDS を含む) |                                                                                              | 75    | 85    |     | mA              |

| 全消費電力                                       |                                                                                              | 2.5   | 2.835 |     | W               |

## 5.5 電気的特性 (続き)

$T_C = 25^\circ\text{C}$  での標準値: 特に記述のない限り、全温度範囲にわたって最小値および最大値  $T_{C,\text{MIN}} = -55^\circ\text{C} \sim T_{C,\text{MAX}} = 125^\circ\text{C}$ 、サンプリングレート = 400MSPS、50% クロック デューティ サイクル、AVDD5 = 5V、AVDD3 = 3.3V、DVDD3 = 3.3V、-1dBFS 差動入力、3V<sub>PP</sub> 差動クロック、特に記述のない限り。

| パラメータ                    | テスト条件                                                         | 最小値                                              | 標準値  | 最大値 | 単位            |

|--------------------------|---------------------------------------------------------------|--------------------------------------------------|------|-----|---------------|

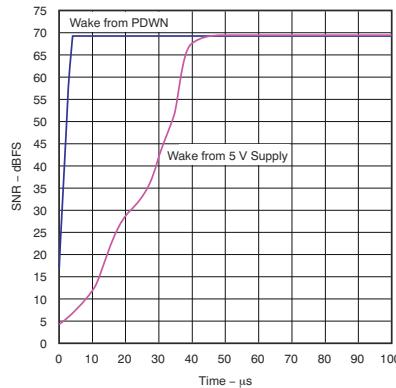

| パワーアップ時間                 | AVDD5 のターンオンから                                                |                                                  | 50   |     | $\mu\text{s}$ |

| ウェークアップ時間                | PDWN ピンを HIGH (PDWN アクティブ) から LOW (ADC 起動) に切り替え (図 5-29 を参照) |                                                  | 5    |     | $\mu\text{s}$ |

| パワーダウン消費電力               | PDWN ピン = ロジック HIGH                                           | 50                                               | 350  |     | mW            |

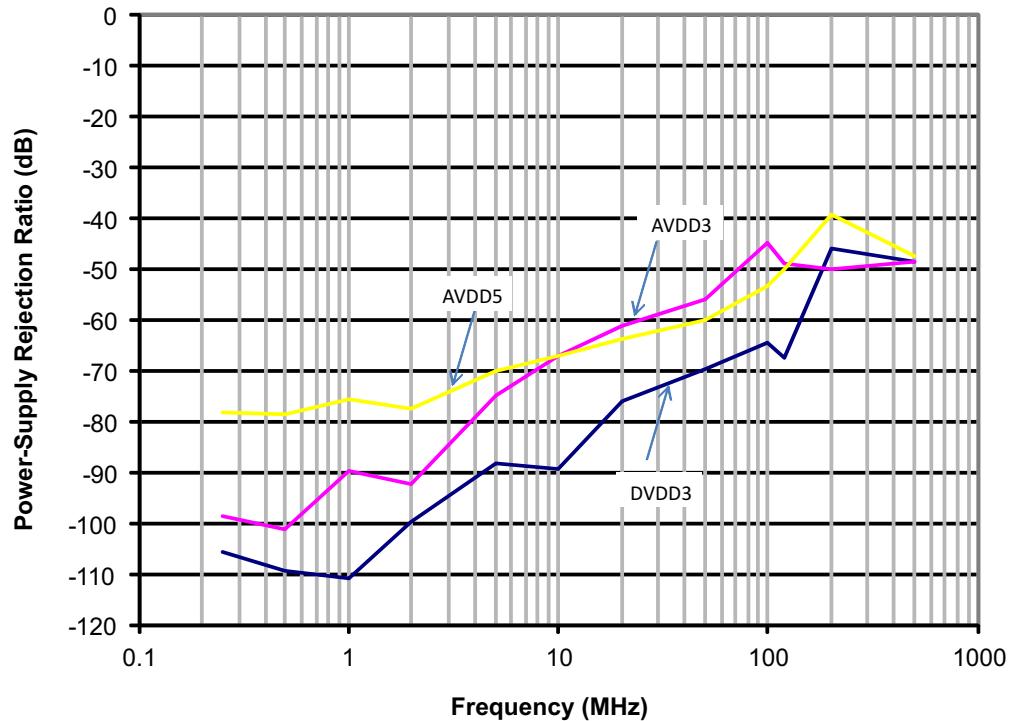

| PSRR                     | 電源電圧変動除去比、AVDD5 電源                                            |                                                  | 75   |     | dB            |

| PSRR                     | 電源電圧変動除去比、AVDD3 電源                                            | 0.1 $\mu\text{F}$ 基板の電源コンデンサなしで、1MHz 未満の電源ノイズを実現 | 90   |     | dB            |

| PSRR                     | 電源電圧変動除去比、DVDD3 電源                                            |                                                  | 110  |     | dB            |

| <b>動的 AC 特性</b>          |                                                               |                                                  |      |     |               |

| SNR 信号対雑音比               | $f_{\text{IN}} = 30\text{MHz}$                                | 70.5                                             |      |     | dBFS          |

|                          | $f_{\text{IN}} = 70\text{MHz}$                                | 65                                               | 68.7 |     |               |

|                          | $f_{\text{IN}} = 130\text{MHz}$                               |                                                  | 69.9 |     |               |

|                          | $f_{\text{IN}} = 230\text{MHz}$                               | 65                                               | 69.8 |     |               |

|                          | $f_{\text{IN}} = 351\text{MHz}$                               |                                                  | 69.2 |     |               |

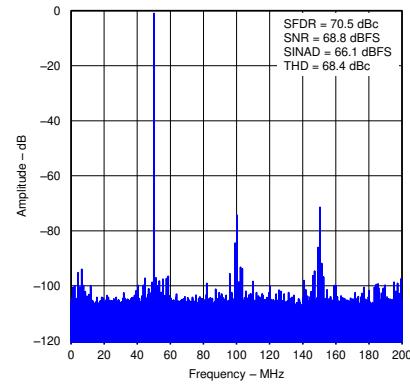

|                          | $f_{\text{IN}} = 451\text{MHz}$                               |                                                  | 68.8 |     |               |

|                          | $f_{\text{IN}} = 651\text{MHz}$                               |                                                  | 67.3 |     |               |

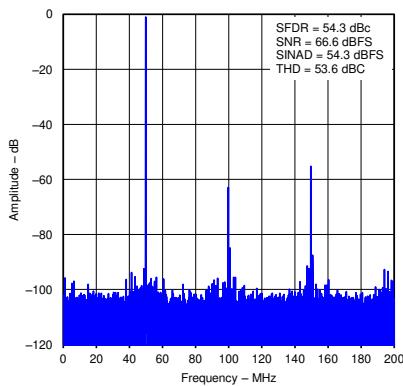

|                          | $f_{\text{IN}} = 751\text{MHz}$                               |                                                  | 66.6 |     |               |

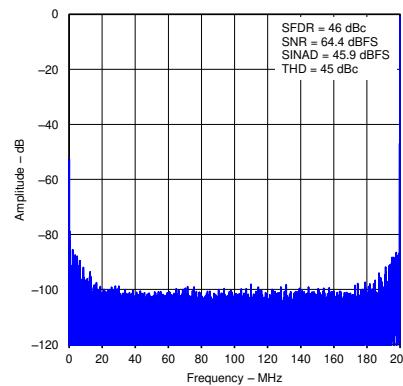

|                          | $f_{\text{IN}} = 999\text{MHz}$                               |                                                  | 64.4 |     |               |

| SFDR スプリアスフリー ダイナミック レンジ | $f_{\text{IN}} = 30\text{MHz}$                                | 79.4                                             |      |     | dBc           |

|                          | $f_{\text{IN}} = 70\text{MHz}$                                | 69                                               | 76.3 |     |               |

|                          | $f_{\text{IN}} = 130\text{MHz}$                               |                                                  | 78.8 |     |               |

|                          | $f_{\text{IN}} = 230\text{MHz}$                               | 64.5                                             | 78   |     |               |

|                          | $f_{\text{IN}} = 351\text{MHz}$                               |                                                  | 74.3 |     |               |

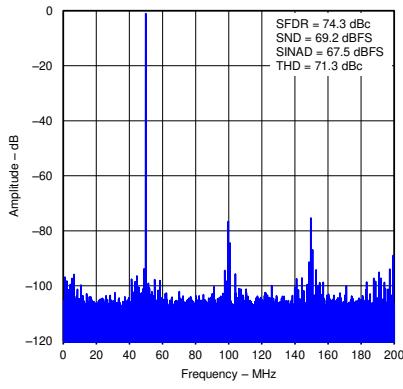

|                          | $f_{\text{IN}} = 451\text{MHz}$                               |                                                  | 70.5 |     |               |

|                          | $f_{\text{IN}} = 651\text{MHz}$                               |                                                  | 58.6 |     |               |

|                          | $f_{\text{IN}} = 751\text{MHz}$                               |                                                  | 54.3 |     |               |

|                          | $f_{\text{IN}} = 999\text{MHz}$                               |                                                  | 46   |     |               |

| HD2 2 次高調波               | $f_{\text{IN}} = 30\text{MHz}$                                | 92                                               |      |     | dBc           |

|                          | $f_{\text{IN}} = 70\text{MHz}$                                | 87                                               |      |     |               |

|                          | $f_{\text{IN}} = 130\text{MHz}$                               | 87                                               |      |     |               |

|                          | $f_{\text{IN}} = 230\text{MHz}$                               | 84                                               |      |     |               |

|                          | $f_{\text{IN}} = 351\text{MHz}$                               | 77                                               |      |     |               |

|                          | $f_{\text{IN}} = 451\text{MHz}$                               | 75                                               |      |     |               |

|                          | $f_{\text{IN}} = 651\text{MHz}$                               | 68                                               |      |     |               |

|                          | $f_{\text{IN}} = 751\text{MHz}$                               | 64                                               |      |     |               |

|                          | $f_{\text{IN}} = 999\text{MHz}$                               | 53                                               |      |     |               |

## 5.5 電気的特性 (続き)

$T_C = 25^\circ\text{C}$  での標準値: 特に記述のない限り、全温度範囲にわたって最小値および最大値  $T_{C,\text{MIN}} = -55^\circ\text{C} \sim T_{C,\text{MAX}} = 125^\circ\text{C}$ 、サンプリングレート = 400MSPS、50% クロック デューティ サイクル、AVDD5 = 5V、AVDD3 = 3.3V、DVDD3 = 3.3V、-1dBFS 差動入力、3V<sub>PP</sub> 差動クロック、特に記述のない限り。

| パラメータ                          |            | テスト条件                           | 最小値  | 標準値  | 最大値 | 単位  |

|--------------------------------|------------|---------------------------------|------|------|-----|-----|

| HD3                            | 3 次高調波     | $f_{\text{IN}} = 30\text{MHz}$  |      | 81   |     | dBc |

|                                |            | $f_{\text{IN}} = 70\text{MHz}$  |      | 86   |     |     |

|                                |            | $f_{\text{IN}} = 130\text{MHz}$ |      | 80   |     |     |

|                                |            | $f_{\text{IN}} = 230\text{MHz}$ |      | 80   |     |     |

|                                |            | $f_{\text{IN}} = 351\text{MHz}$ |      | 76   |     |     |

|                                |            | $f_{\text{IN}} = 451\text{MHz}$ |      | 72   |     |     |

|                                |            | $f_{\text{IN}} = 651\text{MHz}$ |      | 60   |     |     |

|                                |            | $f_{\text{IN}} = 751\text{MHz}$ |      | 56   |     |     |

|                                |            | $f_{\text{IN}} = 999\text{MHz}$ |      | 48   |     |     |

| 最大高調波/スプリアス<br>(HD2 と HD3 を除く) |            | $f_{\text{IN}} = 30\text{MHz}$  |      | 93   |     | dBc |

|                                |            | $f_{\text{IN}} = 70\text{MHz}$  |      | 91   |     |     |

|                                |            | $f_{\text{IN}} = 130\text{MHz}$ |      | 91   |     |     |

|                                |            | $f_{\text{IN}} = 230\text{MHz}$ |      | 88   |     |     |

|                                |            | $f_{\text{IN}} = 351\text{MHz}$ |      | 87   |     |     |

|                                |            | $f_{\text{IN}} = 451\text{MHz}$ |      | 87   |     |     |

|                                |            | $f_{\text{IN}} = 651\text{MHz}$ |      | 91   |     |     |

|                                |            | $f_{\text{IN}} = 751\text{MHz}$ |      | 87   |     |     |

|                                |            | $f_{\text{IN}} = 999\text{MHz}$ |      | 80   |     |     |

| THD                            | 全高調波歪      | $f_{\text{IN}} = 30\text{MHz}$  |      | 77   |     | dBc |

|                                |            | $f_{\text{IN}} = 70\text{MHz}$  |      | 73.5 |     |     |

|                                |            | $f_{\text{IN}} = 130\text{MHz}$ |      | 74.9 |     |     |

|                                |            | $f_{\text{IN}} = 230\text{MHz}$ |      | 74.9 |     |     |

|                                |            | $f_{\text{IN}} = 351\text{MHz}$ |      | 71.3 |     |     |

|                                |            | $f_{\text{IN}} = 451\text{MHz}$ |      | 68.4 |     |     |

|                                |            | $f_{\text{IN}} = 651\text{MHz}$ |      | 57.8 |     |     |

|                                |            | $f_{\text{IN}} = 751\text{MHz}$ |      | 53.6 |     |     |

|                                |            | $f_{\text{IN}} = 999\text{MHz}$ |      | 45   |     |     |

| SINAD                          | 信号対ノイズ + 歪 | $f_{\text{IN}} = 30\text{MHz}$  |      | 69.8 |     | dBc |

|                                |            | $f_{\text{IN}} = 70\text{MHz}$  | 62.5 | 67.7 |     |     |

|                                |            | $f_{\text{IN}} = 130\text{MHz}$ |      | 68.9 |     |     |

|                                |            | $f_{\text{IN}} = 230\text{MHz}$ | 60.5 | 68.9 |     |     |

|                                |            | $f_{\text{IN}} = 351\text{MHz}$ |      | 67.5 |     |     |

|                                |            | $f_{\text{IN}} = 451\text{MHz}$ |      | 66.1 |     |     |

|                                |            | $f_{\text{IN}} = 651\text{MHz}$ |      | 58.2 |     |     |

|                                |            | $f_{\text{IN}} = 751\text{MHz}$ |      | 54.3 |     |     |

|                                |            | $f_{\text{IN}} = 999\text{MHz}$ |      | 45.9 |     |     |

## 5.5 電気的特性 (続き)

$T_C = 25^\circ\text{C}$  での標準値: 特に記述のない限り、全温度範囲にわたって最小値および最大値  $T_{C,\text{MIN}} = -55^\circ\text{C} \sim T_{C,\text{MAX}} = 125^\circ\text{C}$ 、サンプリングレート = 400MSPS、50% クロック デューティ サイクル、AVDD5 = 5V、AVDD3 = 3.3V、DVDD3 = 3.3V、-1dBFS 差動入力、3V<sub>PP</sub> 差動クロック、特に記述のない限り。

| パラメータ                            | テスト条件                                                                                         | 最小値   | 標準値   | 最大値 | 単位            |

|----------------------------------|-----------------------------------------------------------------------------------------------|-------|-------|-----|---------------|

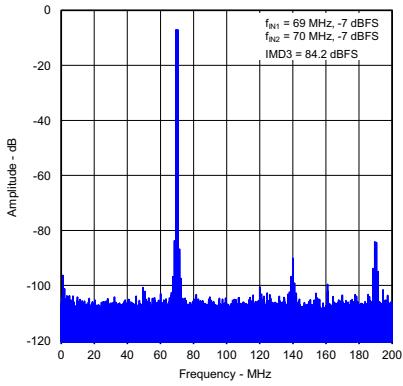

| ツートーン SFDR                       | $f_{\text{IN}1} = 69\text{MHz}$ , $f_{\text{IN}2} = 70\text{MHz}$ ,<br>各トーンは -7dBFS です        | 84.2  |       |     | dBFS          |

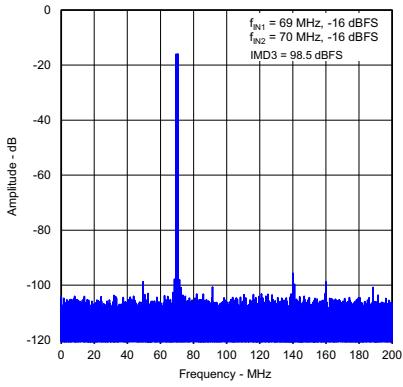

|                                  | $f_{\text{IN}1} = 69\text{MHz}$ , $f_{\text{IN}2} = 70\text{MHz}$ ,<br>各トーンは -16dBFS です       | 98.5  |       |     |               |

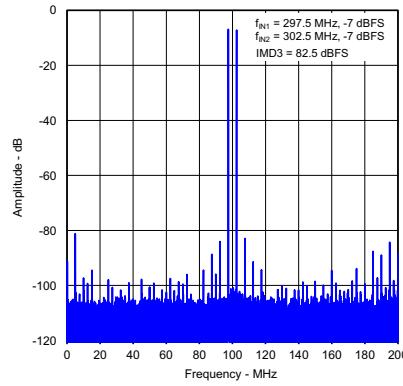

|                                  | $f_{\text{IN}1} = 297.5\text{MHz}$ , $f_{\text{IN}2} = 302.5\text{MHz}$ ,<br>各トーンは -7dBFS です  | 82.5  |       |     |               |

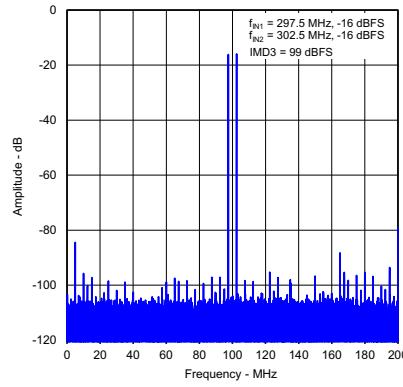

|                                  | $f_{\text{IN}1} = 297.5\text{MHz}$ , $f_{\text{IN}2} = 302.5\text{MHz}$ ,<br>各トーンは -16dBFS です | 99    |       |     |               |

| ENOB 有効ビット数                      | $f_{\text{IN}} = 70\text{MHz}$                                                                | 10.1  | 10.9  |     | ビット           |

|                                  | $f_{\text{IN}} = 230\text{MHz}$                                                               | 9.77  | 10.5  |     |               |

| RMS アイドル チャネル ノイズ                | 同相モードに接続された入力                                                                                 | 1.8   |       |     | LSB           |

| <b>LVDS デジタル出力</b>               |                                                                                               |       |       |     |               |

| $V_{\text{OD}}$ 差動出力電圧 ( $\pm$ ) |                                                                                               | 247   | 350   | 454 | mV            |

| $V_{\text{OC}}$ 同相出力電圧           |                                                                                               | 1.115 | 1.375 |     | V             |

| <b>デジタル入力</b>                    |                                                                                               |       |       |     |               |

| $V_{\text{IH}}$ High レベル入力電圧     | PWD (ピン 33)                                                                                   | 2.0   |       |     | V             |

| $V_{\text{IL}}$ Low レベル入力電圧      |                                                                                               | 0.8   |       |     | V             |

| $I_{\text{IH}}$ High レベル入力電流     |                                                                                               | 1     |       |     | $\mu\text{A}$ |

| $I_{\text{IL}}$ Low レベル入力電流      |                                                                                               | -1    |       |     | $\mu\text{A}$ |

| $C_{\text{IN}}$ 入力容量             |                                                                                               | 2.2   |       |     | pF            |

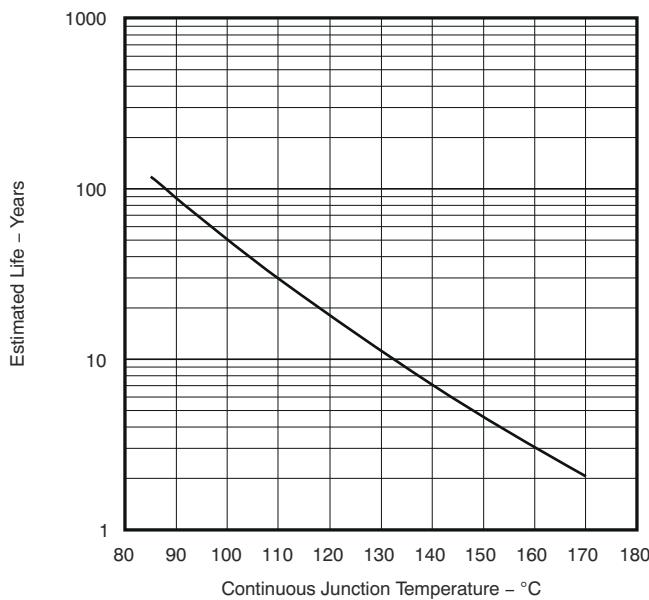

図 5-1. 動作寿命ディレーティング チャート、エレクトロマイグレーション フェイル モード

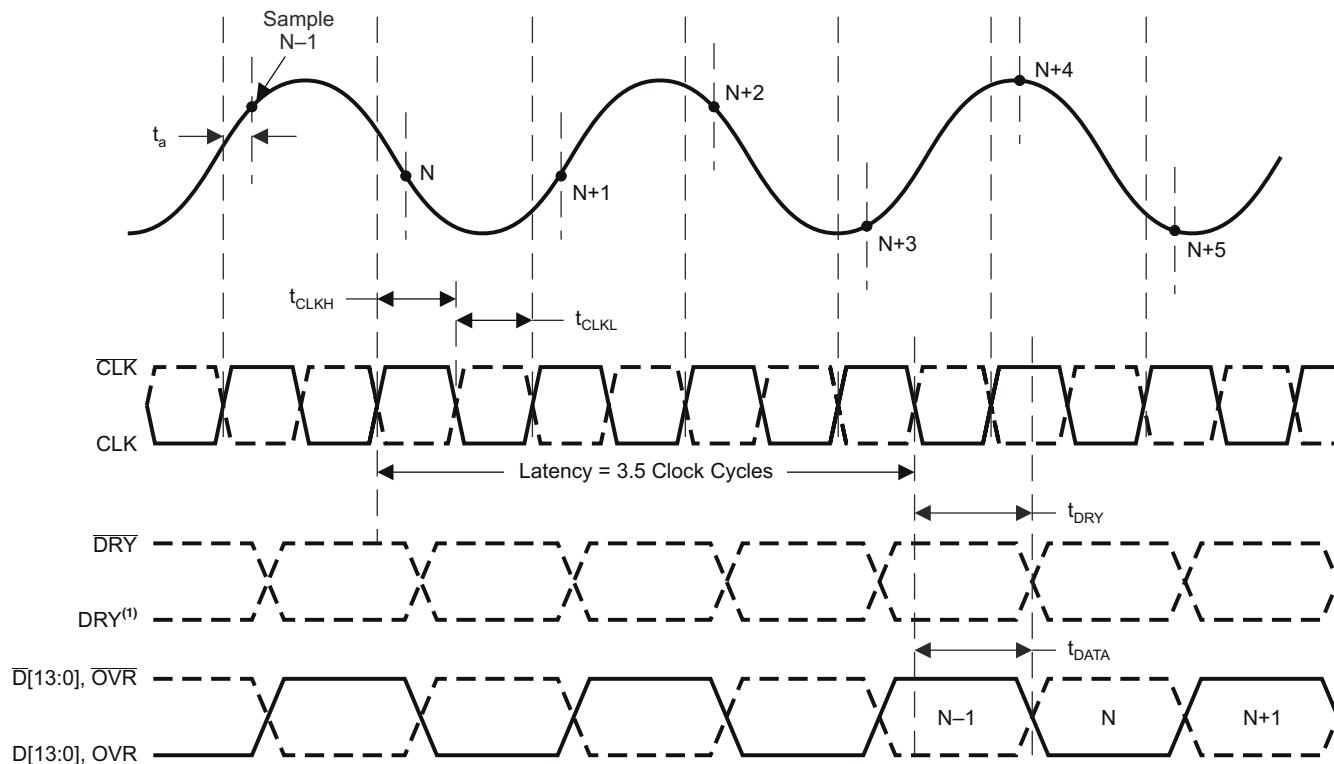

## 5.6 タイミング特性

$T_C = 25^\circ\text{C}$  での標準値: 特に記述のない限り、全温度範囲にわたる最小値および最大値、 $T_{C,\text{MIN}} = -55^\circ\text{C} \sim T_{C,\text{MAX}} = 125^\circ\text{C}$ 、サンプリングレート = 400MSPS、50% クロック デューティ サイクル、AVDD5 = 5V、AVDD3 = 3.3V、DVDD3 = 3.3V、3V<sub>PP</sub> 差動クロック、特に記述のない限り。

| パラメータ (1)                                 | テスト条件                                                        | 最小値  | 標準値  | 最大値  | 単位   |

|-------------------------------------------|--------------------------------------------------------------|------|------|------|------|

| $t_a$ アペーチャの遅延                            |                                                              |      | 200  |      | ps   |

| アペーチャ ジッタ、rms                             | ADC の内部ジッタ                                                   |      | 103  |      | fs   |

| レイテンシ                                     |                                                              |      | 3.5  |      | サイクル |

| $t_{\text{CLK}}$ クロック周期                   |                                                              | 2.5  | 50   |      | ns   |

| $t_{\text{CLKH}}$ クロック バルス持続時間 high       |                                                              | 1    |      |      | ns   |

| $t_{\text{CLKL}}$ クロック バルス持続時間 low        |                                                              | 1    |      |      | ns   |

| $t_{\text{DRY}}$ CLK から DRY への遅延(2)       | ゼロクロス、各出力ピンの GND に対する 10pF の寄生負荷                             | 700  | 1600 | 2500 | ps   |

| $t_{\text{DATA}}$ CLK から DATA/OVR への遅延(2) | ゼロクロス、各出力ピンの GND に対する 10pF の寄生負荷                             | 650  | 1600 | 2600 | ps   |

| $t_{\text{SKEW}}$ DATA から DRY キューへ        | $t_{\text{DATA}} - t_{\text{DRY}}$ 、各出力ピンの GND への 10pF の寄生負荷 | -700 | 0    | 700  | ps   |

| $t_{\text{RISE}}$ DRY/DATA/OVR 立ち上がり時間    | 各出力ピンで GND への寄生負荷は 10pF                                      |      | 500  |      | ps   |

| $t_{\text{FALL}}$ DRY/DATA/OVR 立ち下がり時間    | 各出力ピンで GND への寄生負荷は 10pF                                      |      | 500  |      | ps   |

(1) タイミング パラメータは特性評価によって保証されますが、出荷時のテストは行っていません。

(2) DRY、DATA、OVR は、CLK の立ち下がりエッジで更新されます。全体の伝搬遅延を決定するには、レイテンシを  $t_{\text{DATA}}$  に追加する必要があります。

A. DRY の極性は不定です。詳細については、[セクション 6.1.3](#) を参照してください。

図 5-2. タイミング図

## 5.7 代表的特性

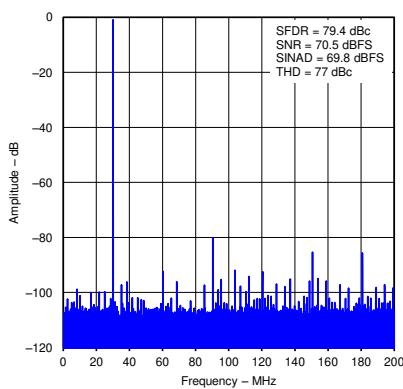

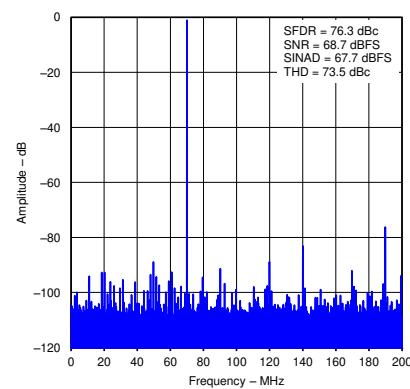

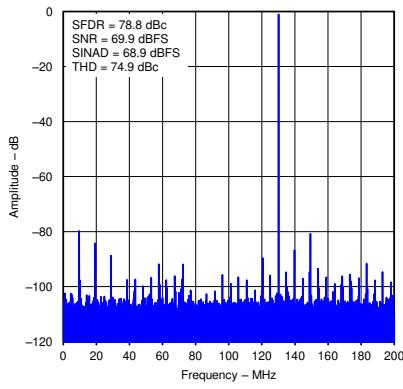

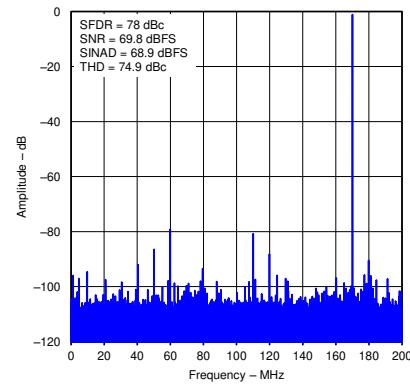

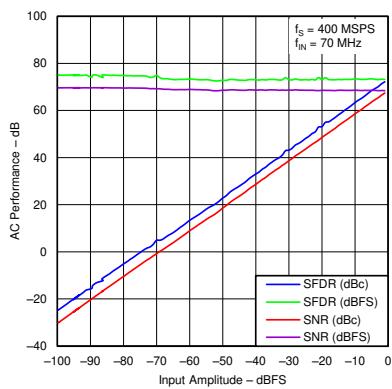

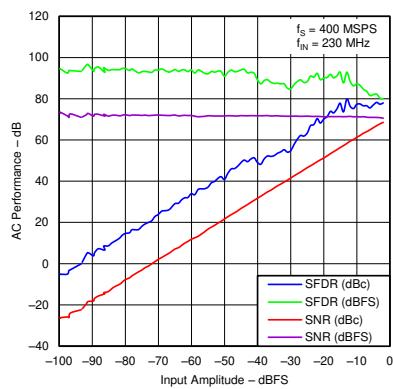

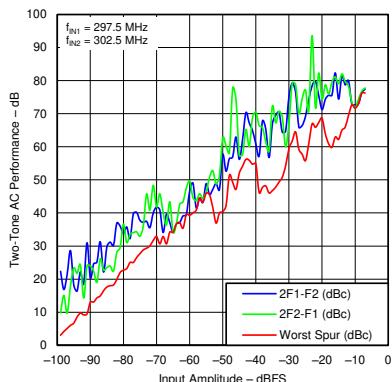

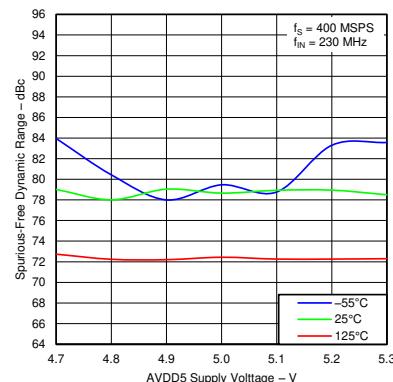

$T_A = 25^\circ\text{C}$ 、サンプリングレート = 400MSPS、50% クロック デューティ サイクル、 $3V_{\text{PP}}$  差動正弦波クロック、アナログ入力振幅 =  $-1\text{dBFS}$ 、AVDD5 = 5V、AVDD3 = 3.3V、DVDD3 = 3.3V の場合、特に記述のない限り。

図 5-3. 30MHz 入力信号のスペクトル性能 FFT

図 5-4. 70MHz 入力信号のスペクトル性能 FFT

図 5-5. 130MHz 入力信号のスペクトル性能 FFT

図 5-6. 230MHz 入力信号のスペクトル性能 FFT

図 5-7. 351MHz 入力信号のスペクトル性能 FFT

図 5-8. 451MHz 入力信号のスペクトル性能 FFT

## 5.7 代表的特性 (続き)

$T_A = 25^\circ\text{C}$ 、サンプリングレート = 400MSPS、50% クロック デューティ サイクル、3V<sub>PP</sub> 差動正弦波クロック、アナログ入力振幅 = -1dBFS、AVDD5 = 5V、AVDD3 = 3.3V、DVDD3 = 3.3V の場合、特に記述のない限り。

図 5-9. 751MHz 入力信号のスペクトル性能 FFT

図 5-10. 999MHz 入力信号のスペクトル性能 FFT

図 5-11. ツートーン相互変調歪み (-7dBFS での 69MHz と 70MHz の FFT)

図 5-12. ツートーン相互変調歪み (-7dBFS での 297.5MHz と 302.5MHz の FFT)

図 5-13. ツートーン相互変調歪み (-16dBFS での 69MHz と 70MHz の FFT)

図 5-14. ツートーン相互変調歪み (-16dBFS での 297.5MHz と 302.5MHz の FFT)

## 5.7 代表的特性 (続き)

$T_A = 25^\circ\text{C}$ 、サンプリングレート = 400MSPS、50% クロック デューティ サイクル、 $3V_{\text{PP}}$  差動正弦波クロック、アナログ入力振幅 =  $-1\text{dBFS}$ 、AVDD5 = 5V、AVDD3 = 3.3V、DVDD3 = 3.3V の場合、特に記述のない限り。

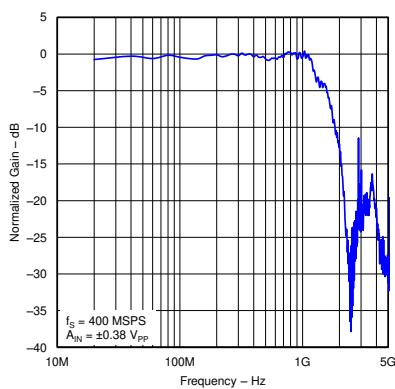

図 5-15. 正規化ゲイン応答と入力周波数との関係

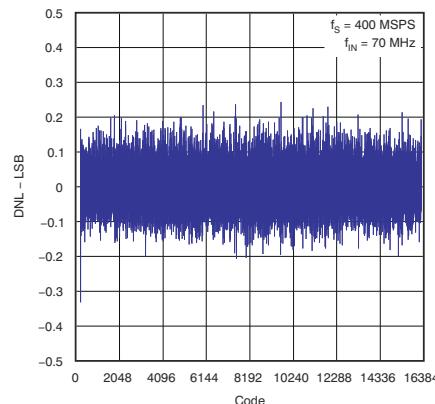

図 5-16. 微分非直線性

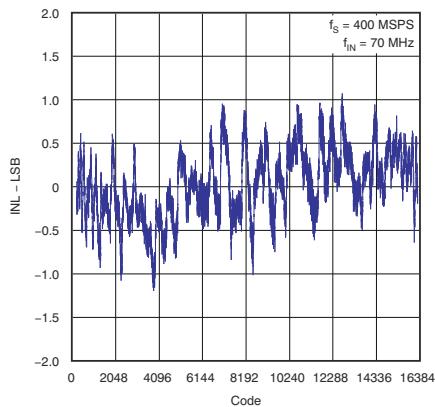

図 5-17. 積分非直線性

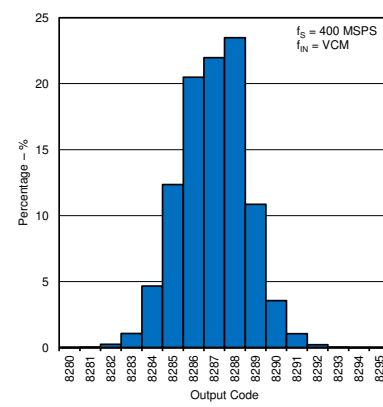

図 5-18. 入力短絡によるノイズヒストグラム

図 5-19. AC 性能と入力振幅との関係 (70MHz 入力信号)

図 5-20. AC 性能と入力振幅との関係 (230MHz 入力信号)

## 5.7 代表的特性 (続き)

$T_A = 25^\circ\text{C}$ 、サンプリングレート = 400MSPS、50% クロック デューティ サイクル、 $3V_{\text{PP}}$  差動正弦波クロック、アナログ入力振幅 =  $-1\text{dBFS}$ 、AVDD5 = 5V、AVDD3 = 3.3V、DVDD3 = 3.3V の場合、特に記述のない限り。

図 5-21. ツー トーン性能と入力振幅との関係 ( $F1 = 297.5\text{MHz}$  および  $F2 = 302.5\text{MHz}$ )

図 5-22. SFDR と AVDD5 との関係 過熱

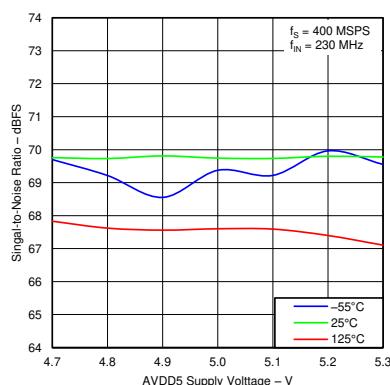

図 5-23. SNR と AVDD5 との関係 過熱

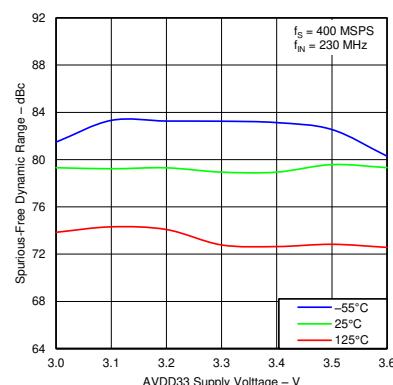

図 5-24. SFDR と AVDD33 との関係 過熱

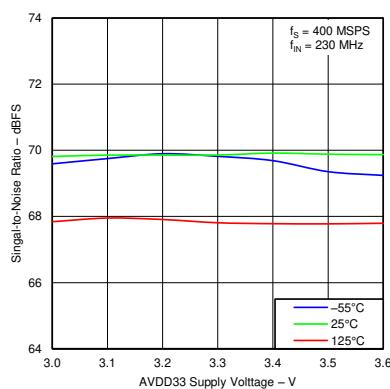

図 5-25. SNR と AVDD33 との関係 過熱

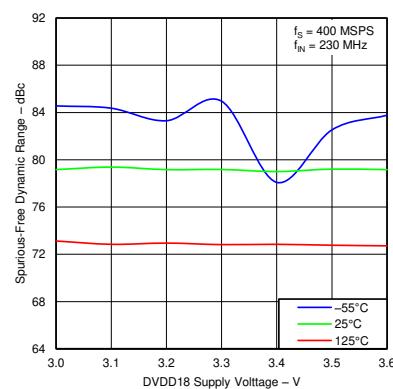

図 5-26. SFDR と DVDD18 との関係 過熱

## 5.7 代表的特性 (続き)

$T_A = 25^\circ\text{C}$ 、サンプリングレート = 400MSPS、50% クロック デューティ サイクル、 $3V_{\text{PP}}$  差動正弦波クロック、アナログ入力振幅 =  $-1\text{dBFS}$ 、AVDD5 = 5V、AVDD3 = 3.3V、DVDD3 = 3.3V の場合、特に記述のない限り。

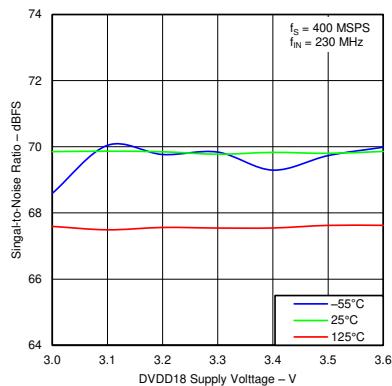

図 5-27. SNR と DVDD18 との関係 過熱

図 5-28. CMRR と同相入力周波数との関係

図 5-29. ADC ウェークアップ時間

## 6 詳細説明

### 6.1 概要

ADS5474 は 14 ビット、400MSPS、モノリシック パイプライン ADC です。バイポーラ アナログ コアは 5V および 3.3V 電源で動作し、出力は 3.3V 電源を使用して LVDS 互換の出力を提供します。外部入力クロックの立ち上がりエッジにより、変換プロセスが開始されます。変換プロセスの直後に、差動入力信号は入力トラック アンド ホールド (T&H) によってキャプチャされ、入力サンプルは一連の低分解能段によって連続的に変換され、出力はデジタル補正ロジックブロックに結合されます。立ち上がりクロックエッジと立ち下がりクロックエッジの両方が、半クロック サイクルごとにサンプルをパイプラインに伝播します。このプロセスのデータレイテンシは 3.5 クロック サイクルとなり、その後、出力データはオフセットバイナリ形式でコード化された 14 ビットパラレル ワードとして利用可能になります。

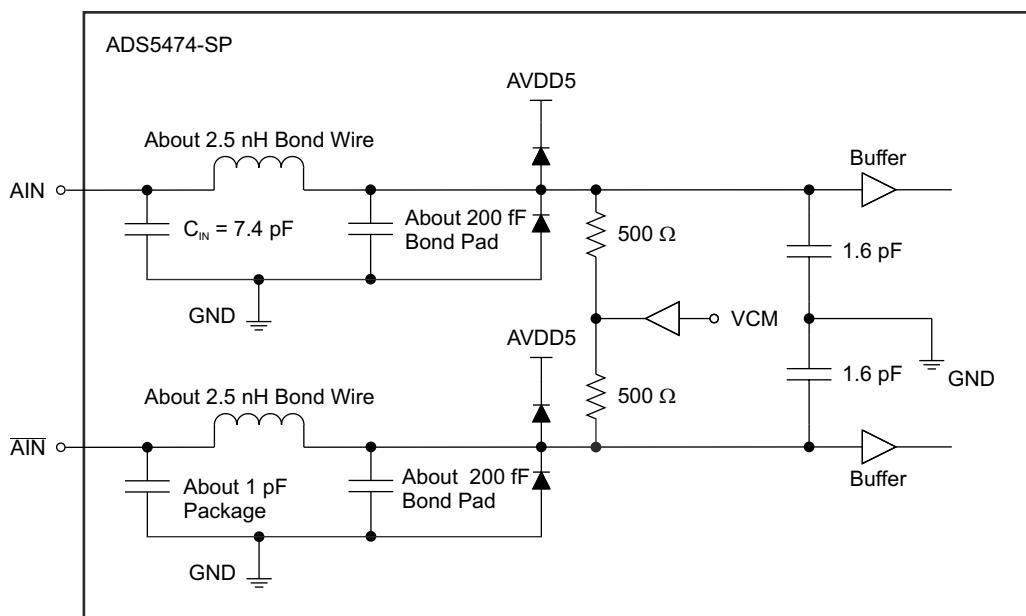

#### 6.1.1 入力構成

ADS5474 のアナログ入力は、アナログ疑似差動バッファと、それに続くバイポーラトランジスタ T&H で構成されます。アナログ バッファは、ADC の入力を駆動するソースを内部スイッチングから絶縁し、バッファ付き入力を使用しない ADC と比較して、高い入力周波数で容易に駆動できる高インピーダンスを示します。入力同相は、500Ω の抵抗を使用して内部で設定し、各入力に 3.1V の電圧を接続します (このファミリーの 12 ビットと 13 ビットの製品では同相モードは約 2.4V です)。この構成により、1kΩ の差動入力インピーダンスが得られます。

図 6-1. アナログ入力等価回路

フルスケール差動入力の場合、入力信号 (ピン 16 および 17) の各差動ラインは  $(3.1V + 0.55V)$  と  $(3.1V - 0.55V)$  の間で対称的にスイングします。この範囲は、各入力の最大信号スイングが  $1.1V_{PP}$ 、合計差動入力信号スイングが  $2.2V_{PP}$  であることを意味します。 $2.2V_{PP}$  未満での動作は許容されますが、性能と入力振幅との関係の特性は 図 5-19 および 図 5-20 に示します。たとえば、 $2.2V_{PP}$  ではなく  $1.1V_{PP}$  での性能については、-6dBFS での SNR および SFDR (0dBFS =  $2.2V_{PP}$ ) を参照してください。最大スイングは内部基準電圧ジェネレータによって決定されるため、この目的のための外部回路は不要です。

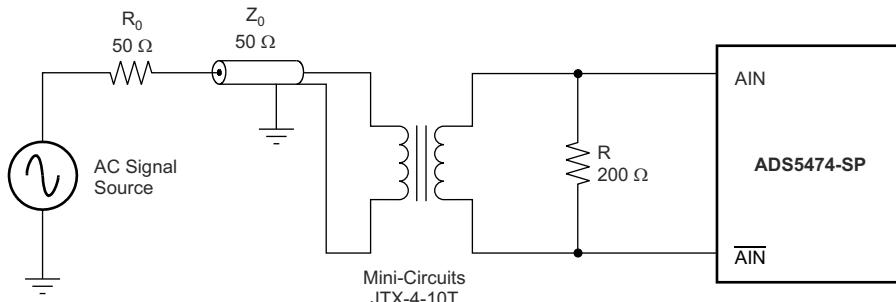

ADS5474 の最高の性能は、アナログ入力が差動駆動される場合です。図 6-2 の回路は、トランスの 1 次側または 2 次側の終端を持つ RF トランスを使用した可能な構成の 1 つを示しています。加えて、評価基板の構成は 2 個の双方向トランスを使用しており、良好な性能をさらに実証できます。電圧ゲインが必要な場合は、昇圧トランスを使用します。

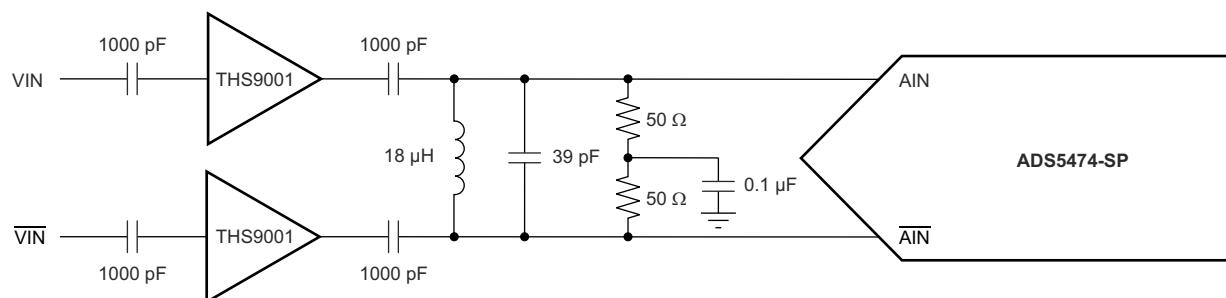

図 6-2. RF トランスを使用したシングル エンド入力を差動信号に変換

トランスの構成に加えて、テキサス インstrumentでは、アプリケーションに応じて選択できる幅広いシングル エンド オペアンプを提供しています。高入力周波数のアプリケーションでは THS9001 などの RF ゲイン ブロック アンプを使用します。50MHz から 400MHz の範囲の中間周波数で大きな電圧ゲインを得るには、図 6-3 に示す構成を使用します。異なる中間周波数に合わせて構成部品の値を調整します。この例 図 6-3 は評価基板にあり、170MHz の IF 用に調整されています。この構成の詳細については [ADS5474 EVM ユーザーガイド](#) および [THS9001 50MHz から 350MHz カスケード接続可能アンプデータシート](#) を参照してください。

図 6-3. THS9001 の if アンプを ADS5474 と組み合わせて使用

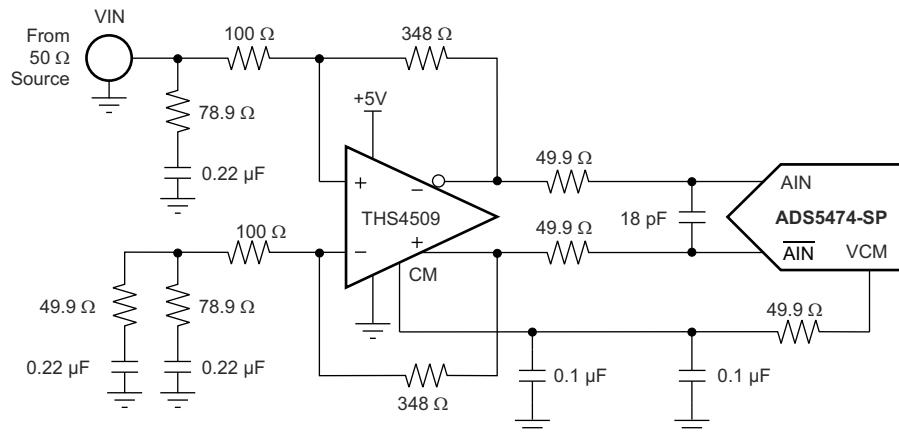

信号ソースとの DC 結合を必要とするアプリケーションでは、THS4509 などの差動入力または差動出力アンプ (図 6-4 を参照) を使用することで、広い周波数範囲にわたって良好な高調波性能と低ノイズを実現できます。

図 6-4. THS4509 または THS4520 を ADS5474 と組み合わせて使用します

この構成では、THS4509 アンプ回路は 10dB のゲインを実現し、シングル エンド入力を差動に変換して、ADC の VCM 出力ピンを使用して適切な入力同相電圧を ADS5474 に設定します。THS4509 出力と ADS5474 入力の間にある 50Ω の抵抗と 18pF のコンデンサ (ADC の入力容量とともに) により、信号の帯域幅は約 70MHz (-3dB) に制限されます。グ

ランドへの入力終端は、 $78.9\Omega$  抵抗と  $0.22\mu\text{F}$  コンデンサを介して、アンプ回路の入力インピーダンスとともに行われます。

回路のバランスを取るため、代替入力の  $78.9\Omega$  抵抗と  $0.22\mu\text{F}$  コンデンサの間のグランドに  $0.22\mu\text{F}$  コンデンサと  $49.9\Omega$  抵抗を挿入します。ゲインは、ソース インピーダンス、終端、 $348\Omega$  帰還抵抗の関数です。他の一般的なゲインに適切な  $50\Omega$  終端を設定するための部品値については、[THS4509 広帯域、低ノイズ、低歪み、完全差動アンプデータシート](#)を参照してください。

ADS5474 の推奨入力同相電圧は  $3.1\text{V}$  なので、THS4509 は  $V_{S+} = 5\text{V}$ 、 $V_{S-} = 0\text{V}$  (グランド) の単一電源入力で動作します。この構成では、ADC 入力同相モードが  $3.1\text{V}$  および  $+0.55\text{V}$  フルスケール信号により、THS4509 の  $3.6\text{V}$  からの推奨出力電圧をわずかに超える可能性があります。電圧を超えると THS4509 は損傷しませんが、THS4509 の高調波性能が低下する可能性があります。

推奨出力電圧範囲がより広いアンプは THS4520 です。このデバイスは、約  $20\text{MHz}$  までの周波数範囲で低ノイズ、低歪みを実現できるよう最適化済みです。高調波歪みの影響を受けないアプリケーションでは、高い周波数でのデバイスの選択が検討されます。

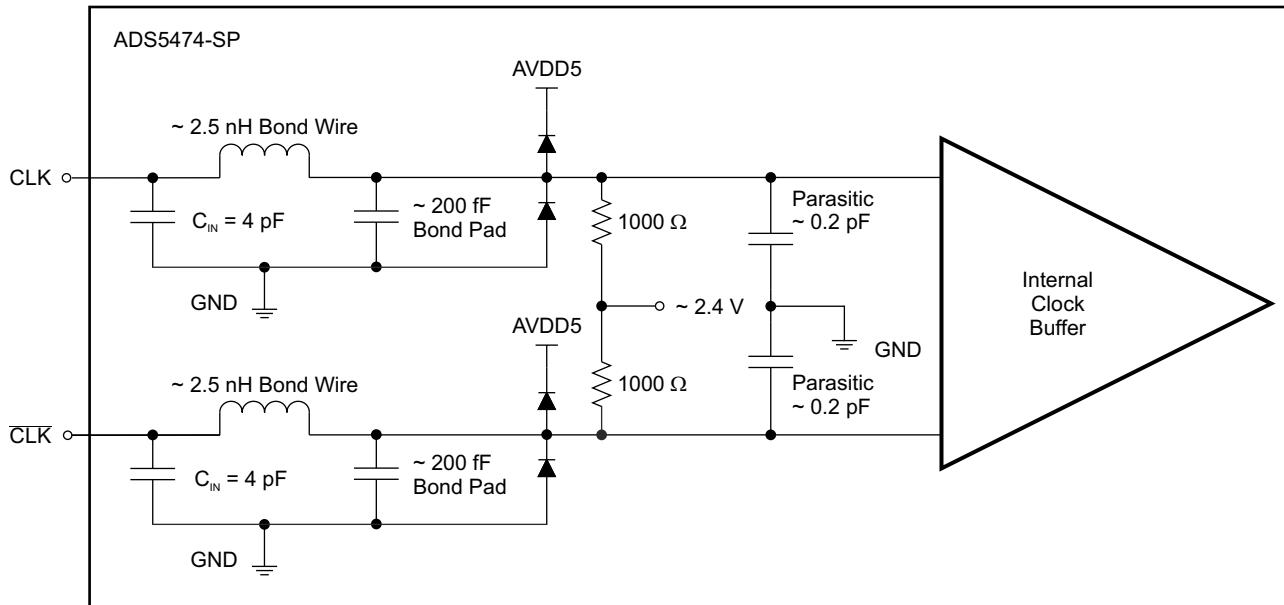

### 6.1.2 クロック入力

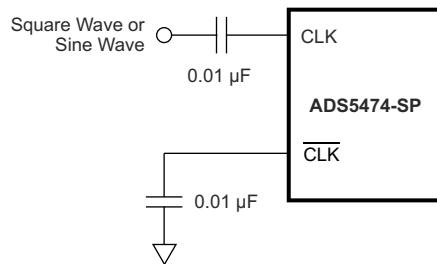

差動クロック信号またはシングルエンドクロック入力を使用して ADS5474 のクロック入力を駆動します。ADS5474 の特性評価は一般に、 $3\text{V}_{\text{PP}}$  の差動クロックで行われますが、ADC は約  $0.5\text{V}_{\text{PP}}$  の差動クロック振幅で良好に動作します。アナログ入力周波数が高くなるにつれて、クロックの振幅は性能の要素になります。ジッタが大きな問題とならない可能性のある低入力周波数のアプリケーションでは、シングルエンド クロックを使用すると、性能の大幅なトレードオフを伴わずにコストと基板面積を削減できます。この構成でクロック供給される場合、図 6-6 に示すように、TI は  $\overline{\text{CLK}}$  を  $0.01\mu\text{F}$  コンデンサを使用してグランドに接続することを推奨します。一方、 $\text{CLK}$  は  $0.01\mu\text{F}$  コンデンサでクロックソースに AC 結合されます。

S0292-04

図 6-5. クロック入力回路

**図 6-6. シングルエンド クロック**

ジッタに敏感なアプリケーションでは、システム レベルで差動クロックを使用する利点があります。差動クロックは、プリント基板 (PCB) レベルでの同相ノイズ除去を可能にします。差動クロックを使用する場合、ボード レベルのクロック ジッタが最適であるため、ジッタの影響を受けやすい高周波アプリケーションにとって ADC の信号対雑音比がより優れています。

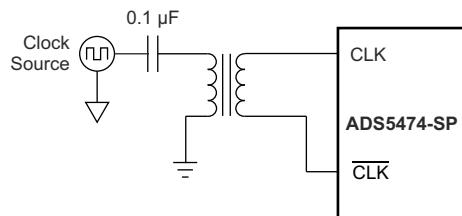

高いアナログ入力周波数または低速クロック周波数を使用する場合は、より大きなクロック振幅レベルを推奨します。正弦波クロックの場合、振幅が大きいほどクロックのスルーレートが高くなり、クロック ノイズがジッタに及ぼす影響が低減されます。アナログ入力周波数が高い場合、サンプリング プロセスはジッタの影響を受けやすくなります。クロック周波数が低速では、振幅の小さい正弦波クロックのスルーレートが低くなり、ジッタに関する SNR が低下する可能性があります。シングル エンド クロック ソースを差動クロックに変換するための推奨方法を、図 6-7 に示します。この方法は評価ボードに搭載されている構成と似て、特性評価の多くに使用されました。詳細については、[高速データコンバータのクロック供給アナログ設計ジャーナル](#)を参照してください。

**図 6-7. 差動クロック**

クロック入力の同相電圧は、内部の  $1\text{k}\Omega$  抵抗を使用して内部で  $2.4\text{V}$  に設定されます。TI は AC カップリングを使用することを推奨します。AC 結合が不可能な場合、ADS5474 はクロックの同相変動に対する優れた許容誤差を備えています。さらに、内部 ADC コアは変換プロセスにクロックの両方のエッジを使用します。50% デューティ サイクルのクロック信号が非常に優れた選択肢です。

ADS5474 は、アナログ入力周波数の  $350\text{MHz}$  で  $69.2\text{dBFS}$  の SNR を実現できます。 $350\text{MHz}$  で SNR を達成するには、RMS ジッタの合計が  $177\text{fs}$  である場合、クロック ソースの RMS ジッタが  $144\text{fs}$  以上であることを確認します。アナログ入力周波数の関数として推奨される最大 RMS クロック ジッタの概要を表 6-1 に示します。テーブルの作成に使用される式 1 および式 2 は以下の通りです。

**表 6-1. 推奨 RMS クロック ジッタ**

| 入力周波数 (MHz) | SNR (dBc) 測定値 | 総ジッタ (fsec RMS) | 最大クロック ジッタ (fsec RMS) |

|-------------|---------------|-----------------|-----------------------|

| 30          | 69.3          | 1818            | 1816                  |

| 70          | 69.1          | 798             | 791                   |

| 130         | 69.1          | 429             | 417                   |

| 230         | 68.8          | 251             | 229                   |

| 350         | 68.2          | 177             | 144                   |

| 450         | 67.4          | 151             | 110                   |

| 750         | 65.6          | 111             | 42                    |

| 1000        | 63.7          | 104             | 14                    |

式 1 および式 2 を使用して、必要なクロック ソース ジッタを推定します。

$$\text{SNR(dBc)} = -20 \times \log_{10}(2 \times \pi \times f_{\text{IN}} \times j_{\text{TOTAL}}) \quad (1)$$

$$j_{\text{TOTAL}} = [j_{\text{ADC}}^2 + j_{\text{CLOCK}}^2]^{\frac{1}{2}} \quad (2)$$

ここで、

- $j_{\text{TOTAL}}$  = クロックと ADC アペーチャ ジッタの RMS 合計

- $f_{\text{IN}}$  = アナログ入力周波数

- $j_{\text{ADC}}$  = ADC 内部アペーチャ ジッタ、データシートに記載されています

- $j_{\text{CLOCK}}$  = ADC へのクロック入力ピンにおけるクロックの RMS ジッタ

SNR は、クロック周波数ではなく、アナログ入力周波数に強く依存する関数です。クロック ソースのエッジのスロープは SNR にやや影響する可能性があり、これらの推定値では考慮されていません。この理由から、ADC クロック入力でのクロック ソースの振幅を最大化することを推奨しますが、必要はありません (ジッタ関連の SNR を実現するには、より高速なスロープが望ましい)。高速 ADC のクロック供給の詳細については、[高速、高 IF ADC デバイス向けの CDC7005 低ジッタクロックソリューションの実装アプリケーションノート](#)を参照してください。推奨されるクロックディストリビューションチップ (CDC) は、TI [CDC7005](#)、[CDCM7005-SP](#) および [CDCE72010](#) です。

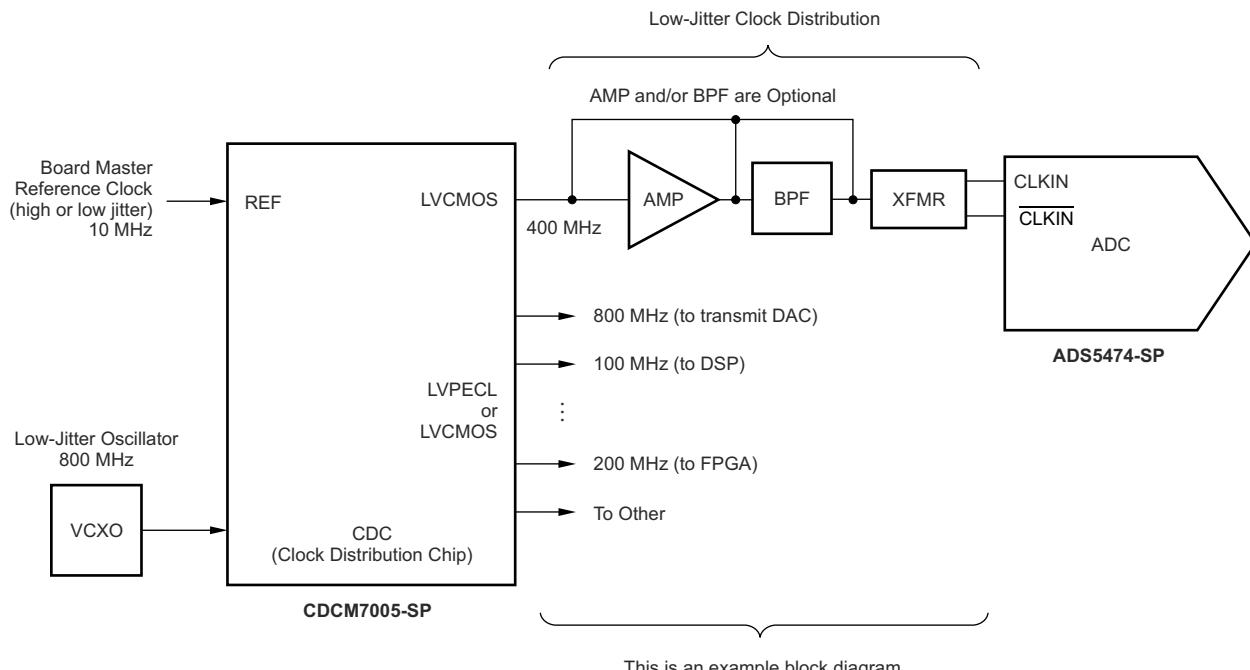

ジッタ要件に応じて、CDC と ADC との間にバンド パス フィルタ (BPF) が必要になることがあります。BPF の挿入損失により、ADC に対してクロック振幅が小さすぎる場合、またはクロック ソースの振幅が小さすぎる場合、まず CDC と BPF の間に安価なアンプを配置します。

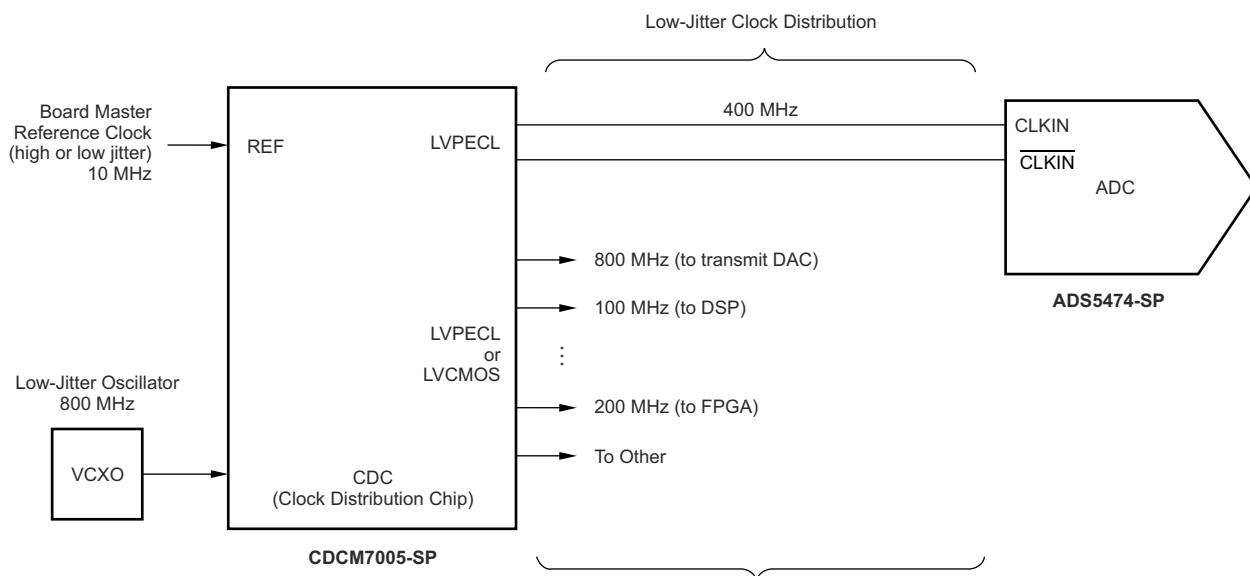

図 6-8 は、最大振幅と最小ジッタを実現するように最適化されたクロック信号パスを備えた、TI CDCM7005-SP から LVCMOS シングル エンド クロック出力を使用するシナリオを示しています。このタイプのコンディショニングは、150MHz を超える入力周波数と組み合わせて使用するのに最適です。このセットアップのジッタは推定が困難で、クロック パスの位相ノイズを慎重に分析する必要があります。BPF (BPF に挿入損失があるため低コストのアンプ) により、CDC から供給されるジッタが不十分な場合、CDC と ADC の間のジッタが改善されます。CDCM7005-SP 出力の合計ジッタは、選択した VCXO と CDCM7005-SP の位相ノイズに大きく依存し、通常 50 ~ 100fs の RMS ジッタがあります。VCXO を備えた CDCM7005-SP からのジッタが、追加のコンディショニングを行わずに十分であるとユーザーが判断した場合、図 6-9 に示すように、差動 LVPECL 出力を使用して CDCM7005-SP から ADS5474 に直接クロックを供給できます (正確な回路図については、[CDCM7005-SP 3.3V 高性能クロックシンクロナイザおよびジッタクリーナデータシート](#)を参照)。このシナリオは、ジッタがそれほど重要でない入力周波数の 150MHz 未満に最適です。TI は、適切なアプローチを決定する前に、必要なジッタを注意深く分析することを推奨しています。

This is an example block diagram.

入出力の許容周波数および振幅範囲の適切な回路図と仕様については [CDCM7005 3.3V 高性能クロックシンクロナイザおよびジッタクリーナデータシート](#)を参照してください。

図 6-8. 最高のジッタ クロック回路

This is an example block diagram.

入出力の許容周波数および振幅範囲の適切な回路図と仕様については [CDCM7005 3.3V 高性能クロックシンクロナイザおよびジッタクリーナデータシート](#)を参照してください。

図 6-9. 許容可能なジッタ クロック回路

### 6.1.3 デジタル出力

ADC は 14LVDS 互換でオフセット バイナリ データ出力 (D13 ~ D0、D13 は MSB、D0 は LSB)、データ準備完了信号 (DRY)、オーバー レンジ インジケータ (OVR) を備えています。TI では、DRY 信号を使用して ADS5474 の出力データをキャプチャすることを推奨します。DRY は DATA/OVR 出力とソース同期し、同じ周波数で動作するハーフレート DDR インターフェイスを形成し、DRY の立ち上がりエッジと立ち下がりエッジの両方でデータを更新します。TI は、デジタル出力の容量性負荷を最小限に抑えることを推奨します。容量が大きいと、データ有効なタイミング ウィンドウが短くなります。タイミングに対する値 (図 5-2 を参照) は、各 LVDS ラインのグランドに対して測定された 10pF の寄生基板容量 (または 5pF 差動寄生容量) を使って得られます。受信デバイスで DRY とデータの時間関係を設定する場合、セットアップ時間とホールド時間の組合せを最大化することを推奨しますが、この時間はデジタル データ (FPGA やフィールド プログラマブル フィールド アレイなど) を受信するデバイスのセットアップおよびホールド時間に部分的に依存します。DRY とデータは一致しているため、セットアップ時間を最大化するために、DRY またはデータのいずれかを遅延させることを推奨します。

図 5-2 を参照すると、サンプル N データ出力遷移に対する DRY の極性は、DRY 信号を生成するクロック分周器のスタートアップロジックレベルが不明なため決定されません (DRY は CLK の周波数分周です)。DRY の立ち上がりエッジまたは立ち下がりエッジはサンプル N と一致しており、DRY の極性は、電源がオフまたはオンでサイクルされたとき、またはパワーダウン ピンがサイクルされたときに反転できます。DRY の極性ではなく、遷移からのデータ キャプチャを推奨しますが、必須ではありません。複数の ADS5474 デバイスの同期が必要な場合は、データをキャプチャするために DRY ではなく、CLKIN 信号の形式を使用する必要があります。

DRY 周波数は ADS5474 と ADS5463 で同じですが (DRY は  $\frac{1}{2}$  CLK 周波数に相当)、ピン互換の ADS5444 では異なります (DRY は CLK 周波数に相当)。LVDS 出力はすべて、予想される LVDS 電圧レベルを満たすために、各出力ペア間に外部  $100\Omega$  負荷を接続する必要があります。トレースが長い場合、整合されたインピーダンスを実現し、信号の反射を回避するため、各デジタル出力にできるだけ近づけて  $100\Omega$  の負荷を ADS5474 に、LVDS 伝送ラインの端に別の  $100\Omega$  差動負荷を配置する必要があります。この場合、実効負荷により、LVDS 電圧レベルが半分に低下します。

14 ビットの出力ワードがすべて 0s またはすべて 1s を超えようとすると、OVR 出力はロジック High に等しくなります。このフラグは、アナログ入力信号がフルスケール入力の制限である約  $2.2V_{PP}$  ( $\pm$ ゲイン誤差) を超えたことを示します。OVR インジケータは、ゲイン制御を使用してアナログ入力信号を許容可能な制限範囲内に維持するシステム向けに提供されています。

## 7 アプリケーションと実装

### 注

以下のアプリケーションセクションにある情報は、TI の製品仕様に含まれるものではなく、TI はその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただされることになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 7.1 電源に関する推奨事項

ADS5474 は 3 つの電源を使用します。このリファレンス デザインのアナログ部分には、5V と 3.3V の電源 (AVDD5 と AVDD3) を使用し、デジタル部分は 3.3V 電源 (DVDD3) を使用します。適切なデカップリングを備えた低ノイズ電源の使用を推奨します。リニア電源はスイッチ電源を推奨します。スイッチ電源は、ADS5474 と結合できるノイズ成分をより多く生成する傾向があります。ユーザーは理想的未満の電源でデバイスに電力を供給しながら、優れた性能を達成できます。すべてのシステムで、電源の種類とデカップリングのレベルごとに単一の推奨事項を作成することはできません。アプリケーションとプロセスによって、ADS5474 の消費電力は、クロックレートまたは入力周波数を超えて大きく変化することはできません。

AVDD3 と DVDD3 の間には内部で 2 個のダイオードが逆方向に接続されているため、電源オンシーケンスを推奨します。これら 2 つの電源の間に電源オンに遅延がある場合、遅延している電源オン前に内部ダイオードを介して電流がシンクされる可能性があります。シンク電流は、外部電源のインピーダンスに応じて大きくても小さくとも、デバイスの損傷や電源に影響を及ぼす可能性があります。

最適な電源オンシーケンスは、以下のオプションのいずれかです (AVDD5 が電源投入されるタイミングに関係なく):

1. AVDD3 と DVDD3 の両方を同時に起動します (最適なシナリオ)、または

2. 電源投入時は、AVDD3 と DVDD3 の電圧差を 0.8V 未満に維持してください (0.8V は厳密な仕様ではありません。電源間の差分が小さいほど安全です)。

上記のシーケンスが実用的でない場合は、電源からのシンク電流を制御するか、保護を外部に追加する必要があります。DVDD3 ピンまたは AVDD3 ピンの最大過渡電流 ( $\mu$  s 単位) は 500mA であり、デバイスへの損傷の可能性を回避したり、デバイスの寿命を短くしたりするためです。

セクション 5.1 に示すアナログおよびクロック入力の値は、電源がオンのときに有効です。電源がオフで、クロックまたはアナログ入力が依然として動作している場合、デバイスの損傷を防止するため、入力電圧と入力電流を制限する必要があります。ADC 電源がオフの場合、最大/最小連続 DC 電圧は  $\pm 0.95V$  で、最大 DC 電流は各入力ピン (クロックまたはアナログ) の、グランドを基準とした 20mA です。

図 7-1. PSRR と供給注入周波数との関係

## 8 デバイスおよびドキュメントのサポート

### 8.1 デバイス サポート

#### 8.1.1 仕様の定義

**アナログ帯域幅** 基本波の電力が低周波数値に対して 3dB 低減されるアナログ入力周波数。

**アペーチャ遅延** 入力サンプリング クロックの立ち上がりエッジから、実際にサンプリングが行われるまでの遅延時間。

**アペーチャの不安定性 (ジッタ)** アペーチャ遅延におけるサンプル間の変動。

**クロック パルス幅/デューティサイクル** クロック信号のデューティサイクルは、クロック信号の周期に対する、信号が high に維持される時間の割合 (クロック パルス幅) です。

**微分非直線性 (DNL)** 理想的な ADC は、正確に 1LSB 間隔で配置されたアナログ入力値でコード遷移を示します。DNL は、この理想的な値からの 1 ステップの偏差で、LSB 単位で測定します。

**同相信号除去比 (CMRR)** CMRR は、両方のアナログ入力に同時に印加される信号を除去する能力を測定します。注入された同相周波数レベルは dBFS に変換され、出力 FFT のスプリアスは dBFS 単位で測定され、その差は CMRR (dB 単位) です。

**有効ビット数 (ENOB)** ENOB は、量子化ノイズに基づく理論的な制限と比較して、コンバータ性能のビット単位で表される測定値です：

$$\text{ENOB} = [\text{SINAD} - 1.76] \div 6.02 \quad (3)$$

**ゲイン誤差** ゲイン誤差は、ADC の実際の入力フルスケール範囲が、理想的な入力フルスケール範囲に対するパーセンテージで表され、理想的な値からどれだけ逸脱しているかを示します。

**積分非直線性 (INL)** INL は、その伝達関数の最小 2 乗曲線当てはめによって決定される、最適なフィットラインからの ADC 伝達関数の偏差です。各アナログ入力値の INL は、実際の伝達関数と、この最適なラインとの差 (LSB 単位で測定) です。

**オフセット誤差** オフセット誤差は、両方の入力が同相に接続されているときの、出力コードの中間コードからの偏差です。

**電源電圧変動除去比 (PSRR)** PSRR は、電源に存在する周波数を除去する能力の指標です。注入された周波数レベルは dBFS に変換され、出力 FFT のスプリアスは dBFS 単位で測定され、その差は PSRR (dB 単位) です。測定では、基板の電源デカッピング コンデンサの利点が較正されています。

**信号対雑音比 (SNR)** SNR は基本波の出力 ( $P_S$ ) とノイズ フロア出力 ( $P_N$ ) との比で、DC および最初の 5 次の高調波の出力は除外されます。

$$\text{SNR} = 10 \log_{10} \frac{P_S}{P_N} \quad (4)$$

SNR は、基本波の絶対電力をリファレンスとして使用する場合は dBc (dB からキャリアまで) 単位、または基本波の電力がコンバータのフルスケール範囲に外挿されている場合は dBFS (dB からフルスケールまで) 単位で表されます。

**信号対雑音および歪み (SINAD)** SINAD は基本波の電力 ( $P_S$ ) と、ノイズ ( $P_N$ ) や歪み ( $P_D$ ) も含め、DC を除く他のすべてのスペクトル成分の電力との比です。

$$\text{SINAD} = 10 \log_{10} \frac{P_S}{P_N + P_D} \quad (5)$$

SINAD は、基本波の絶対電力をリファレンスとして使用する場合は dBc (キャリアまで) 単位、または基本波の電力がコンバータのフルスケール範囲に外挿されている場合は dBFS (dB からフルスケールまで) 単位で表されます。

**温度ドリフト** 温度ドリフト (ゲイン誤差およびオフセット誤差を基準とした) は、公称温度での値から  $T_{MIN}$  または  $T_{MAX}$  での値への変化を規定しています。これは、全温度範囲にわたるパラメータの最大変動を  $T_{MIN} - T_{MAX}$  で割った値として計算されます。

**全高調波歪み (THD)** THD は、基本波の電力 ( $P_S$ ) と最初の 5 つの高調波の電力 ( $P_D$ ) との比です。

$$THD = 10 \log_{10} \frac{P_S}{P_D} \quad (6)$$

THD は通常、dBc (dB 対キャリア) 単位で表されます。

**ツートーン相互調波歪み (IMD3)** IMD3 は、(周波数  $f_1, f_2$  における) 基本波の電力と、周波数  $2f_1 - f_2$  または  $2f_2 - f_1$  において、基本波の電力と最悪のスペクトル成分の電力の比です。IMD3 は、基本波の絶対電力をリファレンスとして使用する場合の dBc (dB からキャリアへ)、または基本波の電力がコンバータのフルスケール範囲に外挿されている場合の dBFS (dB からフルスケールまで) の単位で表されます。

## 8.2 ドキュメントのサポート

### 8.2.1 関連資料

- テキサス・インスツルメンツ、[50MHz から 750MHz カスケード接続可能アンプデータシート](#)

- テキサス・インスツルメンツ、[ADS5440/44/63/74 EVM ユーザー ガイド](#)

- テキサス・インスツルメンツ、[CDCM7005 3.3V 高性能クロックシンクロナイザおよびジッタクリーナデータシート](#)

- テキサス・インスツルメンツ、[CDCM7005-SP 3.3V 高性能 Rad-Tolerant Class V、クロックシンクロナイザおよびジッタクリーナデータシート](#)

- テキサス・インスツルメンツ、[高速データコンバータのクロック供給アナログ設計ジャーナル](#)

- テキサス・インスツルメンツ、[高速高 IF ADC デバイス用の CDC7005 低ジッタクロックソリューションの実装アプリケーションノート](#)

- テキサス・インスツルメンツ、[THS4509 幅広帯域、低ノイズ、低歪み、完全差動アンプデータシート](#)

### 8.3 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 8.4 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

### 8.5 商標

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

## 8.6 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

## 8.7 用語集

### テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 9 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| <b>Changes from Revision A (December 2013) to Revision B (November 2025)</b>                                     | <b>Page</b> |

|------------------------------------------------------------------------------------------------------------------|-------------|

| • タイトルを次のように更新: Class V, 14 ビット、400MSPS アナログからデジタルコンバータ: ADS5474-SP, Class V, 14 ビット、400MSPS、アナログ デジタルコンバータ..... | 1           |

| • ドキュメント全体にわたって表、図、相互参照の採番方法を更新.....                                                                             | 1           |

| • ピン構成の図のピン 1, 22, 43, 64 を更新しました: AGND から GND.....                                                              | 3           |

| • ピン構成および機能セクションを仕様セクションの前に移動しました.....                                                                           | 3           |

| • ESD 定格セクションを追加しました.....                                                                                        | 5           |

| • ESD 定格を絶対最大定格セクションから ESD 定格セクションに移動しました.....                                                                   | 5           |

| • ESD 定格セクションの後に推奨動作条件セクションを移動しました.....                                                                          | 5           |

| • タイトルを次のように更新: 熱特性から: 熱に関する情報.....                                                                              | 6           |

| • 熱に関する情報セクションを推奨動作条件セクションの後に移動しました.....                                                                         | 6           |

| • $R_{\theta JA}$ を更新しました: $21.81^{\circ}\text{C}/\text{W} >> 19^{\circ}\text{C}/\text{W}$ .....                 | 6           |

| • $R_{\theta JC}$ を更新しました: $0.849^{\circ}\text{C}/\text{W} >> 1.8^{\circ}\text{C}/\text{W}$ .....                | 6           |

| • アナログ入力の入力容量の標準値を次のように変更しました: 7.4pF から: 2.8pF.....                                                              | 6           |

| • 動作寿命のディレーティングチャート、エレクトロマイグレーション故障モードを熱特性セクションから電気的特性セクションに移動しました.....                                          | 6           |

| • タイミング図をタイミング特性セクションに移動しました.....                                                                                | 10          |

| • セクションのタイトルをアプリケーション情報から詳細説明に変更しました.....                                                                        | 16          |

| • セクションのタイトルを動作原理から概要に変更しました.....                                                                                | 16          |

| • 図 6-1 の容量を「約 1pF パッケージ」に変更しました.....                                                                            | 16          |

| • デジタル出力の (DRY は CLK 周波数と等しい) を (DRY は CLK 周波数の $\frac{1}{2}$ と等しい) に変更しました.....                                 | 22          |

| • 「アプリケーションと実装」セクションを追加.....                                                                                     | 23          |

| • セクションのタイトルを電源から電源推奨に更新しました.....                                                                                | 23          |

| • 電源に関する推奨事項セクションをアプリケーションと実装セクションに移動しました.....                                                                   | 23          |

| • 静電放電に関する注意事項をデバイスおよびドキュメント サポートセクションに移動しました.....                                                               | 25          |

| <b>Changes from Revision * (September 2013) to Revision A (December 2013)</b> | <b>Page</b> |

|-------------------------------------------------------------------------------|-------------|

| • 特長の一覧に箇条書き項目エンジニアリング評価 (IEM) を追加しました.....                                   | 1           |

## 10 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのプラウザ版を使用されている場合は、画面左側の説明をご覧ください。

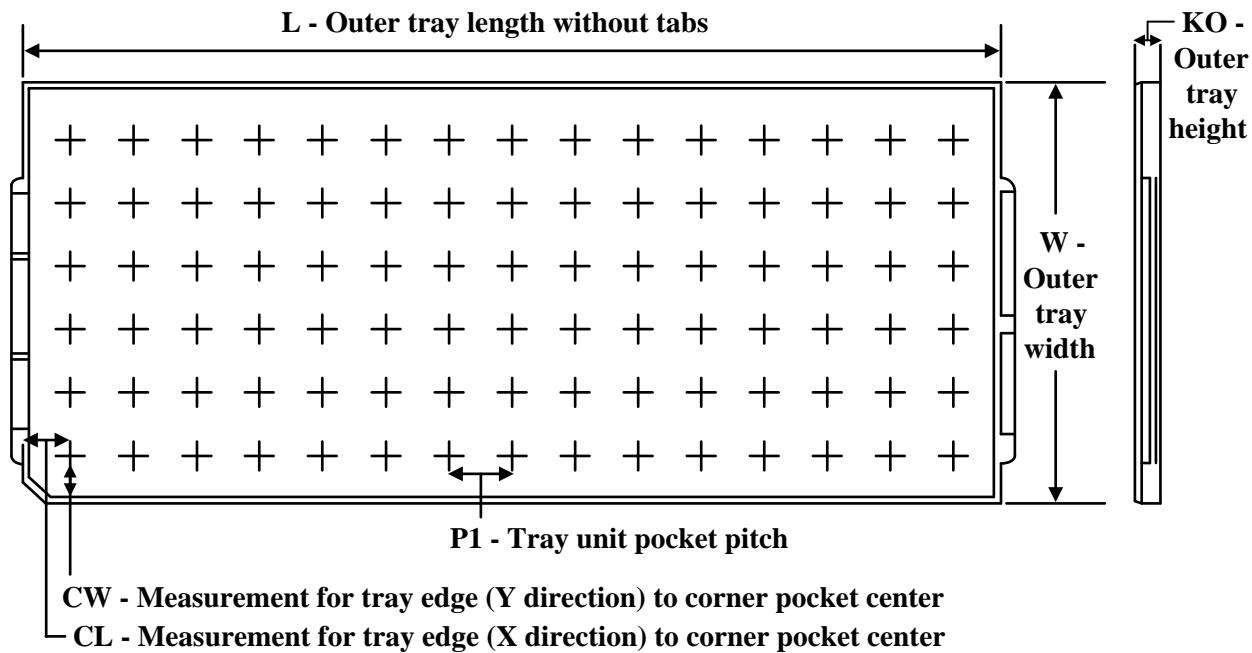

**TRAY**

Chamfer on Tray corner indicates Pin 1 orientation of packed units.

\*All dimensions are nominal

| Device        | Package Name | Package Type | Pins | SPQ | Unit array matrix | Max temperature (°C) | L (mm) | W (mm) | KO (µm) | P1 (mm) | CL (mm) | CW (mm) |

|---------------|--------------|--------------|------|-----|-------------------|----------------------|--------|--------|---------|---------|---------|---------|

| ADS5474HFG/EM | HFG          | CFP          | 84   | 1   | 2 x 5             | 150                  | 315    | 135.9  | 7620    | 57      | 43.5    | 39.45   |

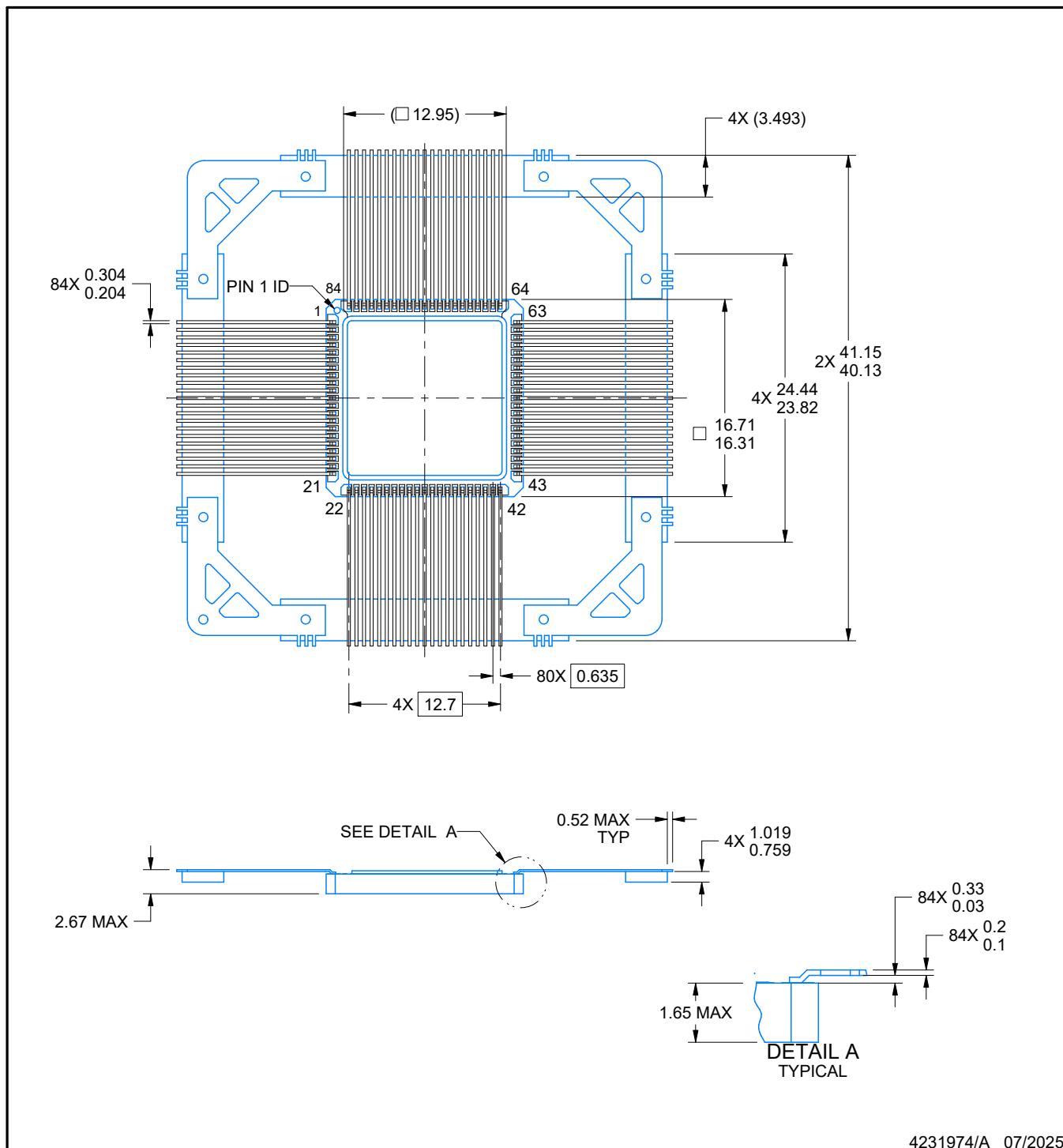

# DATA BOOK PACKAGE OUTLINE

|                   |

|-------------------|

| SUBSTRATE EXAMPLE |

| 4041137           |

|                              |                  |                                                                                                                                          |        |                                  |  |

|------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------------------------|--|

| DRAFTER: ANIS FAUZI          | DATE: 07/10/2025 |                                                                                                                                          |        | DIMENSIONS IN MILLIMETERS        |  |

| DESIGNER:                    | DATE:            |  <b>TEXAS INSTRUMENTS</b><br>SEMICONDUCTOR OPERATIONS |        | CODE IDENTITY<br>NUMBER<br>01295 |  |

| CHECKER: K. SINCERBOX        | DATE: 07/10/2025 |                                                                                                                                          |        |                                  |  |

| ENGINEER: LI JIANG           | DATE: 07/10/2025 |                                                                                                                                          |        |                                  |  |

| APPROVED: NICK CHU           | DATE: 07/10/2025 |                                                                                                                                          |        |                                  |  |

| RELEASED: ANIS FAUZI         | DATE: 07/10/2025 | <b>ePOD, HFG0084B / CFP,<br/>84 PIN, 0.635 MM PITCH</b>                                                                                  |        | REV A PAGE 1 OF 3                |  |

| TEMPLATE INFO: EDGE# 4218519 | DATE: 03/20/2013 | SCALE 2X                                                                                                                                 | SIZE A | 4231974                          |  |

# PACKAGE OUTLINE

HFG0084B

CFP - 2.67 mm max height

CFP

4231974/A 07/2025

## NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This package is hermetically sealed with a metal lid.

4. The lid and the heat sink are connected to ground leads.

5. The leads are gold plated and can be solder dipped.

## REVISIONS

| REV | DESCRIPTION         | ECR     | DATE       | ENGINEER / DRAFTSMAN  |

|-----|---------------------|---------|------------|-----------------------|

| A   | RELEASE NEW DRAWING | 2213474 | 07/10/2025 | LI JIANG / ANIS FAUZI |

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月