## 2次デルタ-シグマ・モジュレータ用 クワッド・デジタル・フィルタ

### 特 長

- 4個の独立したプログラム可能なデジタル・フィルタ

- 4個のウィンドウ・コンパレータ

- 4種のインターフェイスモードを選択可能

3種のパラレルモード/1種のシリアルモード

- 包括的な割り込みシステム

- プログラマブルな入力条件設定

- リゾルバ・アプリケーション用の搬送波周波数生成機能内蔵

### アプリケーション

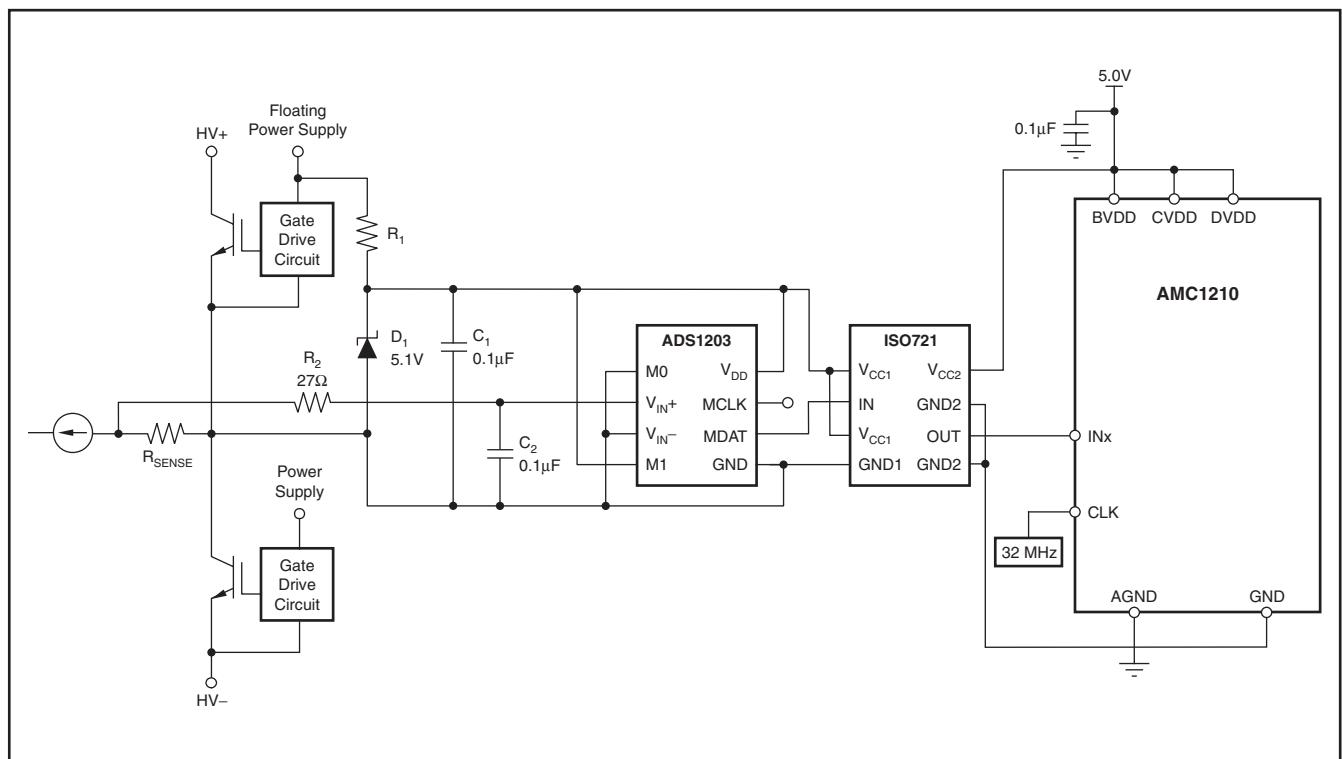

- 電流測定

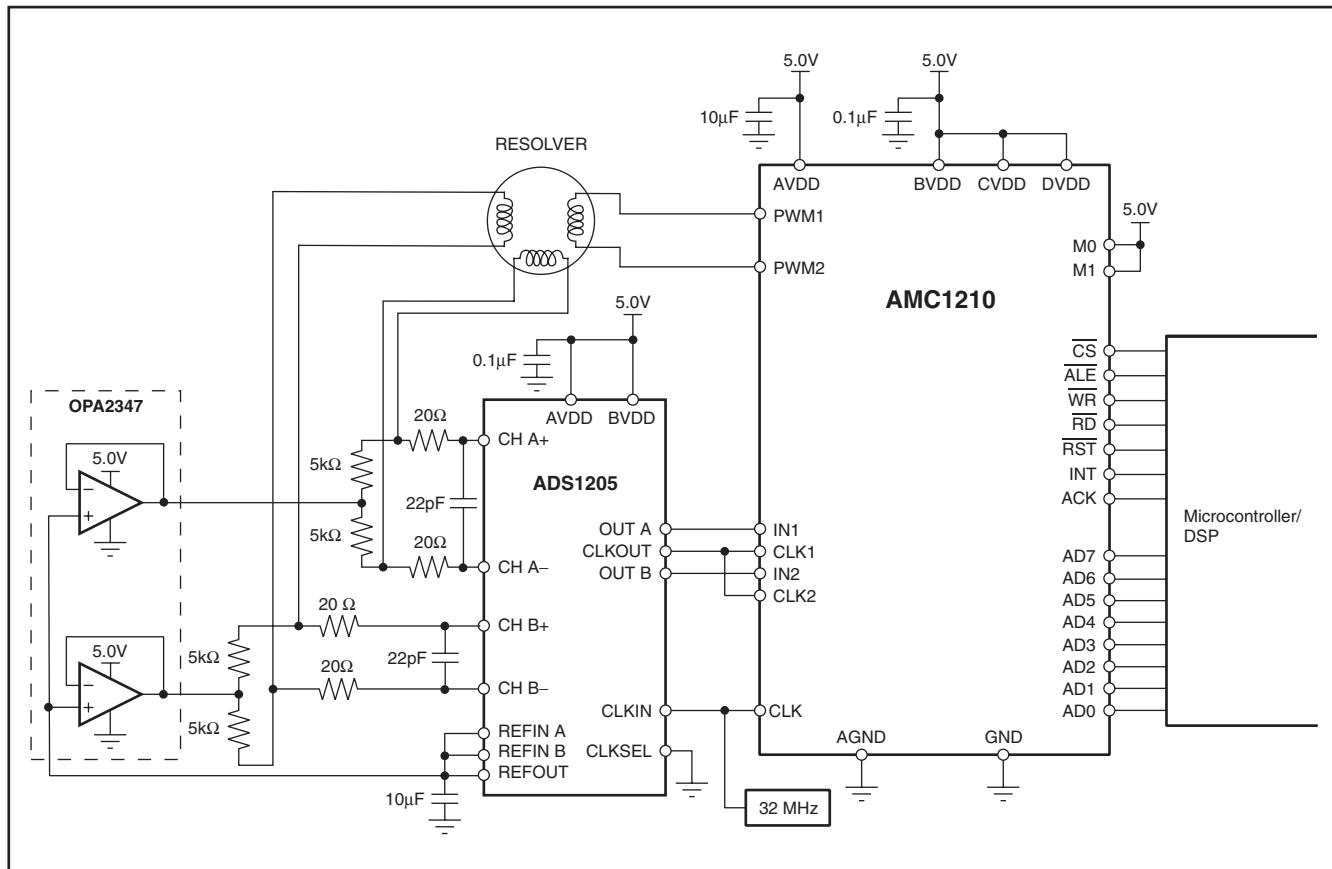

- リゾルバのデコード

### 概 要

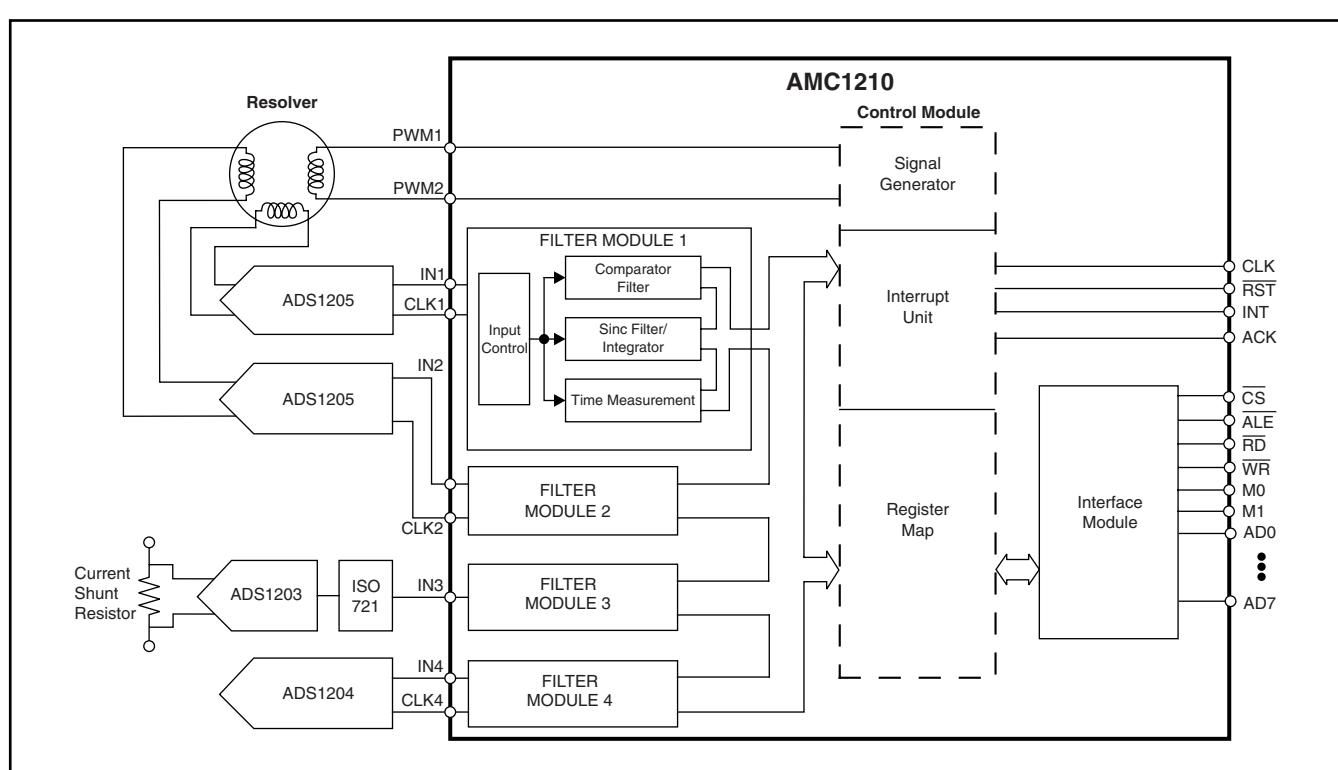

AMC1210は、4チャネルのデジタル・フィルタであり、電流測定、モーター制御アプリケーションのリゾルバ位置デコードに特化して設計されたものです。

各入力は、独立したデルタ-シグマ( $\Delta\Sigma$ )モジュレータのビット・ストリームを受け取ります。これらのビット・ストリームは、独立してプログラム可能な4つのデジタル・デシメーション・フィルタによって処理されます。AMC1210には柔軟性の高いインターフェイスと包括的な割り込みユニットもあるので、カスタマイズしたデジタル機能の実現と、過電流モニタ用にデジタル・スレッシュホールドの比較をすぐに行うことが可能です。

すべての商標および登録商標は、それぞれの所有者に帰属します。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ (日本TI) が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。

日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。

TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

## 静電気放電対策

静電気放電はわずかな性能の低下から完全なデバイスの故障に至るまで、様々な損傷を与えます。すべての集積回路は、適切なESD保護方法を用いて、取扱いと保存を行うようにして下

さい。高精度の集積回路は、損傷に対して敏感であり、極めてわずかなパラメータの変化により、デバイスに規定された仕様に適合しなくなる場合があります。

### 御発注の手引き<sup>(1)</sup>

| PRODUCT | PACKAGE-LEAD | PACKAGE DESIGNATOR | SPECIFIED TEMPERATURE RANGE | PACKAGE MARKING | ORDERING NUMBER | TRANSPORT MEDIA, QUANTITY |

|---------|--------------|--------------------|-----------------------------|-----------------|-----------------|---------------------------|

| AMC1210 | QFN          | RHA                | −40°C to +85°C              | AMC1210I        | AMC1210IRHAT    | Tape and Reel, 250        |

|         |              |                    |                             |                 | AMC1210IRHAR    | Tape and Reel, 2500       |

(1) 最新の仕様とパッケージ情報については、このデータシートの末尾にある「付録: パッケージ・オプション」を参照するか、TI の Web サイト ([www.ti.com](http://www.ti.com)) を参照してください。

### 絶対最大定格

特に指定がない限り、自由通気の全温度範囲に適用<sup>(1)</sup>

|                                                              | AMC1210                       | UNIT |

|--------------------------------------------------------------|-------------------------------|------|

| Supply voltage, all supplies (AVDD, BVDD, CVDD, DVDD) to GND | −0.3 to +6                    | V    |

| Digital input to GND                                         | GND − 0.3 to BVDD + 0.3       | V    |

| Ground voltage difference, AGND to GND                       | ±0.3                          | V    |

| Input current to any pin except supply                       | −10 to +10                    | mA   |

| Power dissipation                                            | See Dissipation Ratings Table |      |

| Operating virtual junction temperature range, T <sub>J</sub> | −40 to +150                   | °C   |

| Operating free-air temperature range, T <sub>A</sub>         | −40 to +85                    | °C   |

| Storage temperature range, T <sub>STG</sub>                  | −65 to +150                   | °C   |

| Lead temperature, 1.6mm (1/16-inch) from case for 10 seconds | +260                          | °C   |

(1) 絶対最大定格以上のストレスは、致命的なダメージを製品に与えることがあります。これはストレスの定格のみについて示しており、このデータシートの「電気的特性に示された値を超える状態での本製品の機能動作を意味するものではありません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

### 損失定格

| PACKAGE            | T <sub>A</sub> ≤ +25°C<br>POWER RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = +25°C | T <sub>A</sub> = +70°C<br>POWER RATING | T <sub>A</sub> = +85°C<br>POWER RATING |

|--------------------|----------------------------------------|-------------------------------------------------|----------------------------------------|----------------------------------------|

| RHA <sup>(1)</sup> | 3787mW                                 | 30.3mW/°C                                       | 2424mW                                 | 1969mW                                 |

(1) RHA パッケージの熱抵抗(ジャンクションから周囲へ)は、32°C/W です。

## 電気的特性

特に指定がない限り、 $-40^{\circ}\text{C} \sim +85^{\circ}\text{C}$  の範囲で、AVDD、CVDD、DVDD = 5V、BVDD = 2.7V です。

各電圧に関して、条件( $\text{CVDD} \geq \text{DVDD} \geq \text{BVDD}$ )が成立していることが必要です。

| PARAMETER                                | TEST CONDITIONS                             | AMC1210 |      |     | UNIT                     |

|------------------------------------------|---------------------------------------------|---------|------|-----|--------------------------|

|                                          |                                             | MIN     | TYP  | MAX |                          |

| <b>DIGITAL INPUT/OUTPUT</b>              |                                             |         |      |     |                          |

| Logic levels:                            |                                             |         |      |     |                          |

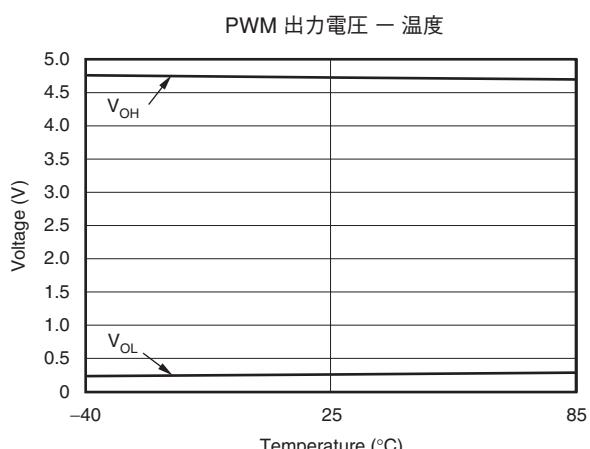

| $V_{\text{OH}}$                          | BVDD = 2.7                                  | 2.4     |      |     | V                        |

|                                          | BVDD = 5.0                                  | 4.44    |      |     | V                        |

| $V_{\text{OL}}$                          | BVDD = 2.7                                  |         |      | 0.4 | V                        |

|                                          | BVDD = 5.0                                  |         |      | 0.5 | V                        |

| System clock frequency                   | Pin 'CLK'                                   |         |      | 90  | MHz                      |

| Modulator clock frequency                | Pins CLK1, CLK2, CLK3, CLK4<br>Mode = 0     |         |      | 22  | MHz                      |

| SPI interface clock frequency            | Pin $\overline{\text{WR}}$ , option 1       |         |      | 25  | MHz                      |

| SPI interface clock frequency            | Pin $\overline{\text{WR}}$ , option 2       |         |      | 40  | MHz                      |

| Parallel interface read/write frequency  | Pin $\overline{\text{CS}}$                  |         |      | 22  | MHz                      |

| <b>POWER SUPPLY REQUIREMENTS</b>         |                                             |         |      |     |                          |

| Power-supply voltage, pin AVDD           |                                             | 4.5     |      | 5.5 |                          |

| Power-supply voltage, pins CVDD and DVDD | CVDD $\geq$ DVDD $\geq$ BVDD                | 3.3     |      | 5.5 | V                        |

| Power-supply voltage, pin DVDD           | CVDD $\geq$ DVDD $\geq$ BVDD                | 2.7     |      | 5.5 | V                        |

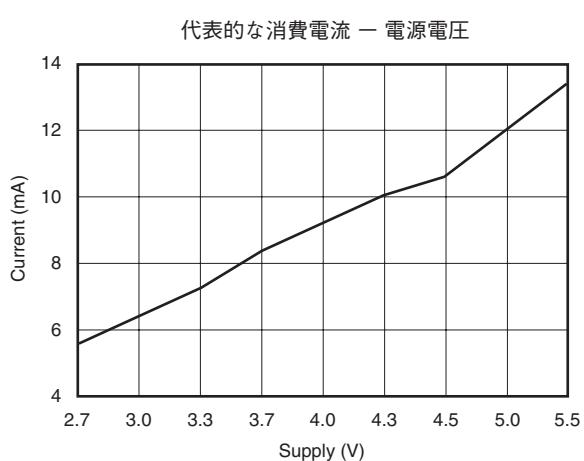

| Total power <sup>(1)</sup>               | All supplies = 5V                           |         | 24.5 |     | mW                       |

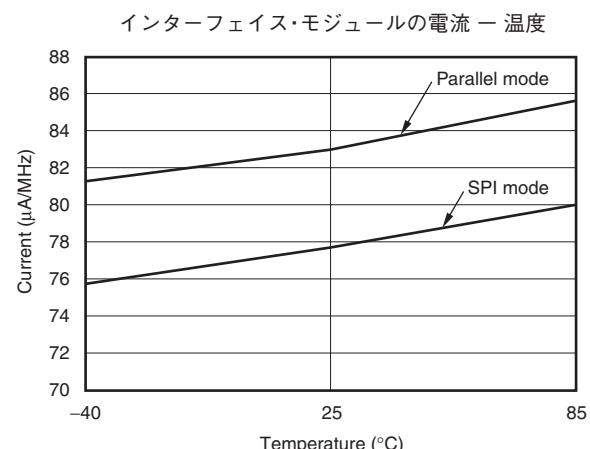

| Power-supply current                     | One filter module <sup>(2)</sup>            |         | 260  |     | $\mu\text{A}/\text{MHz}$ |

| Power-supply current                     | Four filter modules <sup>(2)</sup>          |         | 850  |     | $\mu\text{A}/\text{MHz}$ |

|                                          | SPI interface                               |         | 78   |     | $\mu\text{A}/\text{MHz}$ |

|                                          | Parallel interface <sup>(3)</sup>           |         | 83   |     | $\mu\text{A}/\text{MHz}$ |

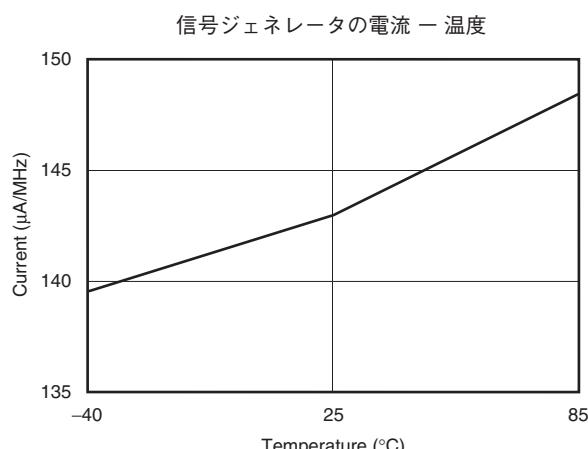

|                                          | Signal generator                            |         | 140  |     | $\mu\text{A}/\text{MHz}$ |

| <b>SIGNAL GENERATOR OUTPUT</b>           |                                             |         |      |     |                          |

| $V_{\text{OH}}$                          | $R_{\text{LOAD}} = 50\Omega$ , bit HPE = 1  | 4.60    | 4.73 |     | V                        |

| $V_{\text{OL}}$                          | $R_{\text{LOAD}} = 50\Omega$ , bit HPE = 1  |         | 0.26 | 0.4 | V                        |

| $V_{\text{OH}}$                          | $R_{\text{LOAD}} = 500\Omega$ , bit HPE = 0 | 4.60    | 4.73 |     | V                        |

| $V_{\text{OL}}$                          | $R_{\text{LOAD}} = 500\Omega$ , bit HPE = 0 |         | 0.26 | 0.4 | V                        |

(1) 2個のモジュールが動作し、両方がSinc<sup>3</sup>、SOSR = 256に設定されている状態での消費電力です。

(2) フィルタ・モジュールは、コンバレータ・ユニットのフィルタをSinc<sup>3</sup>、およびCOSR = 32 に設定し、sincユニットのフィルタをSinc<sup>3</sup>構造、

およびSOSR = 256に設定した状態で構成します。

(3) 3つのモードすべてに共通です。

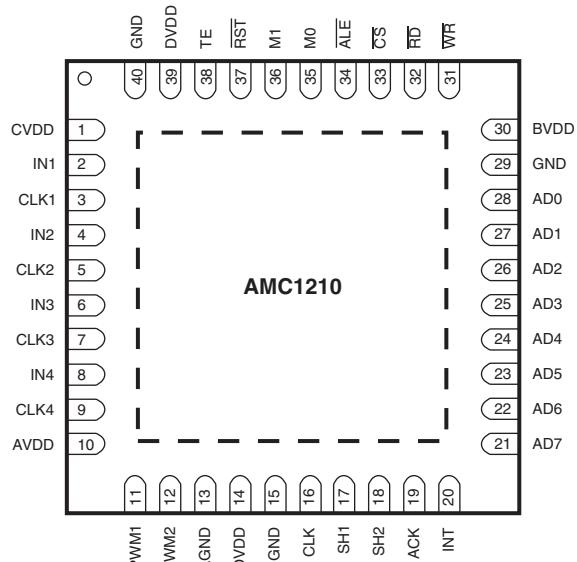

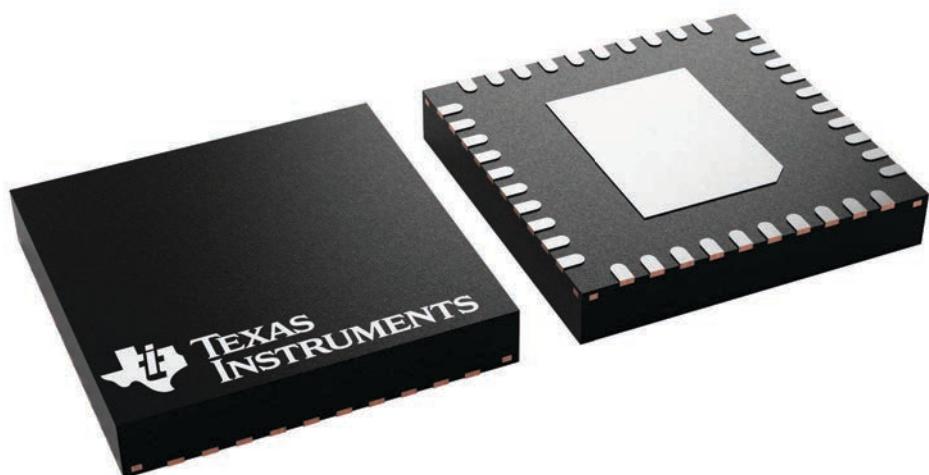

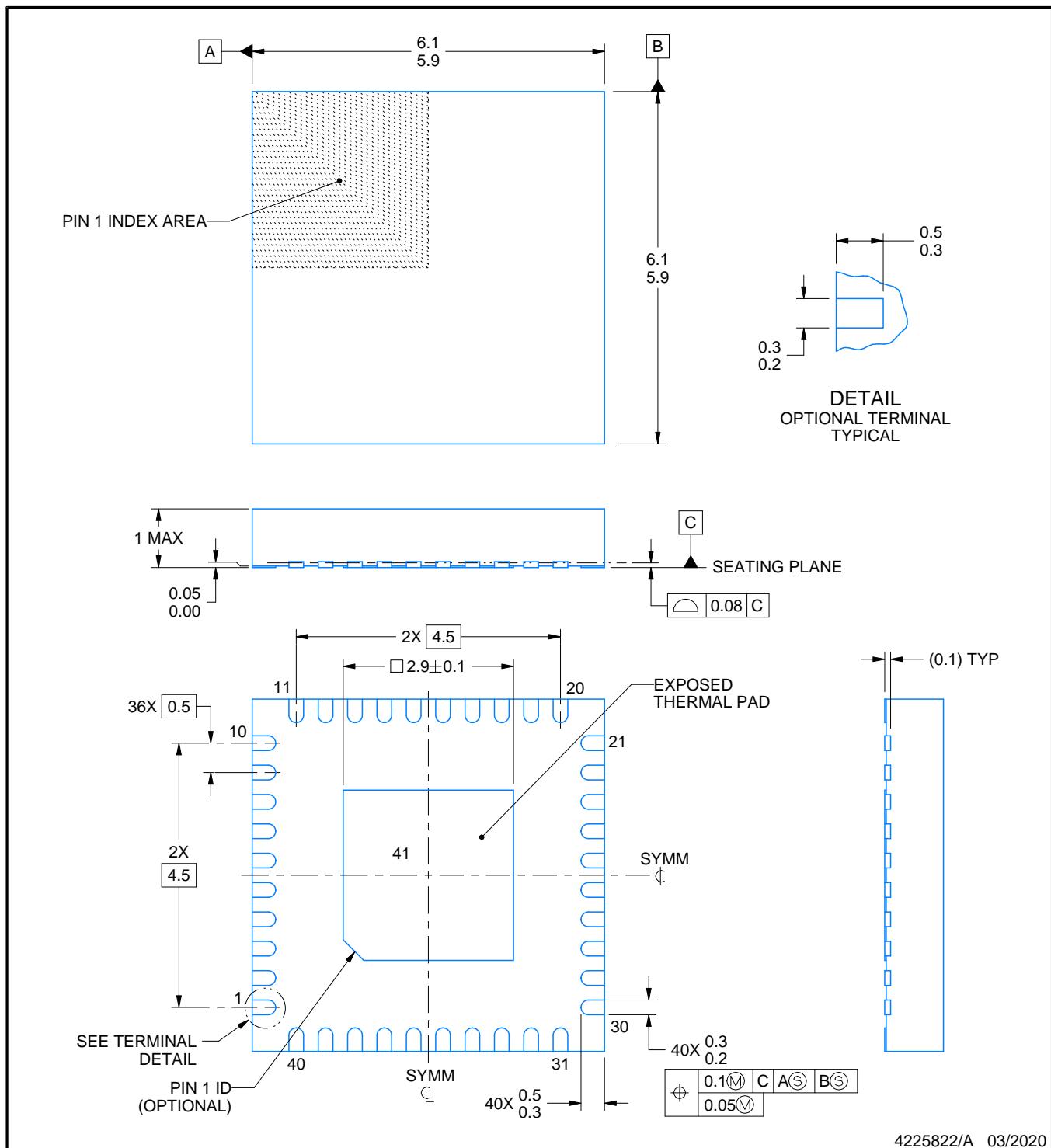

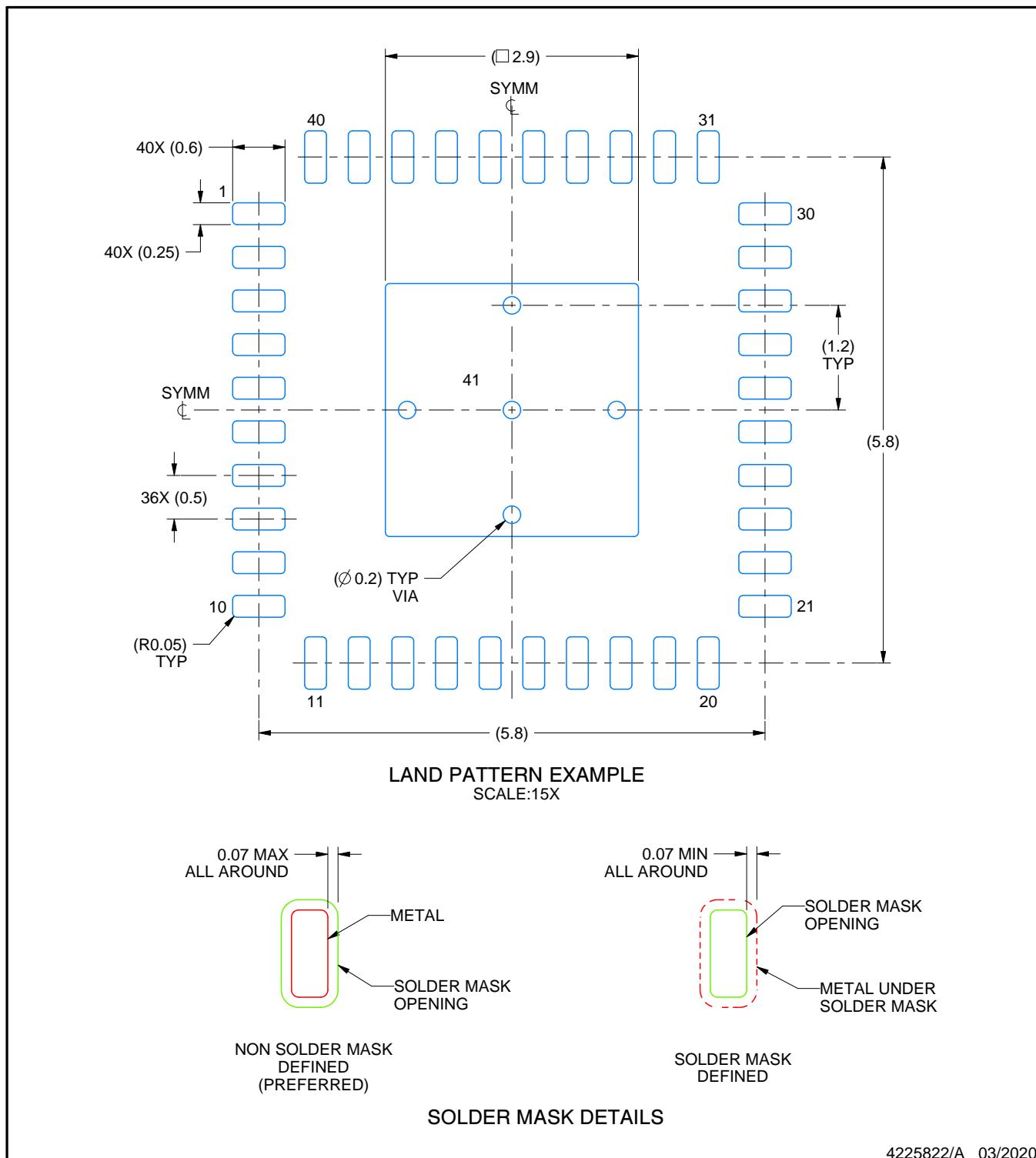

## デバイス情報

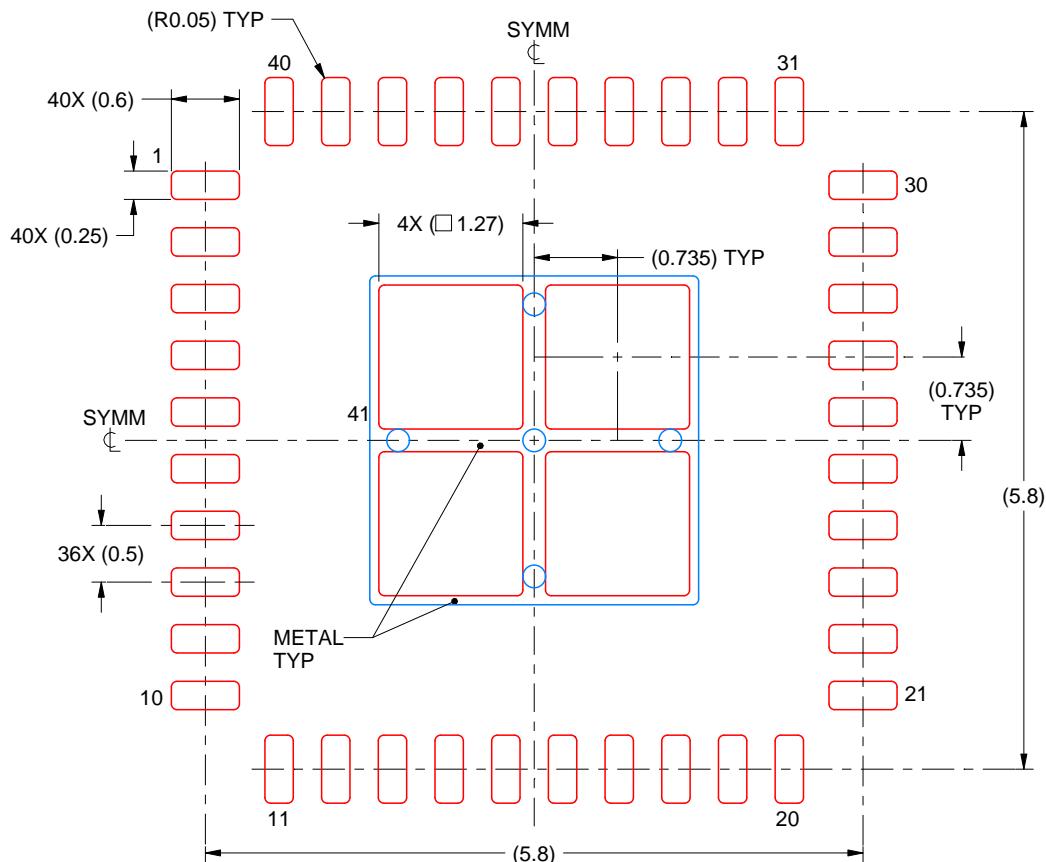

RHA

QFN-40

| TERMINAL |                  | I/O           | DESCRIPTION                                           |

|----------|------------------|---------------|-------------------------------------------------------|

| NO.      | NAME             |               |                                                       |

| 1        | CVDD             |               | Modulator side supply <sup>(1)</sup>                  |

| 2        | IN1              | Input         | Data input from Modulator 1                           |

| 3        | CLK1             | Bidirectional | Clock from/to Modulator 1                             |

| 4        | IN2              | Input         | Data input from Modulator 2                           |

| 5        | CLK2             | Bidirectional | Clock from/to Modulator 2                             |

| 6        | IN3              | Input         | Data input from Modulator 3                           |

| 7        | CLK3             | Bidirectional | Clock from/to Modulator 3                             |

| 8        | IN4              | Input         | Data input from Modulator 4                           |

| 9        | CLK4             | Bidirectional | Clock from/to Modulator 4                             |

| 10       | AVDD             |               | Signal generator supply                               |

| 11       | PWM1             | Output        | Signal generator output                               |

| 12       | PWM2             | Output        | Signal generator output (inverted)                    |

| 13       | AGND             |               | Signal generator ground                               |

| 14       | DVDD             |               | Core supply                                           |

| 15       | GND              |               | Ground                                                |

| 16       | CLK              | Input         | System clock                                          |

| 17       | SH1              | Input         | First asynchronous sample-and-hold                    |

| 18       | SH2              | Input         | Second asynchronous sample-and-hold                   |

| 19       | ACK              | Output        | Acknowledge signal                                    |

| 20       | INT              | Output        | Interrupt signal                                      |

| 21       | AD7              | Bidirectional | Data bus bit 7 (most significant bit)                 |

| 22       | AD6              | Bidirectional | Data bus bit 6                                        |

| 23       | AD5              | Bidirectional | Data bus bit 5                                        |

| 24       | AD4              | Bidirectional | Data bus bit 4                                        |

| 25       | AD3              | Bidirectional | Data bus bit 3                                        |

| 26       | AD2              | Bidirectional | Data bus bit 2                                        |

| 27       | AD1              | Bidirectional | Data bus bit 1                                        |

| 28       | AD0              | Bidirectional | Data bus bit 0 (least significant bit) <sup>(2)</sup> |

| 29       | GND              |               | Ground                                                |

| 30       | BVDD             |               | Controller side supply <sup>(3)</sup>                 |

| 31       | $\overline{WR}$  | Input         | Write signal <sup>(2)</sup>                           |

| 32       | $\overline{RD}$  | Input         | Read signal <sup>(2)</sup>                            |

| 33       | $\overline{CS}$  | Input         | Chip select signal <sup>(2)</sup>                     |

| 34       | $\overline{ALE}$ | Input         | Address latch enable <sup>(2)</sup>                   |

| 35       | M0               | Input         | First mode pin                                        |

| 36       | M1               | Input         | Second mode pin                                       |

| 37       | $\overline{RST}$ | Input         | Active-low asynchronous reset                         |

| 38       | TE               | Input         | For factory test only; must be tied to ground         |

| 39       | DVDD             |               | Core supply                                           |

| 40       | GND              |               | Ground                                                |

(1) モジュレータ側のピンは1~9です。

(2) 機能はデバイスの設定に依存します。各モードでのピンの機能/名前のリストを、表3に示します。

(3) コントローラ側のピンは16~38です。

表 1. 端子機能

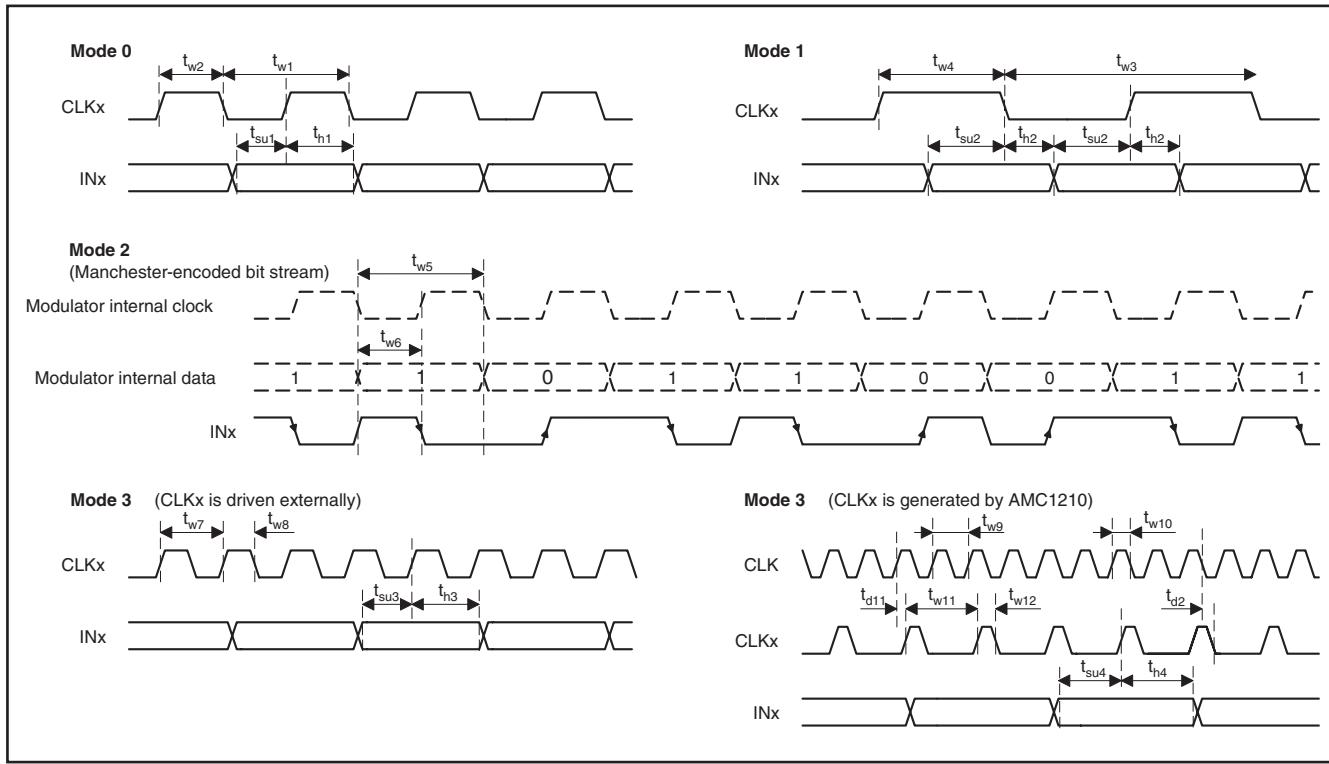

# モジュレータ入力モード

## タイミング特性

特に指定がない限り、自由通気かつ  $-40^{\circ}\text{C} \sim +85^{\circ}\text{C}$  の全温度範囲で、DVDD = +5V、CVDD = +5V、BVDD = +2.7V です。

| PARAMETER |                                                         | MIN           | MAX                                    | UNIT |

|-----------|---------------------------------------------------------|---------------|----------------------------------------|------|

| $t_{w1}$  | Mode 0 clock period CLKx                                | 45            | 1/64th of CLK period                   | ns   |

| $t_{w2}$  | Mode 0 clock high time CLKx                             | 10            | $t_{w1} - 10$                          | ns   |

| $t_{su1}$ | Setup time from data valid to CLKx high                 | 5             |                                        | ns   |

| $t_{h1}$  | Hold time from CLKx high to data invalid                | 5             |                                        | ns   |

| $t_{w3}$  | Mode 1 clock period CLKx                                | 90            | 1/128th of CLK period                  | ns   |

| $t_{w4}$  | Mode 1 clock high time CLKx                             | 20            | $t_{w3} - 10$                          | ns   |

| $t_{su2}$ | Setup time from data valid to CLKx high or low          | 5             |                                        | ns   |

| $t_{h2}$  | Hold time from CLKx high or low to data invalid         | 5             |                                        | ns   |

| $t_{w5}$  | Mode 2 data width INx                                   | 45            |                                        | ns   |

| $t_{w6}$  | Mode 2 data pulse width INx                             | 22            |                                        | ns   |

| $t_{w7}$  | Mode 3 clock period CLKx                                | 22            | 1/32nd of CLK period                   | ns   |

| $t_{w8}$  | Mode 3 clock high time CLKx                             | 5             | $t_{w7} - 5$                           | ns   |

| $t_{su3}$ | Setup time from data valid to any CLKx high             | 5             |                                        | ns   |

| $t_{h3}$  | Hold time from any CLKx high to data invalid            | 5             |                                        | ns   |

| $t_{w9}$  | System clock period CLK                                 | 11            | $10^6$                                 | ns   |

| $t_{w10}$ | System clock high time CLK                              | 3             | $t_{w9} - 3$                           | ns   |

| $t_{w11}$ | Mode 3 generated clock period CLKx                      | $t_{w9}$      | $t_{w9} \times \text{MD control bits}$ | ns   |

| $t_{w12}$ | Mode 3 generated high time CLKx                         | $t_{w10} - 2$ | $t_{w10} + 2$                          | ns   |

| $t_{d1}$  | Delay from system clock CLK high to generated CLKx high | 0             | 3                                      | ns   |

| $t_{d2}$  | Delay from system clock CLK low to generated CLKx low   | 0             | 3                                      | ns   |

| $t_{su4}$ | Setup time from data valid to any CLKx high             | 5             |                                        | ns   |

| $t_{h4}$  | Hold time from any CLKx high to data invalid            | 5             |                                        | ns   |

図 1. モジュレータ入力モードのタイミング

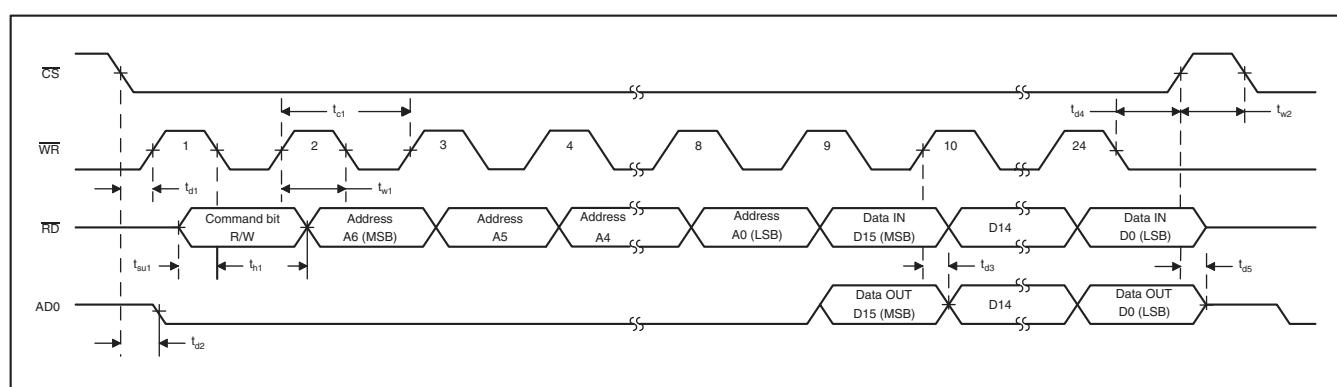

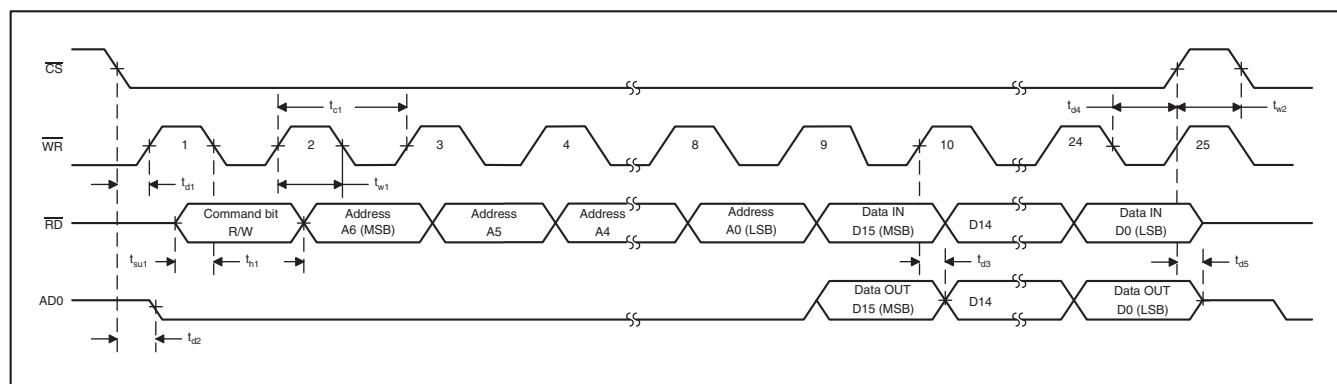

# SPI インターフェイス・モード

## タイミング特性<sup>(1)</sup>

特に指定がない限り、自由通気かつ  $-40^{\circ}\text{C} \sim +85^{\circ}\text{C}$  の全温度範囲で、DVDD = +5V、BVDD = +2.7V です。

| PARAMETER | Option 1                                       |     | Option 2 |     | UNIT |

|-----------|------------------------------------------------|-----|----------|-----|------|

|           | MIN                                            | MAX | MIN      | MAX |      |

| $t_{c1}$  | WR period                                      | 40  | 25       |     | ns   |

| $t_{w1}$  | WR HIGH or LOW time                            | 10  | 10       |     | ns   |

| $t_{d1}$  | Delay time from CS falling to WR rising edge   | 0   | 0        |     | ns   |

| $t_{d2}$  | Delay time from CS falling to ADO not tristate |     | 10       | 10  | ns   |

| $t_{su1}$ | Data setup time                                | 5   | 5        |     | ns   |

| $t_{h1}$  | Input data hold time                           | 5   | 5        |     | ns   |

| $t_{d3}$  | Output data delay time                         |     | 24       | 24  | ns   |

| $t_{d4}$  | Enable lag time                                | 10  | 10       |     | ns   |

| $t_{d5}$  | ADO disable time                               |     | 10       | 10  | ns   |

| $t_{w2}$  | Sequential transfer delay                      | 15  | 15       |     | ns   |

(1) すべての入力信号は、 $t_R = t_F = 5\text{ns}$  (BVDDの10%～90%) という条件下で規定され、 $(V_{IL} + V_{IH})/2$  という電圧レベルでタイミング測定されます。

図 2. SPI インターフェイス、オプション1-SPIの通常インターフェイス

図 3. SPI インターフェイス、オプション2-SPI 高速インターフェイス (25MHzを上回る場合)

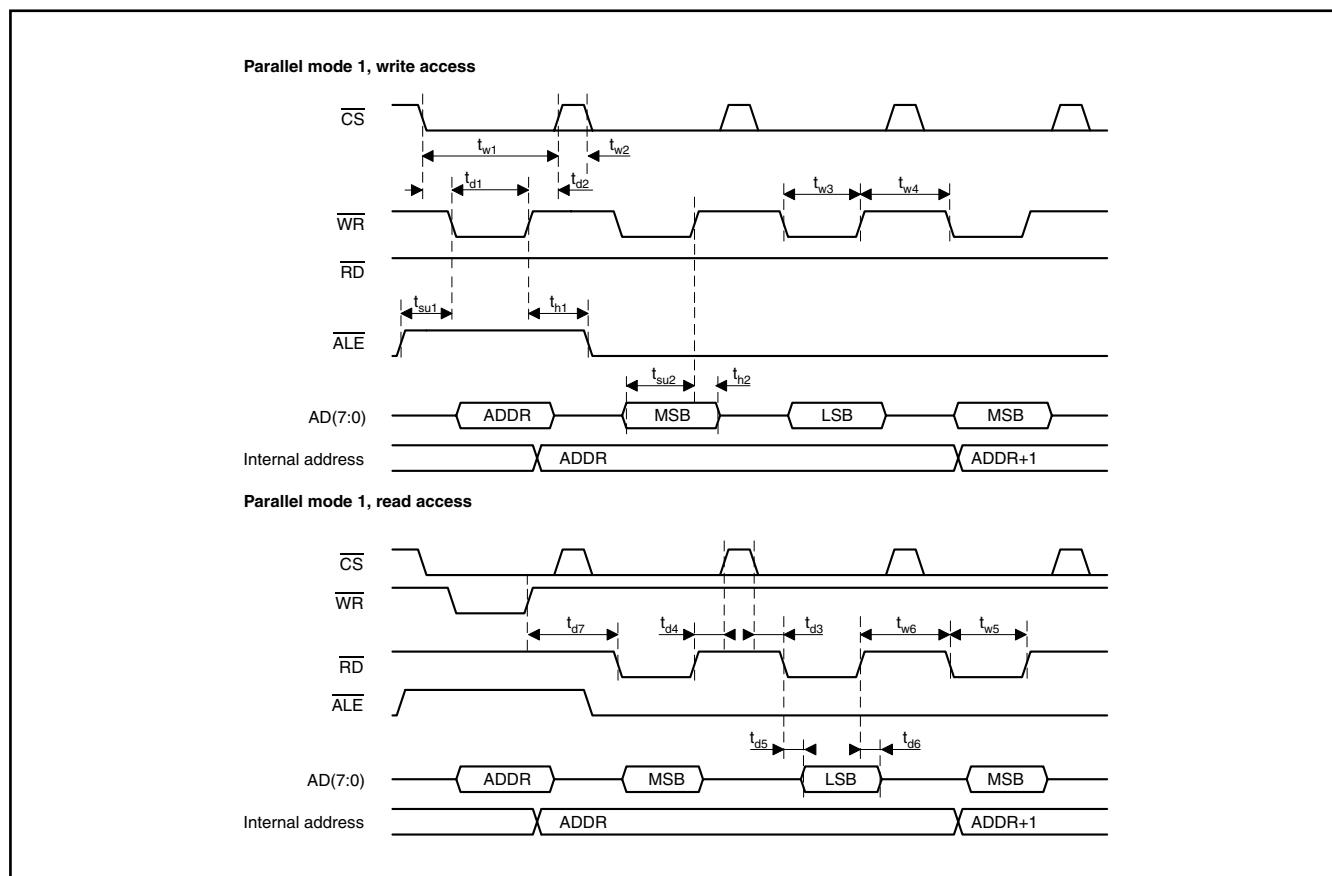

## パラレル・モード 1

### タイミング特性<sup>(1)</sup>

特に指定がない限り、自由通氣かつ  $-40^{\circ}\text{C} \sim +85^{\circ}\text{C}$  の全温度範囲で、DVDD = +5V、BVDD = +2.7V です。

| PARAMETER <sup>(2)</sup> |                                                                            | MIN | MAX | UNIT |

|--------------------------|----------------------------------------------------------------------------|-----|-----|------|

| $t_{w1}$                 | $\overline{\text{CS}}$ low width                                           | 40  |     | ns   |

| $t_{w2}$                 | $\overline{\text{CS}}$ high width                                          | 5   |     | ns   |

| $t_{d1}$                 | Delay time from $\overline{\text{CS}}$ low to $\overline{\text{WR}}$ low   | 3   |     | ns   |

| $t_{d2}$                 | Delay time from $\overline{\text{WR}}$ high to $\overline{\text{CS}}$ high | 5   |     | ns   |

| $t_{w3}$                 | $\overline{\text{WR}}$ low width                                           | 10  |     | ns   |

| $t_{w4}$                 | $\overline{\text{WR}}$ high width                                          | 10  |     | ns   |

| $t_{su1}$                | Setup time from $\overline{\text{ALE}}$ high to $\overline{\text{WR}}$ low | 0   |     | ns   |

| $t_{h1}$                 | Hold time from $\overline{\text{WR}}$ high to $\overline{\text{ALE}}$ low  | 2   |     | ns   |

| $t_{su2}$                | Setup time from address valid to $\overline{\text{WR}}$ high               | 6   |     | ns   |

| $t_{h2}$                 | Hold time from $\overline{\text{WR}}$ high to address invalid              | 5   |     | ns   |

| $t_{d3}$                 | Delay time from $\overline{\text{CS}}$ low to $\overline{\text{RD}}$ low   | 0   |     | ns   |

| $t_{d4}$                 | Delay time from $\overline{\text{RD}}$ high to $\overline{\text{CS}}$ high | 6   |     | ns   |

| $t_{w5}$                 | $\overline{\text{RD}}$ low width                                           | 30  |     | ns   |

| $t_{w6}$                 | $\overline{\text{RD}}$ high width                                          | 13  |     | ns   |

| $t_{d5}$                 | Delay time from $\overline{\text{RD}}$ low to data valid                   |     | 30  | ns   |

| $t_{d6}$                 | Delay time from $\overline{\text{RD}}$ high to databus in tristate         | 0   | 10  | ns   |

| $t_{d7}$                 | Delay time from $\overline{\text{WR}}$ high to $\overline{\text{RD}}$ low  | 10  |     | ns   |

(1) すべての入力信号は、 $t_R = t_F = 5\text{ns}$  (BVDD の 10%~90%) という条件下で規定され、 $(V_{IL} + V_{IH})/2$  という電圧レベルでタイミング測定されます。

(2)  $\overline{\text{WR}}$  と  $\overline{\text{RD}}$  の各パルスの間も  $\overline{\text{CS}}$  が "L" レベルにとどまる場合は、 $t_{w2}$  は適用されません。

図 4. パラレル・モード1のタイミング

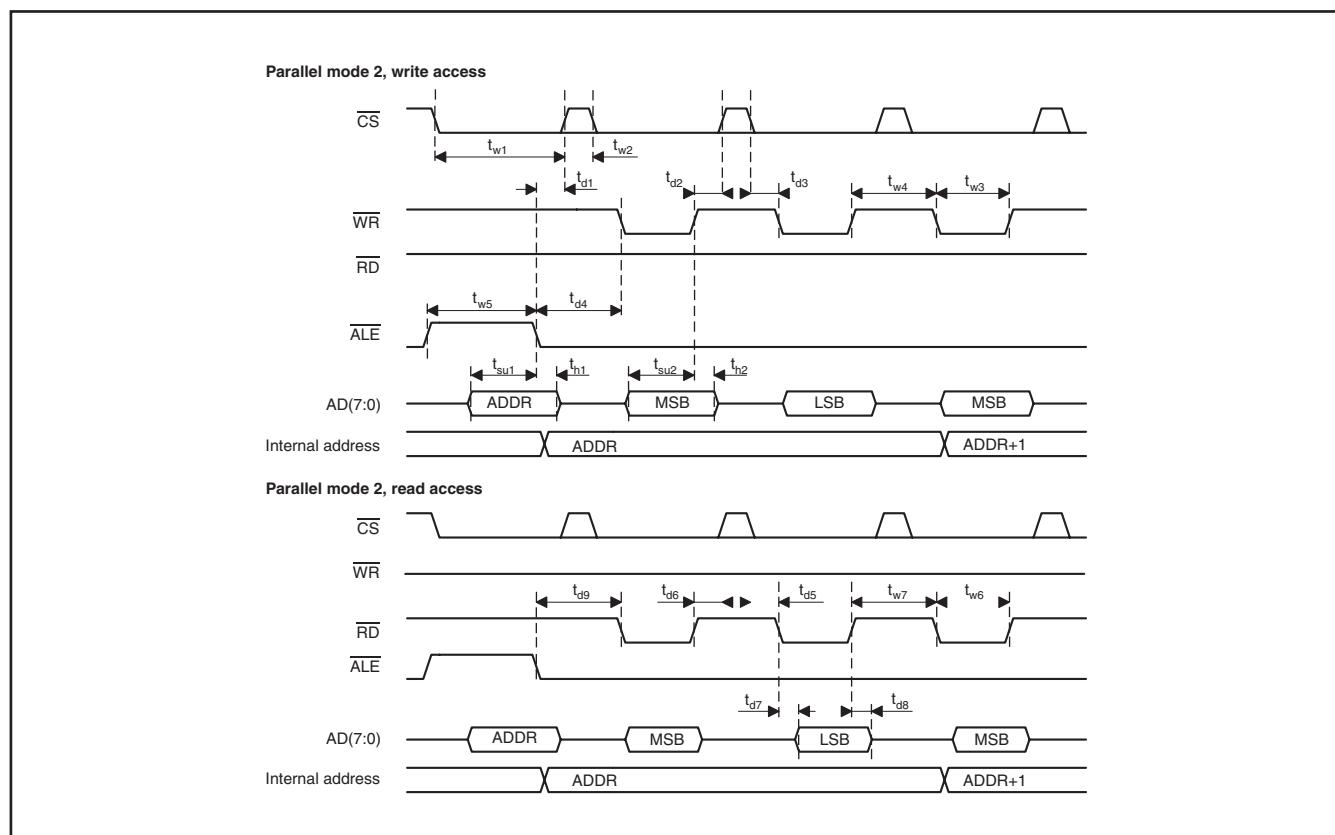

## パラレル・モード2

### タイミング特性<sup>(1)</sup>

特に指定がない限り、自由通気かつ $-40^{\circ}\text{C} \sim +85^{\circ}\text{C}$  の全温度範囲で、DVDD = +5V、BVDD = +2.7V です。

| PARAMETER <sup>(2)</sup> |                                                                            | MIN | MAX | UNIT |

|--------------------------|----------------------------------------------------------------------------|-----|-----|------|

| $t_{w1}$                 | $\overline{\text{CS}}$ low width                                           | 40  |     | ns   |

| $t_{w2}$                 | $\overline{\text{CS}}$ high width                                          | 5   |     | ns   |

| $t_{d1}$                 | Delay time from $\overline{\text{ALE}}$ low to $\overline{\text{CS}}$ high | 5   |     | ns   |

| $t_{d2}$                 | Delay time from $\overline{\text{WR}}$ high to $\overline{\text{CS}}$ high | 5   |     | ns   |

| $t_{d3}$                 | Delay time from $\overline{\text{CS}}$ low to $\overline{\text{WR}}$ low   | 3   |     | ns   |

| $t_{w3}$                 | $\overline{\text{WR}}$ low width                                           | 10  |     | ns   |

| $t_{w4}$                 | $\overline{\text{WR}}$ high width                                          | 10  |     | ns   |

| $t_{w5}$                 | $\overline{\text{ALE}}$ high width                                         | 10  |     | ns   |

| $t_{d4}$                 | Delay time from $\overline{\text{ALE}}$ low to $\overline{\text{WR}}$ low  | 10  |     | ns   |

| $t_{su1}$                | Setup time from address valid to $\overline{\text{ALE}}$ low               | 6   |     | ns   |

| $t_{h1}$                 | Hold time from $\overline{\text{ALE}}$ low to address invalid              | 5   |     | ns   |

| $t_{d5}$                 | Delay time from $\overline{\text{CS}}$ low to $\overline{\text{RD}}$ low   | 0   |     | ns   |

| $t_{su2}$                | Setup time from data valid to $\overline{\text{WR}}$ high                  | 6   |     | ns   |

| $t_{h2}$                 | Hold time from $\overline{\text{WR}}$ high to data invalid                 | 5   |     | ns   |

| $t_{d6}$                 | Delay time from $\overline{\text{RD}}$ high to $\overline{\text{CS}}$ high | 6   |     | ns   |

| $t_{w6}$                 | $\overline{\text{RD}}$ low width                                           | 30  |     | ns   |

| $t_{w7}$                 | $\overline{\text{RD}}$ high width                                          | 13  |     | ns   |

| $t_{d7}$                 | Delay time from $\overline{\text{RD}}$ low to data valid                   | 30  |     | ns   |

| $t_{d8}$                 | Delay time from $\overline{\text{RD}}$ high to databus in tristate         | 0   | 10  | ns   |

| $t_{d9}$                 | Delay time from $\overline{\text{ALE}}$ low to $\overline{\text{RD}}$ low  | 10  |     | ns   |

(1) すべての入力信号は、 $t_R = t_F = 5\text{ns}$  (BVDD の 10%~90%) という条件下で規定され、 $(V_{IL} + V_{IH})/2$  という電圧レベルでタイミング測定されます。

(2)  $\overline{\text{WR}}$ 、 $\overline{\text{RD}}$ 、 $\overline{\text{ALE}}$  の各パルスの間も  $\overline{\text{CS}}$  が "L" レベルにとどまる場合は、 $t_{w2}$  は適用されません。

図 5. パラレル・モード2のタイミング

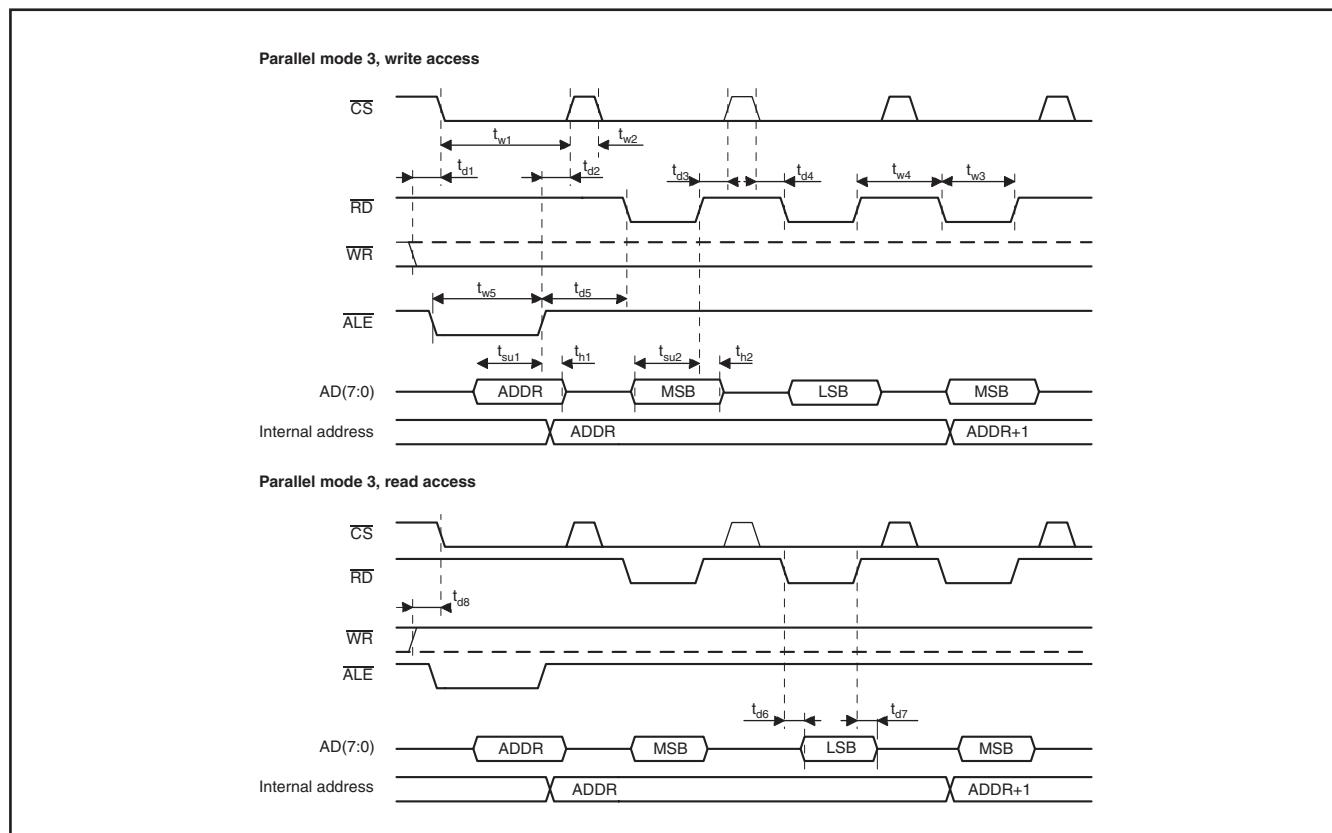

## パラレル・モード3

### タイミング特性<sup>(1)</sup>

特に指定がない限り、自由通氣かつ $-40^{\circ}\text{C} \sim +85^{\circ}\text{C}$  の全温度範囲で、DVDD = +5V、BVDD = +2.7V です。

| PARAMETER <sup>(2)</sup> |                                                | MIN | MAX | UNIT |

|--------------------------|------------------------------------------------|-----|-----|------|

| $t_{w1}$                 | CS low width                                   | 40  |     | ns   |

| $t_{w2}$                 | CS high width                                  | 5   |     | ns   |

| $t_{d1}$                 | Delay time from WR low to CS low               | 5   |     | ns   |

| $t_{d2}$                 | Delay time from ALE high to CS high            | 5   |     | ns   |

| $t_{d3}$                 | Delay time from RD high to CS high             | 5   |     | ns   |

| $t_{d4}$                 | Delay time from CS low to RD low               | 3   |     | ns   |

| $t_{w3}$                 | RD low width                                   | 10  |     | ns   |

| $t_{w4}$                 | RD high width                                  | 30  |     | ns   |

| $t_{w5}$                 | ALE low width                                  | 6   |     | ns   |

| $t_{d5}$                 | Delay time from ALE high to RD low             | 10  |     | ns   |

| $t_{su1}$                | Setup time from address valid to ALE high      | 5   |     | ns   |

| $t_{h1}$                 | Hold time from ALE high to address invalid     | 5   |     | ns   |

| $t_{su2}$                | Setup time from data valid to RD high          | 5   |     | ns   |

| $t_{h2}$                 | Hold time from RD high to data invalid         | 5   |     | ns   |

| $t_{d6}$                 | Delay time from RD low to data valid           |     | 30  | ns   |

| $t_{d7}$                 | Delay time from RD high to databus in tristate | 0   | 10  | ns   |

| $t_{d8}$                 | Delay time from WR high to CS low              | 5   |     | ns   |

(1) すべての入力信号は、 $t_R = t_F = 5\text{ns}$  (BVDD の 10%~90%) という条件下で規定され、 $(V_{IL} + V_{IH})/2$  という電圧レベルでタイミング測定されます。

(2) RD と ALE の各パルスの間も CS が "L" レベルにとどまる場合は、 $t_{w2}$  は適用されません。

図 6. パラレル・モード3のタイミング

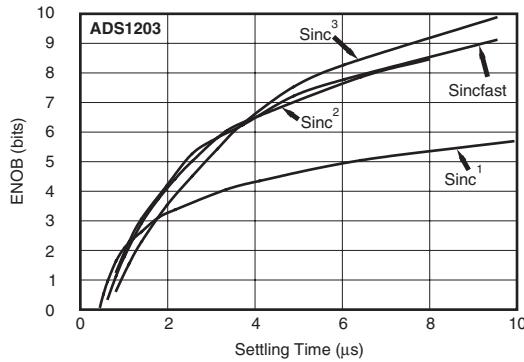

## 代表的特性

特に指定がない限り、 $-40^{\circ}\text{C} \sim +85^{\circ}\text{C}$  の範囲で、AVDD、CVDD、DVDD =  $+5\text{V}$ 、BVDD =  $+2.7\text{V}$  です。

各電圧に関して、次の条件が成立していることが必要です。CVDD  $\geq$  DVDD  $\geq$  BVDD。

図 7

図 8

図 9

図 10

図 11

# THEORY OF OPERATION

## 概要

AMC1210は、柔軟性の高いデジタル・フィルタ・デバイスであり、モーター制御アプリケーションに特化して設計されたものです。デジタル処理ブロックに4つの独立したデジタル・フィルタを内蔵し、SPIバス、または8ビットのマルチプレックス・パラレルI/Oを使用して通信することができます。各データストリーム入力は、外部クロック、またはデルタ-シグマ・モジュレータから供給されるクロックを使用して、クロック同期することができます。時間測定単位を指定できるので、サンプリングの速度とデータ収集をソフトウェアからモニタし、包括的に制御できます。また割り込みユニットがあるので、AMC1210の状態をリアルタイム・モニタすることができます。デジタル・コンパレータ・ユニットが用意されているので、さまざまなデータストリームに対してプログラム可能なピーク条件のアラートを発行できます。電流測定アプリケーションで使用する場合は、デジタル・コンパレータ・ユニットを使用して、過電流または電流不足の状況に対してアラートを発行できます。

## インターフェイス・モジュール

AMC1210は、4つの異なるインターフェイス・モードを使用して、デジタル・シグナル・プロセッサ(DSP)またはマイクロコントローラ( $\mu$ C)と通信することができます。1つのシリアル・モードと、3つの8ビット・マルチプレックス・パラレル・モードです。シリアル・モードは標準的なSPIモードであり、通常は24ビット転送を行います。マルチプレックス・パラレル・モードは、広い範囲のコントローラと組み合わせて動作させるために設計されたものです。モード・ピンであるM0とM1は、モード選択を決定します。表2に、デジタル・インターフェイスの構成を示します。

デジタル・インターフェイス・ピンは、インターフェイス・モードによって、異なる機能を果たします。表3に、さまざまなモードでのピンの動作を示します。

| INTERFACE MODES | PIN M1 | PIN M0 |

|-----------------|--------|--------|

| SPI             | 0      | 0      |

| Parallel Mode 1 | 0      | 1      |

| Parallel Mode 2 | 1      | 0      |

| Parallel Mode 3 | 1      | 1      |

表2. デジタル・インターフェイスの構成

| PIN | SPI MODE     | PARALLEL MODE 1     | PARALLEL MODE 2      | PARALLEL MODE 3 |

|-----|--------------|---------------------|----------------------|-----------------|

| M1  | 0            | 0                   | 1                    | 1               |

| M0  | 0            | 1                   | 0                    | 1               |

| ALE | —            | Address/Data Select | Address Latch Enable | Address Valid   |

| CS  | Frame sync   | Chip Select         | Chip Select          | Chip Select     |

| RD  | SPI Data In  | Read                | Read                 | Strobe          |

| WR  | SPI Clock    | Write               | Write                | Read/Write      |

| AD0 | SPI Data Out | Databus 0 (LSB)     | Databus 0 (LSB)      | Databus 0 (LSB) |

| AD1 | —            | Databus 1           | Databus 1            | Databus 1       |

| AD2 | —            | Databus 2           | Databus 2            | Databus 2       |

| AD3 | —            | Databus 3           | Databus 3            | Databus 3       |

| AD4 | —            | Databus 4           | Databus 4            | Databus 4       |

| AD5 | —            | Databus 5           | Databus 5            | Databus 5       |

| AD6 | —            | Databus 6           | Databus 6            | Databus 6       |

| AD7 | —            | Databus 7 (MSB)     | Databus 7 (MSB)      | Databus 7 (MSB) |

表3. さまざまなコミュニケーション・モードでのピンの機能

| MODULE/UNIT                | FEATURE                                 | CLOCK FUNCTION                                                          |

|----------------------------|-----------------------------------------|-------------------------------------------------------------------------|

| Interface/Signal Generator | Signal generator                        | Determines output data rate                                             |

| Filter/Input Control       | Manchester Decoder in control unit      | Allows decoding of Manchester data                                      |

|                            | CLKx signal in control unit             | Provides timing for CLKx pin when bit CD in the control parameter = '1' |

|                            | Clock dividers for CLKx in control unit | Divides CLKx speed                                                      |

|                            | Modulator failure detection             | Allows AMC1210 to monitor input clock CLKx                              |

| Filter/Time Measurement    | Time measurement                        | TMU counts number of CLK cycles when TM = 0                             |

表4. CLK ピンの機能

## クロックの設定

クロック・ピンであるCLKは、いくつかの機能のタイミングを制御します。表4に、CLK信号を使用してタイミングを調整するユニットと機能を示します。この表の中にある機能がどれも必要でない場合は、電流消費の増加を防止するために、CLKピンをGNDに接続してください。

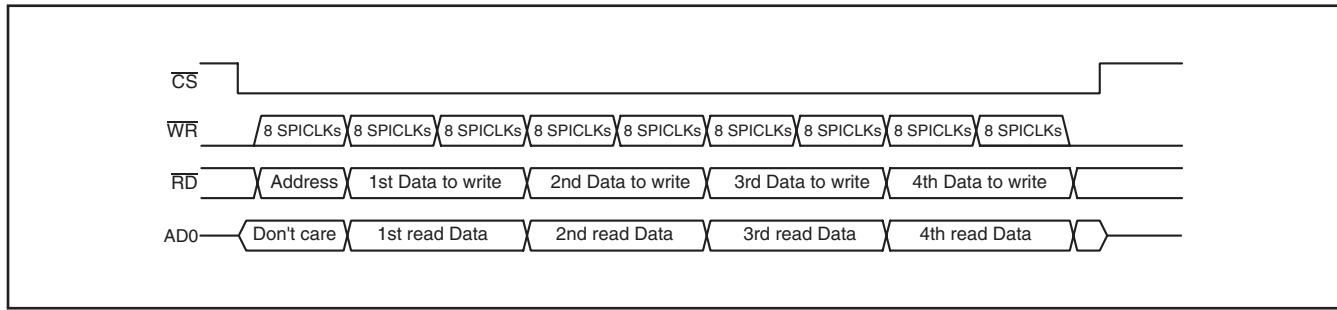

## SPIモード

SPIインターフェイスは、システムの他の部分とは完全に非同期で動作します。SPIインターフェイスには、 $\overline{WR}$ 、 $\overline{RD}$ 、AD0、および $\overline{CS}$ という4つの信号があります。SPIインターフェイスの最大速度は40MHzです。選択信号である $\overline{CS}$ が“H”レベルの場合、AddressとData Registerを除き、SPIインターフェイス全体がリセット状態になります。 $\overline{CS}$ が“H”レベルである間は、SPIのクロックである $\overline{WR}$ と、シリアル・データ入力である $\overline{RD}$ は無効になります。受信データは $\overline{WR}$ の立ち下がりエッジで、SPIインターフェイスによってストローブされます。送信データは $\overline{WR}$ の立ち上がりエッジで、出力AD0に書き込まれます（「SPIインターフェイス・モード」を参照）。16ビットから成る1ワードを伝送するには、24ビットが必要です。AMC1210が最初に受信する1ビットは、伝送全体が読み取りまたは書き込みのいずれかの動作であること決定します。“H”レベルのビットは読み取り動作、“L”レベルのビットは書き込み動作を表します。その後に、7ビットのアドレス・ビットが続きます。アドレス・ビットの後に、表5に示すシーケンスに従って16ビットのデータ・ビットが送信または受信されます。

## SPIオプション1

SPIオプション1では、1回の16ビット传送は次の方法で実施されます。

1.  $\overline{WR}$ の最初の立ち下がりエッジで、読み取り/書き込みビットがストロークされます。

2.  $\overline{WR}$ の2回目の立ち下がりエッジで、アドレスのMSB(最上位ビット、つまりビット6)がストロークされます。

3.  $\overline{WR}$ の8回目の立ち下がりビットで、アドレスのLSB(最下位ビット、つまりビット0)がストロークされ、レジスタ・マップのうち、対応するデータが読み取られます。

4. 9回目の立ち上がりエッジ(MSB)で、レジスタ・マップから読み取られたデータはシフト・レジスタの中にラッチされ、 $\overline{WR}$ の立ち上がりエッジのたびに1ビットがシフトされます。速度が25MHz未満の場合は、次の立ち下がりエッジ(オプション1)で読み取りを行うことをお勧めします。書き込み動作が実行されている場合でも、このデータは必ず外部に対して送信されます。

5.  $\overline{WR}$ の24回目の立ち下がりエッジ(LSB)で、最後のデータ・ビットが $\overline{RD}$ からシフト・インし、書き込み動作が実行されている場合はデータをレジスタ・マップに書き込むための書き込みパルスが生成されます。

図2と図3に、このSPIモードに関する詳細なタイミング情報を示します。

|     |         |     |     |     |     |     |     |     |            |     |     |     |      |     |    |    |    |    |    |    |    |    |    |           |

|-----|---------|-----|-----|-----|-----|-----|-----|-----|------------|-----|-----|-----|------|-----|----|----|----|----|----|----|----|----|----|-----------|

| A24 | A23     | A22 | A21 | A20 | A19 | A18 | A17 | A16 | MSB<br>A15 | A14 | A13 | A12 | A11  | A10 | A9 | A8 | A7 | A6 | A5 | A4 | A3 | A2 | A1 | LSB<br>A0 |

| R/W | Address |     |     |     |     |     |     |     |            |     |     |     | Data |     |    |    |    |    |    |    |    |    |    |           |

表5. SPI書き込み時の24ビット・ワードのフォーマット

図12. シリアル通信の代表的な動作

連続的な読み取りまたは書き込みを行っている間は、各読み取りまたは各書き込みの後にアドレスがインクリメントします。アドレスが7Fhに達した時点で、アドレス・カウンタは再び0から始まります。各データ・ワードの16番目に相当するWRの時点で、データはレジスタ・マップに書き込まれます。データ・ワードのうち16番目に相当するWRより前の時点で、CSがインアクティブであった場合、データはレジスタ・マップに書き込まれません。そのデータは失われます。図12に、この機能の代表的な例を示します。

## SPIオプション2

SPIオプション2は、クロック・スピードが25MHzを上回る場合に推奨されます。オプション1とオプション2の唯一の違いは、出力データをストローブするエッジです。オプション2では、レジスタ・マップからデータをラッチした後、立ち上がりエッジでユーザーがデータを読み取る必要があります(オプション1に比べると、1.5クロック・サイクル後)。この場合は、余分のクロック・サイクルが必要になります(24ではなく、25クロック・サイクル)。図3のタイミング図を参照してください。

## パラレル・モード1

パラレル・モード1では、ホスト・ポートはWRとRDを使用し、AMC1210への書き込みアクセスと読み取りアクセスを独立して実行します。電流サイクルは、AMC1210のCS入力が“L”レベルである間にのみ処理されます。RDは、AMC1210に対して、ホスト・プロセッサがデータ伝送を要求したことを知らせます。その後、AMC1210はデータをホストに出力します。

AMC1210の中にあるレジスタを構成するために、ホスト・プロセスはWR信号を発行し、有効なデータがバスで利用できることを知らせます。WRの立ち上がりエッジで、このデータはAMC1210の中にラッチされます。AMC1210に対して指定するアドレスは、WRの最初の立ち上がりエッジの時点で有効になっている必要があります。アドレスが発行されたことを知らせるには、WR信号を“L”に設定する前に、信号ALEを“H”に設定する必要があります。書き込みまたは読み取りを2回連続して実行する場合は、その間、CS信号を“L”レベルにとどめておくこともできます。

図4に、パラレル・モード1の詳細なタイミング図を示します。

## パラレル・モード2

パラレル・モード2では、ホスト・ポートはWRとRDを使用し、AMC1210への書き込みアクセスと読み取りアクセスを独立して実行します。電流サイクルは、AMC1210のCS入力が“L”レベルである間にのみ処理されます。RDは、AMC1210に対して、ホスト・プロセッサがデータ伝送を要求したことを知らせます。その後、AMC1210はデータをホストに出力します。

AMC1210のレジスタを構成するために、ホスト・プロセスはWR信号を発行し、有効なデータがバスで利用できることを知らせます。WRの立ち上がりエッジで、このデータはAMC1210の中にラッチされます。信号ALEを“L”レベルに設定する時点で、アドレスはAMC1210の中にラッチされます。書き込みまたは読み取りを2回連続して実行する場合は、その間、CS信号を“L”レベルにとどめておくこともできます。

図5に、パラレル・モード2の詳細なタイミング図を示します。

## パラレル・モード3

パラレル・モード3では、ホスト・ポートは $\overline{RD}$ と $\overline{WR}$ を使用し、AMC1210への書き込みアクセスと読み取りアクセスを実行します。電流サイクルは、AMC1210のCS入力が“L”レベルである間にのみ処理されます。 $\overline{WR}$ は、AMC1210に対して、ホスト・プロセッサが読み取り伝送または書き込み伝送を開始したことを知らせます。 $\overline{WR}$ が“H”レベルであり、 $\overline{RD}$ が“L”レベルである場合は、AMC1210はデータをホストに出力します。

AMC1210の中にあるレジスタを構成するために、ホスト・プロセスは $\overline{RD}$ 信号を発行し、同時に $\overline{WR}$ を“L”レベルに設定して、有効なデータがバスで利用できることを知らせます。 $\overline{RD}$ 信号の立ち上がりエッジで、このデータはAMC1210の中にラッチされます。信号 $\overline{ALE}$ を“H”レベルに設定する時点で、アドレスはAMC1210の中にラッチされます。書き込みまたは読み取りを2回連続して実行する場合は、その間、 $\overline{CS}$ 信号を“L”レベルにとどめておくこともできます。

図6に、パラレル・モード3の詳細なタイミング図を示します。

どのパラレル・モードでも、AMC1210に新しいアドレスを書き込むことなく、各アドレスをシーケンシャル・アクセスすることもできます。ユーザーがアドレスを設定した場合、ポインタもそのアドレスを指すように設定されます。連続した読み取りまたは書き込み操作を実行する場合は、各操作が終わるごとに、レジスタ・マップの中でアドレスが1インクリメントします。

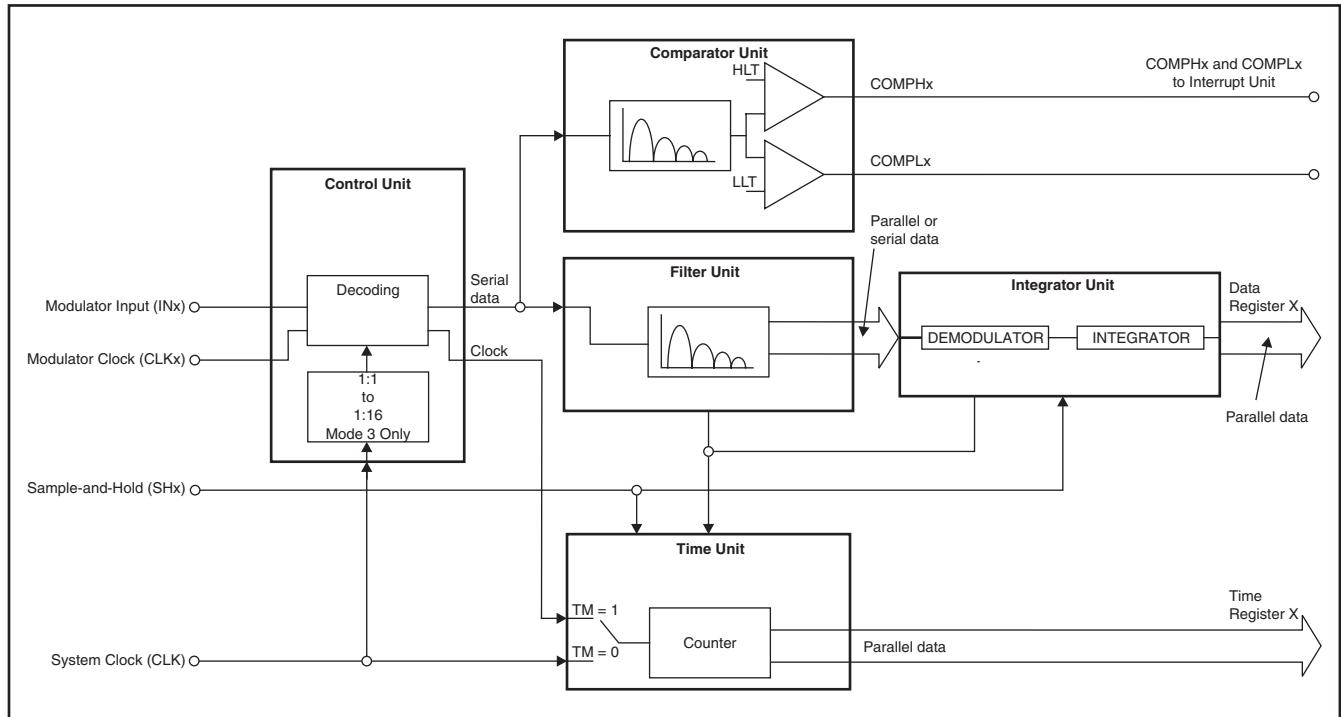

## フィルタ・モジュール

フィルタ・モジュールは、制御ブロック・ユニット、コンパレータ・フィルタ・ユニット、sincフィルタ・ユニット、時間測定ユニット、およびデモジュレータ/インテグレータ・ユニットによって形成されています。各ユニットは、個別にプログラムして、いくつかの異なる動作モードに設定することができます。図13に、1つのフィルタ・モジュールのブロック図を示します。4つのフィルタ・モジュールは互いに同一であり、それぞれ独立して構成できます。

図 13. AMC1210 のフィルタ・モジュール

| MODULATOR MODE | MOD1 | MOD0 | DESCRIPTION                                                                                                                                        |

|----------------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 0              | 0    | 0    | The modulator clock is running with the modulator data rate. The modulator data is strobed at every rising edge of the modulator clock.            |

| 1              | 0    | 1    | The modulator clock is running with half of the modulator data rate. The modulator data is strobed at every edge of the modulator clock.           |

| 2              | 1    | 0    | The modulator clock is off and the modulator data is Manchester-encoded.                                                                           |

| 3              | 1    | 1    | The modulator clock is running with double of the modulator data rate. The modulator data is strobed at every other positive modulator clock edge. |

表 6. インターフェイス・モード

## 制御ユニット

制御ユニットは、モジュレータの入力データとそれに対応するクロックを変換し、AMC1210がそれらを使用できるようにします。モジュレータのモードに応じて、4つの入力オプションが使用できます。これらのオプションを選択するには、制御パラメータ・レジスタのMOD1およびMOD0という各ビットを使用します。表6に、各入力モードを示します。これらの各モジュールの詳細なタイミング図は、「タイミング特性」セクションに示しています。図1を参照してください。

モジュレータ・モード2では、データはマンチェスター(Manchester)符号化されます。最適なデコード・パフォーマンスを達成するために、自動キャリブレーションが継続して実行されます。このキャリブレーションの状態は、制御パラメータ・レジスタのビットMS10～MS0、およびステータス・レジスタのビットMALxとMAFxによって確認できます。このモードでは、クロック入力CLKxは無視されます。

## 入力クロック

フィルタ・モジュールのクロックは、システム・クロックとは分離されています（モジュレータ・モード3を使用する場合を除く）。この設計により、フィルタ・モジュールは制御モジュール

とは非同期に動作できるので、入力データと制御ブロックのタイミングに関して、2つの異なる速度を使用できます。クロックの設定は、入力モードごとに異なります。表7を参照してください。

入力データがクロックに正しく同期されている限り、フィルタ・モジュールのすべての機能(sinc フィルタ・ユニット、コンバーティ・ユニットなど)は、同じレートでクロックに同期されます。

## マンチェスター・デコーダ

信号のマンチェスター符号化とは、データ信号を符号化する手法の1つであり、個別のクロック・ラインを使用することなくデータ信号を取得できることが特徴です。モード2で構成した場合、AMC1210はINxピンに供給された、マンチェスター符号化された信号を変換し、クロック信号とデータ信号を取得できます。データのデコードを最適化するために、自動キャリブレーションが継続して実行されます。

| INPUT MODE | CLOCK FUNCTIONALITY                                                                                                                                                                                                                                                                                                 |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0          | The clock for the filter module is fed by the CLKx input, which can be either external or driven by the modulator. The frequency is the same.                                                                                                                                                                       |

| 1          | Each edge of CLKx generates a pulse, which clocks the filter module.                                                                                                                                                                                                                                                |

| 2          | The clock for the filter module is generated by the Manchester decoder.                                                                                                                                                                                                                                             |

| 3          | The clock source is the system clock, from the CLK pin. This clock can be divided down by a programmed number between 1 and 8 by bits MD2-MD0 in the Clock Divider Register. This clock can also be fed to the CLKx pin to drive the modulator clock if the bit CD in the Control Parameter Register is set to '1'. |

表 7. 各インターフェイス・モードでのクロックの動作

| VALUE      | 0    | 0   | 0   | 1   | 1   | 0   | 0   | 1   | 1   | 0   | 0   |

|------------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| BIT        | MS10 | MS9 | MS8 | MS7 | MS6 | MS5 | MS4 | MS3 | MS2 | MS1 | MS0 |

| CLK CYCLES | 11   | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   |

表8. 制御パラメータ・レジスタの例

キャリブレーションのメカニズムは、次のシーケンスに従います。

- モジュレータのデータを、システム・クロック(CLK)と同じ周波数でサンプリングします。

- 遷移から次の遷移までのCLKサイクルの数をカウントし、1,024回の連続した遷移に関してこれを記録します。

- その結果得られた配列では、遷移と遷移の間でカウントされたCLKサイクルの数に対応するビット位置に“1”を書き込みます。たとえば、表8に示すシーケンスでは、3と4、および7と8で少なくとも1つの書き込みが実施されたことを意味し、遷移と遷移の間で発生したCLKサイクルを表しています。この配列は、制御パラメータ・レジスタのMS10-MS0というビットの中に保存されます。

- アルゴリズムは、“1”と“1”的間にさまれた、一連の“0”を検索します。そのパターンが見つからなかった場合は、ステータス・レジスタの中にあるMALxおよびMAFxという各ビットが“H”レベルに設定されます。

- このアルゴリズムが成功した場合、このアルゴリズムは最初の“0”的場所を、周波数を決定したり、マンチェスター符号の中でどの遷移が有効なのか決定したりするために必要なCLKサイクルの数として使用します。

- このアルゴリズムは、ステップ2から自動的に再開されます。

MALxビットは、マンチェスター・デコーダにおける直前のキャリブレーション・サイクルの状態を表します。このビットが“H”レベルである場合、直前のキャリブレーション・サイクルで、デコーダのキャリブレーションは失敗しています。MAFxビットは、ステータス・レジスタの最後の読み取り以降に失敗が発生したかどうかを示します。MALxで失敗が発生した場合は、MAFxが“H”レベルになります。ステータス・レジスタが読み取られた時点で、MAFxはリセットされて“L”レベルになります。

AMC1210がモジュレータ・モード2として構成されている場合、デコード手順は継続して実行されます。デコーダを正しく動作させるには、CLK周波数はマンチェスター・データ・レートの少なくとも6倍である必要があります。

## コンパレータ・ユニット

独立したコンパレータ・ユニットにより、ユーザーは入力測定分解能を犠牲にすることなく、高速なセトリングタイムを指定して入力条件をモニタできます。コンパレータ・ユニットのフィルタはsincフィルタ・ユニットに似ていて、OSRは1~32の範囲にある連続した値のいずれかを取ります。OSRを32に設定した場合は、32,768の幅に相当する15ビットという最大の出力を実現できます。フィルタの出力は、プログラムされた2つのスレッシュホールド・レベルと比較され、値を上回る状況、または値を下回る状況が検出されます。これらのスレッシュホールド・レベルは、個別のフィルタ・モジュールごとに、スレッシュホールド・レジスタの“H”レベルと“L”レベルを介してプログラムするものです。値を上回る状況、または値を下回る状況が発生した場合、コンパレータ・ユニットは割り込みユニットに対して信号を送信し、割り込み信号を設定し、その状況を割り込みレジスタに保存するよう指示します。次に、割り込みレジスタがポーリングされ、割り込み信号を発生させた状況が調査されます。コンパレータ・フィルタの値を読み取ることはできません。

このフィルタは、コンパレータと組み合わされ、一般的には過電流を検出する目的で使用されます。希望の分解能/セトリングタイムの組み合わせを達成するために、OSRを決定する必要があります。このプログラミングについては、「アプリケーション情報」のセクションで詳細に説明します。

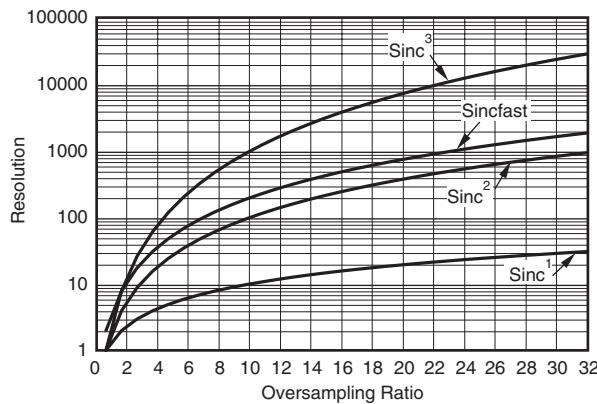

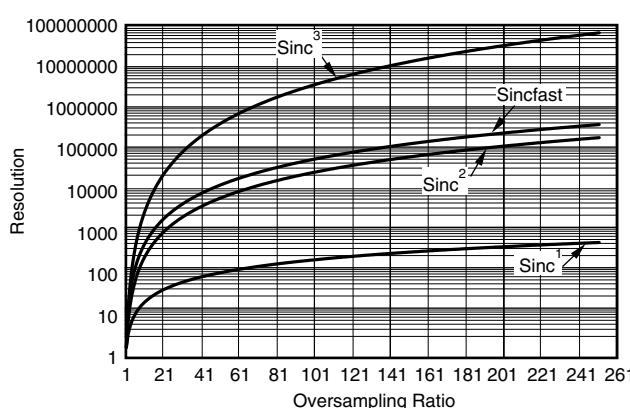

コンパレータ・フィルタ・ユニットとsincフィルタ・ユニットは、入力データの処理方法が異なります。コンパレータ・フィルタ・ユニットは、“L”レベルの入力信号を“0”、“H”レベルの入力信号を“1”に変換します。それに対して、sincフィルタ・ユニットは“-1”と“1”を使用します。その計算の結果、コンパレータ・フィルタの出力は必ず正の値になります。データの表現形式は、ストレートバイナリ形式です。表9と図14に、コンパレータがさまざまなオーバーサンプリング比を使用したときに保存できる、さまざまなフルスケールの値を示します。

| OSR | Sinc <sup>1</sup> | Sinc <sup>2</sup>   | Sinc <sup>3</sup>   | Sincfast             |

|-----|-------------------|---------------------|---------------------|----------------------|

| x   | 0 to x            | 0 to x <sup>2</sup> | 0 to x <sup>3</sup> | 0 to 2x <sup>2</sup> |

| 4   | 0 to 4            | 0 to 16             | 0 to 64             | 0 to 32              |

| 8   | 0 to 8            | 0 to 64             | 0 to 512            | 0 to 128             |

| 16  | 0 to 16           | 0 to 256            | 0 to 4096           | 0 to 512             |

| 32  | 0 to 32           | 0 to 1024           | 0 to 32,768         | 0 to 2048            |

表9. さまざまなOSR/フィルタの組み合わせによるピーク・データ値

図 14. コンパレータ・フィルタの分解能

最大分解能は、表9に示したピーク値を実現します(2進数で15ビット、10進数で32,768)。最大値を実現するには、デルタシグマ・モジュレータを正または負の絶対最大フルスケールで動作させることに注意してください。これは、ほとんどのデルタシグマ・モジュレータでの推奨フルスケールの80%という範囲を超えるものです。

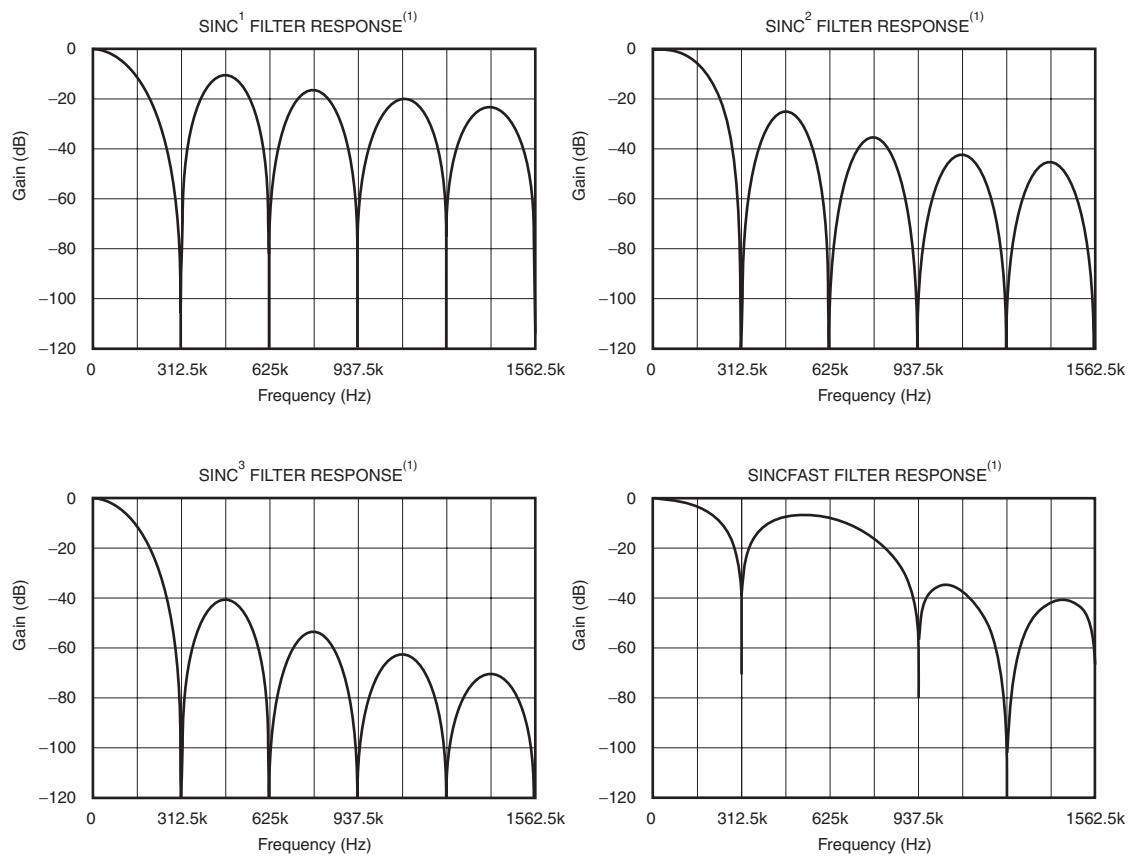

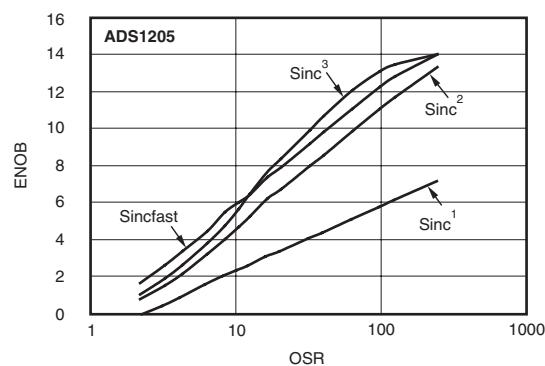

### Sinc フィルタ・ユニット

AMC1210は、標準的な積分/デシメーション/微分の手法を使用して、sincフィルタを実現しています。オーバーサンプリング比(OSR)を1~256の連続した整数のいずれかに設定することにより、このフィルタをSinc1、Sinc2、Sinc3、またはSincfastフィルタとして構成できます。図15に、各タイプのフィルタの周波数応答を示します。

NOTE: (1)  $f_{DATA} = 312.5\text{kHz} = \frac{f_{CLK}}{\text{OSR}} = \frac{10\text{MHz}}{32}$

図 15. さまざまなSincフィルタを使用した場合のAMC1210の周波数応答

これらの図は、あるオーバーサンプリング比(SOSR = 32)および10MHzのモジュレータ比に対するデジタル・フィルタの周波数応答を示します。

デジタル・フィルタの一般的な目的は、入力されたモジュレータ・データの平均を求ることです。より高い分解能を実現するには、平均の対象となる追加のサンプルが要求されます。したがって、急激な変化を正確に表現するために多くのサンプル総数が必要になります。また単一のサンプルを完成させるために、追加のクロック・サイクルも必要になります。サンプルを出力するためのクロック・サイクルの比は、Sincフィルタ・パラメータ・レジスタの中にあるSOSRの値(sincフィルタ・ユニットのオーバーサンプリング比)によって制御されます。表10と図16に、さまざまなフィルタ構造とSOSRの値によって得られる最大の分解能を示します。

sincフィルタは25ビットの幅であり、符号付きの2の補数データ形式で表現されています。実現可能な最大の分解能を使用した場合は、26ビットから成るワード( $\pm 16,777,216$ )が得られます。この値を実現できるのは、デルタ-シグマ・モジュレータを

正または負の絶対最大フルスケールで動作させる場合のみです。これは、ほとんどのデルタ-シグマ・モジュレータでの推奨フルスケールの80%という範囲を超えるものです。この値は、信号の分解能を表すものではありません。信号の分解能はモジュレータによって決まるものであり、フィルタのビット幅を増やしても、モジュレータの能力を上回ってノイズ性能の向上が達成されることはありません。

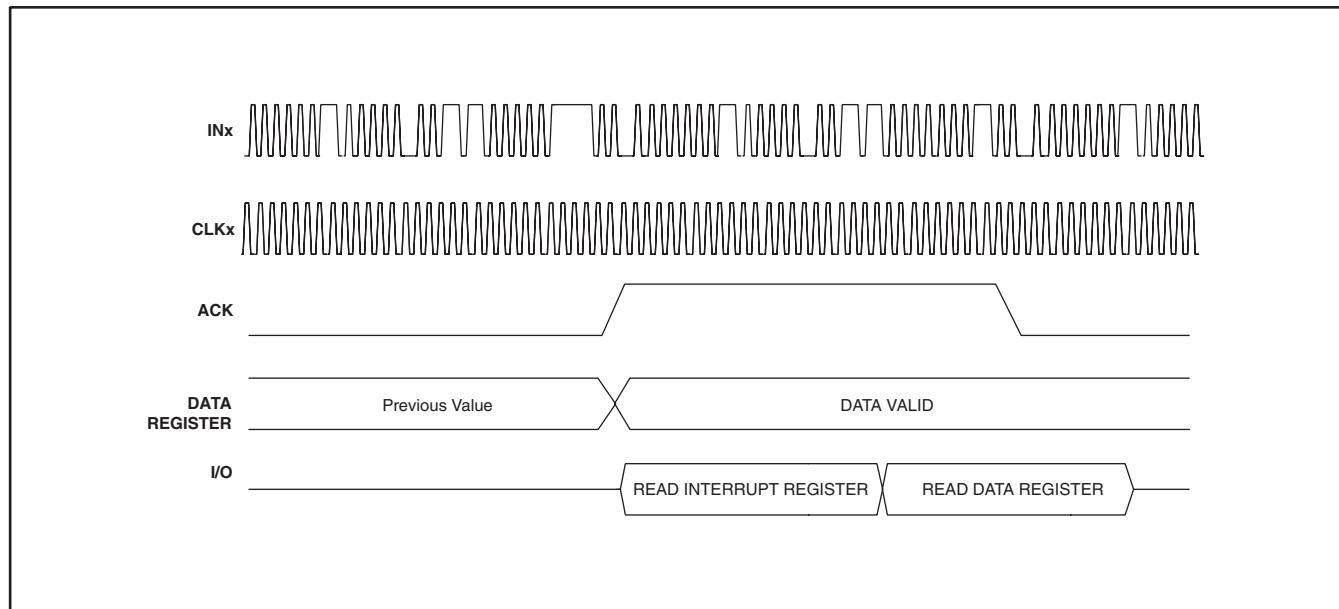

図17に、代表的なアプリケーションでのデジタル・フィルタの使用方法を示します。フィルタが有効になっている場合、フィルタは継続してデータを処理し、出力ワードを生成します。出力ワードを読み取る準備ができる場合は、ACKピンの立ち上がりエッジによって、最初にプロセッサがトリガされます。次に、割り込みレジスタが読み取られ、どのフィルタ・モジュールが新しいデータを生成したのか確認されます。すべての有効なデータ・レジスタが読み取られた時点で、ACKピンは“L”レベルになります。

データ・レジスタは、最大32ビットを使用できます。

| SOSR | Sinc <sup>1</sup> | Sinc <sup>2</sup>      | Sinc <sup>3</sup>         | Sincfast            |

|------|-------------------|------------------------|---------------------------|---------------------|

| x    | $\pm x$           | $\pm x^2$              | $\pm x^3$                 | $\pm 2x^2$          |

| 4    | -4 to 4           | $\pm 16$ to 16         | -64 to 64                 | -32 to 32           |

| 8    | -8 to 8           | $\pm 64$ to 64         | -512 to 512               | -128 to 128         |

| 16   | -16 to 16         | $\pm 256$ to 256       | -4096 to 4096             | -512 to 512         |

| 32   | -32 to 32         | $\pm 1024$ to 1024     | -32,768 to 32,768         | -2048 to 2048       |

| 64   | -64 to 64         | $\pm 4096$ to 4096     | -262,144 to 262,144       | -8192 to 8192       |

| 128  | -128 to 128       | $\pm 16,384$ to 16,384 | -2,097,152 to 2,097,152   | -32,768 to 32,768   |

| 256  | -256 to 256       | $\pm 65,536$ to 65,536 | -16,777,216 to 16,777,216 | -131,072 to 131,072 |

表 10. さまざまな SOSR/フィルタの組み合わせによるピーク・データ値

図 16. Sinc フィルタの分解能

図 17. 代表的なデータ読み取りシーケンス

## インテグレータ・ユニット

インテグレータ（積分機能）を使用すると、sincフィルタ・ユニットがバイパスされている状況で、フィルタ出力データまたは直接のモジュレータ入力データをデジタル積分（累計）できます。このユニットは、パラメータ表記のインテグレータとデータ・シフト・ユニットによって形成されています。インテグレータは簡単な32ビットのバイナリ・アキュームレータであり、2の補数表記を採用しています。積分時間は、IOSR値、または外部のサンプル/ホールド信号のどちらかによって決まります。インテグレータ・パラメータ・レジスタの中にあるIMODビットによって、どのモードを使用するかが決まります。

インテグレータ・パラメータ・レジスタのIENビットを“H”レベルに設定すると、インテグレータは有効になります。IENが“L”レベルである場合、インテグレータは無効になり、リセットされてバイパスされます。

インテグレータに対する入力は、sincフィルタ・ユニットから供給されます。これに調整を加えて、入力を直接インテグレータに供給することもできます。「Sincフィルタ・ユニットのバイパス」を参照してください。

## サンプル/ホールド・モード（IMOD = 1）

サンプル/ホールド・モードを選択した場合は、制御パラメータ・レジスタのSHSビットによって、合計積分時間を決定するために、どのサンプル/ホールド信号を使用するかが決まります。選択したサンプル/ホールド・ピンで立ち上がりエッジが発生した場合、生成されたインテグレータ値がデータ・レジスタの中に保存され、インテグレータはリセットされます。

## オーバーサンプリング・モード（IMOD = 0）

オーバーサンプリング・モードでは、インテグレータはsincフィルタ・ユニットからのサンプルを、あらかじめ設定された数だけ累積します。この数は、インテグレータ・パラメータ・レジスタの中にあるオーバーサンプリング比の値（IOSR）によって決まります。オーバーサンプリング比として、1~128の範囲にある連続した整数のいずれかを指定する方法で、インテグレータを構成できます。インテグレータは、sincフィルタ・ユニットのデータ出力比を使用してサンプリングされます。表11に、さまざまなオーバーサンプリング比の使用時にインテグレータが保存できる複数のフルスケールの値を示します。ここでは、フルスケール出力が実施されるときには、sincフィルタ・ユニットがSOSR=256に設定されることを想定しています。

オーバーサンプリング・モードでのインテグレータ・サイクルの開始は、sincフィルタ・ユニットによって制御されます。sincフィルタが有効になっているときに、新しいインテグレータ・サイクルが開始されます。クロック・デバイダ・レジスタの中にあるMFEビットを使用すると、4つのフィルタ・モジュールすべてに対してインテグレータを同期することができます。MFEビットの立ち上がりエッジに続いて、インテグレータは4つのモジュールすべてのデータの累積を開始します。すべてのsincフィルタで同じデータ出力レートが使用されている場合は、同期のタイミングが実現されます。

## インテグレータがオーバーフローした場合

最大値に到達または超過した場合、インテグレータのオーバーフローがトリガれます (IOxが “H” レベルになります)。このオーバーフロー状態が発生するのは、オーバーサンプリング・モードでsincフィルタがSinc<sup>3</sup>構造に設定されていて、そのフィルタがフルスケールの値を出力した場合のみです。

サンプル/ホールド・モードでは、インテグレータの最大値 (-2,147,483,648 または 2,147,483,648) を上回った場合に、インテグレータのこのフラグが “H” レベルになります。このイベントが発生するのは、サンプル/ホールド信号SHxが、オーバーフロー時間より長い間、アクティブな状態にとどまっていた場合です。

| IOSR | INTEGRATOR OUTPUT MAX<br>(with a Sinc <sup>3</sup> Structure) |

|------|---------------------------------------------------------------|

| x    | -(SOSR <sup>3</sup> )(x) to (SOSR <sup>3</sup> )(x)           |

| 4    | -67,108,864 to 67,108,856                                     |

| 8    | -134,217,728 to 134,217,712                                   |

| 16   | -268,435,456 to 268,435,424                                   |

| 32   | -536,870,912 to 536,870,848                                   |

| 64   | -1,073,741,824 to 1,073,741,696                               |

| 128  | -2,147,483,648 to 2,147,483,648                               |

表 11. さまざまな IOSR 値に対応するピーク・データ値

式1に、インテグレータがオーバーフローするまでの所要時間の計算方法を示します。

条件:

$$t_{\text{OVERFLOW}} = \frac{(\text{INT}_{\text{MAX}} \cdot \text{SOSR})}{(\text{FILT}_{\text{OUT}} \cdot f_{\text{INPUT}})} \quad (1)$$

- INT<sub>MAX</sub>= インテグレータの最大値 (FILT<sub>OUT</sub>< 0 の場合は -2,147,483,648、それ以外の場合は 2,147,483,648)

- FILT<sub>OUT</sub>=Sincフィルタの出力平均値

(-FILT<sub>MAX</sub> ~ +FILT<sub>MAX</sub>範囲、詳細は表10を参照)

- SOSR=Sincフィルタのオーバーサンプリング比

- f<sub>INPUT</sub>=モジュレータのデータ比

たとえば、sincフィルタが39.06kHz のレートで、100,000という平均値のコードを出力する場合は (f<sub>INPUT</sub> = 10.0MHz / SOSR=256)、インテグレータのオーバーフロー・フラグが “H” レベルになるまでに549.8msを要します。

インテグレータのオーバーフローが発生した場合、インテグレータの値はリセットされ、積分が続行されます。

## 16ビットのデータ・シフト

16ビット・データ表現を選択した場合 (DRが “H” レベル)、インテグレータ・パラメータ・レジスタのシフト制御ビット SH は、32ビット・データのうち、どの部分の16ビットをレジスタ・マップに送信するかを制御しました。これらのシフト制御ビットは、16ビットの最大の値範囲を実現するために、32ビットか

ら成るデータ・ワードを左シフトするビット数を意味します。たとえば、sincフィルタがSinc<sup>2</sup>構造で動作していて、オーバーサンプリング比が256である場合、データ値は-16,777,216～16,777,216の範囲になります。16ビットの最大の範囲として-32,767～32,767を取得するには、シフト制御ビットを9に設定する必要があります。この場合、25ビットから成るワードのうち、最下位にある9ビット (LSB) は失われます。符号ビットはシフトの影響を受けません。これは、シフト制御ビットに関わらず、符号が常に正しいことを意味します。

表12に、1つの例を示します。最初の列に32ビットから成る元のワード、2番目の列にSHビットの値を示します。最後の列には、32ビット・ワードのうち、どのビットが16ビット・モードで出力されるかを示します。

| 32-BIT WORD | SH VALUE | 16-BIT REPRESENTATION |

|-------------|----------|-----------------------|

| b31-b0      | 1        | b16-b1                |

|             | 9        | b24-b9                |

|             | 14       | b29-b14               |

表 12. 16ビットの表現例

## Sincフィルタ・ユニットのバイパス

sincフィルタ・ユニットなしでインテグレータを使用する場合は、FENビットを “H” レベル、sincフィルタの構造を Sinc<sup>1</sup>、sincフィルタのOSRを “1” にそれぞれ設定する必要があります。この場合、インテグレータはモジュレータからの直接の入力データを累計します。

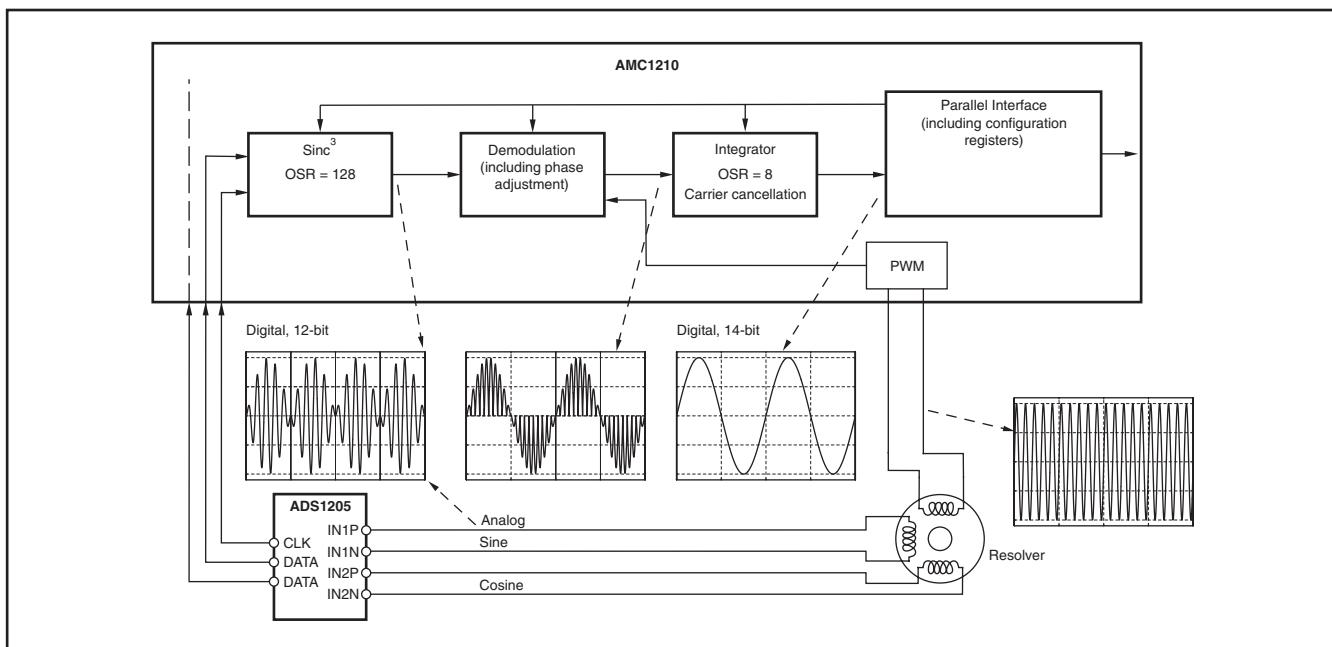

## 復調

AM変調されたリズルバの入力信号からリズルバの位置を取得するには、算術的な復調 (デモジュレーション) を実行する必要があります。位相キャリブレーションの後で、AMC1210がこの計算を実行します。変調 (モジュレーション) を有効にするには、インテグレータ・パラメータ・レジスタの中にあるDENビットを “H” レベルに設定します。詳細については、「信号ジェネレータ・ユニット」の説明と、「アプリケーション情報」を参照してください。

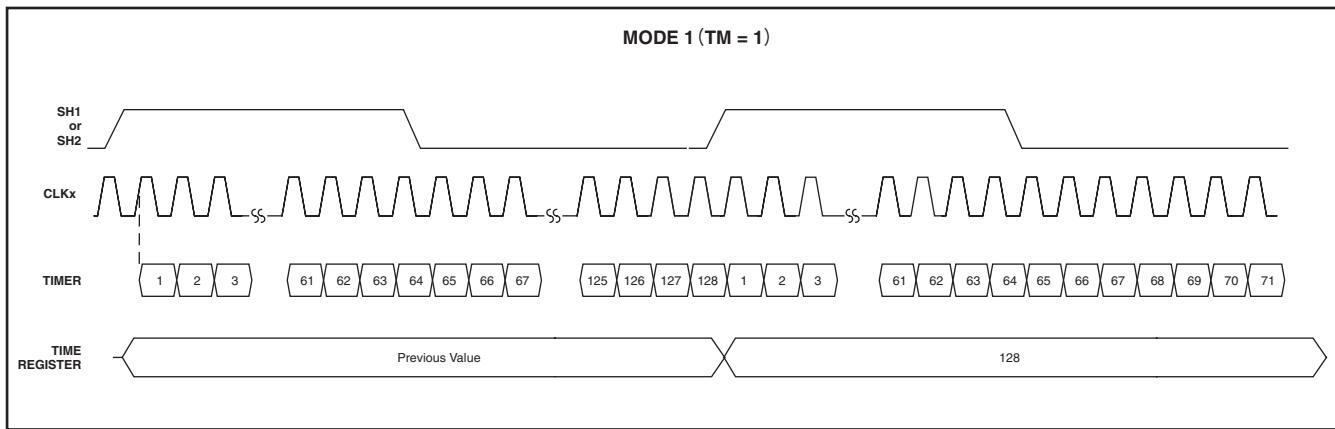

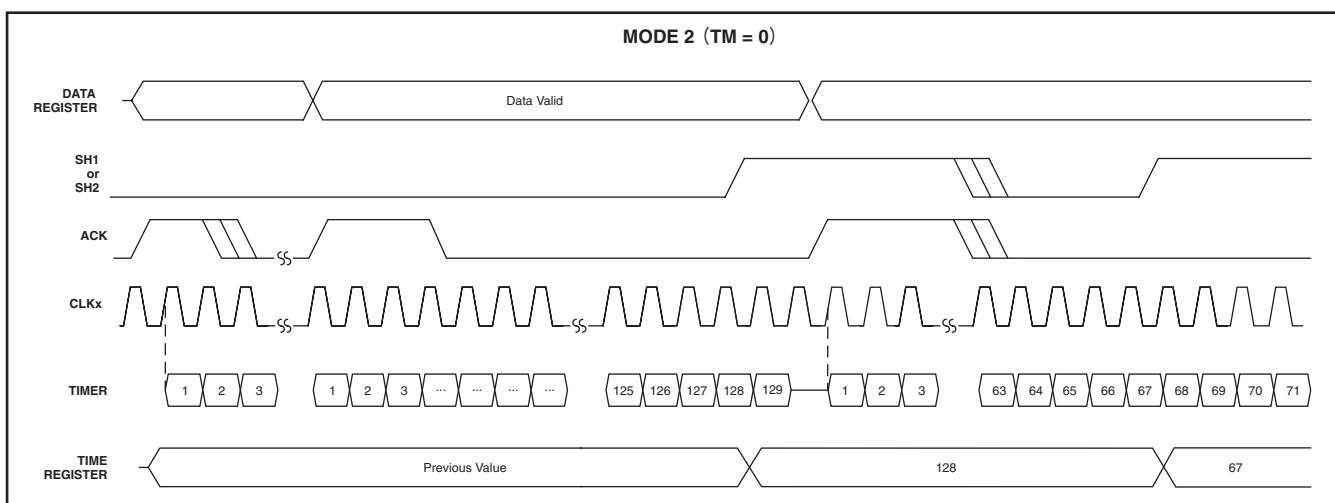

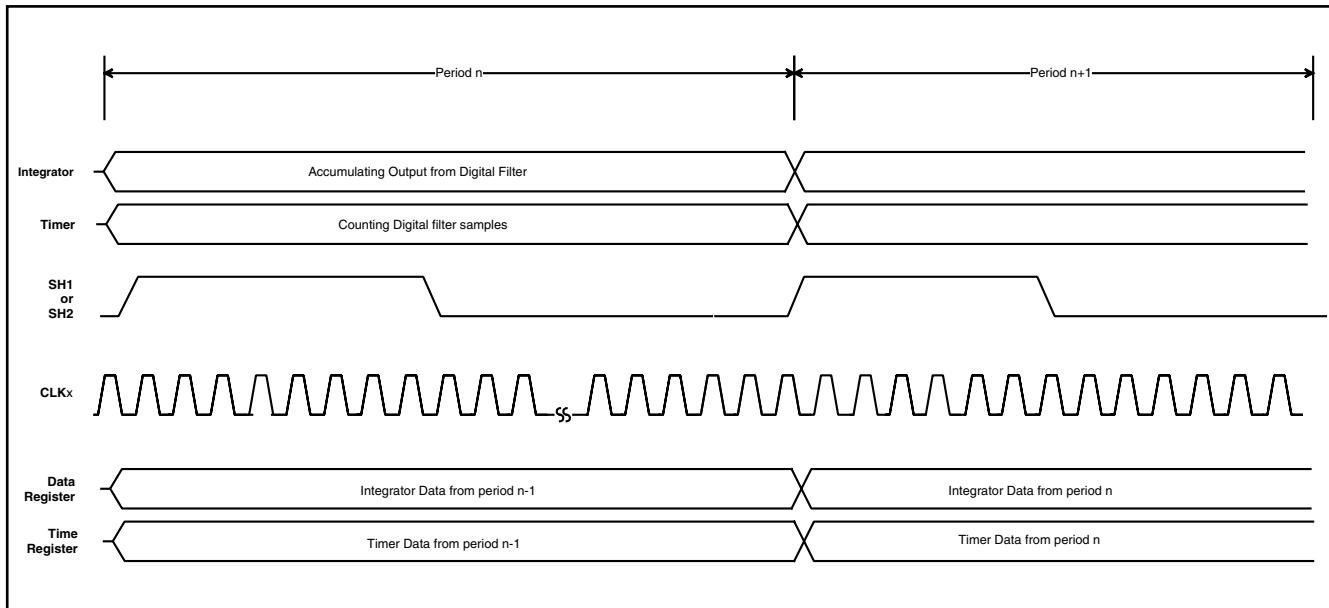

## 時間測定ユニット

時間測定ユニットは、制御パラメータ・レジスタの中にあるTMビットに応じて、時間測定に関する2つのモードを提供します。時間測定ユニットの中に、カウンタが実装されています。これは、モジュレータ・クロック入力またはシステム・クロックからのクロック・サイクルをカウントします。

最大の測定時間である t<sub>MAX</sub> は、式2を使用して計算できます。f<sub>CLK</sub> は、モジュレータ・クロックのスピード、またはシステム・クロックのスピードのどちらかです。

$$t_{\text{MAX}} = \frac{65536}{f_{\text{CLK}}} \quad (2)$$

図 18. 機能に注目したタイマ・シーケンスの代表的な例、モード 1(TM = 1)

## モード1 (TM = 1)

モード1では、時間測定ユニットは、選択したサンプル/ホールド信号(制御パラメータ・レジスタのSHSビットを使用して選択したもの)のうち、2つの立ち上がりエッジまでの間に発生した受信モジュレータ・クロック・サイクルに相当する経過時間を使用して、タイム・レジスタを更新します。このモードを使用して、モジュレータ・クロックのスピードを測定することや、フィルタ・モジュールに対してクロック同期入力された入力ビットの数を判断することができます。選択したサンプル/ホールドの立ち上がりエッジを検出するたびに、タイム・カウンタの値を使用してタイム・レジスタが更新され、タイム・カウンタはリセットされます。図18に、モード1における、機能に注目したタイマ・シーケンスに関する代表的な例を示します。

## モード2 (TM = 0)

モード2では、時間測定ユニットは、最後に使用可能だったデータから、選択したサンプル/ホールド信号の次の立ち上がりエッジまでの間に発生したシステム・クロック・サイクルに相当する経過時間を使用して、タイム・レジスタを更新します。データが使用可能になるたびに、つまり、sincフィルタまたはインテグレータが新しいデータを取得するたびに、タイマはリセットされます。選択したサンプル/ホールド信号の立ち上がりエッジが発生するたびに、タイマは継続してカウントを行います。この時点で、タイム・カウンタの値を使用してタイム・レジスタが更新され、タイム・カウンタがリセットされます。図19に、モード2における、機能に注目したタイマ・シーケンスに関する代表的な例を示します。

タイム・レジスタは16ビット・レジスタなので、最大の測定時間は65,536クロック・サイクルです。タイム・カウンタがオーバーフローを受信した(つまり、カウンタが0xFFFFから0x0000に変化した)ときに、ステータス・レジスタのTOxビットは“H”レベルに設定されます。このステータス・ビットは、ステータス・レジスタが読み取られた時点でリセットされます。

図 19. 機能に注目したタイマ・シーケンスの代表的な例、モード 2(TM = 0)

## 制御および割り込みモジュール

この制御および割り込みモジュールは、信号生成ユニット、包括的な割り込みユニット、およびレジスタ・マップによって形成されています。レジスタ・マップは、AMC1210に関するすべての制御パラメータ、出力データ、およびステータス・ビットを保持しています。各レジスタの詳細な説明は、「レジスタ・マップ」セクションを参照してください。

## 信号ジェネレータ・ユニット

信号ジェネレータ(図20を参照)は、PWM1ピンで5VのPWM(パルス幅変調)信号を生成し、PWM2で相補(反転)信号を生成します。PWM1からPWM2への出力は±5Vの差動信号であり、外部でローパス・フィルタを適用することにより、あらかじめ定義されたクロック周波数を持つ搬送波信号を生成できます。

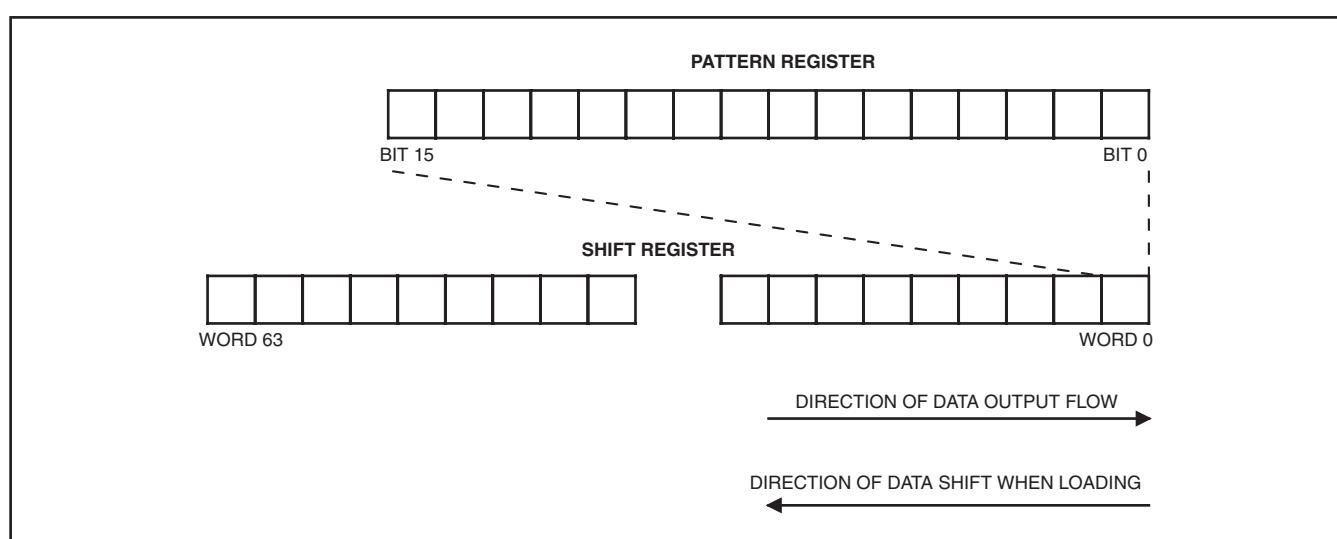

シグナル・ジェネレータは、長さが1~1,024の間にあるシフト・レジスタです。このシフト・レジスタは、パターン・レジスタ(ビットSP)を介してプログラムするものです。ビットSPに対して最初の書き込みコマンドを発行した時点で、シフト・レジスタのうち最初の16ビットがロードされます。その後、書き込みコマンドを発行するたびに、シフト・レジスタ内のデータは16ビット上位にシフトし、パターン・レジスタから取得した16ビットが、シフト・レジスタの最下位ビット(LSB)に書き込まれます。たとえば、874ビットのあらかじめ定義されたパターンがシフト・レジスタの中に保存されている場合は、パターン・レジスタに対して55回の書き込みコマンドを発行する必要があります(MSBが最初、LSBが最後)。また、制御レジスタのPCビットに対して、値873を書き込む必要があります。

信号ジェネレータの出力データ・レートは、クロック・デバイダ・レジスタ(ビットSD)を介してプログラムします。この出力データ・レートは、CLKのレートを整数で除算した値として選択できます。たとえば、CLKピンが40MHzで動作し、ビット

SD=4である場合、シグナル・ジェネレータのピット・レートは10MHzになります。パターンの長さは、制御レジスタ(ビットPC)を介してプログラムできます。長さは、1~1,024ビットの範囲で選択できます。この信号は、リゾルバ・アプリケーションの搬送波周波数として使用するために設計されたものです。適切な復調を行うには、搬送波のタイミングにクロックを完全に同期することが必要です。

## 信号ジェネレータのキャリブレーション

リゾルバの復調を実行する場合は、信号ジェネレータ・ユニットをシステム全体と同期しておく必要があります。この条件を満たすには、信号ジェネレータの出力の位相をsincフィルタの出力に合わせて、キャリブレーションを実行する必要があります。この位相キャリブレーションは、クロック・デバイダ・レジスタのPCALビットを“H”レベルに設定した時点で開始されます。AMC1210は、信号ジェネレータとsincフィルタ両方の出力の極性をモニタする方法で、キャリブレーションを実行します。極性を定義した後に復調信号が生成され、適切な位相シフトが適用されます。

PCALビットは復調を制御します。最初は、このビットは“H”レベルに設定されます。次に、変調が正しく実行された時点で、AMC1210はPCALビットに対して“L”レベルを出力します。このマイクロコントローラ(AMC1210)は、PCALを読み取る方法でキャリブレーションをモニタします。キャリブレーションの最初の試行では、信号ジェネレータの1つの期間をキャリブレートすることを試みます。この期間が経過した後もPCALが“H”レベルにとどまっている場合は、キャリブレーションが失敗したことがわかります。キャリブレーションをもう一度開始するには、PCALの状態をリセットするために、PCALに対して“L”を書き込む必要があります。これ以後、“H”レベルを書き込むと、キャリブレーションがもう一度開始されます。

図 20. AMC1210 の信号ジェネレータ・ユニット

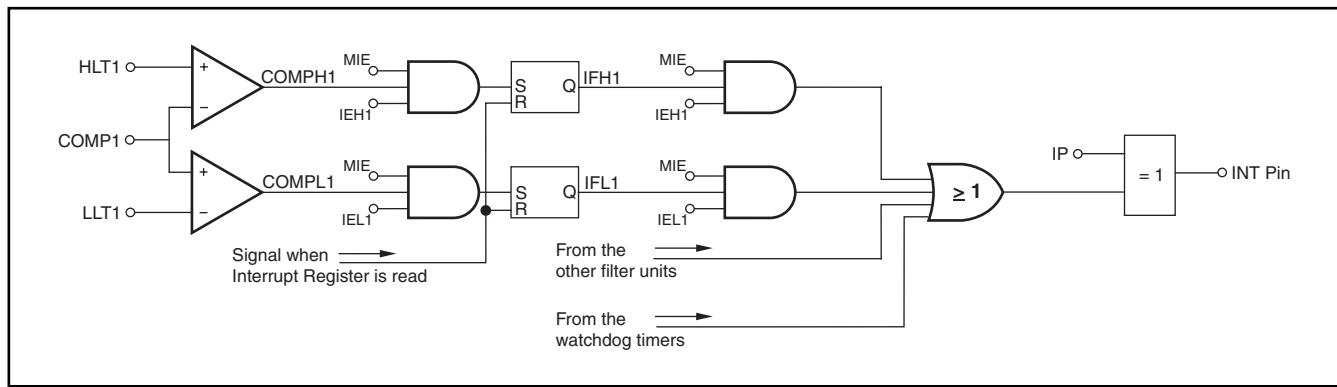

図 21. AMC1210 の割り込みユニット

## 信号ジェネレータを使用した信号の駆動

リゾルバをAMC1210から直接駆動することもできます。ビットHBEが“H”レベルに設定されている場合、PWM1ピンとPWM2ピンは100mAをリゾルバのコイルに直接供給するドライブ能力があります。HBE=0の場合、ドライブ能力はこれより低くなります。

パターン・ジェネレータは、クロック・デバイダ・レジスタの中にあるSGEビットによって有効になります。

## 割り込みユニット

図21に、割り込みユニットの構造を示します。

各コンパレータの出力は、1つの割り込みソース (COMPHx または COMPLx) であり、AMC1210の中では全部で8つのコンパレータ出力が作成されます。マスタ割り込みイネーブル (MIE) と適切な割り込みイネーブル (IEHx または IELx) が “H” レベルに設定されている場合、これら8つの割り込みソースのそれぞれは、フラグ・レジスタ (IFHx または IFLx) の中に保存されます。割り込みが発行された場合、このフラグ・レジスタは “H” レベルに設定されます。割り込みレジスタが読み取られ、割り込みソースがアクティブではない場合、このフラグはリセットされます。割り込みレジスタが読み取られた時点で、割り込みソースが引き続きアクティブである場合、該当のフラグは引き続き設定された状態にとどまります。

該当のモジュレータ・フラグ割り込みイネーブル・ビット (MFIE<sub>x</sub>) とマスタ割り込みイネーブル (MIE) が設定されている場合は、モジュレータ・クロックが立ち下がる時点での (モジュレータ・クロックがシステム・クロック CLK の 1/64 未満である場合)、ウォッチドッグ・タイマは MF<sub>x</sub> フラグを設定します。割り込みレジスタが読み取られた時点で、モジュレータ・クロック

が引き続き “L” レベルにとどまっている場合、該当のフラグは引き続き設定された状態にとどまります。立ち下がりの状態が成立していない場合、このフラグはクリアされ、割り込みレジスタが読み取られます。

12の割り込みビットのいずれかが有効になっている場合は、そのビットが割り込みピンINTをアクティブにします。INTピンの極性は、制御レジスタの中にある極性制御ビット (IP) を使用して選択できます。

## 受信応答 (ACK)

受信応答ピンACKは、フィルタ・モジュールのいずれかで新しいデータが利用可能になっていることを示します。受信応答ピンが “H” レベルになった時点で、1つまたは複数のデータをデータ・レジスタの中で利用できます。割り込みレジスタを読み取る方法で、新しいデータを保持しているフィルタ・モジュールを判断できます。1つのデータ・レジスタを読み取った時点で、割り込みレジスタの中にある該当の受信応答フラグはリセットされます。すべてのフラグがリセットされた場合、受信応答ピンはリセットされて “L” レベルになります。受信応答ピンを反転するには、制御レジスタの極性制御ビット (AP) “H” レベルにセットします。sincフィルタとインテグレータの両方が無効になっている場合、受信応答フラグを設定することはできません。該当のSincフィルタ・パラメータ・レジスタの中にある受信応答イネーブル制御ビット (AE) が “L” レベルに設定されている場合は、各受信応答フラグを無効にすることができます。sincフィルタとインテグレータ両方のオーバーサンプリング・レートが “1” に設定されている場合、受信応答フラグは設定されません。

## レジスタ・マップ

|                  | ADDRESS      | RESET VALUE                      | NAME                                               |

|------------------|--------------|----------------------------------|----------------------------------------------------|

| Filter Module 1  | 0x00         | 0x0000                           | Interrupt Register                                 |

|                  | 0x01         | 0x0000                           | Control Parameter Register for Filter Module 1     |

|                  | 0x02         | 0x0000                           | Sinc Filter Parameter Register for Filter Module 1 |

|                  | 0x03         | 0x0000                           | Integrator Parameter Register for Filter Module 1  |

|                  | 0x04         | 0x7FFF                           | High-level Threshold Register for Filter Module 1  |

|                  | 0x05         | 0x0000                           | Low-level Threshold Register for Filter Module 1   |

|                  | 0x06         | 0x0000                           | Comparator Parameter Register for Filter Module 1  |

| Filter Module 2  | 0x07         | 0x0000                           | Control Parameter Register for Filter Module 2     |

|                  | 0x08         | 0x0000                           | Sinc Filter Parameter Register for Filter Module 2 |

|                  | 0x09         | 0x0000                           | Integrator Parameter Register for Filter Module 2  |

|                  | 0x0A         | 0x7FFF                           | High-level Threshold Register for Filter Module 2  |

|                  | 0x0B         | 0x0000                           | Low-level Threshold Register for Filter Module 2   |

|                  | 0x0C         | 0x0000                           | Comparator Parameter Register for Filter Module 2  |

| Filter Module 3  | 0x0D         | 0x0000                           | Control Parameter Register for Filter Module 3     |

|                  | 0x0E         | 0x0000                           | Sinc Filter Parameter Register for Filter Module 3 |

|                  | 0x0F         | 0x0000                           | Integrator Parameter Register for Filter Module 3  |

|                  | 0x10         | 0x7FFF                           | High-level Threshold Register for Filter Module 3  |

|                  | 0x11         | 0x0000                           | Low-level Threshold Register for Filter Module 3   |

|                  | 0x12         | 0x0000                           | Comparator Parameter Register for Filter Module 3  |

| Filter Module 4  | 0x13         | 0x0000                           | Control Parameter Register for Filter Module 4     |

|                  | 0x14         | 0x0000                           | Sinc Filter Parameter Register for Filter Module 4 |

|                  | 0x15         | 0x0000                           | Integrator Parameter Register for Filter Module 4  |

|                  | 0x16         | 0x7FFF                           | High-level Threshold Register for Filter Module 4  |

|                  | 0x17         | 0x0000                           | Low-level Threshold Register for Filter Module 4   |

|                  | 0x18         | 0x0000                           | Comparator Parameter Register for Filter Module 4  |

|                  | 0x19         | 0x0000                           | Control Register                                   |

|                  | 0x1A         | 0x0000                           | Pattern Register                                   |

|                  | 0x1B         | 0x0000                           | Clock Divider Register                             |

|                  | 0x1C         | 0x0000                           | Status Register                                    |

| Data/Time Output | 0x1D         | 0x0000/0x00000000 <sup>(1)</sup> | Data Register for Filter Module 1 <sup>(1)</sup>   |

|                  | 0x1E         | 0x0000                           | Time Register for Filter Module 1                  |

|                  | 0x1F         | 0x0000/0x00000000 <sup>(1)</sup> | Data Register for Filter Module 2 <sup>(1)</sup>   |

|                  | 0x20         | 0x0000                           | Time Register for Filter Module 2                  |

|                  | 0x21         | 0x0000/0x00000000 <sup>(1)</sup> | Data Register for Filter Module 3 <sup>(1)</sup>   |

|                  | 0x22         | 0x0000                           | Time Register for Filter Module 3                  |

|                  | 0x23         | 0x0000/0x00000000 <sup>(1)</sup> | Data Register for Filter Module 4 <sup>(1)</sup>   |

|                  | 0x24         | 0x0000                           | Time Register for Filter Module 4                  |

|                  | 0x25 to 0x7F | 0x0000                           | Not used. Read will return 0x0000                  |

(1) データ・レジスタは、32ビット形式で表現することも可能です。

すべての制御パラメータは、レジスタ・マップの中に保存されます。さらに、AMC1210の状態(ステータス)は、レジスタ・マップを介して読み取られます。それ以降のレジスタに関するニーモニックと説明は、例1に示します。

## 例1：レジスタの説明とニーモニック

| Bit 8 | Bit 9 | Bit 10 | The bit position in the register.                                                                                     |

|-------|-------|--------|-----------------------------------------------------------------------------------------------------------------------|

| CS1   | -     | SHS    | The name of the register bit. A '-' means <i>Not Used</i> and therefore a write to such a bit position will get lost. |

| '1'   | '0'   | '0'    | The digit is the reset value.                                                                                         |

| W     | R     | RW     | Indicates if the bit position is a read-only (R), readable and writable (RW) or write-only (W).                       |

## レジスタの説明

このセクションでは、各レジスタの機能とそれに対応するビットについて説明します。

### 割り込みレジスタ (アドレス 0x00)

割り込みレジスタには12個の割り込みフラグがあり、それらには受信応答(ACK)フラグが組み合わされています。割り込みが発生した(つまり、コンパレータ・フィルタの出力が“H”

レベルのスレッシュホールドを上回った、“L”レベルのスレッシュホールドを下回った、またはモジュレータのいずれかが動作していない場合、該当の割り込みフラグが設定されます(そのフラグが有効になっている場合)。割り込みレジスタが読み取られ、対応する割り込みソースがアクティブではない場合、割り込みフラグはリセットされます。対応するデータ・レジスタが読み取られた時点で、受信応答ビットはリセットされます。表13に、割り込みレジスタの説明を示します。

| Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| AF4    | AF3    | AF2    | AF1    | MF4    | MF3    | MF2   | MF1   | IFL4  | IFH4  | IFL3  | IFH3  | IFL2  | IFH2  | IFL1  | IFH1  |

|     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| '0' | '0' | '0' | '0' | '0' | '0' | '0' | '0' | '0' | '0' | '0' | '0' | '0' | '0' | '0' | '0' |

| R   | R   | R   | R   | R   | R   | R   | R   | R   | R   | R   | R   | R   | R   | R   | R   |

| BIT POSITION | BIT | DESCRIPTION                                                                                                                  |

|--------------|-----|------------------------------------------------------------------------------------------------------------------------------|

| 15           | AF4 | Acknowledge flag for Filter 4.<br>0: No new data available for Filter 4<br>1: New data available for Filter 4                |

| 14           | AF3 | Acknowledge flag for Filter 3.<br>0: No new data available for Filter 3<br>1: New data available for Filter 3                |

| 13           | AF2 | Acknowledge flag for Filter 2.<br>0: No new data available for Filter 2<br>1: New data available for Filter 2                |

| 12           | AF1 | Acknowledge flag for Filter 1.<br>0: No new data available for Filter 1<br>1: New data available for Filter 1                |

| 11           | MF4 | Modulator failure flag for Filter 4.<br>0: Modulator is operating normally for Filter 4<br>1: Modulator failure for Filter 4 |

| 10           | MF3 | Modulator failure flag for Filter 3.<br>0: Modulator is operating normally for Filter 3<br>1: Modulator failure for Filter 3 |

| 9            | MF2 | Modulator failure flag for Filter 2.<br>0: Modulator is operating normally for Filter 2<br>1: Modulator failure for Filter 2 |

| 8            | MF1 | Modulator failure flag for Filter 1.<br>0: Modulator is operating normally for Filter 1<br>1: Modulator failure for Filter 1 |

表13. 割り込みレジスタ

| BIT POSITION | BIT  | DESCRIPTION                                                                                                                                                                                          |

|--------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7            | IFL4 | Low-level interrupt flag for Filter 4<br>0: Comparator Filter 4 output is above the low limit threshold<br>1: Comparator Filter 4 output is equal to or below the low level threshold, if enabled    |

| 6            | IFH4 | High-level interrupt flag for Filter 4<br>0: Comparator Filter 4 output is below the high limit threshold<br>1: Comparator Filter 4 output is equal to or above the high level threshold, if enabled |

| 5            | IFL3 | Low-level interrupt flag for Filter 3<br>0: Comparator Filter 3 output is above the low limit threshold<br>1: Comparator Filter 3 output is equal to or below the low level threshold, if enabled    |

| 4            | IFH3 | High-level interrupt flag for Filter 3<br>0: Comparator Filter 3 output is below the high limit threshold<br>1: Comparator Filter 3 output is equal to or above the high level threshold, if enabled |

| 3            | IFL2 | Low-level interrupt flag for Filter 2<br>0: Comparator Filter 2 output is above the low limit threshold<br>1: Comparator Filter 2 output is equal to or below the low level threshold, if enabled    |

| 2            | IFH2 | High-level interrupt flag for Filter 2<br>0: Comparator Filter 2 output is below the high limit threshold<br>1: Comparator Filter 2 output is equal to or above the high level threshold, if enabled |

| 1            | IFL1 | Low-level interrupt flag for Filter 1<br>0: Comparator Filter 1 output is above the low limit threshold<br>1: Comparator Filter 1 output is equal to or below the low level threshold, if enabled    |

| 0            | IFH1 | High-level interrupt flag for Filter 1<br>0: Comparator Filter 1 output is below the high limit threshold<br>1: Comparator Filter 1 output is equal to or above the high level threshold, if enabled |

## 制御パラメータ・レジスタ (アドレス0x01、0x07、0x0D、0x13)

制御パラメータ・レジスタは、データ処理に関連するいくつかのパラメータを制御します。制御パラメータ・レジスタの機能には、マンチェスター・デコーダ・キャリブレーションの状態、ク

ロック・ピンの方向制御、デルタ-シグマ・モジュレータのモード選択、サンプル/ホールドの選択、時間測定モードが含まれます。表14に、制御パラメータ・レジスタの説明を示します。

| Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| MS10   | MS9    | MS8    | MS7    | MS6    | MS5    | MS4   | MS3   | MS2   | MS1   | MS0   | CD    | SHS   | TM    | MOD1  | MOD0  |

| '0'    | '0'    | '0'    | '0'    | '0'    | '0'    | '0'   | '0'   | '0'   | '0'   | '0'   | '0'   | '0'   | '0'   | '0'   | '0'   |

| R      | R      | R      | R      | R      | R      | R     | R     | R     | R     | R     | RW    | RW    | RW    | RW    | RW    |

| BIT POSITION | BIT       | DESCRIPTION                                                                                                                                                                                                                                                                              |

|--------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15–5         | MS10–MS0  | Manchester status                                                                                                                                                                                                                                                                        |

| 4            | CD        | Input clock direction.<br>0: Pin CLKx is an input<br>1: Pin CLKx is an output. The outgoing clock comes from the modulator clock divider.                                                                                                                                                |

| 3            | SHS       | Sample-and-hold select.<br>0: Signal SH1 is chosen as sample-and-hold signal<br>1: Signal SH2 is chosen as sample-and-hold signal                                                                                                                                                        |

| 2            | TM        | Time measure mode.<br>0: The time is measured from the last filter update to the last rising edge of the selected sample-and-hold signal<br>1: The time is measured between two rising edges of the selected sample-and-hold signal                                                      |

| 1–0          | MOD1–MOD0 | Delta-Sigma Modulator mode.<br>00: The clock speed is equal to the data rate from the modulator<br>01: The clock rate is half of the data rate from the modulator<br>10: The data from the modulator is Manchester decoded<br>11: The clock rate is twice the data rate of the modulator |

表14. 制御パラメータ・レジスタ

|        |        |        |        |        |        |       |       |       |       |       |       |       |       |       |       |

|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| -      | -      | -      | -      | SST1   | SST0   | AE    | FEN   | SOSR7 | SOSR6 | SOSR5 | SOSR4 | SOSR3 | SOSR2 | SOSR1 | SOSR0 |

| '0'    | '0'    | '0'    | '0'    | '0'    | '0'    | '0'   | '0'   | '0'   | '0'   | '0'   | '0'   | '0'   | '0'   | '0'   | '0'   |

| R      | R      | R      | R      | RW     | RW     | RW    | RW    | RW    | RW    | RW    | RW    | RW    | RW    | RW    | RW    |

| BIT POSITION | BIT         | DESCRIPTION                                                                                                                                                                                                                                               |

|--------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15–12        | -           | Unused. Always read '0'.                                                                                                                                                                                                                                  |

| 11–10        | SST1–SST0   | Sinc filter structure.<br>00: Sinc filter runs with a sincfast structure<br>01: Sinc filter runs with a Sinc <sup>1</sup> structure<br>10: Sinc filter runs with a Sinc <sup>2</sup> structure<br>11: Sinc filter runs with a Sinc <sup>3</sup> structure |

| 9            | AE          | Acknowledge enable.<br>0: The acknowledge flag is disabled for the particular filter<br>1: The acknowledge flag is enabled for the particular filter                                                                                                      |

| 8            | FEN         | Filter enable.<br>0: The filter is disabled and no data is produced<br>1: The filter is enabled and data are produced in the sinc filter and/or integrator                                                                                                |

| 7–0          | SOSR7–SOSR0 | Oversampling ratio. The actual rate is SOSR + 1.<br>These bits set the oversampling ratio of the filter.<br>0xFF represents an oversampling ratio of 256.                                                                                                 |

表 15. Sinc フィルタ・パラメータ・レジスタ

### Sinc フィルタ・パラメータ・レジスタ (アドレス 0x02、0x08、0x0E、0x14)

Sinc フィルタ・パラメータ・レジスタには、オーバーサンプリング比(OSR)、フィルタ・イネーブル、構造制御ビット、および信号モード制御ビットが含まれます。表15に、Sinc フィルタ・パラメータ・レジスタの説明を示します。

### インテグレータ・パラメータ・レジスタ (アドレス 0x03、0x09、0x0F、0x15)

インテグレータ・パラメータ・レジスタは、インテグレータの機能を制御します。このレジスタは、インテグレータのオーバーサンプリング比、モード選択、シフト制御、インテグレータと復調機能のイネーブル、およびデータ表現形式の制御ビットを指定します。表16に、インテグレータ・パラメータ・レジスタの説明を示します。

|        |        |        |        |        |        |       |       |       |       |       |       |       |       |       |       |

|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| SH4    | SH3    | SH2    | SH1    | SH0    | DR     | DEN   | IEN   | IMOD  | IOSR6 | IOSR5 | IOSR4 | IOSR3 | IOSR2 | IOSR1 | IOSR0 |

| '0'    | '0'    | '0'    | '0'    | '0'    | '0'    | '0'   | '0'   | '0'   | '0'   | '0'   | '0'   | '0'   | '0'   | '0'   | '0'   |

| RW     | RW     | RW     | RW     | RW     | RW     | RW    | RW    | RW    | RW    | RW    | RW    | RW    | RW    | RW    | RW    |

| BIT POSITION | BIT         | DESCRIPTION                                                                                                                                                                |

|--------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15–11        | SH4–SH0     | Shift control.<br>These bits indicate by how many bits the 16-bit window is shifted up when 16-bit data representation is chosen.                                          |

| 10           | DR          | Data representation.<br>0: The data is stored in 16-bit two's complement<br>1: The data is stored in 32-bit two's complement                                               |

| 9            | DEN         | Demodulation enable.<br>0: The demodulation for resolver applications is disabled<br>1: The demodulation for resolver applications is enabled                              |

| 8            | IEN         | Integrator enable.<br>0: The data from the sinc filter output is stored in the register map<br>1: The data from the integrator is stored in the register map               |

| 7            | IMOD        | Integrator mode.<br>0: The oversampling mode updates the data output of the integrator<br>1: The selected sample-and-hold signal updates the data output of the integrator |

| 6–0          | IOSR6–IOSR0 | Oversampling ratio. The actual rate is IOSR + 1.<br>These bits set the oversampling ratio of the integrator.<br>0x03 represents an oversampling ratio of 4.                |

表 16. インテグレータ・パラメータ・レジスタ

| Bit 15       | Bit 14     | Bit 13 | Bit 12                                                          | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|--------------|------------|--------|-----------------------------------------------------------------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| -            | HLT14      | HLT13  | HLT12                                                           | HLT11  | HLT10  | HLT9  | HLT8  | HLT7  | HLT6  | HLT5  | HLT4  | HLT3  | HLT2  | HLT1  | HLT0  |

| '0'          | '1'        | '1'    | '1'                                                             | '1'    | '1'    | '1'   | '1'   | '1'   | '1'   | '1'   | '1'   | '1'   | '1'   | '1'   | '1'   |

| R            | RW         | RW     | RW                                                              | RW     | RW     | RW    | RW    | RW    | RW    | RW    | RW    | RW    | RW    | RW    | RW    |

| BIT POSITION | BIT        |        | DESCRIPTION                                                     |        |        |       |       |       |       |       |       |       |       |       |       |

| 15           | -          |        | Unused. Always read '0'.                                        |        |        |       |       |       |       |       |       |       |       |       |       |

| 14–0         | HTL14–HLT0 |        | Unsigned high level threshold for the comparator filter output. |        |        |       |       |       |       |       |       |       |       |       |       |

表 17. “H” レベル・スレッシュホールド・レジスタ

### “H” レベル・スレッシュホールド・レジスタ (アドレス 0x04、0x0A、0x10、0x16)

“H” レベル・スレッシュホールド・レジスタには、コンパレータ・フィルタに適用される割り込みスレッシュホールドの上位レベルの値が保存されています。コンパレータ・フィルタの値が“H” レベル・スレッシュホールド以上である場合は、対応する割り込みフラグが設定されます(そのフラグが有効になっている場合)。表17に、“H” レベル・スレッシュホールド・レジスタの説明を示します。

### “L” レベル・スレッシュホールド・レジスタ (アドレス 0x05、0x0B、0x11、0x17)

“L” レベル・スレッシュホールド・レジスタには、コンパレータ・フィルタに適用される割り込みスレッシュホールドの下位レベルが保存されています。コンパレータ・フィルタの値が“L” レベル・スレッシュホールド以下である場合は、対応する割り込みフラグが設定されます(そのフラグが有効になっている場合)。表18に、“L” レベル・スレッシュホールド・レジスタの説明を示します。

| Bit 15       | Bit 14     | Bit 13 | Bit 12                                                         | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|--------------|------------|--------|----------------------------------------------------------------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| -            | LLT14      | LLT13  | LLT12                                                          | LLT11  | LLT10  | LLT9  | LLT8  | LLT7  | LLT6  | LLT5  | LLT4  | LLT3  | LLT2  | LLT1  | LLT0  |

| '0'          | '0'        | '0'    | '0'                                                            | '0'    | '0'    | '0'   | '0'   | '0'   | '0'   | '0'   | '0'   | '0'   | '0'   | '0'   | '0'   |

| R            | RW         | RW     | RW                                                             | RW     | RW     | RW    | RW    | RW    | RW    | RW    | RW    | RW    | RW    | RW    | RW    |

| BIT POSITION | BIT        |        | DESCRIPTION                                                    |        |        |       |       |       |       |       |       |       |       |       |       |

| 15           | -          |        | Unused. Always read '0'.                                       |        |        |       |       |       |       |       |       |       |       |       |       |

| 14–0         | LTL14–LLT0 |        | Unsigned low level threshold for the comparator filter output. |        |        |       |       |       |       |       |       |       |       |       |       |

表 18. “L” レベル・スレッシュホールド・レジスタ

## コンパレータ・フィルタ・パラメータ・レジスタ (アドレス 0x06、0x0C、0x12、0x18)