# MOSFET内蔵、パワーパス・セレクタ搭載、1.6MHz、 同期整流スイッチ・モードLiイオン/ Liポリマー・スタンドアロン・バッテリ・チャージャ

## 特 長

- 4A N-MOSFET内蔵、1.6MHz同期整流スイッチ・モード・チャージャ

- 最大効率: 94%

- 入力動作範囲: 4.5V~17V

- バッテリ充電電圧

- bq24170: 4.2V/セル(1、2、または3セル)

- bq24172: 可変充電電圧

- 内蔵機能

- アダプタとバッテリのパワーパス自動切換え

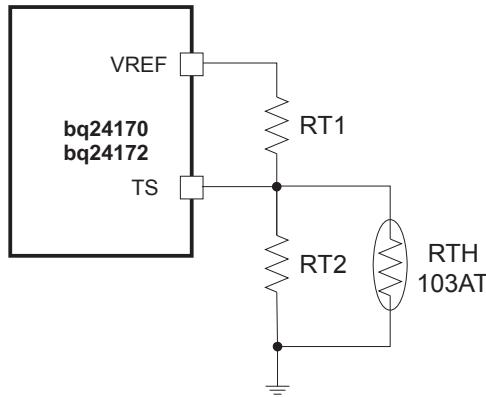

- 動的電源管理

- 20VスイッチングMOSFETを内蔵

- ブーストストラップ・ダイオードを内蔵

- 内部位相補償

- 内部デジタル・ソフト・スタート

- 安全保護

- 熱レギュレーション・ループで充電電流を低減し  $T_j = 120^{\circ}\text{C}$ に制限

- 過熱シャットダウン

- バッテリ・サーミスタ・センサにより高温/低温時の充電一時停止、およびバッテリ検出機能

- スレッショルドを設定可能な入力過電圧保護

- Cycle-by-Cycle電流制限

- 精度

- 充電電圧精度:  $\pm 0.5\%$

- 充電電流精度:  $\pm 4\%$

- 入力電流精度:  $\pm 4\%$

- アダプタ取り外し時のバッテリ電流: 15 $\mu\text{A}$ 未満

- アダプタ接続、充電ディスエーブル時の入力電流: 1.5mA未満

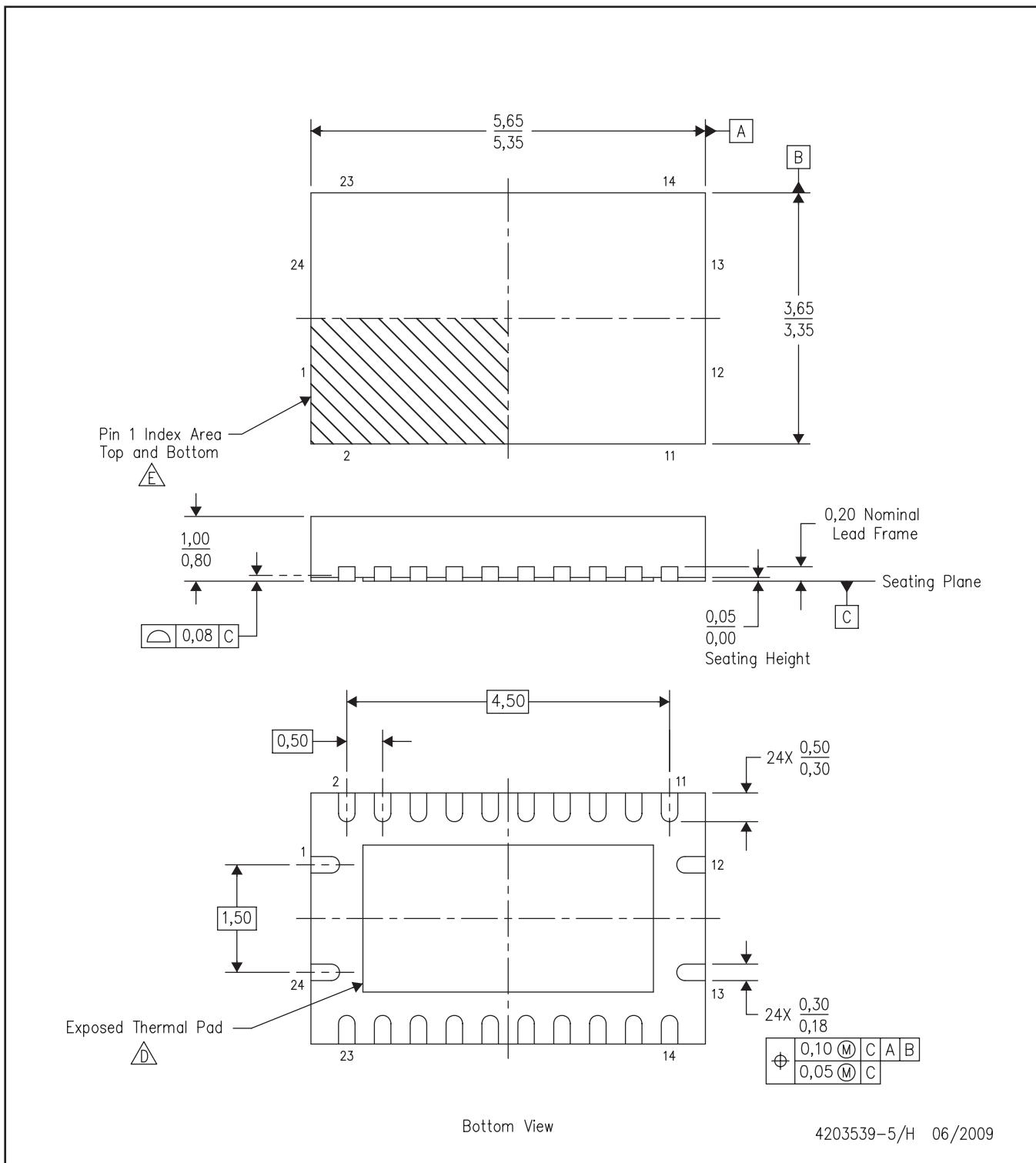

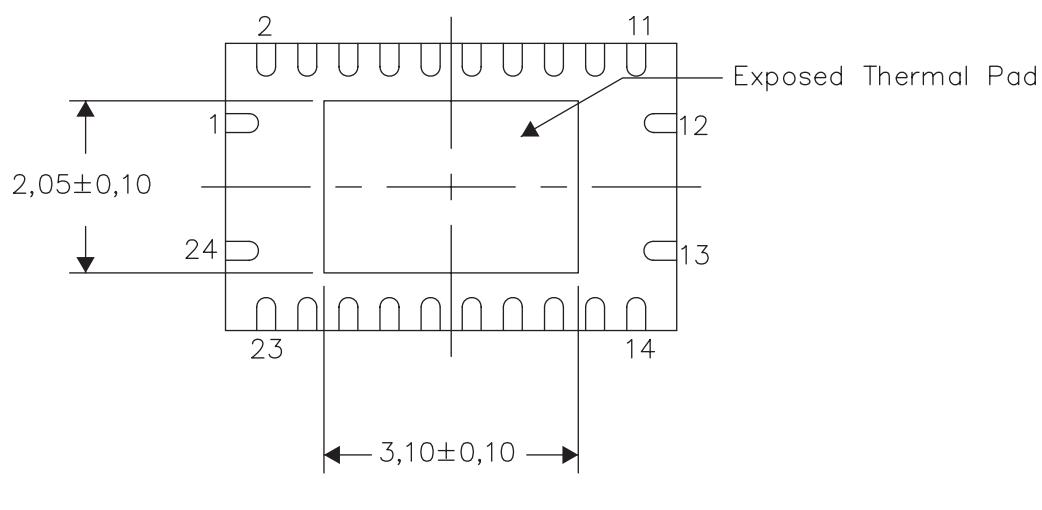

- 小型QFNパッケージ

- 3.5mm×5.5mmの24ピンQFN

## ア プ リ ケ シ ョ ン

- タブレットPC

- ネットブックおよびウルトラモバイル・コンピュータ

- ポータブル・データ・キャプチャ・ターミナル

- ポータブル・プリンタ

- 医療用診断装置

- バッテリ・ベイ・チャージャ

- バッテリ・バックアップ・システム

## 概 要

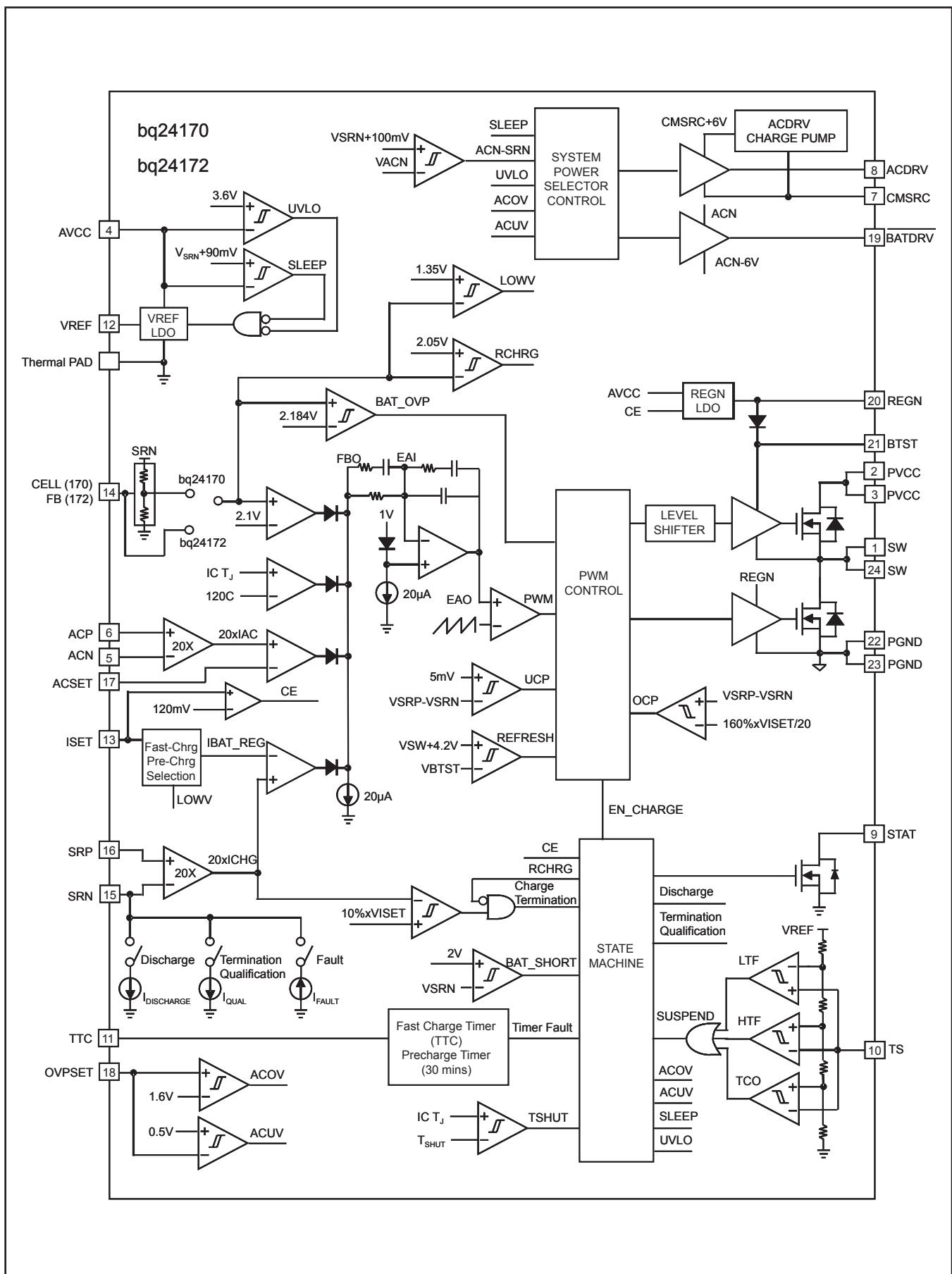

bq24170/172は、LiイオンまたはLiポリマー・バッテリ用にさまざまな機能を集積したスタンドアロンのスイッチ・モード・バッテリ・チャージャであり、2個のNチャネル・パワーMOSFETを内蔵しています。定周波数の同期PWMコントローラを搭載し、入力電流、充電電流、および電圧の高精度制御が可能です。バッテリ・パックの温度を厳密に監視し、設定した温度範囲内でのみ充電を許可します。バッテリ検出、プリチャージ、充電終了、充電ステータス監視などの機能も備えています。熱レギュレーション・ループによって、動作中の接合部温度が120°Cに保持されるよう充電電流を低減します。

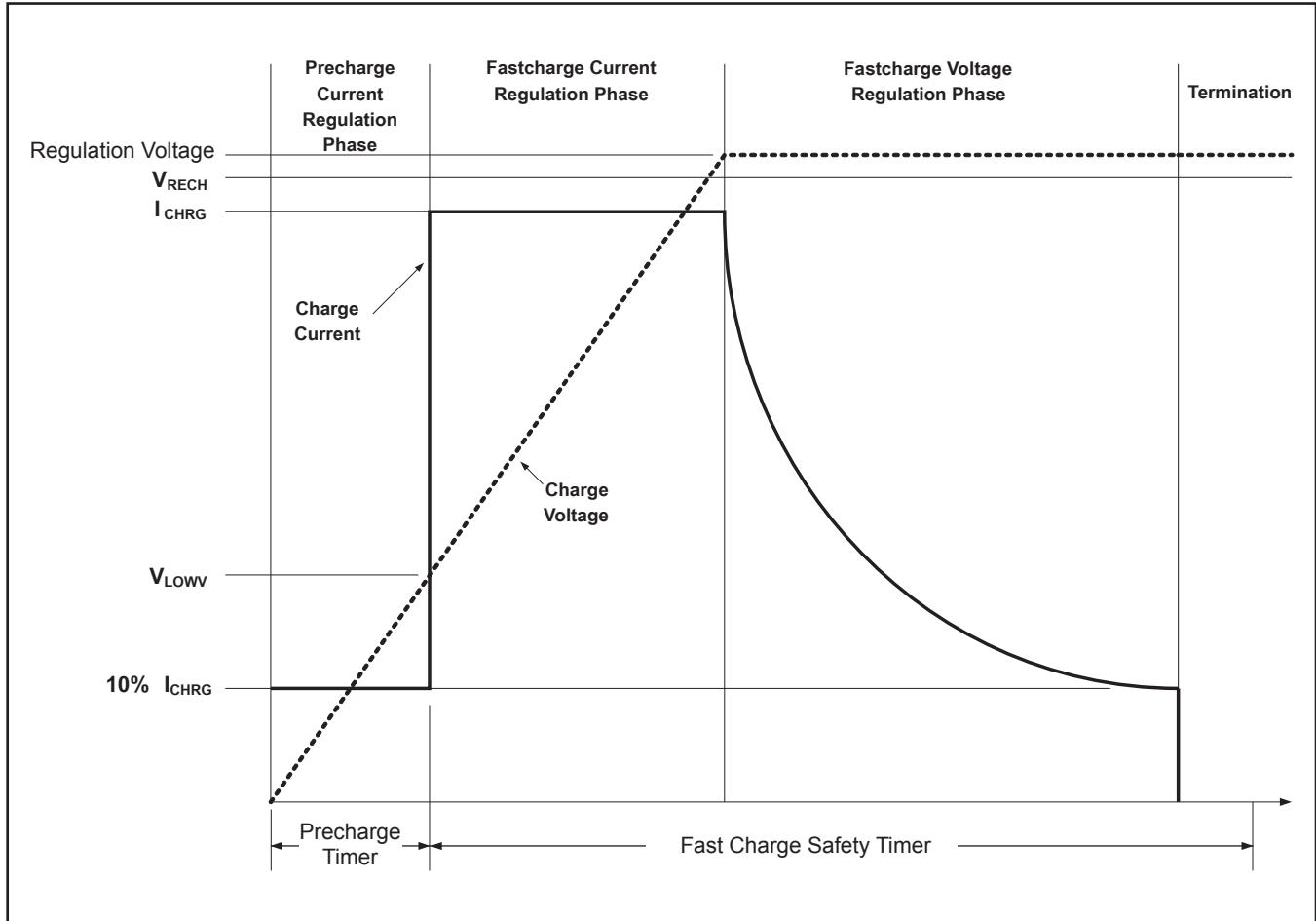

bq24170/172は、プリチャージ、定電流、定電圧の3つのフェーズによりバッテリを充電します。bq24170は1、2、または3セル(CELLピンで選択)のバッテリを充電でき、bq24172は最大3個の直列Li+セルに対して調整可能です。

電流が高速充電レートの10%に達すると、充電が終了します。安全対策として、設定可能な充電タイマも搭載されています。バッテリ電圧が内部のスレッショルドを下回ると、bq24170/172は自動的に充電サイクルを再開します。入力電圧がバッテリ電圧を下回ると、低静止電流のスリープ・モードに入ります。

bq24170/172は動的電源管理(DPM)機能を備え、入力電力

制限に近づくと充電電流を低下させることで、アダプタの過負荷を防ぎます。高精度な電流センス・アンプにより、アダプタからの入力電流を高い精度で検出することができ、システム全体の電力を監視できます。

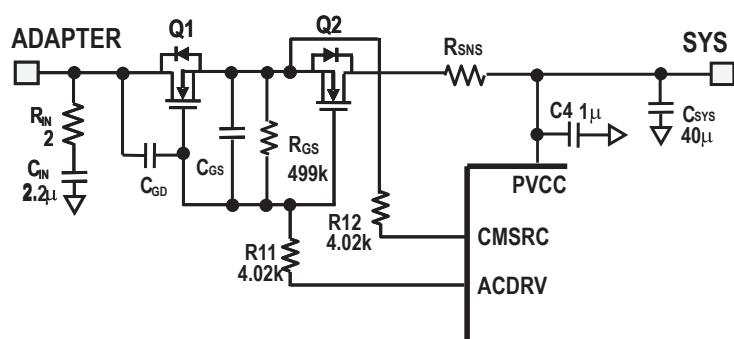

bq24170/172は、入力NMOSペアACFET(Q1)およびRBFET(Q2)上に電源バス選択ゲート・ドライバACDRV/CMSRCを備え、バッテリPMOSデバイス(Q3)上にBATDRVを備えています。適切なアダプタが存在する場合、システムは直接アダプタに接続されます。それ以外の場合、システムはバッテリに接続されます。また、このパワーパスにより、バッテリから入力側への電流供給を防止します。

1セル・アプリケーションで、バッテリが取り外し可能でない場合には、パワーパスの設計を簡略化してコストを低減するために、システムを直接バッテリに接続できます。この構成では、アダプタが過負荷になると、バッテリによって自動的にシステムを補助できます。

bq24170/172は、3.5mm×5.5mmの24ピン薄型QFNパッケージで提供されます。

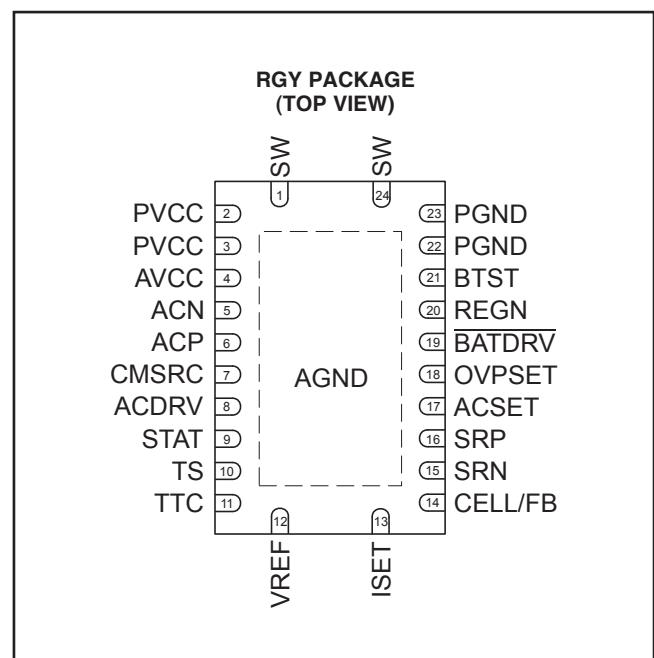

## ピン機能

| ピン    |       | 種類  | 説明                                                                                                                                                                                                                                        |

|-------|-------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 番号    | 名前    |     |                                                                                                                                                                                                                                           |

| 1, 24 | SW    | P   | スイッチング・ノード。充電電流出力インダクタを接続します。SWとBTSTの間には、0.047μFのブートストラップ・コンデンサを接続します。                                                                                                                                                                    |

| 2, 3  | PVCC  | P   | チャージャ入力電圧。PVCCとPGNDとの間に、ICにできる限り近づけて10μF以上のセラミック・コンデンサを接続します。                                                                                                                                                                             |

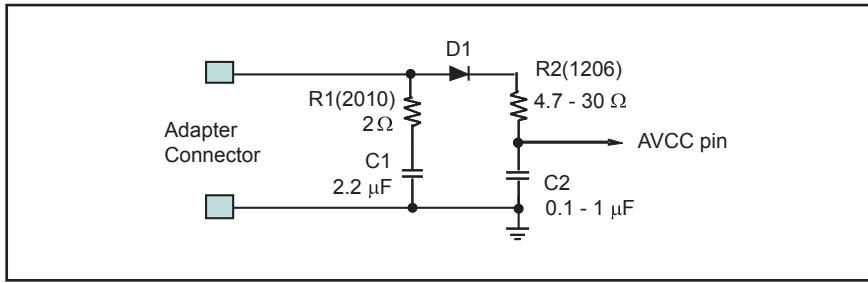

| 4     | AVCC  | P   | IC電力の+電源。AVCCとAGNDとの間に、ICにできる限り近づけて1μFのセラミック・コンデンサを接続します。ノイズをフィルタリングするため、入力側とAVCCピンとの間に10Ωの抵抗を接続します。5V入力の場合は、5Ωの抵抗を推奨します。                                                                                                                 |

| 5     | ACN   | I   | アダプタ電流センス抵抗、一入力。差動モードのフィルタリング用に、ACNとACPの間に0.1μFのセラミック・コンデンサを接続します。同相モードのフィルタリング用には、オプションでACNピンとAGNDの間に0.1μFのセラミック・コンデンサを接続します。                                                                                                            |

| 6     | ACP   | P/I | アダプタ電流センス抵抗、+入力。差動モードのフィルタリング用に、ACNとACPの間に0.1μFのセラミック・コンデンサを接続します。同相モードのフィルタリング用には、ACPピンとAGNDの間に0.1μFのセラミック・コンデンサを接続します。                                                                                                                  |

| 7     | CMSRC | O   | NチャネルACFETと逆流防止用MOSFET (RBFET) のコモン・ソースに接続します。ターンオン速度の制御用に、ACFETとRBFETのコモン・ソースとCMSRCピンとの間には、4kΩの抵抗を配置します。ACDRV-CMSRC間の抵抗は500kΩ以上とする必要があります。                                                                                               |

| 8     | ACDRV | O   | ACアダプタからシステム・スイッチ・ドライバへの出力。4kΩの抵抗を通してACFET Nチャネル・パワーMOSFETのゲート、および逆流防止用Nチャネル・パワーMOSFETに接続します。両方のFETをコモン・ソースとして接続します。内部ゲート駆動は非対称であり、BATDRVに対するBreak-Before-Make内部ロジックに加えて、すばやいターンオフと緩やかなターンオンを実現しています。                                     |

| 9     | STAT  | O   | オープン・ドレインの充電ステータス・ピン。パワーレールとの間に10kΩのプルアップ抵抗を備えています。STATピンは、LEDの駆動またはホスト・プロセッサとの通信に使用できます。このピンは、チャージャの各種動作を示します。充電の実行中は“Low”になります。充電完了時、またはSLEEPモード中は“High”になります。充電の中断、入力過電圧、タイマーエラー、バッテリ未検出などのエラー発生時は、0.5Hzの周波数で“High”/“Low”が切り替わります(点滅)。 |

| 10    | TS    | I   | 温度条件電圧入力。負温度係数のサーミスタを接続します。VREF-TS-AGND間の分圧抵抗を使用して、高温および低温の温度範囲を設定します。温度条件範囲は、5~40°Cまたはさらに広い範囲に設定できます。103ATサーミスタを推奨します。                                                                                                                   |

| 11    | TTC   | I   | 安全タイマおよび終了制御。このノードとAGNDとの間にコンデンサを接続して、高速充電安全タイマ(5.6min/nF)を設定します。ブリチャージ・タイマは、内部で30分に固定されています。充電終了機能および安全タイマをディスエーブルにするには、TTCを“Low”にします。安全タイマをディスエーブルにして充電終了をイネーブルにするには、TTCを“High”にします。                                                    |

| 12    | VREF  | P   | 3.3Vリファレンス電圧出力。VREFとAGNDとの間に、ICに近づけて1μFのセラミック・コンデンサを接続します。この電圧は、ISET、ACSET、およびTSピンの設定に使用できます。また、STATピンおよびCELLピンのプルアップ・レールとしても機能します。                                                                                                       |

## ピン機能 (続き)

| ピン       |                   | 種類  | 説明                                                                                                                                                                                                                 |

|----------|-------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 番号       | 名前                |     |                                                                                                                                                                                                                    |

| 13       | ISET              | I   | 高速充電電流設定点。VREF-ISET-AGND間の分圧回路を使用して、高速充電電流を設定します。<br>$I_{CHG} = \frac{V_{ISET}}{20 \times R_{SR}}$<br>プリチャージおよび終了電流は、内部で充電電流の1/10に設定されています。ISETピンの電圧が40mVを下回るとチャージャはディスエーブルになります。ISETピンの電圧が120mVを超えるとイネーブルになります。   |

| 14       | CELL<br>(bq24170) | I   | セル選択ピン。1セルの場合はCELLピンを“Low”にします。2セルの場合はオープン状態にします(0.8V~1.8V)。3セルの場合は“High”にします(セル当たり4.2Vに固定)。                                                                                                                       |

|          | FB<br>(bq24172)   |     | 充電電圧アナログ帰還調整。バッテリ端子から分圧抵抗回路の出力をこのノードに接続します。定電圧モードでは、出力電圧がFBピン上で2.1Vにレギュレーションされます。                                                                                                                                  |

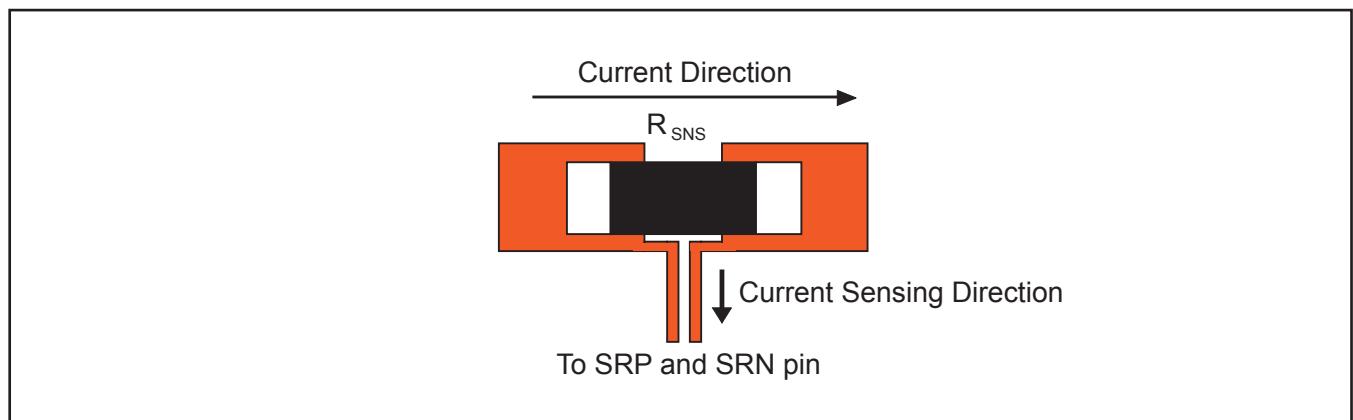

| 15       | SRN               | I   | 充電電流センス抵抗、一入力。差動モードのフィルタリング用に、SRNとSRPの間に0.1μFのセラミック・コンデンサを接続します。同相モードのフィルタリング用には、SRNピンとAGNDの間に0.1μFのセラミック・コンデンサを接続します。                                                                                             |

| 16       | SRP               | I/P | 充電電流センス抵抗、十入力。差動モードのフィルタリング用に、SRNとSRPの間に0.1μFのセラミック・コンデンサを接続します。同相モードのフィルタリング用には、SRPピンとAGNDの間に0.1μFのセラミック・コンデンサを接続します。                                                                                             |

| 17       | ACSET             | I   | 入力電流設定点。VREF-ACSET-AGND間の分圧回路を使用して、この値を設定します。<br>$I_{DPM} = \frac{V_{ACSET}}{20 \times R_{AC}}$                                                                                                                    |

| 18       | OVPSET            | I   | 有効入力電圧設定点。入力-OVPSET-AGND間の分圧回路を使用して、この電圧を設定します。電圧が内部の1.6Vリファレンスよりも高い場合は入力過電圧を示し、電圧が内部の0.5Vリファレンスよりも低い場合は入力低電圧を示します。いずれの場合も、充電は終了し、入力NMOSペアACFET/RBFETがオフになります。STATピンによって駆動されるLEDは点滅を続け、エラー状態を通知します。                |

| 19       | BATDRV            | O   | バッテリ放電MOSFETゲート・ドライバ出力。1kΩの抵抗を通してPチャネル・パワーMOSFET(BATFET)のゲートに接続します。BATFETのソースは、システムの負荷電圧ノードに接続します。BATFETのドレインは、バッテリ・パックの正端子に接続します。内部ゲート駆動は非対称であり、ACDRVに対するBreak-Before-Make内部ロジックに加えて、すばやいターンオフと緩やかなターンオンを実現しています。 |

| 20       | REGN              | P   | PWMローサイド・ドライバの+6V電源出力。REGNとPGNDとの間に、ICに近づけて1μFのセラミック・コンデンサを接続します。REGN-BTST間の内蔵ダイオードによって、ハイサイド・ドライバのブーストストラップ電圧を生成します。                                                                                              |

| 21       | BTST              | P   | PWMハイサイド・ドライバの+電源。SWとBTSTの間に0.047μFのブーストストラップ・コンデンサを接続します。                                                                                                                                                         |

| 22, 23   | PGND              | P   | パワー・グランド。高電流パワー・コンバータ・ノードのグランド接続です。PCBレイアウトでは、チャージャの入力/出力コンデンサのグランド接続に直接接続します。必ず、IC直下のサーマル・パッドを通してAGNDに接続してください。                                                                                                   |

| サーマル・パッド | AGND              | P   | ICの底面にある露出したパッド。サーマル・パッドは常に基板に半田付けし、また、高電流パワー・コンバータ用には、サーマル・パッド・プレーン上にビアを設けて、AGNDおよびグランド・プレーンにスター接続します。このパッドは、ICからの熱を放熱します。                                                                                        |

これらのデバイスは、限定的なESD(静電破壊)保護機能を内蔵しています。保存時または取り扱い時に、MOSゲートに対する静電破壊を防止するために、リード線どうしを短絡しておくか、デバイスを導電性のフォームに入れる必要があります。

## アプリケーション例

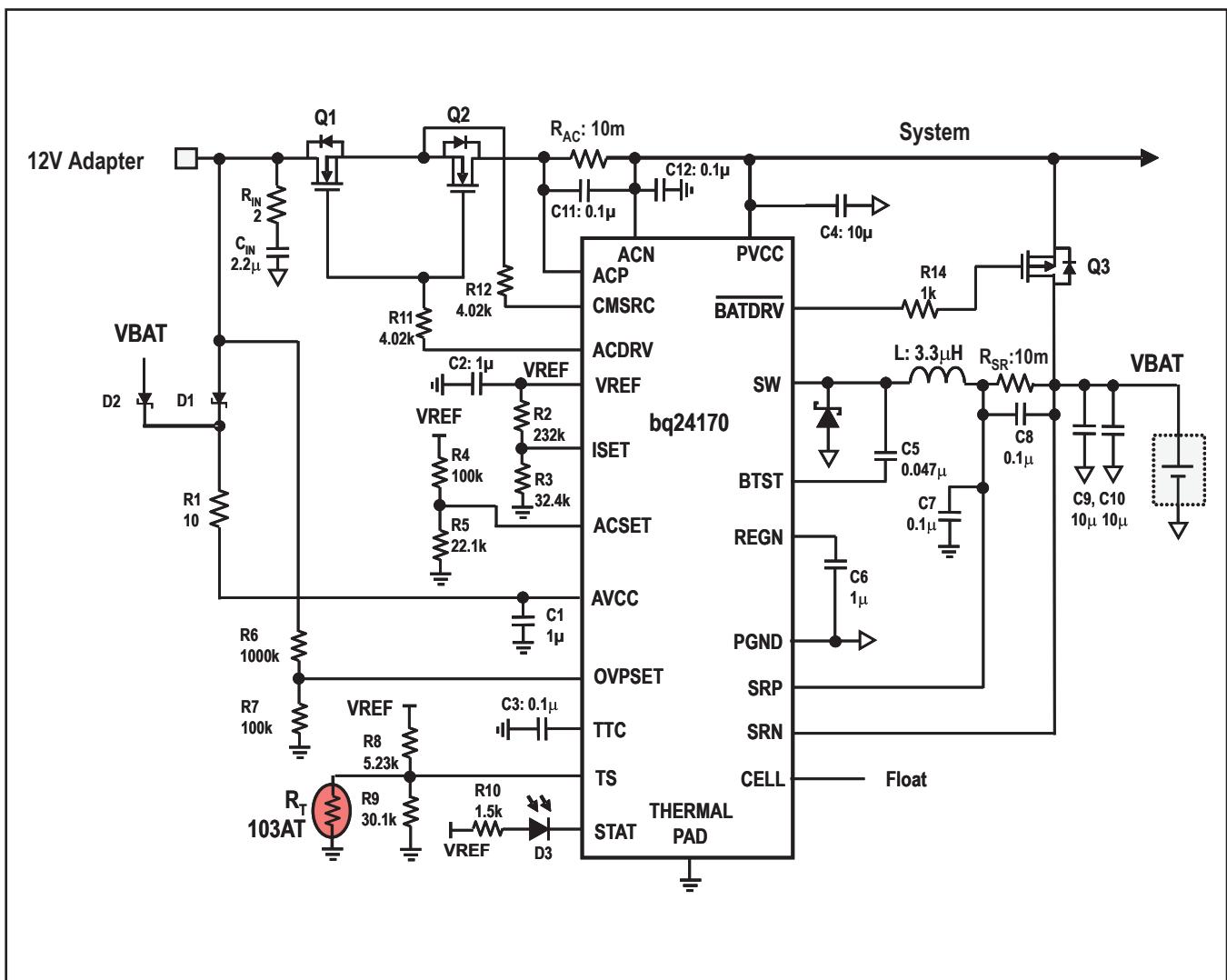

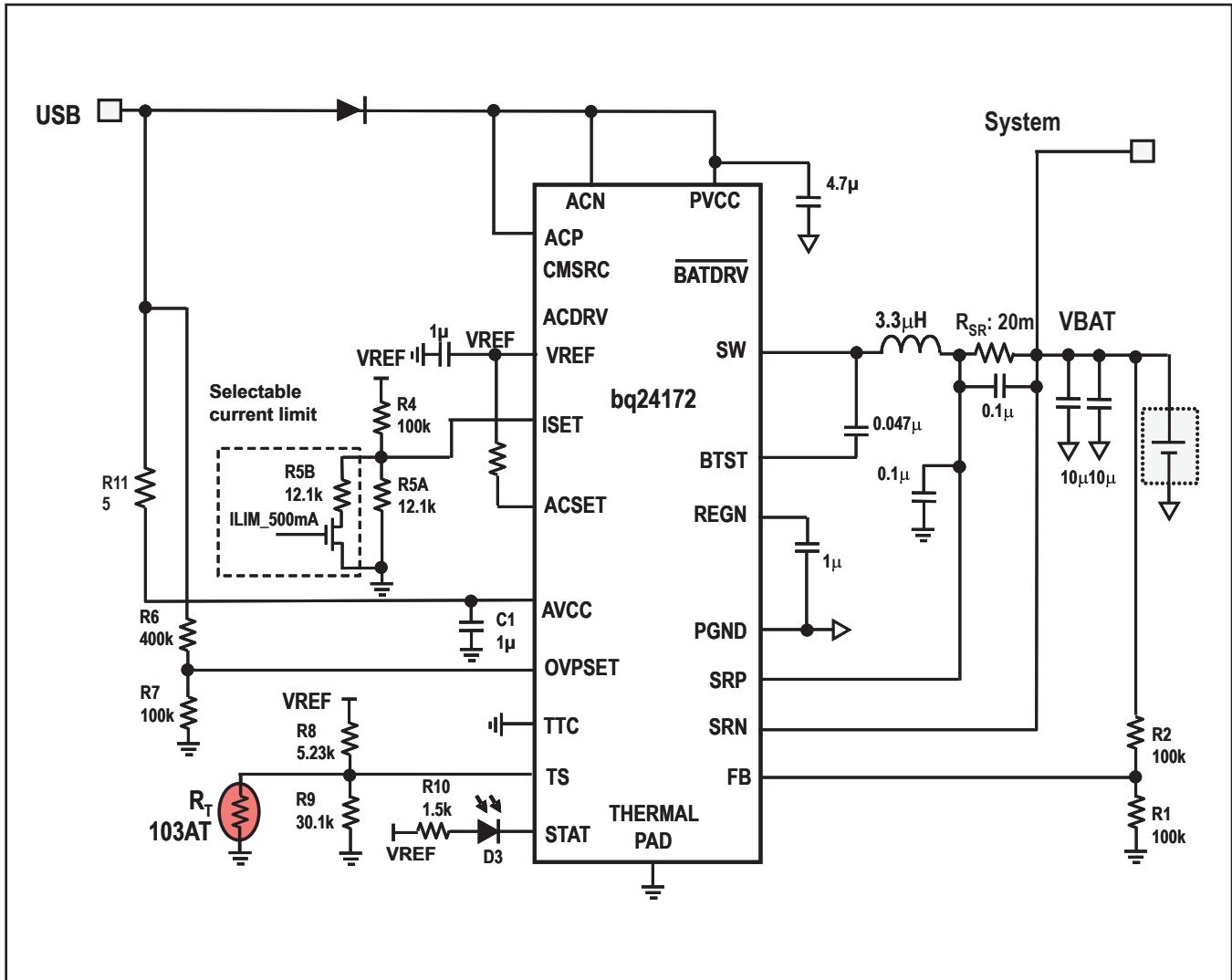

図 1. アプリケーション例回路図 (12V入力、2セル・バッテリ8.4V、充電電流2A、プリチャージ/終了電流0.2A、DPM電流3A、入力OVP = 18V、TS = 0~45°C)

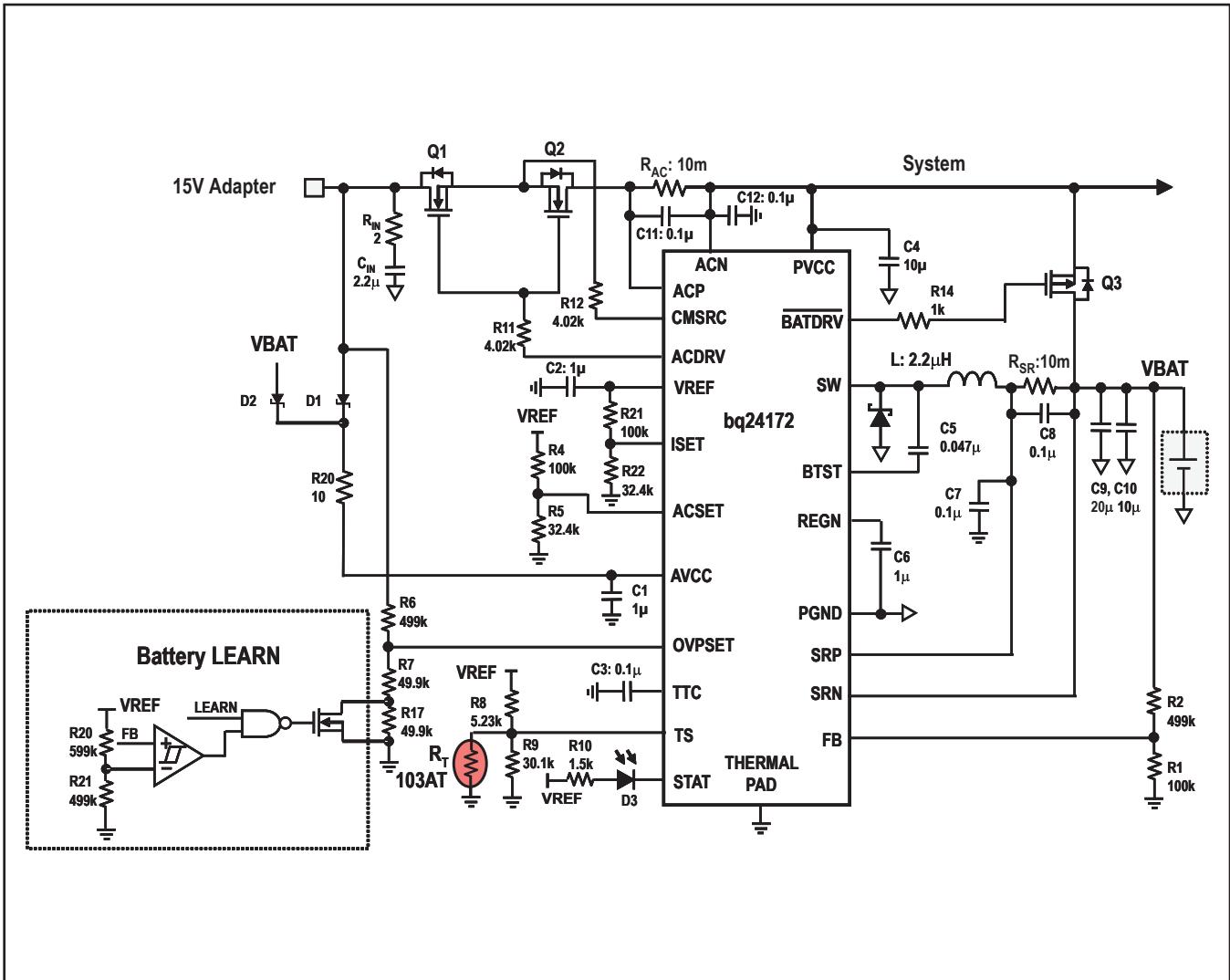

図 2. アプリケーション例回路図、バッテリ学習機能付き (15V入力、3セル・バッテリ12.6V、充電電流4A、プリチャージ/終了電流0.4A、DPM電流4A、TS = 0~45°C)

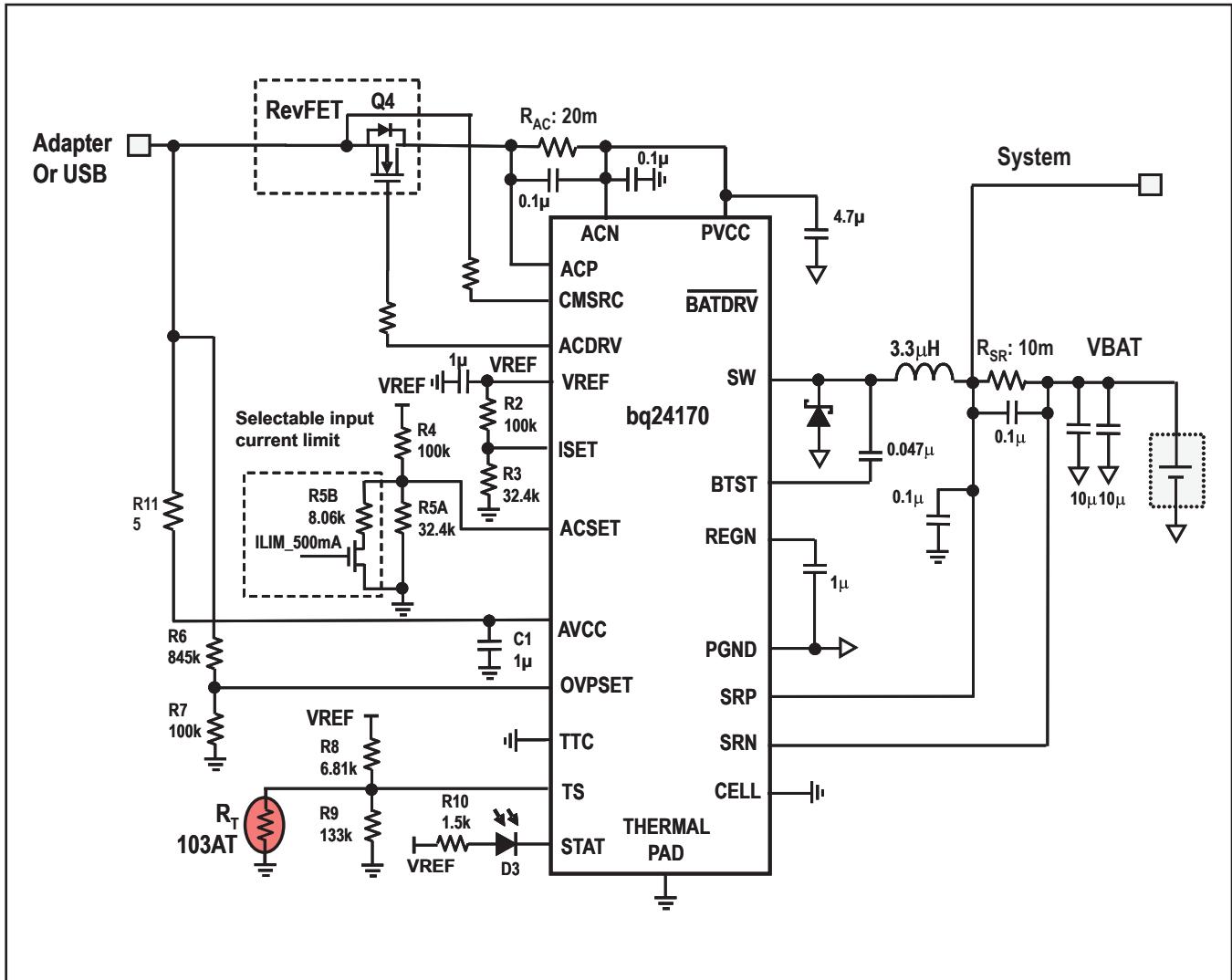

図 3. アプリケーション例回路図、取り外し不可能な1セル・バッテリ(USBまたはアダプタ、入力OVP = 15V、充電電流 = 最大4A、チャージ/終了電流0.4A、アダプタ電流2AまたはUSB電流500mA、TS = 5~40°C、システムをセンス抵抗の前に接続)

図 4. アプリケーション例回路図、取り外し不可能な1セル・バッテリ(USB、入力OVP = 8V、選択可能な充電電流制限900mAまたは500mA、TS = 0~45°C、システムをセンス抵抗の後に接続)

### ご発注の手引き<sup>(1)</sup>

| 部品番号    | 部品捺印    | パッケージ                  | 型番          | 数量   |

|---------|---------|------------------------|-------------|------|

| bq24170 | bq24170 | 24-Pin 3.5mm×5.5mm QFN | bq24170RGYR | 3000 |

|         |         |                        | bq24170RGYT | 250  |

| bq24172 | bq24172 | 24-Pin 3.5mm×5.5mm QFN | bq24172RGYR | 3000 |

|         |         |                        | bq24172RGYT | 250  |

(1) 最新のパッケージおよびご発注情報については、最新の英文データシートの巻末にある「付録:パッケージ・オプション」を参照するか、またはTIのWebサイト([www.ti.com](http://www.ti.com)または[www.tij.co.jp](http://www.tij.co.jp))をご覧ください。

## 絶対最大定格

動作温度範囲内(特に記述のない限り)<sup>(1)</sup> <sup>(2)</sup>

|                                      |                                       | VALUE      | 単位 |

|--------------------------------------|---------------------------------------|------------|----|

| Voltage range (with respect to AGND) | PVCC, AVCC, ACP, ACN, CMSRC, STAT     | -0.3 ~ 20  | V  |

|                                      | ACDRV, BTST                           | -0.3 ~ 26  |    |

|                                      | BATDRV, SRP, SRN                      | -0.3 ~ 20  |    |

|                                      | SW                                    | -2 ~ 20    |    |

|                                      | FB (bq24172)                          | -0.3 ~ 16  |    |

|                                      | OVPSET, REGN, TS, TTC, CELL (bq24170) | -0.3 ~ 7   |    |

|                                      | VREF, ISET, ACSET                     | -0.3 ~ 3.6 |    |

|                                      | PGND                                  | -0.3 ~ 0.3 |    |

| Maximum difference voltage           | SRP-SRN, ACP-ACN                      | -0.5 ~ 0.5 | V  |

| Junction temperature range, $T_J$    |                                       | -40 ~ 155  | °C |

| Storage temperature range, $T_{stg}$ |                                       | -55 ~ 155  | °C |

(1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を越える状態での本製品の機能動作は含まれていません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

(2) 特に指定のない限り、すべての電圧値はGNDを基準にしています。電流は、指定されたピンに流れ込む方向が正、ピンから流れ出る方向が負です。熱に関するパッケージの制限および考慮事項については、データブックの「パッケージ」セクションを参照してください。

## 熱特性について

| THERMAL METRIC <sup>(1)</sup> |                                                             | bq24170/2 | 単位   |

|-------------------------------|-------------------------------------------------------------|-----------|------|

|                               |                                                             | RGY       |      |

|                               |                                                             | 24 PINS   |      |

| $\theta_{JA}$                 | Junction-to-ambient thermal resistance <sup>(2)</sup>       | 35.7      | °C/W |

| $\Psi_{JT}$                   | Junction-to-top characterization parameter <sup>(3)</sup>   | 0.4       |      |

| $\Psi_{JB}$                   | Junction-to-board characterization parameter <sup>(4)</sup> | 31.2      |      |

- 従来の熱特性パラメータと新しい熱特性パラメータの詳細については、アプリケーション・レポート『IC Package Thermal Metrics』(SPRA953)を参照してください。

- 自然状態での接合部-周囲間熱抵抗は、JESD51-2aに記載の環境で、JESD51-7に規定されたJEDEC標準High-K基板上のシミュレーションによって求められます。

- 接合部-上面間の特性化パラメータ $\Psi_{JT}$ は、実システムでのデバイスの接合部温度を見積もるために使用され、JESD51-2a(セクション6および7)に規定される手順を用いて $\theta_{JA}$ を求めるシミュレーション・データから抽出されます。

- 接合部-基板間の特性化パラメータ $\Psi_{JB}$ は、実システムでのデバイスの接合部温度を見積もるために使用され、JESD51-2a(セクション6および7)に規定される手順を用いて $\theta_{JA}$ を求めるシミュレーション・データから抽出されます。

## 推奨動作条件

|                                             |           | MIN  | MAX  | 単位 |

|---------------------------------------------|-----------|------|------|----|

| Input voltage                               | $V_{IN}$  | 4.5  | 17   | V  |

| Output voltage                              | $V_{OUT}$ |      | 13.5 | V  |

| Output current ( $R_{SR} 10m\Omega$ )       | $I_{OUT}$ | 600  | 4    | A  |

| Maximum difference voltage                  | ACP - ACN | -200 | 200  | mV |

|                                             | SRP-SRN   | -200 | 200  | mV |

| Operation free-air temperature range, $T_A$ |           | -40  | 85   | °C |

## 電気的特性

4.5V ≤ V(PVCC, AVCC) ≤ 17V, -40°C < T<sub>J</sub> < +125°C、標準値はT<sub>A</sub> = 25°Cの値、AGND基準です(特に記述のない限り)。

| パラメータ                                   | テスト条件                                                                   | MIN                                                                                                                                                      | TYP                | MAX  | 単位 |

|-----------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|----|

| <b>OPERATING CONDITIONS</b>             |                                                                         |                                                                                                                                                          |                    |      |    |

| V <sub>AVCC_OP</sub>                    | AVCC input voltage operating range during charging                      | 4.5                                                                                                                                                      | 17                 | V    |    |

| <b>QUIESCENT CURRENTS</b>               |                                                                         |                                                                                                                                                          |                    |      |    |

| I <sub>BAT</sub>                        | Battery discharge current (sum of currents into AVCC, PVCC, ACP, ACN)   | V <sub>AVCC</sub> > V <sub>UVLO</sub> , V <sub>SRN</sub> > V <sub>AVCC</sub> (SLEEP), T <sub>J</sub> = 0°C to 85°C                                       | 15                 | μA   |    |

|                                         |                                                                         | BTST, SW, SRP, SRN, V <sub>AVCC</sub> > V <sub>UVLO</sub> , V <sub>AVCC</sub> > V <sub>SRN</sub> , ISET < 40mV, V <sub>BAT</sub> =12.6V, Charge disabled | 25                 |      |    |

|                                         |                                                                         | BTST, SW, SRP, SRN, V <sub>AVCC</sub> > V <sub>UVLO</sub> , V <sub>AVCC</sub> > V <sub>SRN</sub> , ISET > 120mV, V <sub>BAT</sub> =12.6V, Charge done    | 25                 |      |    |

| I <sub>AC</sub>                         | Adapter supply current (sum of current into AVCC, ACP, ACN)             | V <sub>AVCC</sub> > V <sub>UVLO</sub> , V <sub>AVCC</sub> > V <sub>SRN</sub> , ISET < 40mV, V <sub>BAT</sub> =12.6V, Charge disabled                     | 1.2                | mA   |    |

|                                         |                                                                         | V <sub>AVCC</sub> > V <sub>UVLO</sub> , V <sub>AVCC</sub> > V <sub>SRN</sub> , ISET > 120mV, Charge enabled, no switching                                | 2.5                |      |    |

|                                         |                                                                         | V <sub>AVCC</sub> > V <sub>UVLO</sub> , V <sub>AVCC</sub> > V <sub>SRN</sub> , ISET > 120mV, Charge enabled, switching                                   | 15 <sup>(1)</sup>  |      |    |

| <b>CHARGE VOLTAGE REGULATION</b>        |                                                                         |                                                                                                                                                          |                    |      |    |

| V <sub>BAT_REG</sub>                    | SRN regulation voltage (bq24170)                                        | CELL to AGND, 1 cell, measured on SRN                                                                                                                    | 4.2                | V    |    |

|                                         |                                                                         | CELL floating, 2 cells, measured on SRN                                                                                                                  | 8.4                |      |    |

|                                         |                                                                         | CELL to VREF, 3 cells, measured on SRN                                                                                                                   | 12.6               |      |    |

| V <sub>FB_REG</sub>                     | Feedback regulation voltage (bq24172)                                   | Measured on FB                                                                                                                                           | 2.1                | V    |    |

| V <sub>ISET_CD</sub>                    | Charge voltage regulation accuracy                                      | T <sub>J</sub> = 0°C to 85°C                                                                                                                             | -0.5%              | 0.5% |    |

|                                         |                                                                         | T <sub>J</sub> = -40°C to 125°C                                                                                                                          | -0.7%              |      |    |

| I <sub>FB</sub>                         | Leakage current into FB pin (bq24172)                                   | V <sub>FB</sub> = 2.1 V                                                                                                                                  | 100                | nA   |    |

| <b>CURRENT REGULATION – FAST CHARGE</b> |                                                                         |                                                                                                                                                          |                    |      |    |

| V <sub>ISET</sub>                       | ISET Voltage Range                                                      | R <sub>SENSE</sub> = 10mΩ                                                                                                                                | 0.12               | 0.8  | V  |

| K <sub>ISET</sub>                       | Charge Current Set Factor (Amps of Charge Current per Volt on ISET pin) | R <sub>SENSE</sub> = 10mΩ                                                                                                                                | 5                  | A/V  |    |

| V <sub>ISET_CD</sub>                    | Charge Current Regulation Accuracy (with Schottky diode on SW)          | V <sub>SRP-SRN</sub> = 40 mV                                                                                                                             | -4%                |      |    |

|                                         |                                                                         | V <sub>SRP-SRN</sub> = 20 mV                                                                                                                             | -7%                |      |    |

|                                         |                                                                         | V <sub>SRP-SRN</sub> = 5 mV                                                                                                                              | -25%               |      |    |

| V <sub>ISET_CD</sub>                    | Charge Disable Threshold                                                | ISET falling                                                                                                                                             | 40                 | 50   | mV |

| V <sub>ISET_CE</sub>                    | Charge Enable Threshold                                                 | ISET rising                                                                                                                                              | 100                | 120  | mV |

| I <sub>ISET</sub>                       | Leakage Current into ISET                                               | V <sub>ISET</sub> = 2V                                                                                                                                   | 100                | nA   |    |

| <b>INPUT CURRENT REGULATION</b>         |                                                                         |                                                                                                                                                          |                    |      |    |

| K <sub>DPM</sub>                        | Input DPM Current Set Factor (Amps of Input Current per Volt on ACSET)  | R <sub>SENSE</sub> = 10mΩ                                                                                                                                | 5                  | A/V  |    |

| V <sub>ISET_CD</sub>                    | Input DPM Current Regulation Accuracy (with Schottky diode on SW)       | V <sub>ACP-ACN</sub> = 80 mV                                                                                                                             | -4%                |      |    |

|                                         |                                                                         | V <sub>ACP-ACN</sub> = 40 mV                                                                                                                             | -9%                |      |    |

|                                         |                                                                         | V <sub>ACP-ACN</sub> = 20 mV                                                                                                                             | -15%               |      |    |

|                                         |                                                                         | V <sub>ACP-ACN</sub> = 5 mV                                                                                                                              | -20%               |      |    |

|                                         |                                                                         | V <sub>ACP-ACN</sub> = 2.5 mV                                                                                                                            | -40%               |      |    |

| I <sub>ACSET</sub>                      | Leakage Current into ACSET pin                                          | V <sub>ACSET</sub> = 2V                                                                                                                                  | 100                | nA   |    |

| <b>CURRENT REGULATION – PRE-CHARGE</b>  |                                                                         |                                                                                                                                                          |                    |      |    |

| K <sub>IPRECHG</sub>                    | Precharge current set factor                                            | Percentage of fast charge current                                                                                                                        | 10% <sup>(2)</sup> |      |    |

| V <sub>ISET_CD</sub>                    | Precharge current regulation accuracy                                   | V <sub>SRP-SRN</sub> = 4 mV                                                                                                                              | -25%               |      |    |

|                                         |                                                                         | V <sub>SRP-SRN</sub> = 2 mV                                                                                                                              | -40%               |      |    |

(1) 設計で規定されています。

(2) 10mΩセンス抵抗の最小電流は120mAです。

## 電気的特性

4.5V ≤ V(PVCC, AVCC) ≤ 17V, -40°C < T<sub>J</sub> < +125°C、標準値はT<sub>A</sub> = 25°Cの値、AGND基準です(特に記述のない限り)。

| パラメータ                                                    |                                                                                                                                                         | テスト条件                                                                         | MIN                | TYP  | MAX  | 単位 |

|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------|------|------|----|

| <b>CHARGE TERMINATION</b>                                |                                                                                                                                                         |                                                                               |                    |      |      |    |

| K <sub>TERM</sub>                                        | Termination current set factor                                                                                                                          | Percentage of fast charge current                                             | 10% <sup>(3)</sup> |      |      |    |

| t <sub>TERM_DEG</sub>                                    | Termination current regulation accuracy                                                                                                                 | V <sub>SRP-SRN</sub> = 4 mV                                                   | -25%               | 25%  |      |    |

|                                                          |                                                                                                                                                         | V <sub>SRP-SRN</sub> = 2 mV                                                   | -40%               | 40%  |      |    |

| t <sub>TERM</sub>                                        | Deglitch time for termination (both edges)                                                                                                              |                                                                               | 100                |      |      | ms |

| t <sub>QUAL</sub>                                        | Termination qualification time                                                                                                                          | V <sub>SRN</sub> > V <sub>RECH</sub> and I <sub>CHG</sub> < I <sub>TERM</sub> | 250                |      |      | ms |

| I <sub>QUAL</sub>                                        | Termination qualification current                                                                                                                       | Discharge current once termination is detected                                | 2                  |      |      | mA |

| <b>INPUT UNDER-VOLTAGE LOCK-OUT COMPARATOR (UVLO)</b>    |                                                                                                                                                         |                                                                               |                    |      |      |    |

| V <sub>UVLO</sub>                                        | AC under-voltage rising threshold                                                                                                                       | Measure on AVCC                                                               | 3.4                | 3.6  | 3.8  | V  |

| V <sub>UVLO_HYS</sub>                                    | AC under-voltage hysteresis, falling                                                                                                                    | Measure on AVCC                                                               | 300                |      |      | mV |

| <b>SLEEP COMPARATOR (REVERSE DISCHARGING PROTECTION)</b> |                                                                                                                                                         |                                                                               |                    |      |      |    |

| V <sub>SLEEP</sub>                                       | SLEEP mode threshold                                                                                                                                    | V <sub>AVCC</sub> – V <sub>SRN</sub> falling                                  | 50                 | 90   | 150  | mV |

| V <sub>SLEEP_HYS</sub>                                   | SLEEP mode hysteresis                                                                                                                                   | V <sub>AVCC</sub> – V <sub>SRN</sub> rising                                   | 200                |      |      | mV |

| t <sub>SLEEP_FALL_CD</sub>                               | SLEEP deglitch to disable charge                                                                                                                        | V <sub>AVCC</sub> – V <sub>SRN</sub> falling                                  | 1                  |      |      | ms |

| t <sub>SLEEP_FALL_FETOFF</sub>                           | SLEEP deglitch to turn off input FETs                                                                                                                   | V <sub>AVCC</sub> – V <sub>SRN</sub> falling                                  | 5                  |      |      | ms |

| t <sub>SLEEP_FALL</sub>                                  | Deglitch to enter SLEEP mode, disable VREF and enter low quiescent mode                                                                                 | V <sub>AVCC</sub> – V <sub>SRN</sub> falling                                  | 100                |      |      | ms |

| t <sub>SLEEP_PWRUP</sub>                                 | Deglitch to exit SLEEP mode, and enable VREF                                                                                                            | V <sub>AVCC</sub> – V <sub>SRN</sub> rising                                   | 30                 |      |      | ms |

| <b>ACN-SRN COMPARATOR</b>                                |                                                                                                                                                         |                                                                               |                    |      |      |    |

| V <sub>ACN-SRN</sub>                                     | Threshold to turn on BATFET                                                                                                                             | V <sub>ACN-SRN</sub> falling                                                  | 150                | 220  | 300  | mV |

| V <sub>ACN-SRN_HYS</sub>                                 | Hysteresis to turn off BATFET                                                                                                                           | V <sub>ACN-SRN</sub> rising                                                   | 100                |      |      | mV |

| t <sub>BATFETOFF_DEG</sub>                               | Deglitch to turn on BATFET                                                                                                                              | V <sub>ACN-SRN</sub> falling                                                  | 2                  |      |      | ms |

| t <sub>BATFETON_DEG</sub>                                | Deglitch to turn off BATFET                                                                                                                             | V <sub>ACN-SRN</sub> rising                                                   | 50                 |      |      | μs |

| <b>BAT LOWV COMPARATOR</b>                               |                                                                                                                                                         |                                                                               |                    |      |      |    |

| V <sub>LOWV</sub>                                        | Precharge to fast charge transition                                                                                                                     | bq24170, CELL to AGND, 1 cell, measure on SRN                                 | 2.87               | 2.9  | 2.93 | V  |

|                                                          |                                                                                                                                                         | bq24170, CELL floating, 2 cells, measure on SRN                               | 5.74               | 5.8  | 5.86 |    |

|                                                          |                                                                                                                                                         | bq24170, CELL to VREF, 3 cells, measure on SRN                                | 8.61               | 8.7  | 8.79 |    |

|                                                          |                                                                                                                                                         | bq24172, measure on FB                                                        | 1.43               | 1.45 | 1.47 |    |

| V <sub>LOWV_HYS</sub>                                    | Fast charge to precharge hysteresis                                                                                                                     | bq24170, CELL to AGND, 1 cell, measure on SRN                                 | 200                |      |      | mV |

|                                                          |                                                                                                                                                         | bq24170, CELL floating, 2 cells, measure on SRN                               | 400                |      |      |    |

|                                                          |                                                                                                                                                         | bq24170, CELL to VREF, 3 cells, measure on SRN                                | 600                |      |      |    |

|                                                          |                                                                                                                                                         | bq24172, measure on FB                                                        | 100                |      |      |    |

| t <sub>pre2fas</sub>                                     | V <sub>LOWV</sub> rising deglitch                                                                                                                       | Delay to start fast charge current                                            | 25                 |      |      | ms |

| t <sub>fast2pre</sub>                                    | V <sub>LOWV</sub> falling deglitch                                                                                                                      | Delay to start precharge current                                              | 25                 |      |      | ms |

| <b>RECHARGE COMPARATOR</b>                               |                                                                                                                                                         |                                                                               |                    |      |      |    |

| V <sub>RECHG</sub>                                       | Recharge Threshold, below regulation voltage limit, V <sub>BAT_REG</sub> -V <sub>SRN</sub> (bq24170), or V <sub>FB_REG</sub> -V <sub>FB</sub> (bq24172) | bq24170, CELL to AGND, 1 cell, measure on SRN                                 | 70                 | 100  | 130  | mV |

|                                                          |                                                                                                                                                         | bq24170, CELL floating, 2 cells, measure on SRN                               | 140                | 200  | 260  |    |

|                                                          |                                                                                                                                                         | bq24170, CELL to VREF, 3 cells, measure on SRN                                | 210                | 300  | 390  |    |

|                                                          |                                                                                                                                                         | bq24172, measure on FB                                                        | 35                 | 50   | 65   |    |

| t <sub>RECH_RISE_DEG</sub>                               | V <sub>RECHG</sub> rising deglitch                                                                                                                      | V <sub>FB</sub> decreasing below V <sub>RECHG</sub>                           | 10                 |      |      | ms |

| t <sub>RECH_FALL_DEG</sub>                               | V <sub>RECHG</sub> falling deglitch                                                                                                                     | V <sub>FB</sub> increasing above V <sub>RECHG</sub>                           | 10                 |      |      | ms |

(3) 10mΩセンス抵抗の最小電流は120mAです。

## 電気的特性

4.5V ≤ V(PVCC, AVCC) ≤ 17V, -40°C < T<sub>J</sub> < +125°C、標準値はT<sub>A</sub> = 25°Cの値、AGND基準です(特に記述のない限り)。

| パラメータ                                                   | テスト条件                                                                  | MIN                                                                                                                                     | TYP   | MAX   | 単位    |

|---------------------------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|

| <b>BAT OVER-VOLTAGE COMPARATOR</b>                      |                                                                        |                                                                                                                                         |       |       |       |

| V <sub>OV_RISE</sub>                                    | Over-voltage rising threshold                                          | As percentage of V <sub>BAT_REG</sub> (bq24170) or V <sub>FB_REG</sub> (bq24172)                                                        | 104%  |       |       |

| V <sub>OV_FALL</sub>                                    | Over-voltage falling threshold                                         | As percentage of V <sub>SRN</sub> (bq24170) or V <sub>FB_REG</sub> (bq24172)                                                            | 102%  |       |       |

| <b>INPUT OVER-VOLTAGE COMPARATOR (ACOV)</b>             |                                                                        |                                                                                                                                         |       |       |       |

| V <sub>ACOV</sub>                                       | AC Over-Voltage Rising Threshold to turn off ACFET                     | OVPSET rising                                                                                                                           | 1.55  | 1.6   | 1.65  |

| V <sub>ACOV_HYS</sub>                                   | AC over-voltage falling hysteresis                                     | OVPSET falling                                                                                                                          | 50    |       | mV    |

| t <sub>ACOV_RISE_DEG</sub>                              | AC Over-Voltage Rising Deglitch to turn off ACFET and Disable Charge   | OVPSET rising                                                                                                                           | 1     |       | μs    |

| t <sub>ACOV_FALL_DEG</sub>                              | AC Over-Voltage Falling Deglitch to Turn on ACFET                      | OVPSET falling                                                                                                                          | 30    |       | ms    |

| <b>INPUT UNDER-VOLTAGE COMPARATOR (ACUV)</b>            |                                                                        |                                                                                                                                         |       |       |       |

| V <sub>ACUV</sub>                                       | AC Under-Voltage Falling Threshold to turn off ACFET                   | OVPSET falling                                                                                                                          | 0.45  | 0.5   | 0.55  |

| V <sub>ACUV_HYS</sub>                                   | AC Under-Voltage Rising Hysteresis                                     | OVPSET rising                                                                                                                           | 100   |       | mV    |

| t <sub>ACOV_FALL_DEG</sub>                              | AC Under-Voltage Falling Deglitch to turn off ACFET and Disable Charge | OVPSET falling                                                                                                                          | 1     |       | μs    |

| t <sub>ACOV_RISE_DEG</sub>                              | AC Under-Voltage Rising Deglitch to turn on ACFET                      | OVPSET rising                                                                                                                           | 30    |       | ms    |

| <b>THERMAL REGULATION</b>                               |                                                                        |                                                                                                                                         |       |       |       |

| T <sub>J_REG</sub>                                      | Junction Temperature Regulation Accuracy                               | ISET > 120mV, Charging                                                                                                                  | 120   |       | °C    |

| <b>THERMAL SHUTDOWN COMPARATOR</b>                      |                                                                        |                                                                                                                                         |       |       |       |

| T <sub>SHUT</sub>                                       | Thermal shutdown rising temperature                                    | Temperature rising                                                                                                                      | 150   |       | °C    |

| T <sub>SHUT_HYS</sub>                                   | Thermal shutdown hysteresis                                            | Temperature falling                                                                                                                     | 20    |       | °C    |

| t <sub>SHUT_RISE_DEG</sub>                              | Thermal shutdown rising deglitch                                       | Temperature rising                                                                                                                      | 100   |       | μs    |

| t <sub>SHUT_FALL_DEG</sub>                              | Thermal shutdown falling deglitch                                      | Temperature falling                                                                                                                     | 10    |       | ms    |

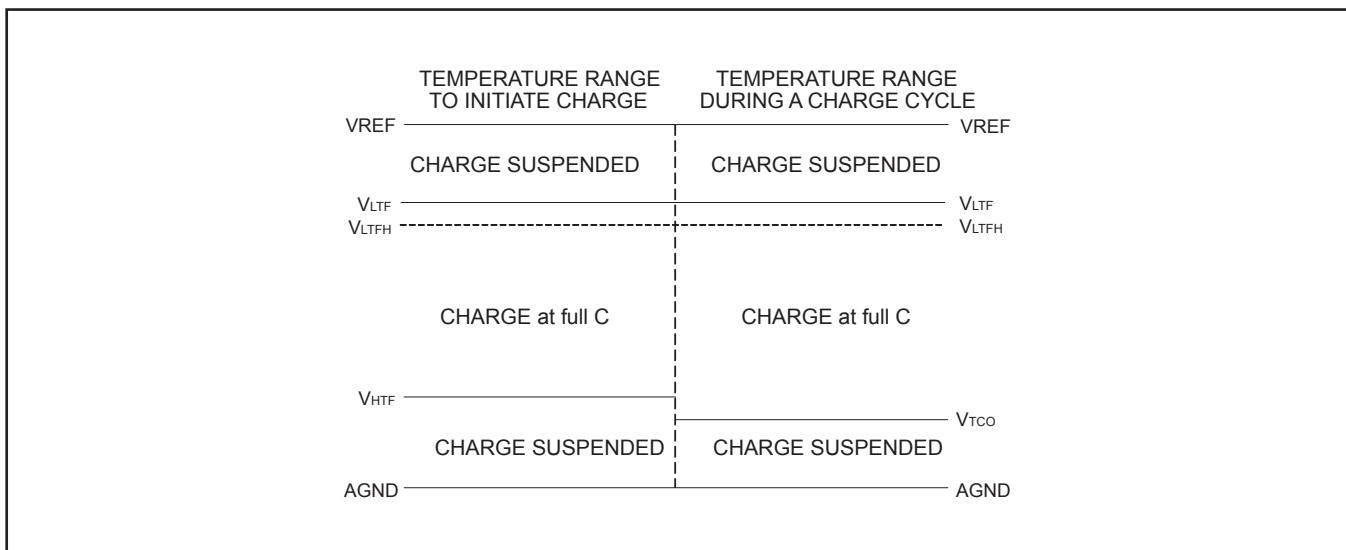

| <b>TERMISTOR COMPARATOR</b>                             |                                                                        |                                                                                                                                         |       |       |       |

| V <sub>LTF</sub>                                        | Cold Temperature Threshold, TS pin Voltage Rising Threshold            | Charger suspends charge. As percentage to V <sub>VREF</sub>                                                                             | 72.5% | 73.5% | 74.5% |

| V <sub>LTF_HYS</sub>                                    | Cold Temperature Hysteresis, TS pin Voltage Falling                    | As percentage to V <sub>VREF</sub>                                                                                                      | 0.2%  | 0.4%  | 0.6%  |

| V <sub>HTF</sub>                                        | Hot Temperature TS pin voltage rising Threshold                        | As percentage to V <sub>VREF</sub>                                                                                                      | 46.6% | 47.2% | 48.8% |

| V <sub>TCO</sub>                                        | Cut-off Temperature TS pin voltage falling Threshold                   | As percentage to V <sub>VREF</sub>                                                                                                      | 44.2% | 44.7% | 45.2% |

| t <sub>TS_CHG_SUS</sub>                                 | Deglitch time for Temperature Out of Range Detection                   | V <sub>TS</sub> > V <sub>LTF</sub> , or V <sub>TS</sub> < V <sub>TCO</sub> , or V <sub>TS</sub> < V <sub>HTF</sub>                      | 20    |       | ms    |

| t <sub>TS_CHG_RESUME</sub>                              | Deglitch time for Temperature in Valid Range Detection                 | V <sub>TS</sub> < V <sub>LTF</sub> - V <sub>LTF_HYS</sub> or V <sub>TS</sub> > V <sub>TCO</sub> , or V <sub>TS</sub> > V <sub>HTF</sub> | 400   |       | ms    |

| <b>CHARGE OVER-CURRENT COMPARATOR (CYCLE-BY-CYCLE)</b>  |                                                                        |                                                                                                                                         |       |       |       |

| V <sub>OCP_CHRG</sub>                                   | Charge Over-Current Rising Threshold, V <sub>SRP</sub> >2.2V           | Current as percentage of fast charge current                                                                                            | 160%  |       |       |

| V <sub>OCP_MIN</sub>                                    | Charge Over-Current Limit Min, V <sub>SRP</sub> <2.2V                  | Measure V <sub>SRP-SRN</sub>                                                                                                            | 45    |       | mV    |

| V <sub>OCP_MAX</sub>                                    | Charge Over-Current Limit Max, V <sub>SRP</sub> >2.2V                  | Measure V <sub>SRP-SRN</sub>                                                                                                            | 75    |       | mV    |

| <b>HSFET OVER-CURRENT COMPARATOR (CYCLE-BY-CYCLE)</b>   |                                                                        |                                                                                                                                         |       |       |       |

| I <sub>OCP_HSFET</sub>                                  | Current limit on HSFET                                                 | Measure on HSFET                                                                                                                        | 8     | 11.5  | A     |

| <b>CHARGE UNDER-CURRENT COMPARATOR (CYCLE-BY-CYCLE)</b> |                                                                        |                                                                                                                                         |       |       |       |

| V <sub>UCP</sub>                                        | Charge under-current falling threshold                                 | Measure on V <sub>(SRP-SRN)</sub>                                                                                                       | 1     | 5     | 9     |

|                                                         |                                                                        |                                                                                                                                         |       |       | mV    |

## 電気的特性

4.5V ≤ V(PVCC, AVCC) ≤ 17V, -40°C < T<sub>J</sub> < +125°C、標準値はT<sub>A</sub> = 25°Cの値、AGND基準です(特に記述のない限り)。

| パラメータ                                 | テスト条件                                                                                | MIN                                                                                                           | TYP                | MAX  | 単位      |

|---------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--------------------|------|---------|

| <b>BAT SHORT COMPARATOR</b>           |                                                                                      |                                                                                                               |                    |      |         |

| V <sub>BATSH</sub> T                  | Battery short falling threshold                                                      | Measure on SRN                                                                                                | 2                  |      | V       |

| V <sub>BATSH</sub> _HYS               | Battery short rising hysteresis                                                      | Measure on SRN                                                                                                | 200                |      | mV      |

| t <sub>BATSH</sub> _DEG               | Deglitch on both edges                                                               |                                                                                                               | 1                  |      | μs      |

| V <sub>BATSH</sub> T                  | Charge Current during BATSHORT                                                       | Percentage of fast charge current                                                                             | 10% <sup>(4)</sup> |      |         |

| <b>VREF REGULATOR</b>                 |                                                                                      |                                                                                                               |                    |      |         |

| V <sub>VREF</sub> _REG                | VREF regulator voltage                                                               | V <sub>AVCC</sub> > V <sub>UVLO</sub> , No load                                                               | 3.267              | 3.3  | 3.333   |

| I <sub>VREF</sub> _LIM                | VREF current limit                                                                   | V <sub>VREF</sub> = 0 V, V <sub>AVCC</sub> > V <sub>UVLO</sub>                                                | 35                 | 90   | mA      |

| <b>REGN REGULATOR</b>                 |                                                                                      |                                                                                                               |                    |      |         |

| V <sub>REGN</sub> _REG                | REGN regulator voltage                                                               | V <sub>AVCC</sub> > 10 V, ISET > 120 mV                                                                       | 5.7                | 6.0  | 6.3     |

| I <sub>REGN</sub> _LIM                | REGN current limit                                                                   | V <sub>REGN</sub> = 0 V, V <sub>AVCC</sub> > 10 V, ISET > 120 mV                                              | 40                 | 120  | mA      |

| <b>TTC INPUT</b>                      |                                                                                      |                                                                                                               |                    |      |         |

| t <sub>prechrg</sub>                  | Precharge Safety Timer                                                               | Precharge time before fault occurs                                                                            | 1620               | 1800 | 1980    |

| t <sub>fastchrg</sub>                 | Fast Charge Timer Range                                                              | T <sub>chg</sub> =C <sub>TTC</sub> *K <sub>TTC</sub>                                                          | 1                  | 10   | hr      |

|                                       | Fast Charge Timer Accuracy                                                           |                                                                                                               | -10%               | 10%  |         |

| K <sub>TTC</sub>                      | Timer Multiplier                                                                     |                                                                                                               | 5.6                |      | min/nF  |

| V <sub>TTC</sub> _LOW                 | TTC Low Threshold                                                                    | TTC falling                                                                                                   |                    | 0.4  | V       |

| I <sub>TTC</sub>                      | TTC Source/Sink Current                                                              |                                                                                                               | 45                 | 50   | μA      |

| V <sub>TTC</sub> _OSC_HI              | TTC oscillator high threshold                                                        |                                                                                                               |                    | 1.5  | V       |

| V <sub>TTC</sub> _OSC_LO              | TTC oscillator low threshold                                                         |                                                                                                               |                    | 1    | V       |

| <b>BATTERY SWITCH (BATFET) DRIVER</b> |                                                                                      |                                                                                                               |                    |      |         |

| R <sub>DS</sub> _BAT_OFF              | BATFET Turn-off Resistance                                                           | V <sub>AVCC</sub> > 5V                                                                                        |                    | 100  | Ω       |

| R <sub>DS</sub> _BAT_ON               | BATFET Turn-on Resistance                                                            | V <sub>AVCC</sub> > 5V                                                                                        |                    | 20   | kΩ      |

| V <sub>BATDRV</sub> _REG              | BATFET Drive Voltage                                                                 | V <sub>BATDRV</sub> _REG =V <sub>ACN</sub> - V <sub>BATDRV</sub> when V <sub>AVCC</sub> > 5V and BATFET is on | 4.2                | 7    | V       |

| t <sub>BATFET</sub> _DEG              | BATFET Power-up Delay to turn off BATFET after adapter is detected                   |                                                                                                               |                    | 30   | ms      |

| <b>AC SWITCH (ACFET) DRIVER</b>       |                                                                                      |                                                                                                               |                    |      |         |

| I <sub>ACFET</sub>                    | ACDRV Charge Pump Current Limit                                                      | V <sub>ACDRV</sub> - V <sub>CMSRC</sub> = 5V                                                                  | 60                 |      | μA      |

| V <sub>ACDRV</sub> _REG               | Gate Drive Voltage on ACFET                                                          | V <sub>ACDRV</sub> - V <sub>CMSRC</sub> when V <sub>AVCC</sub> > V <sub>UVLO</sub>                            | 4.2                | 6    | V       |

| R <sub>ACDRV</sub> _LOAD              | Maximum load between ACDRV and CMSRC                                                 |                                                                                                               | 500                |      | kΩ      |

| <b>AC/BAT SWITCH DRIVER TIMING</b>    |                                                                                      |                                                                                                               |                    |      |         |

| t <sub>DRV</sub> _DEAD                | Driver Dead Time                                                                     | Dead Time when switching between ACFET and BATFET                                                             | 10                 |      | μs      |

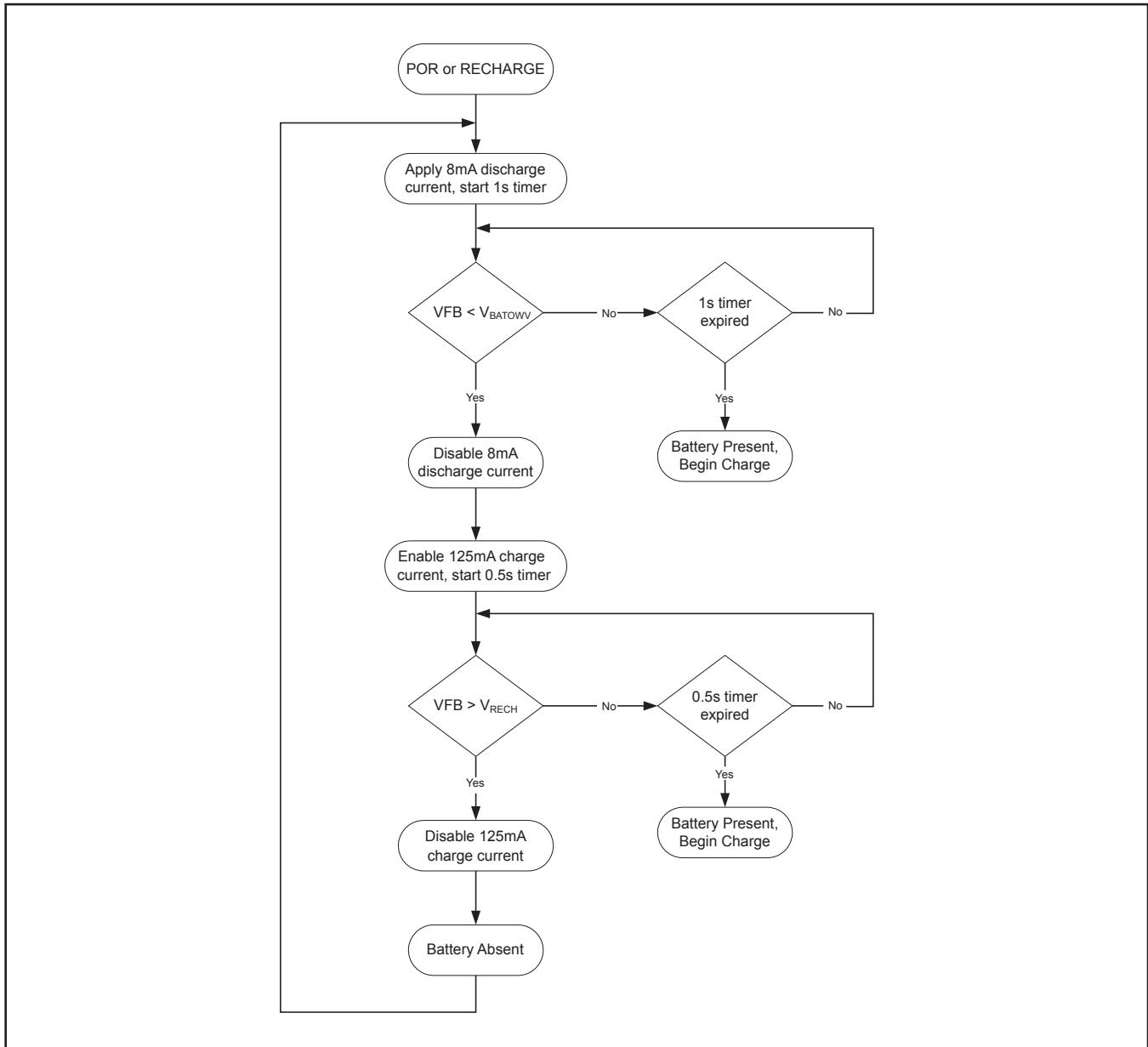

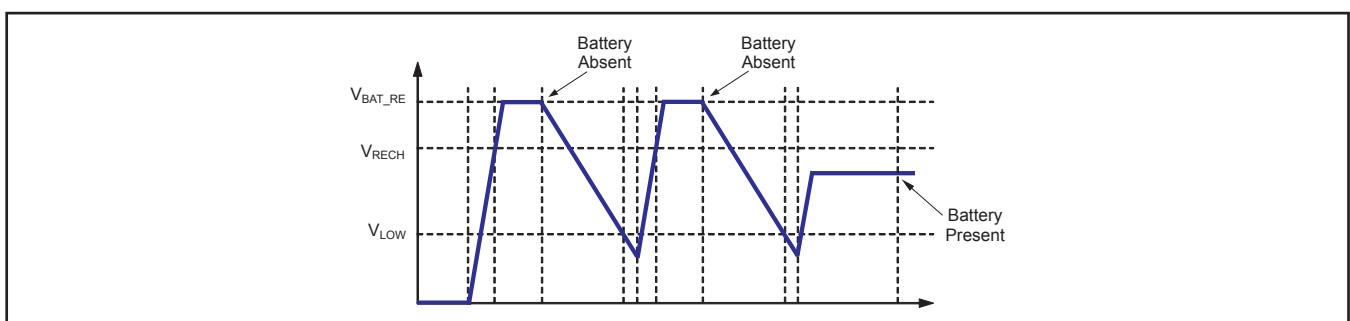

| <b>BATTERY DETECTION</b>              |                                                                                      |                                                                                                               |                    |      |         |

| t <sub>WAKE</sub>                     | Wake timer                                                                           | Max time charge is enabled                                                                                    | 500                |      | ms      |

| I <sub>WAKE</sub>                     | Wake current                                                                         | R <sub>SENSE</sub> = 10 mΩ                                                                                    | 50                 | 125  | 200     |

| t <sub>DISCHARGE</sub>                | Discharge timer                                                                      | Max time discharge current is applied                                                                         | 1                  |      | sec     |

| I <sub>DISCHARGE</sub>                | Discharge current                                                                    |                                                                                                               | 8                  |      | mA      |

| I <sub>FAULT</sub>                    | Fault current after a timeout fault                                                  |                                                                                                               | 2                  |      | mA      |

| V <sub>WAKE</sub>                     | Wake threshold with respect to V <sub>REG</sub> To detect battery absent during WAKE | Measure on SRN (bq24170)                                                                                      | 100                |      | mV/cell |

|                                       |                                                                                      | Measure on FB (bq24172)                                                                                       | 50                 |      | mV      |

| V <sub>DISCH</sub>                    | Discharge Threshold to detect battery absent during discharge                        | Measure on SRN (bq24170)                                                                                      | 2.9                |      | V/cell  |

|                                       |                                                                                      | Measure on VFB (bq24172)                                                                                      | 1.45               |      | V       |

(4) 10mΩセンス抵抗の最小電流は120mAです。

## 電気的特性

4.5V ≤ V(PVCC, AVCC) ≤ 17V, -40°C < T<sub>J</sub> < +125°C、標準値はT<sub>A</sub> = 25°Cの値、AGND基準です(特に記述のない限り)。

| パラメータ                                                           |                                                       | テスト条件                                                                                                 | MIN  | TYP  | MAX  | 単位   |

|-----------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------|------|------|------|

| <b>INTERNAL PWM</b>                                             |                                                       |                                                                                                       |      |      |      |      |

| f <sub>SW</sub>                                                 | PWM Switching Frequency                               |                                                                                                       | 1360 | 1600 | 1840 | kHz  |

| t <sub>SW_DEAD</sub>                                            | Driver Dead Time <sup>(5)</sup>                       | Dead time when switching between LSFET and HSFET no load                                              |      | 30   |      | ns   |

| R <sub>DS_HI</sub>                                              | High Side MOSFET On Resistance                        | V <sub>BTST</sub> - V <sub>SW</sub> = 4.5 V                                                           |      | 25   | 45   | mΩ   |

| R <sub>DS_LO</sub>                                              | Low Side MOSFET On Resistance                         |                                                                                                       |      | 60   | 110  | mΩ   |

| V <sub>BTST_REFRESH</sub>                                       | Bootstrap Refresh Comparator Threshold Voltage        | V <sub>BTST</sub> - V <sub>SW</sub> when low side refresh pulse is requested, V <sub>AVCC</sub> =4.5V |      | 3    |      | V    |

|                                                                 |                                                       | V <sub>BTST</sub> - V <sub>SW</sub> when low side refresh pulse is requested, V <sub>AVCC</sub> >6V   |      | 4    |      |      |

| <b>INTERNAL SOFT START (8 steps to regulation current ICHG)</b> |                                                       |                                                                                                       |      |      |      |      |

| SS_STEP                                                         | Soft start steps                                      |                                                                                                       |      | 8    |      | step |

| T <sub>SS_STEP</sub>                                            | Soft start step time                                  |                                                                                                       |      | 1.6  | 3    | ms   |

| <b>CHARGER SECTION POWER-UP SEQUENCING</b>                      |                                                       |                                                                                                       |      |      |      |      |

| t <sub>CE_DELAY</sub>                                           | Delay from ISET above 120mV to start charging battery |                                                                                                       |      | 1.5  |      | s    |

| <b>INTEGRATED BTST DIODE</b>                                    |                                                       |                                                                                                       |      |      |      |      |

| V <sub>F</sub>                                                  | Forward Bias Voltage                                  | I <sub>F</sub> =120mA at 25°C                                                                         |      | 0.85 |      | V    |

| V <sub>R</sub>                                                  | Reverse breakdown voltage                             | I <sub>R</sub> =2uA at 25°C                                                                           |      |      | 20   | V    |

| <b>LOGIC IO PIN CHARACTERISTICS (STAT1, STAT2, TERM_EN)</b>     |                                                       |                                                                                                       |      |      |      |      |

| V <sub>OUT_LO</sub>                                             | STAT Output Low Saturation Voltage                    | Sink Current = 5 mA                                                                                   |      |      | 0.5  | V    |

| V <sub>CELL_LO</sub>                                            | CELL pin input low threshold, 1 cell (bq24170)        | CELL pin voltage falling edge                                                                         |      |      | 0.5  | V    |

| V <sub>CELL_MID</sub>                                           | CELL pin input mid threshold, 2 cells (bq24170)       | CELL pin voltage rising for MIN, falling for MAX                                                      |      | 0.8  | 1.8  | V    |

| V <sub>CELL_HI</sub>                                            | CELL pin input high threshold, 3 cells (bq24170)      | CELL pin voltage rising edge                                                                          |      | 2.5  |      | V    |

(5) 設計で規定されています。

## 標準的特性

| 図   | 説明                                     |

|-----|----------------------------------------|

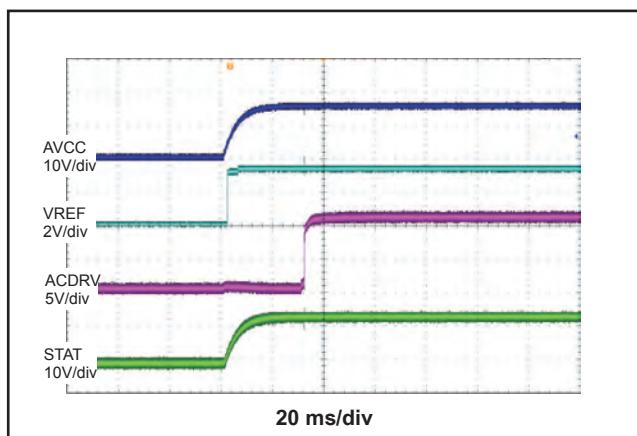

| 図5  | AVCC、VREF、ACDRV、およびSTATのパワーアップ(ISET=0) |

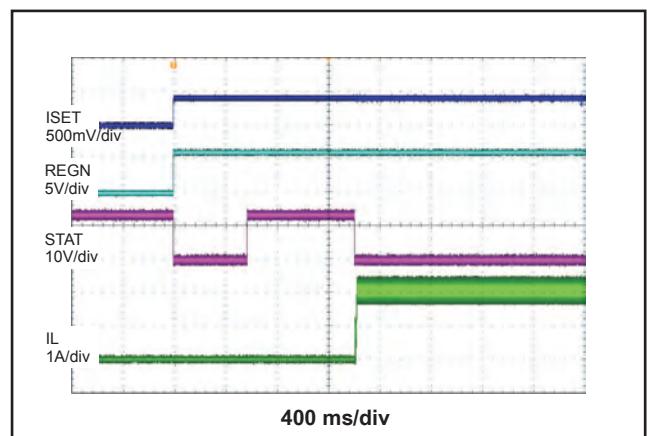

| 図6  | ISETによる充電イネーブル                         |

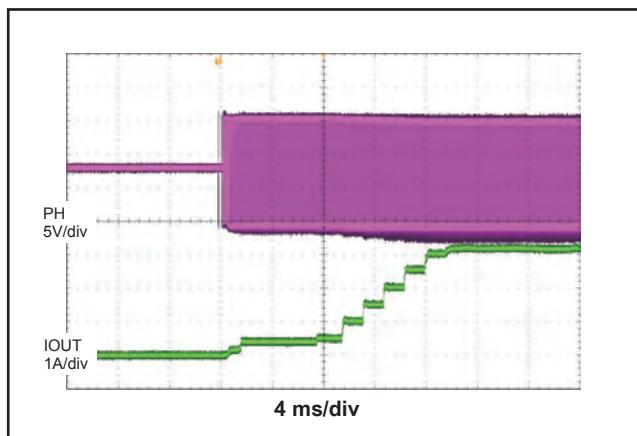

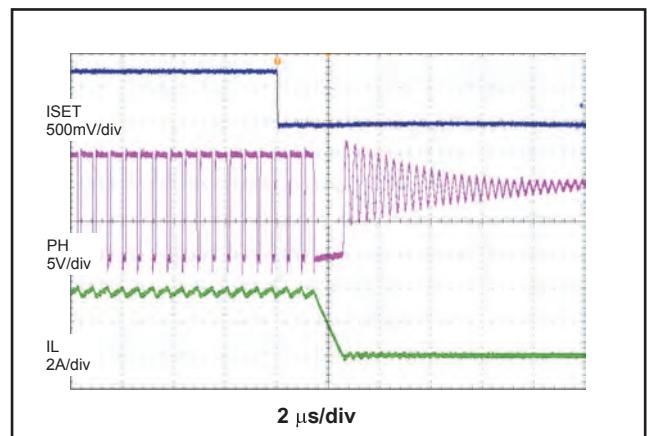

| 図7  | 電流ソフト・スタート                             |

| 図8  | ISETによる充電ディスエーブル                       |

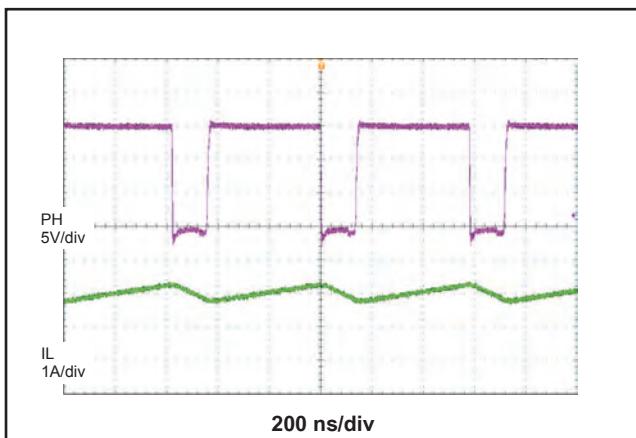

| 図9  | 連続導通モードのスイッチング                         |

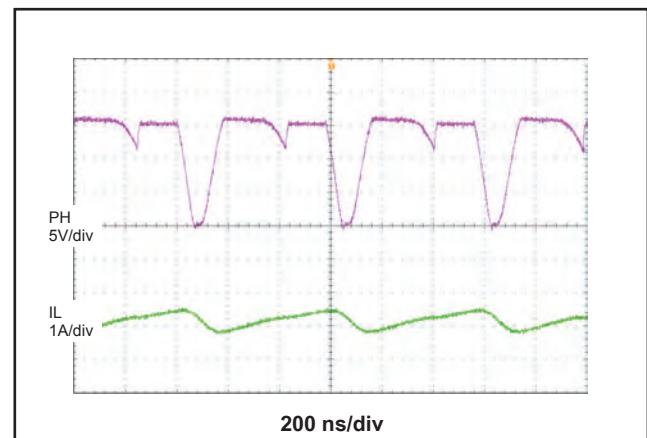

| 図10 | 不連続導通モードのスイッチング                        |

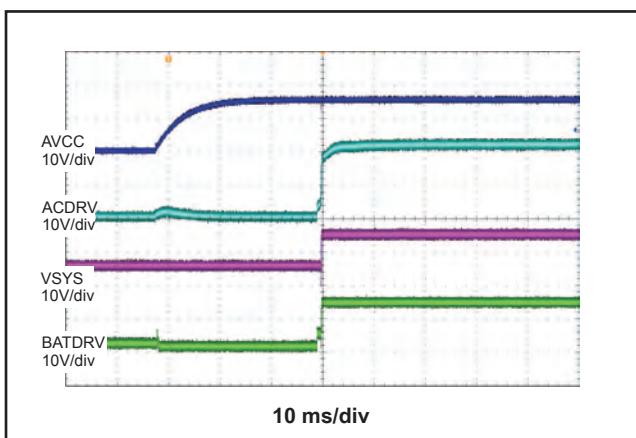

| 図11 | パワーアップ中のBATFETからACFETへの遷移              |

| 図12 | システム負荷過渡(入力電流DPM)                      |

| 図13 | バッテリ挿入および取り外し                          |

| 図14 | バッテリ—GND 短絡保護                          |

| 図15 | バッテリ—GND 短絡過渡                          |

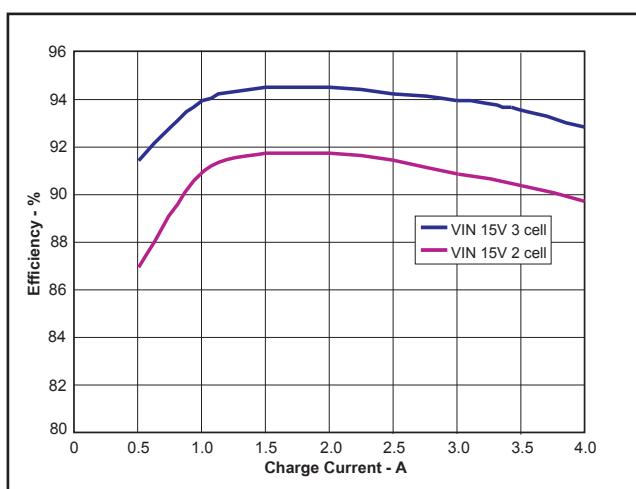

| 図16 | 効率 対 出力電流(VIN=15V)                     |

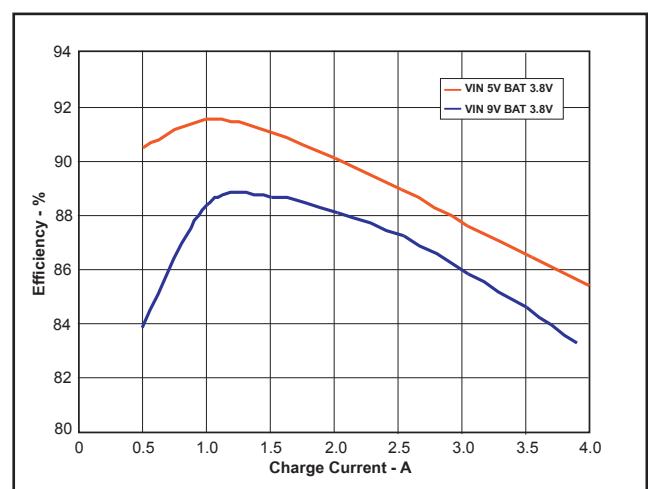

| 図17 | 効率 対 出力電流(VOUT=3.8V)                   |

表 1. グラフ一覧<sup>(1)</sup>

(1) すべての波形およびデータはHPA610およびHPA706 EVMで測定されています。

図 5. パワーアップ(ISET = 0)

図 6. ISETによる充電イネーブル

図 7. 電流ソフト・スタート

図 8. ISETによる充電ディスエーブル

図 9. 連続導通モードのスイッチング

図 10. 不連続導通モードのスイッチング

図 11. パワーアップ中のBATFETからACFETへの遷移

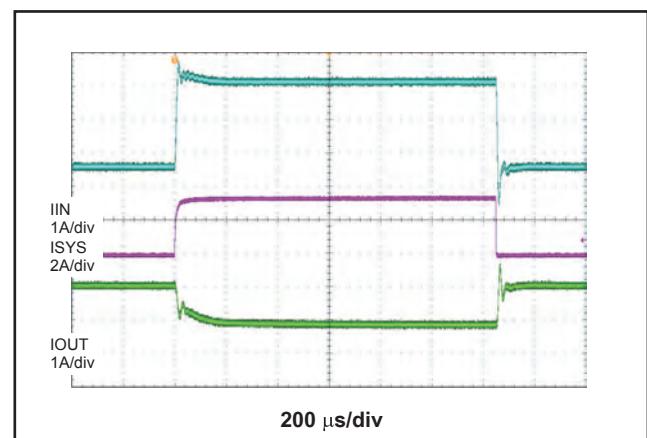

図 12. システム負荷過渡(入力電流DPM)

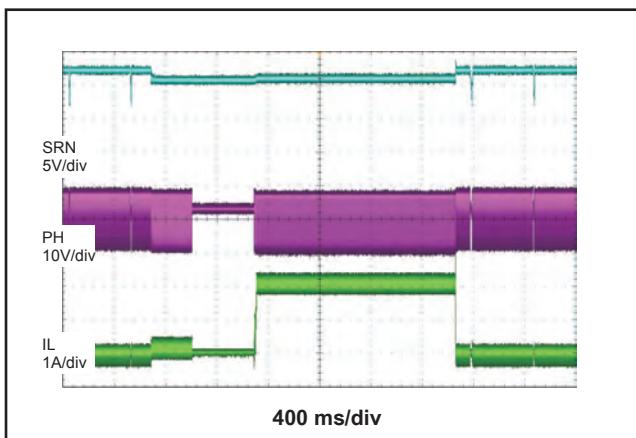

図 13. バッテリ挿入および取り外し

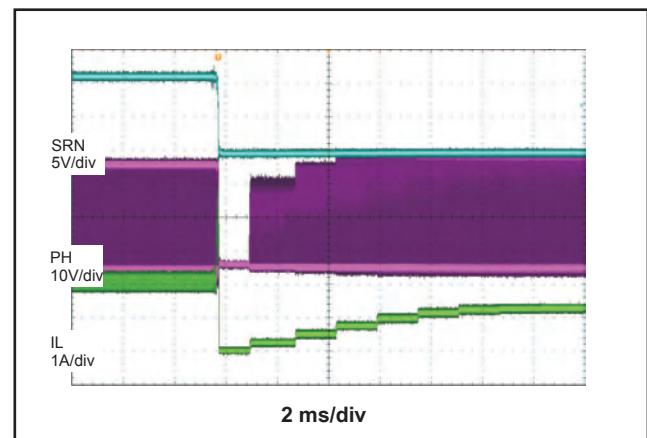

図 14. バッテリ—GND 短絡保護

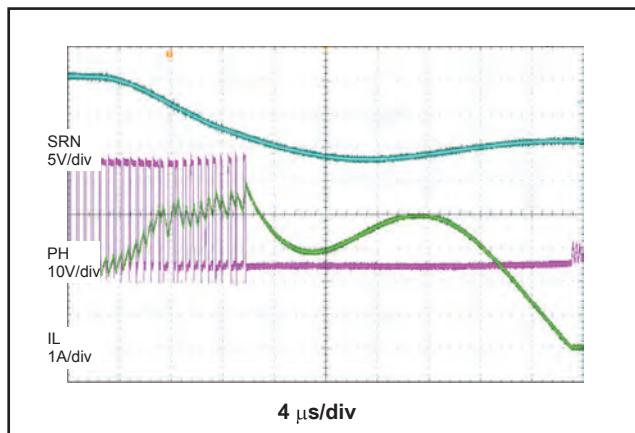

図 15. バッテリ — GND 短絡過渡

図 16. 効率 対 出力電流 (VIN = 15V)

図 17. 効率 対 出力電流 (VOUT = 3.8V)

## 機能ブロック図

図 18. 機能ブロック図

図 19. 標準的な充電プロファイル

## バッテリ電圧レギュレーション

bq24170/172は、充電電圧に対して高精度の電圧レギュレータを実現します。bq24170では、CELLピンを使用してセル数を選択できます(4.2V/セルに固定)。CELLをAGNDに接続すると1セル出力が設定され、CELLピンをオープン状態にすると2セル出力、VREFに接続すると3セル出力が設定されます。

| CELLピン   | 電圧制御   |

|----------|--------|

| AGND     | 4.2V   |

| Floating | 8.4 V  |

| VREF     | 12.6 V |

表 2. bq24170のCELLピン設定

bq24172では、外部分圧抵抗を使用して、電圧帰還を行うとともに、FBピン上の電圧を内部の2.1V基準電圧に制御します。bq24172の制御電圧には、次の式を使用します。

$$V_{BAT} = 2.1 \text{ V} \times \left[ 1 + \frac{R2}{R1} \right] \quad (1)$$

ここで、R2はFB-バッテリ間、R1はFB-GND間に接続されます。

## バッテリ電流制御

ISET入力によって、充電電流の最大値が設定されます。バッテリ電流は、SRPとSRNの間に接続された電流センス抵抗RSRによって検出されます。SRP-SRN間のフルスケール差動電圧は最大40mVです。充電電流は次の式で求められます。

$$I_{CHARGE} = \frac{V_{ISET}}{20 \times R_{SR}} \quad (2)$$

ISETの有効入力電圧範囲は、最大0.8Vです。10mΩのセンス抵抗に対する最大出力電流は、4Aです。20mΩのセンス抵抗に対する最大出力電流は、2Aです。

ISETピンの電圧が40mVを下回るとチャージャはディスエーブルになります、ISETピンの電圧が120mVを超えるとイネーブルになります。10mΩの電流センス抵抗に対して、最小高速充電電流は600mAより大きい必要があります。

周囲温度が高い場合は、ICの温度が120°Cを超えないように、充電電流がフォールドバックされます。

## バッテリ・プリチャージ電流の制御

パワーアップ時にバッテリ電圧が $V_{LOWV}$ レッショルドよりも低い場合、bq24170/172はバッテリにプリチャージ電流を供給します。このプリチャージ機能は、深放電されたセルを再活性化する

ことを目的としています。プリチャージ開始から30分以内にV<sub>LOWV</sub>スレッショルドに達しなかった場合、チャージャはオフになります、ステータス・ピンでFAULTが示されます。

bq24170/172では、プリチャージ電流はISET電圧で設定される高速充電レートの10%に設定されます。

$$I_{\text{PRECHARGE}} = \frac{V_{\text{ISET}}}{200 \times R_{\text{SR}}} \quad (3)$$

## 入力電流制御

ACアダプタまたは他のDCソースからの合計入力は、システムの電源電流およびバッテリ充電電流の関数です。通常、システム電流は、システムの一部がパワーアップまたはパワーダウンされるたびに変動します。動的電源管理(DPM)を使用しない場合、電源は最大システム電流と最大チャージャの入力電流を同時に供給できる必要があります。DPMを使用すると、システム電力と充電電力の合計が最大入力電力を超える場合に、入力電流レギュレータによって充電電流が低減されます。それにより、ACアダプタの電流能力を低めにして、システムのコストを削減することができます。

入力電流は、ACSETピンの電圧から次の式を用いて設定されます。

$$I_{\text{DPM}} = \frac{V_{\text{ACSET}}}{20 \times R_{\text{AC}}} \quad (4)$$

ACPピンとACNピンを使用して、RAC両端の電圧を検知します。RACのデフォルト値は10mΩです。ただし、他の値の抵抗も使用できます。より大きなセンス抵抗を使用すると、センス電圧が高くなり、レギュレーション精度が上がりますが、抵抗損失が大きくなります。

## 充電終了、再充電、および安全タイマ

チャージャは、電圧制御・フェーズ中に充電電流を監視します。SRN電圧(bq24170)またはFB電圧(bq24172)が再充電スレッショルドを上回り、充電電流が次の式で計算される終了電流スレッショルドより低い場合は、充電終了が検出されます。

$$I_{\text{TERM}} = \frac{V_{\text{ISET}}}{200 \times R_{\text{SR}}} \quad (5)$$

ここで、V<sub>ISET</sub>はISETピンの電圧、R<sub>SR</sub>はセンス抵抗です。高速充電からプリチャージへの遷移時には25msのデグリッチ時間があります。

安全対策として、チャージャは内部に30分固定のプリチャージ安全タイマ、および設定可能な高速充電タイマも備えています。高速充電時間は、TTCピンとAGNDの間に接続されるコンデンサにより、次の式を用いて設定します。

$$t_{\text{TTC}} = C_{\text{TTC}} \times K_{\text{TTC}} \quad (6)$$

ここで、C<sub>TTC</sub>はTTCに接続されたコンデンサ、K<sub>TTC</sub>は定数の係数です。

次の条件のいずれかが満たされると、新しい充電サイクルが開始されます。

- ・バッテリ電圧が再充電スレッショルドを下回る。

- ・パワーオン・リセット(POR)が発生する。

- ・ISETピンが40mVより低い(充電ディスエーブル)または120mVより高い(充電イネーブル)電圧に切り替えられる。

充電終了と高速充電安全タイマ(リセット・タイマ)の両方をディスエーブルにするには、TTCピンをAGNDにプルダウンにします。安全タイマをディスエーブルにして充電終了をイネーブルにするには、TTCピンをVREFにプルアップします。

## パワーアップ

チャージャでは、AVCCがバッテリまたはアダプタのいずれかから供給されるため、SLEEPコンパレータを使用してAVCCピンの電源ソースを決定します。アダプタ・ソースが存在し、AVCC電圧がSRN電圧より高い場合には、SLEEPモードが終了します。充電のための条件がすべて満足されていれば、チャージャはバッテリの充電を開始します(「充電のイネーブルとディスエーブル」を参照)。SRN電圧がAVCCより高い場合、チャージャは低静止電流のSLEEPモードに入り、バッテリからの消費電流を最小限に抑えます。SLEEPモード中は、VREF出力がオフになり、STATピンがハイ・インピーダンスになります。

AVCCがUVLOスレッショルドより低い場合、デバイスはディスエーブルになります。

## 入力低電圧ロックアウト(UVLO)

システムが適切に動作するために最小動作電圧以上のAVCCが必要です。このAVCC電圧は、入力アダプタまたはバッテリのいずれかから供給できます。AVCCがUVLOスレッショルドより低い場合、ICのすべての回路がディスエーブルになります。

## 入力過電圧/低電圧保護

ACOVは、高い入力電圧によるシステムの損傷を防ぐための保護機能です。bq24170/172では、OVPSETの電圧が1.6VのACOVスレッショルドを上回るか、または0.5VのACUVスレッショルドを下回ると、充電がディスエーブルになり、入力MOSFETがオフになります。bq24170/172では、入力条件スレッショルドを柔軟に設定可能です。

## 充電のイネーブルとディスエーブル

充電がイネーブルになるには、以下の条件が満足されている必要があります。

- ・ISETピンが120mVを上回る。

- ・デバイスが低電圧ロックアウト(UVLO)モードでない(V<sub>AVCC</sub> > V<sub>UVLO</sub>)。

- ・デバイスがSLEEPモードでない(V<sub>AVCC</sub> > V<sub>SRN</sub>)。

- ・OVPSET電圧が0.5V~1.6Vの範囲内である。

- ・最初のパワーアップ後に1.5sの遅延時間が経過。

- ・REGN LDOおよびVREF LDOの電圧が正しいレベルである。

- ・過熱シャットダウン(TSHUT)状態に達していない。

- ・TSエラーが未検出。

- ・ACFETがオン(詳細は「システム電源セレクタ」を参照)。

次のいずれかの条件が満足されると、実行中の充電が停止されます。

- ISETピンの電圧が40mVを下回る。

- デバイスがUVLOモードになる。

- アダプタが取り外され、デバイスがSLEEPモードに入る。

- OVPSET電圧で、アダプタが有効でないことが示される。

- REGNまたはVREF LDO電圧が過負荷状態。

- TSHUT温度スレッショルドに達する。

- TS電圧が範囲外であり、バッテリ温度が高すぎるか低すぎる。

- ACFETがオフ。

- TTCタイマが満了、またはプリチャージ・タイマが満了。

## システム電源セレクタ

このICは、システム負荷への電源をアダプタとバッテリ電源の間で自動的に切り替えます。パワーアップ中、またはSLEEPモード中は、デフォルトでバッテリがシステムに接続されます。アダプタが接続され、アダプタ電圧がバッテリ電圧を上回っている場合、ICはSLEEPモードを終了します。SLEEP終了後、バッテリがシステムから切り離され、アダプタがシステムに接続されます。自動Break-Before-Makeロジックにより、セレクタ切り替え時の貫通電流を防止しています。

ACDRVは、アダプタとACPの間に接続されたNチャネル・パワーMOSFETのペアを駆動するために使用されます。これらのMOSFETはソースがともにCMSRCに接続されています。ドレインがACP(Q2、RBFET)に接続されたこのNチャネルFETは、バッテリの逆放電を防ぐとともに、低いRDS<sub>ON</sub>により、システムの消費電力を最小限に抑える効果があります。アダプタ入力(Q1、ACFET)に接続されたもう1つのNチャネルFETは、アダプタからバッテリを分離するとともに、FETのターンオン時間を制御することで、システムにアダプタを接続する際のdI/dtを制限します。/BATDRVは、バッテリとシステムの間に接続されたPチャネル・パワーMOSFET(Q3、BATFET)(ドレインをバッテリに接続)を制御します。

アダプタの検出前は、ACDRVがCMSRCにプルアップされてACFETをオフに保持し、アダプタ入力をシステムから切り離します。以下のすべての条件が満足されると、/BATDRVがACN-6V(グランドにクランプ)に保持され、バッテリがシステムに接続されます。

- V<sub>AVCC</sub> > V<sub>UVLO</sub> (バッテリがAVCCを供給)

- V<sub>ACN</sub> < V<sub>SRN</sub> + 200mV

デバイスがSLEEPモードを終了した後、システムはバッテリからアダプタへの切り替えを開始します。この遷移を有効にするには、AVCC電圧がSRNより300mV高い必要があります。Break-Before-Makeロジックにより、ACFETおよびBATFETが10μsだけオフに保持された後、ACFETがオンになります。これにより、貫通電流や大きな放電電流がバッテリに流れ込むのを防止します。以下のすべての条件が満足されると、/BATDRVがACNにプルアップされ、ACDRVピンは内部チャージ・ポンプによりCMSRC+6Vに設定されてNチャネルACFETがオンになり、アダプタがシステムに接続されます。

- V<sub>ACUV</sub> < V<sub>OVPSET</sub> < V<sub>ACOV</sub>

- V<sub>AVCC</sub> > V<sub>SRN</sub> + 300mV

アダプタが取り外されると、ICはACFETをオフにし、SLEEPモードに入ります。

BATFETは、システム電圧がSRNピン電圧の近い値に降下するまでオフのままであります。/BATDRVピンは内部レギュレータによりACN-6Vに駆動されてPチャネルBATFETがオンになり、バッテリがシステムに接続されます。

ACFETおよびBATFETに対する非対称ゲート駆動(高速ターンオフと低速ターンオン)により、Break-Before-Makeロジックの実現を助け、両方のMOSFETのターンオン時にソフト・スタートを可能にします。遅延時間は、パワーMOSFETのゲートソース間にコンデンサを接続することでさらに長くできます。

## コンバータの動作

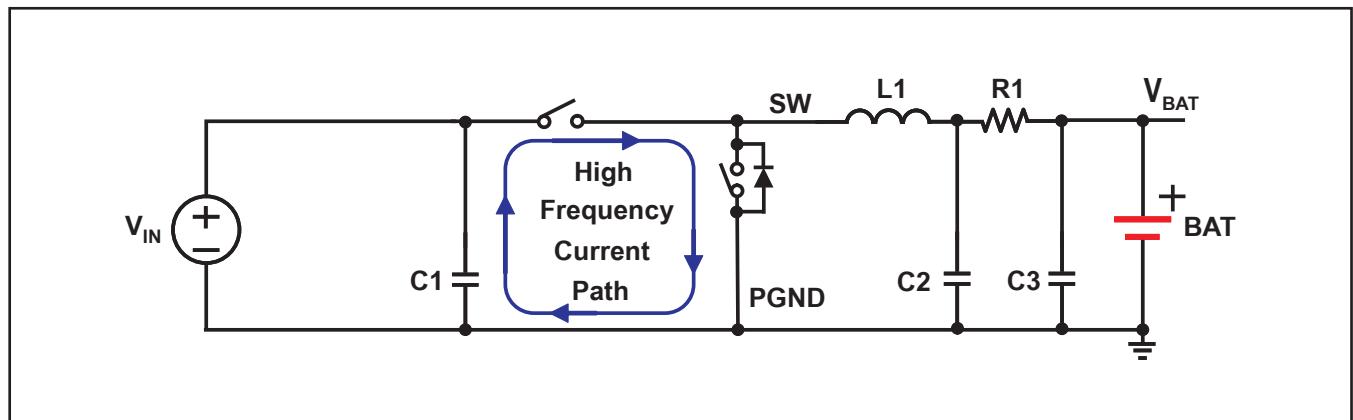

bq24170/172は、1.6MHzの固定周波数降圧型スイッチング・レギュレータとなります。固定周波数発振回路によって、入力電圧、バッテリ電圧、充電電流、および温度のすべての条件下でスイッチング周波数の厳密な制御が維持されることにより、出力フィルタ設計が単純化されて、可聴領域内のノイズを防ぎます。

Type III内部位相補償回路により、コンバータの出力にセラミック・コンデンサを使用できます。内部のこぎり波形が内部誤差制御信号と比較されて、コンバータのデューティ・サイクルを変化させます。波形の高さがAVCC電圧に比例することで、入力電圧の変化によるループ・ゲインの変動を相殺し、ループ補償を単純化します。内部ゲート駆動ロジックにより、パルスのスキップが開始される前に97%のデューティ・サイクルを実現できます。

## 自動内部ソフト・スタート・チャージャ電流

チャージャは、高速充電に入るときに、チャージャ・制御電流を自動的にソフト・スタートさせることで、出力コンデンサまたはパワー・コンバータにオーバーシュートやストレスが加わるのを防ぐことができます。このソフト・スタートは、設定された充電電流に達するまでに、充電レギュレーション電流を8つの等間隔のステップに分けて上昇させることで行います。各ステップは約1.6ms継続され、標準の立ち上がり時間は12.8msです。この機能には、外部部品は必要ありません。

## 充電過電流保護

チャージャは、ハイサイド・センスFETによって上側MOSFETの電流を監視します。ピーク電流がMOSFET制限を超えると、上側MOSFETがオフになり、次のサイクルまでオフに保持されます。チャージャには、2次的なcycle-to-cycleの過電流保護機能があります。この機能は、充電電流を監視して、設定された充電電流の160%を超えないようにします。いずれかの過電流状態が検出されるとハイサイド・ゲート駆動がオフになり、電流が過電流スレッショルドを下回ると自動的に復帰します。

## 充電低電流保護