**BQ25173**

# BQ25173:1~4 セル・スーパーキャパシタ向け 800mA リニア・チャージャ

# 1 特長

- 耐入力電圧:最大 40V

- 自動スリープ・モードによる消費電力低減

- リーク電流:350nA

- 充電ディスエーブル時の入力リーク電流:2µA

- 1~4 セルのスーパーキャパシタをサポート

- OV からのスーパーキャパシタ充電をサポート

- 外付け抵抗によりプログラム可能な動作

- FB ピンによりスーパーキャパシタのレギュレーショ ン電圧を調整

- ISET により充電電流を 10mA~800mA に設定

- 高精度

- **±1%** の充電電圧精度

- ±10% の充電電流精度

- 充電機能

- <u>CE</u> ピンによる充電機能の制御

- ステータスおよびフォルト表示用のオープン・ドレイ

- パワー・グッド表示用のオープン・ドレイン出力

- フォルト保護機能内蔵

- 18V の IN 過電圧保護

- 1000mA の過電流保護機能

- 125°Cのサーマル・レギュレーション、150°Cのサー マル・シャットダウン保護

- OUT 短絡保護

- ISET ピンの短絡 / 開放保護

# 2 アプリケーション

- スマート・メーター

- バーコード・スキャナー

- 携帯医療機器

- ダッシュボード・カメラ

# 3 概要

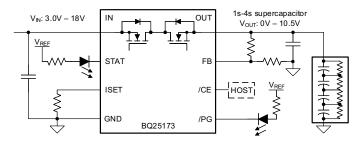

BQ25173 は、スペースに制約のあるアプリケーションの 1 ~4 セル・スーパーキャパシタに対応する統合型 800mA リニア・チャージャです。本デバイスには、スーパーキャパ シタを充電する電源出力が 1 つあります。システム負荷を スーパーキャパシタと並列に接続できます (充電電流はシ ステムとスーパーキャパシタの間で共有されます)。

充電中、内部制御ループにより IC 接合部の温度が監視 され、内部の温度スレッショルド (TREG) を超えた場合は充 電電流が引き下げられます。この機能により、完全に放電 されたスーパーキャパシタでも高速充電できます。

充電器の電源段と充電電流センス機能は完全に統合され ています。充電器には、高精度の電流および電圧レギュレ ーション・ループ、充電ステータスの表示、充電機能制御 の機能があります。充電電圧と高速充電電流は、外付け 抵抗で設定できます。

#### 製品情報

|         | And the life into    |               |  |  |

|---------|----------------------|---------------|--|--|

| 部品番号    | パッケージ <sup>(1)</sup> | 本体サイズ (公称)    |  |  |

| BQ25173 | WSON (8)             | 2.0mm × 2.0mm |  |  |

利用可能なすべてのパッケージについては、このデータシートの 末尾にある注文情報を参照してください。

概略回路図

# **Table of Contents**

| 1 特長                                 | 1 | 8 Application and Implementation               | 16              |

|--------------------------------------|---|------------------------------------------------|-----------------|

| 2 アプリケーション                           |   | 8.1 Application Information                    |                 |

| 3 概要                                 |   | 8.2 Typical Applications                       |                 |

| 4 Revision History                   |   | 9 Power Supply Recommendations                 | 20              |

| 5 Pin Configuration and Functions    |   | 10 Layout                                      | 20              |

| 6 Specifications                     |   | 10.1 Layout Guidelines                         | <mark>20</mark> |

| 6.1 Absolute Maximum Ratings         |   | 10.2 Layout Example                            | <mark>20</mark> |

| 6.2 ESD Ratings                      |   | 10.3 Thermal Package                           | 20              |

| 6.3 Recommended Operating Conditions |   | 11 Device and Documentation Support            | 22              |

| 6.4 Thermal Information              |   | 11.1 Device Support                            | <mark>22</mark> |

| 6.5 Electrical Characteristics       |   | 11.2 Receiving Notification of Documentation U | pdates 22       |

| 6.6 Timing Requirements              |   | 11.3 サポート・リソース                                 | 22              |

| 6.7 Typical Characteristics          |   | 11.4 Trademarks                                | 22              |

| 7 Detailed Description               |   | 11.5 Electrostatic Discharge Caution           | 22              |

| 7.1 Overview                         |   | 11.6 Glossary                                  | 22              |

| 7.2 Functional Block Diagram         |   | 12 Mechanical, Packaging, and Orderable        |                 |

| 7.3 Feature Description              |   | Information                                    | 23              |

| 7.4 Device Functional Modes          |   |                                                |                 |

# **4 Revision History**

| DATE          | REVISION | NOTES           |  |  |

|---------------|----------|-----------------|--|--|

| November 2021 | *        | Initial Release |  |  |

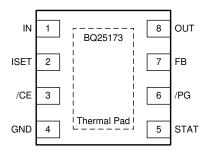

# **5 Pin Configuration and Functions**

図 5-1. DSG (WSON) Package 8-Pin Top View

表 5-1. Pin Functions

| PIN                                                                |     | (1)                |                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------------|-----|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                                               | NO. | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                        |

| IN                                                                 | 1   | Р                  | Input power. Connect to external DC supply. Bypass IN with at least 1-µF capacitor to GND, placed close to the IC.                                                                                                                                                                                                                 |

| ISET                                                               | 2   | I                  | Programs the device fast-charge current, $I_{CHG}$ . External resistor from ISET to GND defines fast-charge current value. Expected range is 30 k $\Omega$ (10 mA) to 375 $\Omega$ (800 mA). $I_{CHG}$ = $K_{ISET}$ / $R_{ISET}$ .                                                                                                 |

| CE 3 I Shutdown mode and charging is disabled when the CE pin is I |     |                    | Active low charge enable pin. Charging is enabled when the CE pin is LOW. IC remains in Shutdown mode and charging is disabled when the CE pin is HIGH. An internal pulldown resistor ( $R_{PD\_CE}$ ) enables the IC by default if this pin is floating.                                                                          |

| GND                                                                | 4   | _                  | Ground pin.                                                                                                                                                                                                                                                                                                                        |

| STAT                                                               | 5   | 0                  | Open-drain charger status indication output. Connect to pullup rail with a 10-k $\Omega$ resistor. LOW indicates $V_{OUT}$ has reached 98% of the programmable regulation voltage, $V_{REG}$ . HIGH indicates charge in progress.                                                                                                  |

| PG                                                                 | 6   | 0                  | Open-drain charger power-good output. Connect to pullup rail with a 10-k $\Omega$ resistor. $\overline{PG}$ goes LOW when $V_{IN} > V_{IN\_LOWV}$ and $V_{OUT} + V_{SLEEPZ} < V_{IN} < V_{IN\_OV}$ .                                                                                                                               |

| FB                                                                 | 7   | ı                  | Programs the supercapacitor regulation voltage, $V_{REG}$ . Use a feedback divider not exceeding 1 M $\Omega$ from $V_{OUT}$ to GND to set the regulation voltage. The bottom of the resistor divider network can be connected to $\overline{PG}$ for reduced power consumption when the input is removed (for $V_{REG} \le 5$ V). |

| OUT                                                                | 8   | Р                  | Supercapacitor connection. System load may be connected in parallel with supercapacitor. Bypass OUT with at least 1-µF capacitor to GND, placed close to the IC.                                                                                                                                                                   |

| Thermal Pad                                                        | _   | Р                  | Exposed pad beneath the IC for heat dissipation. Solder thermal pad to the board with vias connecting to solid GND plane.                                                                                                                                                                                                          |

<sup>(1)</sup> I = Input, O = Output, P = Power

# **6 Specifications**

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                                       |                        | MIN  | MAX | UNIT |

|---------------------------------------|------------------------|------|-----|------|

| Voltage                               | IN                     | -0.3 | 40  | V    |

| Voltage                               | OUT                    | -0.3 | 13  | V    |

| Voltage                               | CE, FB, ISET, STAT, PG | -0.3 | 5.5 | V    |

| Output Sink Current                   | PG, STAT               |      | 5   | mA   |

| Junction temperature, T <sub>J</sub>  |                        | -40  | 150 | °C   |

| Storage temperature, T <sub>stg</sub> |                        | -65  | 150 | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute maximum ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If briefly operating outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not sustain damage, but it may not be fully functional. Operating the d ality, performance, and shorten the device lifetime.

# 6.2 ESD Ratings

| V                  | Human body model (HBM), per ANSI/ESDA/<br>JEDEC JS-001 <sup>(1)</sup> |                                                                           | ±2500 | V |  |  |

|--------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------|-------|---|--|--|

| V <sub>(ESD)</sub> |                                                                       | Charged device model (CDM), per ANSI/ESDA/<br>JEDEC JS-002 <sup>(2)</sup> | ±1500 | V |  |  |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                   |                      | MIN   | NOM MAX | UNIT |

|-------------------|----------------------|-------|---------|------|

| V <sub>IN</sub>   | Input voltage        | 3.0   | 18      | V    |

| V <sub>OUT</sub>  | Output voltage       | 0     | 10.5    | V    |

| I <sub>OUT</sub>  | Output current       |       | 0.8     | Α    |

| T <sub>J</sub>    | Junction temperature | -40   | 125     | °C   |

| C <sub>IN</sub>   | IN capacitor         | 1     |         | μF   |

| C <sub>OUT</sub>  | OUT capacitor        | 1     |         | μF   |

| R <sub>ISET</sub> | ISET resistor        | 0.375 | 30      | kΩ   |

Product Folder Links: BQ25173

## **6.4 Thermal Information**

|                       |                                                                | BQ25173    |      |

|-----------------------|----------------------------------------------------------------|------------|------|

|                       | THERMAL METRIC(1)                                              | DSG (WSON) | UNIT |

|                       |                                                                | 8 PINS     |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance (JEDEC <sup>(1)</sup> ) | 75.2       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance                      | 93.4       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance                           | 41.8       | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter                     | 3.8        | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter                   | 41.7       | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance                   | 17.0       | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### 6.5 Electrical Characteristics

$3.0V < V_{IN} < 18V$  and  $V_{IN} > V_{OUT} + V_{SLEEP}$ ,  $T_J = -40^{\circ}$ C to +125°C, and  $T_J = 25^{\circ}$ C for typical values (unless otherwise noted)

|                         | PARAMETER                                                      | °C to +125°C, and T <sub>J</sub> = 25°C for typical va                                                                           | MIN  | TYP   | MAX  | UNIT |

|-------------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------|-------|------|------|

| QUIESCENT C             | URRENTS                                                        |                                                                                                                                  |      |       |      |      |

| 1                       | Outleasent auteut aumant (OUT)                                 | OUT= 4.2V, IN floating or IN = 0V - 5V,<br>Charge Disabled ( $\overline{\text{CE}}$ high), T <sub>J</sub> = 25 °C                |      | 0.350 | 0.6  | μA   |

| I <sub>Q_OUT</sub>      | Quiescent output current (OUT)                                 | OUT= 4.2V, IN floating or IN = 0V - 5V,<br>Charge Disabled ( $\overline{\text{CE}}$ high), T <sub>J</sub> < 105 °C               |      | 0.350 | 0.8  | μA   |

| la aum                  | Quiescent output current (OUT)                                 | OUT = 8.4V, IN floating or IN = 0V - 14V,<br>Charge Disabled ( $\overline{\text{CE}}$ high), T <sub>J</sub> = 25 °C              |      | 0.8   | 1.2  | μA   |

| I <sub>Q_OUT</sub>      | Quiescent output current (OO1)                                 | OUT = 8.4V, IN floating or IN = 0V - 14V,<br>Charge Disabled ( $\overline{\text{CE}}$ high), T <sub>J</sub> < 105 °C             |      | 0.8   | 1.5  | μA   |

| lop w                   | Shutdown input current (IN) with                               | IN = 5V, Charge Disabled ( $\overline{\text{CE}}$ high), no capacitor                                                            |      | 2     | 4    | μA   |

| I <sub>SD_IN</sub>      | charge disabled                                                | IN = 14V, Charge Disabled (CE high), no capacitor                                                                                |      | 3.5   | 6    | μΑ   |

| I <sub>Q_IN</sub>       | Quiescent input current (IN)                                   | IN = 5V, OUT = 3.8V, Charge Enabled (CE low), ICHG = 0A                                                                          | 0.45 |       | 0.6  | mA   |

| I <sub>Q_IN</sub>       | Quiescent input current (IN)                                   | IN = 14V, OUT = 7.6V, Charge Enabled (CE low), ICHG = 0A                                                                         |      | 0.45  | 0.6  | mA   |

| INPUT                   |                                                                |                                                                                                                                  |      |       |      |      |

| V <sub>IN_OP</sub>      | IN operating range                                             |                                                                                                                                  | 3.0  |       | 18   | V    |

| $V_{IN\_LOWV}$          | IN voltage to start charging                                   | IN rising                                                                                                                        | 3.05 | 3.09  | 3.15 | V    |

| V <sub>IN_LOWV</sub>    | IN voltage to stop charging                                    | IN falling                                                                                                                       | 2.80 | 2.95  | 3.10 | V    |

| V <sub>SLEEPZ</sub>     | Exit sleep mode threshold                                      | IN rising, V <sub>IN</sub> - V <sub>OUT</sub> , OUT = 4V                                                                         | 95   | 135   | 175  | mV   |

| V <sub>SLEEP</sub>      | Sleep mode threshold hysteresis                                | IN falling, V <sub>IN</sub> - V <sub>OUT</sub> , OUT = 4V                                                                        |      | 80    |      | mV   |

| V <sub>IN_OV</sub>      | VIN overvoltage rising threshold                               | IN rising                                                                                                                        | 18.1 | 18.4  | 18.7 | V    |

| V <sub>IN_OVZ</sub>     | VIN overvoltage falling threshold                              | IN falling                                                                                                                       |      | 18.2  |      | V    |

|                         | ON PINS SHORT/OPEN PROTECTION                                  |                                                                                                                                  |      |       |      |      |

| R <sub>ISET_SHORT</sub> | Highest resistor value considered short                        | R <sub>ISET</sub> below this at startup, charger does not initiate charge, power cycle or $\overline{\text{CE}}$ toggle to reset |      |       | 350  | Ω    |

| CHARGER                 |                                                                |                                                                                                                                  |      |       |      |      |

| $V_{FB\_REF}$           | Feedback reference voltage                                     |                                                                                                                                  |      | 0.8   |      | V    |

| V <sub>FB_REF_ACC</sub> | Feedback reference voltage accuracy                            | Tj = -40°C to 125°C                                                                                                              | -1   |       | 1    | %    |

| I <sub>CHG_RANGE</sub>  | Typical charge current regulation range                        | V <sub>OUT</sub> > V <sub>BAT_LOWV</sub>                                                                                         | 10   |       | 800  | mA   |

| K <sub>ISET</sub>       | Charge current setting factor, $I_{CHG} = K_{ISET} / R_{ISET}$ | 10mA < ICHG < 800mA                                                                                                              | 270  | 300   | 330  | ΑΩ   |

|                         |                                                                | $R_{ISET} = 375\Omega$ , OUT = 3.8V or 7.6V                                                                                      | 720  | 800   | 880  | mA   |

|                         | Charge current accuracy                                        | R <sub>ISET</sub> = 600Ω, OUT = 3.8V or 7.6V                                                                                     | 450  | 500   | 550  | mA   |

| ICHG_ACC                | Charge current accuracy                                        | R <sub>ISET</sub> = 3.0kΩ, OUT = 3.8V or 7.6V                                                                                    | 90   | 100   | 110  | mA   |

|                         |                                                                | R <sub>ISET</sub> = 30kΩ, OUT = 3.8V or 7.6V                                                                                     | 9    | 10    | 11   | mA   |

| V <sub>CHG</sub>        | Supercapacitor charged threshold                               | OUT rising, as percentage of FB regulation target                                                                                |      | 98    |      | %    |

|                         | 0                                                              | IOUT = 400mA, T <sub>J</sub> = 25°C                                                                                              |      | 845   | 1000 | mΩ   |

| R <sub>ON</sub>         | Charging path FET on-resistance                                | IOUT = 400mA, T <sub>J</sub> = -40 - 125°C                                                                                       |      | 845   | 1450 | mΩ   |

| CHARGER PRO             | OTECTION                                                       |                                                                                                                                  |      | ,     |      | 1    |

| I <sub>OUT_OCP</sub>    | Output current limit threshold                                 | IOUT rising                                                                                                                      | 0.9  | 1     | 1.1  | Α    |

|                         |                                                                |                                                                                                                                  |      |       |      |      |

# **6.5 Electrical Characteristics (continued)**

$3.0 \text{V} < \text{V}_{\text{IN}} < 18 \text{V}$  and  $\text{V}_{\text{IN}} > \text{V}_{\text{OUT}} + \text{V}_{\text{SLEEP}}$ ,  $\text{T}_{\text{J}} = -40 ^{\circ} \text{C}$  to +125  $^{\circ} \text{C}$ , and  $\text{T}_{\text{J}} = 25 ^{\circ} \text{C}$  for typical values (unless otherwise noted)

|                       | PARAMETER                               | TEST CONDITIONS        | MIN | TYP | MAX | UNIT |

|-----------------------|-----------------------------------------|------------------------|-----|-----|-----|------|

| TEMPERATU             | RE REGULATION AND TEMPERATURE S         | SHUTDOWN               |     |     |     |      |

| T <sub>REG</sub>      | Typical junction temperature regulation |                        |     | 125 |     | °C   |

| т                     | Thermal shutdown rising threshold       | Temperature increasing |     | 150 |     | °C   |

| T <sub>SHUT</sub>     | Thermal shutdown falling threshold      | Temperature decreasing |     | 135 |     | °C   |

| LOGIC INPUT           | PIN (/CE)                               |                        |     |     |     |      |

| V <sub>IH</sub>       | Input high threshold level              |                        | 1.3 |     |     | V    |

| V <sub>IL</sub>       | Input low threshold level               |                        |     |     | 0.4 | V    |

| R <sub>PD_CE</sub>    | CE pin internal pulldown resistor       |                        | 3.3 |     |     | ΜΩ   |

| LOGIC OUTP            | UT PIN (STAT, PG)                       |                        |     |     |     |      |

| V <sub>OL</sub>       | Output low threshold level              | Sink current = 5mA     |     |     | 0.4 | V    |

| I <sub>OUT_BIAS</sub> | High-level leakage current              | Pull up rail 3.3V      |     |     | 1   | μΑ   |

# **6.6 Timing Requirements**

|                          |                                                      | MIN | NOM | MAX | UNIT |

|--------------------------|------------------------------------------------------|-----|-----|-----|------|

| CHARGER                  |                                                      |     | '   |     |      |

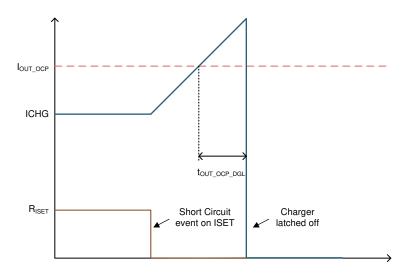

| t <sub>OUT_OCP_DGL</sub> | Deglitch time for I <sub>OUT_OCP</sub> , IOUT rising |     | 100 |     | μs   |

Copyright © 2022 Texas Instruments Incorporated

Submit Document Feedback

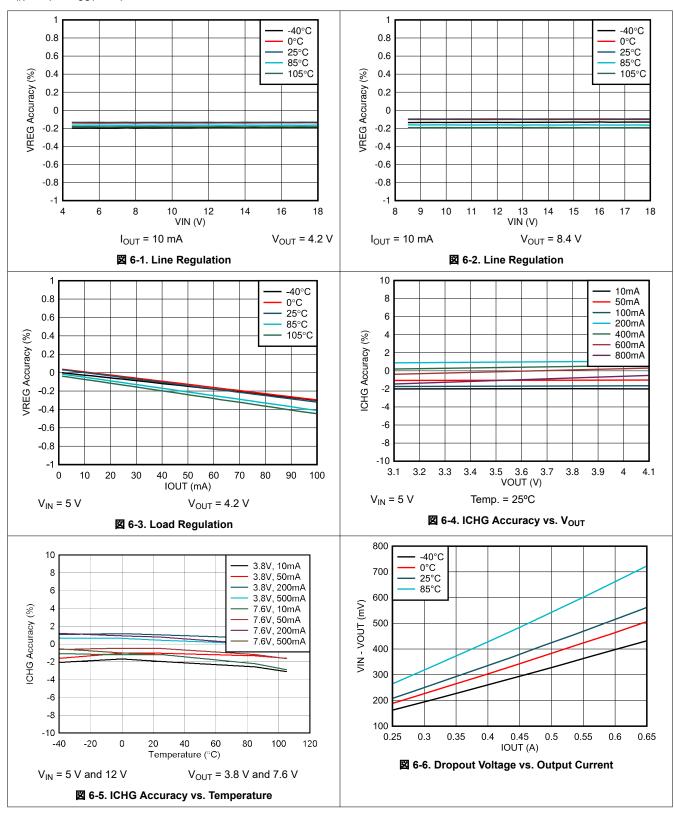

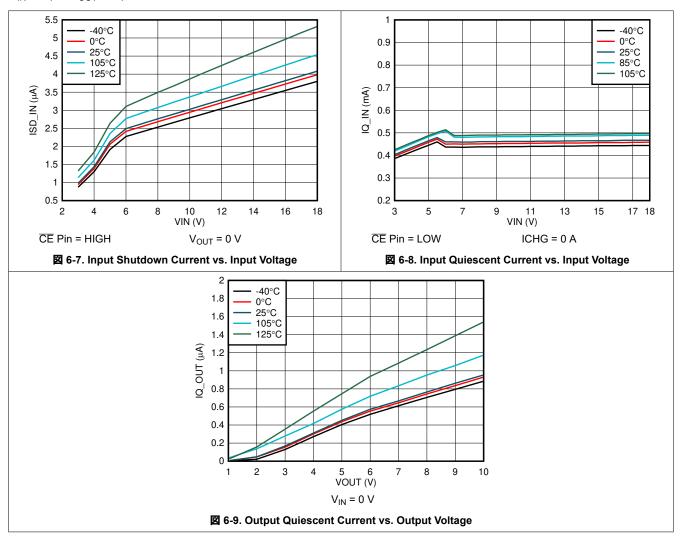

# **6.7 Typical Characteristics**

$$C_{IN}$$

= 1  $\mu$ F,  $C_{OUT}$  = 1  $\mu$ F

# **6.7 Typical Characteristics (continued)**

$C_{IN}$  = 1  $\mu$ F,  $C_{OUT}$  = 1  $\mu$ F

# 7 Detailed Description

### 7.1 Overview

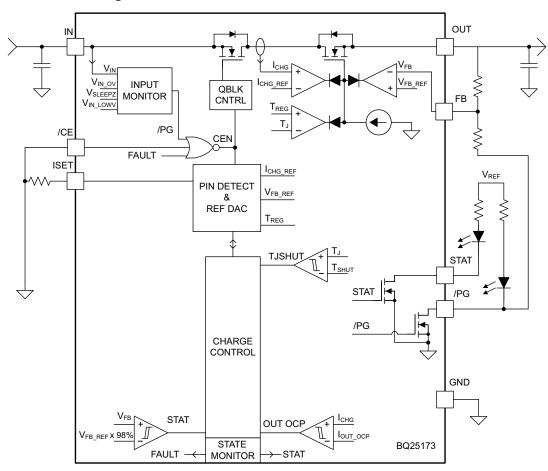

The device has a single power output that charges the supercapacitor. The system load can be placed in parallel with the supercapacitor; the charge current is shared between the system and supercapacitor.

The charger is designed for a single path from the input to the output to charge the supercapacitor. Upon application of a valid input power source, the ISET pin is checked for short/open circuit.

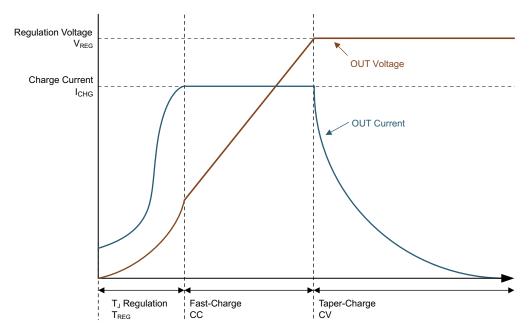

The device attempts to charge the supercapacitor at the fast-charge current setting from fully discharged (0 V) up to the programmable regulation voltage,  $V_{REG}$ . Power dissipation in the IC is greatest in fast charge with a lower supercapacitor voltage. If the IC temperature reaches  $T_{REG}$ , the IC enters thermal regulation and reduces the charge current as needed to keep the temperature from rising any further. The fast-charge current is programmed using the ISET pin.  $\boxtimes$  7-1 shows the typical supercapacitor charging profile with thermal regulation. At lower fast-charge settings, the junction temperature of the IC is less than  $T_{REG}$  and thermal regulation is not entered.

Once the supercapacitor has charged to the regulation voltage, the voltage loop takes control and holds the voltage at the regulation voltage as the current tapers down to zero. There is no current termination threshold as seen in Li-ion chargers.

Further details are described in セクション 7.3.

☑ 7-1. Supercapacitor Charging Profile with Thermal Regulation

# 7.2 Functional Block Diagram

## 7.3 Feature Description

#### 7.3.1 Device Power Up from Input Source

When an input source is plugged in and charge is enabled, the device checks the input source voltage to turn on all of the bias circuits. The device detects and sets the charge current limits before the linear regulator is started. The power-up sequence from the input source is listed below:

- 1. ISET pin detection

- 2. Charger power up

### 7.3.1.1 ISET Pin Detection

After a valid VIN is plugged in and the  $\overline{\text{CE}}$  pin is pulled LOW, the device checks the resistor on the ISET pin for a short circuit ( $R_{\text{ISET}} < R_{\text{ISET\_SHORT}}$ ). If a short condition is detected, the charger remains in the FAULT state until the input or  $\overline{\text{CE}}$  pin is toggled. If the ISET pin is open circuit, the charger proceeds through pin detection and starts the charger with no charge current. This pin is monitored during charging and changes in  $R_{\text{ISET}}$  while the charger is operating immediately translates to changes in charge current.

An external pulldown resistor (±1% or better recommended to minimize charge current error) from the ISET pin to GND sets the charge current as:

$$I_{CHG} = \frac{K_{ISET}}{R_{ISET}}$$

(1)

where:

- I<sub>CHG</sub> is the desired fast-charge current

- K<sub>ISET</sub> is the gain factor found in the electrical specifications

- R<sub>ISET</sub> is the pulldown resistor from the ISET pin to GND

For charge currents below 50 mA, an extra RC circuit is recommended on the ISET pin to achieve a more stable current signal. For greater accuracy at lower currents, part of the current-sensing FET is disabled to give better resolution.

#### 7.3.2 Supercapacitor Regulation Voltage

The device allows for the supercapacitor regulation voltage,  $V_{REG}$ , to be programmed with a resistor divider between the OUT and FB pins:

$$V_{REG} = V_{FB\_REF} \times \frac{R_{FBT} + R_{FBB}}{R_{FBB}}$$

(2)

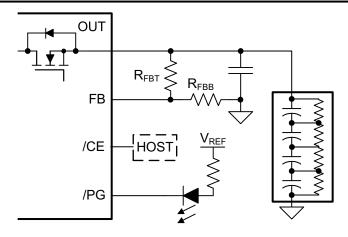

Where  $V_{FB\_REF}$  is listed in the electrical characteristics table. The resistors can be seen in  $\boxtimes$  7-2. The total resistance  $(R_{FBT} + R_{FBB})$  should not exceed 1 M $\Omega$ .

図 7-2. BQ25173 Feedback Divider

### 7.3.3 Supercapacitor Charging Profile

The device charges a supercapacitor in two phases: constant current and constant voltage. Power dissipation in the IC is greatest in fast charge with a lower supercapacitor voltage. If the IC temperature reaches  $T_{REG}$ , the IC enters thermal regulation and reduces the charge current as needed to keep the temperature from rising any further. As the supercapacitor approaches the regulation voltage, the current tapers down to 0 mA. There is no current termination threshold as seen in Li-lon chargers.

## 7.3.4 Status Outputs (PG, STAT)

# 7.3.4.1 Power Good Indicator (PG Pin)

This open-drain pin pulls LOW to indicate a good input source when:

- 1. VIN above V<sub>IN LOWV</sub>

- 2. VIN above V<sub>OUT</sub> + V<sub>SLEEPZ</sub> (not in SLEEP)

- 3. VIN below V<sub>IN OV</sub>

The  $\overline{PG}$  pin can be used as the GND connection for the bottom resistor in the feedback divider to prevent divider leakage current from the supercapacitor when the charger is disabled. This is only recommended when  $V_{REG} \le 5$  V (1-2s supercapacitors) as the absolute maximum rating on  $\overline{PG}$  is 5.5 V. An example circuit can be seen in  $\boxtimes$  8-1.

#### 7.3.4.2 Charging Status Indicator (STAT)

The device indicates the charging state on the open-drain STAT pin. This pin can drive an LED.

CHARGING STATE

STAT PIN STATE

$V_{FB} < 98\%$  of  $V_{FB\_REF}$  High

$V_{FB} > 98\%$  of  $V_{FB\_REF}$  Low

Fault (VIN OVP, OUT OCP, or ISET pin short)

Blink at 1 Hz

表 7-1. STAT Pin State

#### 7.3.5 Protection Features

The device closely monitors input and output voltage, as well as internal FET current and temperature for safe linear regulator operation.

# 7.3.5.1 Input Overvoltage Protection (VIN OVP)

If the voltage at the IN pin exceeds  $V_{IN\_OV}$ , the device enters STANDBY mode. Once the IN voltage recovers to normal level, charging resumes.

### 7.3.5.2 Output Overcurrent Protection (OUT OCP)

During normal operation, the OUT current should be regulated to the ISET programmed value. However, if a short circuit occurs on the ISET pin, the OUT current may rise to an unintended level. If current at the OUT pin exceeds  $I_{OUT\_OCP}$ , the device turns off after a deglitch,  $t_{OUT\_OCP\_DGL}$ , and the device remains latched off. An input supply or  $\overline{CE}$  pin toggle is required to restart operation.

☑ 7-3. Overcurrent Protection

### 7.3.5.3 Thermal Regulation and Thermal Shutdown ( $T_{REG}$ and $T_{SHUT}$ )

The device monitors its internal junction temperature  $(T_J)$  to avoid overheating and to limit the IC surface temperature. When the internal junction temperature exceeds the thermal regulation limit, the device automatically reduces the charge current to maintain the junction temperature at the thermal regulation limit  $(T_{REG})$ . During thermal regulation, the actual charging current is usually below the programmed value on the ISET pin.

Additionally, device thermal shutdown turns off the linear regulator when the IC junction temperature exceeds the  $T_{SHUT}$  threshold. The charger resumes operation when the IC die temperature decreases below the  $T_{SHUT}$  falling threshold.

#### 7.4 Device Functional Modes

#### 7.4.1 Shutdown or Undervoltage Lockout (UVLO)

The device is in the shutdown state if the IN pin voltage is less than  $V_{IN\_LOWV}$ . The internal circuitry is powered down, all the pins are high impedance, and the device draws from the input supply. Once the IN voltage rises above the  $V_{IN\_LOW}$  threshold, the IC will enter Sleep Mode or Active Mode depending on the OUT pin voltage.

### 7.4.2 Sleep Mode

The device is in Sleep Mode when  $V_{IN\_LOWV} < V_{IN} < V_{OUT} + V_{SLEEPZ}$ . The device waits for the input voltage to rise above  $V_{OUT} + V_{SLEEPZ}$  to start operation.

#### 7.4.3 Active Mode

The device is powered up and charges the supercapacitor when the  $\overline{\text{CE}}$  pin is LOW and the IN voltage ramps above both  $V_{\text{IN\_LOWV}}$ , and  $V_{\text{OUT}} + V_{\text{SLEEPZ}}$ . The device draws  $I_{\text{Q\_IN}}$  from the supply to bias the internal circuitry. For details on the device power-up sequence, refer to  $299 \times 7.3.1$ .

# 7.4.3.1 Standby Mode

The device is in Standby Mode if a valid input supply is present and a recoverable fault is detected. The internal circuitry is partially biased, and the device continues to monitor for the recoverable fault to be removed.

#### 7.4.4 Fault Mode

The fault conditions are categorized into recoverable and nonrecoverable as follows:

- Recoverable, from which the device should automatically recover once the fault condition is removed:

- VIN OVP

- Nonrecoverable, requiring pin or input supply toggle to resume operation:

- OUT OCP

- ISET pin short detected

# 8 Application and Implementation

#### Note

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes, as well as validating and testing their design implementation to confirm system functionality.

## 8.1 Application Information

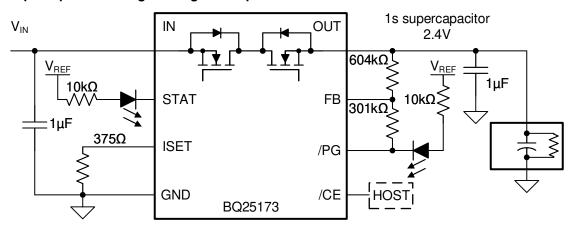

A typical application consists of the device configured as a standalone charger for a 1- to 4-cell supercapacitor. The regulation voltage,  $V_{REG}$ , is configured using a resistor divider between the OUT and FB pins. The charge current is configured using a pulldown resistor on the ISET pin. Pulling the  $\overline{CE}$  pin above  $V_{IH}$  disables the charging function. Charger and input supply status are reported with the STAT and PG pins.

### 8.2 Typical Applications

#### 8.2.1 1s Supercapacitor Charger Design Example

図 8-1. BQ25173 1s Supercapacitor Application Diagram

#### 8.2.1.1 Design Requirements

- Supply voltage is 5 V to 18 V

- Fast charge current: I<sub>CHG</sub> = 800 mA

- Regulation voltage: V<sub>REG</sub> = 2.4 V

- CE is an open-drain control pin

- PG pin is used as the GND connection in the feedback divider to minimize supercapacitor current leakage

#### 8.2.1.2 Detailed Design Procedure

- With R<sub>FBT</sub> = 604 kΩ, calculate R<sub>FBB</sub> so V<sub>REG</sub> = 2.4 V using 式 2

- R<sub>ISET</sub> = [K<sub>ISET</sub> / I<sub>CHG</sub>] from electrical characteristics table.

- K<sub>ISET</sub> = 300 A $\Omega$

- R<sub>ISET</sub> = [300 AΩ/0.8 A] = 375 Ω

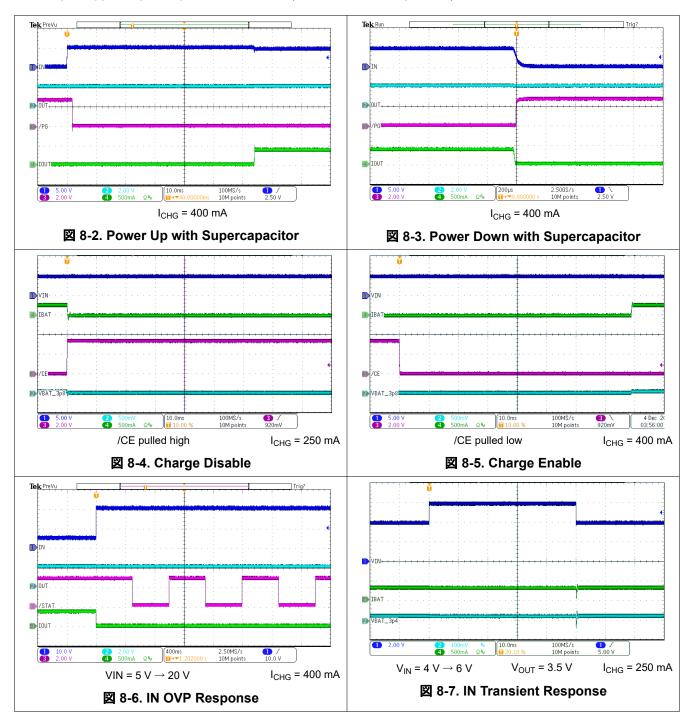

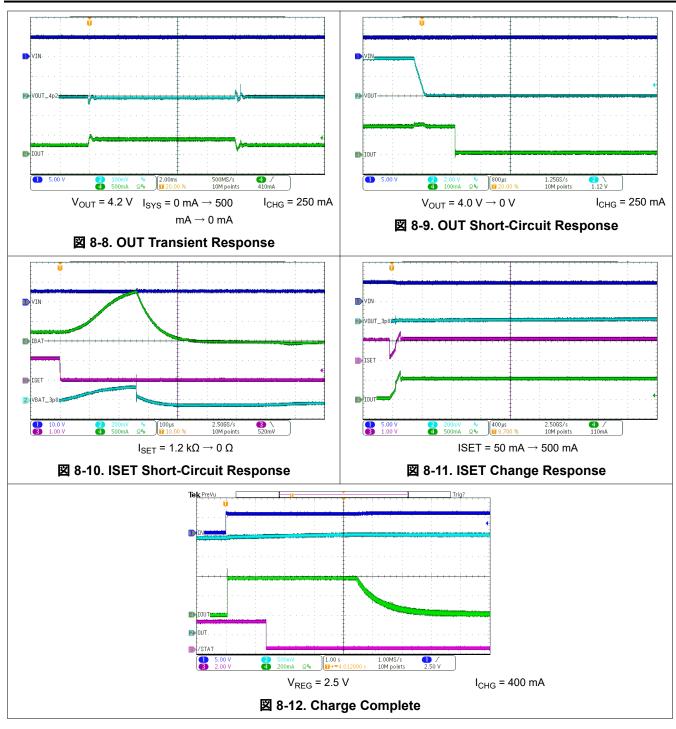

## 8.2.1.3 Application Curves

$C_{IN}$  = 1  $\mu$ F,  $C_{OUT}$  = 1  $\mu$ F,  $C_{SC}$  = 25 F,  $V_{IN}$  = 5 V (unless otherwise specified)

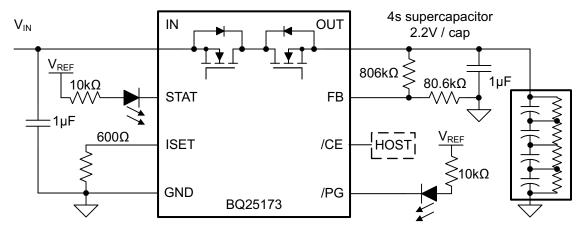

# 8.2.2 4s Supercapacitor Charger Design Example

図 8-13. BQ25173 4s Supercapacitor Application Diagram

## 8.2.2.1 Design Requirements

The design requirements include the following:

- Supply voltage is 9 V to 18 V

- Fast charge current: I<sub>CHG</sub> = 500 mA

- Regulation voltage: V<sub>REG</sub> = 8.8 V

- $\overline{\text{CE}}$  is a control pin, pull high to disable the charger

## 8.2.2.2 Application Curves

For application curves, refer to セクション 8.2.1.3.

# 9 Power Supply Recommendations

The device is designed to operate from an input voltage supply range between 3.0 V and 18 V (up to 40 V tolerant) and current capability of at least the maximum designed charge current. If located more than a few inches from the IN and GND pins, a larger capacitor is recommended.

# 10 Layout

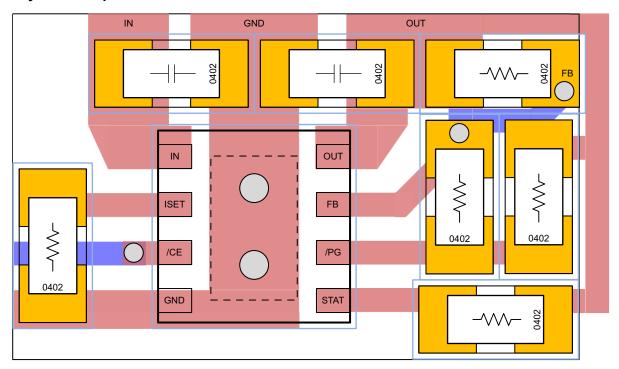

### 10.1 Layout Guidelines

To obtain optimal performance, the decoupling capacitor from IN to GND and the output filter capacitor from OUT to GND should be placed as close as possible to the device, with short trace runs to both IN, OUT, and GND.

- All low-current GND connections should be kept separate from the high-current charge or discharge paths from the supercapacitor. Use a single-point ground technique incorporating both the small signal ground path and the power ground path.

- The high-current charge paths into the IN pin and from the OUT pin must be sized appropriately for the maximum charge current in order to avoid voltage drops in these traces.

# 10.2 Layout Example

図 10-1. BQ25173 Board Layout Example

### 10.3 Thermal Package

The most common measure of package thermal performance is thermal impedance  $(\theta_{JA})$  measured (or modeled) from the chip junction to the air surrounding the package surface (ambient). The mathematical expression for  $\theta_{JA}$  is:

$$\theta_{JA} = (T_J - T) / P \tag{3}$$

Where:

$T_J$  = chip junction temperature

T = ambient temperature

P = device power dissipation

Factors that can influence the measurement and calculation of  $\theta_{JA}$  include:

- · Whether or not the device is board mounted

- · Trace size, composition, thickness, and geometry

- Orientation of the device (horizontal or vertical)

- · Volume of the ambient air surrounding the device under test and airflow

- · Whether other surfaces are in close proximity to the device being tested

Due to the charge profile of supercapacitors, maximum power dissipation is typically seen at the beginning of the charge cycle when the voltage is at its lowest.

Device power dissipation, P, is a function of the charge rate and the voltage drop across the internal PowerFET. P can be calculated from the following equation during charging:

$$P = [V_{(IN)} - V_{(OUT)}] \times I_{(OUT)}$$

(4)

The thermal loop feature reduces the charge current to limit excessive IC junction temperature. It is recommended that the design not run in thermal regulation for typical operating conditions (nominal input voltage and nominal ambient temperatures) and use the feature for nontypical situations such as hot environments or higher than normal input source voltage. With that said, the IC will still perform as described, if the thermal loop is always active.

Copyright © 2022 Texas Instruments Incorporated

# 11 Device and Documentation Support

# 11.1 Device Support

#### 11.1.1 Third-Party Products Disclaimer

TI'S PUBLICATION OF INFORMATION REGARDING THIRD-PARTY PRODUCTS OR SERVICES DOES NOT CONSTITUTE AN ENDORSEMENT REGARDING THE SUITABILITY OF SUCH PRODUCTS OR SERVICES OR A WARRANTY, REPRESENTATION OR ENDORSEMENT OF SUCH PRODUCTS OR SERVICES, EITHER ALONE OR IN COMBINATION WITH ANY TI PRODUCT OR SERVICE.

# 11.2 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. Click on *Subscribe to updates* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

#### 11.3 サポート・リソース

TI E2E<sup>™</sup> サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、該当する貢献者により、現状のまま提供されるものです。これらは TI の仕様を構成するものではなく、必ずしも TI の見解を反映したものではありません。 TI の使用条件を参照してください。

#### 11.4 Trademarks

TI E2E<sup>™</sup> is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 11.5 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### 11.6 Glossary

TI Glossary

This glossary lists and explains terms, acronyms, and definitions.

# 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

Copyright © 2022 Texas Instruments Incorporated

Submit Document Feedback

www.ti.com 9-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins | Package qty   Carrier | <b>RoHS</b> (3) | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|----------------|-----------------------|-----------------|-------------------------------|----------------------------|--------------|------------------|

| BQ25173DSGR           | Active | Production    | WSON (DSG)   8 | 3000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | B173             |

| BQ25173DSGR.A         | Active | Production    | WSON (DSG)   8 | 3000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | B173             |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF BQ25173:

Automotive: BQ25173-Q1

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 9-Nov-2025

| NOTE: Qualified Version Definiti | on: | efinitio | Defir | ersion | V | Qualified | • | TF: | VΩ | ١ |

|----------------------------------|-----|----------|-------|--------|---|-----------|---|-----|----|---|

|----------------------------------|-----|----------|-------|--------|---|-----------|---|-----|----|---|

• Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects

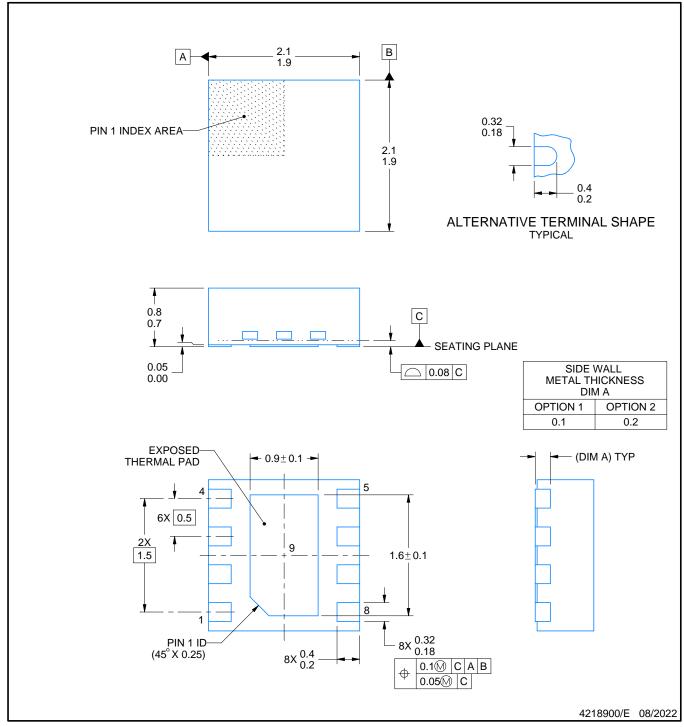

2 x 2, 0.5 mm pitch

PLASTIC SMALL OUTLINE - NO LEAD

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

PLASTIC SMALL OUTLINE - NO LEAD

#### NOTES:

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

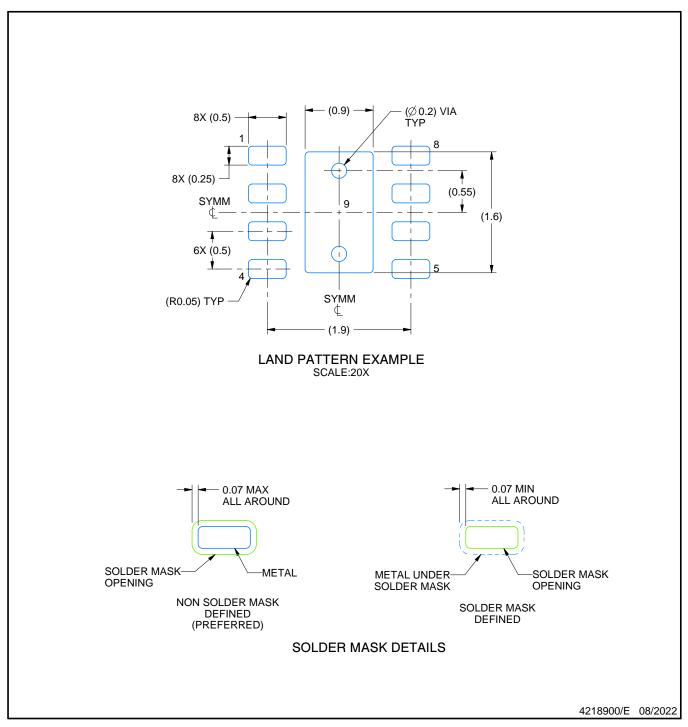

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

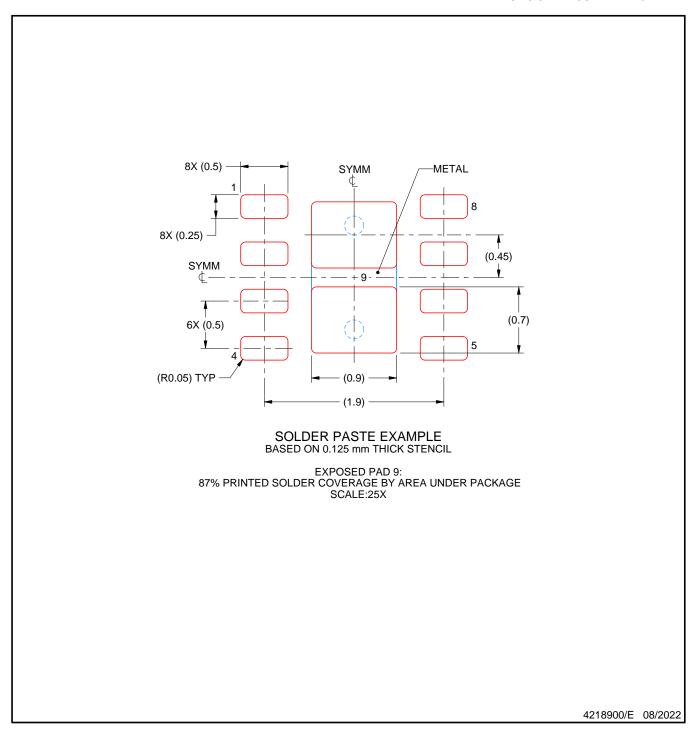

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TIの製品は、TIの販売条件、TIの総合的な品質ガイドライン、 ti.com または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。 TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日:2025 年 10 月