# DP83TC813x-Q1 TC-10 準拠、小型フォーム ファクタ 100BASE-T1 車載用イーサネット PHY

## 1 特長

- Open Alliance および IEEE 802.3bw 100BASE-T1 準拠

- 内蔵 LPF によりレベル IV 放射に合格

- 20µA 未満のスリープ電流で TC-10 準拠

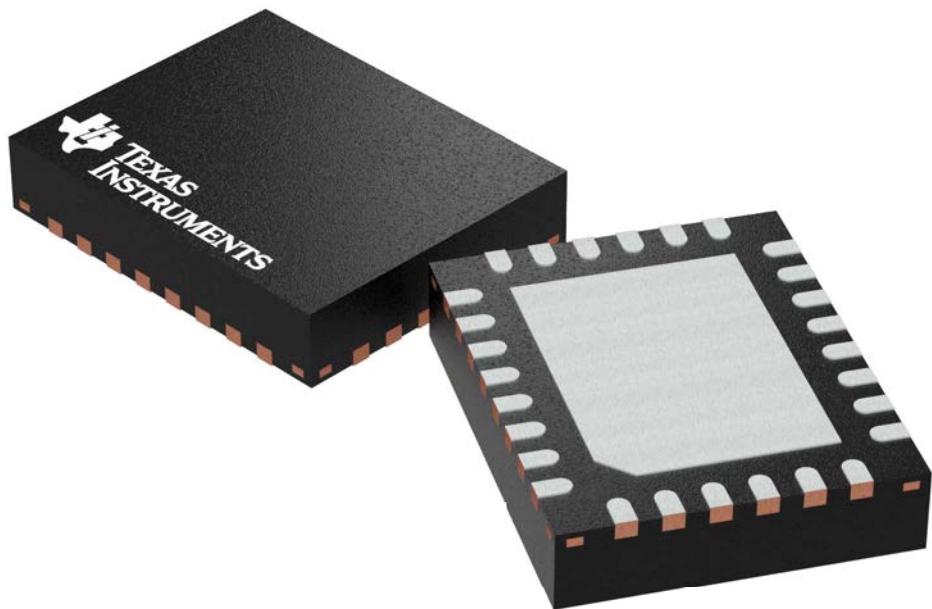

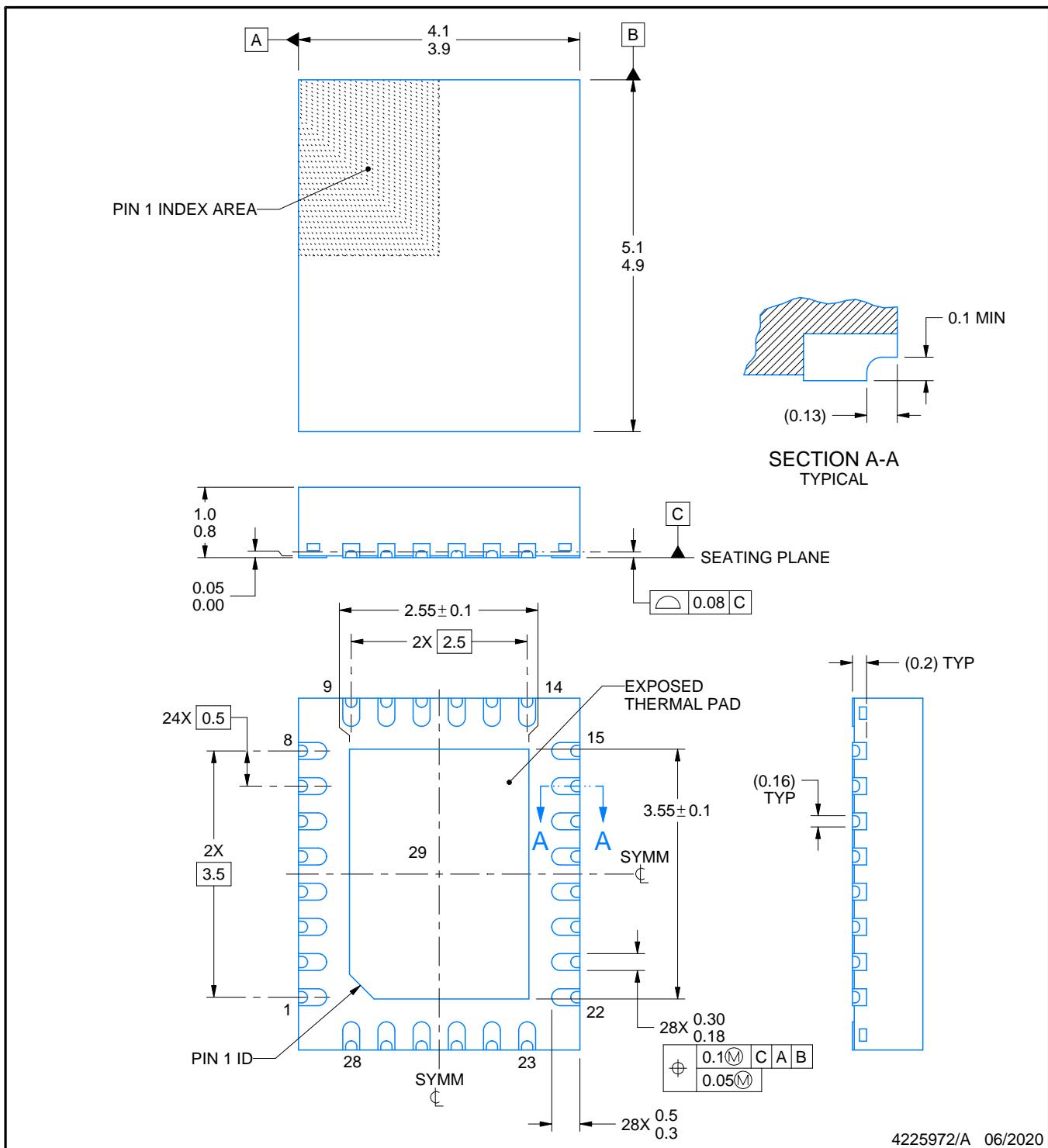

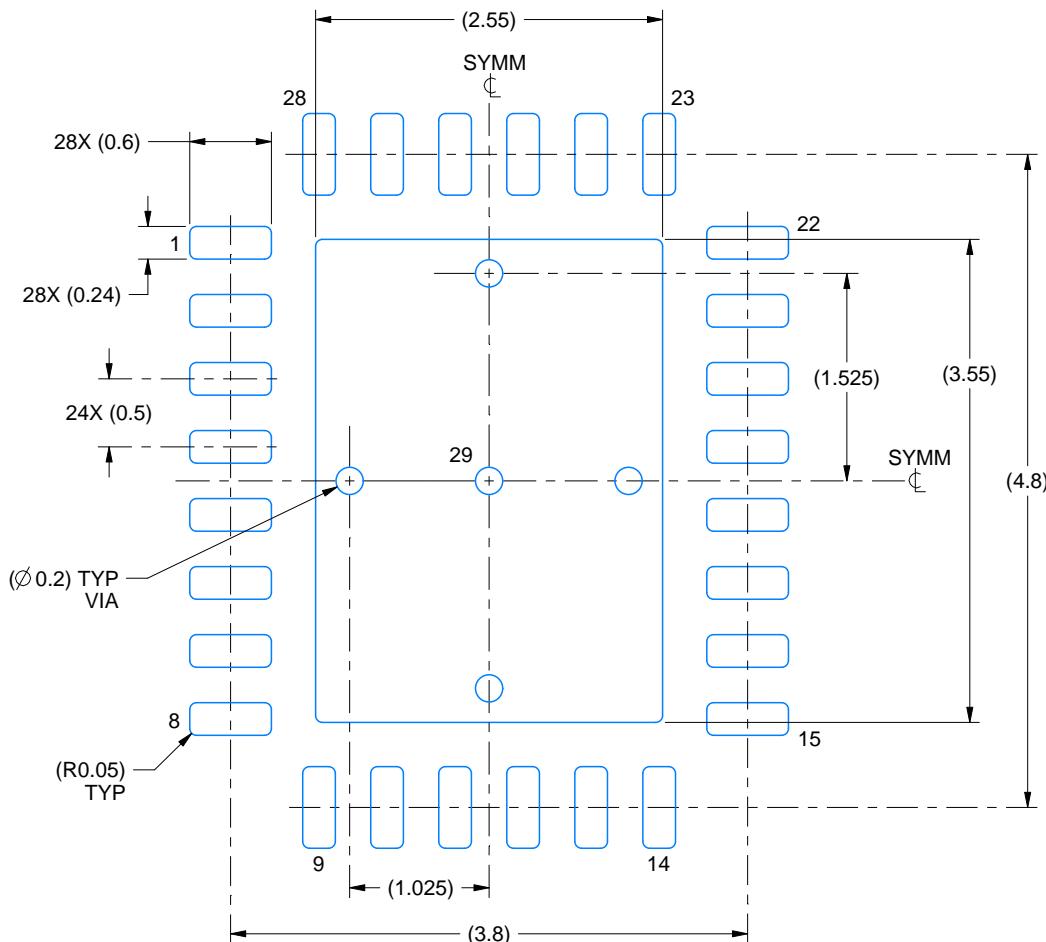

- 小型フォーム ファクタ: 28 ピン VQFN (5mm x 4mm)

- SAE J2962-3 EMC 準拠

- 設定可能な I/O 電圧: 3.3V, 2.5V, 1.8V

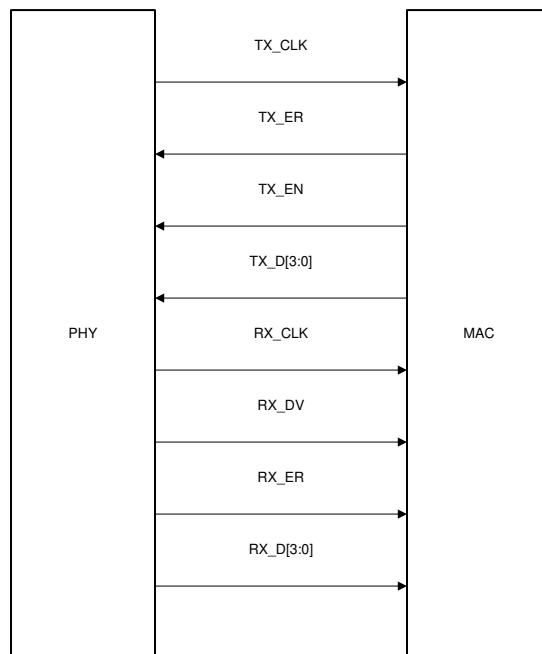

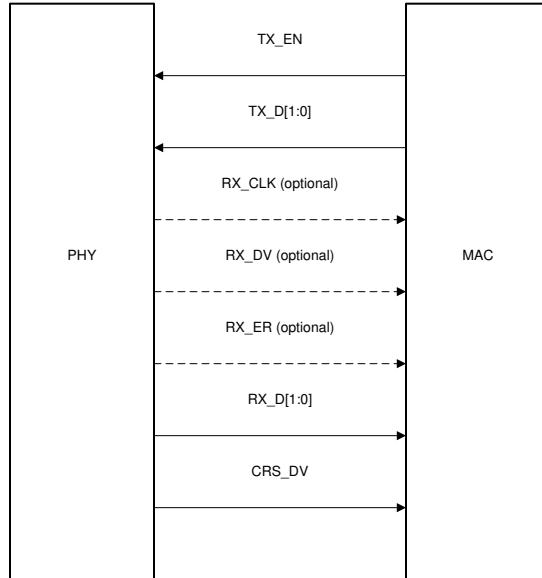

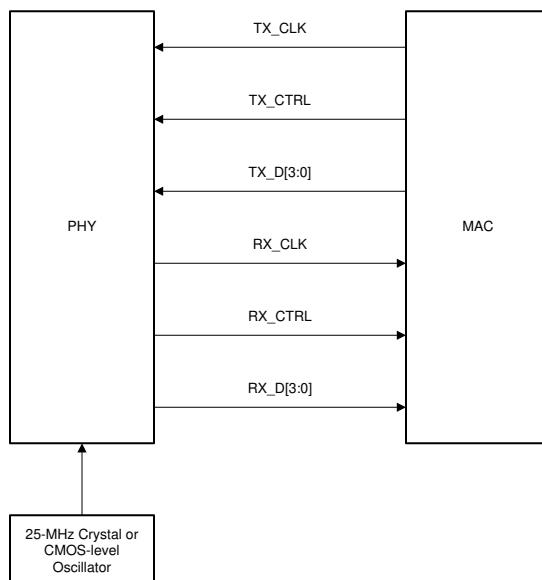

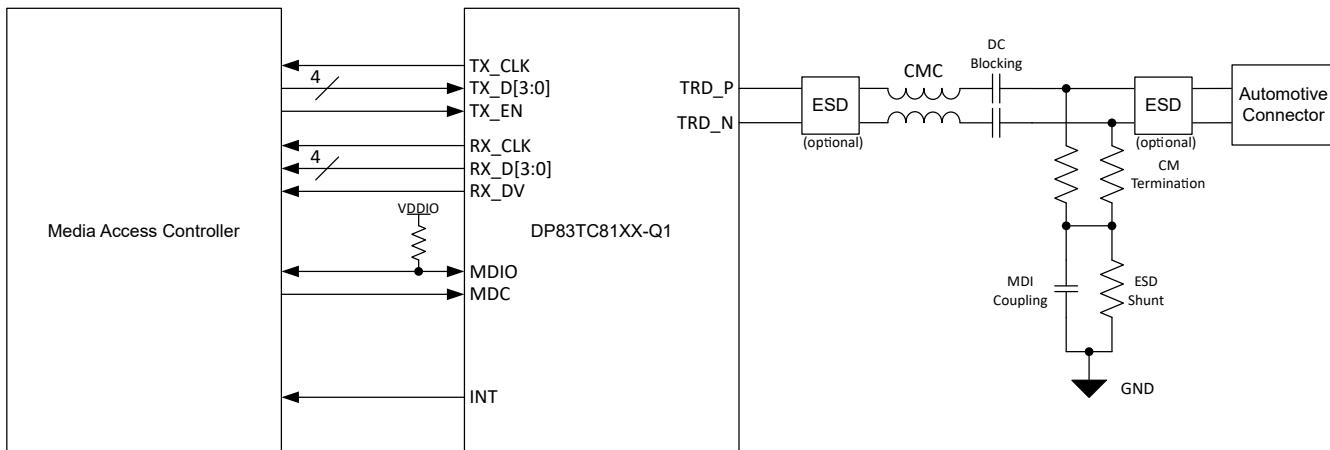

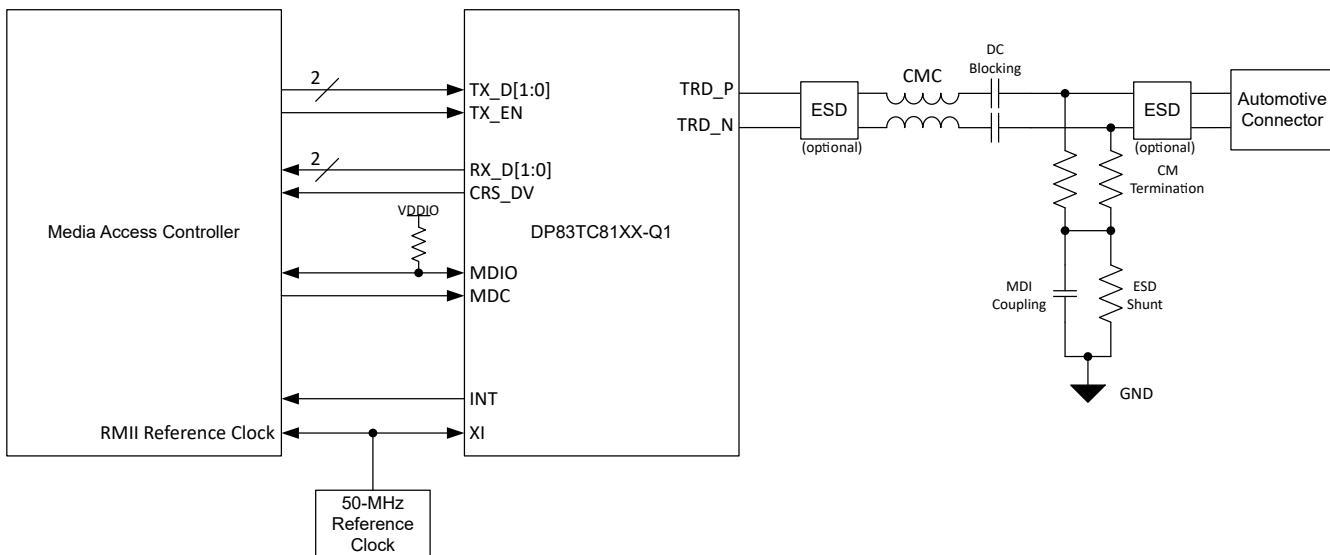

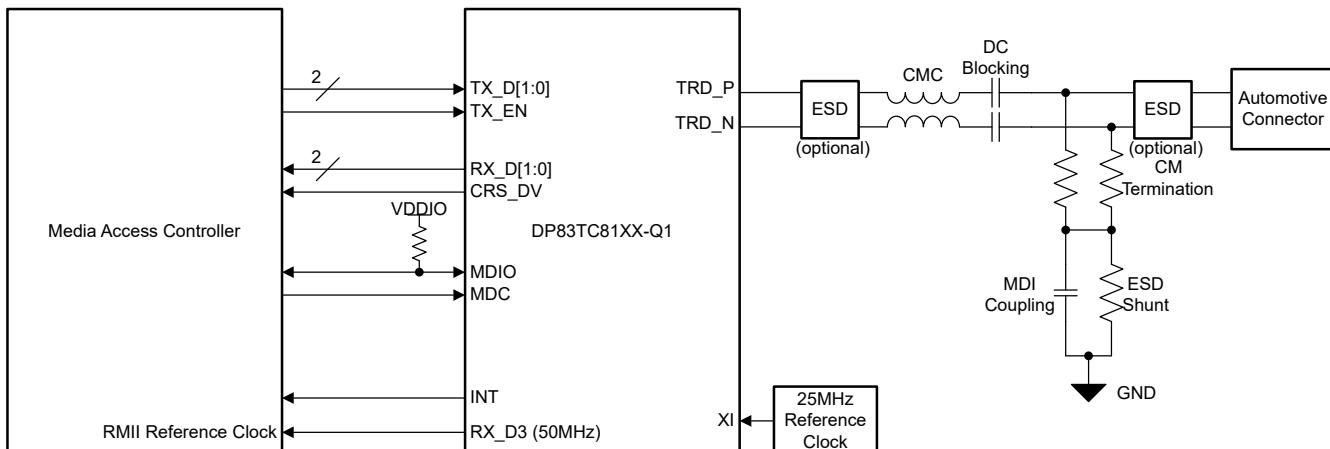

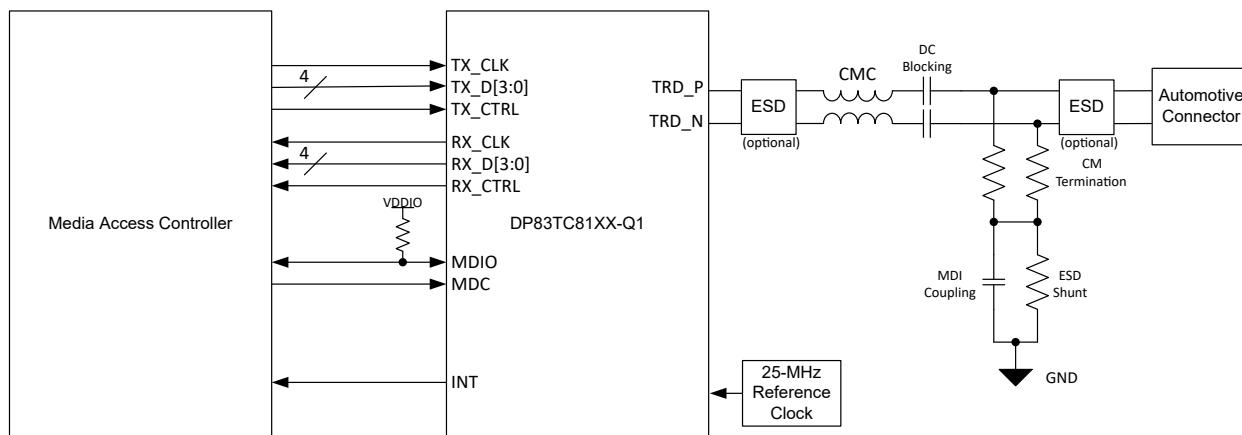

- MAC インターフェイス: MII, RMII, RGMII, SGMII

- MAC インターフェイス ピンに対して独立した電圧レール (3.3V, 2.5V, 1.8V) を選択可能

- 車載アプリケーション用に AEC-Q100 認定済み:

- 温度グレード 1: -40°C ~ +125°C の動作時周囲温度

- ピン 19 および 20 に対して ±8kV HBM ESD

- ピン 19 および 20 に対して IEC61000-4-2 ESD 分類レベル 4: ±8kV 接触放電

- IEEE 1588 SFD のサポート

- 802.3br フレーム プリエンプション サポート準拠の TSN

- 低い動作時消費電力: 230mW 未満

- 診断ツール キット

- 信号品質表示 (SQI)

- 時間領域反射計測 (TDR)

- 静電放電センサ

- 電圧センサ

- PRBS 内蔵セルフ テスト

- ループバック

- VQFN、ウェッタブル フランク パッケージ

- **機能安全対応**

- 機能安全システムの設計に役立つ資料を利用可能

## 2 アプリケーション

- 先進運転支援システム (ADAS)

- ゲートウェイおよび車体制御

- テレマティクス

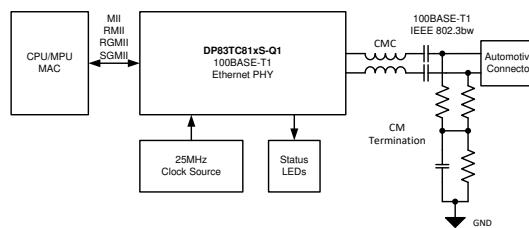

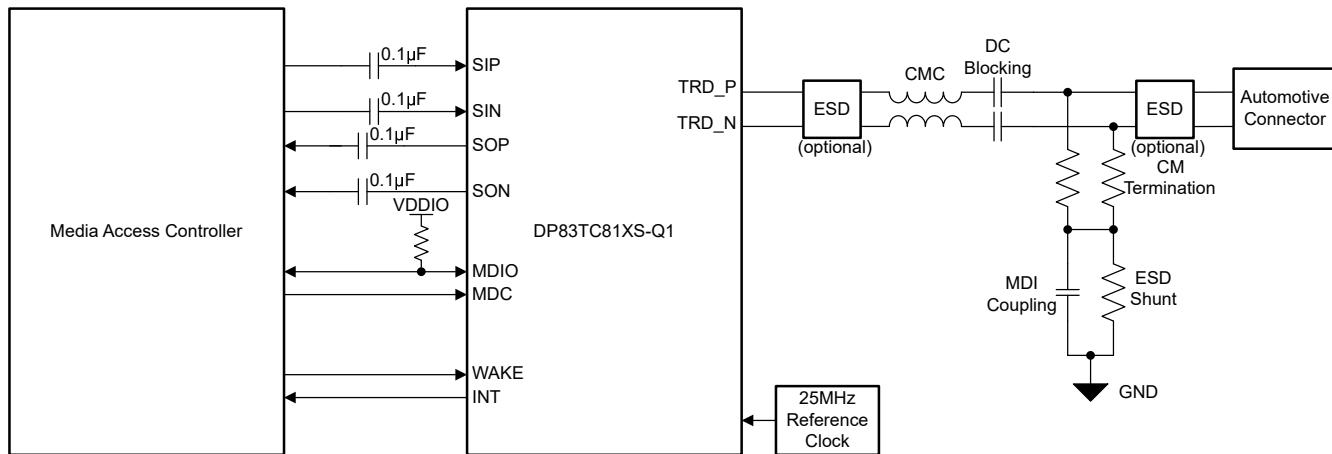

概略回路図

## 3 説明

DP83TC813-Q1 デバイスは、IEEE 802.3bw 準拠の車載用 PHYTER™ イーサネット物理層トランシーバで、シールドなしツイストペア ケーブルを使って動作できます。この PHY は、TC10 スリープおよびウェイク機能をサポートしています。この PHY は、非シールド単一ツイストペアケーブルでデータを送受信するために必要なすべての物理層機能を提供します。このデバイスは xMII の柔軟性があり、標準の MII、RMII、RGMII、SGMII MAC インターフェイスをサポートします。また、この PHY は MDI 側にローパス フィルタを内蔵することで、放射を低減しています。

このデバイスには診断ツールキットが含まれており、広範なリアルタイム監視ツール、デバッグツール、テストモードが用意されています。ツールキットには、初めて内蔵された静電放電 (ESD) 監視ツールが含まれています。このデバイスを使用すると、MDI 上の ESD イベントをカウントでき、プログラム可能な割り込みを使用してリアルタイム監視も行えます。さらに、DP83TC813-Q1 には、疑似ランダムバイナリ シーケンス (PRBS) フレーム生成ツールが含まれており、内部ループバックと完全に互換性があり、MAC を使用せずデータを送受信します。このデバイスは、5.00mm × 4.00mm、28 ピンの VQFN ウェッタブル フランク パッケージに収容されています。

### パッケージ情報

| 部品番号          | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|---------------|----------------------|--------------------------|

| DP83TC813S-Q1 | RHF (VQFN, 28)       | 5.00mm × 4.00mm          |

| DP83TC813R-Q1 | RHF (VQFN, 28)       | 5.00mm × 4.00mm          |

(1) 詳細については、[セクション 12](#) を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあります。TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                |    |                         |     |

|----------------|----|-------------------------|-----|

| 1 特長           | 1  | 7.5 プログラミング             | 59  |

| 2 アプリケーション     | 1  | 8 レジスタ マップ              | 63  |

| 3 説明           | 1  | 8.1 レジスタ アクセスの概要        | 63  |

| 4 デバイス比較表      | 3  | 8.2 DP83TC813 のレジスタ     | 64  |

| 5 ピン構成および機能    | 4  | 9 アプリケーションと実装           | 163 |

| 6 仕様           | 17 | 9.1 アプリケーション情報          | 163 |

| 6.1 絶対最大定格     | 17 | 9.2 代表的なアプリケーション        | 163 |

| 6.2 ESD 定格     | 17 | 9.3 電源に関する推奨事項          | 170 |

| 6.3 推奨動作条件     | 17 | 9.4 レイアウト               | 172 |

| 6.4 熱に関する情報    | 18 | 10 デバイスおよびドキュメントのサポート   | 175 |

| 6.5 電気的特性      | 18 | 10.1 ドキュメントの更新通知を受け取る方法 | 175 |

| 6.6 タイミング要件    | 23 | 10.2 サポート・リソース          | 175 |

| 6.7 タイミング図     | 26 | 10.3 コミュニティリソース         | 175 |

| 6.8 代表的特性      | 32 | 10.4 商標                 | 175 |

| 7 詳細説明         | 33 | 10.5 静電気放電に関する注意事項      | 175 |

| 7.1 概要         | 33 | 10.6 用語集                | 175 |

| 7.2 機能ブロック図    | 34 | 11 改訂履歴                 | 175 |

| 7.3 機能説明       | 35 | 12 メカニカル、パッケージ、および注文情報  | 176 |

| 7.4 デバイスの機能モード | 44 |                         |     |

## 4 デバイス比較表

| 部品番号          | SGMII のサポート | 動作温度          |

|---------------|-------------|---------------|

| DP83TC813R-Q1 | なし          | -40°C ~ 125°C |

| DP83TC813S-Q1 | あり          | -40°C ~ 125°C |

## 5 ピン構成および機能

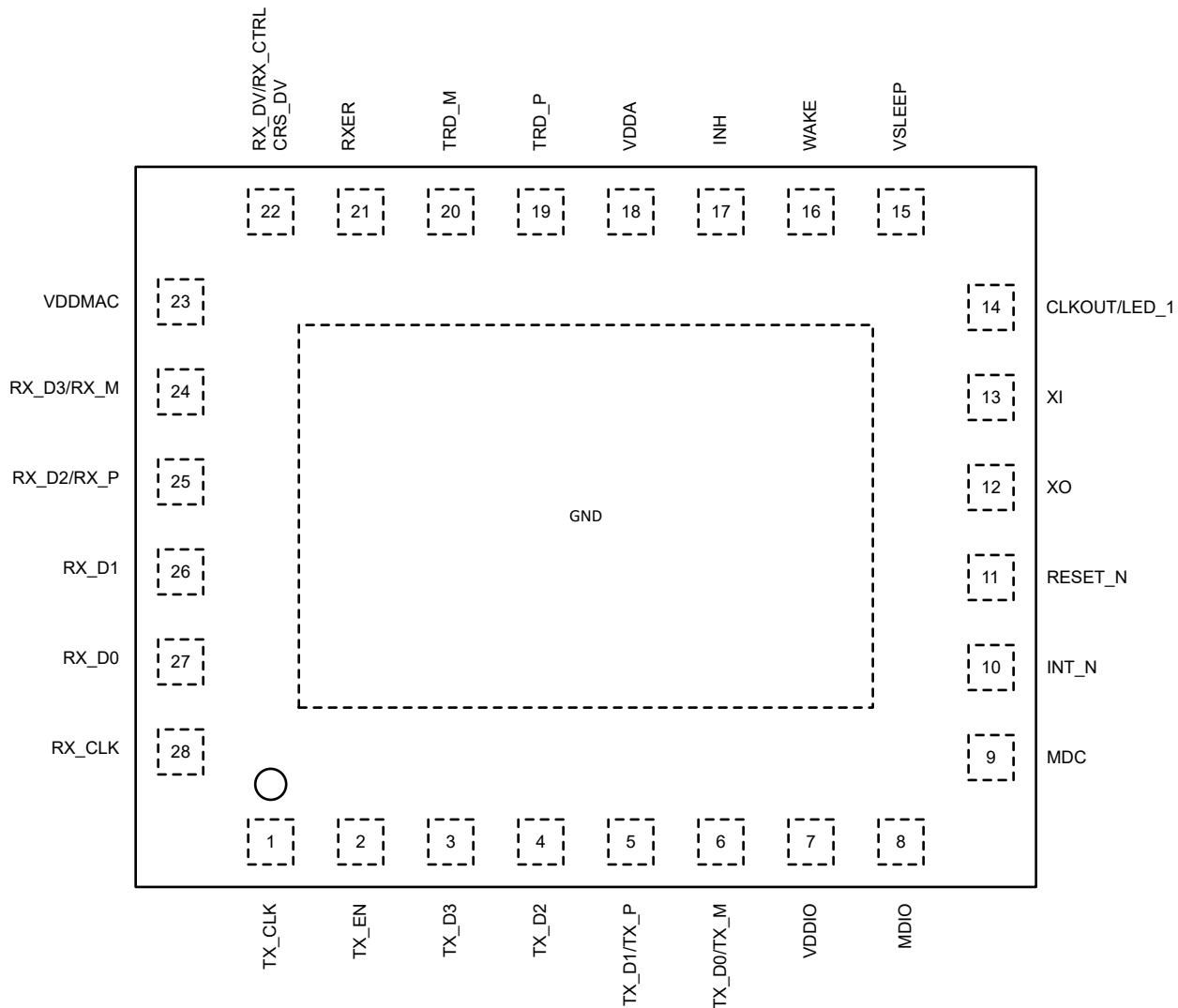

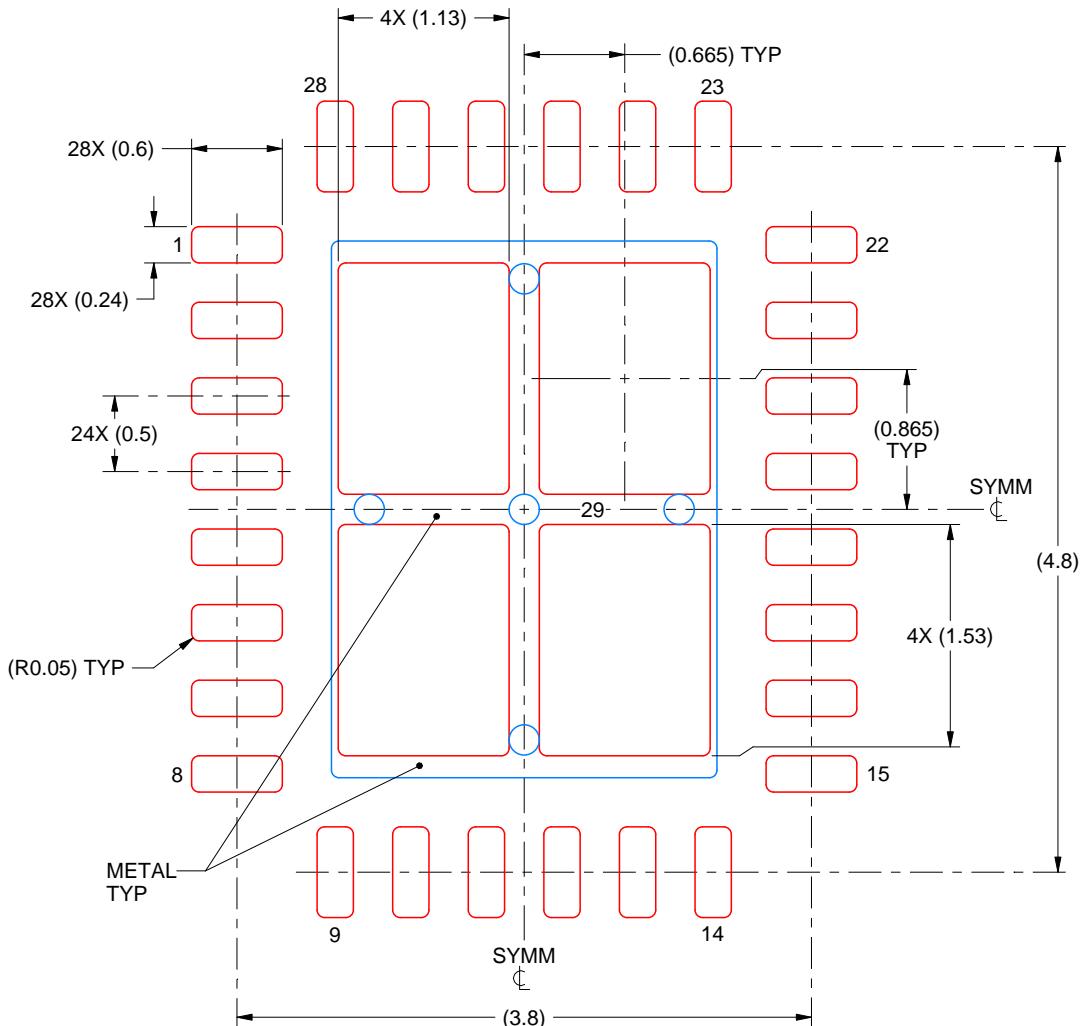

図 5-1. DP83TC813S-Q1 RHF パッケージ

28-ピン VQFN

上面図

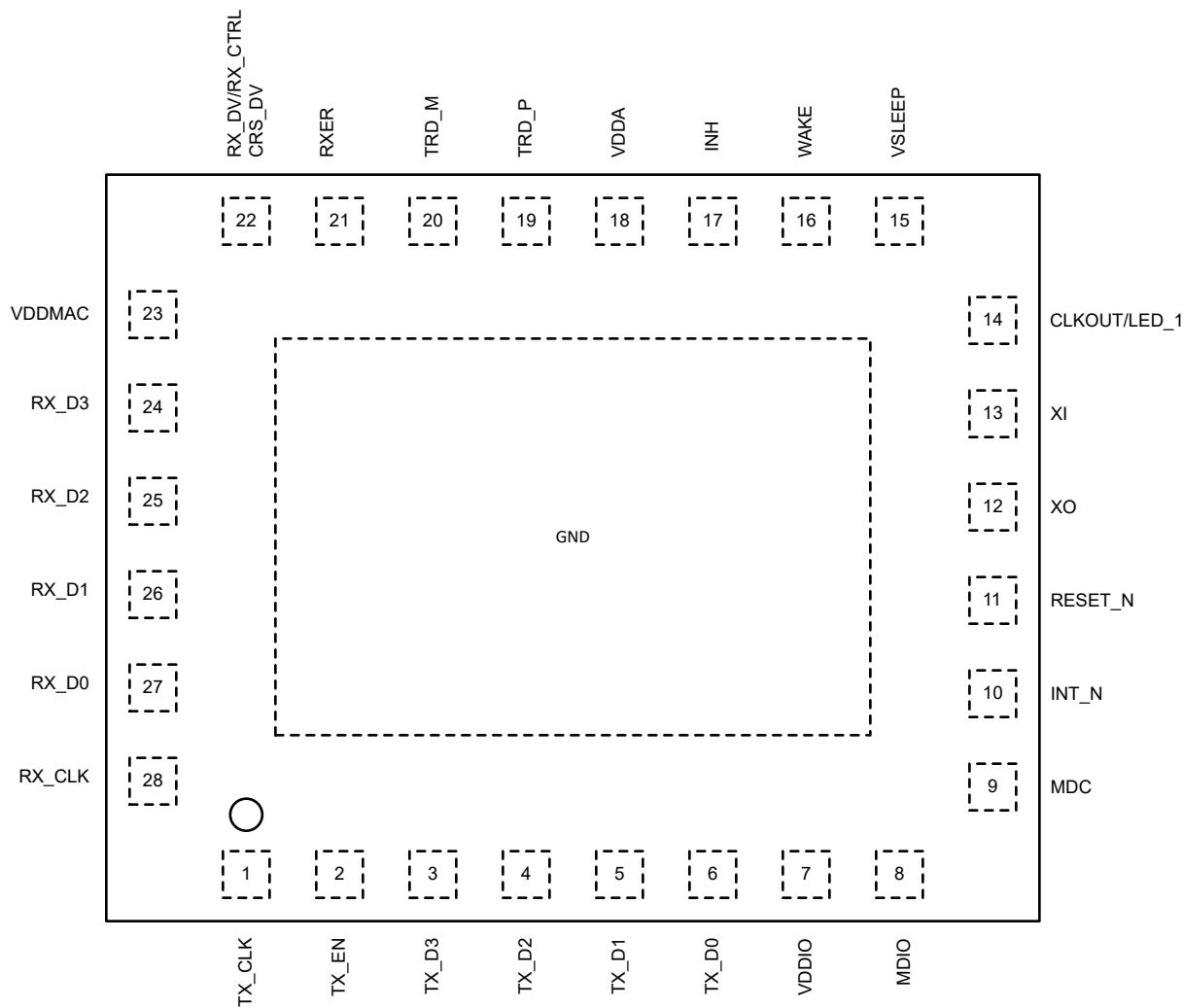

**図 5-2. DP83TC813R-Q1 RHF パッケージ

28-ピン VQFN

上面図**

表 5-1. ピンの機能

| ピン                           |    | 状態 <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------------------|----|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称 <sup>(2)</sup>            | 番号 |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <b>MAC インターフェイス</b>          |    |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RX_D3                        | 24 | S, PD, O          | <b>受信データ:</b> ケーブルで受信されたシンボルはデコードされ、RX_CLK の立ち上がりエッジに同期してこれらのピンから送信されます。RX_DV がアサートされている間のみ有効なデータを含みます。MII および RGMII モードでは、データニブル RX_D[3:0] を出力します。RMII モードでは 2 ビット RX_D[1:0] を出力します。RMII モードでは、RX_D[3:2] は使用されません。                                                                                                                                                                                                                                             |

| RX_D2                        |    |                   | PHY が RMII リーダー モードにブートストラップされている場合、50MHz クロック基準が RX_D3 に自動的に出力されます。このクロックは MAC に入力する必要があります。                                                                                                                                                                                                                                                                                                                                                                   |

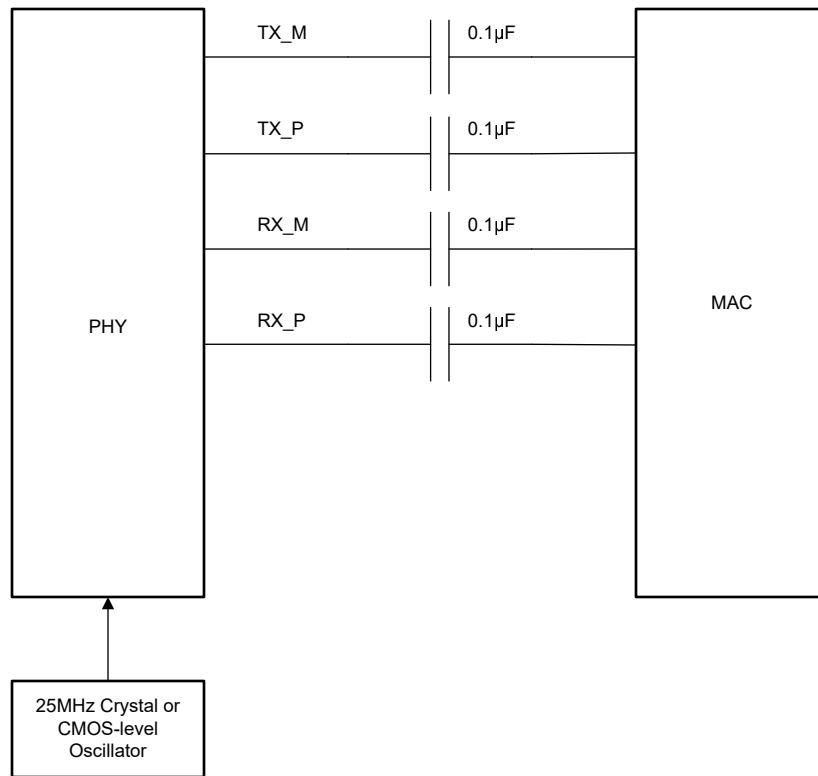

| RX_D1                        |    |                   | <b>RX_M/RX_P:</b> 差動 SGMII データ出力。これらのピンは PHY から MAC にデータを送信します。                                                                                                                                                                                                                                                                                                                                                                                                 |

| RX_D0                        |    |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RX_CLK                       | 28 | S, PD, O          | <b>受信クロック:</b> MII および RGMII モードでは、受信クロックから 25MHz 基準クロックが供給されます。<br><b>RGMII および SGMII モードでは未使用</b>                                                                                                                                                                                                                                                                                                                                                             |

| RX_ER                        | 21 | S, PD, O          | <b>受信エラー:</b> MII および RMII モードでは、このピンは受信パケット内で受信エラー シンボルが検出されたことを示します。MII モードでは、RX_CLK の立ち上がりエッジに同期して、RX_ER が High にアサートされます。RMII モードでは、基準クロックの立ち上がりエッジに同期して、RX_ER が High にアサートされます。PHY は受信エラーの際にデータを自動的に破損するため、MII または RMII では MAC がこのピンを使用する必要はありません。<br><b>RGMII および SGMII モードでは未使用</b>                                                                                                                                                                      |

| RX_DV<br>CRS_DV<br>RX_CTRL   | 22 | S, PD, O          | <b>受信データ有効:</b> MII モードでは、このピンは RX_D[3:0] 上に有効なデータが出力されていることを示します。<br><b>キャリア センス データ有効:</b> このピンは、キャリア検出とデータ有効を 1 本の非同期信号にまとめて示します。RMII モードでは、CRS_DV がアサートされているときに RX_D[1:0] にデータが出力されます。<br><b>RGMII 受信制御:</b> 受信制御は、受信データ有効表示と受信エラー表示を 1 つの信号に統合したものです。RX_DV は RX_CLK の立ち上がりエッジに示され、RX_ER は RX_CLK の立ち下がりエッジに示されます。<br>このピンを RX_DV として構成するにはレジスタ 0x0551 = 0x0000 を設定し、このピンを CRS_DV としてプログラムするにはレジスタ 0x0551 = 0x0010 (デフォルト) を設定します。<br><b>SGMII モードでは未使用</b> |

| TX_CLK                       | 1  | PD, I, O          | <b>送信クロック:</b> MII モードでは、送信クロックは 25MHz 出力 (50Ω ドライバ) で、基準クロックを基準とする位相は一定です。RGMII モードでは、このクロックが MAC 層から PHY へ入力されます。25MHz クロックを供給する必要があります (同期 RGMII が有効化されない限り、リファレンス クロックに対して一定の位相を持つ必要はありません)。<br><b>RGMII および SGMII モードでは未使用</b>                                                                                                                                                                                                                             |

| TX_EN<br>TX_CTRL             | 2  | PD, I             | <b>送信イネーブル:</b> MII モードでは、送信イネーブルは送信クロックの立ち上がりエッジより前に提示されます。TX_EN は、TX_D[3:0] に有効なデータ入力が存在することを示します。RMII モードでは、送信イネーブルは送信クロックの立ち上がりエッジより前に提示されます。TX_EN は、TX_D[1:0] に有効なデータ入力が存在することを示します。<br><b>RGMII 送信制御:</b> 送信制御は、送信イネーブルと送信エラー表示を 1 つの信号に統合したものです。TX_EN は TX_CLK の立ち上がりエッジの前に示され、TX_ER は TX_CLK の立ち下がりエッジより前に示されます。<br><b>SGMII モードでは未使用</b>                                                                                                               |

| TX_D3                        | 3  | PD, I             | <b>送信データ:</b> MII および RGMII モードでは、送信データニブル TX_D[3:0] を、TX_CLK の立ち上がりエッジより前に MAC から受信します。RMII モードでは、TX_D[1:0] を基準クロックの立ち上がりエッジより前に MAC から受信します。RMII モードでは TX_D[3:2] は使用しません。                                                                                                                                                                                                                                                                                     |

| TX_D2                        |    |                   | <b>TX_M/TX_P:</b> 差動 SGMII データ入力。これらのピンは、MAC から PHY に送信されたデータを受信します。                                                                                                                                                                                                                                                                                                                                                                                            |

| TX_D1                        |    |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TX_P                         |    |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TX_D0                        | 6  |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <b>シリアル マネージメント インターフェイス</b> |    |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| MDC                          | 9  | I                 | <b>管理データ クロック:</b> MDIO シリアル マネージメント入力および出力データに同期したクロック。このクロックは、MAC の送信クロックおよび受信クロックと非同期にすることができます。                                                                                                                                                                                                                                                                                                                                                             |

**表 5-1. ピンの機能 (続き)**

| ピン                |    | 状態 <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                                                                           |

|-------------------|----|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称 <sup>(2)</sup> | 番号 |                   |                                                                                                                                                                                                                                                                                                              |

| MDIO              | 8  | OD, IO            | <p><b>管理データ入出力 (Management Data Input/Output):</b> 管理ステーションまたは PHY から出力される可能性がある双方向管理データ信号。このピンはブルアップ抵抗を必要とします。同一の MDIO-MDC バスを複数の PHY で共有するシステムでは、MDIO ラインに 1 本だけブルアップ抵抗を使用する必要があります。</p> <p>2.2kΩ と 9kΩ の間に抵抗を使用することを推奨します。</p> <p>Open Alliance 準拠に合格するには MDIO/MDC へのアクセスが必要です。セクション 7.3.2 を参照してください。</p> |

表 5-1. ピンの機能 (続き)

| ピン                       |    | 状態 <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------|----|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称 <sup>(2)</sup>        | 番号 |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| <b>制御インターフェイス</b>        |    |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| INT                      | 10 | PU, OD, IO        | <p><b>割り込み:</b> アクティブ Low 出力。割り込み条件が発生すると、Low にアサートされます。このピンは弱いブルアップを内蔵しています。各種割り込みトリガを有効化するには、レジスタ アクセスが必要です。割り込みイベントフラグが一度セットされると、その割り込みイベントをクリアするためにもレジスタ アクセスが必要になります。このピンは、レジスタ 0x0011 を用いてアクティブ High 出力として構成することもできます。</p> <p>レジスタ 12 ~ 13 の割り込みステータスは、INT_N が LOW のときにのみ読み取ることを推奨します。また、このピンをパワーダウン制御ピンとして動作させることもでき、その場合は本ピンを low にアサートすると PHY をパワーダウン モードにし、high にアサートすると PHY を通常モードに戻します。この機能は、レジスタ 0x0011 によって有効化できます。</p> |

| RESET                    | 11 | PU, I             | <p><b>リセット:</b> アクティブ Low 入力で、PHY を初期化または再初期化します。このピンを 1μs 以上 Low にアサートすると、リセットプロセスが強制的に開始されます。すべての内部レジスタは、「レジスタ マップ」セクションで各ビットに対して指定されたデフォルト状態に再初期化されます。リセットのデアサート時に、すべてのブートストラップ ピンが再サンプリングされます。</p>                                                                                                                                                                                                                                |

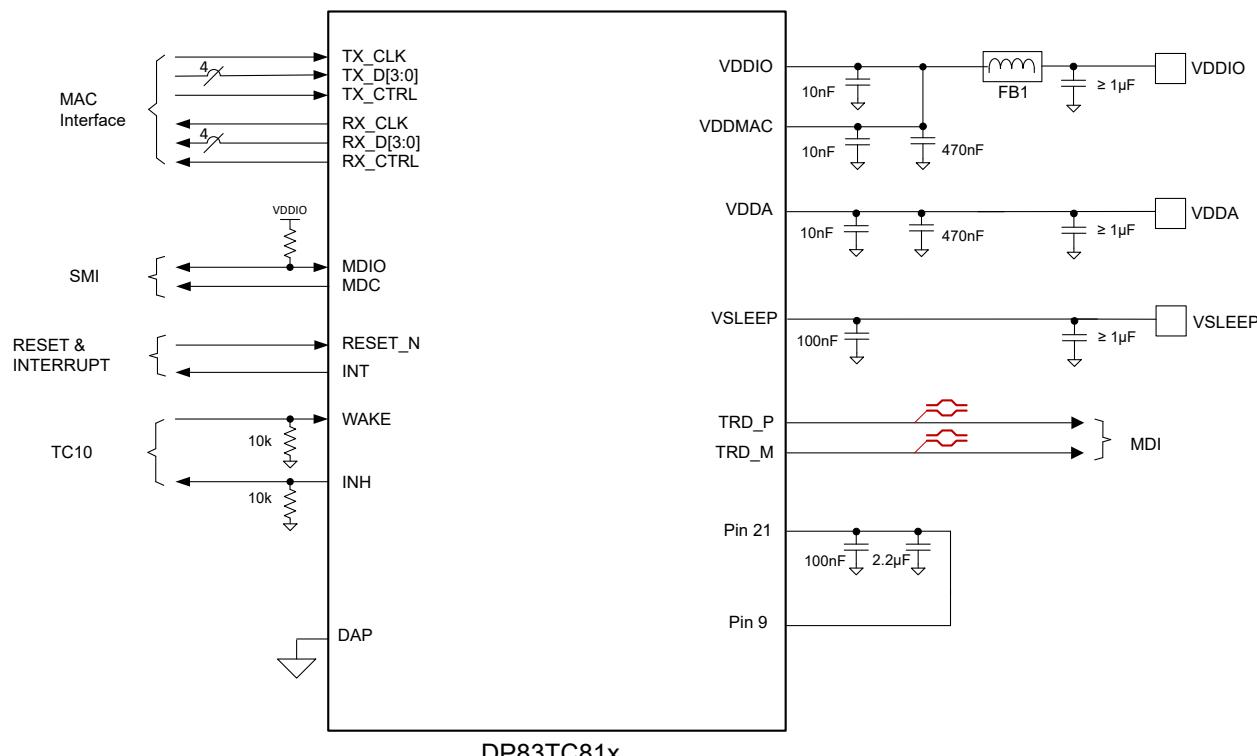

| WAKE                     | 16 | PD, I/O           | <p><b>WAKE:</b> アクティブ HIGH 入力であり、PHY を TC-10 スリープからウェークアップします。電源投入時にこのピンを HIGH にアサートすると、PHY がスリープ状態になることを防ぎます。TC-10 回路を実装する場合は、誤ってウェークアップしてしまうことを防ぐため、10kΩ の外付けブルダウン抵抗を使用できます。このピンを VSLEEP に直接接続することで、本デバイスをウェークアップできます。</p>                                                                                                                                                                                                          |

| INH                      | 17 | O, OD             | <p><b>INH:</b> アクティブ HIGH 出力です。PHY が TC-10 スリープのとき、このピンはハイインピーダンスになります。このピンは、その他のすべての PHY 状態では HIGH になります。TC-10 回路を実装する場合は、外付け 2kΩ ~ 10kΩ ブルダウン抵抗を使用する必要があります。複数のデバイスが INH ピンを共有している場合は、ブルダウン抵抗を 1 本だけ使用します。</p>                                                                                                                                                                                                                      |

| <b>クロックインターフェイス</b>      |    |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| XI                       | 13 | I                 | <p><b>基準クロック入力 (RMII):</b> RMII フォロワ モードで基準クロックとして 50MHz CMOS レベル発振器を入力します。RMII リーダー モードは、25MHz の水晶または発振器を基準クロックとして入力します。</p> <p><b>基準クロック入力 (その他の MAC インターフェイス):</b> 25MHz の水晶または発振器を基準クロック入力として使用します。本デバイスは、外付け水晶振動子（ピン XI とピン XO の間に接続）と外付け CMOS レベル発振器（ピン XI のみに接続、XO は浮動）のどちらにも対応しています。</p>                                                                                                                                      |

| XO                       | 12 | O                 | <p><b>基準クロック出力:</b> XO ピンは水晶振動子の場合にのみ使用されます。CMOS レベル発振器を XI に接続する場合、このピンを浮動にする必要があります。</p>                                                                                                                                                                                                                                                                                                                                            |

| <b>LED/GPIO インターフェイス</b> |    |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| CLKOUT/<br>LED_1         | 14 | IO                | <p><b>クロック出力:</b> 50MHz である RMII フォロワを除くすべてのモードでの 25MHz 基準クロック。このピンは、レジスタ設定により LED または GPIO として使用できます。clkout ピンでのスイッチングを無効にするには、レジスタ &lt;0x045F&gt;=0x000F およびレジスタ &lt;0x0453&gt;=0x0003 をプログラムします。</p>                                                                                                                                                                                                                               |

| <b>メディア依存インターフェイス</b>    |    |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| TRD_M                    | 20 | IO                | 差動送信および受信: 100BASE-T1 動作用に構成された双方向差動信号。IEEE 802.3bw 準拠。                                                                                                                                                                                                                                                                                                                                                                               |

| TRD_P                    | 19 |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| <b>電源接続</b>              |    |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| VDDA                     | 18 | 電源                | <p><b>コア電源:</b> 3.3V<br/>0.47μF および 0.01μF セラミック デカップリング コンデンサの使用を推奨します。オプションとしてフェライト ビーズも使用できます。</p>                                                                                                                                                                                                                                                                                                                                 |

| VDDIO                    | 7  | 電源                | <p><b>IO 電源:</b> 1.8V、2.5V、または 3.3V<br/>フェライト ビーズ、0.47μF および 0.01μF セラミック デカップリング コンデンサの使用を推奨します。</p>                                                                                                                                                                                                                                                                                                                                 |

| VDDMAC                   | 23 | 電源                | <p><b>オプションの MAC インターフェイス電源:</b> 1.8V、2.5V、または 3.3V<br/>MAC インターフェイス ピン向けのオプションの独立電源です。このピンは MAC インターフェイス ピンに電源を供給し、他の IO ピンとは異なる電圧レベルに設定できます。0.47μF および 0.01μF セラミック デカップリング コンデンサ、フェライト ビーズの使用を推奨します。システムで個別の VDDMAC を必要としない場合は、VDDIO に接続しなければなりません。VDDIO に接続する場合、0.47μF は取り外すことができます。</p>                                                                                                                                          |

**表 5-1. ピンの機能 (続き)**

| ピン                |     | 状態 <sup>(1)</sup> | 説明                                                           |

|-------------------|-----|-------------------|--------------------------------------------------------------|

| 名称 <sup>(2)</sup> | 番号  |                   |                                                              |

| VSLEEP            | 15  | 電源                | <b>VSLEEP</b> 電源:3.3V<br>0.1μF セラミック デカップリング コンデンサの使用を推奨します。 |

| グランド              | DAP | グランド              | <b>グランド:</b> これは、常に電源グランドに接続する必要があります。                       |

(1) ピンの種類:

I = 入力

O = 出力

IO = 入出力

OD = オープンドレイン

PD = 内部プルダウン

PU = 内部プルアップ

S = ブートストラップ構成ピン (すべての設定ピンには弱い内部プルアップまたはプルダウンが入っています)

(2) ピンを使用しない場合は、上記の表に示す推奨接続要件に従ってください。必要な終端がないピンは、フローティングのままとしてかまいません。

表 5-2. ピン ドメイン

| ピン番号 | ピン名                  | 電圧ドメイン |

|------|----------------------|--------|

| 9    | MDC                  | VDDIO  |

| 10   | INT_N                | VDDIO  |

| 11   | RESET_N              | VDDIO  |

| 12   | XO                   | VDDIO  |

| 13   | XI                   | VDDIO  |

| 14   | LED_1/GPIO_1         | VDDIO  |

| 16   | WAKE                 | VSLEEP |

| 17   | INH                  | VSLEEP |

| 19   | TRD_P                | VDDA   |

| 20   | TRD_M                | VDDA   |

| 21   | RX_ER                | VDDMAC |

| 22   | RX_DV/CRS_DV/RX_CTRL | VDDMAC |

| 24   | RX_D3/RX_M           | VDDMAC |

| 25   | RX_D2/RX_P           | VDDMAC |

| 26   | RX_D1                | VDDMAC |

| 27   | RX_D0                | VDDMAC |

| 28   | RX_CLK               | VDDMAC |

| 1    | TX_CLK               | VDDMAC |

| 2    | TX_EN/TX_CTRL        | VDDMAC |

| 3    | TX_D3                | VDDMAC |

| 4    | TX_D2                | VDDMAC |

| 5    | TX_D1/TX_P           | VDDMAC |

| 6    | TX_D0/TX_M           | VDDMAC |

| 8    | MDIO                 | VDDIO  |

**表 5-3. ピンの状態 - 電源投入 / リセット**

| ピン番号 | ピン名    | 起動 / リセット            |       |             |

|------|--------|----------------------|-------|-------------|

|      |        | ピンの状態 <sup>(1)</sup> | プルタイプ | プル値<br>(kΩ) |

| 9    | MDC    | I                    | なし    | なし          |

| 10   | INT    | I                    | PU    | 9           |

| 11   | RESET  | I                    | PU    | 9           |

| 12   | XO     | O                    | なし    | なし          |

| 13   | XI     | I                    | なし    | なし          |

| 15   | VSLEEP | 電源                   | なし    | なし          |

| 16   | WAKE   | I/O                  | PD    | 455         |

| 17   | INH    | OD、O                 | なし    | なし          |

| 18   | VDDA   | 電源                   | なし    | なし          |

| 19   | TRD_P  | IO                   | なし    | なし          |

| 20   | TRD_M  | IO                   | なし    | なし          |

| 21   | RX_ER  | I                    | PD    | 6           |

| 22   | RX_DV  | I                    | PD    | 6           |

| 23   | VDDMAC | 電源                   | なし    | なし          |

| 24   | RX_D3  | I                    | PD    | 9           |

| 25   | RX_D2  | I                    | PD    | 9           |

| 26   | RX_D1  | I                    | PD    | 9           |

| 27   | RX_D0  | I                    | PD    | 9           |

| 28   | RX_CLK | I                    | PD    | 9           |

| 1    | TX_CLK | I                    | なし    | なし          |

| 2    | TX_EN  | I                    | なし    | なし          |

| 3    | TX_D3  | I                    | なし    | なし          |

| 4    | TX_D2  | I                    | なし    | なし          |

| 5    | TX_D1  | I                    | なし    | なし          |

| 6    | TX_D0  | I                    | なし    | なし          |

| 7    | VDDIO  | 電源                   | なし    | なし          |

| 8    | MDIO   | OD、IO                | なし    | なし          |

表 5-4. ピンの状態 - TC10 スリープ

| ピン番号 | ピン名    | TC10 スリープ (すべての電源がオン) |       |          |

|------|--------|-----------------------|-------|----------|

|      |        | ピンの状態 (1)             | プルタイプ | プル値 (kΩ) |

| 9    | MDC    | I                     | なし    | なし       |

| 10   | INT    | I                     | PU    | 9        |

| 11   | RESET  | I                     | PU    | 9        |

| 12   | XO     | O                     | なし    | なし       |

| 13   | XI     | I                     | なし    | なし       |

| 15   | VSLEEP | 電源                    | なし    | なし       |

| 16   | WAKE   | I/O                   | PD    | 455      |

| 17   | INH    | OD、O                  | なし    | なし       |

| 18   | VDDA   | 電源                    | なし    | なし       |

| 19   | TRD_P  | IO                    | なし    | なし       |

| 20   | TRD_M  | IO                    | なし    | なし       |

| 21   | RX_ER  | I                     | PD    | 6        |

| 22   | RX_DV  | I                     | PD    | 6        |

| 23   | VDDMAC | 電源                    | なし    | なし       |

| 24   | RX_D3  | I                     | PD    | 9        |

| 25   | RX_D2  | I                     | PD    | 9        |

| 26   | RX_D1  | I                     | PD    | 9        |

| 27   | RX_D0  | I                     | PD    | 9        |

| 28   | RX_CLK | I                     | PD    | 9        |

| 1    | TX_CLK | I                     | なし    | なし       |

| 2    | TX_EN  | I                     | なし    | なし       |

| 3    | TX_D3  | I                     | なし    | なし       |

| 4    | TX_D2  | I                     | なし    | なし       |

| 5    | TX_D1  | I                     | なし    | なし       |

| 6    | TX_D0  | I                     | なし    | なし       |

| 7    | VDDIO  | 電源                    | なし    | なし       |

| 8    | MDIO   | OD、IO                 | なし    | なし       |

**表 5-5. ピンの状態 - MAC 分離および IEEE PWDN**

| ピン番号 | ピン名    | MAC 分離    |       |          | IEEE PWDN |       |          |

|------|--------|-----------|-------|----------|-----------|-------|----------|

|      |        | ピンの状態 (1) | プルタイプ | プル値 (kΩ) | ピンの状態 (1) | プルタイプ | プル値 (kΩ) |

| 9    | MDC    | I         | なし    | なし       | I         | なし    | なし       |

| 10   | INT    | OD, O     | PU    | 9        | OD, O     | PU    | 9        |

| 11   | RESET  | I         | PU    | 9        | I         | PU    | 9        |

| 12   | XO     | O         | なし    | なし       | O         | なし    | なし       |

| 13   | XI     | I         | なし    | なし       | I         | なし    | なし       |

| 15   | VSLEEP | 電源        | なし    | なし       | 電源        | なし    | なし       |

| 16   | WAKE   | IO        | PD    | 455      | IO        | PD    | 455      |

| 17   | INH    | OD, O     | なし    | なし       | OD, O     | なし    | なし       |

| 18   | VDDA   | 電源        | なし    | なし       | 電源        | なし    | なし       |

| 19   | TRD_P  | IO        | なし    | なし       | IO        | なし    | なし       |

| 20   | TRD_M  | IO        | なし    | なし       | IO        | なし    | なし       |

| 21   | RX_ER  | I         | PD    | 6        | I         | PD    | 6        |

| 22   | RX_DV  | I         | PD    | 6        | O         | なし    | なし       |

| 23   | VDDMAC | 電源        | なし    | なし       | 電源        | なし    | なし       |

| 24   | RX_D3  | I         | PD    | 9        | O         | なし    | なし       |

| 25   | RX_D2  | I         | PD    | 9        | O         | なし    | なし       |

| 26   | RX_D1  | I         | PD    | 9        | O         | なし    | なし       |

| 27   | RX_D0  | I         | PD    | 9        | O         | なし    | なし       |

| 28   | RX_CLK | I         | PD    | 9        | O         | なし    | なし       |

| 1    | TX_CLK | I         | PD    | 9        | I         | なし    | なし       |

| 2    | TX_EN  | I         | PD    | 9        | I         | なし    | なし       |

| 3    | TX_D3  | I         | PD    | 9        | I         | なし    | なし       |

| 4    | TX_D2  | I         | PD    | 9        | I         | なし    | なし       |

| 5    | TX_D1  | I         | PD    | 9        | I         | なし    | なし       |

| 6    | TX_D0  | I         | PD    | 9        | I         | なし    | なし       |

| 7    | VDDIO  | 電源        | なし    | なし       | 電源        | なし    | なし       |

| 8    | MDIO   | OD, IO    | なし    | なし       | OD, IO    | なし    | なし       |

表 5-6. ピンの状態 - MII および RGMII

| ピン番号 | ピン名    | MII       |       |          | RGMII     |       |          |

|------|--------|-----------|-------|----------|-----------|-------|----------|

|      |        | ピンの状態 (1) | プルタイプ | プル値 (kΩ) | ピンの状態 (1) | プルタイプ | プル値 (kΩ) |

| 9    | MDC    | I         | なし    | なし       | I         | なし    | なし       |

| 10   | INT    | OD, O     | PU    | 9        | OD, O     | PU    | 9        |

| 11   | RESET  | I         | PU    | 9        | I         | PU    | 9        |

| 12   | XO     | O         | なし    | なし       | O         | なし    | なし       |

| 13   | XI     | I         | なし    | なし       | I         | なし    | なし       |

| 15   | VSLEEP | 電源        | なし    | なし       | 電源        | なし    | なし       |

| 16   | WAKE   | IO        | PD    | 455      | IO        | PD    | 455      |

| 17   | INH    | OD, O     | なし    | なし       | OD, O     | なし    | なし       |

| 18   | VDDA   | 電源        | なし    | なし       | 電源        | なし    | なし       |

| 19   | TRD_P  | IO        | なし    | なし       | IO        | なし    | なし       |

| 20   | TRD_M  | IO        | なし    | なし       | IO        | なし    | なし       |

| 21   | RX_ER  | O         | なし    | なし       | I         | PD    | 6        |

| 22   | RX_DV  | O         | なし    | なし       | O         | なし    | なし       |

| 23   | VDDMAC | 電源        | なし    | なし       | 電源        | なし    | なし       |

| 24   | RX_D3  | O         | なし    | なし       | O         | なし    | なし       |

| 25   | RX_D2  | O         | なし    | なし       | O         | なし    | なし       |

| 26   | RX_D1  | O         | なし    | なし       | O         | なし    | なし       |

| 27   | RX_D0  | O         | なし    | なし       | O         | なし    | なし       |

| 28   | RX_CLK | O         | なし    | なし       | O         | なし    | なし       |

| 1    | TX_CLK | O         | なし    | なし       | I         | なし    | なし       |

| 2    | TX_EN  | I         | なし    | なし       | I         | なし    | なし       |

| 3    | TX_D3  | I         | なし    | なし       | I         | なし    | なし       |

| 4    | TX_D2  | I         | なし    | なし       | I         | なし    | なし       |

| 5    | TX_D1  | I         | なし    | なし       | I         | なし    | なし       |

| 6    | TX_D0  | I         | なし    | なし       | I         | なし    | なし       |

| 7    | VDDIO  | 電源        | なし    | なし       | 電源        | なし    | なし       |

| 8    | MDIO   | OD, IO    | なし    | なし       | OD, IO    | なし    | なし       |

**表 5-7. ピンの状態 — RMII リーダーと RMII フォロワー**

| ピン番号 | ピン名    | RMII リーダー |       |          | RMII フォロワー |       |          |

|------|--------|-----------|-------|----------|------------|-------|----------|

|      |        | ピンの状態 (1) | プルタイプ | プル値 (kΩ) | ピンの状態 (1)  | プルタイプ | プル値 (kΩ) |

| 9    | MDC    | I         | なし    | なし       | I          | なし    | なし       |

| 10   | INT    | OD, O     | PU    | 9        | OD, O      | PU    | 9        |

| 11   | RESET  | I         | PU    | 9        | I          | PU    | 9        |

| 12   | XO     | O         | なし    | なし       | O          | なし    | なし       |

| 13   | XI     | I         | なし    | なし       | I          | なし    | なし       |

| 15   | VSLEEP | 電源        | なし    | なし       | 電源         | なし    | なし       |

| 16   | WAKE   | IO        | PD    | 455      | IO         | PD    | 455      |

| 17   | INH    | OD, O     | なし    | なし       | OD, O      | なし    | なし       |

| 18   | VDDA   | 電源        | なし    | なし       | 電源         | なし    | なし       |

| 19   | TRD_P  | IO        | なし    | なし       | IO         | なし    | なし       |

| 20   | TRD_M  | IO        | なし    | なし       | IO         | なし    | なし       |

| 21   | RX_ER  | O         | なし    | なし       | O          | なし    | なし       |

| 22   | RX_DV  | O         | なし    | なし       | O          | なし    | なし       |

| 23   | VDDMAC | 電源        | なし    | なし       | 電源         | なし    | なし       |

| 24   | RX_D3  | O, 50MHz  | なし    | なし       | I          | PD    | 9        |

| 25   | RX_D2  | I         | PD    | 9        | I          | PD    | 9        |

| 26   | RX_D1  | O         | なし    | なし       | O          | なし    | なし       |

| 27   | RX_D0  | O         | なし    | なし       | O          | なし    | なし       |

| 28   | RX_CLK | I         | PD    | 9        | I          | PD    | 9        |

| 1    | TX_CLK | I         | なし    | なし       | I          | なし    | なし       |

| 2    | TX_EN  | I         | なし    | なし       | I          | なし    | なし       |

| 3    | TX_D3  | I         | なし    | なし       | I          | なし    | なし       |

| 4    | TX_D2  | I         | なし    | なし       | I          | なし    | なし       |

| 5    | TX_D1  | I         | なし    | なし       | I          | なし    | なし       |

| 6    | TX_D0  | I         | なし    | なし       | I          | なし    | なし       |

| 7    | VDDIO  | 電源        | なし    | なし       | 電源         | なし    | なし       |

| 8    | MDIO   | OD, IO    | なし    | なし       | OD, IO     | なし    | なし       |

表 5-8. ピンの状態 - SGMII

| ピン番号 | ピン名    | SGMII     |       |          |

|------|--------|-----------|-------|----------|

|      |        | ピンの状態 (1) | プルタイプ | プル値 (kΩ) |

| 9    | MDC    | I         | なし    | なし       |

| 10   | INT    | OD, O     | PU    | 9        |

| 11   | RESET  | I         | PU    | 9        |

| 12   | XO     | O         | なし    | なし       |

| 13   | XI     | I         | なし    | なし       |

| 15   | VSLEEP | 電源        | なし    | なし       |

| 16   | WAKE   | IO        | PD    | 455      |

| 17   | INH    | OD, O     | なし    | なし       |

| 18   | VDDA   | 電源        | なし    | なし       |

| 19   | TRD_P  | IO        | なし    | なし       |

| 20   | TRD_M  | IO        | なし    | なし       |

| 21   | RX_ER  | I         | PD    | 6        |

| 22   | RX_DV  | I         | PD    | 6        |

| 23   | VDDMAC | 電源        | なし    | なし       |

| 24   | RX_D3  | O         | なし    | なし       |

| 25   | RX_D2  | O         | なし    | なし       |

| 26   | RX_D1  | I         | PD    | 9        |

| 27   | RX_D0  | I         | PD    | 9        |

| 28   | RX_CLK | I         | PD    | 9        |

| 1    | TX_CLK | I         | なし    | なし       |

| 2    | TX_EN  | I         | なし    | なし       |

| 3    | TX_D3  | I         | なし    | なし       |

| 4    | TX_D2  | I         | なし    | なし       |

| 5    | TX_D1  | I         | なし    | なし       |

| 6    | TX_D0  | I         | なし    | なし       |

| 7    | VDDIO  | 電源        | なし    | なし       |

| 8    | MDIO   | OD, IO    | なし    | なし       |

- (1) 種類:I = 入力

O = 出力

IO = 入出力

OD = オープンドレイン

PD = 内部プルダウン

PU = 内部プルアップ

## 6 仕様

### 6.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                  |                                      | 最小値  | 標準値          | 最大値 | 単位 |

|------------------|--------------------------------------|------|--------------|-----|----|

| 入力電圧             | VDDA                                 | -0.3 |              | 4   | V  |

| 入力電圧             | VDDIO/VDDMAC (3.3V)                  | -0.3 |              | 4   | V  |

| 入力電圧             | VDDIO/VDDMAC (2.5V)                  | -0.3 |              | 4   | V  |

| 入力電圧             | VDDIO/VDDMAC (1.8V)                  | -0.3 |              | 4   | V  |

| 入力電圧             | VSLEEP                               | -0.3 |              | 4   | V  |

| ピン               | MDI                                  | -0.3 |              | 4   | V  |

| ピン               | MAC インターフェイス                         | -0.3 | VDDMAC + 0.3 |     | V  |

| ピン               | MDIO、MDC、GPIO、XI、XO、INT、RESET、CLKOUT | -0.3 | VDDIO + 0.3  |     | V  |

| ピン               | WAKE、INH                             | -0.3 | VSLEEP + 0.3 |     | V  |

| DC の出力電圧         | すべてのピン                               | -0.3 |              | 4   | V  |

| T <sub>J</sub>   | 接合部温度                                |      |              | 150 | °C |

| T <sub>stg</sub> | 保存温度                                 | -65  |              | 150 | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

### 6.2 ESD 定格

|                    |      |                                             |                | 値     | 単位 |

|--------------------|------|---------------------------------------------|----------------|-------|----|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、AEC Q100-002 に準拠 <sup>(1)</sup> | すべてのピン         | ±2000 | V  |

|                    |      |                                             | TRD_N、TRD_P ピン | ±8000 |    |

|                    |      | 荷電デバイスモデル (CDM)、AEC Q100-011 準拠             | 角のピン           | ±750  |    |

|                    |      |                                             | その他のピン         | ±750  |    |

|                    |      | IEC 61000-4-2 接触放電                          | TRD_N、TRD_P ピン | ±8000 |    |

- (1) AEC Q100-002 は、HBM ストレス試験を ANSI / ESDA / JEDEC JS-001 仕様に従って実施しなければならないと規定しています。

### 6.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                  |                 | 最小値  | 公称値 | 最大値  | 単位 |

|------------------|-----------------|------|-----|------|----|

| VDDIO/<br>VDDMAC | IO 電源電圧、1.8V 動作 | 1.62 | 1.8 | 1.98 | V  |

|                  | IO 電源電圧、2.5V 動作 | 2.25 | 2.5 | 2.75 |    |

|                  | IO 電源電圧、3.3V 動作 | 2.97 | 3.3 | 3.63 |    |

| VDDA             | コア電源電圧、3.3V     | 2.97 | 3.3 | 3.63 | V  |

| VSLEEP           | スリープ電源電圧、3.3V   | 2.97 | 3.3 | 3.63 | V  |

| T <sub>A</sub>   | 周囲温度            | -40  |     | 125  | °C |

## 6.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup>        |                   | DP83TC813  | 単位   |

|-----------------------------|-------------------|------------|------|

|                             |                   | RHF (VQFN) |      |

|                             |                   | 28 ピン      |      |

| $R_{\theta JA}$             | 接合部から周囲への熱抵抗      | 39.0       | °C/W |

| $R_{\theta JC(\text{top})}$ | 接合部からケース(上面)への熱抵抗 | 29.6       | °C/W |

| $R_{\theta JB}$             | 接合部から基板への熱抵抗      | 17.4       | °C/W |

| $\Psi_{JT}$                 | 接合部から上面への特性パラメータ  | 0.7        | °C/W |

| $\Psi_{JB}$                 | 接合部から基板への特性パラメータ  | 17.4       | °C/W |

| $R_{\theta JC(\text{bot})}$ | 接合部からケース(底面)への熱抵抗 | 5.8        | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション ノートを参照してください。

## 6.5 電気的特性

自由気流での動作温度範囲内(特に記述のない限り)

| パラメータ                        | テスト条件                                   | 最小値                                 | 標準値 | 最大値                 | 単位                  |

|------------------------------|-----------------------------------------|-------------------------------------|-----|---------------------|---------------------|

| <b>100BASE-T1 PMA 準拠</b>     |                                         |                                     |     |                     |                     |

| $V_{OD-MDI}$                 | 出力差動電圧 $R_{L(\text{diff})} = 100\Omega$ |                                     | 2.2 |                     | V                   |

| $R_{MDI-Diff}$               | 内蔵差動出力終端 TRD_P と TRD_M                  |                                     | 100 |                     | Ω                   |

| <b>ポートストラップ DC 特性(2 レベル)</b> |                                         |                                     |     |                     |                     |

| $V_{MODE1}$                  | モード 1 ストラップ電圧範囲                         | $VDDIO = 3.3V \pm 10\%$ 、2 レベルストラップ | 0   | 0.8                 | V                   |

| $V_{MODE2}$                  | モード 2 ストラップ電圧範囲                         | $VDDIO = 3.3V \pm 10\%$ 、2 レベルストラップ | 2   | $VDDIO$             | V                   |

| $V_{MODE1}$                  | モード 1 ストラップ電圧範囲                         | $VDDIO = 2.5V \pm 10\%$ 、2 レベルストラップ | 0   | 0.7                 | V                   |

| $V_{MODE2}$                  | モード 2 ストラップ電圧範囲                         | $VDDIO = 2.5V \pm 10\%$ 、2 レベルストラップ | 1.5 | $VDDIO$             | V                   |

| $V_{MODE1}$                  | モード 1 ストラップ電圧範囲                         | $VDDIO = 1.8V \pm 10\%$ 、2 レベルストラップ | 0   | $0.35 \times VDDIO$ | V                   |

| $V_{MODE2}$                  | モード 2 ストラップ電圧範囲                         | $VDDIO = 1.8V \pm 10\%$ 、2 レベルストラップ |     | $0.65 \times VDDIO$ | $VDDIO$             |

| <b>ポートストラップ DC 特性(3 レベル)</b> |                                         |                                     |     |                     |                     |

| $V_{MODE1}$                  | モード 1 ストラップ電圧範囲                         | $VDDIO = 3.3V \pm 10\%$ 、3 レベルストラップ | 0   | $0.18 \times VDDIO$ | V                   |

| $V_{MODE2}$                  | モード 2 ストラップ電圧範囲                         | $VDDIO = 3.3V \pm 10\%$ 、3 レベルストラップ |     | $0.22 \times VDDIO$ | $0.42 \times VDDIO$ |

| $V_{MODE3}$                  | モード 3 ストラップ電圧範囲                         | $VDDIO = 3.3V \pm 10\%$ 、3 レベルストラップ |     | $0.46 \times VDDIO$ | $VDDIO$             |

| $V_{MODE1}$                  | モード 1 ストラップ電圧範囲                         | $VDDIO = 2.5V \pm 10\%$ 、3 レベルストラップ | 0   | $0.19 \times VDDIO$ | V                   |

| $V_{MODE2}$                  | モード 2 ストラップ電圧範囲                         | $VDDIO = 2.5V \pm 10\%$ 、3 レベルストラップ |     | $0.27 \times VDDIO$ | $0.41 \times VDDIO$ |

| $V_{MODE3}$                  | モード 3 ストラップ電圧範囲                         | $VDDIO = 2.5V \pm 10\%$ 、3 レベルストラップ |     | $0.58 \times VDDIO$ | $VDDIO$             |

| $V_{MODE1}$                  | モード 1 ストラップ電圧範囲                         | $VDDIO = 1.8V \pm 10\%$ 、3 レベルストラップ | 0   | $0.35 \times VDDIO$ | V                   |

| $V_{MODE2}$                  | モード 2 ストラップ電圧範囲                         | $VDDIO = 1.8V \pm 10\%$ 、3 レベルストラップ |     | $0.40 \times VDDIO$ | $0.75 \times VDDIO$ |

## 6.5 電気的特性 (続き)

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ               |                             | テスト条件                                                                | 最小値          | 標準値          | 最大値  | 単位 |

|---------------------|-----------------------------|----------------------------------------------------------------------|--------------|--------------|------|----|

| V <sub>MODE3</sub>  | モード3 ストラップ電圧範囲              | VDDIO = 1.8V±10%、3 レベルストラップ                                          | 0.84 × VDDIO | VDDIO        | V    | V  |

| <b>IO 特性</b>        |                             |                                                                      |              |              |      |    |

| V <sub>IH</sub>     | High レベル入力電圧                | VDDIO = 3.3V ±10%                                                    | 2            |              |      | V  |

| V <sub>IL</sub>     | Low レベル入力電圧                 | VDDIO = 3.3V ±10%                                                    |              | 0.8          |      | V  |

| V <sub>OH</sub>     | High レベル出力電圧                | I <sub>OH</sub> = -2mA、VDDIO = 3.3V ±10%                             | 2.4          |              |      | V  |

| V <sub>OL</sub>     | Low レベル出力電圧                 | I <sub>OL</sub> = 2mA、VDDIO = 3.3V ±10%                              |              | 0.4          |      | V  |

| V <sub>IH</sub>     | High レベル入力電圧                | VDDIO = 2.5V ±10%                                                    | 1.7          |              |      | V  |

| V <sub>IL</sub>     | Low レベル入力電圧                 | VDDIO = 2.5V ±10%                                                    |              | 0.7          |      | V  |

| V <sub>OH</sub>     | High レベル出力電圧                | I <sub>OH</sub> = -2mA、VDDIO = 2.5V ±10%                             | 2            |              |      | V  |

| V <sub>OL</sub>     | Low レベル出力電圧                 | I <sub>OL</sub> = 2mA、VDDIO = 2.5V ±10%                              |              | 0.4          |      | V  |

| V <sub>IH</sub>     | High レベル入力電圧                | VDDIO = 1.8V ±10%                                                    | 0.65 × VDDIO |              |      | V  |

| V <sub>IL</sub>     | Low レベル入力電圧                 | VDDIO = 1.8V ±10%                                                    |              | 0.35 × VDDIO |      | V  |

| V <sub>OH</sub>     | High レベル出力電圧                | I <sub>OH</sub> = -2mA、VDDIO = 1.8V ±10%                             | VDDIO-0.45   |              |      | V  |

| V <sub>OL</sub>     | Low レベル出力電圧                 | I <sub>OL</sub> = 2mA、VDDIO = 1.8V ±10%                              |              | 0.45         |      | V  |

| I <sub>IH</sub>     | 入力 High 電流 <sup>(1)</sup>   | T <sub>A</sub> = -40°C ~ 125°C、VIN=VDDIO、XI と WAKE を除くすべてのピン         | -10          | 10           |      | μA |

| I <sub>IH-XI</sub>  | 入力 High 電流 <sup>(1)</sup>   | T <sub>A</sub> = -40°C ~ 125°C、VIN=VDDIO、XI ピン                       | -15          | 15           |      | μA |

| I <sub>IL-XI</sub>  | 入力 Low 電流 <sup>(1)</sup>    | T <sub>A</sub> = -40°C ~ 125°C、VIN=GND、XI ピン                         | -15          | 15           |      | μA |

| I <sub>IL</sub>     | 入力 Low 電流 <sup>(1)</sup>    | T <sub>A</sub> = -40°C ~ 125°C、VIN=GND、XI ピンを除くすべてのピン                | -10          | 10           |      | μA |

| I <sub>lozh</sub>   | トライステート出力高電流                | T <sub>A</sub> = -40°C ~ 125°C、VIN=VDDIO、RX_CTRL および RX_ER を除くすべてのピン | -10          | 10           |      | μA |

| I <sub>lozh</sub>   | トライステート出力高電流                | T <sub>A</sub> = -40°C ~ 125°C、VIN=VDDIO、RX_CTRL および RX_ER           | -52          | 52           |      | μA |

| I <sub>lozl</sub>   | トライステート出力低電流 <sup>(2)</sup> | T <sub>A</sub> = -40°C ~ 125°C、VOUT=GND                              | -10          | 10           |      | μA |

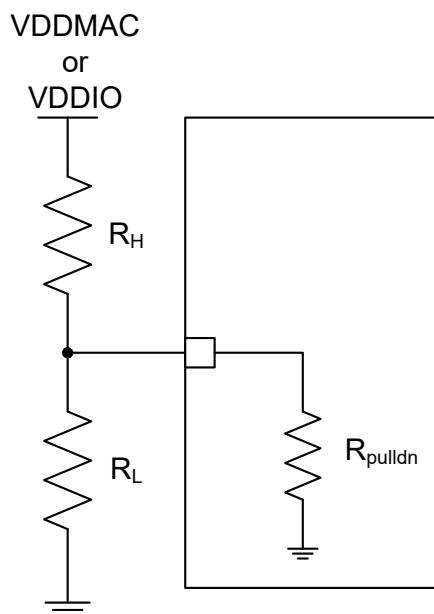

| R <sub>pulldn</sub> | 内蔵プルダウン抵抗                   | RX_D[3:0]、RX_CLK、LED_1                                               | 6.2          | 8.4          | 10.7 | kΩ |

| R <sub>pulldn</sub> | 内蔵プルダウン抵抗                   | RX_CTRL、RX_ER                                                        | 4.725        | 5.8          | 7.2  | kΩ |

| R <sub>pulldn</sub> | 内蔵プルダウン抵抗                   | WAKE                                                                 |              | 455          |      | kΩ |

| R <sub>pullup</sub> | 内蔵プルアップ抵抗                   | INT、RESET                                                            | 6.3          | 9            | 11.2 | kΩ |

| XI V <sub>IH</sub>  | High レベル入力電圧                |                                                                      | 1.3          | VDDIO        |      | V  |

| XI V <sub>IL</sub>  | Low レベル入力電圧                 |                                                                      |              | 0.5          |      | V  |

| C <sub>IN</sub>     | XI の入力容量                    |                                                                      | 1            |              |      | pF |

| C <sub>IN</sub>     | 入力ピンの入力容量                   |                                                                      | 5            |              |      | pF |

| C <sub>OUT</sub>    | XO の出力容量                    |                                                                      | 1            |              |      | pF |

| C <sub>OUT</sub>    | 出力ピンの出力容量                   |                                                                      | 5            |              |      | pF |

| R <sub>series</sub> | 内蔵 MAC 直列終端抵抗               | RX_D[3:0]、RX_ER、RX_DV、RX_CLK                                         | 35           | 50           | 65   | Ω  |

| <b>消費電力</b>         |                             |                                                                      |              |              |      |    |

| I(3V3)              | MII                         | -40°C ~ 125°C                                                        | 57           | 63           |      | mA |

| I(3V3)              | RMII                        | -40°C ~ 125°C                                                        | 57           | 63           |      | mA |

## 6.5 電気的特性 (続き)

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ           |             | テスト条件                                    | 最小値 | 標準値 | 最大値 | 単位 |

|-----------------|-------------|------------------------------------------|-----|-----|-----|----|

| I(3V3)          | RGMII       | -40°C ~ 125°C                            |     | 57  | 63  | mA |

| I(3V3)          | SGMII       | -40°C ~ 125°C                            |     | 81  | 95  | mA |

| I(VDDIO=3.3V)   | MII         | -40°C ~ 125°C、VDDIO = VDDMAC             |     | 19  | 24  | mA |

| I(VDDIO=3.3V)   | RMII        | -40°C ~ 125°C、VDDIO = VDDMAC             |     | 18  | 23  | mA |

| I(VDDIO=3.3V)   | RGMII       | -40°C ~ 125°C、VDDIO = VDDMAC             |     | 13  | 21  | mA |

| I(VDDIO=3.3V)   | SGMII       | -40°C ~ 125°C、VDDIO = VDDMAC             |     | 7   | 12  | mA |

| I(VDDIO=2.5V)   | MII         | -40°C ~ 125°C、VDDIO = VDDMAC             |     | 12  | 18  | mA |

| I(VDDIO=2.5V)   | RMII        | -40°C ~ 125°C、VDDIO = VDDMAC             |     | 12  | 17  | mA |

| I(VDDIO=2.5V)   | RGMII       | -40°C ~ 125°C、VDDIO = VDDMAC             |     | 12  | 16  | mA |

| I(VDDIO=2.5V)   | SGMII       | -40°C ~ 125°C、VDDIO = VDDMAC             |     | 6   | 9   | mA |

| I(VDDIO=1.8V)   | MII         | -40°C ~ 125°C、VDDIO = VDDMAC             |     | 9   | 13  | mA |

| I(VDDIO=1.8V)   | RMII        | -40°C ~ 125°C、VDDIO = VDDMAC             |     | 9   | 13  | mA |

| I(VDDIO=1.8V)   | RGMII       | -40°C ~ 125°C、VDDIO = VDDMAC             |     | 9   | 12  | mA |

| I(VDDIO=1.8V)   | SGMII       | -40°C ~ 125°C、VDDIO = VDDMAC             |     | 4   | 6   | mA |

| 消費電力 (低消費電力モード) |             |                                          |     |     |     |    |

| I(VDDA3V3)      | IEEE パワーダウン | -40°C ~ 125°C、全インターフェース                  |     | 8   | 22  | mA |

| I(VDDA3V3)      | TC-10 スリープ  | -40°C ~ 125°C、全インターフェース                  |     | 30  | 50  | mA |

| I(VDDA3V3)      | リセット        | -40°C ~ 125°C、全インターフェース                  |     | 9   | 23  | mA |

| I(VDDA3V3)      | スタンバイ       | -40°C ~ 125°C、MII                        |     | 15  | 33  | mA |

| I(VDDA3V3)      | スタンバイ       | -40°C ~ 125°C、RMII                       |     | 15  | 30  | mA |

| I(VDDA3V3)      | スタンバイ       | -40°C ~ 125°C、RGMII                      |     | 15  | 30  | mA |

| I(VDDA3V3)      | スタンバイ       | -40°C ~ 125°C、SGMII                      |     | 15  | 30  | mA |

| I(VDDIO=3.3V)   | IEEE パワーダウン | -40°C ~ 125°C、全インターフェース、<br>VDDIO=VDDMAC |     | 15  | 23  | mA |

| I(VDDIO=3.3V)   | TC-10 スリープ  | -40°C ~ 125°C、全インターフェース、<br>VDDIO=VDDMAC |     | 15  | 23  | mA |

| I(VDDIO=3.3V)   | リセット        | -40°C ~ 125°C、全インターフェース、<br>VDDIO=VDDMAC |     | 15  | 23  | mA |

| I(VDDIO=3.3V)   | スタンバイ       | -40°C ~ 125°C、MII、VDDIO=VDDMAC           |     | 19  | 25  | mA |

| I(VDDIO=3.3V)   | スタンバイ       | -40°C ~ 125°C、RMII、VDDIO=VDDMAC          |     | 16  | 20  | mA |

| I(VDDIO=3.3V)   | スタンバイ       | -40°C ~ 125°C、RGMII、VDDIO=VDDMAC         |     | 14  | 20  | mA |

| I(VDDIO=3.3V)   | スタンバイ       | -40°C ~ 125°C、SGMII、VDDIO=VDDMAC         |     | 14  | 16  | mA |

| I(VDDIO=2.5V)   | IEEE パワーダウン | -40°C ~ 125°C、全インターフェース、<br>VDDIO=VDDMAC |     | 10  | 16  | mA |

| I(VDDIO=2.5V)   | TC-10 スリープ  | -40°C ~ 125°C、全インターフェース、<br>VDDIO=VDDMAC |     | 10  | 16  | mA |

| I(VDDIO=2.5V)   | リセット        | -40°C ~ 125°C、全インターフェース、<br>VDDIO=VDDMAC |     | 10  | 16  | mA |

| I(VDDIO=2.5V)   | スタンバイ       | -40°C ~ 125°C、MII、VDDIO=VDDMAC           |     | 14  | 18  | mA |

| I(VDDIO=2.5V)   | スタンバイ       | -40°C ~ 125°C、RMII、VDDIO=VDDMAC          |     | 11  | 14  | mA |

| I(VDDIO=2.5V)   | スタンバイ       | -40°C ~ 125°C、RGMII、VDDIO=VDDMAC         |     | 9   | 14  | mA |

| I(VDDIO=2.5V)   | スタンバイ       | -40°C ~ 125°C、SGMII、VDDIO=VDDMAC         |     | 9   | 14  | mA |

## 6.5 電気的特性 (続き)

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                |                                          | テスト条件                                    | 最小値  | 標準値 | 最大値 | 単位 |

|----------------------|------------------------------------------|------------------------------------------|------|-----|-----|----|

| I(VDDIO=1.8V)        | IEEE パワーダウン                              | -40°C ~ 125°C、全インターフェース、<br>VDDIO=VDDMAC |      | 7   | 11  | mA |

| I(VDDIO=1.8V)        | TC-10 スリープ                               | -40°C ~ 125°C、全インターフェース、<br>VDDIO=VDDMAC |      | 7   | 11  | mA |

| I(VDDIO=1.8V)        | リセット                                     | -40°C ~ 125°C、全インターフェース、<br>VDDIO=VDDMAC |      | 7   | 11  | mA |

| I(VDDIO=1.8V)        | スタンバイ                                    | -40°C ~ 125°C、MII、VDDIO=VDDMAC           |      | 10  | 12  | mA |

| I(VDDIO=1.8V)        | スタンバイ                                    | -40°C ~ 125°C、RMII、VDDIO=VDDMAC          |      | 7   | 11  | mA |

| I(VDDIO=1.8V)        | スタンバイ                                    | -40°C ~ 125°C、RGMII、VDDIO=VDDMAC         |      | 6   | 11  | mA |

| I(VDDIO=1.8V)        | スタンバイ                                    | -40°C ~ 125°C、SGMII、VDDIO=VDDMAC         |      | 6   | 11  | mA |

| I(VSLEEP)            | TC-10 スリープ                               | -40°C ~ 125°C、全インターフェイス、他のすべて<br>の電源オフ   |      | 7   | 18  | μA |

| <b>SGMII 入力</b>      |                                          |                                          |      |     |     |    |

| V <sub>IDTH</sub>    | 入力差動電圧スレッショルド                            | SI_P および SI_N、AC 結合                      | 0.1  |     |     | V  |

| R <sub>IN-DIFF</sub> | 受信差動入力インピーダンス (DC)                       |                                          | 80   | 120 |     | Ω  |

| <b>SGMII 出力</b>      |                                          |                                          |      |     |     |    |

|                      | クロック信号デューティサイクル                          | SO_P および SO_N、AC 結合、0101010101 パターン      | 48   | 52  |     | %  |

|                      | 出力差動電圧                                   | SO_P および SO_N、AC 結合                      | 150  | 400 |     | mV |

| <b>電圧センサ</b>         |                                          |                                          |      |     |     |    |

| VDDA                 | VDDA センサの範囲                              | -40°C ~ +125°C                           | 2.7  | 3.3 | 4   | V  |

|                      | VDDA センサの分解能 (LSB)                       | -40°C ~ +125°C                           |      | 8.8 |     | mV |

|                      | VDDA センサの精度 (1 つの部品での電圧と温度による変動)         | -40°C ~ +125°C                           | -120 | 120 |     | mV |

|                      | VDDA センサの精度 (部品間のばらつき)                   | -40°C ~ +125°C                           | -50  | 50  |     | mV |

| VDDIO/VDDMAC         | VDDIO/VDDMAC センサの範囲                      | -40°C ~ +125°C                           | 1.44 | 3.9 |     | V  |

|                      | VDDIO/VDDMAC センサの分解能 (LSB)               | -40°C ~ +125°C                           |      | 16  |     | mV |

|                      | VDDIO/VDDMAC センサの精度 (1 つの部品での電圧と温度による変動) | -40°C ~ +125°C                           | -144 | 144 |     | mV |

|                      | VDDIO/VDDMAC センサの精度 (部品間のばらつき)           | -40°C ~ +125°C                           | -85  | 85  |     | mV |

## 6.5 電気的特性 (続き)

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ  | テスト条件                              | 最小値            | 標準値  | 最大値 | 単位  |

|--------|------------------------------------|----------------|------|-----|-----|

| VSLEEP | VSLEEP センサの範囲                      | -40°C ~ +125°C | 2.7  | 3.3 | 4 V |

|        | VSLEEP センサの分解能 (LSB)               | -40°C ~ +125°C |      | 8.8 | mV  |

|        | VSLEEP センサの精度 (1 つの部品での電圧と温度による変動) | -40°C ~ +125°C | -120 | 120 | mV  |

|        | VSLEEP センサの精度 (部品間のばらつき)           | -40°C ~ +125°C | -50  | 50  | mV  |

- (1) 対象ピン: MDC、TX\_CLK、TX\_CTRL、TX\_D[3:0]、RESET\_N

- (2) 対象ピン: RX\_D[3:0]、RX\_CLK、RX\_CTRL、MDIO、INT\_N、XO。

## 6.6 タイミング要件

| パラメータ                     |                                                      | テスト条件                   | 最小値  | 公称値 | 最大値 | 単位  |

|---------------------------|------------------------------------------------------|-------------------------|------|-----|-----|-----|

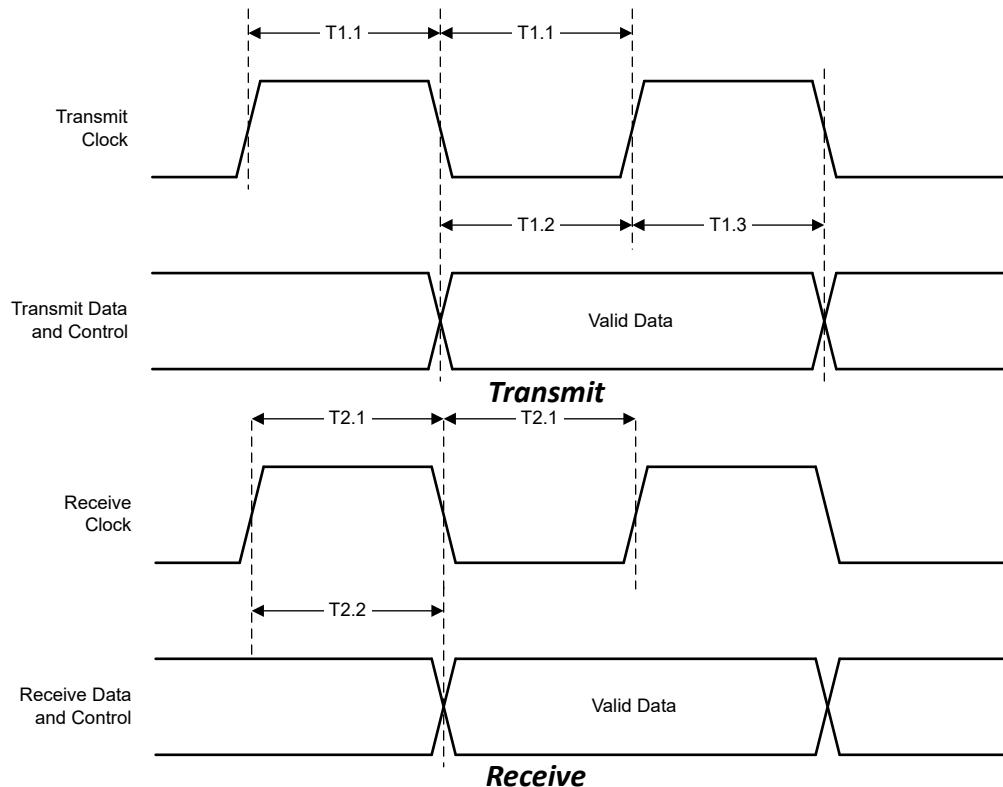

| <b>MII タイミング</b>          |                                                      |                         |      |     |     |     |

| T1.1                      | TX_CLK High / Low 時間                                 |                         | 16   | 20  | 24  | ns  |

| T1.2                      | TX_CLK までの TX_D[3:0]、TX_ER、TX_EN のセットアップ             |                         | 10   |     |     | ns  |

| T1.3                      | TX_CLK からの TX_D[3:0]、TX_ER、TX_EN のホールド               |                         | 0    |     |     | ns  |

| T2.1                      | RX_CLK High / Low 時間                                 |                         | 16   | 20  | 24  | ns  |

| T2.2                      | RX_CLK 立ち上がりからの RX_D[3:0]、RX_ER、RX_DV の遅延            |                         | 10   |     | 30  | ns  |

| <b>RMII リーダー タイミング</b>    |                                                      |                         |      |     |     |     |

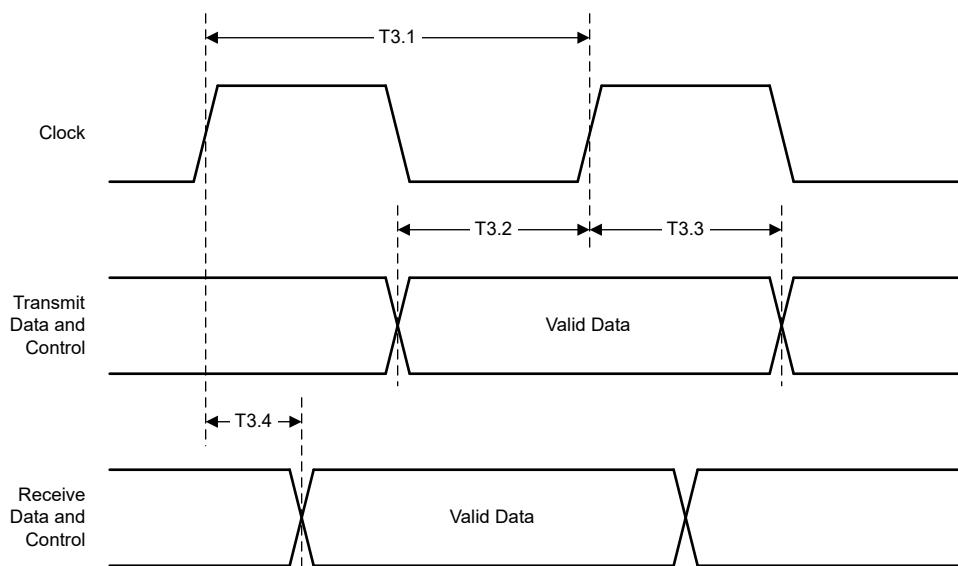

| T3.1                      | RMII リーダー クロック周期                                     |                         | 20   |     |     | ns  |

|                           | RMII リーダー クロック デューティサイクル                             |                         | 35   | 65  | %   |     |

| T3.2                      | TX_D[1:0]、TX_ER、TX_EN の RMII リーダー クロックに対するセットアップ     |                         | 4    |     |     | ns  |

| T3.3                      | TX_D[1:0]、TX_ER、TX_EN の RMII リーダー クロックからのホールド        |                         | 2    |     |     | ns  |

| T3.4                      | RX_D[1:0]、RX_ER、CRS_DV の RMII リーダー クロック立ち上がりエッジからの遅延 |                         | 4    | 10  | 14  | ns  |

| <b>RMII フォロワ タイミング</b>    |                                                      |                         |      |     |     |     |

| T3.1                      | 入力基準クロック周期                                           |                         | 20   |     |     | ns  |

|                           | 入力クロック デューティサイクル                                     |                         | 35   | 65  | %   |     |

| T3.2                      | XI クロックの立ち上がりまでの TX_D[1:0]、TX_ER、TX_EN のセットアップ       |                         | 4    |     |     | ns  |

| T3.3                      | XI クロックの立ち上がりからの TX_D[1:0]、TX_ER、TX_EN のホールド         |                         | 2    |     |     | ns  |

| T3.4                      | XI クロックの立ち上がりからの RX_D[1:0]、RX_ER、CRS_DV の遅延          |                         | 4    | 14  |     | ns  |

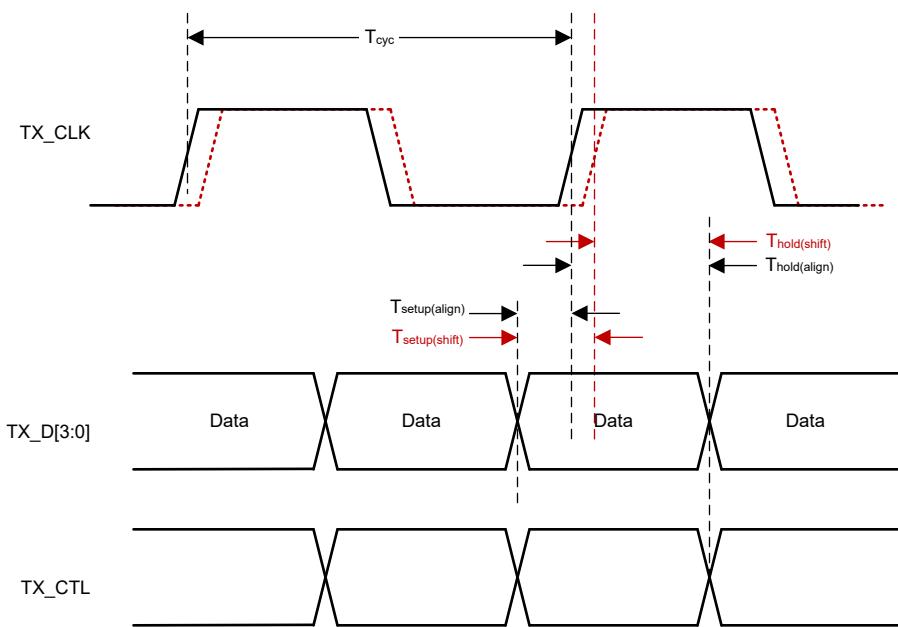

| <b>RGMII 入力タイミング</b>      |                                                      |                         |      |     |     |     |

| T <sub>cyc</sub>          | クロック周期                                               | TX_CLK                  | 36   | 40  | 44  | ns  |

| T <sub>setup(align)</sub> | TX_D[3:0]、TX_CLK までの TX_CTRL のセットアップ時間 (整列モード)       |                         | 1    | 2   |     | ns  |

| T <sub>hold(align)</sub>  | TX_D[3:0]、TX_CLK からの TX_CTRL のホールド時間 (整列モード)         |                         | 1    | 2   |     | ns  |

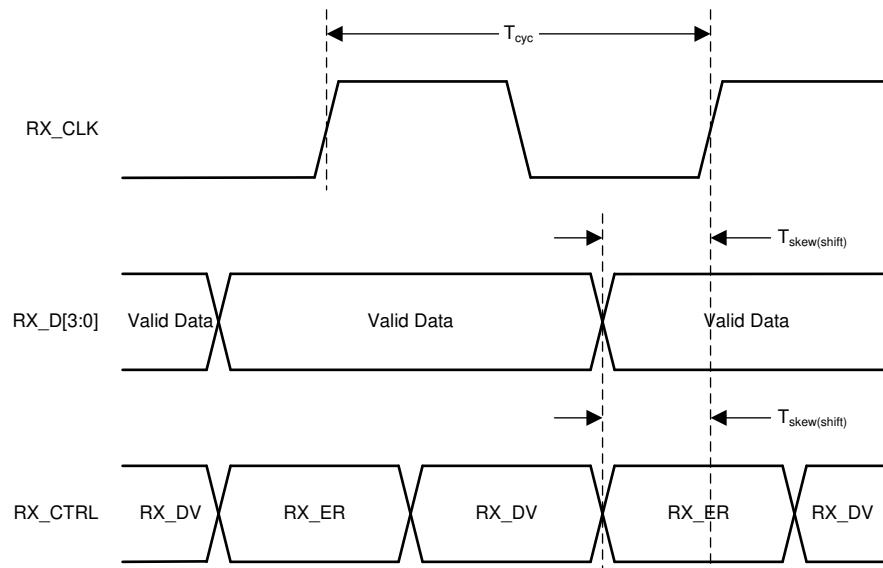

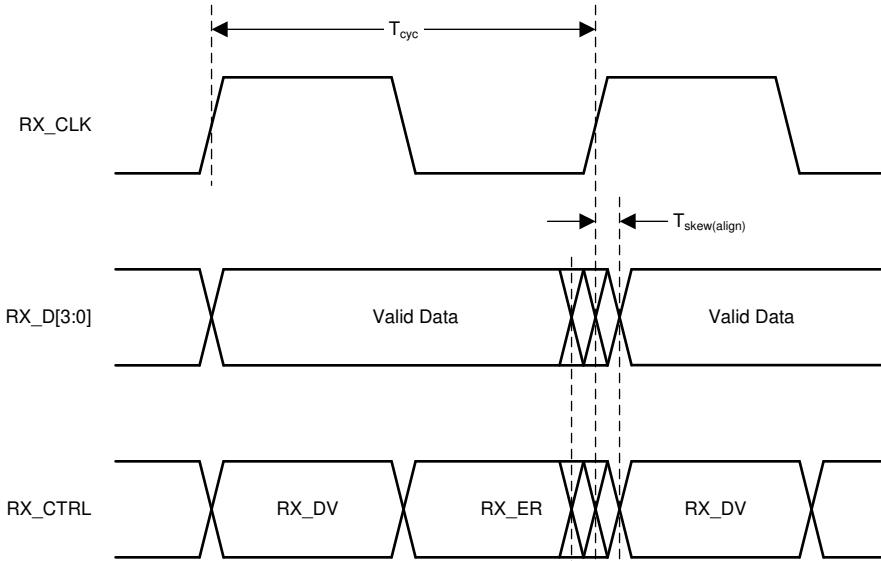

| <b>RGMII 出力タイミング</b>      |                                                      |                         |      |     |     |     |

| T <sub>skew(align)</sub>  | RX_D[3:0]、RX_CLK からの RX_CTRL の遅延時間 (整列モード有効)         | PHY ピン上                 | -750 | 750 |     | ps  |

| T <sub>setup(shift)</sub> | RX_D[3:0]、RX_CLK からの RX_CTRL の遅延時間 (シフトモード有効デフォルト)   | PHY ピン上                 | 2    |     |     | ns  |

| T <sub>cyc</sub>          | クロック周期                                               | RX_CLK                  | 36   | 40  | 44  | ns  |

| Duty_G                    | デューティサイクル                                            | RX_CLK                  | 45   | 50  | 55  | %   |

| Tr/Tf                     | 立ち上がり / 立ち下がり時間 (20% ~ 80%)                          | C <sub>LOAD</sub> = 5pF |      | 1.2 |     | ns  |

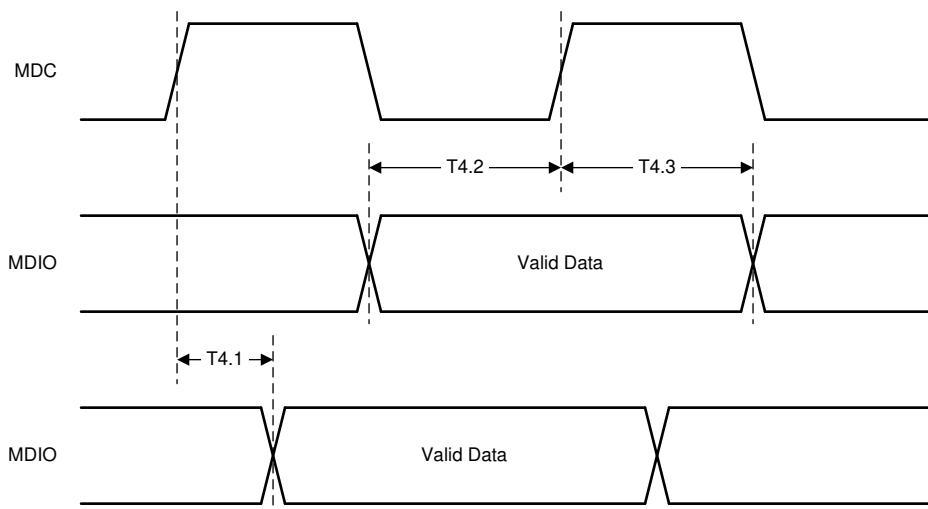

| <b>SMI タイミング</b>          |                                                      |                         |      |     |     |     |

| T4.1                      | MDC から MDIO (出力) までの遅延時間                             | 25pF の負荷容量              | 0    | 40  |     | ns  |

| T4.2                      | MDC に対する MDIO (入力) のセットアップ時間                         |                         | 10   |     |     | ns  |

| T4.3                      | MDC に対する MDIO (入力) のホールド時間                           |                         | 10   |     |     | ns  |

|                           | MDC 周波数                                              |                         |      | 2.5 | 20  | MHz |

| <b>電源投入のタイミング</b>         |                                                      |                         |      |     |     |     |

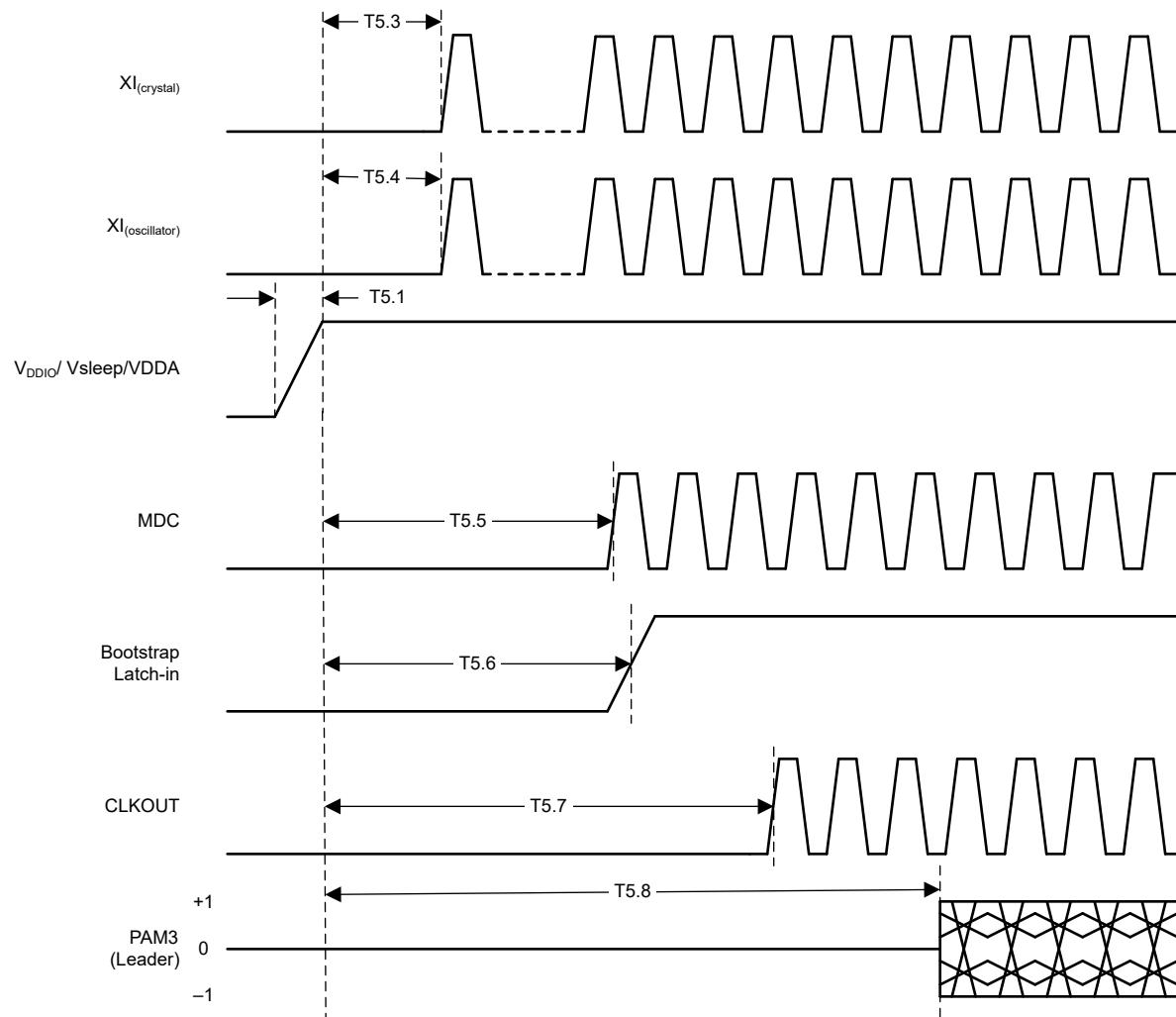

| T5.1                      | 電源ランプ時間: VSLEEP を除くすべての電源について <sup>(1)</sup>         |                         | 0.2  | 8   |     | ms  |

## 6.6 タイミング要件 (続き)

| パラメータ                        |                                                                       | テスト条件 | 最小値  | 公称値  | 最大値 | 単位 |

|------------------------------|-----------------------------------------------------------------------|-------|------|------|-----|----|

| T5.1                         | 電源ランプ時間: VSLEEP について <sup>(1)</sup>                                   |       | 0.4  | 8    | ms  |    |

| T5.3                         | XTAL の起動 / セトリング: 電源投入から XI 正常 / 安定化まで                                |       |      | 0.35 | ms  |    |

| T5.4                         | 電源投入からの発振器の安定化時間                                                      |       |      | 10   | ms  |    |

|                              | 最後の電源立ち上がりからリセット解除まで                                                  |       |      | 10   | ms  |    |

| T5.5                         | 電源投入後、SMI 準備完了まで: 電源投入後、レジスタ アクセスのために MDC プリアンブルを送信できるようになるまでに必要な待ち時間 |       |      | 10   | ms  |    |

| T5.6                         | 電源オンからストラップ ラッチインまで                                                   |       |      | 10   | ms  |    |

| T5.7                         | CLKOUT の起動 / セトリング: 電源投入から CLKOUT 正常 / 安定化まで                          |       |      | 10   | ms  |    |

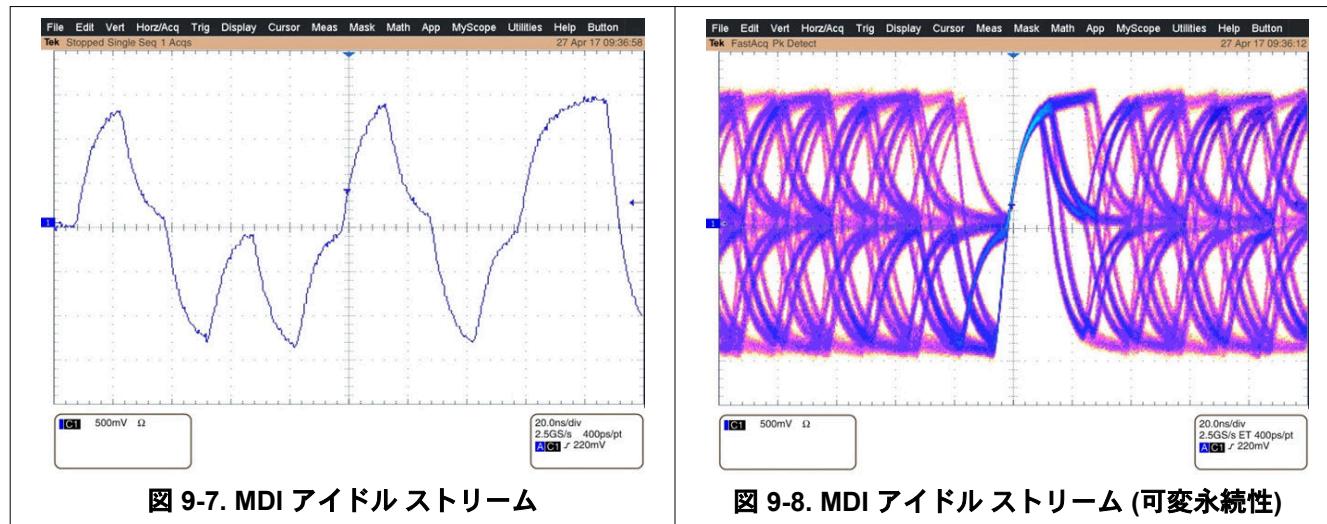

| T5.8                         | 電源投入からアイドル ストリーム出力まで                                                  |       |      | 10   | ms  |    |

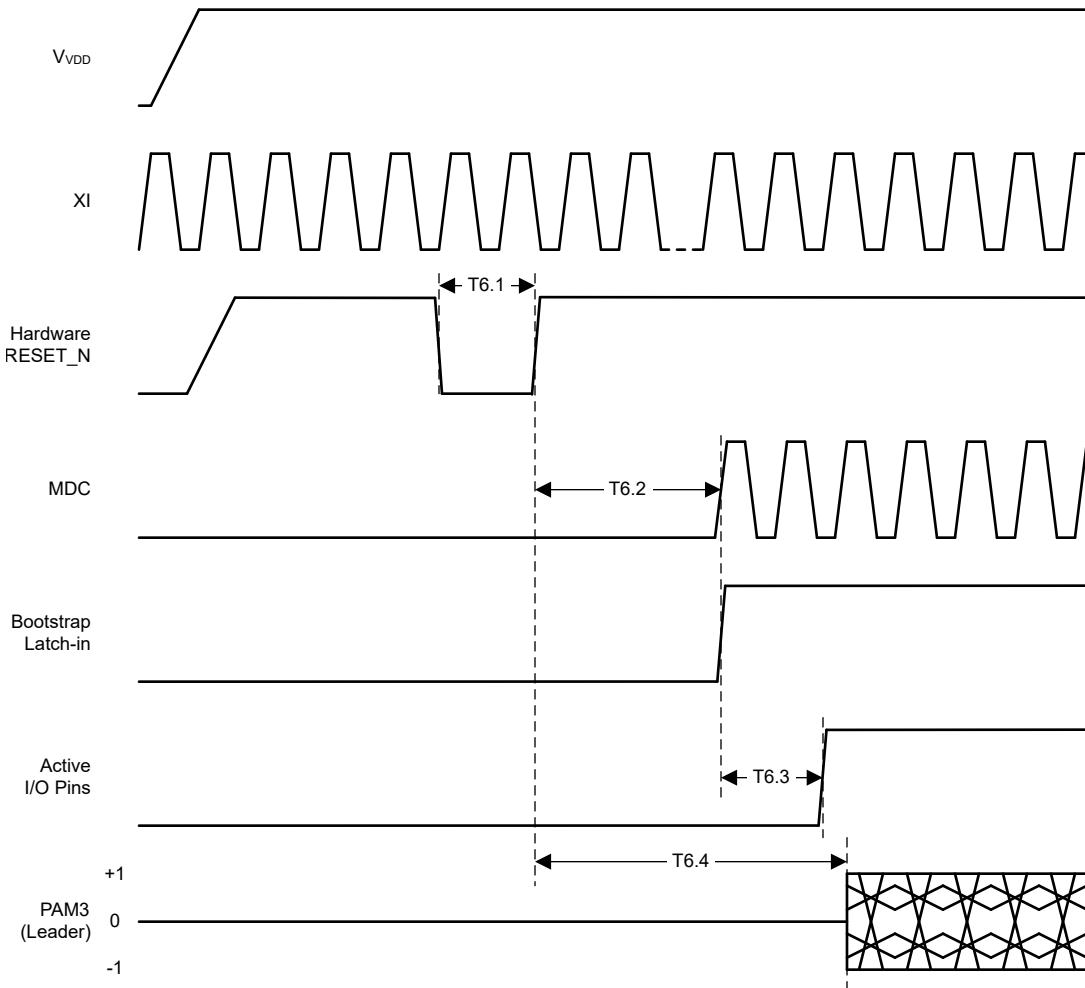

| <b>リセットタイミング (RESET_N)</b>   |                                                                       |       |      |      |     |    |

| T6.1                         | リセットパルス幅: リセット可能にするための最小リセットパルス幅                                      |       | 720  |      | ns  |    |

| T6.2                         | リセットから SMI レディまで: リセット後、レジスタ アクセスのために MDC プリアンブルを送信できるようになるまでに必要な待ち時間 |       | 1    | ms   |     |    |

| T6.3                         | リセットからストラップ 値ラッチインまで: ハードウェア構成のピンの遷移から出力ドライバまで                        |       | 40   |      | μs  |    |

| T6.4                         | リセットからアイドル ストリーム出力まで                                                  |       |      | 1800 | μs  |    |

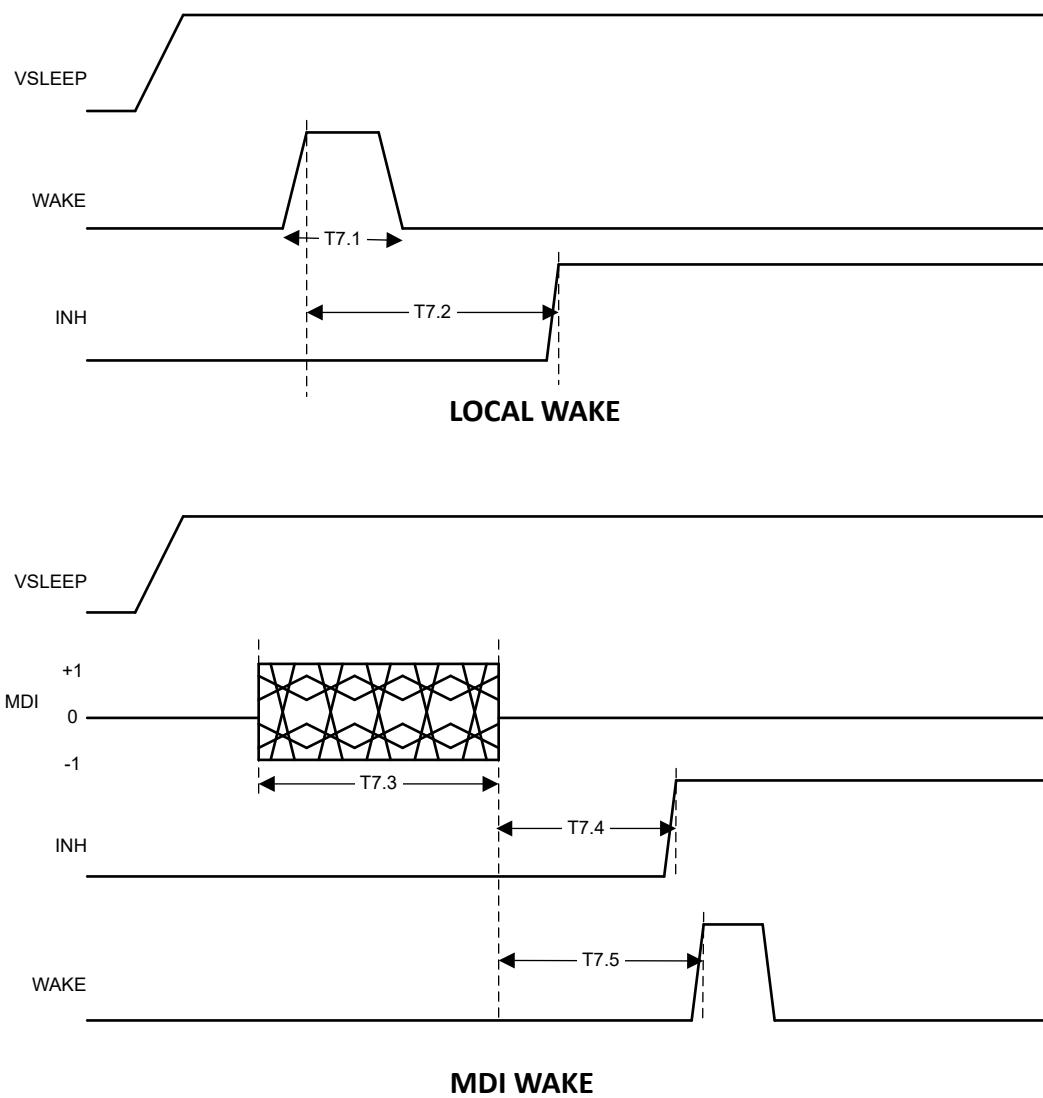

| <b>ウェーク要求とウェーク パルスのタイミング</b> |                                                                       |       |      |      |     |    |

| T7.1                         | ローカル ウェークアップ パルス幅                                                     |       | 40   |      | μs  |    |

| T7.2                         | ローカル ウェークアップから INH 遷移まで                                               |       |      | 40   | μs  |    |

| T7.3                         | エナジー検出に基づくウェークアップ パルス幅                                                |       |      | 0.7  | ms  |    |

| T7.4                         | エナジー検出に基づくウェークアップから INH 遷移まで                                          |       |      | 0.7  | ms  |    |

| T7.5                         | エナジー検出に基づくウェークアップから WAKE 転送パルスまで                                      |       |      | 1.4  | ms  |    |

| <b>送信レイテンシ タイミング</b>         |                                                                       |       |      |      |     |    |

|                              | MII の TX_CLK の立ち上がりエッジ (TX_EN アサート時) から MD の SSD シンボルまで               |       | 205  | 233  | ns  |    |

|                              | RMII フォロワの XI クロックの立ち上がりエッジ (TX_EN アサート時) から MDI の SSD シンボルまで         |       | 374  | 409  | ns  |    |

|                              | RMII リーダーのクロックの立ち上がりエッジ (TX_EN アサート時) から MDI の SSD シンボルまで             |       | 382  | 408  | ns  |    |

|                              | RGMII の TX_CLK の立ち上がりエッジ (TX_CTRL アサート時) から MDI の SSD シンボルまで          |       | 370  | 390  | ns  |    |

|                              | SGMII の最初のシンボルから MDI の SSD シンボルまで                                     |       | 420  | 456  | ns  |    |

| <b>受信レイテンシ タイミング</b>         |                                                                       |       |      |      |     |    |

|                              | MDI の SSD シンボルから MII の RX_CLK の立ち上がりエッジ (RX_DV アサート時) まで              |       | 467  | 491  | ns  |    |

|                              | MDI の SSD シンボルからフォロワ RMII の XI クロックの立ち上がりエッジ (CRS_DV アサート時) まで        |       | 527  | 574  | ns  |    |

|                              | MDI の SSD シンボルから RMII リーダーのリーダー クロックの立ち上がりエッジ (CRS_DV アサート時) まで       |       | 521  | 557  | ns  |    |

|                              | MDI の SSD シンボルから RGMII の RX_CLK の立ち上がりエッジ (RX_CTRL アサート時) まで          |       | 484  | 511  | ns  |    |

|                              | MDI の SSD シンボルから SGMII の最初のシンボルまで                                     |       | 708  | 788  | ns  |    |

| <b>25MHz 発振器の要件</b>          |                                                                       |       |      |      |     |    |

|                              | 周波数の許容誤差                                                              |       | -100 | +100 | ppm |    |

## 6.6 タイミング要件 (続き)

| パラメータ                       | テスト条件 | 最小値  | 公称値 | 最大値  | 単位  |

|-----------------------------|-------|------|-----|------|-----|

| 立ち上がり / 立ち下がり時間 (10% ~ 90%) |       |      | 8   |      | ns  |

| ジッター耐性 (RMS)                |       |      | 25  |      | ps  |

| 外部クロック モードでの XI デューティ サイクル  |       | 40   | 60  |      | %   |

| <b>50MHz 発振器の要件</b>         |       |      |     |      |     |

| 周波数                         |       | 50   |     | 100  | MHz |

| 温度と経時変化に対する周波数の許容誤差と安定性     |       | -100 | 100 | 100  | ppm |

| 立ち上がり / 立ち下がり時間 (10% - 90%) |       | 4    |     | 4    | ns  |

| デューティ サイクル                  |       | 35   | 65  | 65   | %   |

| <b>25MHz 水晶振動子の要件</b>       |       |      |     |      |     |

| 周波数                         |       | 25   |     | 100  | MHz |

| 温度と経時変化に対する周波数の許容誤差と安定性     |       | -100 | 100 | 100  | ppm |

| 等価直列抵抗                      |       | 100  |     | 100  | Ω   |

| <b>出力クロック タイミング (25MHz)</b> |       |      |     |      |     |

| 周波数 (PPM)                   |       | -100 | 100 | 100  | -   |

| デューティ サイクル                  |       | 40   | 60  | 60   | %   |

| 立ち上がり時間                     |       | 5000 |     | 5000 | ps  |

| 立ち下がり時間                     |       | 5000 |     | 5000 | ps  |

| ジッタ (短期)                    |       | 1000 |     | 1000 | ps  |

| 周波数                         |       | 25   |     | 100  | MHz |

(1) ランプレートが 8ms より長い電源では、最後の電源が安定した後にリセットパルスが必要です。

## 6.7 タイミング図

図 6-1. MII のタイミング

図 6-2. RMII の送信および受信タイミング

図 6-3. RGMII 送信タイミング

図 6-4. RGMII の受信タイミング (内部遅延有効化)

図 6-5. RGMII の受信タイミング (内部遅延無効化)

図 6-6. シリアル マネージメントのタイミング

図 6-7. パワーアップのタイミング

図 6-8. リセットタイミング

図 6-9. WAKE のタイミング

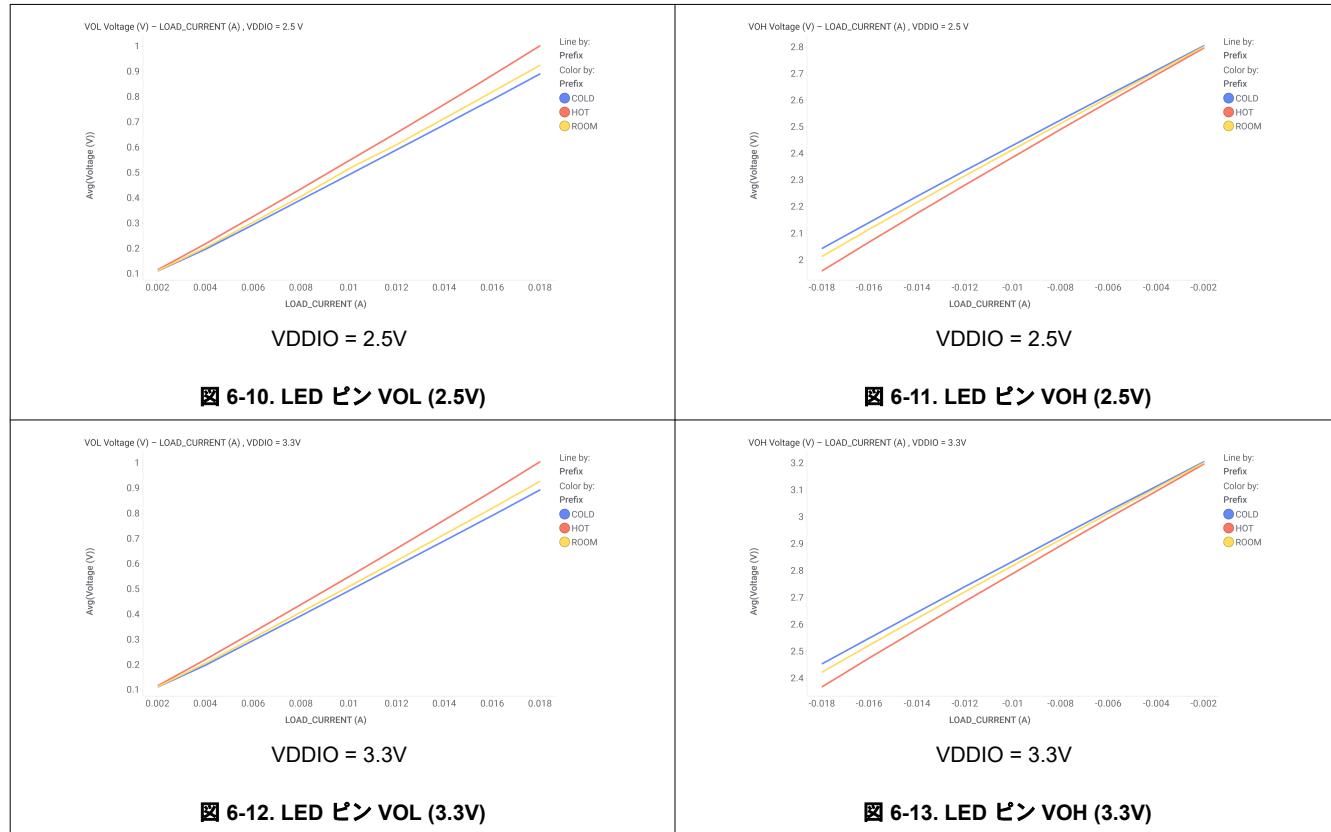

## 6.8 代表的特性

## 7 詳細説明

### 7.1 概要

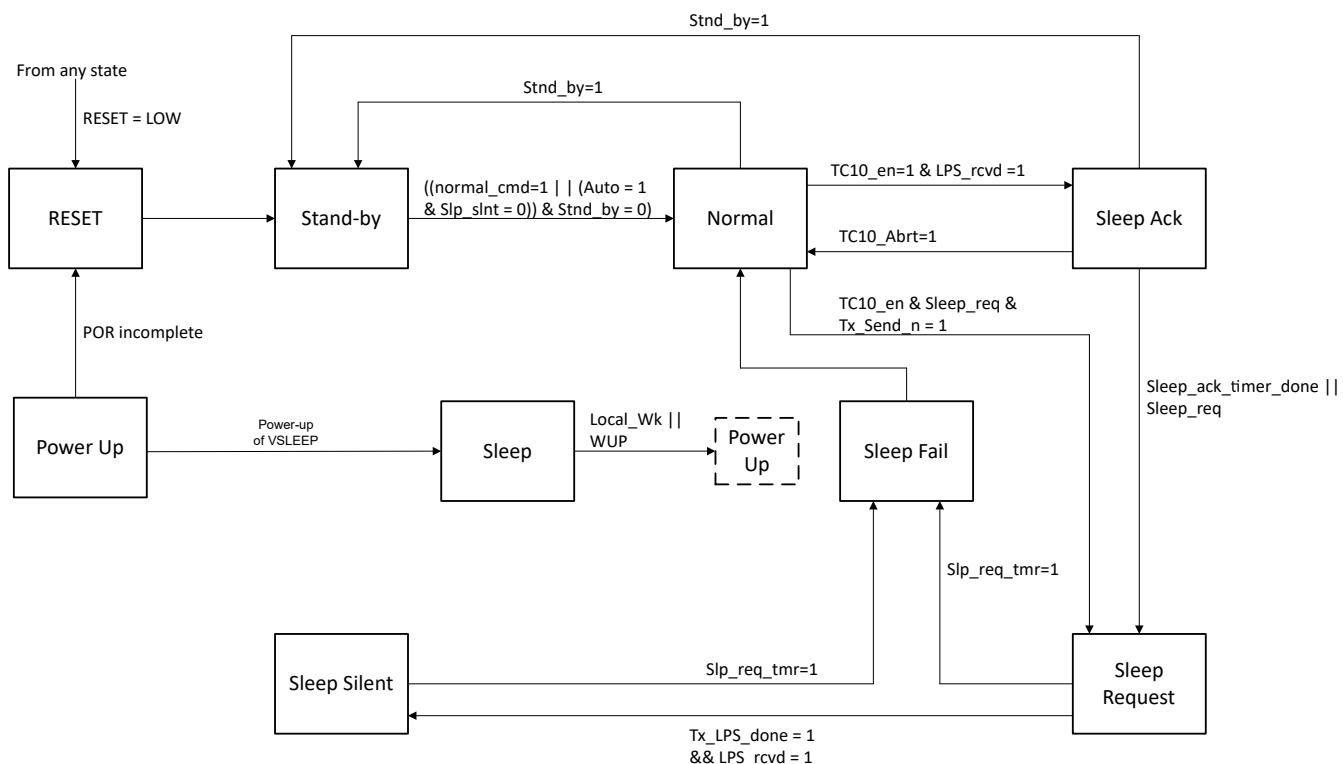

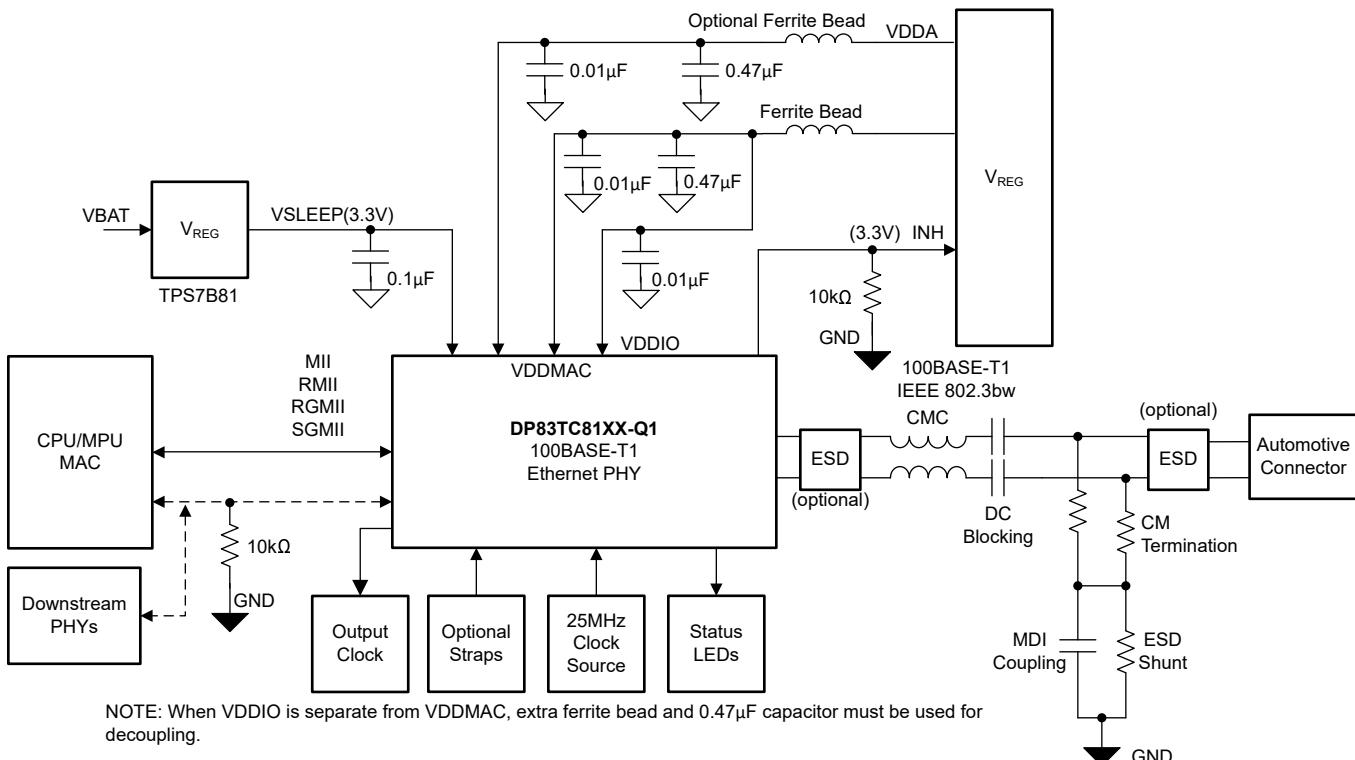

DP83TC813S-Q1 は 100BASE-T1 の車載用イーサネット物理層トランシーバです。本デバイスは IEEE 802.3bw に準拠しており 車載アプリケーション向けに AEC-Q100 認定済みです。DP83TC813S-Q1 は、BroadR-Reach PHY および 100BASE-T1 PHY の両方と相互運用可能です。

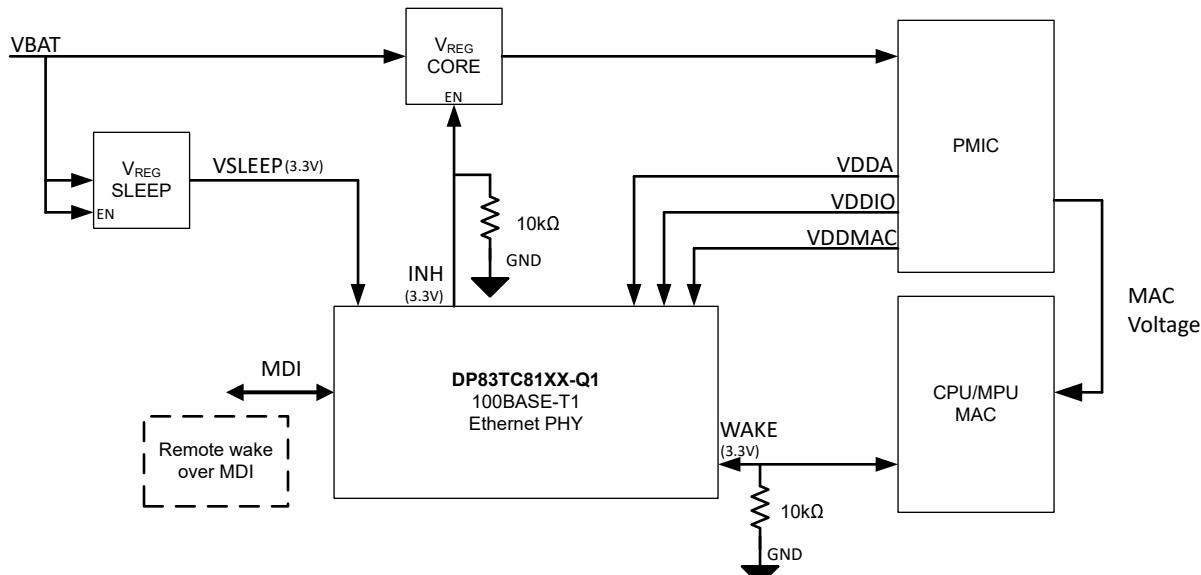

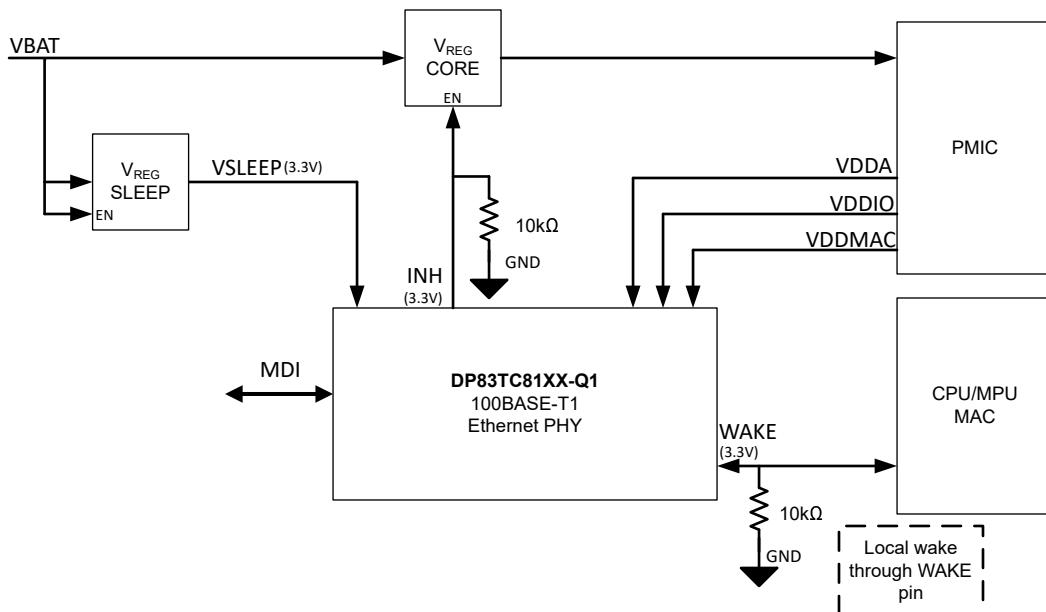

DP83TC813S-Q1 は Open Alliance TC-10 低消費電力モードもサポートして、さらに消費電力を削減できます。この PHY は、WAKE および INH ピンをサポートしているため、システムに TC-10 機能を実装できます。

このデバイスは、自動車用 EMC の厳しい制限を満たしながら、100Mbps の速度で動作するように特別に設計されています。DP83TC813S-Q1 は、シールドなしシングルツイストペア ケーブルを介して 66.667MHz で PAM3 三元記号を送信します。このデバイスはアプリケーションの柔軟性が高く 単一の 28 ピン VQFN ウェッタブル フランク パッケージで MII、RMII、RGMII、SGMII をサポートしています。

DP83TC813S-Q1 には、システム内での使用に加え、デバッグ、準拠、システム プロトタイピングの両方を目的とする広範な診断ツール キットがあります。DP83TC813S-Q1 は IEC61000-4-2 レベル 4 の静電放電制限を満たすことができ、ESD イベントをリアルタイムで検出するためのオンチップ ESD センサも搭載しています。

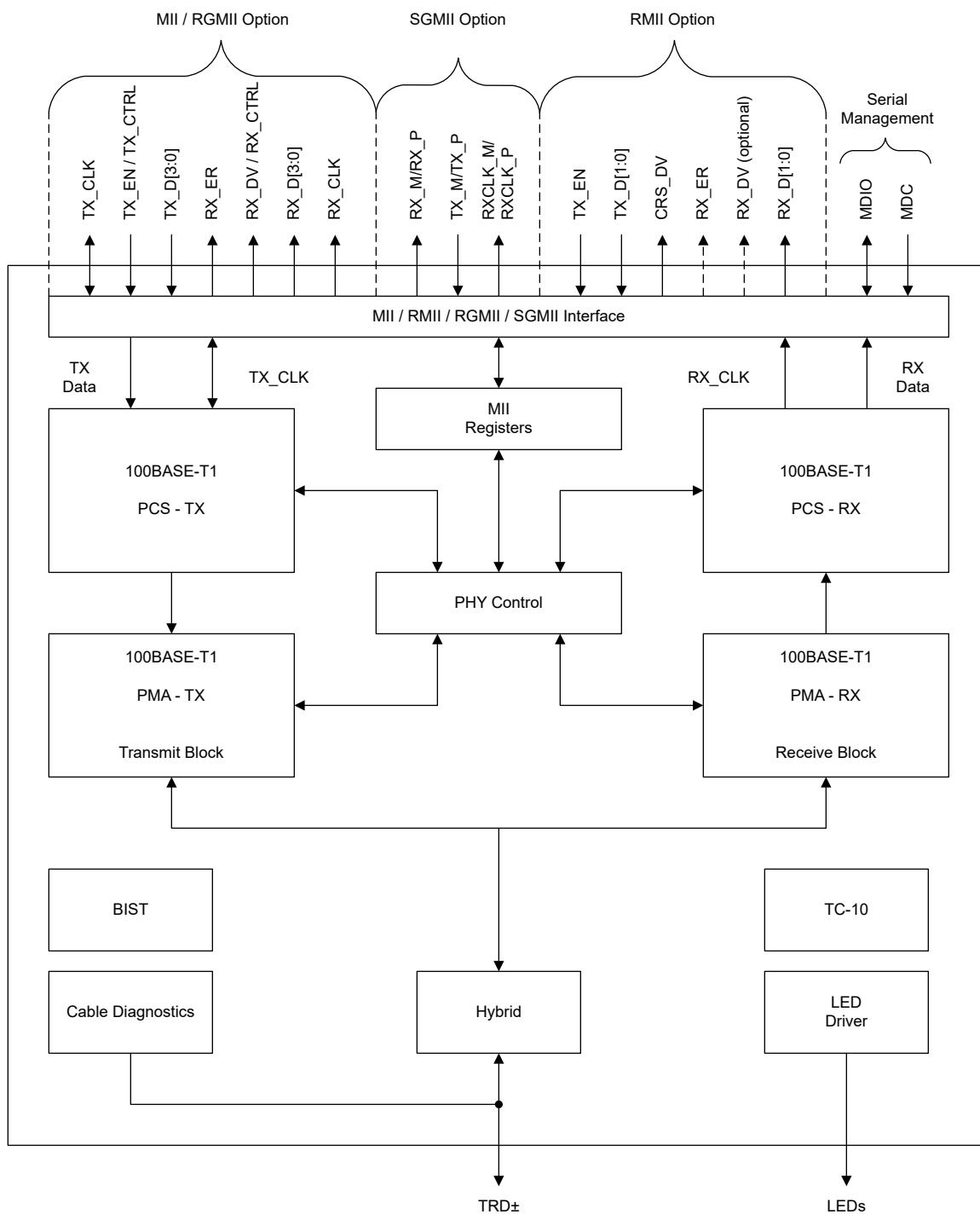

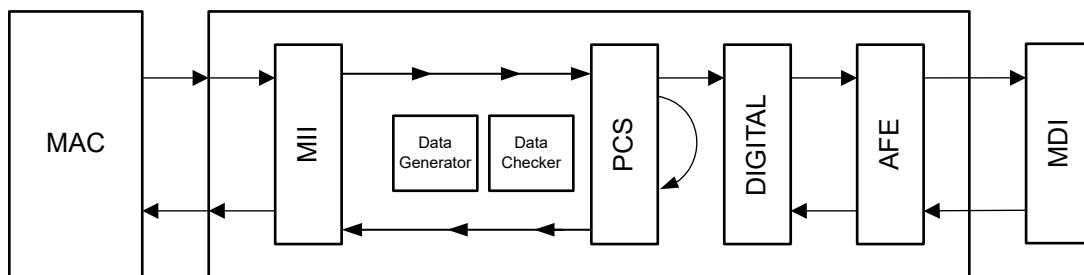

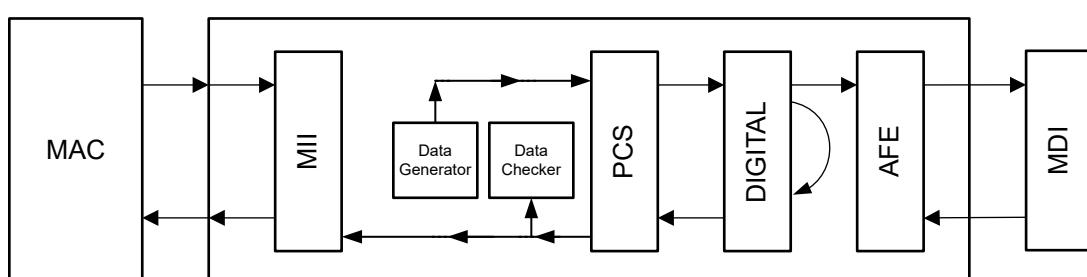

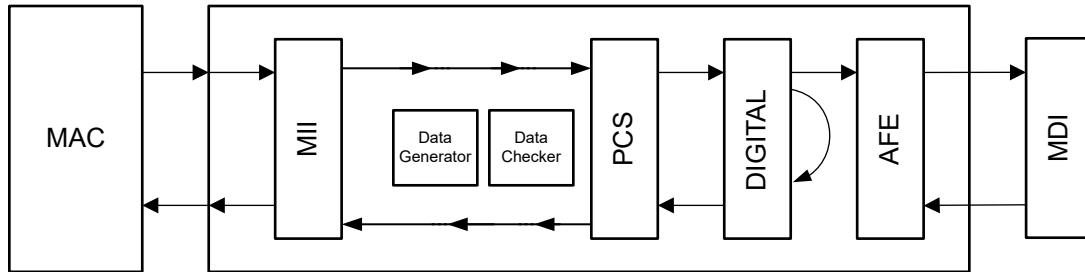

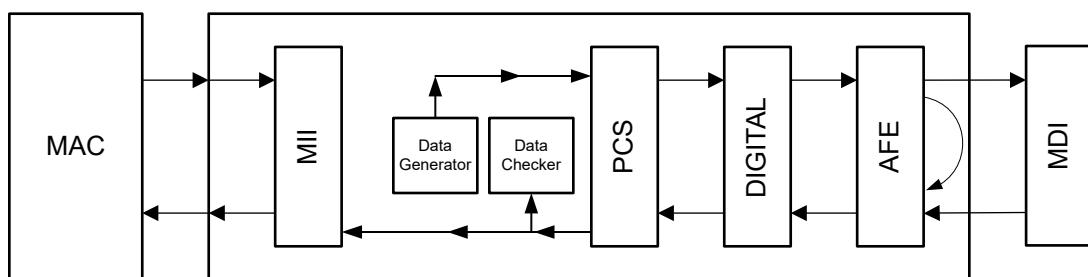

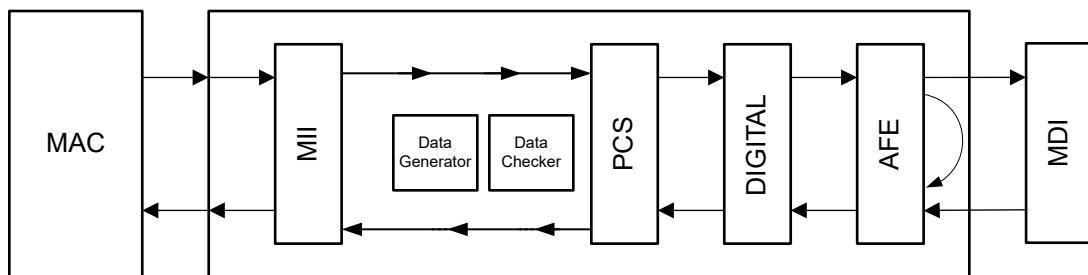

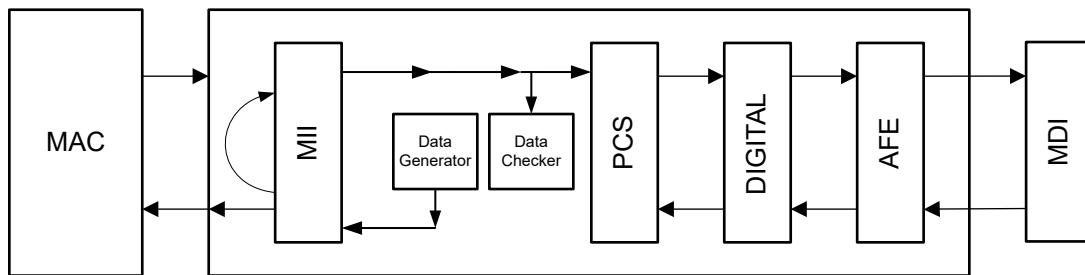

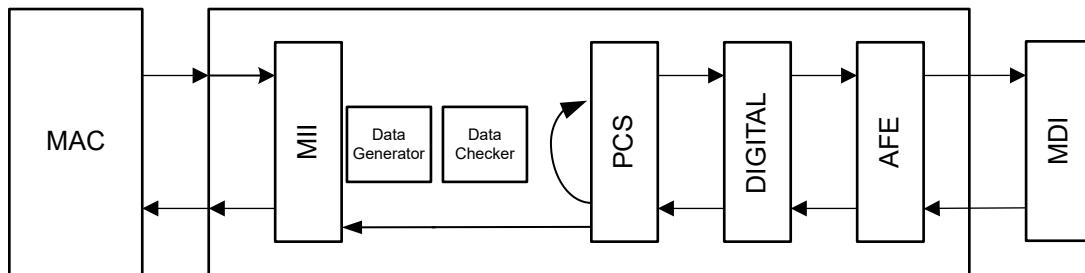

## 7.2 機能ブロック図

図 7-1. DP83TC813S-Q1

## 7.3 機能説明

### 注

*DP83TC812, DP83TC813, DP83TC814 を参考。準拠性テストに使用されるレジスタ設定の詳細について

は、Open Alliance 仕様準拠のための構成アプリケーション ノートを参照してください。準拠性テスト時と同じ

性能を得るには、これらのレジスタ設定を使用する必要があります。*

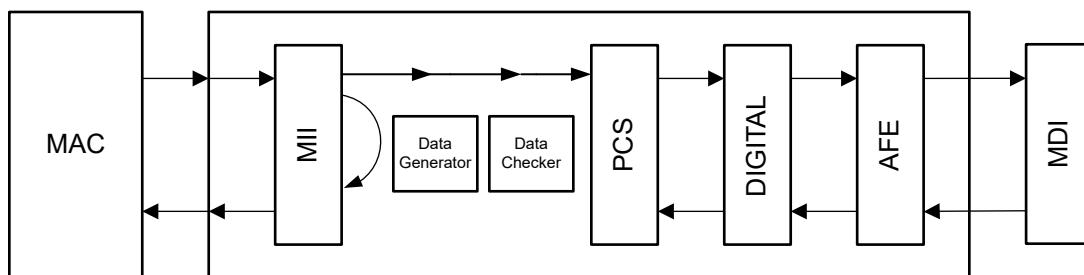

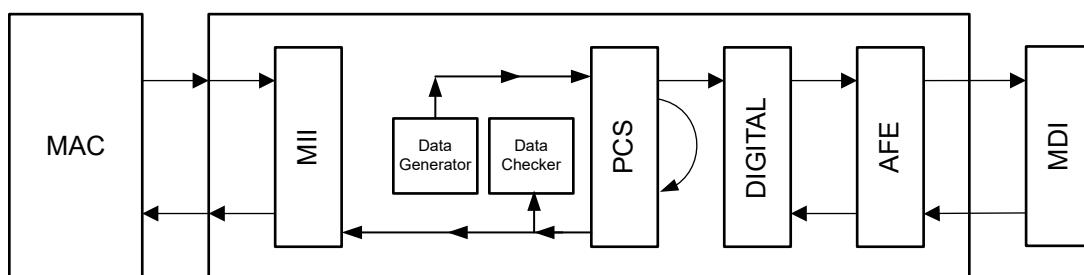

### 7.3.1 診断ツール キット

DP83TC813 の診断ツール キットは、通常動作の監視、デバイス レベル デバッグ、システム レベル デバッグ、フォルト検出、準拠性テストのための機能を備えています。このツール キットには、PRBS データによる内蔵セルフ テスト、各種ループバック モード、信号品質インジケータ (SQI)、時間領域反射計測 (TDR)、温度モニタ、静電放電モニタ、IEEE 802.3bw テスト モードが含まれています。

#### 7.3.1.1 信号品質インジケータ

DP83TC813S-Q1 が動作している場合、信号品質インジケータを使用して、本デバイスによる SNR 測定値に基づいてリンクの品質を判定できます。SQI は 8 レベルの表示として示されています。信号品質表示は、レジスタ 0x871 からアクセスできます。リアルタイムのリンク信号品質ステータスを確保できるように、PHY は SQI を継続的に監視します。

レジスタ 0x871 のビット [3:1] には現在の SQI 値が格納され、ビット [7:5] には前回の読み取り以降で観測された最悪の SQI 値が格納されます。レジスタ 0x871[SQI] で報告される値は、3:1 アライアンスで必要とされる SQI レベルに直接マップされます。

最も正確な SQI レポートを得るには、SNLA389 アプリケーション ノートに説明されている初期化ルーチンを使用してください。

**表 7-1. 信号品質インジケータ**

| REG 0x871[3:1] | OPEN ALLIANCE SQI レベル | リンクの品質      |

|----------------|-----------------------|-------------|

| 0x0            | 0 (最悪)                | 弱い / リンクなし  |

| 0x1            | 1                     |             |

| 0x2            | 2                     |             |

| 0x3            | 3                     |             |

| 0x4            | 4                     | 良好 / 優れたリンク |

| 0x5            | 5                     |             |

| 0x6            | 6                     |             |

| 0x7            | 7 (最高)                |             |

#### 7.3.1.2 静電気放電 (ESD) 検出

静電気放電は電子回路にとって重要な問題であり、適切に緩和しない場合、短期的な問題 (シグナル インテグリティ、リンク ドロップ、パケット喪失) だけでなく、長期的な信頼性に関する不具合を引き起こす可能性があります。DP83TC813 は堅牢な ESD 保護回路を内蔵して、ESD 検出アーキテクチャを備えています。さらなる分析とデバッグのため、ESD イベントを MDI ピンで独立して検出できます。

さらに、DP83TC813 には割り込みステータス フラグがあり、ESD イベントがログに記録されるとレジスタ 0x12[11] が設定されます。この割り込みは、同じレジスタのビット [3] を使用して INT\_N ピンに接続できます。レジスタ 0x442[14:9] には、電源投入以降に発生した ESD イベントの回数が格納されます。保証されていないクリア動作を防止するため、ESDS レジスタはハードウェアおよびソフトウェアリセットを無視します。

#### 7.3.1.3 時間領域反射計測

時間領域反射計測は、ケーブル上の開放および短絡故障の推定に加えて、ケーブル、コネクタ、終端の品質の判定に役立ちます。DP83TC813S-Q1 は、接続されたツイストペアケーブルをテスト パルスを送信します。送信されたパルスはケーブルを伝わり、欠陥や故障などの不完全な箇所で反射します。これにより、デバイスは反射が戻ってくるまでの時間と、す

べての反射の強度(振幅)を測定できます。この手法により、DP83TC813-Q1を使用してケーブルの開放および短絡を識別できます。

TDRは、レジスタ0x1Eのbit[15]を設定することで有効化されます。手順は以下の通りです。

- SNLA389 アプリケーションノートの初期化設定に従って、DP83TC813-Q1を構成します

- PHYに接続されているリンクパートナーはサイレントである必要があります。TDR実行中、リンクはダウンしています。

- SNLA389に記載されているように、TDR前の構成設定を実行します。

- レジスタ0x1E[15]を「1」に設定して、TDRを開始します。

- 100ms待機、レジスタ0x1E[1:0]を読み出します

- レジスタが0b10を読み出すと、TDRは正常に実行されました。

- TDRが正常に実行された場合、レジスタ0x310を読み取ってTDR結果を取得します。

- 0x310[7]:0 = ケーブルフォルトが検出されない、または1 = ケーブルフォルトが検出されました

- 0x310[6]:0 = ケーブルフォルトが短絡、または1 = ケーブルフォルトがオープン

- 有効なケーブルフォルトが検出された場合、0x310[5:0]に位置の値がメートル単位で格納されます。

#### 7.3.1.4 電圧検出

DP83TC813には、電源ピンで電圧を監視するためのセンサを提供します。低電圧監視は、DP83TC813では、デフォルトで常にアクティブです。低電圧状態が検出された場合、レジスタ0x0013に割り込みステータスフラグがセットされます。これらの割り込みは、同じレジスタを使用してINTピンに配線することもできます。

各センサの読み取りには、次の方法を使用する必要があります。

- ステップ1: レジスタ0x0467 = 0x6004をプログラムします; モニタの初期設定

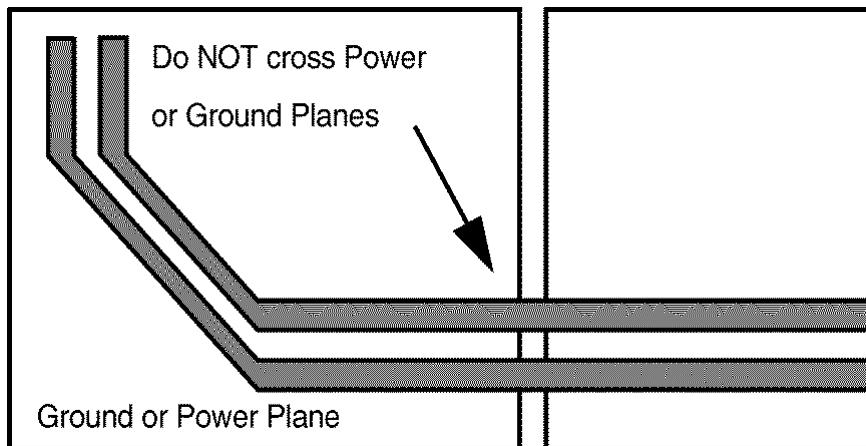

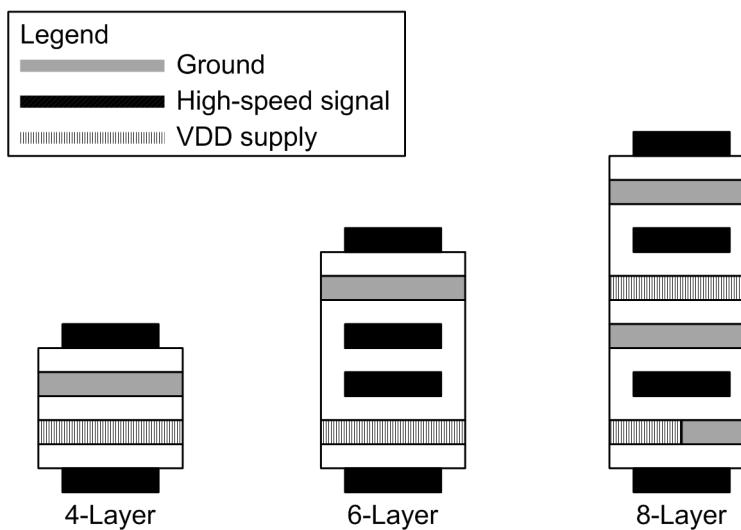

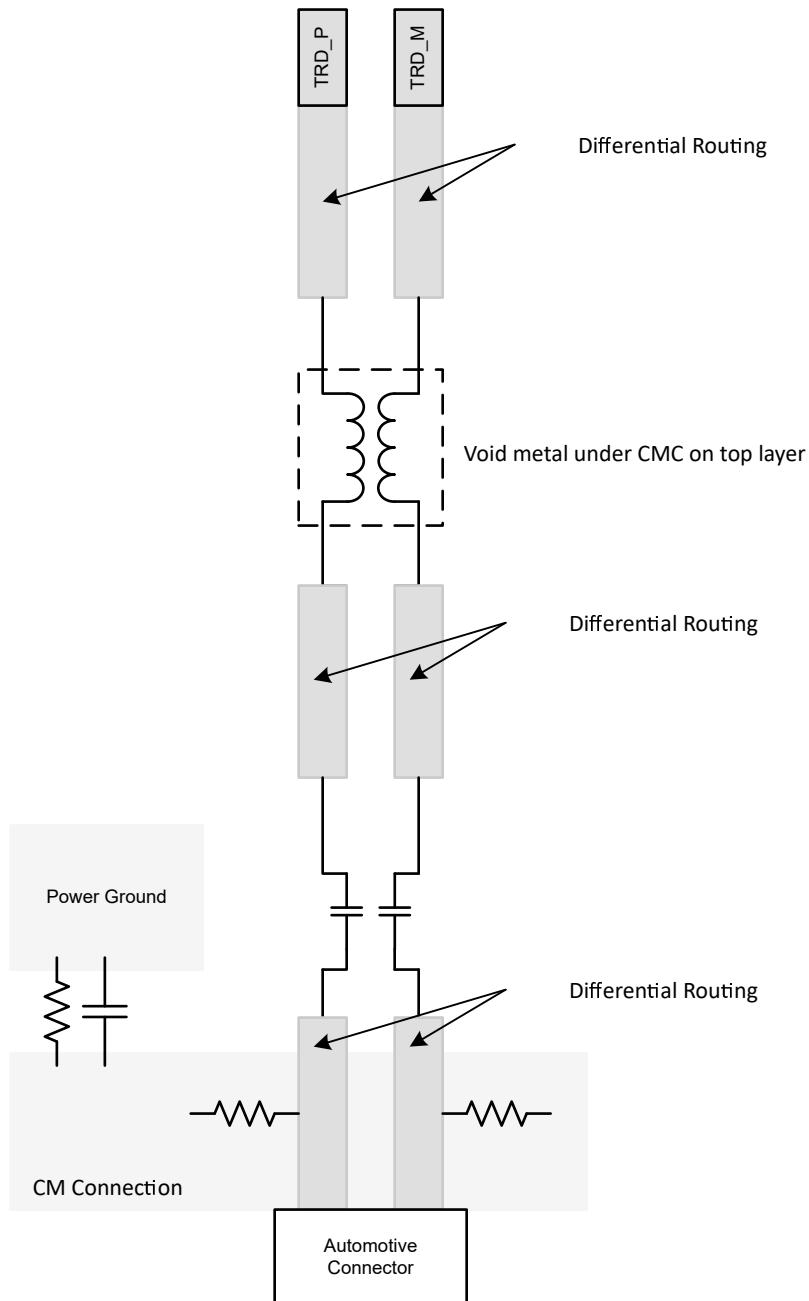

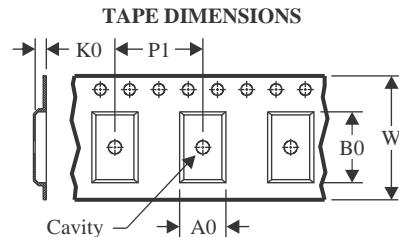

- ステップ2: レジスタ0x046A = 0x00A3をプログラムします; モニタを有効化します