## DirectPath™ 2Vrms、可変ゲイン、 ライン・ドライバおよびヘッドホン・アンプ

### 特 長

- DirectPath™

- ポップ音/クリック音を防止

- 出力DCブロッキング・コンデンサが不要

- 電源電圧：3.0V ~ 3.7V

- 低ノイズ、低THD

- SNR > 109dB

- $V_n$  (typ) < 7 $\mu$ Vrms、20Hz ~ 20kHz

- THD+N < 0.002% (10k $\Omega$ )

- 出力電圧 (5k $\Omega$ 負荷)

- 2Vrms (電源電圧3.3V時)

- ステレオDirectPath™ヘッドホン：

- 40mW (32 $\Omega$ 、電源電圧3.3V)

- 安定負荷範囲：16 $\Omega$  ~  $\infty$   $\Omega$

- 差動入力

- 電力センスUVPによるブラウンアウト保護

- 短絡保護と過熱保護

- $\pm 8kV$ のIEC ESD保護

- DRV602およびDRV603と互換性のあるフットプリント

- デュアル・ライン・ドライバ構成をサポート

Gate Drive、PowerPAD は、テキサス・インスツルメンツの商標です。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ (日本 TI) が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。

日本 TI による和文資料は、あくまでも TI 正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。

TI および日本 TI は、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

### ア プ リ ケ シ ョ ン

- 液晶テレビ、プラズマ・テレビ

- Blu-ray Disc™プレーヤー、DVDプレーヤー

- ミニ/マイクロ・コンボ・システム

- サウンドカード

### 概 要

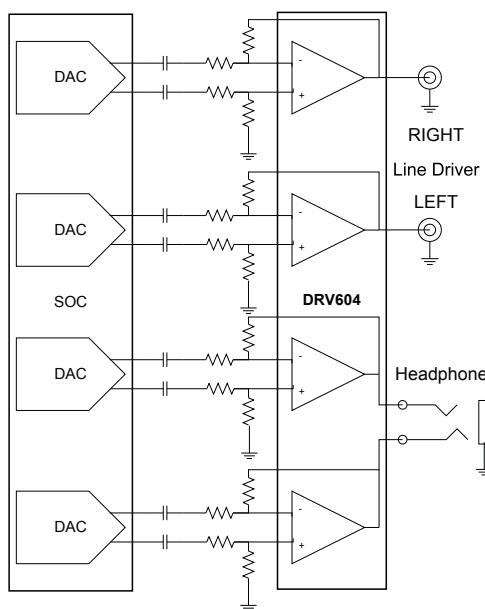

DRV604は、出力DCブロッキング・コンデンサが不要なため部品数およびコストを削減できるように設計された、ステレオ・ヘッドホン出力付きの2Vrmsポップフリー・ステレオ・ライン・ドライバです。このデバイスは、サイズおよびコストが設計上重要なパラメータとなる単一電源回路に対して最適です。

TIが特許を持つDirectPath™テクノロジを使用して設計されたDRV604は、5k $\Omega$ の負荷に対して2Vrmsを駆動できます。ヘッドホン出力は、3.3Vの電源から32 $\Omega$ の負荷にクリーンな40mWを供給できます。このデバイスは差動入力を持ち、-1V/V ~ -10V/V のゲイン範囲をサポートする外部ゲイン設定抵抗を使用します。ヘッドホン出力およびライン出力では、単純なESD保護回路によって $\pm 8kV$ のIEC ESD保護を実現します。DRV604は、ポップ音のないオン/オフ制御のための内蔵インエーブル制御を備えています。DRV604は、内蔵コンパレータを使用して外部電源電圧を監視し、ブラウンアウト状態中にシャットダウンすることにより、アップストリームのオーディオDACでクリック音やポップ音が発生するのを防ぎます。

オーディオ製品でDRV604を使用すると、ヘッドホン出力および2Vrms出力を生成する従来の方法と比較して、部品数を大きく減らすことができます。DRV604では、5.6Vppの出力を生成するために3.3V以上の電源は必要とせず、分割レール電源も必要ありません。DRV604には、独自のチャージ・ポンプが内蔵され、クリーンでポップ音のないグランド・バイアスの2Vrms出力を供給する負電源レールを生成できます。

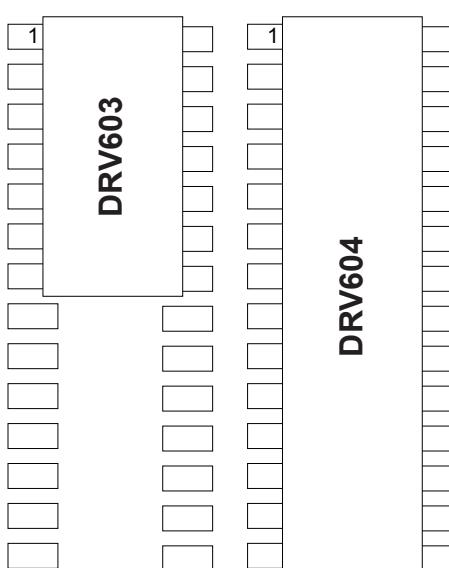

DRV604は、28ピンHTSSOPパッケージで供給されます。ヘッドホン・アンプのないステレオ・ライン・ドライバについては、DRV603を参照してください。

SLOS659A 翻訳版

# 静電気放電対策

静電気放電はわずかな性能の低下から完全なデバイスの故障に至るまで、様々な損傷を与えます。すべての集積回路は、適切な ESD 保護方法を用いて、取扱いと保存を行うようにして下さい。高精度の集積回路は、損傷に対して敏感であり、極めてわずかなパラメータの変化により、デバイスに規定された仕様に適合しなくなる場合があります。

## 製品情報

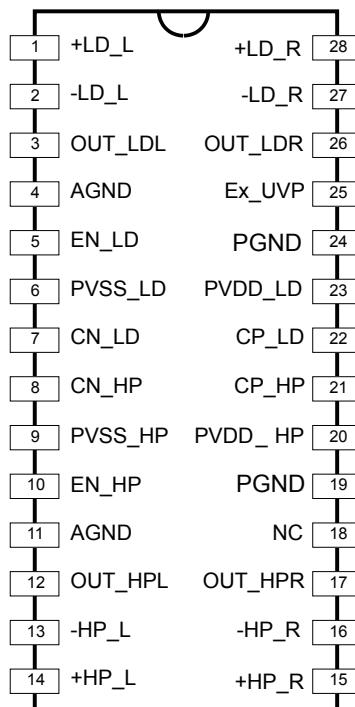

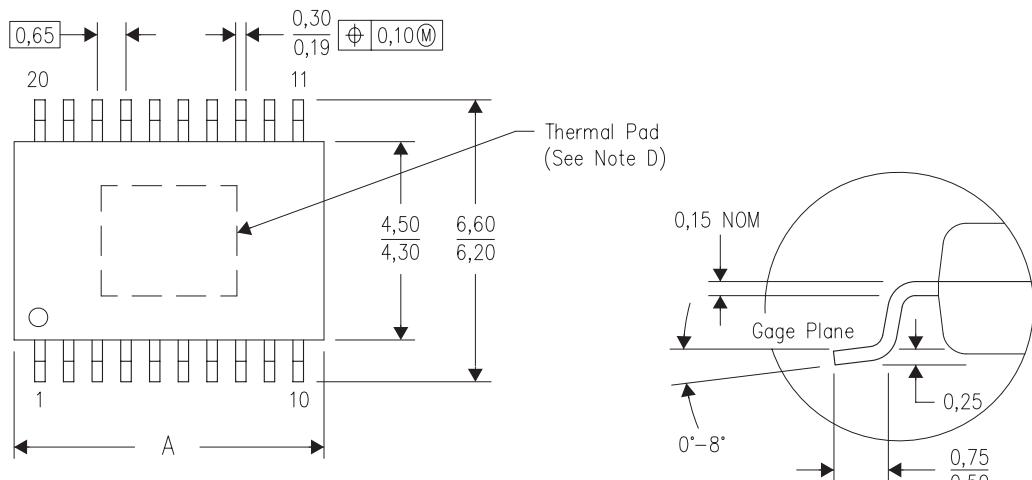

### ピン配置

DRV604は、熱特性強化型28ピンHTSSOPパッケージ（PWP）で供給されます。

### ピン機能

| 名前      | ピン<br>PWP番号 | 機能 <sup>(1)</sup> | 概要                               |

|---------|-------------|-------------------|----------------------------------|

| +LD_L   | 1           | I                 | 正入力、ライン・ドライバ左                    |

| -LD_L   | 2           | I                 | 負入力、ライン・ドライバ左                    |

| OUT_LDL | 3           | O                 | 出力、ライン・ドライバ左                     |

| AGND    | 4           | P                 | アナログ・グランド                        |

| EN_LD   | 5           | I                 | ライン・ドライバのイネーブル、アクティブ・ハイ          |

| PVSS_LD | 6           | O                 | ライン・ドライバのチャージ・ポンプ負電源電圧出力         |

| CN_LD   | 7           | I/O               | チャージ・ポンプのフライング・コンデンサ負接続、ライン・ドライバ |

| CN_HP   | 8           | I/O               | チャージ・ポンプのフライング・コンデンサ負接続、ヘッドホン    |

| PVSS_HP | 9           | O                 | ヘッドホンのチャージ・ポンプ負電源電圧出力            |

| EN_HP   | 10          | I                 | ヘッドホンのイネーブル、アクティブ・ハイ             |

| AGND    | 11          | P                 | アナログ・グランド                        |

| OUT_HPL | 12          | O                 | 出力、ヘッドホン左                        |

| -HP_L   | 13          | I                 | 負入力、ヘッドホン左                       |

| +HP_L   | 14          | I                 | 正入力、ヘッドホン左                       |

| +HP_R   | 15          | I                 | 正入力、ヘッドホン右                       |

| -HP_R   | 16          | I                 | 負入力、ヘッドホン右                       |

(1) I = 入力、O = 出力、P = 電源

## ピン機能（続き）

| ピン      |       | 機能 <sup>(1)</sup> | 説明                               |

|---------|-------|-------------------|----------------------------------|

| 名前      | PWP番号 |                   |                                  |

| OUT_HPR | 17    | O                 | 出力、ヘッドホン右                        |

| NC      | 18    |                   | 未接続                              |

| PGND    | 19    | P                 | チャージ・ポンプのパワー・グランド、ヘッドホン          |

| PVDD_HP | 20    | P                 | ヘッドホン電源電圧、正電源に接続、内部でピン23に接続      |

| CP_HP   | 21    | I/O               | チャージ・ポンプのフライング・コンデンサ正接続、ヘッドホン    |

| CP_LD   | 22    | I/O               | チャージ・ポンプのフライング・コンデンサ正接続、ライン・ドライバ |

| PVDD_LD | 23    | P                 | ライン・ドライバ電源電圧、正電源に接続、内部でピン20に接続   |

| PGND    | 24    | P                 | チャージ・ポンプのパワー・グランド、ライン・ドライバ       |

| Ex_UVP  | 25    | I                 | 外部低電圧保護                          |

| OUT_LDR | 26    | O                 | 出力、ライン・ドライバ右                     |

| -LD_R   | 27    | I                 | 負入力、ライン・ドライバ右                    |

| +LD_R   | 28    | I                 | 正入力、ライン・ドライバ右                    |

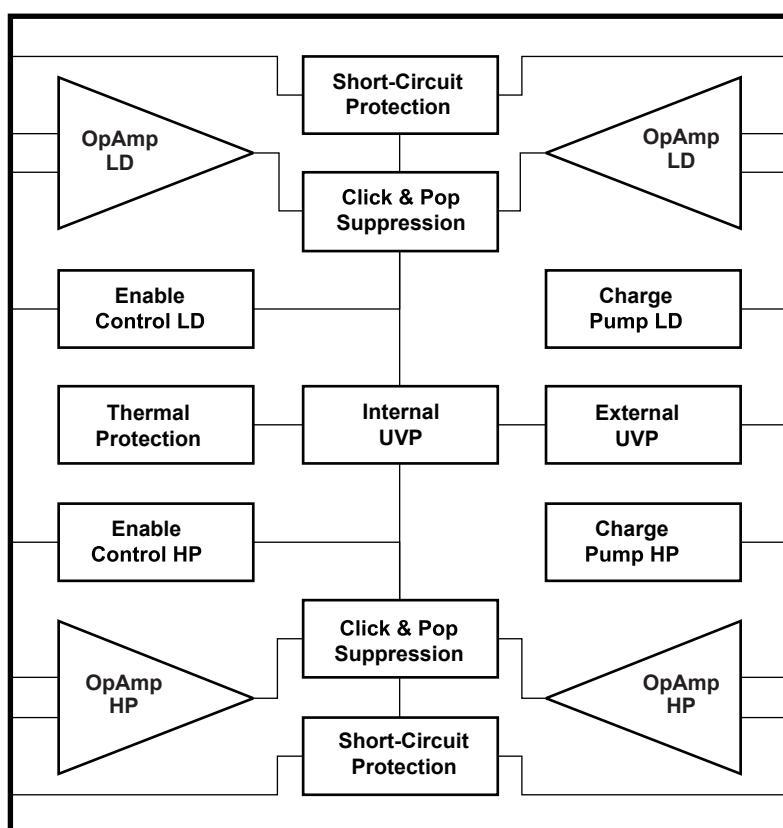

## システム・ブロック図

## ご発注の手引き<sup>(1)</sup>

| T <sub>A</sub> | パッケージ     | 概要   |

|----------------|-----------|------|

| -40°C~85°C     | DRV604PWP | 28ピン |

(1) 最新のパッケージおよびご発注情報については、このデータ・シートの巻末にある「付録：パッケージ・オプション」を参照するか、またはTIのWebサイト([www.ti.com](http://www.ti.com)または[www.tij.co.jp](http://www.tij.co.jp))をご覧ください。

## 絶対最大定格

動作温度範囲内（特に記述のない限り）<sup>(1)</sup>

|                                 | <b>DRV604PWP</b>     | <b>単位</b> |

|---------------------------------|----------------------|-----------|

| PVDD～GND                        | -0.3 to 4.5          | V         |

| 入力電圧、V <sub>I</sub>             | PVSS-0.3 to PVDD+0.3 | V         |

| 最小負荷インピーダンス—ライン出力               | 1000                 | Ω         |

| 最小負荷インピーダンス—ヘッドホン出力             | 8                    | Ω         |

| EN_LD～GND                       | -0.3 to PVDD+0.3     | V         |

| EN_HP～GND                       | -0.3 to PVDD+0.3     | V         |

| 最大動作ジャンクション部温度範囲、T <sub>J</sub> | -40 to 150           | °C        |

| 保存温度                            | -40 to 150           | °C        |

(1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を超える状態での本製品の機能動作は含まれていません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

### 定格熱抵抗<sup>(1)</sup>

| パッケージ     | R <sub>θJP</sub> (°C/W) | R <sub>θJA</sub> (°C/W) | R <sub>ψJT</sub> (°C/W) |

|-----------|-------------------------|-------------------------|-------------------------|

| DRV604PWP | 0.72                    | 28                      | 0.45                    |

(1) PowerPADをTI推奨基板に半田付け

## 推奨動作条件

動作温度範囲内（特に記述のない限り）

|                     |                |              | 最小  | 公称  | 最大  | 単位    |

|---------------------|----------------|--------------|-----|-----|-----|-------|

| PVDD                | 電源             | DC電源電圧       | 3.0 | 3.3 | 3.7 | V     |

| R <sub>L</sub> (HP) | 負荷インピーダンス      |              | 32  | 32  |     | Ω     |

|                     |                |              | 5   | 10  |     | kΩ    |

| V <sub>IL</sub>     | “Low” レベル入力電圧  | EN_LD, EN_HP | 38  | 40  | 43  | %PVDD |

| V <sub>IH</sub>     | “High” レベル入力電圧 | EN_LD, EN_HP | 57  | 60  | 66  | %PVDD |

| T <sub>A</sub>      | 周囲温度           |              | -40 | 25  | 85  | °C    |

## 電気的特性

$PVDD\_LD = PVDD\_HP = 3.3 \text{ V}$ ,  $R_{LD} = 5 \text{ k}\Omega$ ,  $R_{HP} = 32 \Omega$ ,  $R_{FB} = 20 \text{ k}\Omega$ ,  $R_{IN} = 10 \text{ k}\Omega$ ,  $T_A = 25^\circ\text{C}$ , チャージ・ポンプ :  $C_{CP\_LD} = C_{CP\_HP} = 1.0 \mu\text{F}$  (特に記述のない限り)

| パラメータ                 | 測定条件               | DRV604                                              |      |       | 単位  |

|-----------------------|--------------------|-----------------------------------------------------|------|-------|-----|

|                       |                    | 最小                                                  | 標準   | 最大    |     |

| $ V_{os} $            | 出力オフセット電圧          | PVDD = 3.3 V                                        |      | 1     | mV  |

| PSRR                  | 電源除去比              |                                                     | 70   | 80    | dB  |

| $V_{OH}$              | “High” レベル出力電圧     | PVDD = 3.3 V                                        | 3.1  |       | V   |

| $V_{OL}$              | “Low” レベル出力電圧      | PVDD = 3.3 V                                        |      | -3.05 | V   |

| $V_{uvp\_on}$         | PVDD、低電圧検出内部低電圧検出  | Internal under-voltage detection.                   |      | 2.8   | V   |

| $V_{uvp\_hysteresis}$ | PVDD、低電圧検出、ヒステリシス  |                                                     | 200  |       | mV  |

| $V_{uvp}$             | 外部低電圧検出            |                                                     | 1.25 |       | V   |

| $I_{Hys}$             | 外部低電圧検出ヒステリシス電流    |                                                     | 5    |       | μA  |

| $F_{cp}$              | チャージ・ポンプのスイッチング周波数 |                                                     | 260  | 700   | kHz |

| $ I_{IH} $            | “High” レベル入力電流     | PVDD = 3.3 V, $V_{IH} = PVDD$ , EN_HP, EN_LD        | 1    |       | μA  |

| $ I_{IL} $            | “Low” レベル入力電流      | PVDD = 3.3 V, $V_{IL} = 0 \text{ V}$ , EN_HP, EN_LD | 1    |       | μA  |

| $I_{(PVDD)}$          | 電源電流、無負荷           | PVDD, EN_LD, EN_HP = 3.3 V                          | 15   | 25    | 35  |

|                       | 電源電流、ライン・ドライバ、無負荷  | PVDD, EN_LD = 3.3 V, EN_HP = GND                    |      | 12    |     |

|                       | 電源電流、ヘッドホン、無負荷     | PVDD, EN_LD = GND, EN_HP = 3.3 V                    |      | 13    |     |

|                       | 電源電流、ディスエーブル       | PVDD = 3.3 V, EN_LD, EN_HP = GND, Ex_UVP = GND      | 2.5  | 5     |     |

| $T_{sd}$              | 過熱シャットダウン          |                                                     | 150  |       | °C  |

|                       | 過熱保護ヒステリシス         |                                                     | 15   |       | °C  |

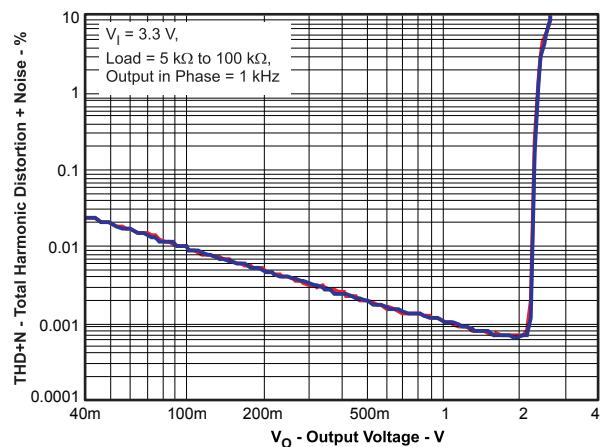

## 電気的特性、ライン・ドライバ

$PVDD\_LD = PVDD\_HP = 3.3 \text{ V}$ ,  $R_{load} = 5 \text{ k}\Omega$ ,  $R_{FB} = 20 \text{ k}\Omega$ ,  $R_{IN} = 10 \text{ k}\Omega$ ,  $T_A = 25^\circ\text{C}$ , チャージ・ポンプ :  $C_{CP\_LD} = C_{CP\_HP} = 1.0 \mu\text{F}$  (特に記述のない限り)

| パラメータ           | 測定条件                  | DRV604                                                 |      |        | 単位   |

|-----------------|-----------------------|--------------------------------------------------------|------|--------|------|

|                 |                       | 最小                                                     | 標準   | 最大     |      |

| $V_O$           | 出力電圧、出力が同相            | 1% THD+N, $f = 1 \text{ kHz}$ , 10 kΩ 負荷               |      | 2.1    | Vrms |

| THD+N           | 全高調波歪+ノイズ             | $f = 1 \text{ kHz}$ , 10 kΩ 負荷, $V_O = 2 \text{ Vrms}$ |      | 0.001% |      |

| SNR             | 信号対雑音比                | A-weighted, AES17 フィルタ、2 Vrms 基準                       | 109  |        | dB   |

| DNR             | ダイナミック・レンジ            | A-weighted, AES17 フィルタ、2 Vrms 基準                       | 109  |        | dB   |

| $V_n$           | ノイズ電圧                 | A-weighted, AES17 フィルタ                                 | 7    |        | uV   |

|                 | スルー・レート               |                                                        | 4.5  |        | V/μS |

| GBW             | ユニティ・ゲイン帯域幅           |                                                        | 8    |        | MHz  |

|                 | クロストーク - ラインL-RおよびR-L | 10 kΩ 負荷, $V_O = 2 \text{ Vrms}$                       | -100 |        | dB   |

| $V_{incm\_pos}$ | 正の同相モード入力電圧           |                                                        | +2.0 |        | V    |

| $V_{incm\_neg}$ | 負の同相モード入力電圧           |                                                        | -3.0 |        | V    |

| $I_{limit}$     | 電流制限                  | PVDD = 3.3 V                                           | 60   |        | mA   |

|                 | 最大容量性負荷               |                                                        | 220  |        | pF   |

## 電気的特性、ヘッドホン

PVDD\_LD = PVDD\_HP = 3.3 V, R<sub>HP</sub> = 32 Ω, T<sub>A</sub> = 25°C, チャージ・ポンプ : C<sub>CP\_LD</sub> = C<sub>CP\_HP</sub> = 1.0 μF (特に記述のない限り)

| パラメータ                 | 測定条件        | DRV604                                                      |    |        | 単位   |

|-----------------------|-------------|-------------------------------------------------------------|----|--------|------|

|                       |             | 最小                                                          | 標準 | 最大     |      |

| P <sub>O</sub>        | 出力電力、出力が同相  | THD+N = 1%, f = 1 kHz, 32 Ω 負荷                              |    | 40     | mW   |

| V <sub>O</sub>        | 出力電圧、出力が同相  | THD+N = 1%, f = 1 kHz, 32 Ω 負荷                              |    | 1.45   | Vrms |

| THD+N                 | 全高調波歪+ノイズ   | f = 1 kHz, 32 Ω 負荷, P <sub>O</sub> = 40 mW                  |    | 0.02%  |      |

|                       |             | f = 1 kHz, 5 kΩ 負荷, V <sub>O</sub> = 2 Vrms                 |    | 0.001% |      |

| SNR                   | 信号対雑音比      | A-weighted、AES17フィルタ、1.45Vrms基準<br>(32Ω負荷に対して66mW)          |    | 106    | dB   |

|                       |             | A-weighted、AES17フィルタ、2Vrms基準、5kΩ負荷                          |    | 109    |      |

| DNR                   | ダイナミック・レンジ  | A-weighted、AES17フィルタ、1.45Vrms基準<br>(32Ω負荷に対して66mW)          |    | 106    | dB   |

|                       |             | A-weighted、AES17フィルタ、2Vrms基準、5kΩ負荷                          |    | 109    |      |

| V <sub>n</sub>        | ノイズ電圧       | A-weighted、AES17フィルタ                                        |    | 7      | μV   |

|                       | スルー・レート     |                                                             |    | 4.5    | V/μS |

| GBW                   | ユニティ・ゲイン帯域幅 |                                                             |    | 8      | MHz  |

| クロストーク チャネル間          |             | f = 1 kHz, R <sub>load</sub> = 32 Ω, P <sub>O</sub> = 40 mW |    | 75     | dB   |

| V <sub>incm_pos</sub> | 正の同相モード入力電圧 |                                                             |    | 2.0    | V    |

| V <sub>incm_neg</sub> | 負の同相モード入力電圧 |                                                             |    | -3.0   | V    |

| I <sub>limit</sub>    | 出力電流制限      |                                                             |    | 190    | mA   |

|                       | 最大容量性負荷     |                                                             |    | 220    | pF   |

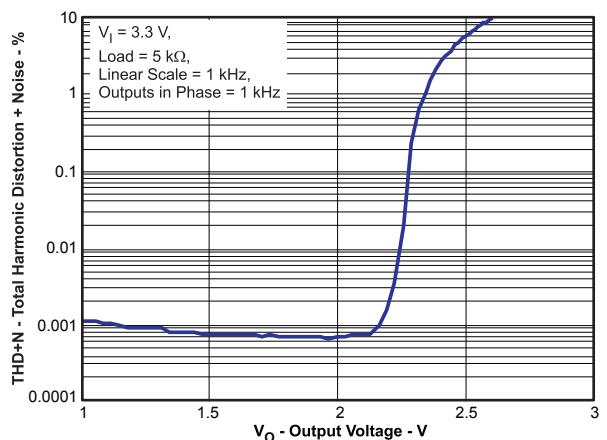

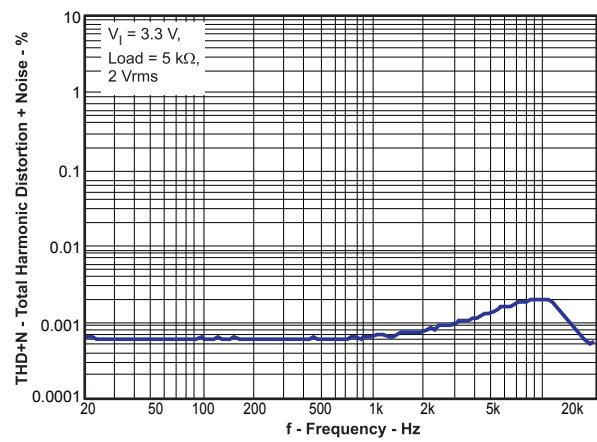

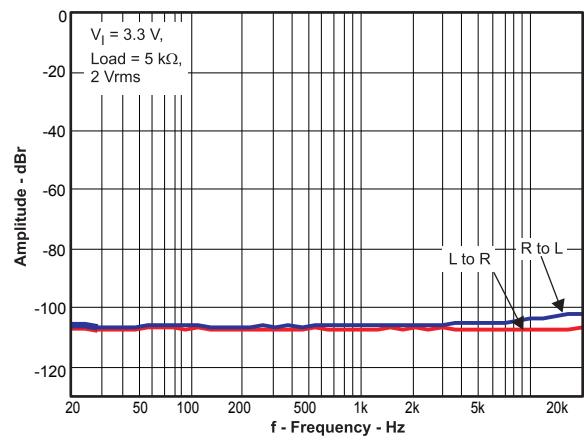

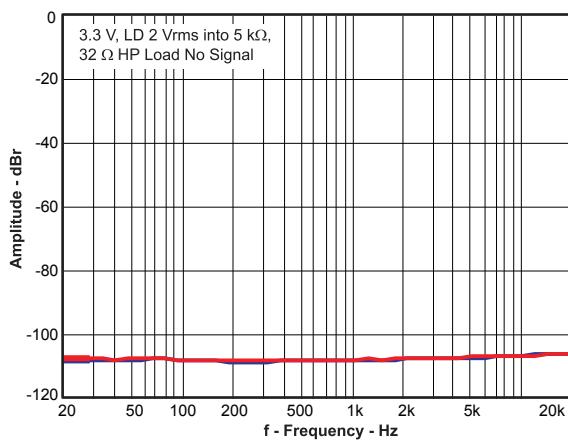

## 標準的特性、ライン・ドライバ

図1. THD+N 対 出力電圧

図2. THD+N 対 出力電圧、リニア・スケール

図3. THD+N 対 周波数

図4. チャネル・セパレーション

図5. ヘッドホン-ライン・ドライバ間クロストーク

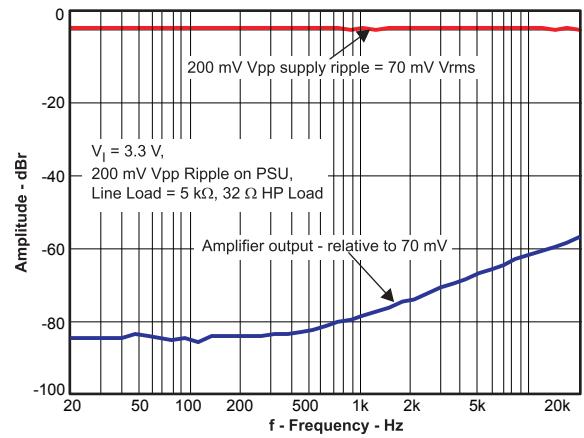

図6. AC PSRR, Ksvr

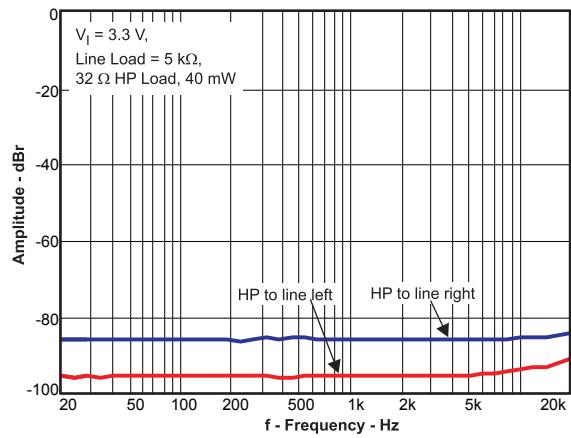

## 標準的特性、ヘッドホン

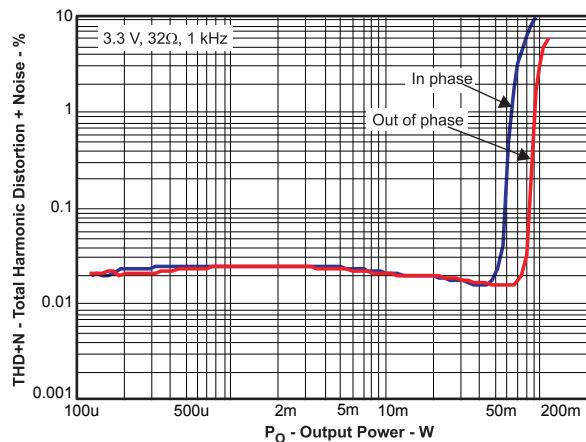

図7. THD+N 対 出力電力

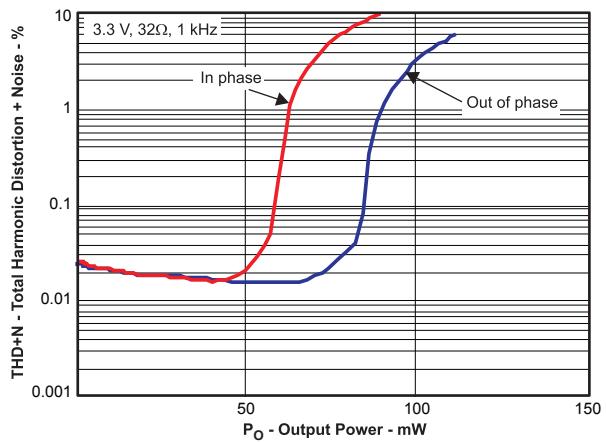

図8. THD+N 対 出力電力、リニア・スケール

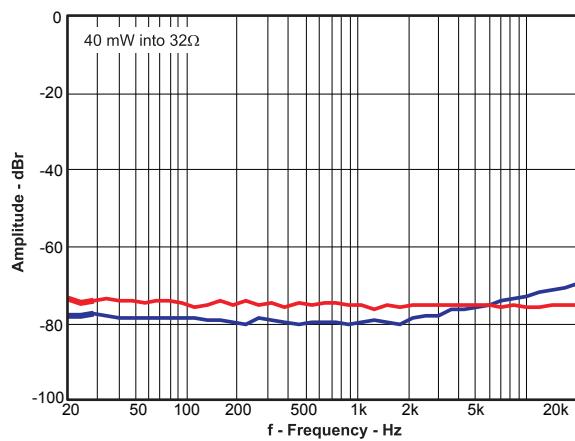

図9. チャネル・セパレーション

図10. ライン・ドライバ-ヘッドホン間クロストーク

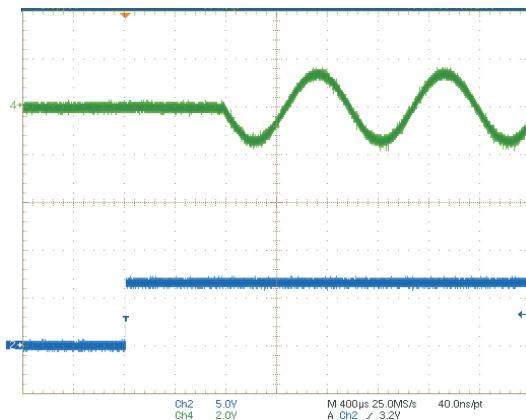

図11. 開始

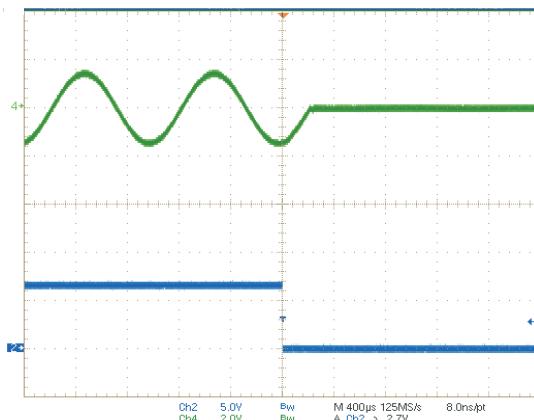

図12. 停止

## アプリケーション情報

### ライン・ドライバ・アンプ

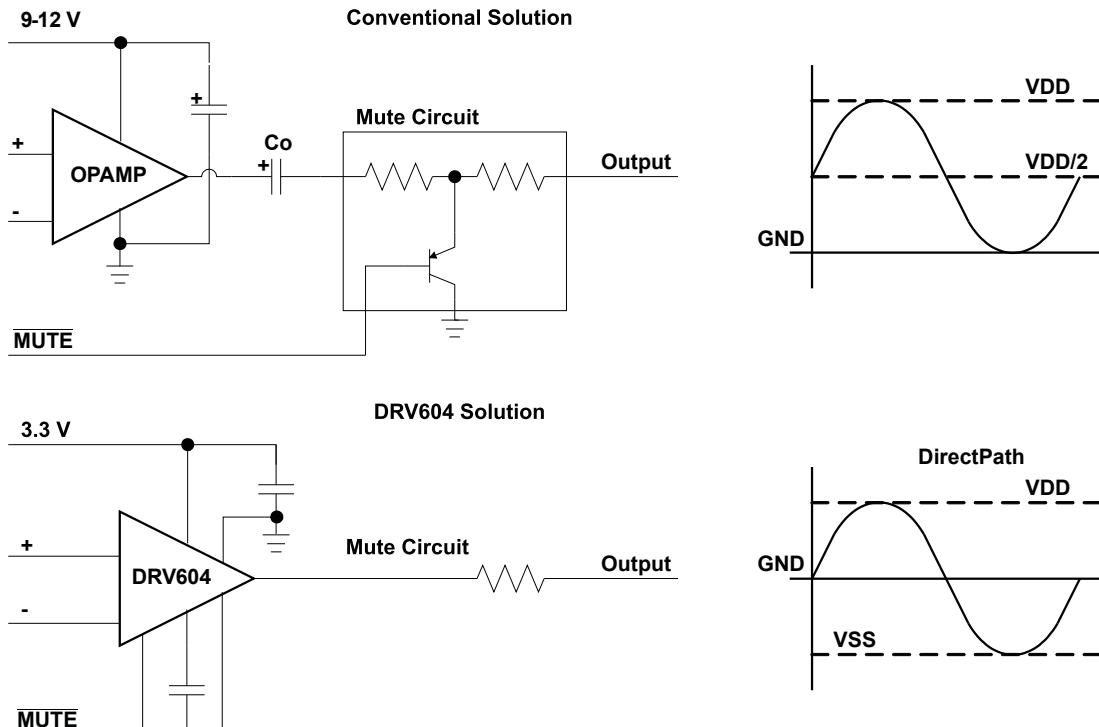

一般的な単一電源のヘッドホンおよびライン・ドライバ・アンプは、DCブロッキング・コンデンサを必要とします。図13の上側の図は、従来のライン・ドライバ・アンプでの負荷接続および出力信号を示しています。

ほとんどの場合、ヘッドホン・アンプのDCブロッキング・コンデンサは大きな値を有しています。また、ヘッドホンとライン・ドライバの両方に対して、起動時のクリック音やポップ音を最小限に抑えるためにミュート回路が必要となります。これらの出力コンデンサやミュート回路は、PCB実装領域を増やし、組み立てコストを増加させ、オーディオ出力信号の忠実度を低下させる場合もあります。

図13. 従来およびDirectPathのヘッドホン/ライン・ドライバ

DirectPath<sup>TM</sup>アンプ・アキテクチャは、単一電源で動作しますが、内部のチャージ・ポンプを使用して負の電圧レールを提供します。

ユーザが提供する正のレールとICで生成される負のレールを組み合わせることにより、デバイスは実質的な分割電源モードで動作します。

出力電圧は0Vを中心として正レールまたは負レールにスイングできます。さらに、クリック/ポップ音低減回路を内蔵することで、DirectPath<sup>TM</sup>アンプでは出力DCブロッキング・コンデンサを必要としません。

図13の下側のブロック図および波形は、グランド基準のヘッドホンおよびライン・ドライバ・アキテクチャを示しています。これがDRV604のアキテクチャです。

### 部品の選択

#### チャージ・ポンプ

チャージ・ポンプのフライング・コンデンサは、負電源電圧の生成時に電荷を転送する働きをします。最大の電荷転送を実現するには、PVSSコンデンサの容量がチャージ・ポンプ・コンデンサの容量以上である必要があります。低ESRのコンデンサが理想的であり、値は1μFが標準です。ヘッドホン部に対しては、1μFより小さいコンデンサ値は推奨できません。これは、低インピーダンス負荷での負電圧スイングが制限されるためです。

## デカップリング・コンデンサ

DRV604は、DirectPath™アンプであり、ノイズと全高調波歪（THD）を低減するために適切な電源デカップリングを必要とします。等価直列抵抗（ESR）の低いセラミック・コンデンサ（標準で $1\mu\text{F}$ ）をデバイスのPVDDリードにできる限り近づけて配置するのが最適です。このデカップリング・コンデンサをDRV604の近くに配置することは、アンプの性能にとって重要です。より低い周波数のノイズ信号をフィルタリングするために、 $10\mu\text{F}$ 以上のコンデンサをオーディオ・パワー・アンプの近くに配置することも有用ですが、このデバイスではPSRRが高いため、ほとんどのアプリケーションではこのコンデンサは不要です。

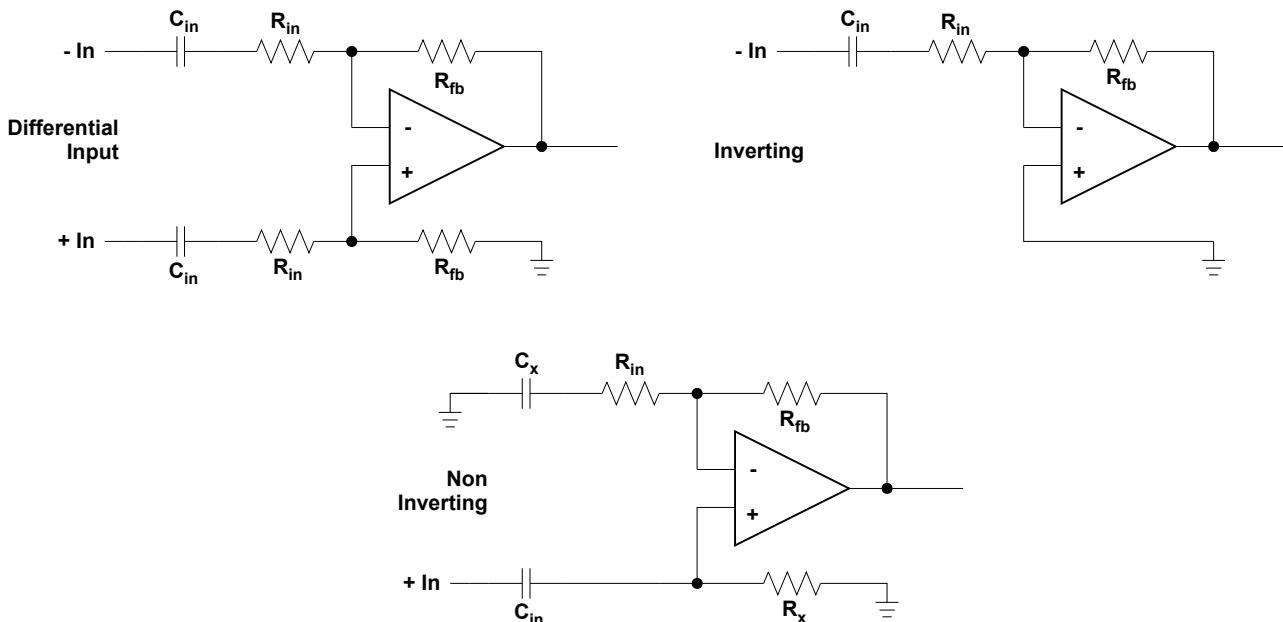

## ゲイン設定抵抗の範囲

ゲイン設定抵抗 $R_{in}$ および $R_{fb}$ は、DRV604のノイズ、安定性、および入力コンデンサ・サイズが許容制限内に収まるよう選択する必要があります。電圧ゲインは、 $R_{fb}$ を $R_{in}$ で割った値として定義されます。選択する値が低すぎると、大きな入力AC結合コンデンサ $C_{IN}$ が必要になります。選択する値が高すぎると、アンプのノイズが増加します。表1に、各ゲイン設定に対して推奨される抵抗値を示します。

表1. 推奨抵抗値

| 入力抵抗値、 $R_{in}$ | 帰還抵抗値、 $R_{fb}$ | 差動入力ゲイン  | 反転入力ゲイン   | 非反転入力ゲイン |

|-----------------|-----------------|----------|-----------|----------|

| 10 kΩ           | 10 kΩ           | 1.0 V/V  | -1.0 V/V  | 2.0 V/V  |

| 10 kΩ           | 15 kΩ           | 1.5 V/V  | -1.5 V/V  | 2.5 V/V  |

| 10 kΩ           | 20 kΩ           | 2.0 V/V  | -2.0 V/V  | 3.0 V/V  |

| 4.7 kΩ          | 47 kΩ           | 10.0 V/V | -10.0 V/V | 11.0 V/V |

図14. 差動、反転、および非反転ゲイン構成

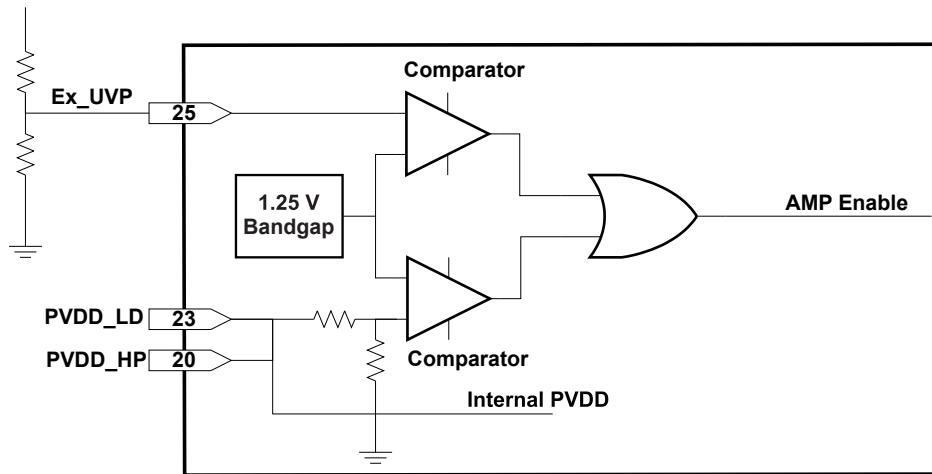

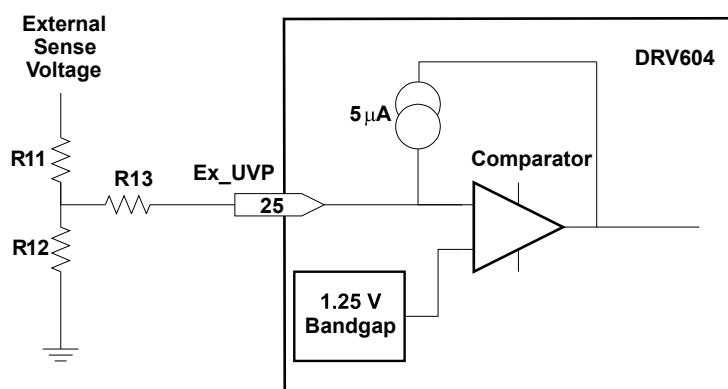

## 内部および外部低電圧検出とRESET出力

DRV604には、内部に高精度のバンドギャップ・リファレンス電圧と2つのコンパレータが搭載されています。1つは電源電圧PVDD\_LDおよびPVDD\_HPの監視に使用され、もう1つはピン25のユーザが選択可能な外部電圧の監視に使用されます。内部PVDD監視は、2.8V（ヒステリシス200mV）に設定されています。

外部低電圧検出を使用して、入力デバイスにポップ音が発生する前にDRV604をシャットダウンすることができます。Ex\_UVPピンのシャットダウン・スレッシュホールドは1.25Vです。分圧抵抗を使用して、アプリケーションに適したシャットダウン・スレッシュホールドおよびヒステリシスを設定できます。

選択するスレッシュホールドは次のように求めることができます。

$$V_{UVP} = 1.25 \text{ V} \times \frac{(R_{11} + R_{12})}{R_{12}} \quad (1)$$

$$V_{Hysteresis} = 5 \mu\text{A} \times R_{13} \times \left( \frac{R_{11}}{R_{12}} + 1 \right) \quad (2)$$

ここで、 $R_{13} \gg R_{11}||R_{12}$  です。

例えば、 $V_{UVP}=4.5\text{V}$ でヒステリシスを400mVに設定するには、 $R_{11}=10\text{k}\Omega$ 、 $R_{12}=3\text{k}\Omega$ 、および $R_{13}=22\text{k}\Omega$ を使用します。

電源のスパイクやノイズをフィルタリングするには、 $R_{12}$ と並列にコンデンサを追加できます。

### 入力ブロッキング・コンデンサ

DRV604の入力ピンへのオーディオ信号と直列に、DC入力ブロッキング・コンデンサを追加する必要があります。これらのコンデンサは、オーディオ・ソースのDC成分をブロックし、DRV604の入力を適切にバイパスして性能を最大限に高めます。また、入力ブロッキング・コンデンサはDCゲインを1に制限し、出力のDCオフセット電圧を制限します。

これらのコンデンサは、入力抵抗 $R_{in}$ とハイパス・フィルタを形成します。カットオフ周波数は、式1で計算されます。この計算で使用されている容量は、入力ブロッキング・コンデンサであり、抵抗は表1から選択された入力抵抗です。それにより、周波数および容量は、いずれか一方の値が与えられれば求めることができます。

$$f_{C_{in}} = \frac{1}{2\pi \times R_{in} \times C_{in}} \quad C_{in} = \frac{1}{2\pi \times f_{C_{in}} \times R_{in}} \quad (3)$$

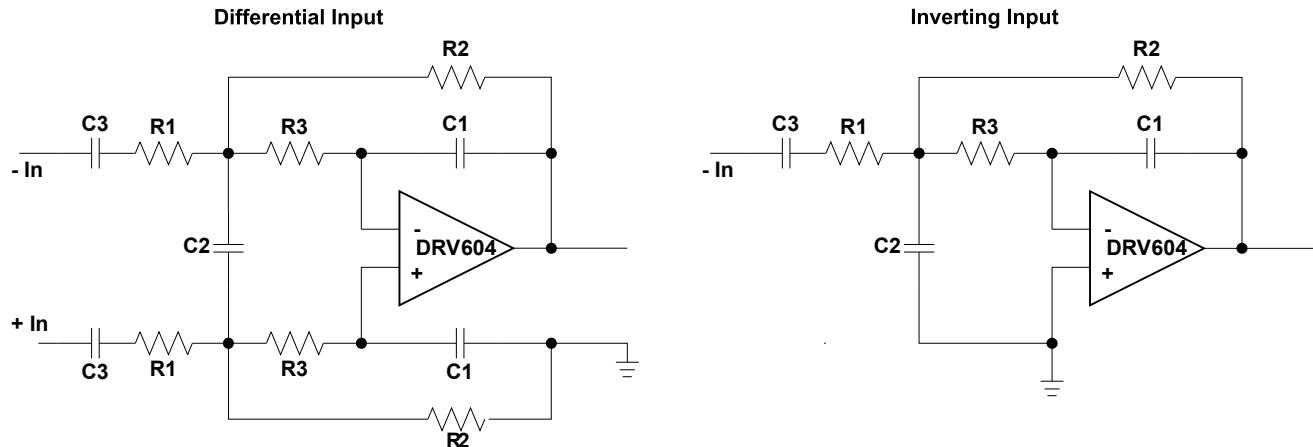

## RV604を2次フィルタとして使用

最近のオーディオDACの一部は、帯域外ノイズを除去するために外部ローパス・フィルタを必要とします。これは、標準的なオペアンプのように使用できるDRV604にもあてはまる可能性があります。いくつかのフィルタ・トポロジはシングルエンドと差動の両方で実装できます。下の図は、差動入力とシングルエンド入力のマルチ・フィードバック (MFB) 型を示しています。

ソースからのDC成分を除去するAC結合コンデンサが示されています。これは、ソースからのすべてのDC成分をブロッキングとともに、DCゲインを1に制限することで、出力DCオフセットを最小限に抑える働きをします。

各部品値は、次のWebサイトで提供されているTIのFilterPro™プログラムによって計算できます。

<http://focus.ti.com/docs/tools/folders/print/filterpro.html>

図15. 2次アクティブ・ローパス・フィルタ

抵抗値は、ノイズ低減のために小さくする必要がありますが、AC結合コンデンサのサイズを小さくするためには、ある程度大きい必要があります。C2は、中点をGNDに接続して2つに分割できます。それにより、同相モードの減衰が大きくなる場合があります。

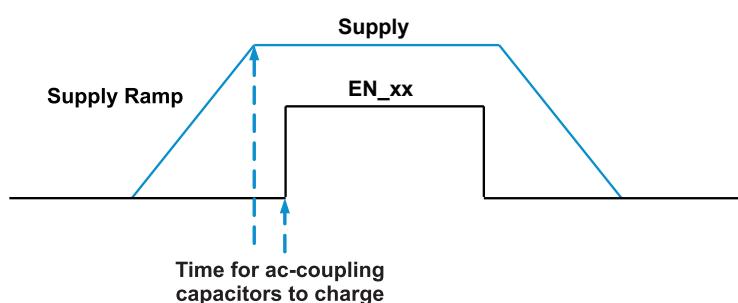

## ポップフリー・パワーアップ

電源電圧の上昇中または下降中にEN\_LDおよびEN\_HPまたはEx\_UVPを“Low”に保持することで、ポップフリー・パワーアップを保証できます。EN\_xxピンを“High”にアサートする前に、入力AC結合コンデンサが完全に充電されるまで、これらのピンを“Low”に保持する必要があります。それにより、AC結合の適切なプリチャージが行われ、ポップ音のないパワーアップが実現されます。図16に、推奨シーケンスを示します。

図16. パワーアップ/ダウン・シーケンス

## デュアル・ステレオ・ライン・ドライバ

DRV604のヘッドホン・ステレオ・アンプは、ライン・ドライバとしても使用でき、 $5\text{k}\Omega$ の負荷インピーダンス駆動条件にてライン・アンプと同じ高出力電圧能力を提供します。これにより、DRV604は、液晶テレビのデュアルSCART出力のようなアプリケーションに最適です。また、DVDやBlue-rayプレーヤーなどの複数ライン出力で、2個のDRV604を使用すれば、非常にスペース効率の良い8チャネル・ライン出力を実現できます。

### 容量性負荷

DRV604は、 $220\text{pF}$ までの高い容量性負荷を直接ドライブできます。それより高い容量性負荷は、ライン・ドライバ出力に対して $47\text{\Omega}$ 以上の出力直列抵抗を追加することで対応できます。

### レイアウトに関する推奨事項

DRV604EVMユーザ・ガイド (SLOU288) にDRV604の推奨レイアウトが記載されています。また、Gerberファイルをwww.ti.comからダウンロードできます。DRV604製品フォルダを開いて、Tools and Softwareフォルダを参照してください。

ゲイン設定抵抗 $R_{in}$ および $R_{fb}$ は、入力ピンの近くに配置する必要があります。それにより、これらの入力ピンの容量性負荷が最小限に抑えられ、DRV604の安定性を最大限に確保できます。

ハム干渉を最小限に抑えるため、グランド・パターンはスター・グランドとして配線することを推奨します。

PVDD、PVSSデカッピング・コンデンサ、およびチャージ・ポンプ・コンデンサは、短いパターンで接続する必要があります。

### DRV603と互換性のあるフットプリント

DRV604のステレオ・ライン・ドライバ部は、DRV603とピン・コンパチブルです。したがって、スタッフィング・オプションにより1つのPCBレイアウトで異なる出力構成が可能です。

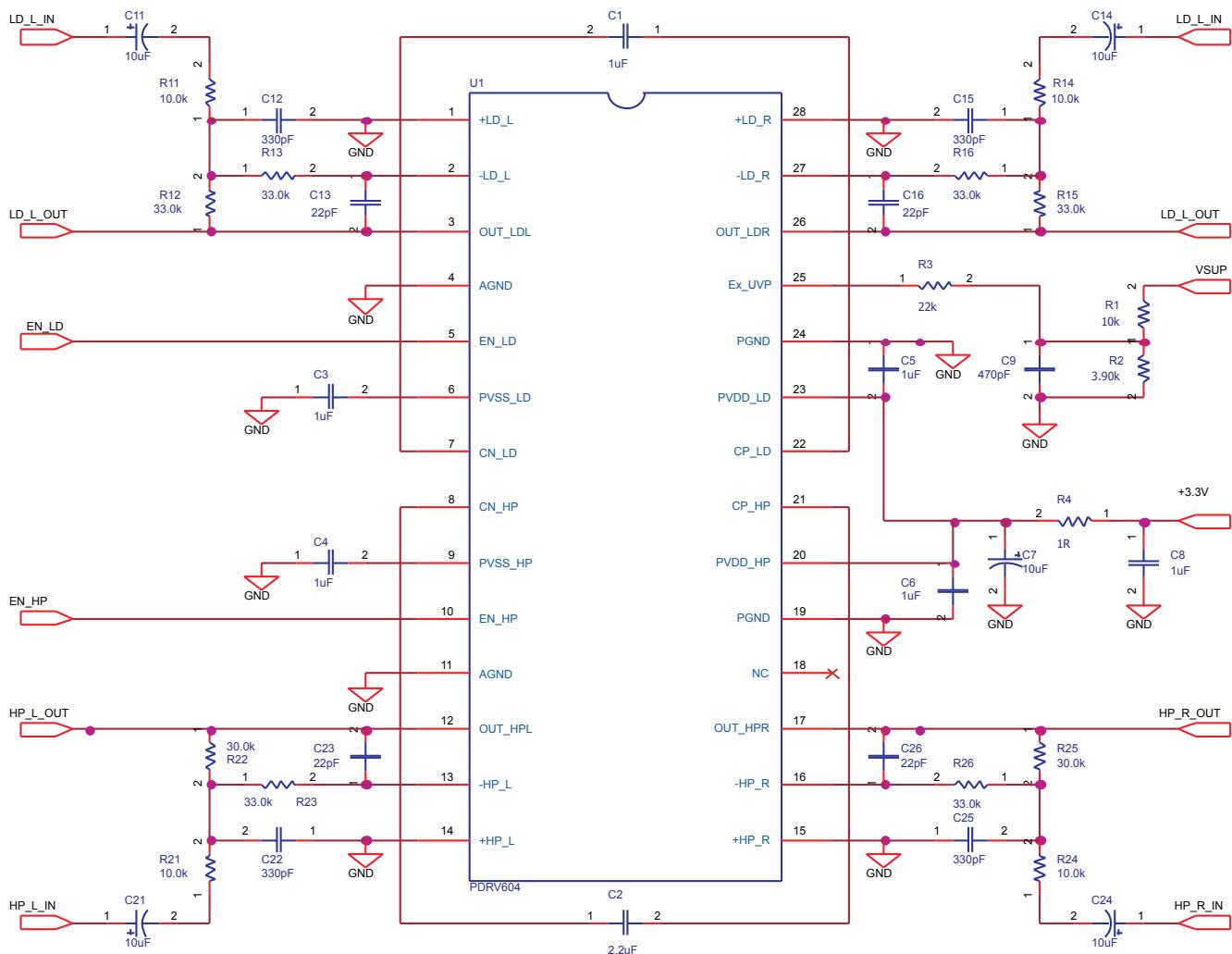

## アプリケーション回路

シングルエンド入力および出力、ライン部のゲインは3.3x、ヘッドホン部のゲインは3x。AC結合入力、ハイパス極1.6Hz、2次ローパス・フィルタ50kHz。

## パッケージ情報

| Orderable Device | Status <sup>(1)</sup> | Package Type | Package Drawing | Pins | Package Qty | Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|--------------|-----------------|------|-------------|-------------------------|------------------|------------------------------|

| DRV604PWP        | ACTIVE                | HTSSOP       | PWP             | 28   | 50          | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-3-260C-168 HR          |

| DRV604PWPR       | ACTIVE                | HTSSOP       | PWP             | 28   | 2000        | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-3-260C-168 HR          |

(1) マーケティング・ステータスは次のように定義されています。

ACTIVE : 製品デバイスが新規設計用に推奨されています。

LIFEBUY : TI によりデバイスの生産中止予定が発表され、ライフタイム購入期間が有効です。

NRND : 新規設計用に推奨されていません。デバイスは既存の顧客をサポートするために生産されていますが、TI では新規設計にこの部品を使用することを推奨していません。

PREVIEW : デバイスは発表済みですが、まだ生産が開始されていません。サンプルが提供される場合と、提供されない場合があります。

OBSOLETE : TI によりデバイスの生産が中止されました。

(2) エコ・プラン - 環境に配慮した製品分類プランであり、Pb-Free (RoHS)、Pb-Free (RoHS Expert) および Green (RoHS & no Sb/Br) があります。最新情報および製品内容の詳細については、<http://www.ti.com/productcontent> でご確認ください。

TBD : Pb-Free/Green 変換プランが策定されていません。

Pb-Free (RoHS) : TI における “Lead-Free” または “Pb-Free” (鉛フリー) は、6 つの物質すべてに対して現在の RoHS 要件を満たしている半導体製品を意味します。これには、同種の材質内で鉛の重量が 0.1% を超えないという要件も含まれます。高温で半田付けするように設計されている場合、TI の鉛フリー製品は指定された鉛フリー・プロセスでの使用に適しています。

Pb-Free (RoHS Exempt) : この部品は、1) ダイとパッケージの間に鉛ベースの半田バンプ使用、または 2) ダイとリードフレーム間に鉛ベースの接着剤を使用、が除外されています。それ以外は上記の様に Pb-Free (RoHS) と考えられます。

Green (RoHS & no Sb/Br) : TI における “Green” は、“Pb-Free” (RoHS 互換) に加えて、臭素 (Br) およびアンチモン (Sb) をベースとした難燃材を含まない(均質な材質中の Br または Sb 重量が 0.1% を超えない)ことを意味しています。

(3) MSL、ピーク温度 -- JEDEC 業界標準分類に従った耐湿性レベル、およびピーク半田温度です。

重要な情報および免責事項：このページに記載された情報は、記載された日付時点での TI の知識および見解を表しています。TI の知識および見解は、第三者によって提供された情報に基づいており、そのような情報の正確性について何らの表明および保証も行うものではありません。第三者からの情報をより良く統合するための努力は続けております。TI では、事実を適切に表す正確な情報を提供すべく妥当な手順を踏み、引き続きそれを継続してゆきますが、受け入れる部材および化学物質に対して破壊試験や化学分析は実行していない場合があります。TI および TI 製品の供給者は、特定の情報を機密情報として扱っているため、CAS 番号やその他の制限された情報が公開されない場合があります。

いかなる場合においても、そのような情報から生じた TI の責任は、このドキュメント発行時点での TI 製品の価格に基づく TI から顧客への合計購入価格（年次ベース）を超えることはありません。

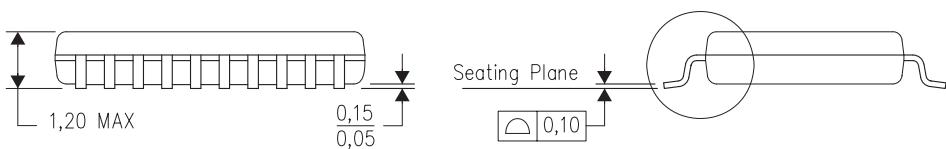

20 PIN SHOWN

| PINS **<br>DIM | 14   | 16   | 20   | 24   | 28   |

|----------------|------|------|------|------|------|

| A MAX          | 5,10 | 5,10 | 6,60 | 7,90 | 9,80 |

| A MIN          | 4,90 | 4,90 | 6,40 | 7,70 | 9,60 |

4073225/H 12/05

## 注記 :

- A. 全ての線寸法の単位はミリメートルです。

- B. 図は予告なく変更することがあります。

- C. このパッケージは、基板上のサーマル・パッドに半田付けされるように設計されています。推奨基板レイアウトについては、テクニカル・ブリーフ『PowerPAD Thermally Enhanced Package』(TI 文献番号 SLMA002) を参照してください。これらのドキュメントは、ホームページ [www.ti.com](http://www.ti.com) で入手できます。

- D. JEDEC MO-153 に準拠しています。

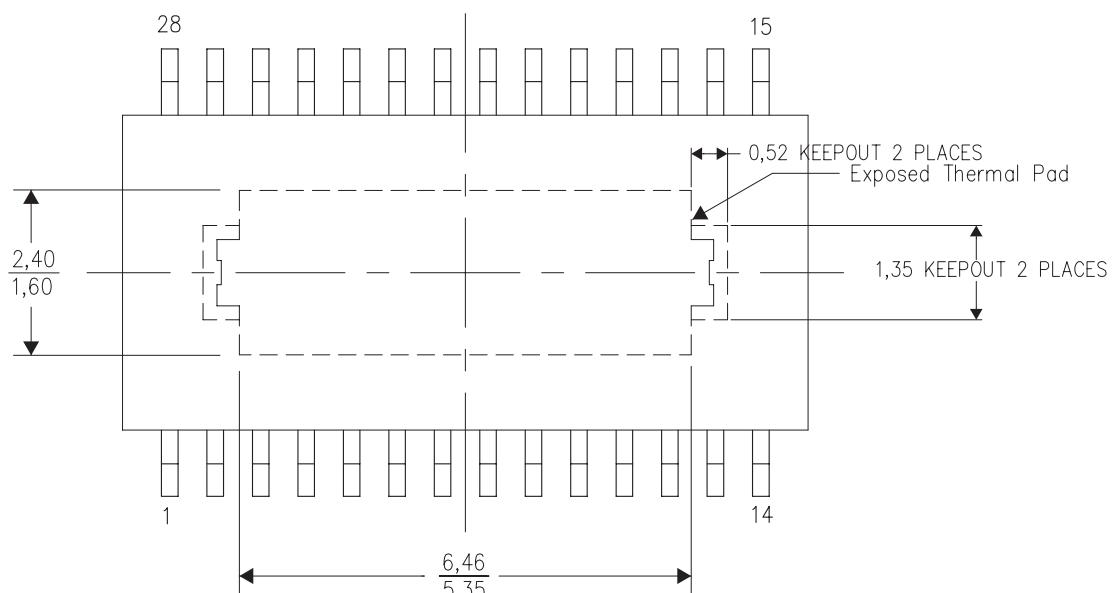

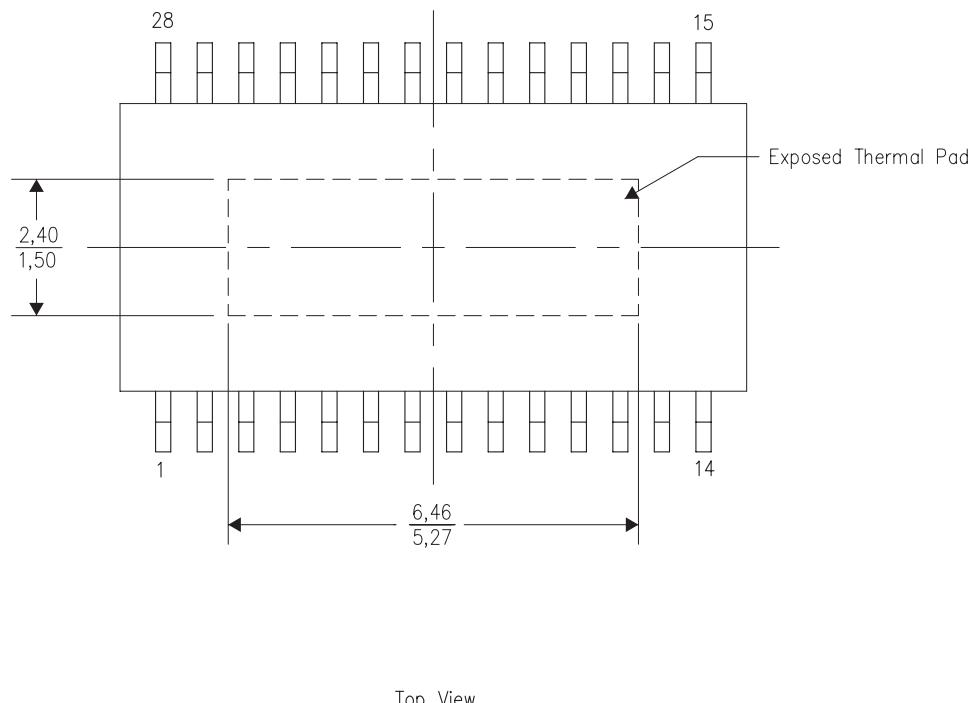

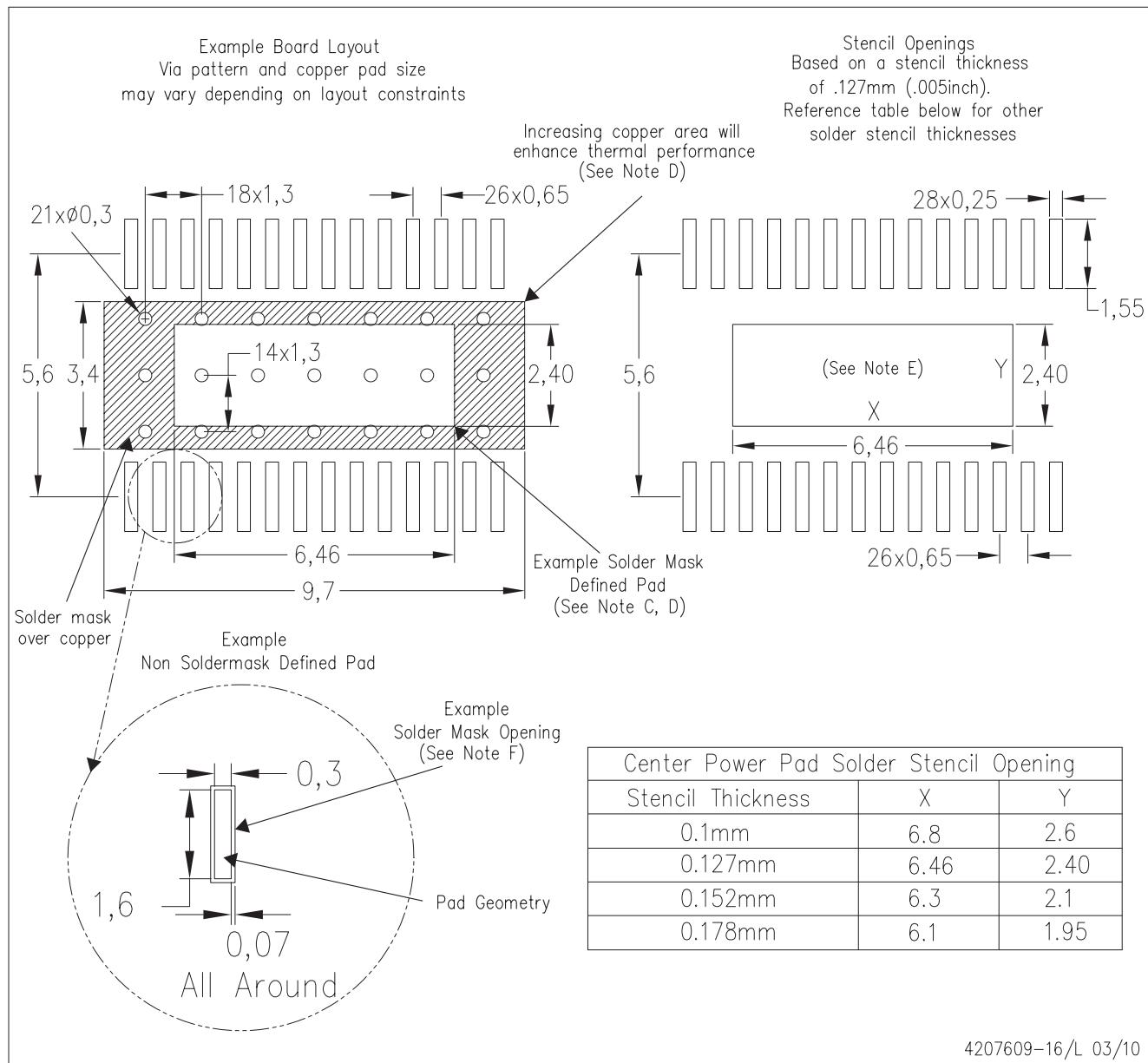

## サーマル・インフォメーション

このPowerPAD™パッケージには、外付けヒートシンクに直に取り付けるように設計された露出放熱パッドを備えています。放熱パッドは、プリント基板（PCB）に直接半田付けしなくてはなりません。半田付け終了後、PCBはヒートシンクとして使用可能です。さらに、サーマル・ピアを使用することで、放熱パッドは、デバイス用の電気回路図に示すように適正な銅プレーンに直に取り付けることができ、あるいは、PCB内に組み込むような特殊ヒートシンク構造に取り付けることができます。この設計により、集積回路（IC）からの熱移動を最適化します。

PowerPADパッケージおよびその放熱機能の利用方法に関する追加情報については、技術資料、TI文献番号SLMA002、PowerPAD Thermally Enhanced Packageおよびアプリケーション資料、TI文献番号SLMA004、PowerPAD Made Easyをご覧ください。両文献は、[www.ti.com](http://www.ti.com)にて入手可能です。

本パッケージ用の露出放熱パッドの寸法は、以下のイラストに記しています。

Top View

注記：

長さ寸法の単位すべてはミリメートルです。

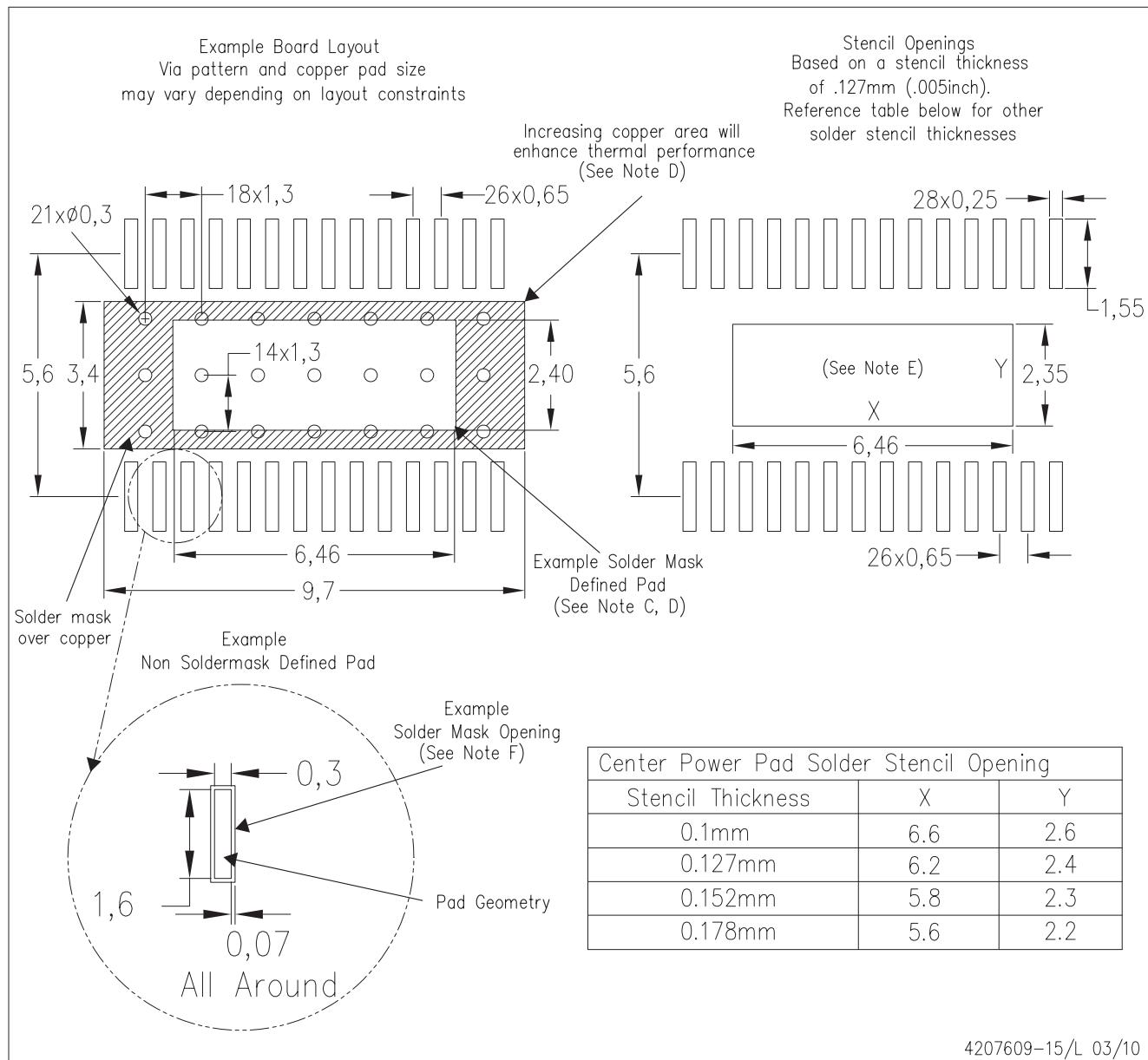

## 露出放熱パッド寸法

## 注記:

- A. 全ての線寸法の単位はミリメートルです。

- B. 図は予告なく変更することがあります。

- C. 中央の半田マスク定義パッドを変更しないように、回路基板組み立て図に注記を書き込んでください。

- D. このパッケージは、基板上のサーマル・パッドに半田付けされるように設計されています。推奨基板レイアウトについては、テクニカル・ブリーフ『PowerPAD Thermally Enhanced Package』(TI 文献番号 SLMA002) を参照してください。これらのドキュメントは、ホームページ [www.ti.com](http://www.ti.com) で入手できます。

- E. レーザ切断開口部の壁面を台形にし、角に丸みをつけることで、ペーストの離れがよくなります。ステンレス設計要件については、基盤組み立て拠点にお問い合わせください。例に示したステンシル設計は、50% 容積のメタルロード半田ペーストに基づいています。ステンシルに関するほかの推奨事項については、IPC-7525 を参照してください。

- F. 信号パッド間および信号パッド周囲の半田マスク許容差については、基盤組み立て拠点にお問い合わせください。

PowerPAD は、テキサス・インスツルメンツの商標です。

## サーマル・インフォメーション

このPowerPAD™パッケージには、外付けヒートシンクに直に取り付けるように設計された露出放熱パッドを備えています。放熱パッドは、プリント基板（PCB）に直接半田付けしなくてはなりません。半田付け終了後、PCBはヒートシンクとして使用可能です。さらに、サーマル・ピアを使用することで、放熱パッドは、デバイス用の電気回路図に示すように適正な銅プレーンに直に取り付けることができ、あるいは、PCB内に組み込むような特殊ヒートシンク構造に取り付けることができます。この設計により、集積回路（IC）からの熱移動を最適化します。

PowerPADパッケージおよびその放熱機能の利用方法に関する追加情報については、技術資料、TI文献番号SLMA002、PowerPAD Thermally Enhanced Packageおよびアプリケーション資料、TI文献番号SLMA004、PowerPAD Made Easyをご覧ください。両文献は、[www.ti.com](http://www.ti.com)にて入手可能です。

本パッケージ用の露出放熱パッドの寸法は、以下のイラストに記しています。

注記：

長さ寸法の単位すべてはミリメートルです。

## 露出放熱パッド寸法

## 注記 :

- A. 全ての線寸法の単位はミリメートルです。

- B. 図は予告なく変更することがあります。

- C. xx

- D. このパッケージは、基板上のサーマル・パッドに半田付けされるように設計されています。推奨基板レイアウトについては、テクニカル・ブリーフ TI 文献番号 SLMA002、SLMA004 を参照してください。これらのドキュメントは、ホームページ [www.ti.com](http://www.ti.com) で入手できます。代替設計については、資料 IPC-7351 を推奨します。

- E. 信号パッド間および信号パッド周囲の半田マスク許容差については、基盤組み立て拠点にお問い合わせください。

PowerPAD は、テキサス・インスツルメンツの商標です。

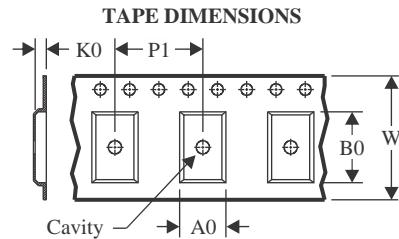

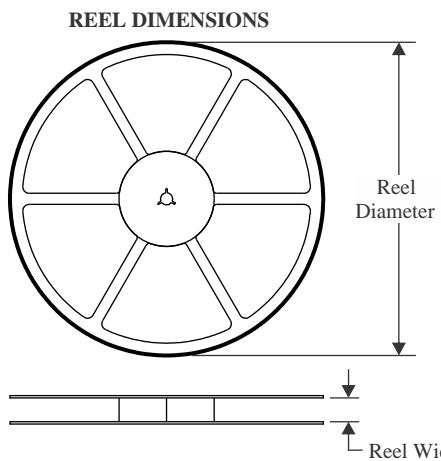

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

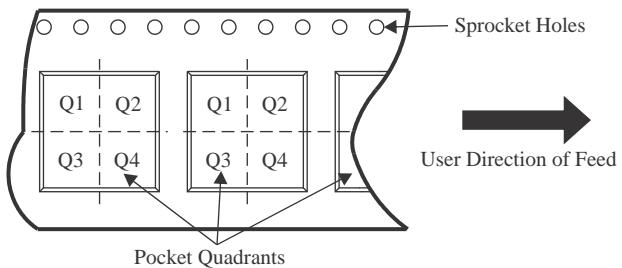

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device     | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| DRV604PWPR | HTSSOP       | PWP             | 28   | 2000 | 330.0              | 16.4               | 6.9     | 10.2    | 1.8     | 12.0    | 16.0   | Q1            |

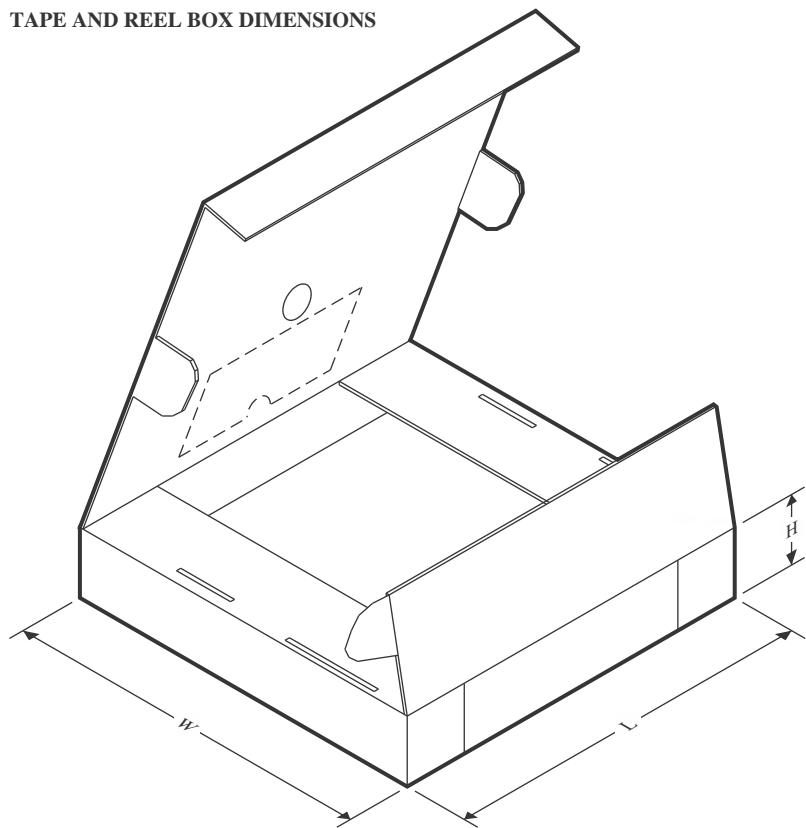

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device     | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------|--------------|-----------------|------|------|-------------|------------|-------------|

| DRV604PWPR | HTSSOP       | PWP             | 28   | 2000 | 350.0       | 350.0      | 43.0        |

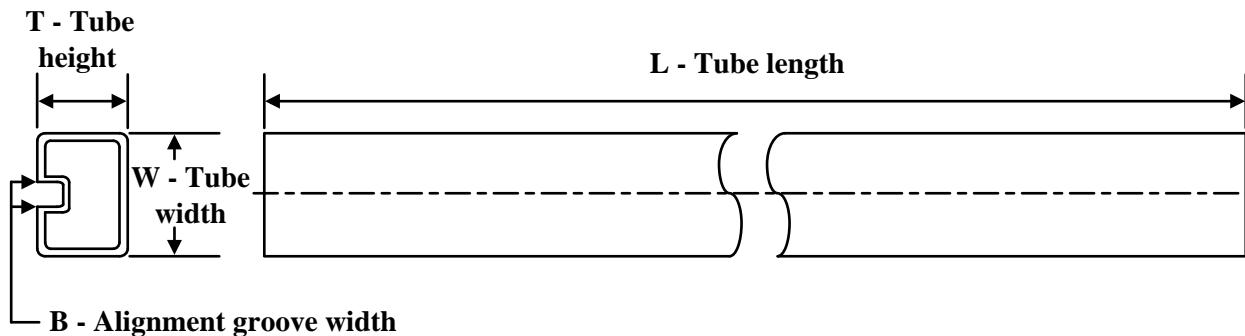

## TUBE

\*All dimensions are nominal

| Device      | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T ( $\mu$ m) | B (mm) |

|-------------|--------------|--------------|------|-----|--------|--------|--------------|--------|

| DRV604PWP   | PWP          | HTSSOP       | 28   | 50  | 530    | 10.2   | 3600         | 3.5    |

| DRV604PWP.A | PWP          | HTSSOP       | 28   | 50  | 530    | 10.2   | 3600         | 3.5    |

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月