# DRV8452 : 50V、5A ステッパ・モーター・ドライバ、高効率およびノイズレス動作

## 1 特長

- ステッパ・モーター・ドライバ

- STEP/DIR ピン付きの SPI または H/W インターフェイス

- 最高 **1/256** のマイクロステッピング・インデクサ

- **4.5V~48V** の動作電源電圧範囲

- 標準の 24V、36V レールをサポート

- 低い  $R_{DS(ON)}$ : 24V、25°C で **100mΩ** HS + LS

- ブリッジごとの大電流能力:

- DDW パッケージ: **5A** フルスケール、3.5A RMS

- PWP パッケージ: **4A** フルスケール、2.8A RMS

- DDW パッケージは次のデバイスとピン互換

- **DRV8462/61**: 65V、3~10A

- PWP パッケージは次のデバイスとピン互換

- SPI インターフェイス: **DRV8434S**: 48V、2.5A

- H/W インターフェイス: **DRV8424/26**: 33V、1.5~2.5A

- 電流検出およびレギュレーション機能を内蔵

- **5%** のフルスケール電流精度

- スマート・チューンと混合減衰のレギュレーション・オプション

- サイレント・ステップ減衰モードは静止時および低速時のサイレント動作に使用

- 自動マイクロステッピング・モードはステップ周波数補間に使用

- カスタマイズ可能なマイクロステッピング・インデクサの表

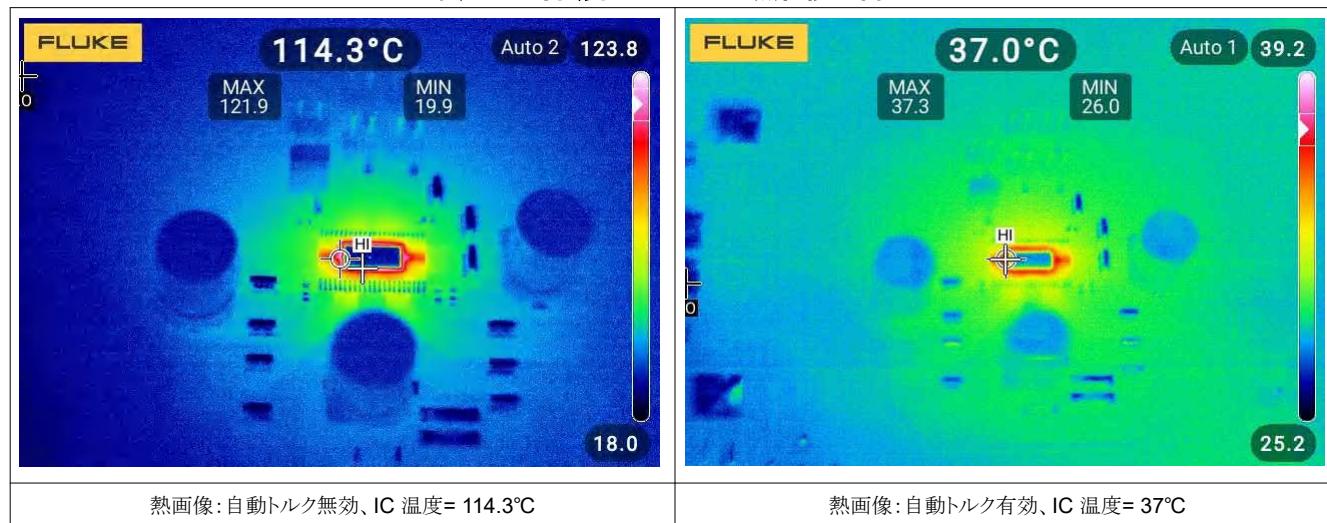

- 自動トルクは負荷に依存する電流制御に使用

- 静止電力節約モード

- 1.8V、3.3V、5.0V のロジック入力をサポート

- 低消費電流のスリープ・モード (**3μA**)

- 独立のロジック電源電圧 (**VCC**)

- 保護および診断機能

- センサレスのストール検出

- VM 低電圧誤動作防止 (UVLO)

- 開放負荷検出 (OL)

- 過電流保護 (OCP)

- サーマル・シャットダウン (OTSD)

- フォルト条件出力 (**nFAULT**)

- インデクサのゼロ位置出力 (**nHOME**)

## 2 アプリケーション

- 繊維機械、ミシン

- ファクトリ・オートメーション、ステッパ・ドライブ、ロボット

- 医療用画像処理、診断、および機器

- 舞台照明

- ATM、貨幣計数機

- PLC、DCS、PAC

- マルチファンクション・プリンタ

- 3D プリンタ

- 屋外 IP カメラ

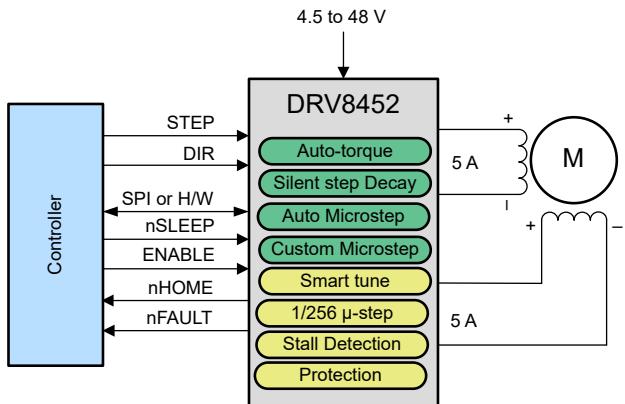

## 3 概要

DRV8452 は、広い電圧範囲、大電力、高性能のステッパ・モーター・ドライバです。このデバイスは最大 **48V** の電源電圧をサポートし、**100mΩ** の HS + LS オン抵抗を持つ MOSFET を内蔵しているため、最大 **5A** の電流を供給できます。

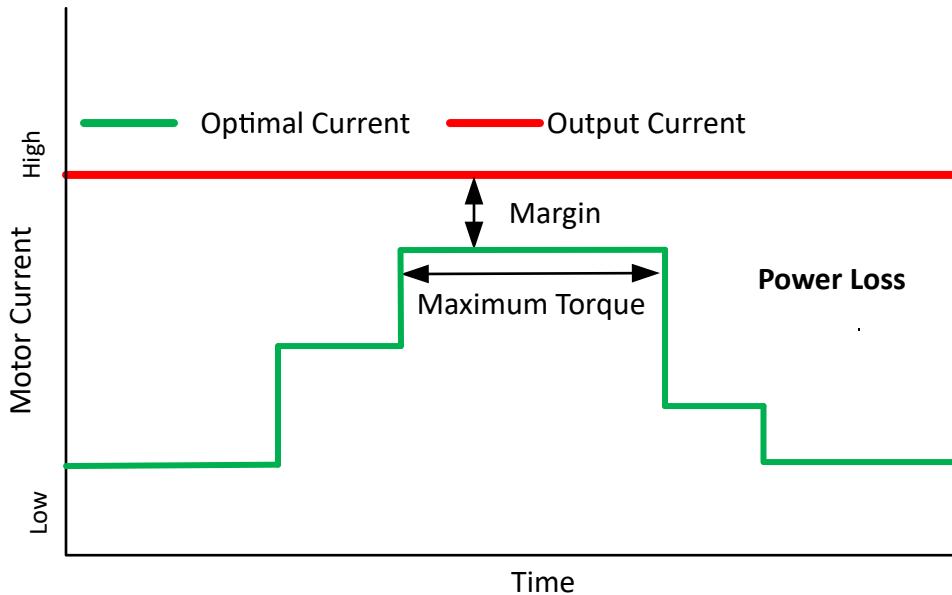

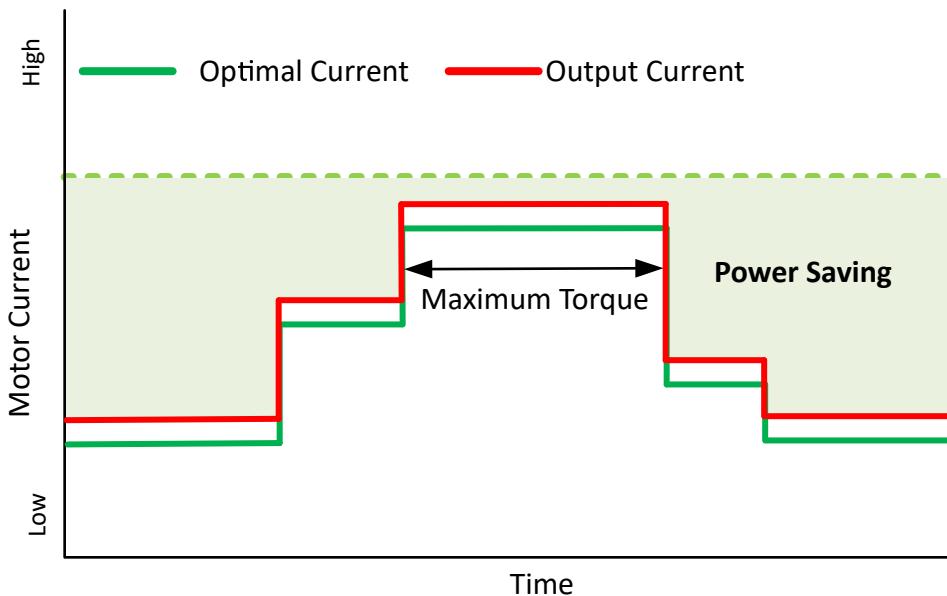

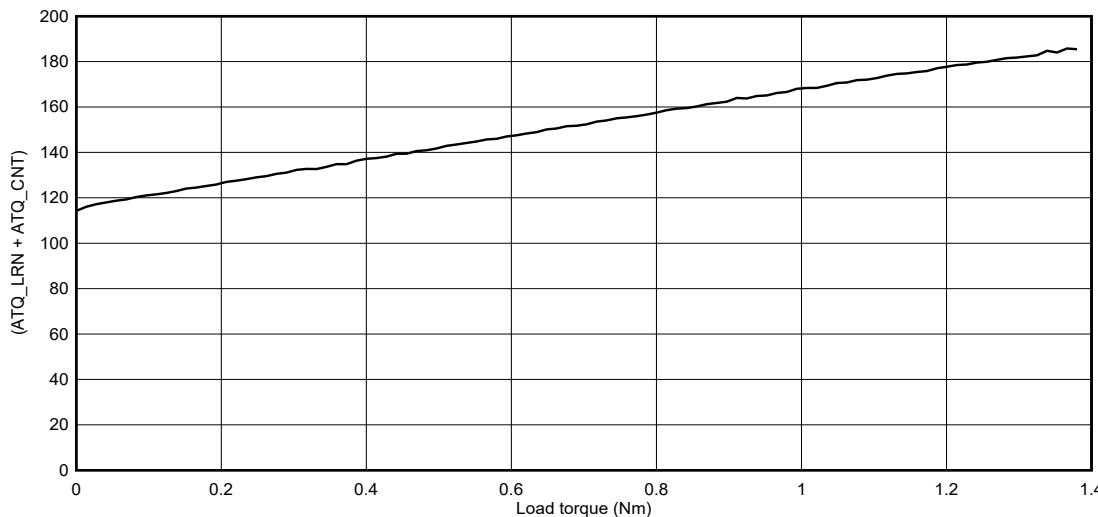

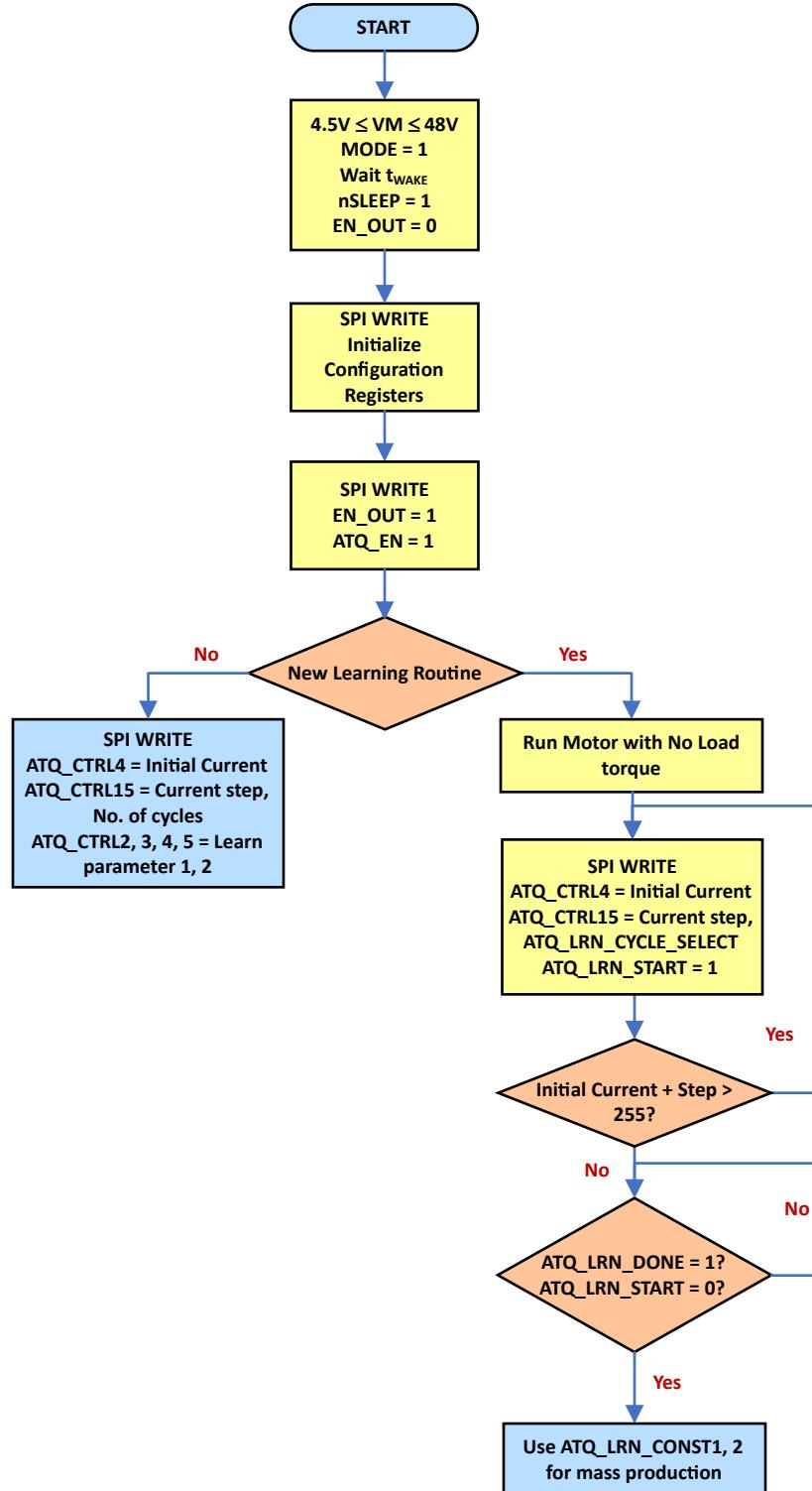

自動トルク機能により、負荷トルクに応じて電流を調整することで、効率が向上します。静止電力節約モードにより、モーターの保持状態での電力損失が低減されます。サイレント・ステップにより、低速および静止時にノイズのない動作が保証されます。電流検出機能を内蔵しており、外付けの検出抵抗が不要になるため、PCB の面積とコストを削減できます。内蔵のインデクサは最大 **1/256** のマイクロステッピングをサポートし、自動マイクロステッピング・モードで入力ステップ信号を補間することにより、コントローラのオーバーヘッドを低減します。センサレスのストール検出により、システムでのエンド・ストップが不要になります。このデバイスは、他の保護および診断機能をサポートしており、堅牢で信頼性の高い動作を実現します。

DRV8452 は、最小限の調整で機能を構成できます。外付け FET ドライバよりも高い電力密度をサポートし、PCB 面積が小さくなっています。高いエネルギー効率と、高精度でノイズのない動作により、DRV8452 は高性能ステッパ・システムに理想的な選択肢です。

## 製品情報

| 部品番号         | インターフェイス    | パッケージ <sup>(1)</sup> | 本体サイズ       |

|--------------|-------------|----------------------|-------------|

| DRV8452DDWR  | SPI または H/W | HTSSOP (44)          | 14 × 6.1mm  |

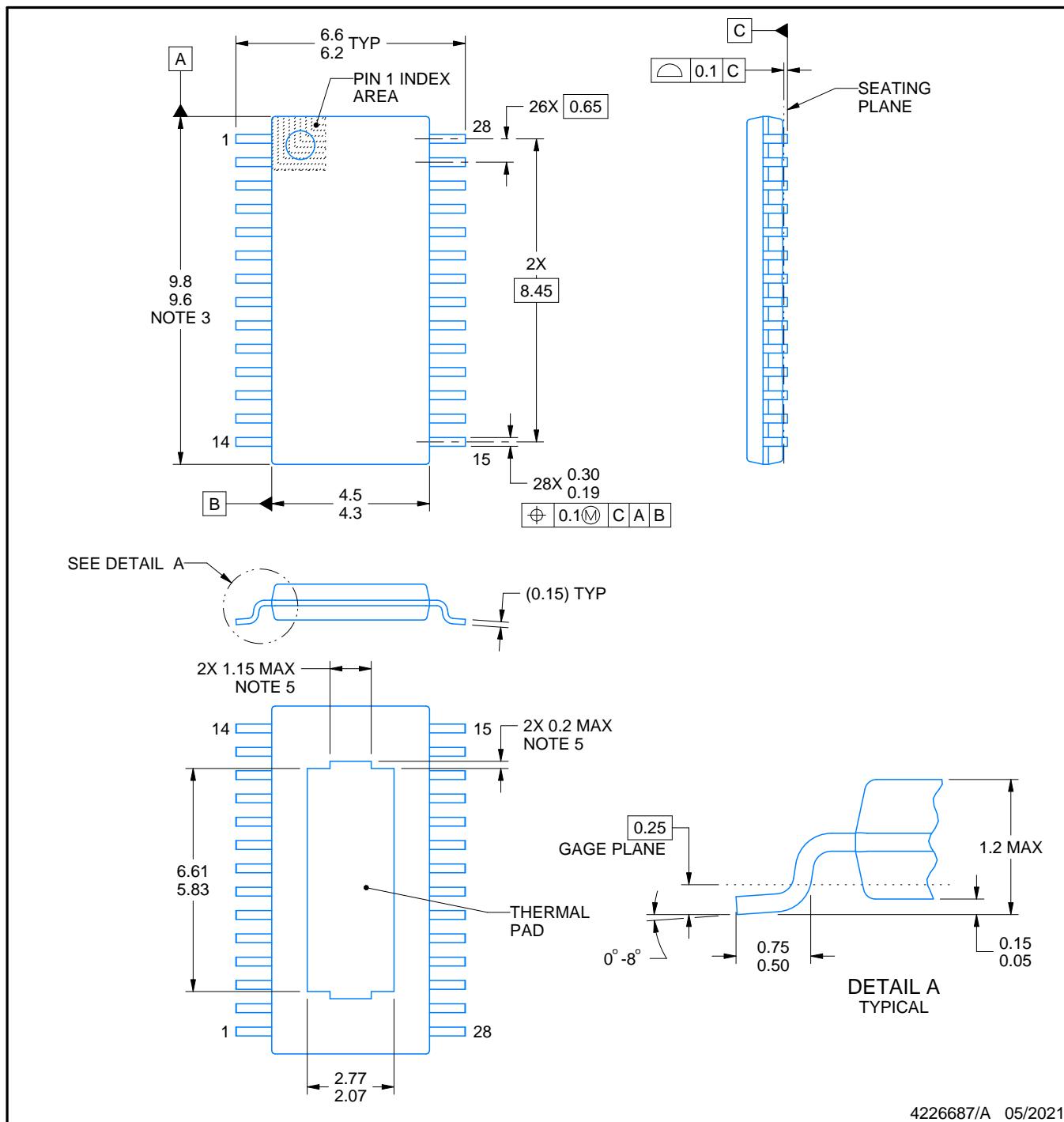

| DRV8452SPWPR | SPI         | HTSSOP (28)          | 9.7 × 4.4mm |

| DRV8452PWPR  | H/W         | HTSSOP (28)          | 9.7 × 4.4mm |

(1) 利用可能なパッケージについては、このデータシートの末尾にある注文情報を参照してください。

英語版の TI 製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、必ず最新版の英語版をご参照ください。

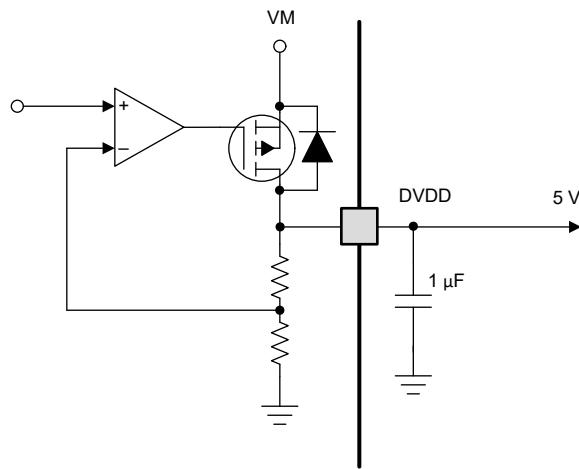

概略回路図

## 目次

|               |     |                         |     |

|---------------|-----|-------------------------|-----|

| 1 特長          | 1   | 8.1 アプリケーション情報          | 103 |

| 2 アプリケーション    | 1   | 8.2 代表的なアプリケーション        | 103 |

| 3 概要          | 1   | 9 熱に関する注意事項             | 109 |

| 4 改訂履歴        | 3   | 9.1 サーマル・パッド            | 109 |

| 5 ピン構成および機能   | 4   | 9.2 PCB 材料に関する推奨事項      | 109 |

| 6 仕様          | 8   | 10 電源に関する推奨事項           | 110 |

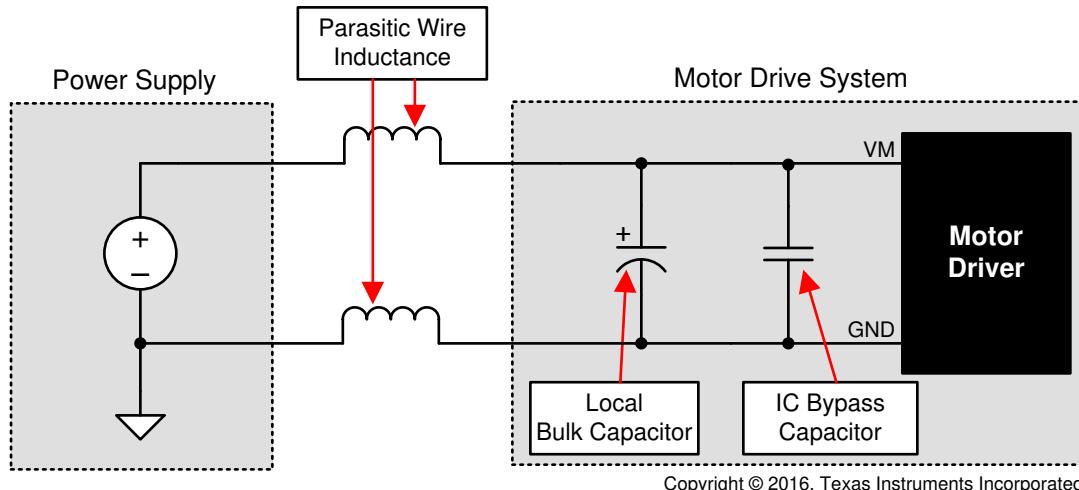

| 6.1 絶対最大定格    | 8   | 10.1 バルク容量              | 110 |

| 6.2 ESD 定格    | 8   | 10.2 電源                 | 110 |

| 6.3 推奨動作条件    | 8   | 11 レイアウト                | 112 |

| 6.4 熱に関する情報   | 9   | 11.1 レイアウトのガイドライン       | 112 |

| 6.5 電気的特性     | 9   | 11.2 レイアウト例             | 112 |

| 6.6 代表的な特性    | 14  | 12 デバイスおよびドキュメントのサポート   | 113 |

| 7 詳細説明        | 16  | 12.1 関連資料               | 113 |

| 7.1 概要        | 16  | 12.2 ドキュメントの更新通知を受け取る方法 | 113 |

| 7.2 機能ブロック図   | 17  | 12.3 サポート・リソース          | 113 |

| 7.3 機能説明      | 19  | 12.4 商標                 | 113 |

| 7.4 プログラミング   | 69  | 12.5 静電気放電に関する注意事項      | 113 |

| 7.5 レジスタ・マップ  | 73  | 12.6 用語集                | 113 |

| 8 アプリケーションと実装 | 103 | 13 メカニカル、パッケージ、および注文情報  | 114 |

## 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision * (August 2022) to Revision A (December 2022) | Page |

|---------------------------------------------------------------------|------|

| • デバイス・ステータスを「事前情報」から「量産データ」に更新                                     | 1    |

## 5 ピン構成および機能

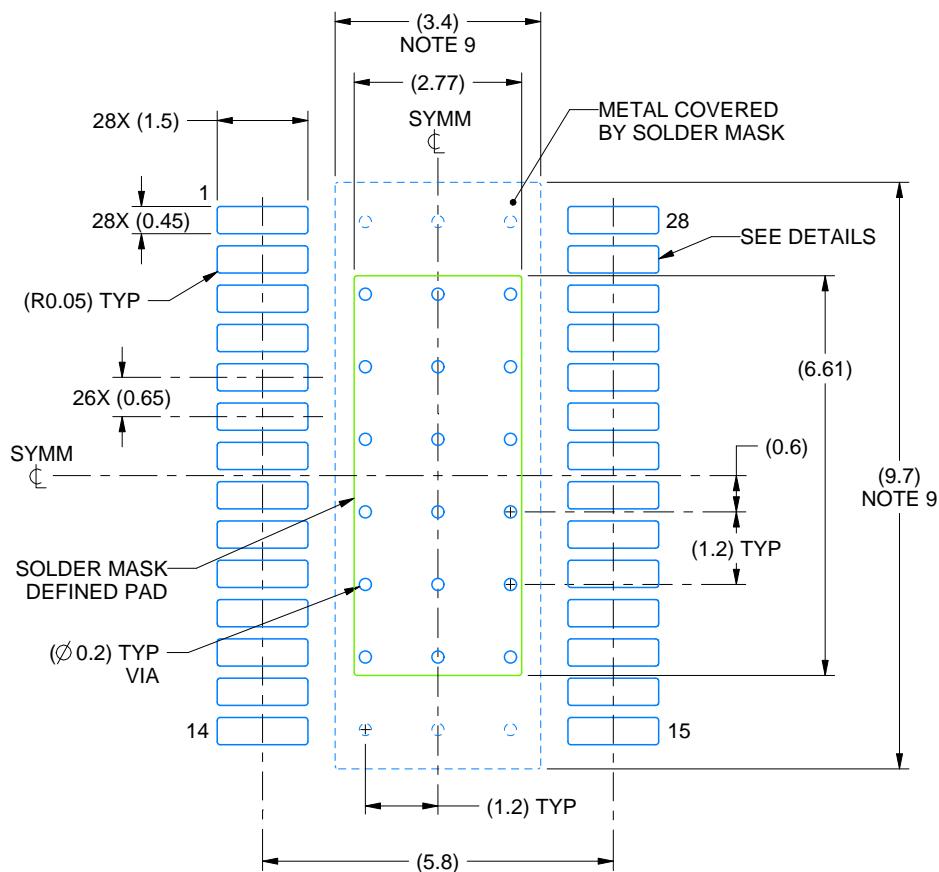

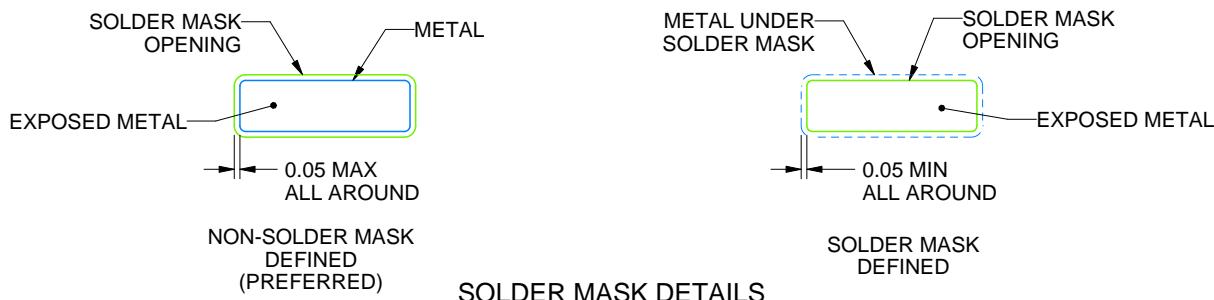

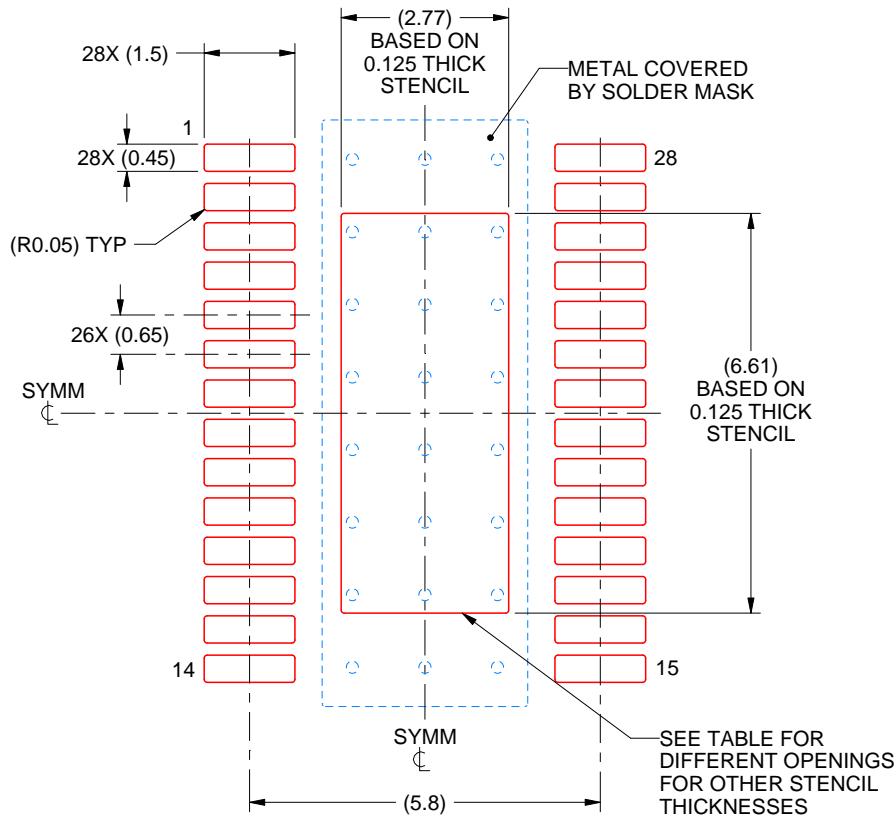

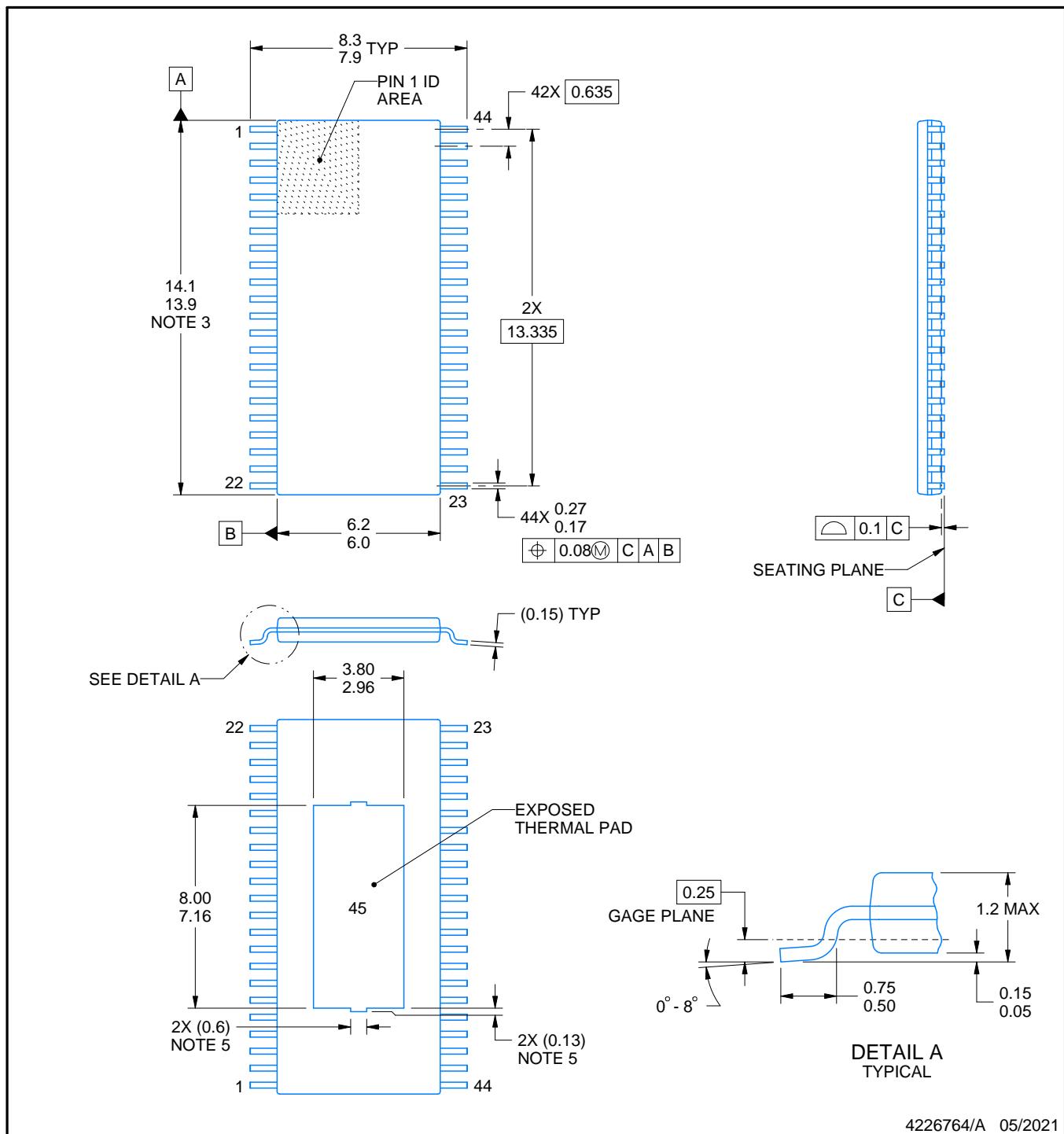

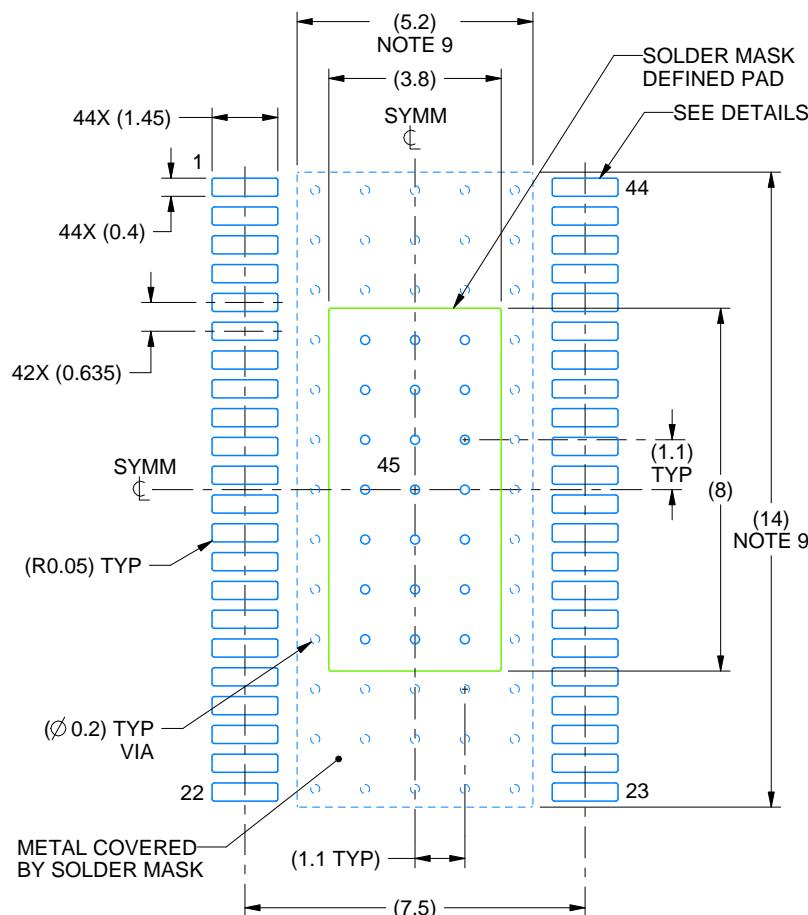

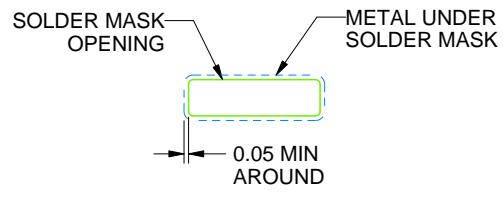

図 5-1. DDW パッケージ (44 ピン HTSSOP)、上面図

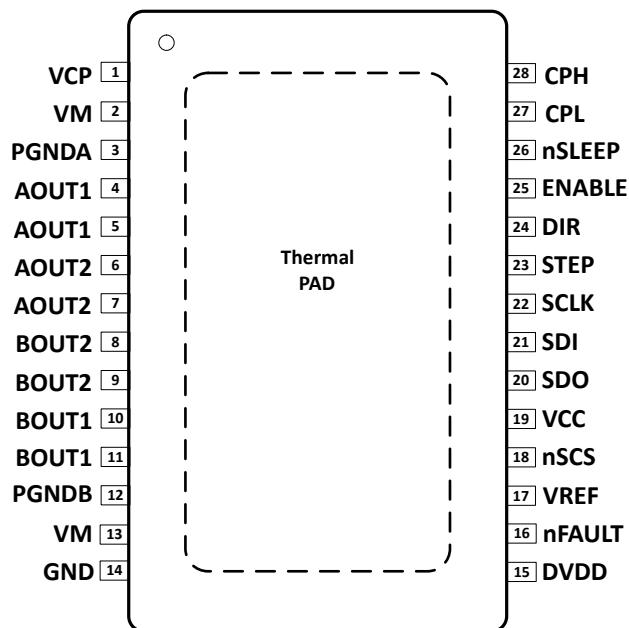

図 5-2. SPI インターフェイス搭載の PWP パッケージ (28 ピン HTSSOP)、上面図

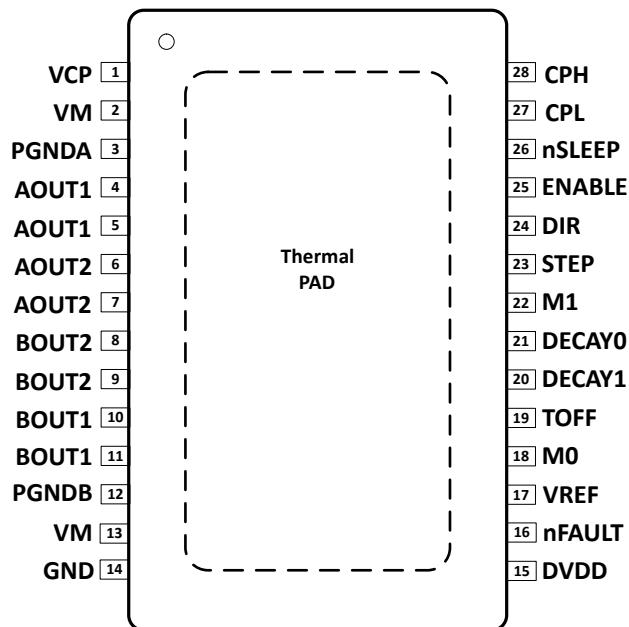

図 5-3. ハードウェア・インターフェイス搭載の PWP パッケージ (28 ピン HTSSOP)、上面図

表 5-1. ピン機能

| 名称         | DDW            | ピン           |                        | 種類 | 説明                                                                                                                                                                          |

|------------|----------------|--------------|------------------------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |                | SPI インターフェイス | PWP<br>ハードウェア・インターフェイス |    |                                                                                                                                                                             |

| VCC        | 25             | 19           | -                      | 電力 | 内部ロジック・ブロックの電源電圧。個別のロジック電源電圧が利用できない場合は、VCC ピンを DVDD ピンに接続します。SPI インターフェイスで構成した場合、VCC ピンは SDO 出力の電源ピンとしても機能します。詳しくは、 <a href="#">セクション 7.3.16</a> を参照してください。                 |

| RSVD/TOFF  | 35             | -            | 19                     | 入力 | このピンは SPI インターフェイスでは使用しません。<br>ハードウェア・インターフェイスでは、このピンで PWM 電流レギュレーションのオフ時間をプログラムします。                                                                                        |

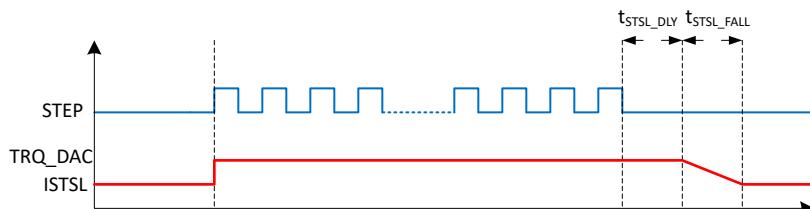

| VCP        | 1              | 1            |                        | 電力 | チャージ・ポンプの出力。X7R、1μF、16V セラミック・コンデンサを VCP と VM との間に接続します。                                                                                                                    |

| VM         | 2, 11, 12, 21  | 2, 13        |                        | 電力 | 電源。モーターの電源電圧に接続し、VM 定格の 2 つの 0.01μF セラミック・コンデンサと 1 つのバルク・コンデンサを使用して、PGNDA と PGND にバイパスします。                                                                                  |

| PGNDA      | 3, 10          | 3            |                        | 電力 | 電源グランド。システム・グランドに接続します。                                                                                                                                                     |

| PGNDB      | 13, 20         | 12           |                        | 電力 | 電源グランド。システム・グランドに接続します。                                                                                                                                                     |

| AOUT1      | 4, 5, 6        | 4, 5         |                        | 出力 | 巻線 A 出力。モーターの巻線に接続します。                                                                                                                                                      |

| AOUT2      | 7, 8, 9        | 6, 7         |                        | 出力 | 巻線 A 出力。モーターの巻線に接続します。                                                                                                                                                      |

| BOUT2      | 14, 15, 16     | 8, 9         |                        | 出力 | 巻線 B 出力。モーターの巻線に接続します。                                                                                                                                                      |

| BOUT1      | 17, 18, 19     | 10, 11       |                        | 出力 | 巻線 B 出力。モーターの巻線に接続します。                                                                                                                                                      |

| GND        | 22, 23         | 14           |                        | 電力 | デバイスのグランド。システム・グランドに接続します。                                                                                                                                                  |

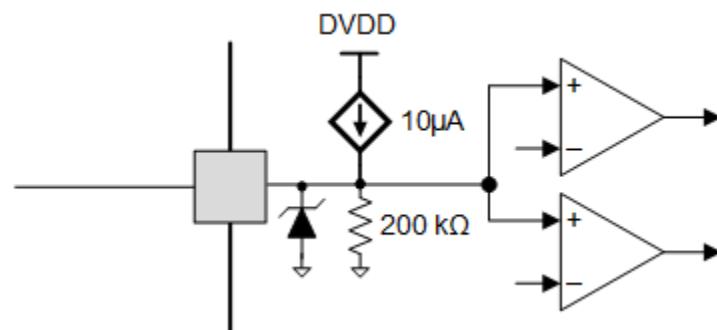

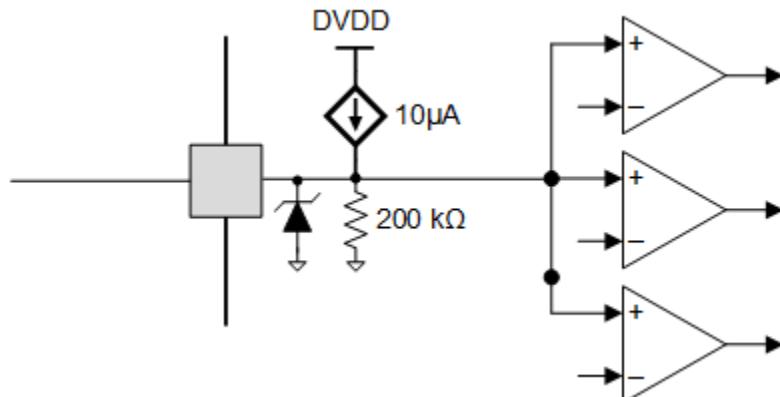

| DVDD       | 24             | 15           |                        | 電力 | 内部 LDO 出力。X7R、1μF、6.3V または 10V 定格セラミック・コンデンサを GND との間に接続します。                                                                                                                |

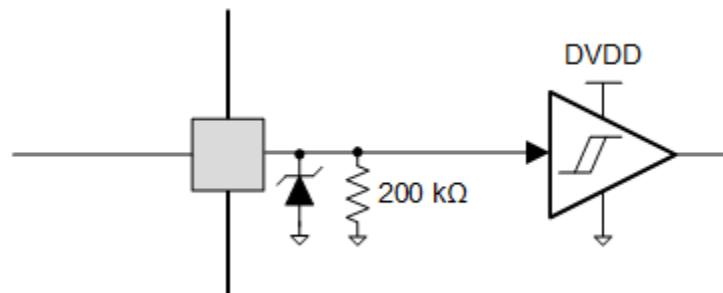

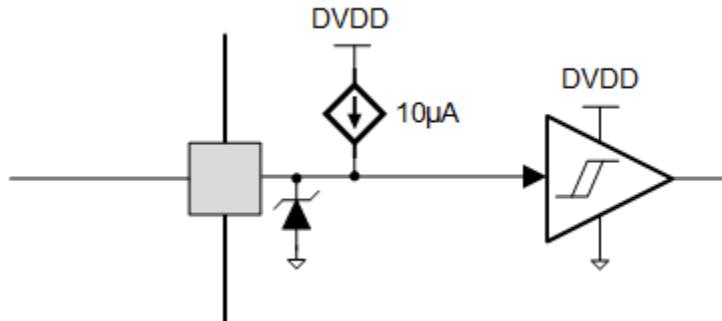

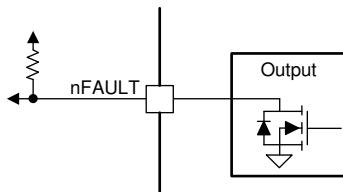

| nFAULT     | 26             | 16           | オープンドレイン               |    | フォルト通知出力。フォルト状態時にロジック Low にブル。オープン・ドレイン nFAULT には外付けブルアップ抵抗が必要です。                                                                                                           |

| nHOME      | 27             | -            | オープンドレイン               |    | 内部インデクサがステップ・テーブルのホーム位置 (45°) にあるとき、ロジック Low にブルします。nHOME ピンは、360° の電気的回転 (4 回のフルステップ) ごとに 1 つの低パルスを出力します。詳しくは、 <a href="#">セクション 7.3.5.1</a> を参照してください。DDW パッケージでのみ利用できます。 |

| MODE       | 28             | -            |                        | 入力 | MODE ピンは、SPI インターフェイスまたはハードウェア (H/W) ピン・インターフェイスで動作するようにデバイスをプログラムします。詳しくは、 <a href="#">セクション 7.3.1</a> を参照してください。                                                          |

| RSVD       | 29, 30, 31, 32 | -            | -                      |    | 予約済み。未接続のままにします。                                                                                                                                                            |

| VREF       | 33             | 17           |                        | 入力 | フルスケール電流を設定するための電圧リファレンス入力。DVDD と抵抗分割器を使用して VREF を生成できます。SPI インターフェイスで構成した場合、VREF_INT_EN ビットが「1b」のときは VREF ピンを未接続のままにできます。                                                  |

| nSCS/M0    | 34             | 18           |                        | 入力 | SPI インターフェイスでは、このピンはシリアル・チップ・セレクトとして機能します。このピンを Low にするとシリアル・インターフェイス通信が有効になります。H/W インターフェイスでは、このピンはマイクロステッピング・モードをプログラムします。                                                |

| SDO/DECAY1 | 36             | 20           | プッシュプル / 入力            |    | SPI インターフェイスでは、このピンはシリアル・データ出力として機能します。データは、SCLK ピンの立ち上がりエッジでシフト・アウトされます。H/W インターフェイスでは、このピンは減衰モードをプログラムします。                                                                |

**表 5-1. ピン機能 (continued)**

| 名称         | DDW | ピン           |                        | 種類 | 説明                                                                                                                                                         |

|------------|-----|--------------|------------------------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |     | SPI インターフェイス | PWP<br>ハードウェア・インターフェイス |    |                                                                                                                                                            |

| SDI/DECAY0 | 37  | 21           |                        | 入力 | SPI インターフェイスでは、このピンはシリアル・データ入力として機能します。データは、SCLK ピンの立ち下がりエッジでキャプチャされます。H/W インターフェイスでは、このピンは減衰モードをプログラムします。                                                 |

| SCLK/M1    | 38  | 22           |                        | 入力 | SPI インターフェイスにより、このピンはシリアル・クロック入力として動作します。シリアル・データは、このピンの対応する立ち上がりおよび立ち下がりエッジでシフト・アウトおよびキャプチャされます。H/W インターフェイスでは、このピンはマイクロステッピング・モードをプログラムします。              |

| STEP       | 39  | 23           |                        | 入力 | ステップ入力。アクティブ・エッジにより、インデクサは 1 ステップ進みます。SPI インターフェイスの場合、STEP のアクティブ・エッジは立ち上がりエッジ、または立ち上がりと立ち下がりの両方のエッジに設定できます。H/W インターフェイスでは、STEP アクティブ・エッジは常に立ち上がりエッジになります。 |

| DIR        | 40  | 24           |                        | 入力 | 方向入力。ロジック・レベルはステッピングの方向を設定します。                                                                                                                             |

| ENABLE     | 41  | 25           |                        | 入力 | ロジック Low でデバイスの出力をディセーブル。ロジック High でイネーブル。デバイスが H/W インターフェイスで動作している場合、ENABLE ピンによって OCP、OL、OTSD のフォルト回復方法も決まります。                                           |

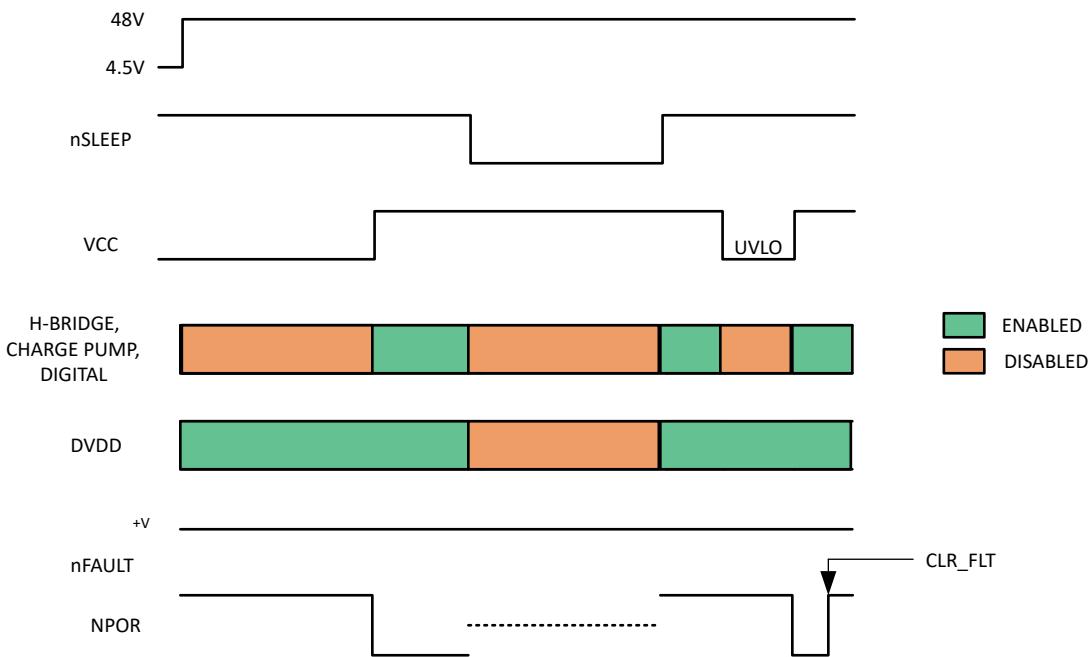

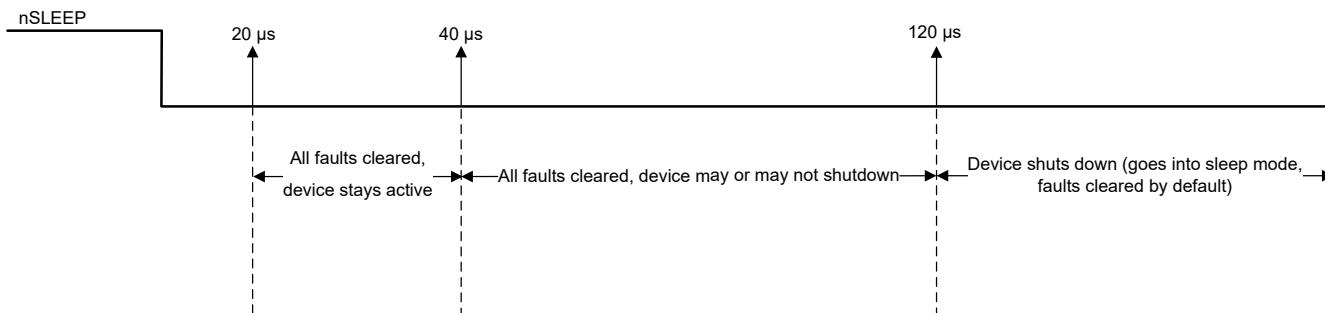

| nSLEEP     | 42  | 26           |                        | 入力 | スリープ・モード入力。デバイスは、ロジック High でイネーブルし、ロジック Low で低消費電力スリープ・モードに移行します。<br>nSLEEP リセット・パルス幅が狭いと、ラッチされた障害はクリアされます。                                                |

| CPL        | 43  | 27           | 電力                     | 電力 | チャージ・ポンプのスイッチング・ノード。X7R、0.1μF、VM 定格セラミック・コンデンサを CPH と CPL の間に接続します。                                                                                        |

| CPH        | 44  | 28           | 電力                     |    |                                                                                                                                                            |

| PAD        | -   | -            | -                      | -  | サーマル・パッド。システム・グランドに接続します。                                                                                                                                  |

## 6 仕様

### 6.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り)<sup>(1)(2)</sup>

|                                             | 最小値    | 最大値          | 単位 |

|---------------------------------------------|--------|--------------|----|

| 電源電圧 ( $V_M$ )                              | -0.3   | 50           | V  |

| チャージ・ポンプ電圧 (VCP、CPH)                        | -0.3   | $V_M + 5.75$ | V  |

| チャージ・ポンプ負スイッチング・ピン (CPL)                    | -0.3   | $V_M$        | V  |

| nSLEEP ピン電圧 (nSLEEP)                        | -0.3   | $V_M$        | V  |

| 内部レギュレータ電圧 (DVDD)                           | -0.3   | 5.75         | V  |

| 外部ロジック電源 (VCC)                              | -0.3   | 5.75         | V  |

| 制御ピン電圧                                      | -0.3   | 5.75         | V  |

| リファレンス入力ピン電圧 (VREF)                         | -0.3   | 5.75         | V  |

| PGND <sub>x</sub> から GND への電圧               | -0.5   | 0.5          | V  |

| PGND <sub>x</sub> から GND への電圧、1μs 未満        | -2.5   | 2.5          | V  |

| オープン・ドレイン出力電流 (nFAULT、nHOME)                | 0      | 10           | mA |

| 連続出力ピン電圧 (AOUT1、AOUT2、BOUT1、BOUT2)          | -1     | $V_M + 1$    | V  |

| 出力ピン電圧 (過渡 100ns) (AOUT1、AOUT2、BOUT1、BOUT2) | -3     | $V_M + 3$    | V  |

| ピーク駆動電流 (AOUT1、AOUT2、BOUT1、BOUT2)           | 内部的に制限 |              | A  |

| 動作時の周囲温度、 $T_A$                             | -40    | 125          | °C |

| 動作時の接合部温度、 $T_J$                            | -40    | 150          | °C |

| 保存温度、 $T_{stg}$                             | -65    | 150          | °C |

- 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値と等しい、またはそれを超える条件で本製品が正しく動作することを暗に示すものではありません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

- すべての電圧値は、回路のグランド端子 GND を基準としたものです。

### 6.2 ESD 定格

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>     | 値    | 単位 |

|-------------|------|----------------------------------------------------------|------|----|

|             |      | デバイス帯電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 準拠 <sup>(2)</sup> | 角のピン |    |

|             |      | その他のピン                                                   | ±500 |    |

(1) JEDEC のドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスで安全な製造が可能であると記載されています。

(2) JEDEC のドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスで安全な製造が可能であると記載されています。

### 6.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)。

|           | 最小値               | 最大値  | 単位 |

|-----------|-------------------|------|----|

| $V_M$     | 通常 (DC) 動作の電源電圧範囲 | 4.5  | V  |

| $V_I$     | ロジック・レベル入力電圧      | 0    | V  |

| $V_{VCC}$ | VCC ピン電圧          | 3.05 | V  |

## 6.3 推奨動作条件 (continued)

自由気流での動作温度範囲内 (特に記述のない限り)。

|            |                                          | 最小値  | 最大値                | 単位  |

|------------|------------------------------------------|------|--------------------|-----|

| $V_{REF}$  | リファレンス電圧 ( $V_{REF}$ )                   | 0.05 | 3.3                | V   |

| $f_{STEP}$ | 適用される STEP 信号 (STEP)                     | 0    | 100 <sup>(1)</sup> | kHz |

| $I_{FS}$   | DDW パッケージ ( $xOUTx$ ) を使用したモーターのフルスケール電流 | 0    | 5 <sup>(2)</sup>   | A   |

| $I_{FS}$   | PWP パッケージでのモーターのフルスケール電流 ( $xOUTx$ )     | 0    | 4 <sup>(2)</sup>   | A   |

| $I_{RMS}$  | DDW パッケージ ( $xOUTx$ ) を使用したモーターの RMS 電流  | 0    | 3.5 <sup>(2)</sup> | A   |

| $I_{RMS}$  | PWP パッケージでのモーターの RMS 電流 ( $xOUTx$ )      | 0    | 2.8 <sup>(2)</sup> | A   |

| $T_A$      | 動作時周囲温度                                  | -40  | 125                | °C  |

| $T_J$      | 動作時接合部温度                                 | -40  | 150                | °C  |

1.  $STEP$  入力は最高 500kHz で動作しますが、システムの帯域幅はモーターの負荷により制限されます。

2. 消費電力および温度の制限に従う必要があります。

## 6.4 熱に関する情報

| 熱評価基準                |                     | DDW  | PWP  | 単位   |

|----------------------|---------------------|------|------|------|

| $R_{\theta JA}$      | 接合部から周囲への熱抵抗        | 22.5 | 24.5 | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース (上面) への熱抵抗 | 9.8  | 13.5 | °C/W |

| $R_{\theta JB}$      | 接合部から基板への熱抵抗        | 5.9  | 5.2  | °C/W |

| $\Psi_{JT}$          | 接合部から上面への熱特性パラメータ   | 0.2  | 0.2  | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性評価パラメータ  | 5.8  | 5.1  | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース (底面) への熱抵抗 | 0.9  | 0.9  | °C/W |

## 6.5 電気的特性

標準値は  $T_A = 25^\circ\text{C}$ 、 $V_{VM} = 24\text{V}$  での値です。特に記述のない限り、すべての限界値は推奨動作条件の全範囲を満たすものとします。

| パラメータ                         | テスト条件                  | 最小値                                        | 標準値  | 最大値          | 単位   |

|-------------------------------|------------------------|--------------------------------------------|------|--------------|------|

| <b>電源 (VM、DVDD)</b>           |                        |                                            |      |              |      |

| $I_{VM}$                      | VM 動作電源電流              | ENABLE = 1、nSLEEP = 1、モーター負荷なし、VCC = 外部 5V |      | 5            | 8.5  |

|                               |                        | ENABLE = 1、nSLEEP = 1、モーター負荷なし、VCC = DVDD  |      | 8            | 12   |

| $I_{VMQ}$                     | VM スリープ・モード電源電流        | nSLEEP = 0                                 |      | 3            | 8    |

| $t_{SLEEP}$                   | スリープ時間                 | nSLEEP = 0 からスリープモードまで                     | 120  |              | μs   |

| $t_{RESET}$                   | nSLEEP リセット・パルス        | nSLEEP = Low でフォルトクリア                      | 20   | 40           | μs   |

| $t_{WAKE}$                    | ウェークアップ時間              | H/W インターフェイス、nSLEEP = 1 で出力遷移              |      | 0.85         | 1.2  |

|                               |                        | SPI インターフェイス、nSLEEP = 1 で SPI 準備完了         |      | 0.15         | 0.25 |

| $t_{ON}$                      | ターンオン時間 <sup>(1)</sup> | VM > UVLO で出力遷移                            |      | 1            | 1.3  |

| $V_{DVDD}$                    | 内部レギュレータ電圧             | 外部負荷なし、 $6\text{V} < V_{VM} < 48\text{V}$  | 4.75 | 5            | 5.25 |

|                               |                        | 外部負荷なし、 $V_{VM} = 4.5\text{V}$             | 4.2  | 4.35         | V    |

| <b>チャージ・ポンプ (VCP、CPH、CPL)</b> |                        |                                            |      |              |      |

| $V_{VCP}$                     | VCP 動作電圧               | $6\text{V} < V_{VM} < 48\text{V}$          |      | $V_{VM} + 5$ | V    |

標準値は  $T_A = 25^\circ\text{C}$ 、 $V_{VM} = 24\text{V}$  での値です。特に記述のない限り、すべての限界値は推奨動作条件の全範囲を満たすものとします。

| パラメータ                                                         |                                                 | テスト条件                                              | 最小値  | 標準値  | 最大値  | 単位               |

|---------------------------------------------------------------|-------------------------------------------------|----------------------------------------------------|------|------|------|------------------|

| $f_{VCP}$                                                     | チャージ・ポンプのスイッチング周波数                              | $V_{VM} > \text{UVLO}$ , $nSLEEP = 1$              |      | 357  |      | kHz              |

| $f_{CLK}$                                                     | 内部デジタル・クロック周波数                                  | $V_{VM} > \text{UVLO}$ , $nSLEEP = 1$              |      | 10   |      | MHz              |

| <b>ロジック・レベル入力 (STEP、DIR、MODE、DECAY1、nSCS、SCLK、SDI、nSLEEP)</b> |                                                 |                                                    |      |      |      |                  |

| $V_{IL}$                                                      | 入力ロジック Low 電圧                                   |                                                    | 0    |      | 0.6  | V                |

| $V_{IH}$                                                      | 入力論理 High 電圧 (DECAY1 を除くすべてのピン)                 |                                                    | 1.5  |      | 5.5  | V                |

| $V_{IH\_DECAY1}$                                              | 入力ロジック High 電圧 (DECAY1 ピン)                      |                                                    | 2.7  |      | 5.5  | V                |

| $V_{HYS}$                                                     | 入力ロジック・ヒステリシス (nSLEEP を除くすべてのピン)                |                                                    |      | 100  |      | mV               |

| $V_{HYS\_SLEEP}$                                              | nSLEEP ロジック・ヒステリシス                              |                                                    |      | 300  |      | mV               |

| $I_{IL}$                                                      | 入力ロジック Low 電流 (nSCS を除くすべてのピン)                  | $V_{IN} = 0\text{V}$                               | -1   |      | 1    | $\mu\text{A}$    |

| $I_{IL\_nSCS}$                                                | nSCS ロジック Low 電流                                | $nSCS = 0\text{V}$                                 | 8    |      | 12   | $\mu\text{A}$    |

| $I_{IH}$                                                      | 入力ロジック High 電流 (nSCS を除くすべてのピン、200k の内部プルダウン抵抗) | $V_{IN} = DVDD$                                    |      |      | 50   | $\mu\text{A}$    |

| $I_{IH\_nSCS}$                                                | nSCS ロジック High 電流                               | $nSCS = DVDD$                                      |      |      | 0.1  | $\mu\text{A}$    |

| <b>トライレベル入力 (M0、DECAY0、ENABLE)</b>                            |                                                 |                                                    |      |      |      |                  |

| $V_{I1\_tri}$                                                 | 入力ロジック Low 電圧                                   | GND に接続                                            | 0    |      | 0.6  | V                |

| $V_{I2\_tri}$                                                 | 入力 Hi-Z 電圧                                      | Hi-Z                                               | 1.8  | 2    | 2.2  | V                |

| $V_{I3\_tri}$                                                 | 入力ロジック High 電圧                                  | DVDD に接続                                           | 2.7  |      | 5.5  | V                |

| $I_{O\_tri}$                                                  | 出力プルアップ電流                                       |                                                    |      | 10.5 |      | $\mu\text{A}$    |

| <b>クワッドレベル入力 (M1、TOFF)</b>                                    |                                                 |                                                    |      |      |      |                  |

| $V_{I1\_quad}$                                                | 入力ロジック Low 電圧                                   | GND に接続                                            | 0    |      | 0.6  | V                |

| $V_{I2\_quad}$                                                | 入力セカンド・レベル電圧                                    | $330\text{k}\Omega \pm 5\%$ を GND との間に接続           | 1    | 1.25 | 1.4  | V                |

| $V_{I3\_quad}$                                                | 入力 Hi-Z 電圧                                      | Hi-Z                                               | 1.8  | 2    | 2.2  | V                |

| $V_{I4\_quad}$                                                | 入力ロジック High 電圧                                  | DVDD に接続                                           | 2.7  |      | 5.5  | V                |

| $I_{O\_quad}$                                                 | 出力プルアップ電流                                       |                                                    |      | 10.5 |      | $\mu\text{A}$    |

| <b>プッシュプル出力 (SDO)</b>                                         |                                                 |                                                    |      |      |      |                  |

| $R_{PD,SDO}$                                                  | 内部プルダウン抵抗                                       | 5mA 負荷、GND 基準                                      |      | 30   | 70   | $\Omega$         |

| $R_{PU,SDO}$                                                  | 内部プルアップ抵抗                                       | 5mA 負荷、VCC 基準                                      |      | 60   | 110  | $\Omega$         |

| $I_{SDO}$                                                     | SDO リーク電流 <sup>(1)</sup>                        | $V_{VM} > 6\text{V}$ 、 $SDO = VCC$ および $0\text{V}$ | -2.5 |      | 2.5  | $\mu\text{A}$    |

| <b>制御出力 (nFAULT、nHOME)</b>                                    |                                                 |                                                    |      |      |      |                  |

| $V_{OL}$                                                      | 出力ロジック Low 電圧                                   | $I_O = 5\text{mA}$                                 |      |      | 0.35 | V                |

| $I_{OH}$                                                      | 出力ロジック High リーク電流                               |                                                    | -1   |      | 1    | $\mu\text{A}$    |

| <b>モーター・ドライバ出力 (AOUT1、AOUT2、BOUT1、BOUT2)</b>                  |                                                 |                                                    |      |      |      |                  |

| $R_{DS(ONH, DDW)}$                                            | ハイサイド FET オン抵抗、DDW パッケージ                        | $T_J = 25^\circ\text{C}$ , $I_O = -5\text{A}$      |      | 53   | 60   | $\text{m}\Omega$ |

|                                                               |                                                 | $T_J = 125^\circ\text{C}$ , $I_O = -5\text{A}$     |      | 80   | 94   | $\text{m}\Omega$ |

|                                                               |                                                 | $T_J = 150^\circ\text{C}$ , $I_O = -5\text{A}$     |      | 90   | 107  | $\text{m}\Omega$ |

標準値は  $T_A = 25^\circ\text{C}$ 、 $V_{VM} = 24\text{V}$  での値です。特に記述のない限り、すべての限界値は推奨動作条件の全範囲を満たすものとします。

| パラメータ              |                                             | テスト条件                                                         | 最小値 | 標準値 | 最大値 | 単位               |

|--------------------|---------------------------------------------|---------------------------------------------------------------|-----|-----|-----|------------------|

| $R_{DS(ONL, DDW)}$ | ローサイド FET オン抵抗、<br>DDW パッケージ                | $T_J = 25^\circ\text{C}, I_O = 5\text{A}$                     |     | 53  | 60  | $\text{m}\Omega$ |

|                    |                                             | $T_J = 125^\circ\text{C}, I_O = 5\text{A}$                    |     | 80  | 94  | $\text{m}\Omega$ |

|                    |                                             | $T_J = 150^\circ\text{C}, I_O = 5\text{A}$                    |     | 90  | 107 | $\text{m}\Omega$ |

| $R_{DS(ONH, PWP)}$ | ハイサイド FET オン抵抗、<br>PWP パッケージ                | $T_J = 25^\circ\text{C}, I_O = -4\text{A}$                    |     | 55  | 66  | $\text{m}\Omega$ |

|                    |                                             | $T_J = 125^\circ\text{C}, I_O = -4\text{A}$                   |     | 83  | 100 | $\text{m}\Omega$ |

|                    |                                             | $T_J = 150^\circ\text{C}, I_O = -4\text{A}$                   |     | 94  | 116 | $\text{m}\Omega$ |

| $R_{DS(ONL, PWP)}$ | ローサイド FET オン抵抗、<br>PWP パッケージ                | $T_J = 25^\circ\text{C}, I_O = 4\text{A}$                     |     | 55  | 66  | $\text{m}\Omega$ |

|                    |                                             | $T_J = 125^\circ\text{C}, I_O = 4\text{A}$                    |     | 83  | 100 | $\text{m}\Omega$ |

|                    |                                             | $T_J = 150^\circ\text{C}, I_O = 4\text{A}$                    |     | 94  | 116 | $\text{m}\Omega$ |

| $I_{LEAK}$         | ディスエーブル・モードでの出力リーケ電流をグランドに接続 <sup>(1)</sup> | H ブリッジは Hi-Z、 $V_{VM} = 48\text{V}$                           |     |     | 200 | $\mu\text{A}$    |

| $t_{RF}$           | 出力立ち上がり / 立ち下がり時間                           | ハードウェア・インターフェイス、 $I_O = 5\text{A}$ 、<br>10% と 90% の間          |     | 140 |     | ns               |

|                    |                                             | SPI インターフェイス、 $SR = 0b$ 、 $I_O = 5\text{A}$ 、<br>10% と 90% の間 |     | 140 |     |                  |

|                    |                                             | SPI インターフェイス、 $SR = 1b$ 、 $I_O = 5\text{A}$ 、<br>10% と 90% の間 |     | 70  |     |                  |

| $t_D$              | 出力デッドタイム                                    | $VM = 24\text{V}, I_O = 5\text{A}$                            |     | 300 |     | ns               |

#### PWM 電流制御 (VREF)

|                        |                      |                                                    |       |      |       |               |

|------------------------|----------------------|----------------------------------------------------|-------|------|-------|---------------|

| $K_V$                  | トランジンピーダンス・ゲイン       | $VREF = 3.3\text{V}$                               | 0.625 | 0.66 | 0.695 | V/A           |

| $I_{VREF}$             | $VREF$ ピンのリーケ電流      | $VREF = 3.3\text{V}$                               |       |      | 20    | nA            |

| $t_{OFF}$              | PWM オフ時間             | TOFF = 0 または TOFF = 00b                            |       | 9    |       | $\mu\text{s}$ |

|                        |                      | TOFF = 1 または TOFF = 01b                            |       | 19   |       |               |

|                        |                      | TOFF = Hi-Z または TOFF = 10b                         |       | 27   |       |               |

|                        |                      | TOFF = 330k $\Omega$ を GND に接続、または<br>TOFF = 11b   |       | 35   |       |               |

| $\Delta I_{TRIP\_EXT}$ | 電流トリップ精度、外部 VREF 入力  | 10%～20% フルスケール電流                                   | -12   |      | 12    | %             |

|                        |                      | 20%～40% フルスケール電流                                   | -7.5  |      | 7.5   |               |

|                        |                      | 40%～100% フルスケール電流                                  | -5    |      | 5     |               |

| $\Delta I_{TRIP\_INT}$ | 電流トリップ精度、内部 VREF     | 10%～20% フルスケール電流                                   | -12   |      | 12    | %             |

|                        |                      | 20%～40% フルスケール電流                                   | -8    |      | 8     |               |

|                        |                      | 40%～100% フルスケール電流                                  | -6    |      | 5     |               |

| $I_{O,CH}$             | AOUT と BOUT の電流マッチング | 100% フルスケール電流                                      | -2.5  |      | 2.5   | %             |

| $t_{BLK}$              | 電流レギュレーション・ブランкиング時間 | SPI インターフェイス、 $TBLANK\_TIME = 00b$                 |       | 1    |       | $\mu\text{s}$ |

|                        |                      | H/W インターフェイスまたは SPI インターフェイス、 $TBLANK\_TIME = 01b$ |       | 1.5  |       |               |

|                        |                      | SPI インターフェイス、 $TBLANK\_TIME = 10b$                 |       | 2    |       |               |

|                        |                      | SPI インターフェイス、 $TBLANK\_TIME = 11b$                 |       | 2.5  |       |               |

| $t_{DEG}$              | 電流レギュレーション・グリッチ除去時間  |                                                    |       | 0.5  |       | $\mu\text{s}$ |

標準値は  $T_A = 25^\circ\text{C}$ 、 $V_{VM} = 24\text{V}$  での値です。特に記述のない限り、すべての限界値は推奨動作条件の全範囲を満たすものとします。

| パラメータ           |                         | テスト条件                                                  | 最小値 | 標準値          | 最大値  | 単位    |

|-----------------|-------------------------|--------------------------------------------------------|-----|--------------|------|-------|

| <b>保護回路</b>     |                         |                                                        |     |              |      |       |

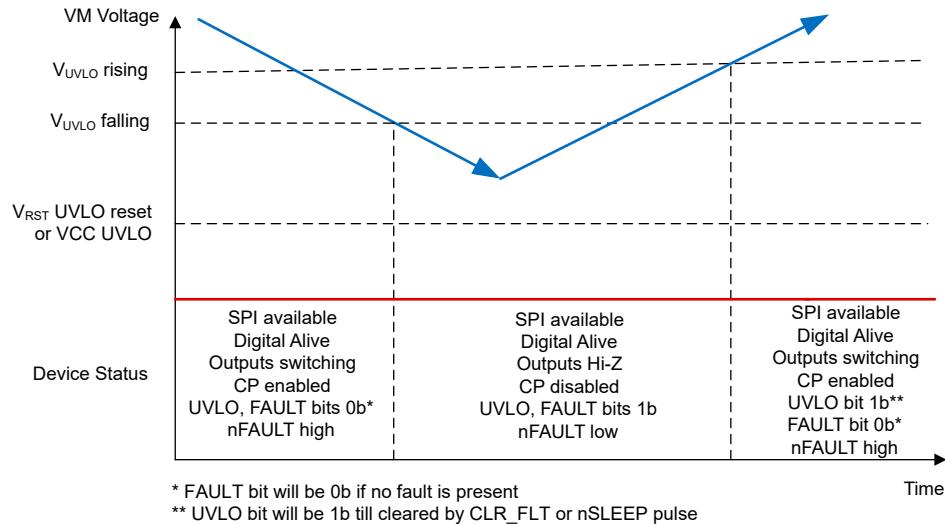

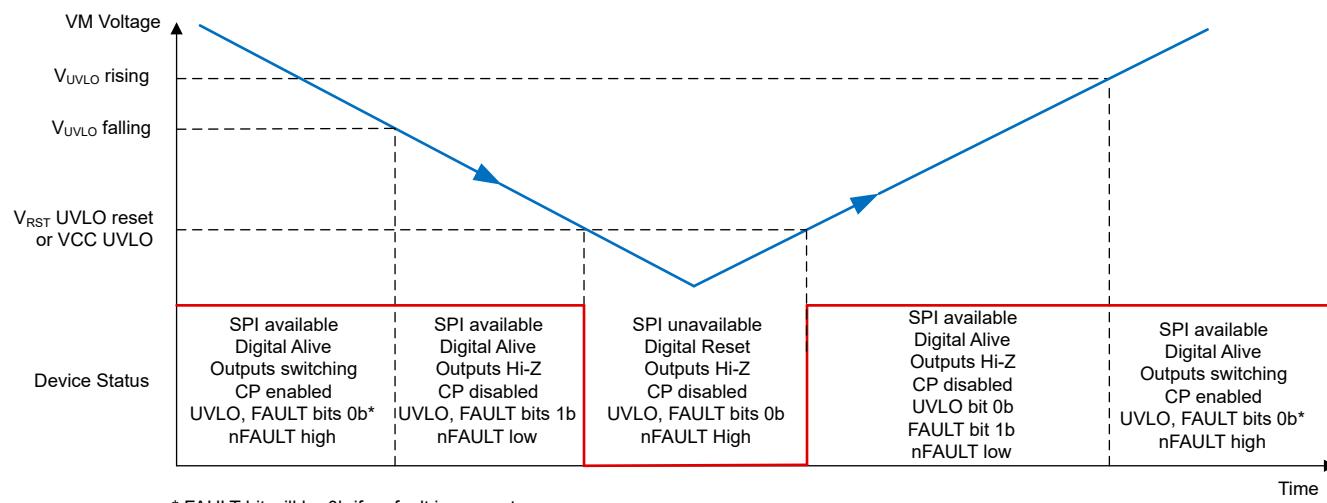

| $V_{M_{UVLO}}$  | VM 低電圧誤動作防止 (UVLO)      | VM 立ち下がり                                               | 4.1 | 4.25         | 4.35 | V     |

|                 |                         | VM 立ち上がり                                               | 4.2 | 4.35         | 4.46 |       |

| $V_{C_{UVLO}}$  | VCC 低電圧誤動作防止 (UVLO)     | VCC を外部電圧に接続、VCC 立ち下がり                                 | 2.7 | 2.8          | 2.9  | V     |

|                 |                         | VCC を外部電圧に接続、VCC 立ち上がり                                 | 2.8 | 2.9          | 3.05 |       |

| $V_{UVLO,HYS}$  | 低電圧ヒステリシス               | 立ち上がりから立ち下がりへのスレッショルド                                  |     | 100          |      | mV    |

| $V_{RST}$       | VM 低電圧誤動作防止 (UVLO) リセット | $VCC = DVDD$ 、SPI インターフェイス、VM 立ち下がり、デバイス・リセット、SPI 通信なし |     |              | 3.4  | V     |

| $V_{CPUV}$      | チャージ・ポンプ低電圧             | VCP 立ち下がり                                              |     | $V_{VM} + 2$ |      | V     |

| $I_{OCP}$       | 過電流保護                   | いずれかの FET を流れる電流                                       | 7.6 |              |      | A     |

| $t_{OCP}$       | 過電流検出遅延                 | H/W インターフェイス                                           |     | 2.2          |      | \mu s |

|                 |                         | SPI インターフェイス、TOCP = 0b                                 |     | 1.2          |      |       |

|                 |                         | SPI インターフェイス、TOCP = 1b                                 |     | 2.2          |      |       |

| $t_{RETRY}$     | 過電流リトライ時間               |                                                        |     | 4.1          |      | ms    |

| $t_{OL}$        | 開放負荷検出時間                | H/W インターフェイス                                           |     |              | 60   | ms    |

|                 |                         | SPI インターフェイス、OL_T = 00b                                |     |              | 30   |       |

|                 |                         | SPI インターフェイス、OL_T = 01b                                |     |              | 60   |       |

|                 |                         | SPI インターフェイス、OL_T = 10b                                |     |              | 120  |       |

| $I_{OL}$        | 開放負荷電流スレッショルド           |                                                        |     | 190          |      | mA    |

| $T_{OTW}$       | 過熱警告                    | SPI インターフェイス、ダイ温度 $T_J$                                | 135 | 150          | 165  | °C    |

| $T_{HYS\_OTW}$  | 過熱警告ヒステリシス              | SPI インターフェイス、ダイ温度 $T_J$                                |     | 20           |      | °C    |

| $T_{OTSD}$      | サーマル・シャットダウン            | ダイ温度 $T_J$                                             | 150 | 165          | 180  | °C    |

| $T_{HYS\_OTSD}$ | サーマル・シャットダウン・ヒステリシス     | ダイ温度 $T_J$                                             |     | 20           |      | °C    |

(1) 設計により保証されています。

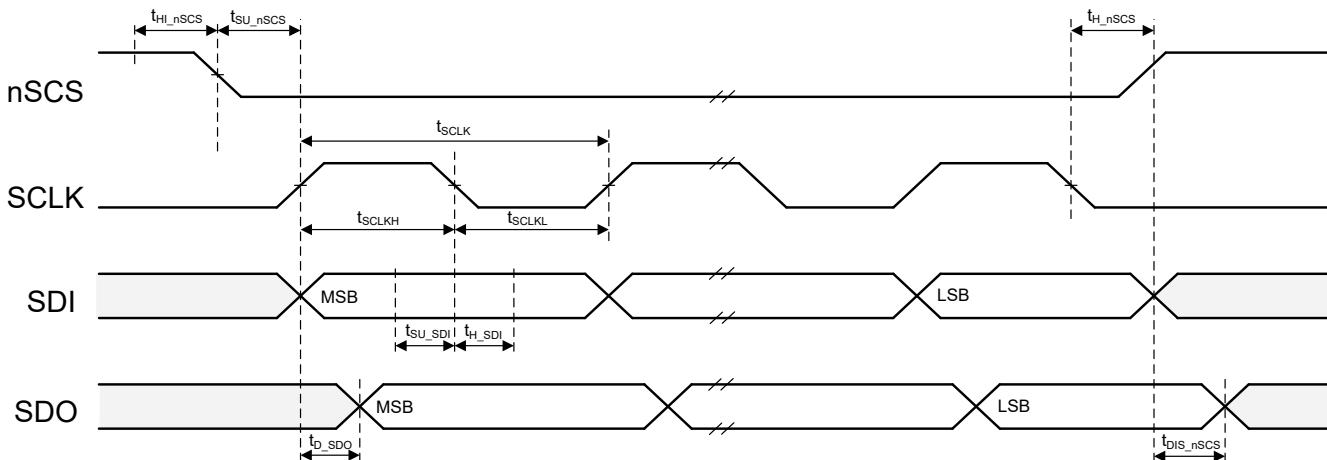

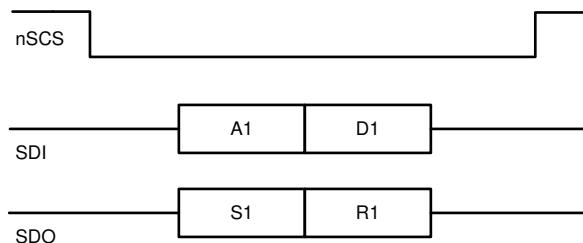

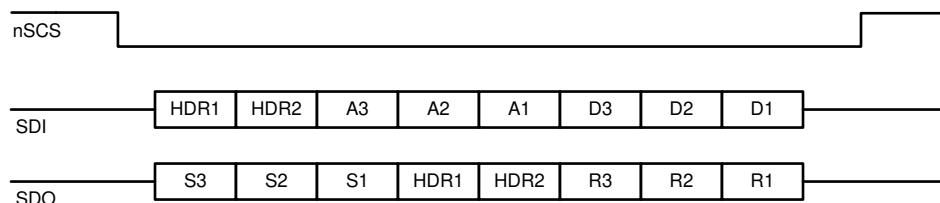

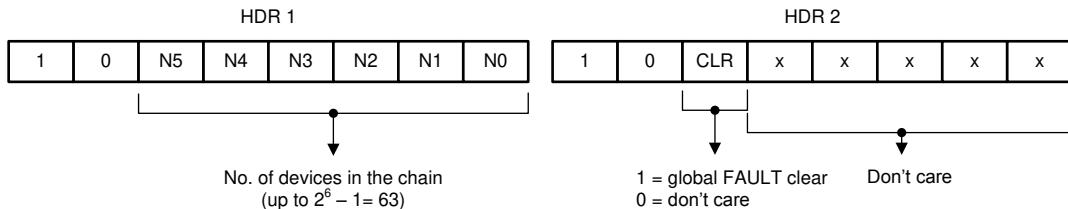

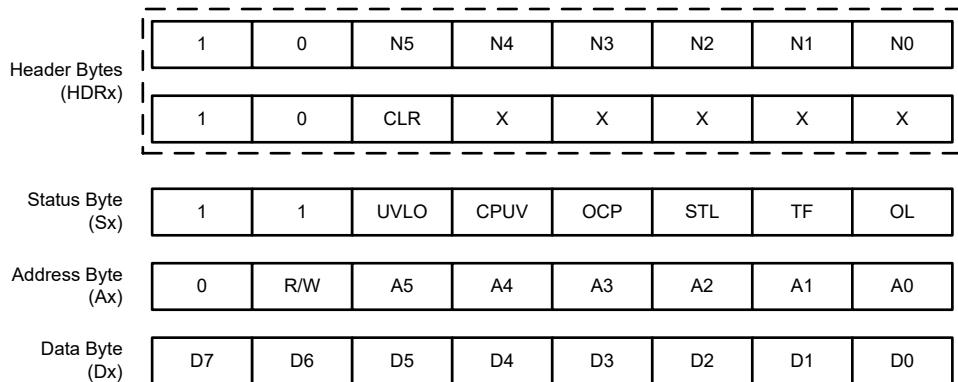

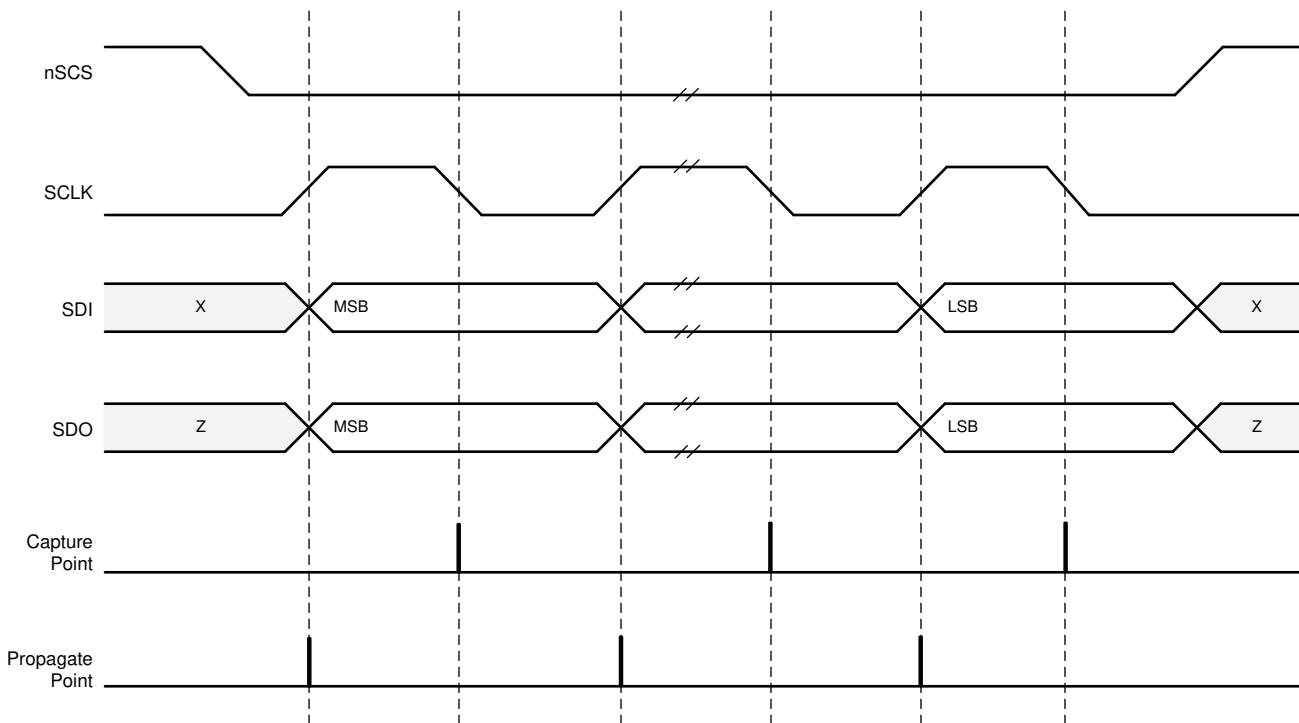

### 6.5.1 SPI のタイミング要件

#### SPI のタイミング図

|                |                                                       | 最小値 | 公称値 | 最大値 | 単位 |

|----------------|-------------------------------------------------------|-----|-----|-----|----|

| $t_{READY}$    | SPI 準備完了、 $VM > V_{RST}$                              |     | 1   |     | ms |

| $t_{SCLK}$     | SCLK の最小周期                                            | 100 |     |     | ns |

| $t_{SCLKH}$    | SCLK 最小 High 時間                                       | 50  |     |     | ns |

| $t_{SCLKL}$    | SCLK 最小 Low 時間                                        | 50  |     |     | ns |

| $t_{SU\_SDI}$  | SDI 入力のセットアップ時間                                       | 20  |     |     | ns |

| $t_{H\_SDI}$   | SDI 入力のホールド時間                                         | 30  |     |     | ns |

| $t_{D\_SDO}$   | SDO 出力遅延時間、SCLK High から SDO 有効まで、 $C_L = 20\text{pF}$ |     |     | 30  | ns |

| $t_{SU\_nSCS}$ | nSCS 入力セットアップ時間                                       | 50  |     |     | ns |

|                 |                                             | 最小値 | 公称値 | 最大値 | 単位 |

|-----------------|---------------------------------------------|-----|-----|-----|----|

| $t_{H\_nSCS}$   | nSCS 入力ホールド時間                               | 50  |     |     | ns |

| $t_{HI\_nSCS}$  | nSCS のアクティブ Low の前の最小 High 時間               |     |     | 2   | μs |

| $t_{DIS\_nSCS}$ | nSCS ディセーブル時間、nSCS High から SDO ハイ・インピーダンスまで |     | 10  |     | ns |

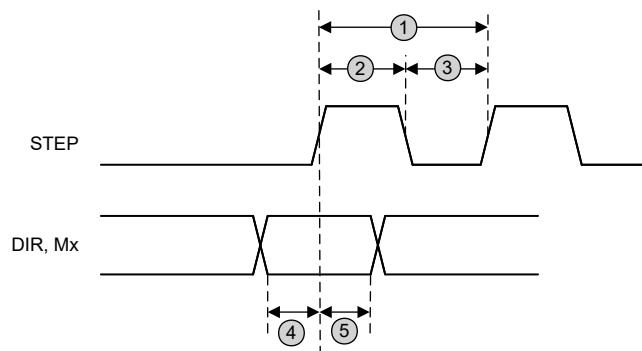

### 6.5.2 STEP と DIR のタイミング要件

標準限界値は  $T_J = 25^\circ\text{C}$ 、 $V_{VM} = 24\text{V}$  での値です。特に記述のない限り、すべての限界値は推奨動作条件の全範囲を満たすものとします。

| 番号 |                   |                                        | 最小値 | 最大値                | 単位  |

|----|-------------------|----------------------------------------|-----|--------------------|-----|

| 1  | $f_{STEP}$        | ステップ周波数                                |     | 500 <sup>(1)</sup> | KHz |

| 2  | $t_{WH\_STEP}$    | パルス幅、STEP High                         | 970 |                    | ns  |

| 3  | $t_{WL\_STEP}$    | パルス幅、STEP Low                          | 970 |                    | ns  |

| 4  | $t_{SU\_DIR, Mx}$ | セットアップ時間、DIR または MODEx から STEP 立ち上がりまで | 200 |                    | ns  |

| 5  | $T_{H\_DIR, Mx}$  | ホールド時間、DIR または Mx から STEP 立ち上がりまで      | 200 |                    | ns  |

- (1) STEP 入力は最高 500kHz で動作しますが、システムの帯域幅はモーターの負荷により制限されます。

図 6-1. STEP と DIR のタイミング図

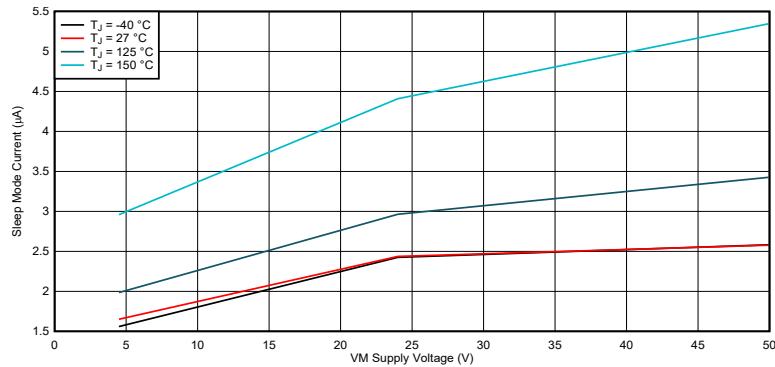

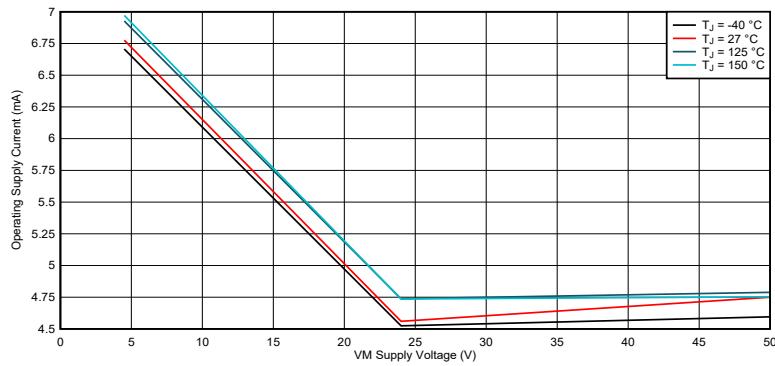

## 6.6 代表的な特性

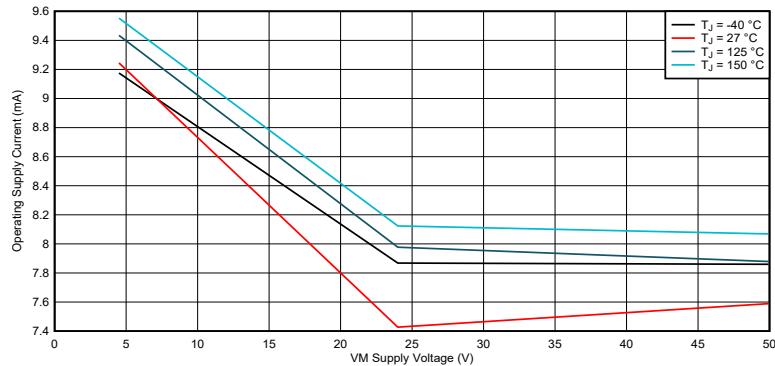

図 6-2. スリープ・モード電源電流

図 6-3. 動作電源電流、VCC = 外部 5V

図 6-4. 動作電源電流、VCC = DVDD

## 6.6 代表的な特性

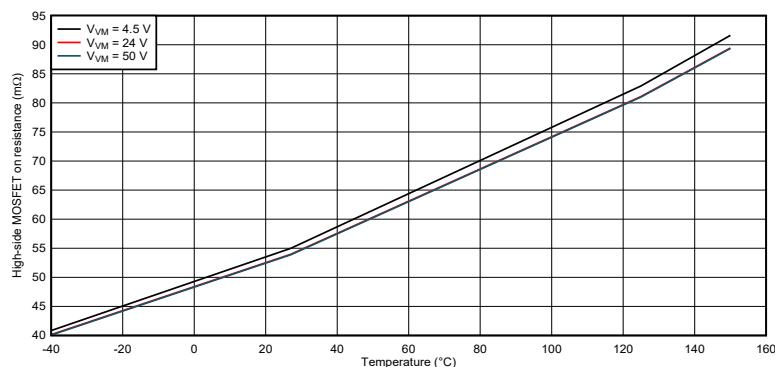

図 6-5. ハイサイド FET オン抵抗

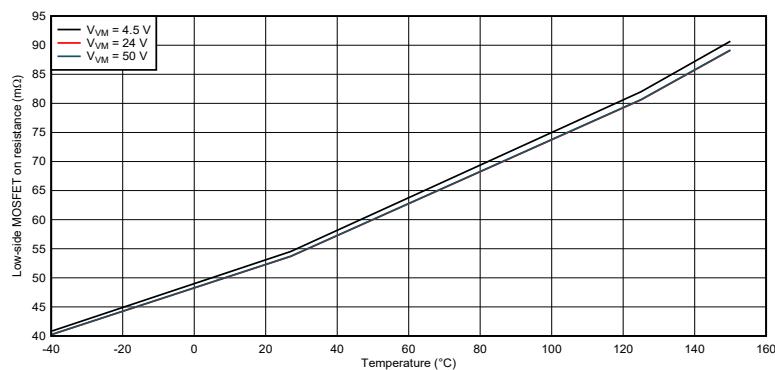

図 6-6. ローサイド FET オン抵抗

## 7 詳細説明

### 7.1 概要

DRV8452 は、バイポーラ・ステッパ・モーター用の統合モーター・ドライバ・ソリューションです。このデバイスには、2つのNチャネル・パワー MOSFET Hブリッジ、電流検出抵抗、電流レギュレーション回路、マイクロステッピング・インデクサが統合されています。DRV8452 は、4.5V～48V の広い電源電圧範囲をサポートできます。このデバイスは、44ピン HTSSOP (DDW) パッケージと、28ピン HTSSOP (PWP) パッケージの2つのパッケージで供給されます。DDW パッケージは、最大 5A のフルスケール、または 3.5A の実効値 (rms) の出力電流を供給します。PWP パッケージは、最大 4A のフルスケール、または 2.8A の実効値 (rms) の出力電流を供給します。実際のフルスケールおよび rms 電流は、周囲温度、電源電圧、PCB の熱設計に依存します。システム設計において、スケーラブルな電圧および電流ソリューションを提供するため、SPI インターフェイス付きの PWP パッケージは [DRV8434S](#) とピン互換です。ハードウェア・インターフェイス付きの PWP パッケージは、[DRV8424](#)、[DRV8426](#)、[DRV8434](#) とピン互換です。DDW パッケージは、[DRV8462](#)、[DRV8461](#) とピン互換です。

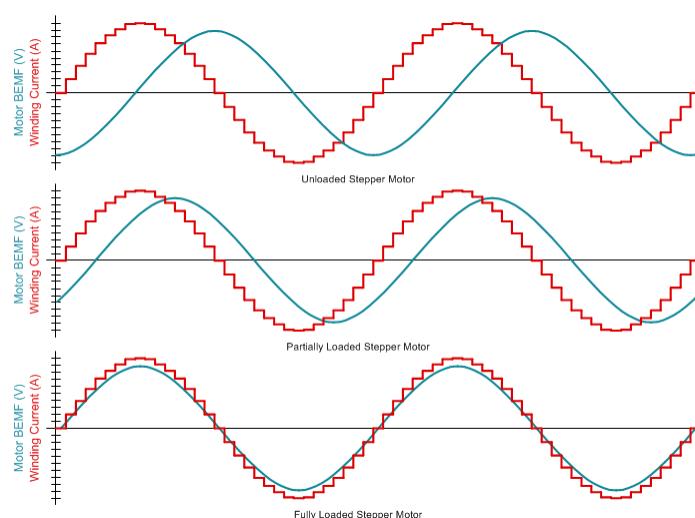

DRV8452 には自動トルク機能が内蔵されており、負荷トルクに応じて出力電流を調整することで、電力損失を低減し、システムの効率を向上させます。SPI インターフェイスには、特定のモーターやシステムの使用事例に合わせて自動トルク・アルゴリズムの性能を最適化できるよう、さまざまなオプションが用意されています。ストール検出機能は、モーターが妨げられている、またはエンドオブトラベル停止に達したときに、モーター・ストールの条件を検出してシステム・コントローラに通知します。さらに、静止電力節約モードにより、モーターが保持位置にあるときの電力損失が低減されます。

DRV8452 は電流検出アキテクチャを内蔵しているため、2つの外部電力検出抵抗が不要になり、基板面積、BOM コスト、設計作業が大幅に削減され、消費電力が大幅に低減されます。このアキテクチャでは、電流検出に電流ミラー手法と内部パワー MOSFET を使うことで、検出抵抗での電力消費をなくしています。オプションの外部電力検出抵抗を PGND ピンと基板グランドの間に接続して、モーターの状態を監視し、フィールド・オリエンテッド・コントロールなどの閉ループ・アルゴリズムを実装することもできます。電流レギュレーションの設定点は VREF ピンの電圧で調整できます。SPI インターフェイスの場合、8ビット・レジスタにより、コントローラは VREF 電圧リファレンスをスケーリングせずに出力電流をスケーリングできます。また、別の 8ビット・レジスタにより、モーター停止時の電力損失を低減する目的で保持電流レベルを構成できます。

STEP/DIR インターフェイスにより、外部コントローラからステッパ・モーターの方向とステップ速度を制御できます。内部マイクロステッピング・インデクサを使うと、巻線電流レベルを制御する外部コントローラを使わずに高精度のマイクロステッピングを実行できます。このインデクサはフルステップ、ハーフステップ、1/4、1/8、1/16、1/32、1/64、1/128、1/256 マイクロステッピングを実行できます。マイクロステッピングが大きいほど、可聴ノイズの低減とスムーズな動作が大きく向上します。自動マイクロステッピング・モードでは、入力ステップ周波数が高分解能に補間されるため、コントローラからの低周波数ステップ入力を使用して動作しながら、電流レギュレーションが改善され、可聴ノイズが低減されます。カスタム・マイクロステッピング表を使用すると、特定のモーターのニーズに合わせて電流波形を調整できます。

ステッパ・モーター・ドライバは、低速減衰、混合減衰、高速減衰など、いくつかの種類の減衰モードを実装することにより、巻線電流を再循環する必要があります。DRV8452 はスマート・チューン減衰モードをサポートしています。スマート・チューンは革新的な減衰メカニズムで、電源電圧、モーター速度のばらつきや経年変化の影響に関係なく、最適な電流レギュレーション性能が得られるよう、自動的に調整を行います。スマート・チューン・リップル・コントロールは、オフ時間可変型のリップル電流制御方式を採用し、モーター巻線電流の歪みを最小限に抑えることができます。スマート・チューン・ダイナミック減衰では、固定オフ時間のダイナミック高速減衰割合方式が使用されます。スマート・チューン減衰モードに加えて、DRV8452 は静止時にノイズのない動作を実現するためのサイレント・ステップ減衰モードと、低速の回転速度にも対応しています。

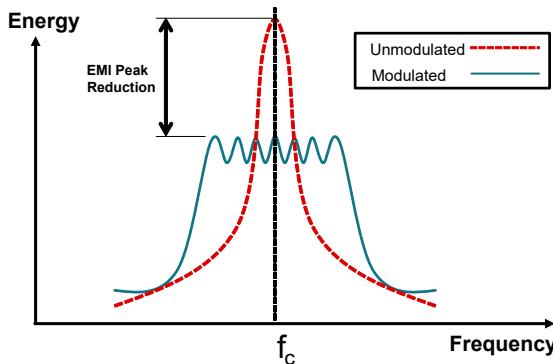

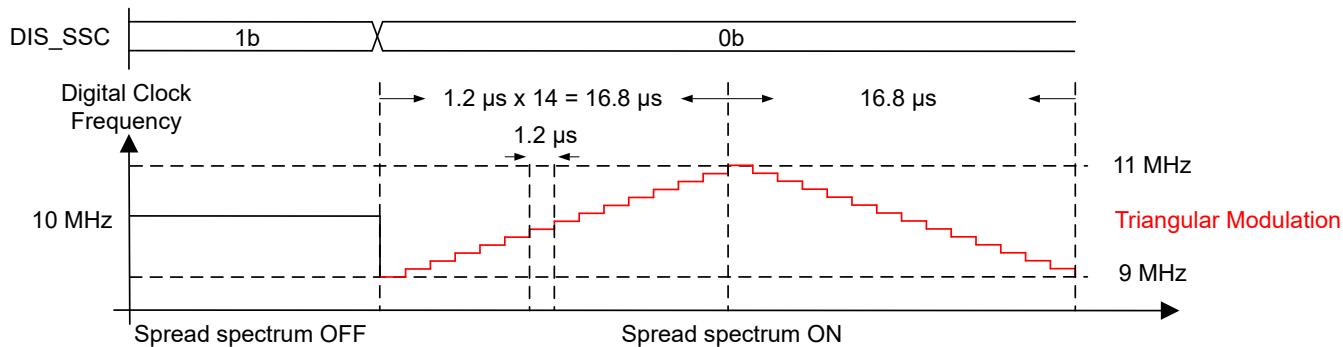

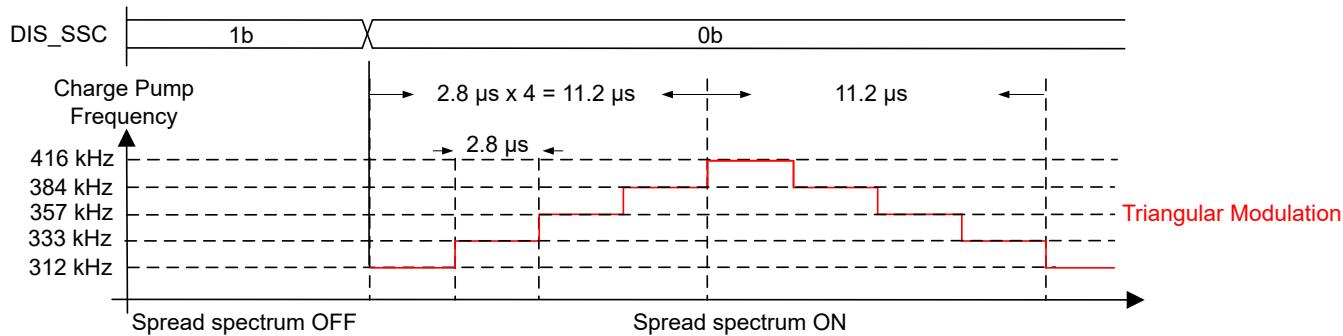

本デバイスは、内蔵デジタル発振器と内蔵チャージ・ポンプのための拡散スペクトラム・クロック処理機能を備えています。この機能により、本デバイスからの電磁放射を最小限に抑えることができます。また、低消費電力スリープ・モードを搭載しているため、モーターをアクティブに駆動していないときにシステムの電力を節約できます。

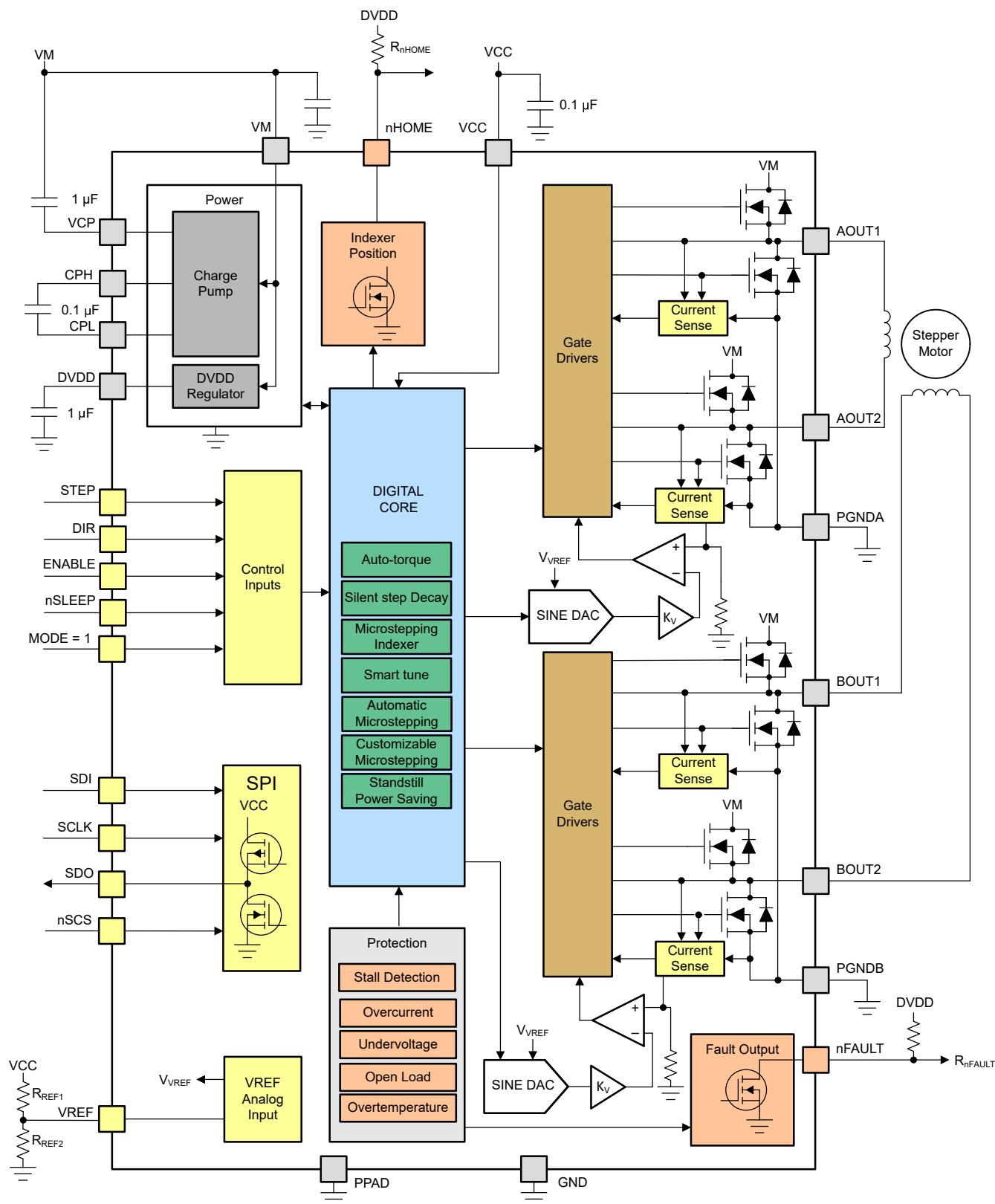

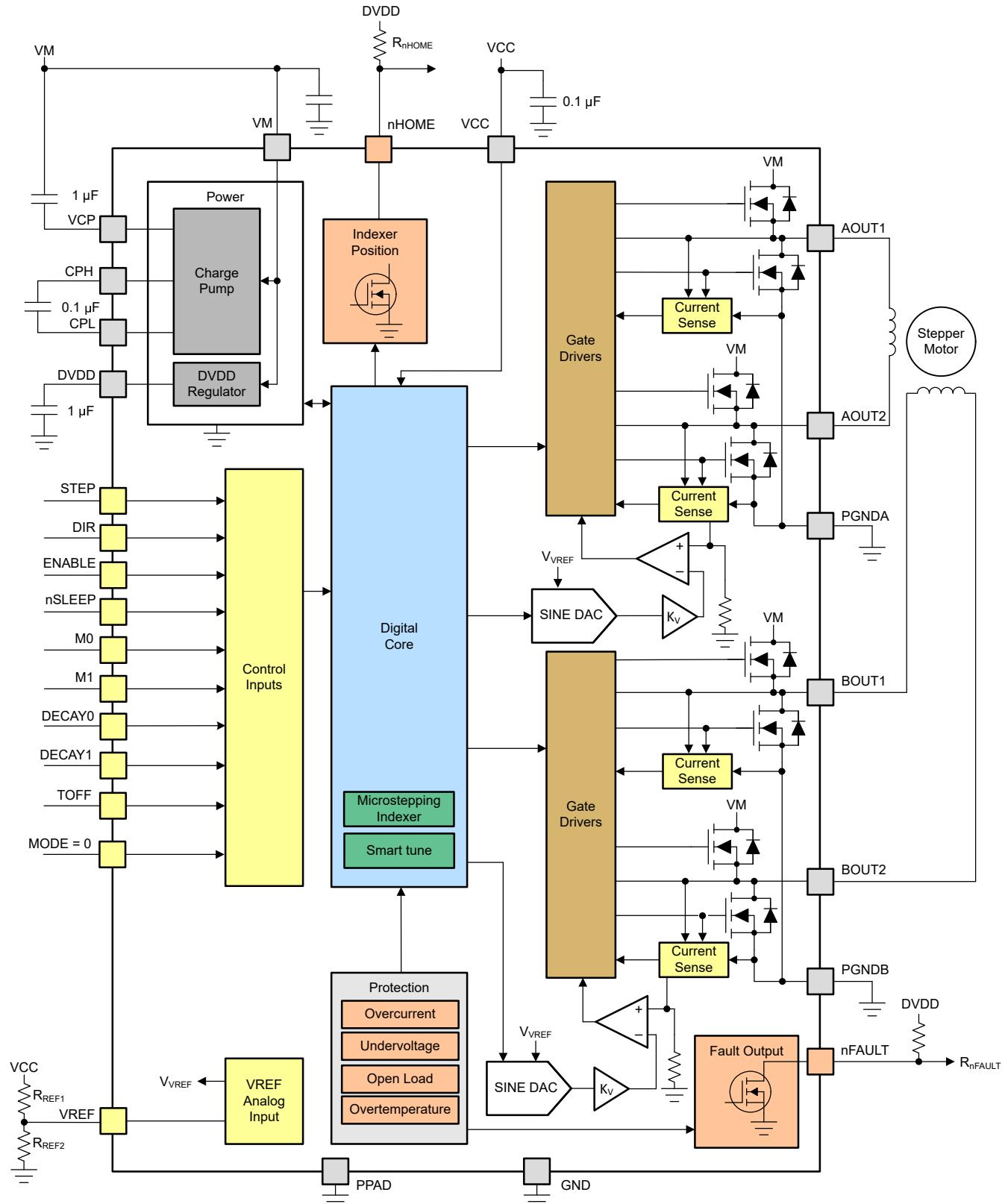

## 7.2 機能ブロック図

図 7-1. SPI インターフェイスを使用する DRV8452 のブロック図

図 7-2. H/W インターフェイスを使用する DRV8452 のブロック図

## 7.3 機能説明

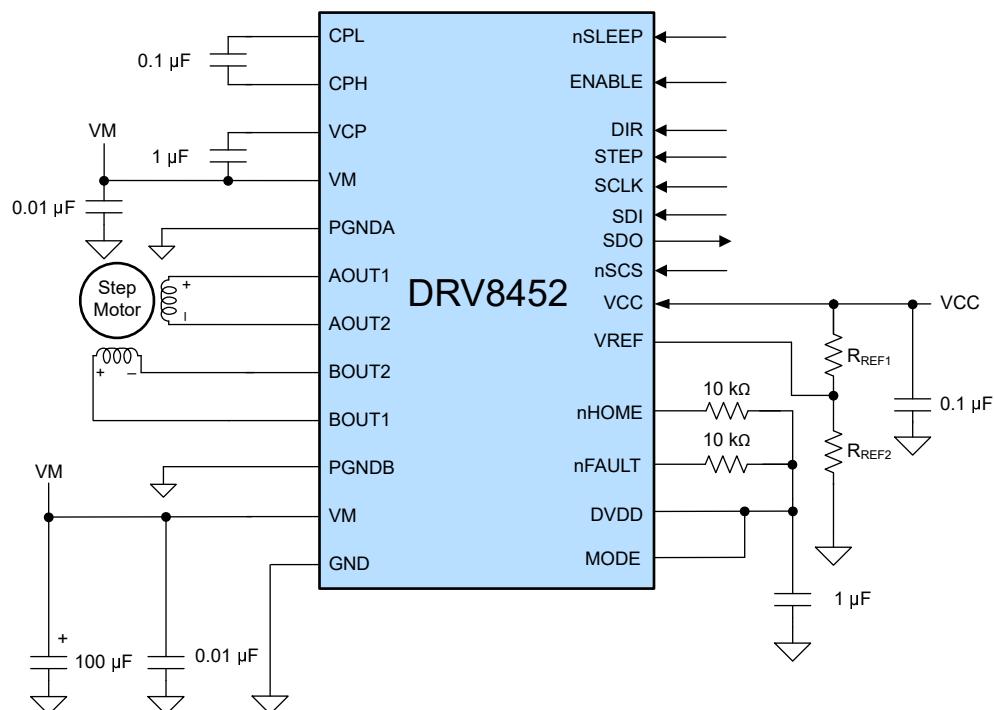

DRV8452 の推奨外付け部品を、[表 7-1](#) に示します。

**表 7-1. 外付け部品**

| 部品                          | ピン 1         | ピン 2         | 推奨事項                                          |

|-----------------------------|--------------|--------------|-----------------------------------------------|

| C <sub>VM1</sub>            | VM           | PGNDA        | X7R、0.01μF、VM 定格セラミック・コンデンサ                   |

| C <sub>VM2</sub>            | VM           | PGNDB        | X7R、0.01μF、VM 定格セラミック・コンデンサ                   |

| C <sub>VM3</sub>            | VM           | PGNDA        | パルク、VM 定格コンデンサ                                |

| C <sub>VCP</sub>            | VCP          | VM           | X7R、1μF、16V セラミック・コンデンサ                       |

| C <sub>SW</sub>             | CPH          | CPL          | X7R、0.1μF、VM 定格セラミック・コンデンサ                    |

| C <sub>DVDD</sub>           | DVDD         | GND          | X7R、1μF、6.3V セラミック・コンデンサ                      |

| C <sub>VCC</sub>            | VCC          | GND          | X7R、0.1μF、6.3V セラミック・コンデンサ                    |

| R <sub>nFAULT</sub>         | DVDD または VCC | nFAULT       | 10kΩ の抵抗                                      |

| R <sub>nHOME</sub> (DDW 専用) | DVDD または VCC | nHOME        | 10kΩ の抵抗                                      |

| R <sub>REF1</sub>           | VREF         | DVDD または VCC | チョッピング電流を設定するための抵抗。VREF_INT_EN = 1b の場合は不要です。 |

| R <sub>REF2</sub>           | VREF         | GND          |                                               |

### 7.3.1 動作インターフェイス

DRV8452 は、ハードウェア (H/W) ピン・インターフェイス、または SPI インターフェイスで動作できます。SPI インターフェイスで動作する場合、デバイスは [表 7-4](#) に示す追加機能と詳細な診断機能をサポートします。

DDW パッケージ・オプションの場合、ロジック・レベルの MODE ピンは、電源投入時または nSLEEP サイクルの後で、動作しているインターフェイスの情報をラッチします。

- この時点での MODE ピンがグランドに接続されていれば、デバイスはハードウェア・ピン・インターフェイスで動作します。

- この時点での MODE ピンがロジック High の場合、デバイスは SPI インターフェイスで動作します。

#### 注

電源投入後または nSLEEP = 1 となった後、MODE ピンのロジック・レベルをすぐに変更しないでください。

5 本のピンの機能は、[表 7-2](#) および [表 7-3](#) に示すように、動作インターフェイスによって異なります。

**表 7-2. ピン機能、DDW パッケージ**

| ピン番号 | ハードウェア・インターフェイス | SPI インターフェイス |

|------|-----------------|--------------|

| 34   | M0              | nSCS         |

| 35   | TOFF            | 予約済み         |

| 36   | DECAY1          | SDO          |

| 37   | DECAY0          | SDI          |

| 38   | M1              | SCLK         |

**表 7-3. ピンの機能、PWP パッケージ**

| ピン番号 | DRV8452SPWPR (SPI インターフェイス) | DRV8452PWPR (ハードウェア・インターフェイス) |

|------|-----------------------------|-------------------------------|

| 18   | nSCS                        | M0                            |

**表 7-3. ピンの機能、PWP パッケージ (continued)**

| ピン番号 | DRV8452SPWPR (SPI インターフェイス) | DRV8452PWPR (ハードウェア・インターフェイス) |

|------|-----------------------------|-------------------------------|

| 19   | VCC                         | TOFF                          |

| 20   | SDO                         | DECAY1                        |

| 21   | SDI                         | DECAY0                        |

| 22   | SCLK                        | M1                            |

表 7-4 は、2 つの動作インターフェイスの機能セットと診断機能を比較したものです。

**表 7-4. 機能セットの違い**

| 機能                   | ハードウェア・インターフェイス | SPI インターフェイス |

|----------------------|-----------------|--------------|

| スマート・チューン            | あり              | あり           |

| 最大 1/256 のマイクロステッピング | あり              | あり           |

| VCC ロジック電源           | あり              | あり           |

| nHOME 出力             | あり              | あり           |

| nFAULT 出力            | あり              | あり           |

| 自動マイクロステッピング         | なし              | あり           |

| カスタマイズ可能なマイクロステッピング  | なし              | あり           |

| インデクサ出力              | なし              | あり           |

| 内部 3.3V リファレンス電圧     | なし              | あり           |

| デュアル・ステップ・アクティブ・エッジ  | なし              | あり           |

| サイレント・ステップ減衰         | なし              | あり           |

| 自動トルク                | なし              | あり           |

| 静止電力節約               | なし              | あり           |

| スペクトラム拡散             | なし              | あり           |

| 保護機能                 |                 |              |

| VM および VCP UVLO      | あり              | あり           |

| VCC パワーオン・リセット       | あり              | あり           |

| 過電流保護                | あり              | あり           |

| 開放負荷検出               | あり              | あり           |

| サーマル・シャットダウン         | あり              | あり           |

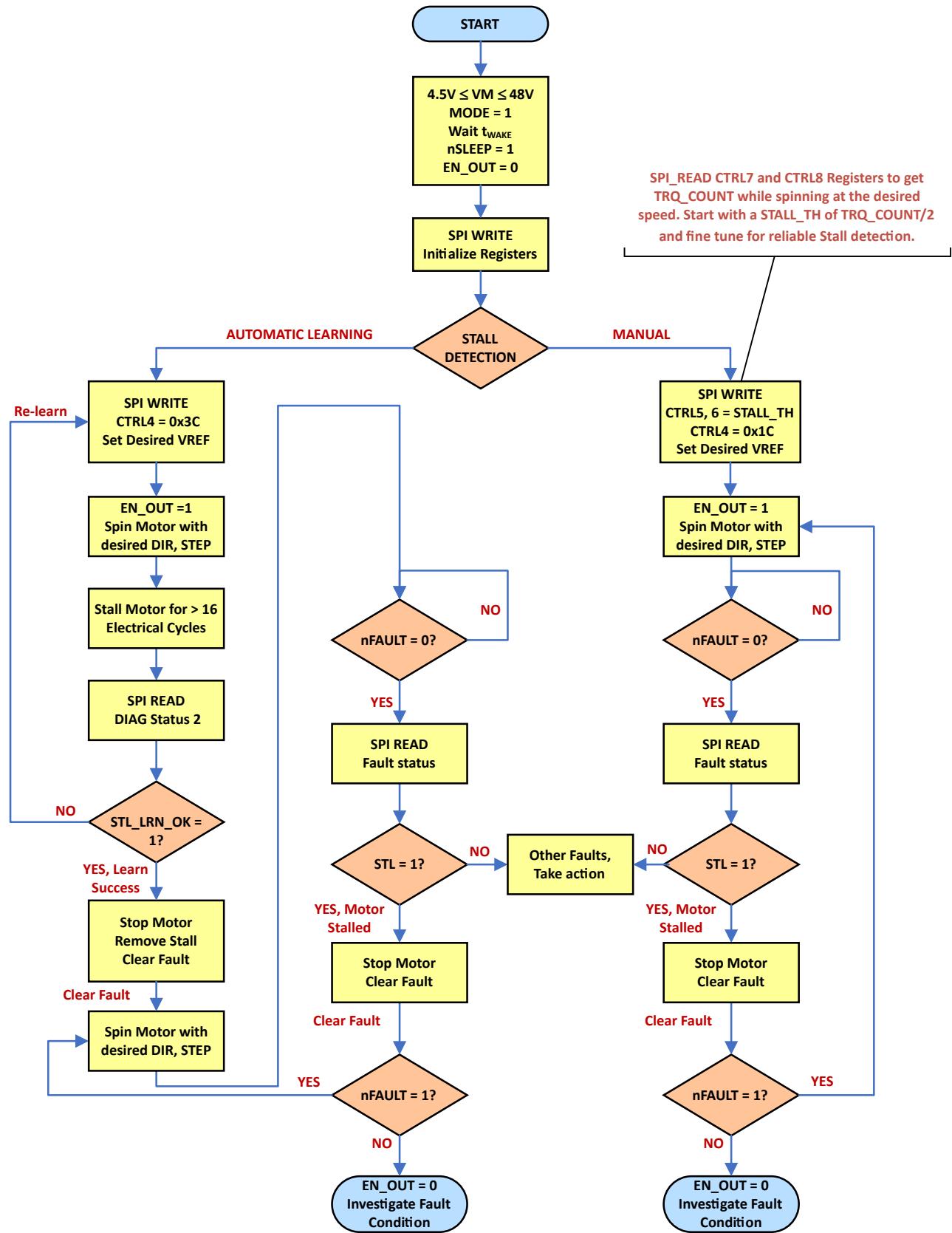

| ストール検出               | なし              | あり           |

| 過熱警告                 | なし              | あり           |

### 7.3.2 ステッパ・モーター・ドライバの電流定格

ステッパ・モーター・ドライバは、出力電流を表す 3 種類の数値 (ピーク、RMS、フルスケール) を使用して分類できます。

#### 7.3.2.1 ピーク電流定格

ステッパ・ドライバのピーク電流は、過電流保護トリップ・スレッショルド  $I_{OCP}$  で制限されます。一般に、 $I_{OCP}$  の最小値は、ステッパ・モーター・ドライバのピーク電流定格を規定します。DRV8452 の場合、ピーク電流定格はブリッジごとに 7.6A です。

### 7.3.2.2 RMS 電流定格

RMS 電流は、IC の熱性能を考慮して決定します。RMS 電流は、25°Cの代表的なシステムでの  $R_{DS(ON)}$ 、立ち上がりおよび立ち下がり時間、PWM 周波数、デバイスの静止電流、パッケージの熱的性能に基づいて計算されます。実動作時の RMS 電流は放熱と周囲温度に応じて上下する場合があります。DDW パッケージの DRV8452 の場合、RMS 電流定格はブリッジあたり 3.5A です。PWP パッケージの場合、RMS 電流定格はブリッジあたり 2.8A です。

### 7.3.2.3 フルスケール電流定格

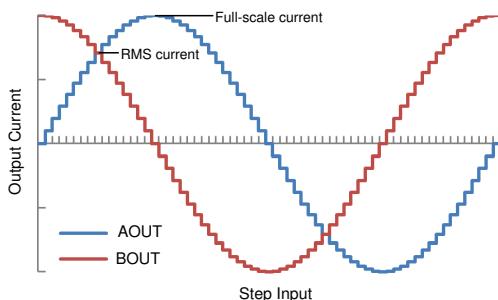

フルスケール電流とは、マイクロステッピング時の正弦波電流波形の最大値を指します。この正弦波振幅は RMS 電流に関係しているため、フルスケール電流もデバイスの熱性能を考慮して求めます。フルスケール電流定格は、正弦波電流波形の場合は約  $\sqrt{2} \times I_{RMS}$ 、方形波電流波形（フルステップ）の場合は  $I_{RMS}$  です。

図 7-3. フルスケール電流と RMS 電流

### 7.3.3 PWM モーター・ドライバ

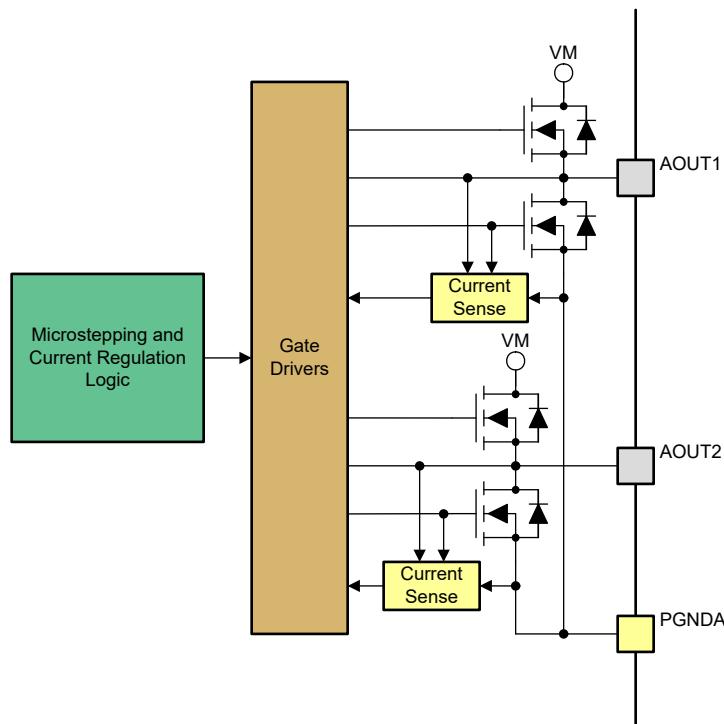

DRV8452 には、バイポーラ・ステッパ・モーターの 2 つの巻線を駆動するため、2 つのフル H ブリッジのドライバがあります。図 7-4 に、この回路のブロック図を示します。

図 7-4. PWM モーター・ドライバのブロック図

### 7.3.4 マイクロステッピング・インデクサ

本デバイスの内蔵インデクサ・ロジックを使用すると、各種ステップ・モードに対応できます。表 7-5 に示すように、SPI レジスタの MICROSTEP\_MODE ビット、または M0 と M1 ピンを使用して、ステップ・モードを設定します。

**表 7-5. マイクロステッピング・インデクサの設定**

| MODE = 1       | MODE = 0   |                    |                          |

|----------------|------------|--------------------|--------------------------|

| MICROSTEP_MODE | M0         | M1                 | ステップ・モード                 |

| 0000b          | 0          | 0                  | 100% 電流によるフルステップ (2 相励磁) |

| 0001b          | 0          | 330kΩ を GND との間に接続 | 71% 電流によるフルステップ (2 相励磁)  |

| 0010b          | 1          | 0                  | 非循環 1/2 ステップ             |

| 0011b          | ハイ・インピーダンス | 0                  | 1/2 ステップ                 |

| 0100b          | 0          | 1                  | 1/4 ステップ                 |

| 0101b          | 1          | 1                  | 1/8 ステップ                 |

| 0110b          | ハイ・インピーダンス | 1                  | 1/16 ステップ                |

| 0111b          | 0          | ハイ・インピーダンス         | 1/32 ステップ                |

| 1000b          | ハイ・インピーダンス | 330kΩ を GND との間に接続 | 1/64 ステップ                |

| 1001b          | ハイ・インピーダンス | ハイ・インピーダンス         | 1/128 ステップ               |

| 1010b          | 1          | ハイ・インピーダンス         | 1/256 ステップ               |

表 7-6 に示すように、SPI インターフェイスで動作している場合、このデバイスでは SPI インターフェイス上でもステッピングと方向の変更を行うことができます。この機能のために、次の 4 ビットが専用で使用されています。

**表 7-6. SPI 上での STEP および DIR 制御**

| ビット      | 0b (デフォルト)                   | 1b                                                      |

|----------|------------------------------|---------------------------------------------------------|

| SPI_DIR  | ドライバは、DIR ピンの入力に基づいて方向を変更します | 方向の変化は、DIR ピットによって異なります                                 |

| SPI_STEP | ステッピングは、STEP ピンの入力に依存します     | ステップの変化は、STEP ピットによって異なります                              |

| DIR      | モーターは逆方向に移動します               | モーターは順方向に移動します                                          |

| STEP     | X                            | インデクサは 1 ステップ進みます。STEP ピットは「1」が書き込まれた後、自己クリアされ「0」になります。 |

表 7-7 に、DIR ピンが論理 High または DIR ピットが「1」の場合のフルステップ (71% 電流)、1/2 ステップ、1/4 ステップ、1/8 ステップ動作の相対電流とステップ方向を示します。マイクロステッピングの分解能がより高い場合も同じパターンに従います。AOUT 電流は電気角の正弦、BOUT 電流は電気角の余弦です。正電流は、駆動時に xOUT1 ピンから xOUT2 ピンに流れる電流と定義します。

**表 7-7. 電流の相対値とステップ方向**

| 1/8 ステップ | 1/4 ステップ | 1/2 ステップ | フルステップ 71% | AOUT 電流<br>(フルスケールに対する %) | BOUT 電流<br>(フルスケールに対する %) | 電気角 (度) |

|----------|----------|----------|------------|---------------------------|---------------------------|---------|

| 1        | 1        | 1        |            | 0%                        | 100%                      | 0.00    |

| 2        |          |          |            | 20%                       | 98%                       | 11.25   |

| 3        | 2        |          |            | 38%                       | 92%                       | 22.50   |

| 4        |          |          |            | 56%                       | 83%                       | 33.75   |

| 5        | 3        | 2        | 1          | 71%                       | 71%                       | 45.00   |

| 6        |          |          |            | 83%                       | 56%                       | 56.25   |

| 7        | 4        |          |            | 92%                       | 38%                       | 67.50   |

| 8        |          |          |            | 98%                       | 20%                       | 78.75   |

| 9        | 5        | 3        |            | 100%                      | 0%                        | 90.00   |

| 10       |          |          |            | 98%                       | -20%                      | 101.25  |

| 11       | 6        |          |            | 92%                       | -38%                      | 112.50  |

| 12       |          |          |            | 83%                       | -56%                      | 123.75  |

| 13       | 7        | 4        | 2          | 71%                       | -71%                      | 135.00  |

| 14       |          |          |            | 56%                       | -83%                      | 146.25  |

| 15       | 8        |          |            | 38%                       | -92%                      | 157.50  |

| 16       |          |          |            | 20%                       | -98%                      | 168.75  |

| 17       | 9        | 5        |            | 0%                        | -100%                     | 180.00  |

| 18       |          |          |            | -20%                      | -98%                      | 191.25  |

| 19       | 10       |          |            | -38%                      | -92%                      | 202.50  |

| 20       |          |          |            | -56%                      | -83%                      | 213.75  |

| 21       | 11       | 6        | 3          | -71%                      | -71%                      | 225.00  |

| 22       |          |          |            | -83%                      | -56%                      | 236.25  |

| 23       | 12       |          |            | -92%                      | -38%                      | 247.50  |

| 24       |          |          |            | -98%                      | -20%                      | 258.75  |

| 25       | 13       | 7        |            | -100%                     | 0%                        | 270.00  |

| 26       |          |          |            | -98%                      | 20%                       | 281.25  |

| 27       | 14       |          |            | -92%                      | 38%                       | 292.50  |

| 28       |          |          |            | -83%                      | 56%                       | 303.75  |

| 29       | 15       | 8        | 4          | -71%                      | 71%                       | 315.00  |

| 30       |          |          |            | -56%                      | 83%                       | 326.25  |

| 31       | 16       |          |            | -38%                      | 92%                       | 337.50  |

| 32       |          |          |            | -20%                      | 98%                       | 348.75  |

表 7-8 に、DIR = 1 の場合の 100% フルスケール電流でのフルステップ動作を示します。このステッピング・モードは、71% の電流によるフルステップ・モードよりも多くの電力を消費しますが、高いモーター RPM で高トルクを実現できます。

**表 7-8. 100% 電流によるフルステップ**

| フルステップ 100% | AOUT 電流<br>(フルスケールに対する %) | BOUT 電流<br>(フルスケールに対する %) | 電気角 (度) |

|-------------|---------------------------|---------------------------|---------|

| 1           | 100                       | 100                       | 45      |

| 2           | 100                       | -100                      | 135     |

| 3           | -100                      | -100                      | 225     |

| 4           | -100                      | 100                       | 315     |

表 7-9 に、DIR = 1 の場合の非循環 1/2 ステップ動作を示します。このステッピング・モードは真円 1/2 ステップ動作よりも多くの電力を消費しますが、高いモーター RPM で高トルクを実現できます。

**表 7-9. 非循環 1/2 ステッピング電流**

| 非循環 1/2 ステップ | AOUT 電流<br>(フルスケールに対する %) | BOUT 電流<br>(フルスケールに対する %) | 電気角 (度) |

|--------------|---------------------------|---------------------------|---------|

| 1            | 0                         | 100                       | 0       |

| 2            | 100                       | 100                       | 45      |

| 3            | 100                       | 0                         | 90      |

| 4            | 100                       | -100                      | 135     |

| 5            | 0                         | -100                      | 180     |

| 6            | -100                      | -100                      | 225     |

| 7            | -100                      | 0                         | 270     |

| 8            | -100                      | 100                       | 315     |

表 7-10 に示すように、SPI インターフェイスで動作している場合、STEP\_EDGE ビットに応じて、STEP アクティブ・エッジを立ち上がりエッジにするか、または立ち上がりエッジと立ち下がりエッジの両方にすることができます。H/W インターフェイスを使用して構成した場合、STEP アクティブ・エッジは立ち上がりエッジのみになります。高い入力 STEP レートで実行する必要のあるアプリケーションでは、両方のエッジをアクティブ・エッジとして構成すると、入力 STEP レートは実質的に 2 倍になるため、コントローラのオーバーヘッドが半分に減少します。

**表 7-10. STEP アクティブ・エッジ**

| インターフェイス | STEP_EDGE  | STEP アクティブ・エッジ    |

|----------|------------|-------------------|

| SPI      | 0b (デフォルト) | 立ち上がりエッジ          |

|          | 1b         | 立ち上がりエッジと立ち下がりエッジ |

| H/W      | X          | 立ち上がりエッジ          |

STEP 入力の各アクティブ・エッジのタイミングで、インデクサは表の次の状態に進みます。この方向は、DIR ピンがロジック High の場合です。DIR ピンがロジック Low の場合、表のシーケンスは反転します。ステップ中にステップ・モードが動的に変更された場合、STEP のアクティブ・エッジで、インデクサは次の有効な状態に進み、新しいステップ・モード設定になります。

電源投入後、ロジック低電圧誤動作防止の終了後、またはスリープ・モードの終了後、インデクサは両方のコイルの 71% のフルスケール電流に相当する、45° の電気角で初期励起状態 (ホーム位置) に移動します。このような場合、すべてのレジスタが各デフォルト値に復元されます。

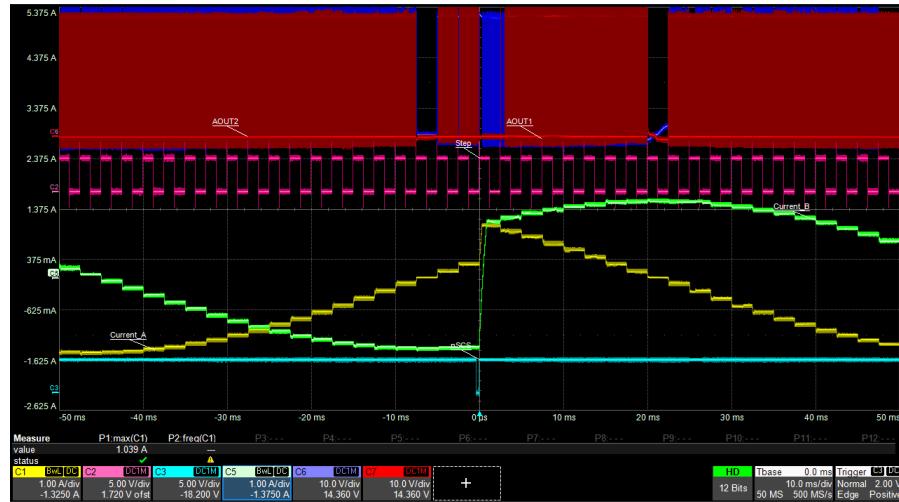

SPI インターフェイスで動作しているとき、IDX\_RST ビットが「1b」の場合、図 7-5 に示すようにインデクサは 45° の電気角にリセットされますが、メモリ・マップ・レジスタの内容は変更されません。

波形パターンは上から下へ順に:AOUT2、AOUT1、STEP、コイル B 電流、コイル A 電流、nSCS

図 7-5. インデクサ・リセット

STEP 入力周波数がジッタすると、ストール検出の目的でデバイスの信号はフィルタリングされます。表 7-11 に示すように、FRQ\_CHG ビットと STEP\_FRQ\_TOL ビットでフィルタ設定をプログラムします。2% のフィルタリングは、中心周波数付近で最大 2% のジッタがフィルタリングされ、内部回路がモーターのストールを検出するためのクリーンな STEP 信号を生成することを意味します。

表 7-11. STEP 周波数のフィルタリング

| FRQ_CHG    | STEP_FRQ_TOL | フィルタリング   |

|------------|--------------|-----------|

| 0b (デフォルト) | 00b          | 1%        |

|            | 01b (デフォルト)  | 2%        |

|            | 10b          | 4%        |

|            | 11b          | 6%        |

| 1b         | X            | フィルタリングなし |

### 7.3.5 インデクサ出力

DRV8452 には INDEX レジスタが搭載されており、予測されるマイクロステップ電流とモータの位置をユーザーに示します。

- CUR\_A\_POS レジスタと CUR\_A\_SIGN ビットは、インデクサ・テーブル内のコイル A 電流の位置を示します。

- CUR\_B\_POS レジスタと CUR\_B\_SIGN ビットは、インデクサ・テーブル内のコイル B 電流の位置を示します。

- CUR\_A レジスタは、予測されるコイル A 電流の値を示します。この電流は  $\sin(90^\circ \times \text{CUR\_A\_POS} / 255)$  です。

- 対応する符号ビットが「1b」の場合、電流は正となり、符号ビットが「0b」の場合、電流は負となります。

表 7-12 に、1/256 マイクロステッピングに対応する電流波形に対する CUR\_A\_POS および CUR\_B\_POS レジスタの出力を示します。

表 7-12. インデクサ出力表

| 電流象限                | CUR_A_POS | CUR_A_SIGN | CUR_B    | CUR_B_SIGN |

|---------------------|-----------|------------|----------|------------|

| 第 1 象限 (0°->90°)    | 0 -> 255  | 1b         | 255 -> 0 | 1b         |

| 第 2 象限 (90°->180°)  | 255 -> 0  | 1b         | 0 -> 255 | 0b         |

| 第 3 象限 (180°->270°) | 0 -> 255  | 0b         | 255 -> 0 | 0b         |

**表 7-12. インデクサ出力表 (continued)**

| 電流象限                                         | CUR_A_POS           | CUR_A_SIGN | CUR_B               | CUR_B_SIGN |

|----------------------------------------------|---------------------|------------|---------------------|------------|

| 第 4 象限 ( $270^\circ \rightarrow 360^\circ$ ) | 255 $\rightarrow$ 0 | 0b         | 0 $\rightarrow$ 255 | 1b         |

インデクサ出力と nHOME 信号を組み合わせることにより、電波内のモーターの位置を特定できます。これをエンコーダ出力と比較することで、ステップ損失など、モーターの動作との不一致を検出できます。

### 7.3.5.1 nHOME 出力

DDW パッケージでは、マイクロステッピング・インデクサが両方のコイルでフルスケール電流の 71% に対応するホーム位置 (電気角  $45^\circ$ ) に達すると、オープン・ドレインの nHOME 出力が Low にプルされます。それ以外の場合はすべて、nHOME 出力が High にプルされます。さらに、デバイスが SPI インターフェイスで動作している場合、インデクサがホーム位置に達すると、SPI レジスタの NHOMEx ビットが「0b」になります。

そのため、nHOME 出力は電気的回転ごとに 1 つの低パルス、つまり、図 7-6 に示すように、4 つのフルステップごとに 1 つのパルスを出力します。したがって、nHOME の Low パルスは、4 フルステップごとに定義されたモーターの位置に対応します。nHOME と機械式ホーム・スイッチを組み合わせることで、モーターのホーム位置をより高精度に設定できます。

プルアップ抵抗を使用して、nHOME を 5V、3.3V、1.8V の電源にプルアップします。5V にプルアップする場合は、nHOME ピンから抵抗を介して DVDD ピンに接続できます。3.3V または 1.8V にプルアップする場合は、外部電源を使う必要があります。

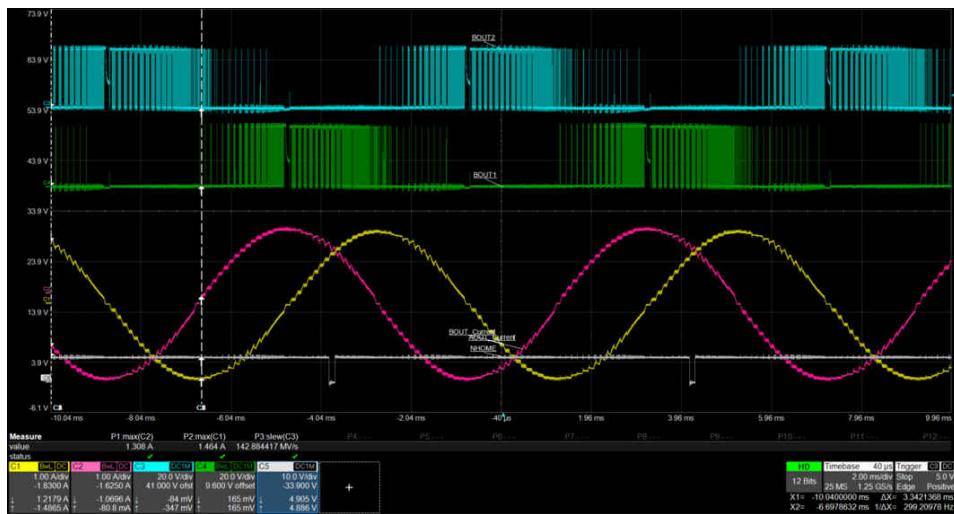

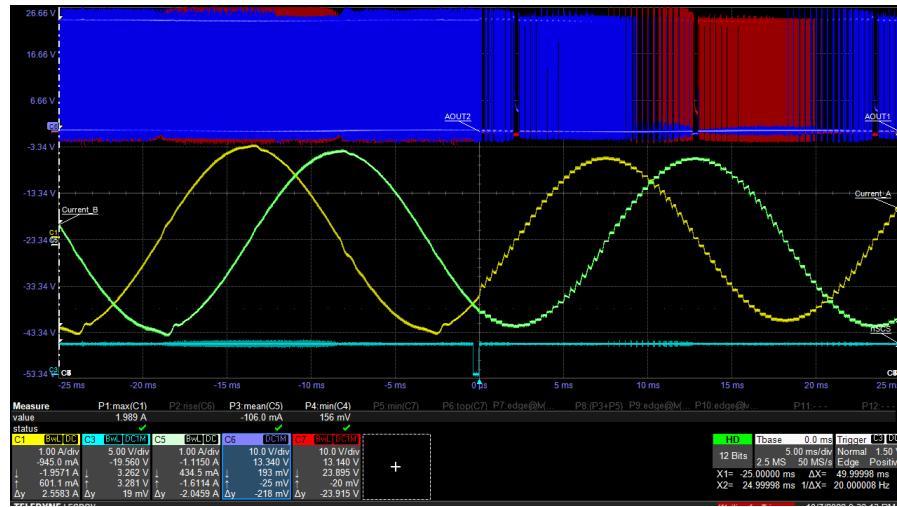

波形パターンは上から下へ順に:BOUT2、BOUT1、コイル B 電流、コイル A 電流、nHOME

**図 7-6. nHOME 出力の波形**

### 7.3.6 自動マイクロステッピング・モード

DRV8452 が SPI インターフェイスで動作しているとき、自動マイクロステッピング・モードは入力ステップ・パルスを補間し、より高い分解能のマイクロステップに対応する電流波形を生成します。これによって、スムーズな正弦波電流が得られ、あらゆるステップ周波数でノイズのない動作が可能になります。

- 自動マイクロステッピングがディセーブルの場合、システム・コントローラは強制的に高周波数のステップ信号を出力して、高い分解能のマイクロステッピング電流波形を生成します。

- 自動マイクロステッピングがイネーブルの場合、低周波数のステップ信号によって滑らかな電流波形を生成することができます。

- これにより、コントローラのオーバーヘッドは大幅に減少するため、3D プリンタや工場のオートメーション、医療機器などのアプリケーションに有用です。

- 補間された周波数は、ステッパー・モーターの共振周波数帯域まで下降しないことに注意してください。

自動マイクロステッピング・モードをイネーブルにするには、EN\_AUTO ビットを「1b」にする必要があります。

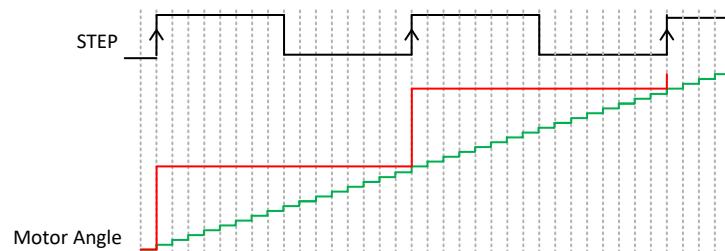

図 7-7. 自動マイクロステッピングによる補間

図 7-7 に、自動マイクロステッピングを使用した場合と使用しない場合のモーター角の増加を示します。自動マイクロステッピングを使用しない場合（赤線）、モーター角はステップ入力のアクティブ・エッジごとに大きく増加します。自動マイクロステッピングを使用すると（緑線）、モーター角は非常に滑らかに変化します。

DRV8452 は、1/32、1/64、1/128、1/256 マイクロステッピング・レベルへの補間をサポートしており、この設定は [表 7-13](#) に示すように、RES\_AUTO ビットで行われます。補間設定は、実行中に変更できます。

表 7-13. 自動マイクロステッピングの補間レベル

| RES_AUTO    | 補間    |

|-------------|-------|

| 00b (デフォルト) | 1/256 |

| 01b         | 1/128 |

| 10b         | 1/64  |

| 11b         | 1/32  |

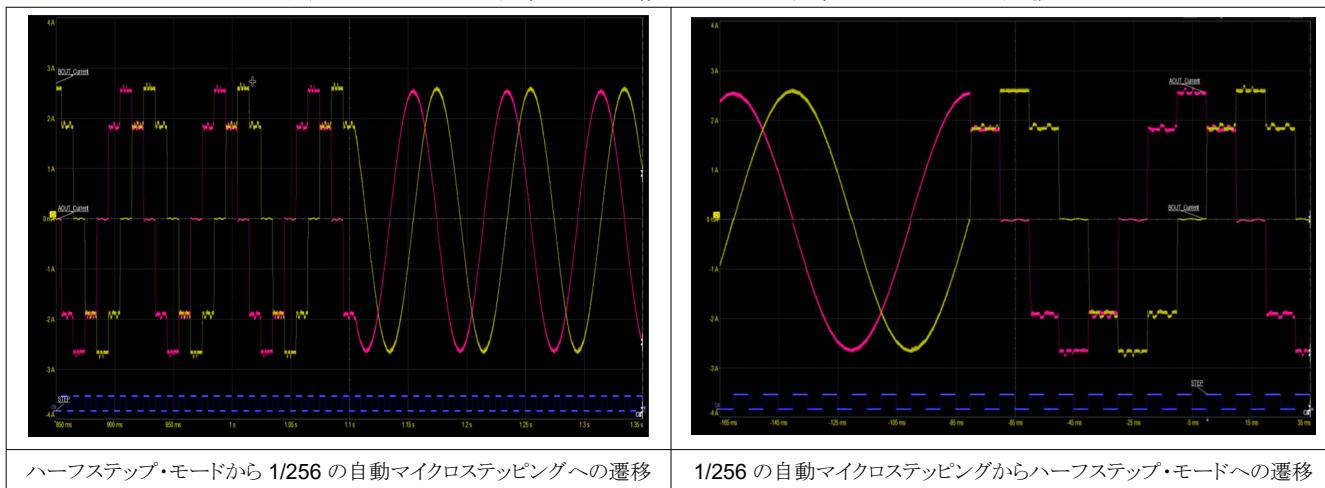

表 7-14 は、コイル電流、および EN\_AUTO ビットにそれぞれ「1b」と「0b」を書き込むことによるハーフステップ・モードと自動マイクロステッピング・モードの滑らかな遷移を示しています。ハーフステップと 1/256 の自動マイクロステッピング・モードでは、ステップ周波数は同じであることに注意してください。

表 7-14. ハーフステップと自動マイクロステッピングの間の遷移

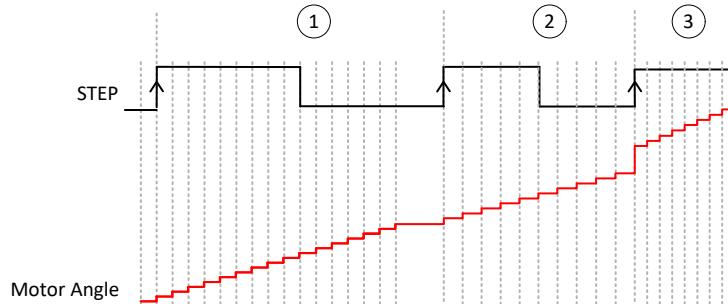

図 7-8. ステップ周波数を変化させたときの自動マイクロステッピング

図 7-8 に示すように、補間は前の 2 つのステップ・パルス間の時間に基づいて行われます。前のインターバル時間は、RES\_AUTO ビットの設定に応じて、均等に補間されます。

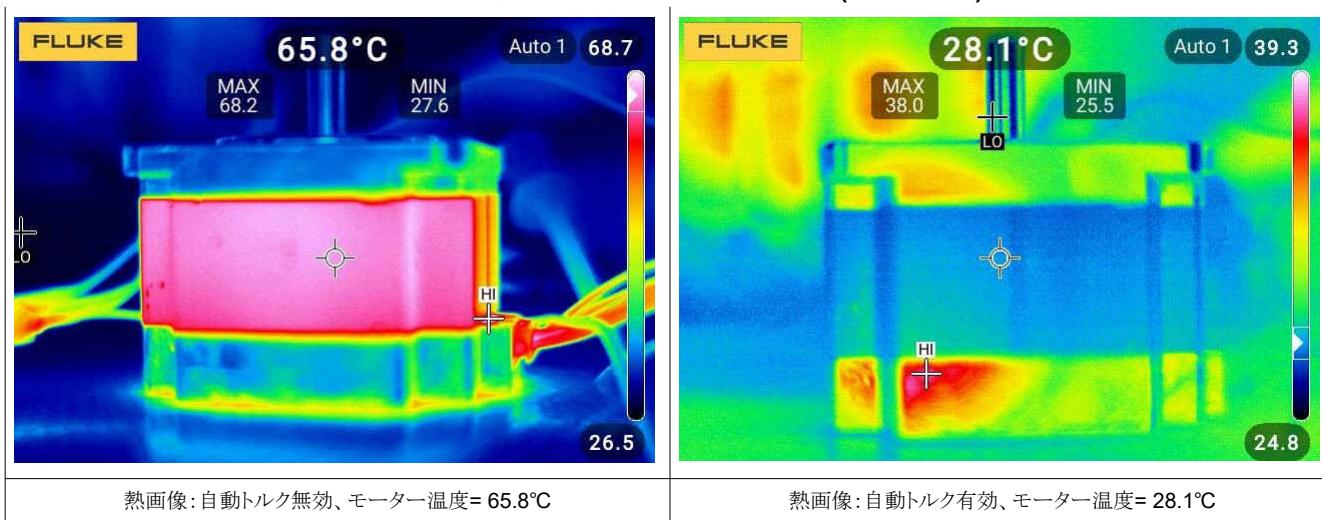

入力ステップ周波数が前のインターバルから低下する場合(図のセグメント「1」)、モーターは次のステップのアクティブ・エッジが発生するまで、同じポジションを維持します。EN\_STSL ビットが「1b」で、t<sub>STSL\_DLY</sub> が経過するまでに次のアクティブ・エッジが発生しなかった場合、デバイスは静止電力節約モードに移行します。次にステップのアクティブ・エッジが発生すると、静止電力節約モードは終了します。

前のインターバルからステップ周波数が増加する場合(図のセグメント「2」)、次のステップのアクティブ・エッジが来ると、モーター角はスムーズに自動補正され、インデクサはステップ入力に応じたポジションに移動します。セグメント「3」では、モーター角はセグメント「2」のステップ周波数に対応して、より高速に増加します。

#### 注

- 自動マイクロステッピング・モードでは、ステップ入力の周波数が 10Hz から 300kHz の間であることが必要です。

- 10Hz 未満のフルステップ相当のステップ周波数で自動マイクロステッピングを実現するには、自動マイクロステッピングを有効にする前に、より高い分解能のマイクロステッピング設定を使用します。

- たとえば、フルステップ・モードでの 1Hz のステップ周波数は、1/16 マイクロステッピング・モードでの 16Hz のステップ周波数に相当します。そのため、フルステップで 1Hz のステップ入力で自動マイクロステッピングを使用する場合は、MICROSTEP\_MODE を 0110b (1/16 マイクロステップ) に設定し、RES\_AUTO ビットを使用して希望の補間レベルを実現できます。

### 7.3.7 カスタム・マイクロステッピング表

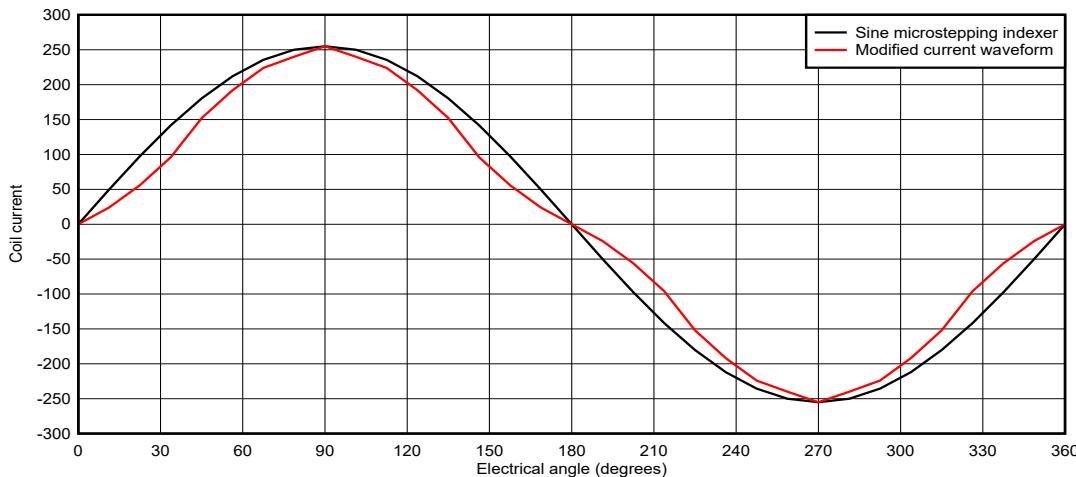

ステッパ・モーター・システムの性能と可聴ノイズは、モーターと負荷の両方から発生するトルク・リップルによって異なります。トルク・リップルは、各マイクロステップにおけるトルクの変動によって定義されます。ほとんどのステッパ・モーターでは、標準的な正弦波マイクロステップ・インデクサで十分なトルク・リップルを実現し、最適な性能を達成できます。

ただし、モーターと負荷トルクの組み合わせによっては、電流プロファイルを変更するとトルク・リップルが減少し、振動と可聴ノイズが低減されます。適切にプログラムすると、カスタマイズされた電流波形により、一定のトルクでマイクロステップ位置が等間隔に配置されるため、最適な位置精度が確保されます。

たとえば、永久磁石モーターの場合、ステップ角 (3.6°~18°) がハイブリッド・モーター (0.9° または 1.8°) より大きいため、トルクの変動がより顕著になります。固定子歯の数が少ないため、ローターが 2 枚の固定子歯の間にいると、固定子歯とローターの間で作用するフランクスは少量になります。これらの中間位置で電流レベルが上昇すると、デフォルトの正弦波インデクサに比べてトルク・リップルが小さくなります。

DRV8452 には、特定のモーターの要件に合わせてマイクロステッピング電流プロファイルをカスタマイズするためのルックアップ・テーブルがあります。変更された電流プロファイルは、EN\_CUSTOM に「1」を書き込むことで、デフォルトの正弦波プロファイルの代わりに使用されます。カスタム・マイクロステッピング・モードでのステップ入力の周波数は、300kHz を超えないようにする必要があります。補間プロセスの詳細を以下に示します。

- ユーザーは、1/8 マイクロステッピング設定で、コイル A 電流の第 1 象限に対応する電流 (TRQ\_DAC の %) をプログラマする必要があります。

- これらの電流値は、CUSTOM\_CURRENT1 レジスタから CUSTOM\_CURRENT8 レジスタに保存されます。

- これらの電流値の位置は、電気角  $11.25^\circ$ 、 $22.5^\circ$ 、 $33.75^\circ$ 、 $45^\circ$ 、 $56.25^\circ$ 、 $67.5^\circ$ 、 $78.75^\circ$ 、 $90^\circ$  に対応します。

- $0^\circ$  の位置の電流値はゼロとします。

- 9 つの電流値 (0% フルスケール電流を含む) は、区分線形手法を使用して合計 256 ポイントまで補間され、完全な電流波形が作られます。補完された波形は、プログラムされたマイクロステッピング・モードに関係なく、常に 1/256 のマイクロステップに対応します。

- 第 1 象限の値を反転して、コイル A 電流の他の第 3 象限と、コイル B 電流の第 4 象限で反復させ、完全な電流波形が形成されます。

表 7-15 に、ユーザーの入力例を示します。

**表 7-15. カスタム・マイクロステッピング表の値**

| 位置 ( $^\circ$ ) | 正弦インデクサ値 | 修正値 (CUSTOM_CURRENTx) |

|-----------------|----------|-----------------------|

| 0               | 0        | 0                     |

| 11.25           | 49.7     | 24                    |

| 22.5            | 97.6     | 56                    |

| 33.75           | 141.7    | 96                    |

| 45              | 180.3    | 152                   |

| 56.25           | 212      | 192                   |

| 67.5            | 235.6    | 224                   |

| 78.75           | 250.1    | 240                   |

| 90              | 255      | 255                   |

図 7-9 に、正弦インデクサで生成される波形と比較した、完全な電気角におけるコイル A の対応する修正電流波形を示します。

**図 7-9. カスタマイズ可能なマイクロステッピング**

### 7.3.8 電流レギュレーション

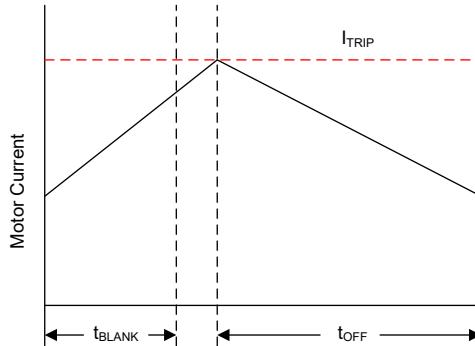

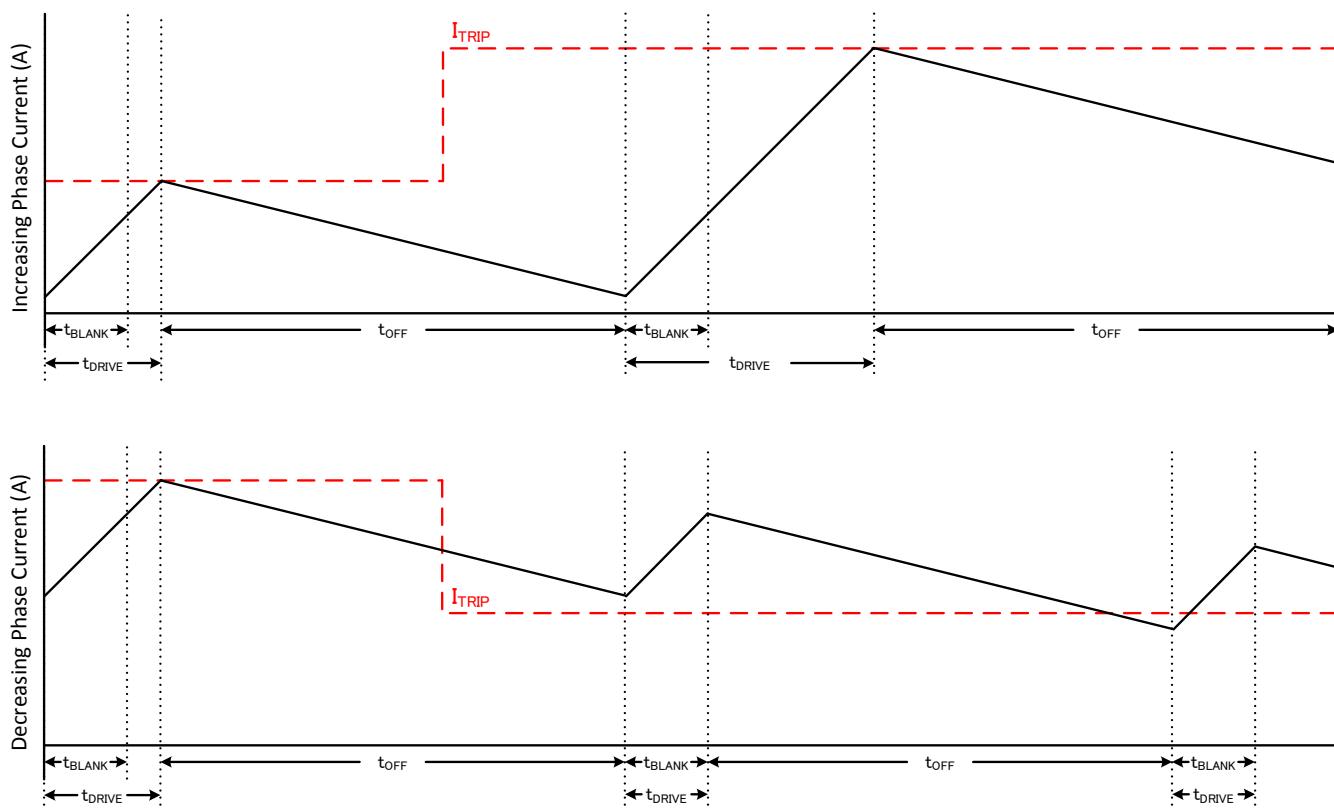

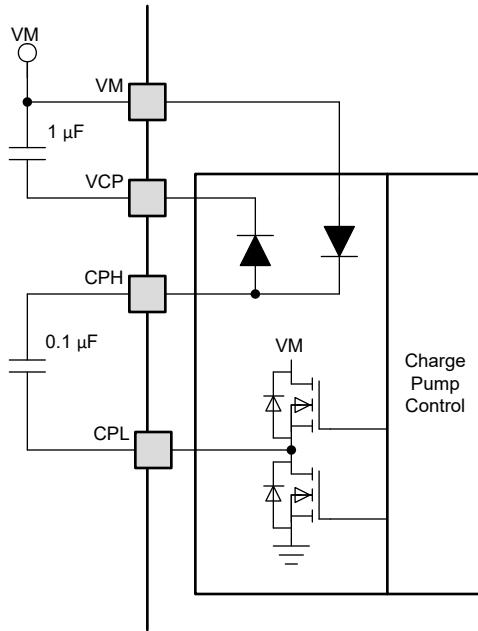

モーター巻線に流れる電流は、PWM 電流レギュレーション回路によって制御されます。H ブリッジをイネーブルになると、現在の電源電圧、巻線のインダクタンス、逆起電力の大きさに応じた速度で、巻線を流れる電流が増加します。電流が電流レギュレーション・スレッショルドに達すると、図 7-10 に示すように、ブリッジはオフ時間の間減衰モードに移行して電流は減少します。オフ時間が経過すると、ブリッジは再びイネーブルになり、次の PWM サイクルを開始します。

図 7-10. 電流チョッピング波形

PWM レギュレーション電流は、ローサイド・パワー MOSFET と並列に接続した電流検出 MOSFET の両端の電圧を監視するコンパレータによって設定されます。このデバイスを H/W インターフェイスで構成する場合、電流センス MOSFET は、電流モードの正弦波で重み付けした DAC の出力であるリファレンス電流でバイアスされます。この DAC のフルスケール・リファレンス電流は VREF ピンの電圧で設定します。SPI インターフェイスで動作している場合、2 つのレジスタ (TRQ\_DAC と ISTSL) により、リファレンス電流をさらにスケーリングできます。

式 1 を使用して、H/W インターフェイスのフルスケール・レギュレーション電流を計算します。

$$I_{FS} (A) = VREF (V) / K_V (V/A) \quad (1)$$

SPI インターフェイスの場合、8 ビットの TRQ\_DAC レジスタはフルスケール電流を式 1 に示すようにさらにスケーリングします。TRQ\_DAC の設定については、表 7-16 を参照してください。

$$I_{FS} (A) = VREF (V) \times TRQ\_DAC / K_V (V/A) \quad (2)$$

表 7-16. TRQ\_DAC 設定

| TRQ_DAC           | 電流スcalar |

|-------------------|----------|

| 11111111b (デフォルト) | 100%     |

| 11111110b         | 99.61%   |

| 11111101b         | 99.22%   |

| 11111100b         | 98.83%   |

| .....             | .....    |

| 00000000b         | 0.39%    |

ステップ・パルスが印加されておらず、モーターが同じ位置に保持されているとき、もう 1 つの 8 ビット・レジスタ ISTSL は保持電流 ( $I_{HOLD}$ ) をプログラムします。保持電流がさらに低い値に遷移すると、モーターおよびドライバの電力損失が減少します。詳しくは、セクション 7.3.13 を参照してください。

$$I_{HOLD} (A) = VREF (V) \times ISTSL / K_V (V/A) \quad (3)$$

表 7-17. ISTSL の設定

| ISTSL             | 保持電流の値 |

|-------------------|--------|

| 11111111b         | 100%   |

| 11111110b         | 99.61% |

| 11111101b         | 99.22% |

| 11111110b         | 98.83% |

| .....             | .....  |

| 10000000b (デフォルト) | 50.39% |

| .....             | .....  |

表 7-17. ISTSL の設定 (continued)

| ISTSL     | 保持電流の値 |

|-----------|--------|

| 00000000b | 0.39%  |

### 注

ISTSL は必ず TRQ\_DAC より小さい値に設定してください。

#### 7.3.8.1 内部リファレンス電圧

SPI インターフェイスで動作する場合、DRV8452 は内部 3.3V リファレンス電圧をサポートします。この内部リファレンスは、VREF\_INT\_EN ビットに 1b を書き込むことでイネーブルにすることができます。その場合、VREF ピンの電圧は無視されるため、VREF ピンはオープンのままにするか、グランドに接続できます。

フルスケール電流と保持電流は、式 4 および 式 4 に示されるように計算されます。

$$I_{FS} (\text{A}) = 3.3\text{V} \times \text{TRQ\_DAC} / K_V (\text{V/A}) \quad (4)$$

$$I_{HOLD} (\text{A}) = 3.3\text{V} \times \text{ISTSL} / K_V (\text{V/A}) \quad (5)$$

リファレンスとして内部 3.3V を使用すると、VREF ピンに接続されている 2 つの抵抗が不要になるため、BOM のコストを削減できます。

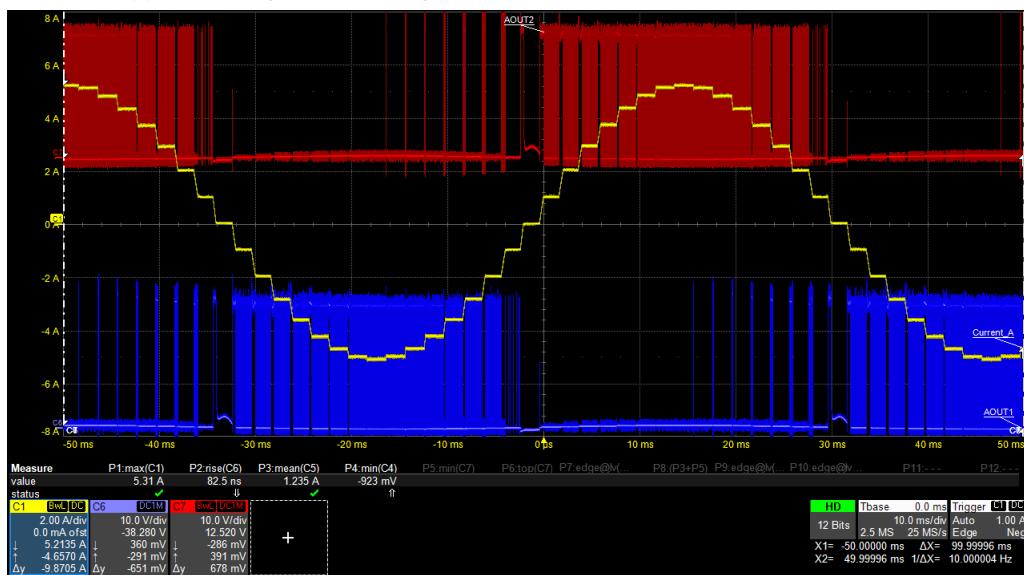

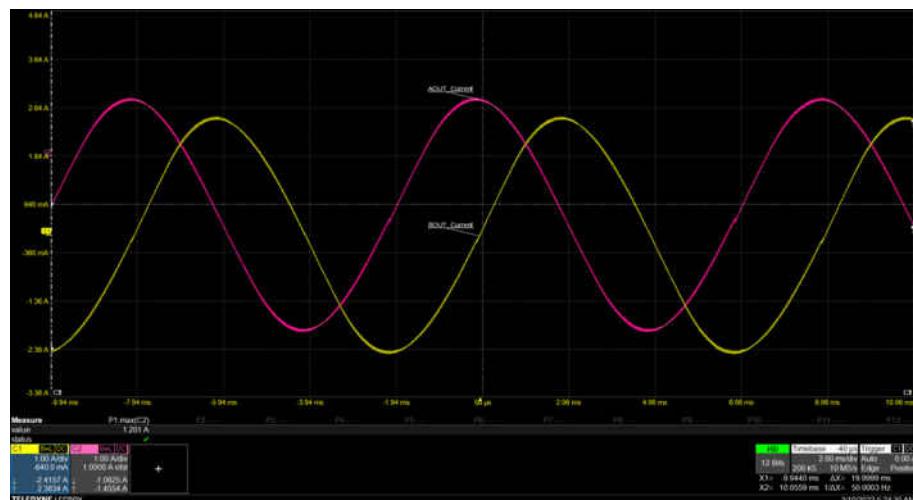

図 7-11 に、VREF\_INT\_EN = 1b および 5A フルスケール電流による電流レギュレーションを示します。

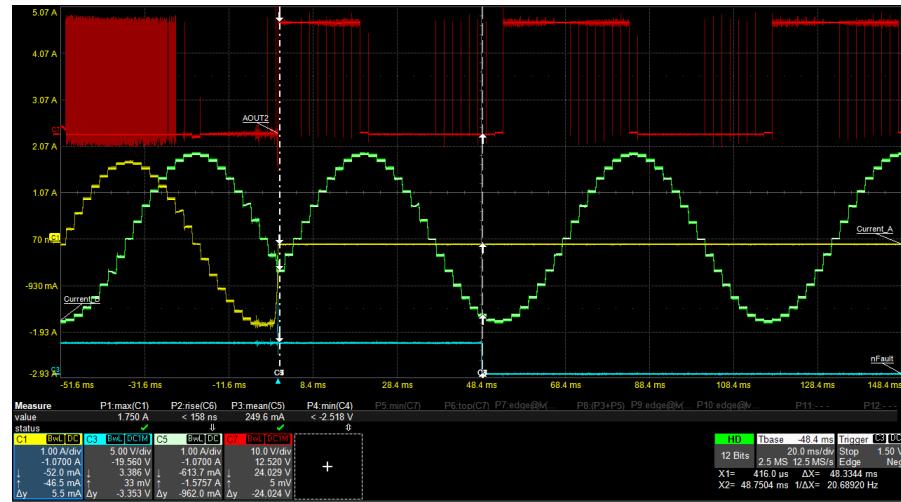

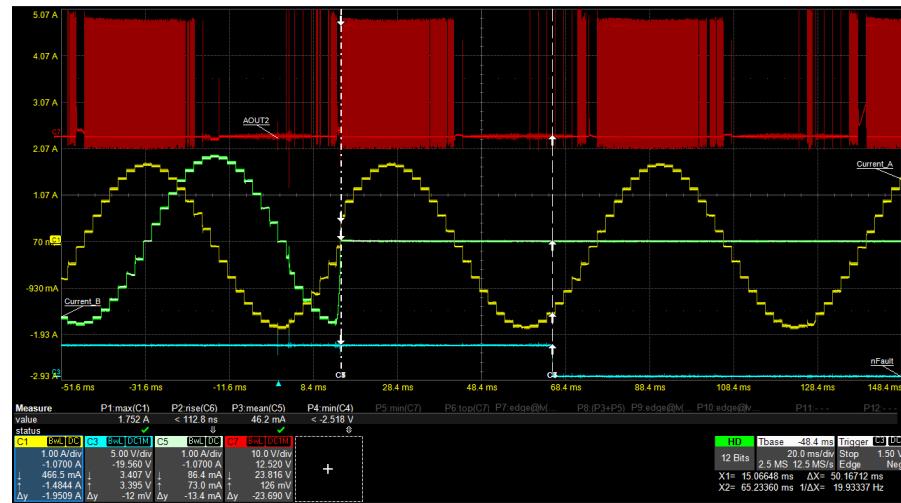

波形パターンは上から下へ順に:AOUT2、コイル A 電流、AOUT1

図 7-11. 内部リファレンス電圧による電流レギュレーション

#### 7.3.9 電流レギュレーション減衰モード

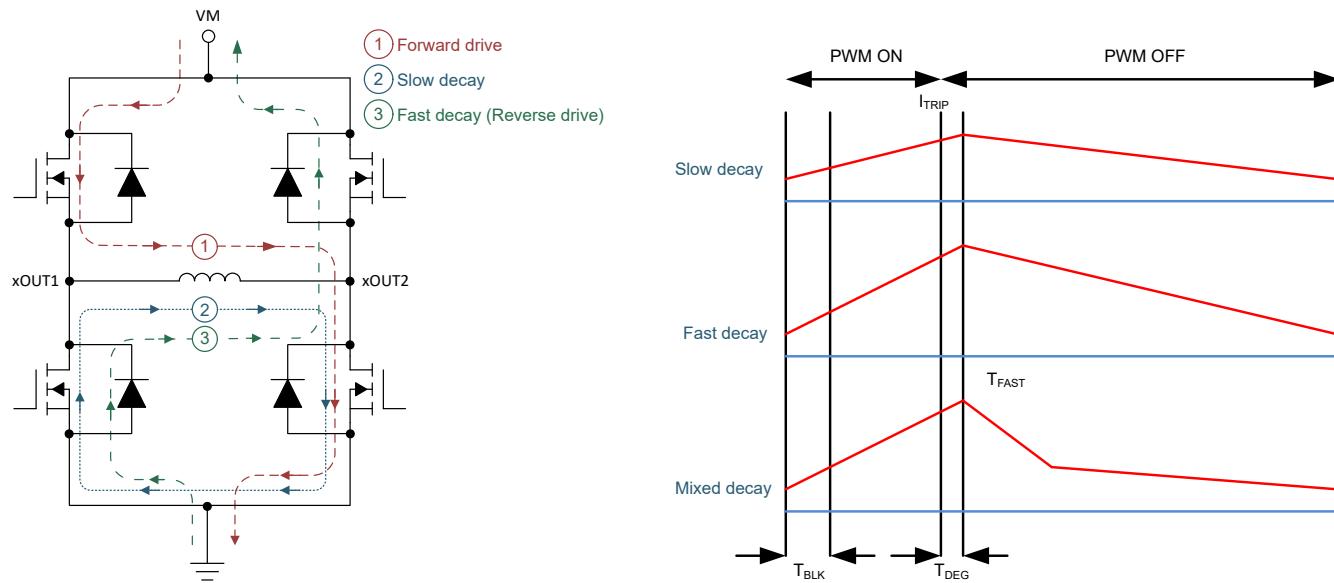

PWM 電流チョッピング中、チョッピング電流スレッショルドに達するまで H ブリッジはモーター巻線を駆動します。図 7-12 の項目 1 にこれを示します。

チョッピング電流スレッショルドに達した後、H ブリッジは 2 種類の状態 (高速減衰または低速減衰) で動作できます。

- 高速減衰モードでは、PWM チョッピング電流レベルに達するとすぐ、巻線電流が逆方向に流れるように反対側のアームの MOSFET に切り換えることで、H ブリッジは状態を反転させます。巻線電流がゼロに近づくと、H ブリッジはディセーブルされ、逆方向の電流がそれ以上流れるのを防止します。図 7-12 の項目 2 に高速減衰モードを示します。

- 低速減衰モードでは、H ブリッジの両方のローサイド MOSFET をイネーブルすることで巻線電流を再循環させます。図 7-12 の項目 3 にこれを示します。

図 7-12. 減衰モード

減衰モードは、表 7-18 に示すように DECAY レジスタまたは DECAY0 と DECAY1 ピンで選択します。この減衰モードは、実行中に変更できます。

表 7-18. 減衰モードの設定

| SPI インターフェイス | H/W インターフェイス |        | 減衰モード  |                       |

|--------------|--------------|--------|--------|-----------------------|

|              | 減衰           | DECAY0 | DECAY1 |                       |

| 000b         | ハイ・インピーダンス   | 1      | 0      | 低速減衰                  |

| 100b         |              | 1      | 0      | 混合減衰:30% 高速           |

| 101b         | ハイ・インピーダンス   | 0      | 0      | 混合減衰:60% 高速           |

| 110b         |              | 0      | 0      | スマート・チューン・ダイナミック減衰    |

| 111b (デフォルト) |              | 0      | 1      | スマート・チューン・リップル・コントロール |

## 注

DECAY ビットの残り (001b, 010b, 011b) の設定、および (DECAY0 = 1, DECAY1 = 1) の設定は予約済みです。

DRV8452 には、低速および静止時の超サイレント動作のため、サイレント・ステップ減衰モードも搭載されています。詳しくは、セクション 7.3.11 を参照してください。

### 7.3.9.1 低速減衰

図 7-13. 低速減衰モード

低速減衰では、H ブリッジのローサイド FET はどちらもオンになり、電流を再循環させます。低速減衰モードを選択する際に考慮すべき点を以下に示します。

- 低速減衰は、与えられた  $t_{OFF}$  に対する減衰モードの中で、最も小さい電流リップルを示します。

- しかし電流減少ステップでは、低速減衰では電流が非常にゆっくり減少するため、新しい  $I_{TRIP}$  レベルに落ち着くのに長い時間がかかります。

- オフ時間終了時の電流が  $I_{TRIP}$  レベルを上回っている場合、もう一度オフ時間の間低速減衰が延長され、オフ時間終了時の電流が  $I_{TRIP}$  レベルを下回るまで繰り返されます。

- 電流が長時間にわたって同じレベルに保持されている (STEP 入力なし) 場合、レギュレーションの目標電流レベルが低い場合、または、ステッピング速度が非常に遅い場合、モーター巻線の逆起電力が非常に小さく、オフ時間中に電流を放電する可能性があるため、低速減衰では適切に電流を調整できない場合があります。この状態では、モーター電流が急速に増加する可能性があり、長いオフ時間を必要とする場合があります。場合によっては、このために電流レギュレーションが失われる可能性があるので、より積極的な減衰モードが推奨されます。

### 7.3.9.2 混合減衰

図 7-14. 混合減衰モード

混合減衰では、 $t_{OFF}$  時間の初めの一定期間 (30% または 60%) は高速減衰で開始し、その後  $t_{OFF}$  の残り時間は低速減衰に切り替わります。混合減衰モードを選択するときは、以下の点を考慮する必要があります。

- このモードでは、低速減衰よりもリップルが大きくなります。

- 電流減少ステップでは、混合減衰は低速減衰よりも早く、新しい  $I_{TRIP}$  レベルに落ち着きます。

- 電流が長時間同じレベルに保持される場合 (ステップ入力なし)、またはステッピング速度が非常に遅い場合、混合減衰を使用すると、モータ巻線に逆起電力が存在しないときに電流をレギュレーションに維持できます。

- 30% または 60% の固定混合減衰方式を採用すると、可聴周波数範囲に収まる電流レギュレーションのパターンが繰り返され、モーターの動作にノイズが発生する可能性があります。

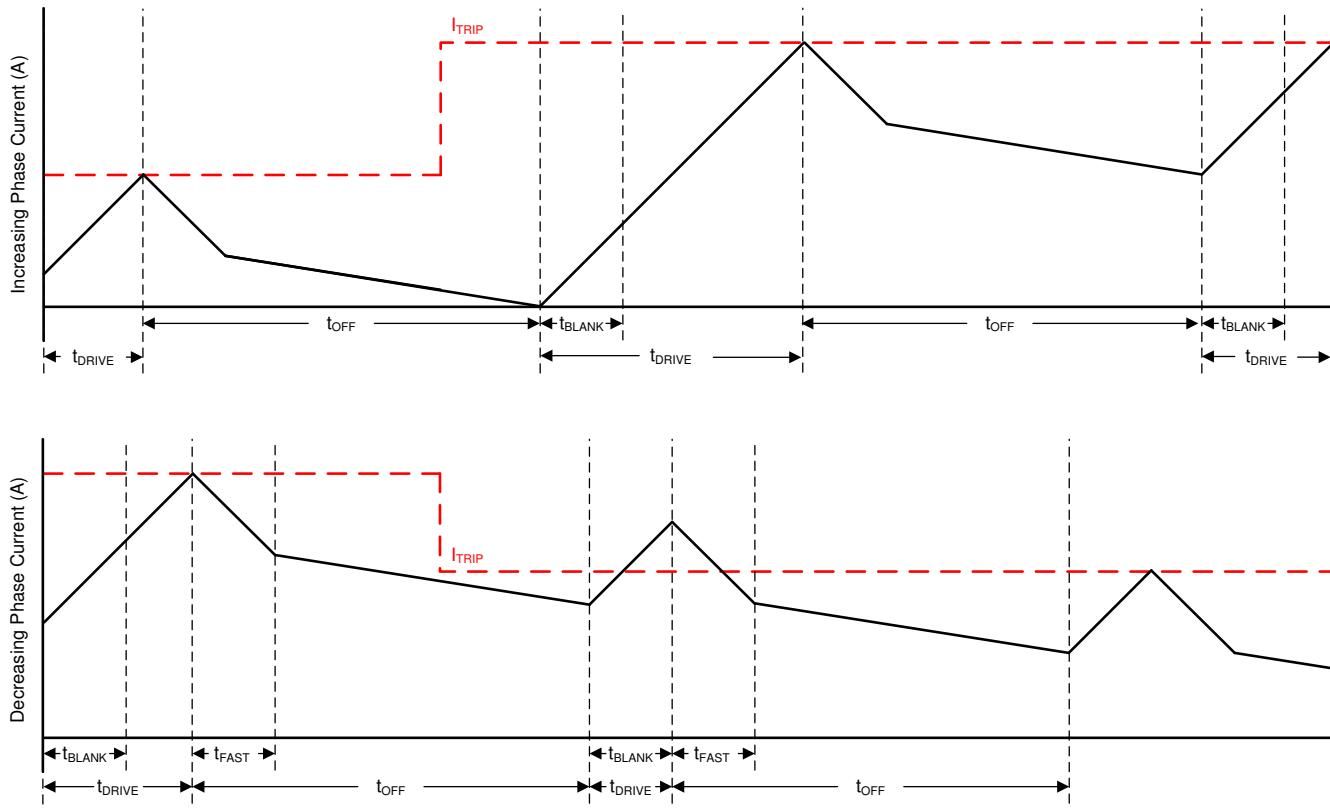

### 7.3.9.3 スマート・チューン・ダイナミック減衰

スマート・チューンは、従来の混合減衰モードに比べて高度な電流レギュレーション方式です。スマート・チューンは、ステップ・モーター・ドライバが以下のような動作要因の変化に基づいて減衰方式を調整するのに役立ちます。

- モーターの巻線抵抗およびインダクタンス

- モーターの経年劣化

- モーターの動的速度および負荷

- モーターの電源電圧変動

- 立ち上がりと立ち下がりのステップにおけるモーターの逆起電力の差

- ステップ遷移

- 小電流と大電流の  $di/dt$

DRV8452 は 2 つのスマート・チューン方式 (スマート・チューン・ダイナミック減衰とスマート・チューン・リップル・コントロール) をサポートしています。

図 7-15. スマート・チューン・ダイナミック減衰モード

スマート・チューン・ダイナミック減衰では、混合減衰の総時間に対する高速減衰の割合が動的に調整されます。これにより、モーターのリップルを最小限に抑え、性能を最大限に高めるために最適な混合減衰設定が自動的に決定されるため、モーター減衰の調整が不要になります。

高速減衰の割合は、各 PWM サイクルで繰り返し最適化されます。モーター電流が目標の  $I_{TRIP}$  レベルを超えると、電流レギュレーションの損失を防ぐため、次のサイクルで混合減衰モードはより積極的になります（高速減衰の割合を増やすことで）。目標の  $I_{TRIP}$  レベルに達するまでに長い駆動時間を必要とする場合は、リップルを抑えるために、次のサイクルで減衰モードはより消極的になります（高速減衰の割合を減らすこと）。立ち下がりステップでは、次のステップに素早く達するために、スマート・チューン・ダイナミック減衰は自動的に高速減衰に切り替わります。

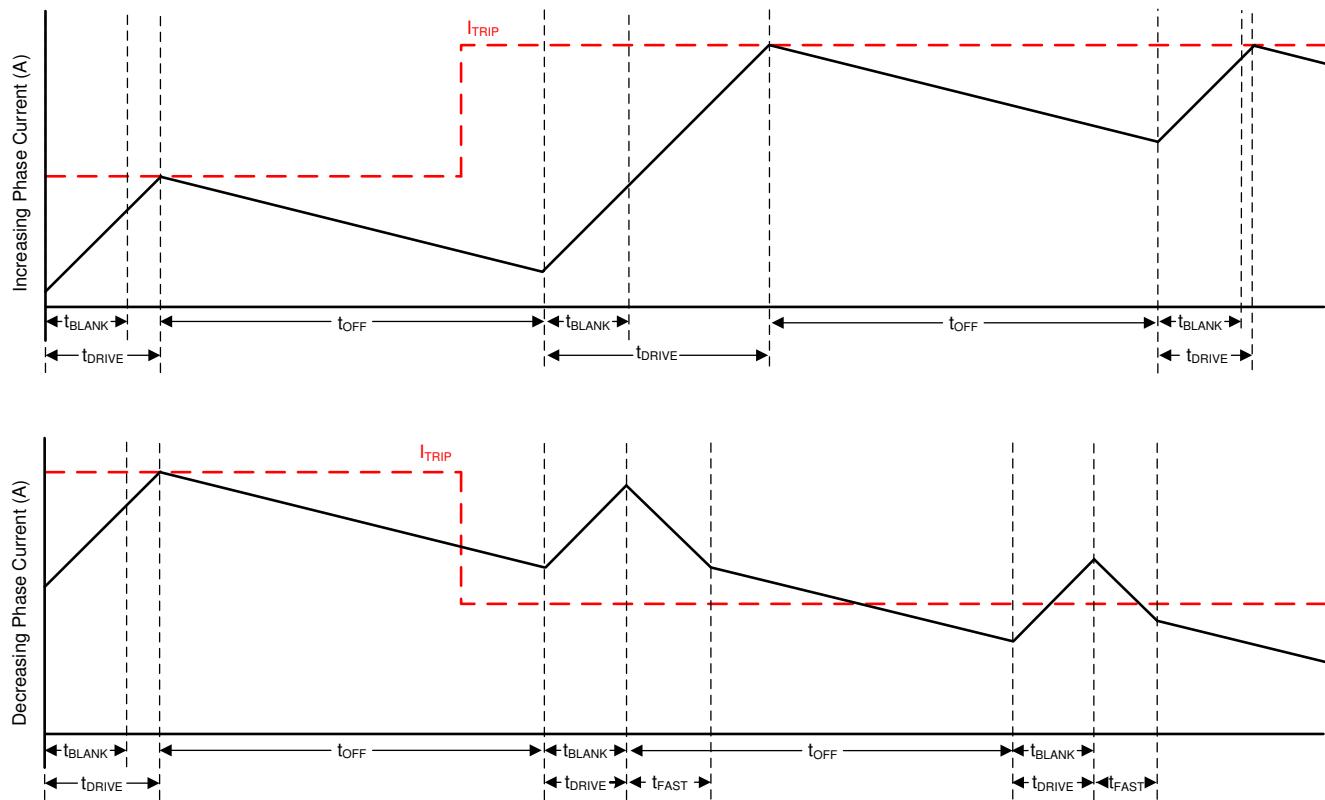

### 7.3.9.4 スマート・チューン・リップル・コントロール

図 7-16. スマート・チューン・リップル・コントロール減衰モード

スマート・チューン・リップル・コントロール減衰モードでは、PWM オフ時間は電流レベルと動作パラメータに応じて変化します。それは、 $I_{TRIP}$  レベルと  $I_{VALLEY}$  レベルを設定することで動作します。電流レベルが  $I_{TRIP}$  に達すると、ドライバは  $t_{OFF}$  時間が経過するまで低速減衰に移行する代わりに、 $I_{VALLEY}$  に達するまで低速減衰に移行します。

スマート・チューン・リップル・コントロール・モードのリップル電流の大きさは、表 7-19 に示すように RC\_RIPPLE[1:0] ビット、または TOFF ピンによってプログラムされます。

表 7-19. 電流リップル設定

| ハードウェア・インターフェイス    | SPI インターフェイス | 特定のマイクロステップ・レベルでの電流リップル                                                                              |

|--------------------|--------------|------------------------------------------------------------------------------------------------------|

| TOFF               | RC_RIPPLE    | 25mA + $I_{TRIP}$ の 1%<br>25mA + $I_{TRIP}$ の 2%<br>25mA + $I_{TRIP}$ の 4%<br>25mA + $I_{TRIP}$ の 6% |

| 0                  | 00b (デフォルト)  |                                                                                                      |

| 1                  | 01b          |                                                                                                      |

| ハイ・インピーダンス         | 10b          |                                                                                                      |

| 330kΩ を GND との間に接続 | 11b          |                                                                                                      |

スマート・チューン・リップル・コントロール方式により、リップル電流のレギュレーションを大幅に厳密化できるため、モーターの効率が向上し、可聴ノイズが低減されます。PWM 周波数が可聴範囲 (< 20kHz) にならないように、リップル電流設定を選択します。

### 7.3.9.5 PWM オフ時間

表 7-20 に示すように、TOFF ビットまたは TOFF ピンにより、スマート・チューン・リップル・コントロールおよびサイレント・ステップ減衰モードを除くすべての減衰モードの PWM オフ時間を設定します。このオフ時間の設定は実行中に変更できます。

**表 7-20. オフ時間の設定**

| SPI インターフェイス | ハードウェア・インターフェイス    | オフ時間 |

|--------------|--------------------|------|

| TOFF         | TOFF               |      |

| 00b          | 0                  | 9μs  |

| 01b (デフォルト)  | 1                  | 19μs |

| 10b          | ハイ・インピーダンス         | 27μs |

| 11b          | 330kΩ を GND との間に接続 | 35μs |

### 7.3.9.6 電流レギュレーション・ブランкиング時間とグリッチ除去時間

H ブリッジでドライブ・フェーズが開始されると、電流検出コンパレータ出力を一定時間(ブランкиング時間)無視した後、電流検出回路を有効にします。ブランкиング時間は、PWM の最小駆動時間も設定します。

- デバイスがハードウェア・インターフェイスで動作している場合、ブランкиング時間は 1.5μs に固定されます。

- デバイスが SPI インターフェイスで動作している場合、表 7-21 に示されているように、ブランкиング時間は TBLANK\_TIME ビットにより、デフォルト値 1.5μs でプログラムできます。

**表 7-21. TBLANK\_TIME の設定**

| TBLANK_TIME | ブランкиング時間 |

|-------------|-----------|

| 00b         | 1μs       |

| 01b (デフォルト) | 1.5μs     |

| 10b         | 2μs       |

| 11b         | 2.5μs     |

電流が  $I_{TRIP}$  レベルに近い場合、適切な電流レギュレーションを確保するためには 0.5μs のグリッチ除去時間を追加します。

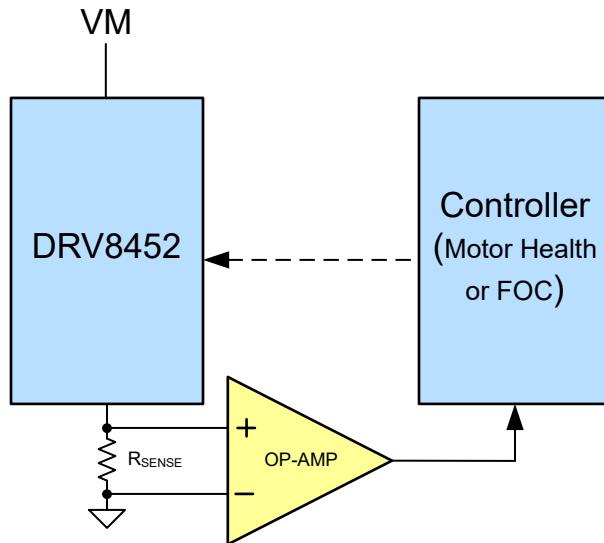

### 7.3.10 外付け抵抗による電流検出

PWM 電流レギュレーションは、DRV8452 の内部検出抵抗で検出される電圧に基づいています。図 7-17 に示すように、PGND ピンとシステム・グラウンドとの間に(または VM ピンと直列に)オプションの外付け抵抗を配置して、コイルの電流を検出できます。DRV8452 には 2 つの PGND\_A ピンと 2 つの PGND\_B ピンがあり、各 H ブリッジに 1 つのペアがあります。そのため、PGND ピンとシステム・グラウンドとの間に検出抵抗を配置することで、各ステッパー・モーター・コイルの電流を別々に検出できます。4 本の VM ピンはすべて内部で短絡しているため、検出抵抗が VM 経路に配置されると、この抵抗は両方の H ブリッジの合計電流を検出します。

PGND ピンとシステム・グラウンドとの間に接続された外部検出抵抗の電圧降下は、300mV を超えないようにする必要があります。検出されたコイル電流はモーターの状態を監視するために処理されたり、フィールド指向制御ループに必要な信号を生成するために使用して、システム全体の効率を向上させます。

図 7-17. 外付け抵抗による電流検出

低速減衰中は電流が検出抵抗を流れないとため、検出抵抗の導通電流はコイル RMS 電流より小さくなります。検出抵抗は、対応する IC ピンのできるだけ近くに配置してください。検出抵抗を左右対称に配置することで、マッチングが適切になります。電圧スパイクとリンクギングを防止するため、低インダクタンスの検出抵抗を使用してください。最適な性能を確保するため、検出抵抗には十分大きな電力を定格とする表面接地型の抵抗を使用してください。

### 7.3.11 サイレント・ステップ減衰モード

従来のピーク電流モード制御は、検出中の MOSFET の瞬間的な電流を調べて、駆動時間と減衰時間を決定します。そのため、モーター・ドライバはシステムの瞬間的な誤差に反応します。このように電流が急激に変化すると、モーターから可聴ノイズが発生します。

ステッパ・モーターがノイズなしで動作するよう、DRV8452 にはサイレント・ステップ減衰モードが搭載されています。サイレント・ステップは、静止状態および低速での PWM スイッチングによるノイズを除去するための、電圧モード PWM レギュレーション方式です。そのため、サイレント・ステップで動作するステッパ・モーター・アプリケーションは、低ノイズでの動作が重要な 3D プリンタ、医療機器、工場オートメーションなどのアプリケーションに最適です。

---

#### 注

デバイスがサイレント・ステップ減衰モードで動作している場合、

- オープン負荷障害検出は、モーターが動作しているときのみ機能しますが、モーターが静止している場合は機能しません。

- ストール検出機能はサポートされていません。

- スペクトラム拡散機能はディセーブルです。

-

サイレント・ステップ・ループは低帯域幅での動作作用に設計されているため、モーター速度が中程度から高速のときは、減衰モードから DECAY ビットでプログラムされた従来の電流モード減衰方式の 1 つに戻すことが可能ですが。サイレント・ステップから他の減衰モードへはすぐに移行しますが、他の減衰モードからサイレント・ステップへは電気的半サイクルの境界で移行します。

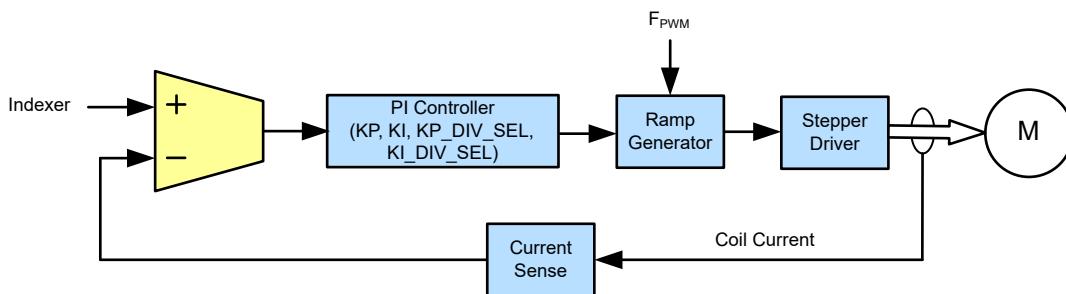

図 7-18 に、サイレント・ステップ減衰モードの実装のブロック図を示します。

図 7-18. サイレント・ステップのブロック図

表 7-22 に、サイレント・ステップ減衰モードに関する SPI レジスタのパラメータを示します。

表 7-22. サイレント・ステップのパラメータ表

| パラメータ              | 概要                                                                                                                                                                                                                                                                                |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EN_SS              | EN_SS ビットが「1b」の場合、サイレント・ステップ減衰モードがイネーブルになります。デバイスは、コイル A およびコイル B の電流に対してそれぞれ 1 回ずつのゼロ・クロスが発生した後、サイレント・ステップで動作を開始します。EN_SS に「0b」を書き込むと、サイレント・ステップ減衰モードがディセーブルされ、減衰ビット設定に従って減衰モードが変化します。                                                                                           |

| SS_PWM_FREQ[1:0]   | サイレント・ステップ減衰モードでの PWM 周波数 ( $F_{PWM}$ ) を表します。 <ul style="list-style-type: none"> <li>00b = 25kHz (デフォルト)</li> <li>01b = 33kHz</li> <li>10b = 42kHz</li> <li>11b = 50kHz</li> </ul> PWM 周波数が高くなると、スイッチング損失も大きくなります。                                                               |

| SS_SMPL_SEL[1:0]   | サイレント・ステップ電流のゼロ・クロス・サンプリング時間。デフォルト値は 2μs です。ゼロ交差付近で電流波形が歪んでいる場合は、サンプリング時間を長くしてください。 <ul style="list-style-type: none"> <li>00b = 2μs (デフォルト)</li> <li>01b = 3μs</li> <li>10b = 4μs</li> <li>11b = 5μs</li> </ul>                                                                  |

| SS_KP[6:0]         | サイレント・ステップ PI コントローラの比例ゲインを表します。範囲は 0~127 で、デフォルト値は 0 です。                                                                                                                                                                                                                         |

| SS_KI[6:0]         | サイレント・ステップ PI コントローラの積分ゲインを表します。範囲は 0~127 で、デフォルト値は 0 です。                                                                                                                                                                                                                         |

| SS_KP_DIV_SEL[2:0] | KP の分割係数。実際の $KP = SS\_KP / SS\_KP\_DIV\_SEL$ です。 <ul style="list-style-type: none"> <li>000b - SS_KP/32 (デフォルト)</li> <li>001b - SS_KP/64</li> <li>010b - SS_KP/128</li> <li>011b - SS_KP/256</li> <li>100b - SS_KP/512</li> <li>101b - SS_KP/16</li> <li>110b - SS_KP</li> </ul> |

| SS_KI_DIV_SEL[2:0] | KI の分割係数。実際の $KI = SS\_KI / SS\_KI\_DIV\_SEL$ です。 <ul style="list-style-type: none"> <li>000b - SS_KI/32 (デフォルト)</li> <li>001b - SS_KI/64</li> <li>010b - SS_KI/128</li> <li>011b - SS_KI/256</li> <li>100b - SS_KI/512</li> <li>101b - SS_KI/16</li> <li>110b - SS_KI</li> </ul> |

**表 7-22. サイレント・ステップのパラメータ表 (continued)**

| パラメータ       | 概要                                                                                                                                                                                                                                                                  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SS_THR[7:0] | <p>デバイスがサイレント・ステップ減衰モードから、DECAY ビットによってプログラムされた別の減衰モードに遷移する周波数をプログラムします。この周波数は、正弦波電流波形の周波数に相当します。</p> <ul style="list-style-type: none"> <li>• 00000001b = 2Hz</li> <li>• 00000010b = 4Hz</li> <li>• .</li> <li>• .</li> <li>• 11111111b = 510Hz (デフォルト)</li> </ul> |

SS\_THR スレッショルドを、指定されたマイクロステッピング設定のステップ周波数 ( $f_{STEP}$ ) に変換するには、式 6 を使用する必要があります。

$$f_{STEP} = (SS\_THR * 1000 * usm) / 256 \quad (6)$$

ここで、usm はマイクロステップ数 (4, 16, 256 など) に相当します。デバイスがカスタム・マイクロステッピング・モードで動作している場合、ステップ周波数求めるには 式 6 に  $usm = 256$  を使用します。

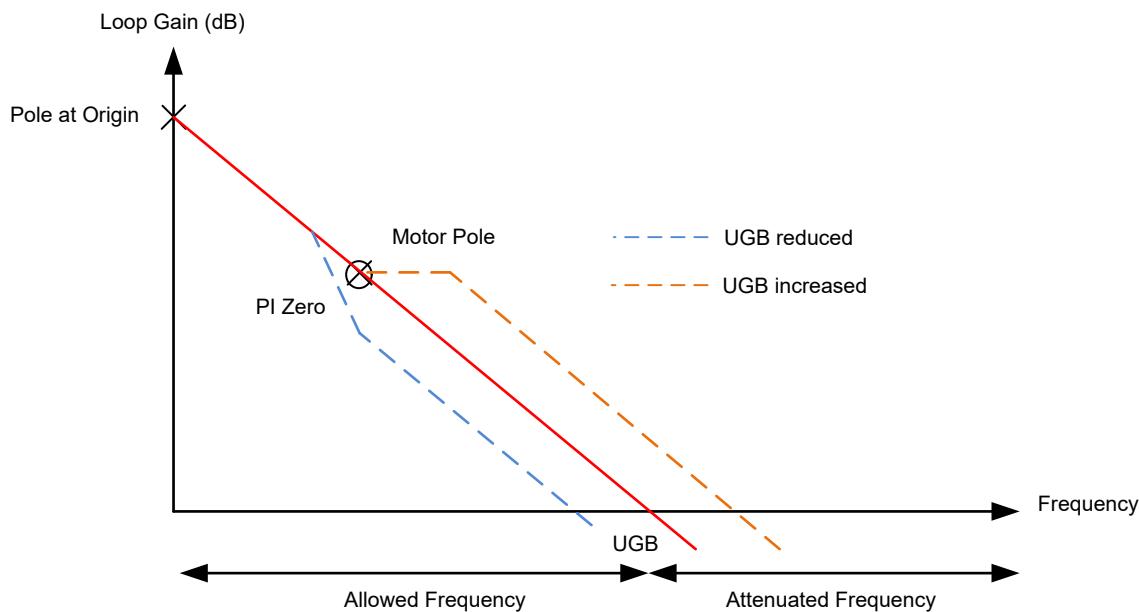

サイレント・ステップ・ループのゲインと周波数の関係を以下に示します。

**図 7-19. サイレント・ステップ・ゲインと周波数の関係**

ループ伝達関数には、次の 2 つの極と 1 つのゼロが含まれます。

- 原点に 1 つの極

- モーター・コイルの抵抗とインダクタンスによる 1 つの極 ( $f_p$ )

$$f_p = R_{MOTOR} / (2 * \pi * L_{MOTOR}) \quad (7)$$

- PI ループによって生成される 1 つのゼロ ( $f_z$ )

$$f_z = (K_I * F_{PWM}) / (2 * \pi * K_P) \quad (8)$$

目標のループ・ゲインを実現するには、比例ゲイン  $K_P$  を選択する必要があります。 $K_P$  は次の式で計算します。

$$K_P = 10 * \pi * UGB * L_{MOTOR} / V_M \quad (9)$$

ここで、UGB はループのユニティ・ゲイン帯域幅、 $R_{MOTOR}$  はモーターのコイルの抵抗、 $L_{MOTOR}$  はモーターのコイルのインダクタンス、 $I_{FS}$  はフルスケール電流、VM は電源電圧です。

- いずれかの周波数が UGB 未満になると、通過が許可されます。

- PWM 周波数やステップ周波数など、UGB より高い周波数は減衰され、モーターのノイズには影響しません。

- 可聴範囲内の大部分の周波数を減衰させるには、UGB を 200Hz にするのが妥当です。

- 電源電圧が変化した場合は、KP の値を変更することで UGB を変更できます。この方法で、さまざまな動作条件にわたって同様のオーディオ・ノイズを抑制することができます。

- モーターの極より低い周波数にゼロを選択すると、ゲインと周波数の関係の図に示すように UGB は増加します。

モーターの極をキャンセルするようにゼロを配置する必要があります。離散化された実装では  $f_P$  と  $f_Z$  を等しくすることで、次の式を使用して KI を計算できます。

$$KI = KP * R_{MOTOR} / (F_{PWM} * L_{MOTOR}) \quad (10)$$

例として、以下の使用事例を考えてみます。

- VM = 24V

- $I_{FS} = 5A$

- $R_{MOTOR} = 0.3\Omega$

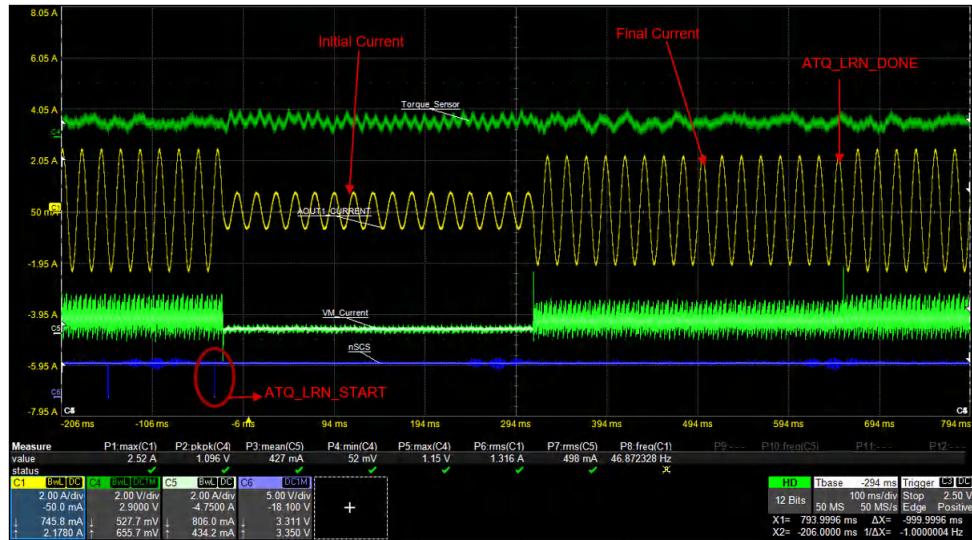

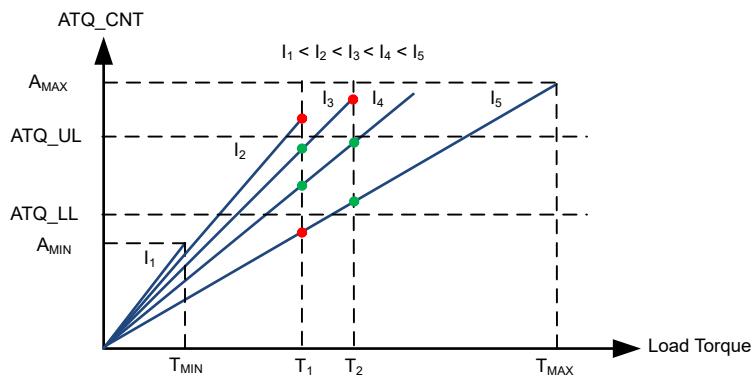

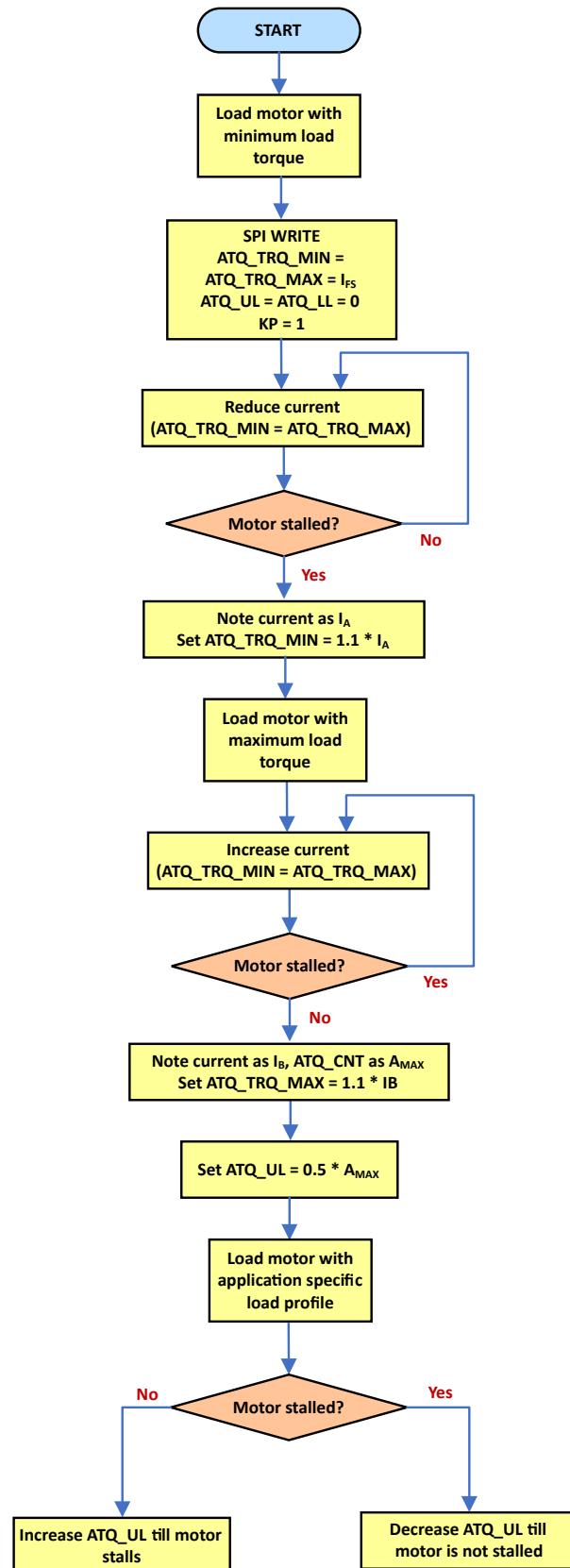

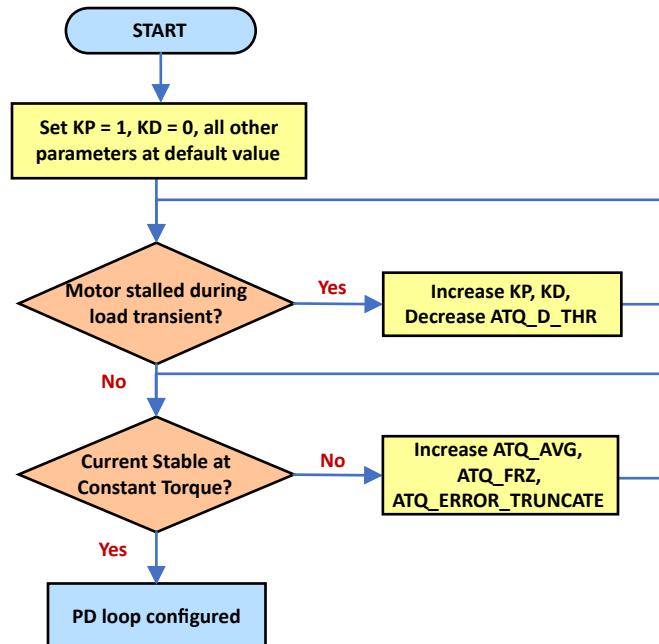

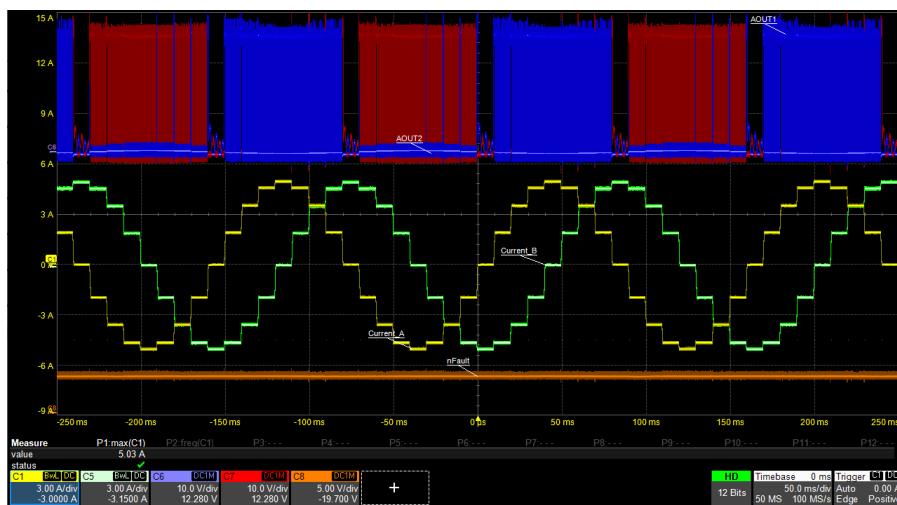

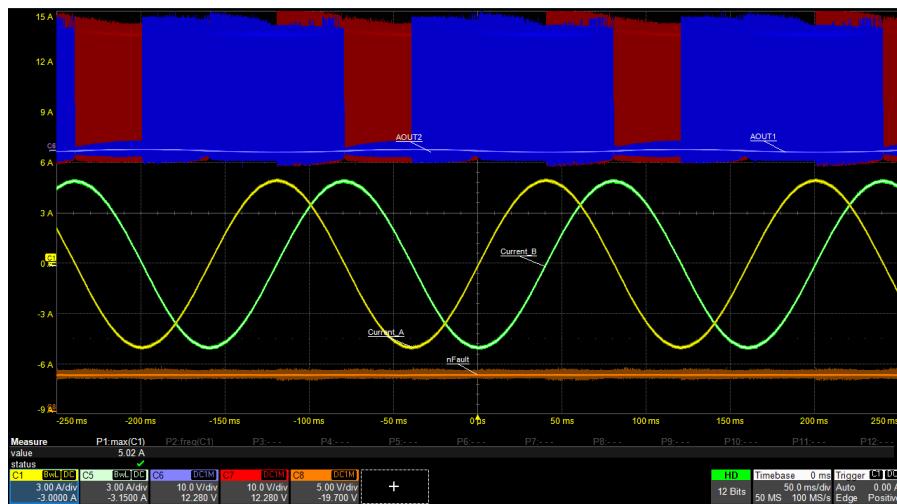

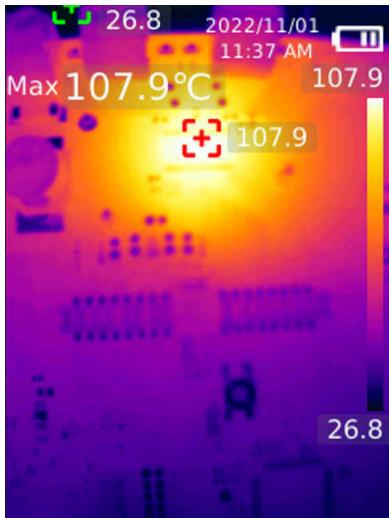

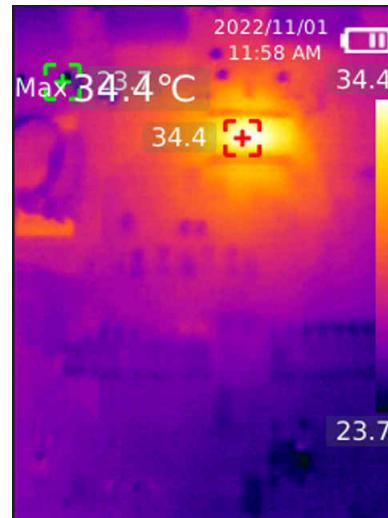

- $L_{MOTOR} = 0.7mH$