# DS40MB200 送信プリエンファシス機能と受信イコライゼーション機能搭載、デュアル、4Gbps、2:1/1:2 CML マルチプレクサ/バッファ

## 1 特長

- 1Gbps~4Gbps の低ジッタ動作

- 固定入力イコライゼーション

- 出力プリエンファシスをプログラム可能

- 独立したスイッチおよびライン側のプリエンファシス制御

- スイッチ側ループバック モードをプログラム可能

- オンチップ終端

- 3.3V 電源

- ESD 定格: 6kV HBM

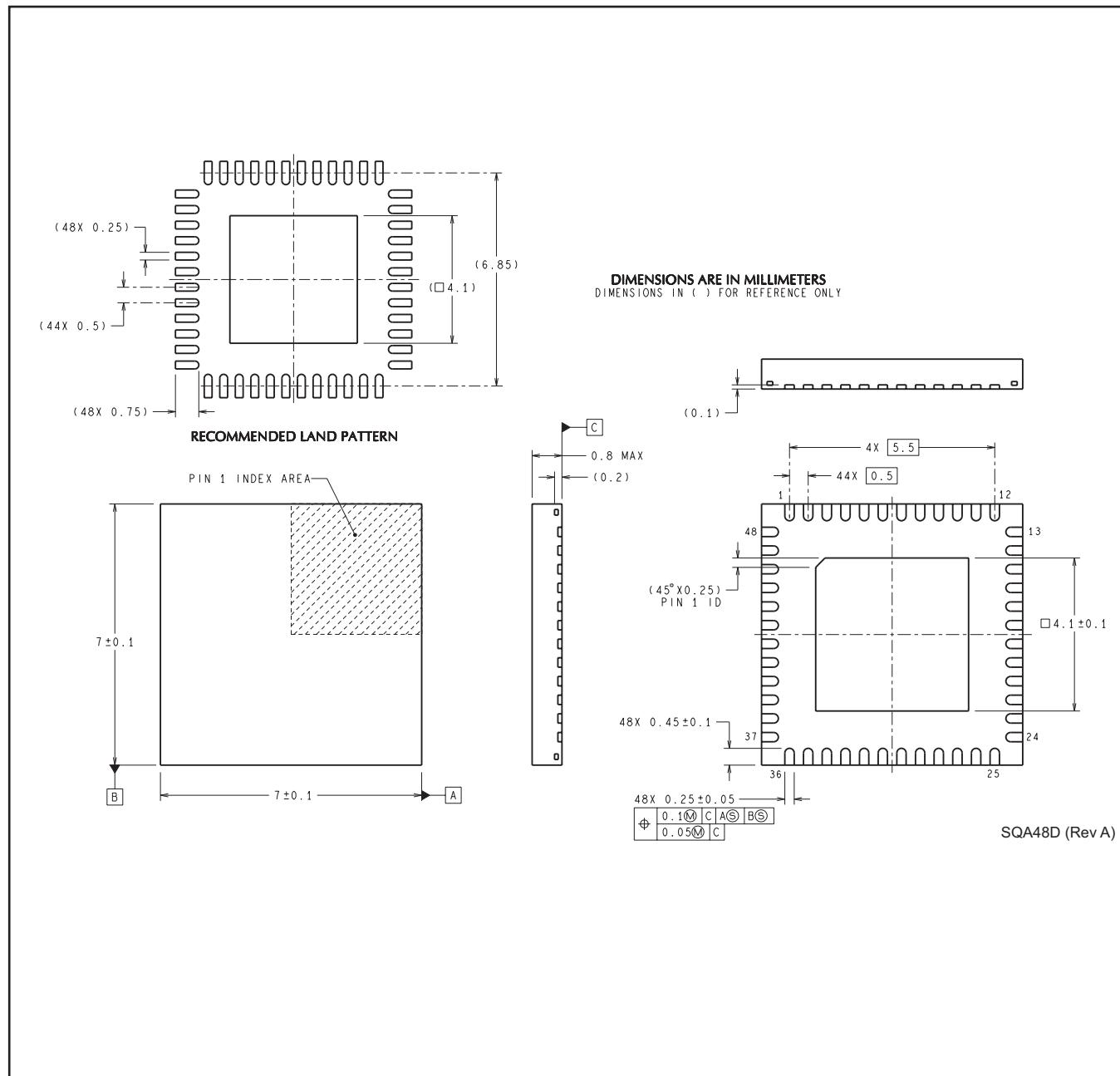

- 48 リードレス WQFN パッケージ (7mm × 7mm)

- 0°C~+85°C の動作温度範囲

## 2 アプリケーション

- バックプレーンまたはケーブル ドライバ

- 冗長化およびシグナル コンディショニング アプリケーション

- XAUI

## 3 概要

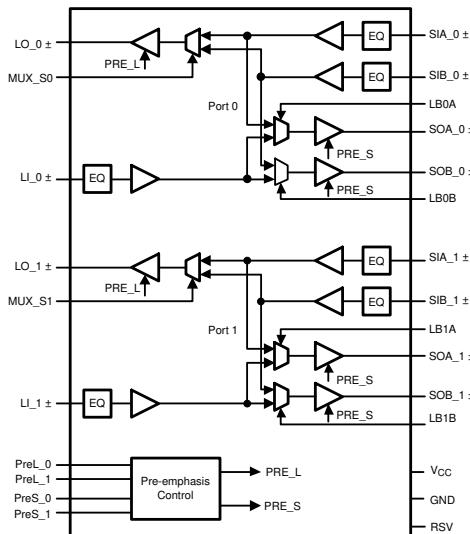

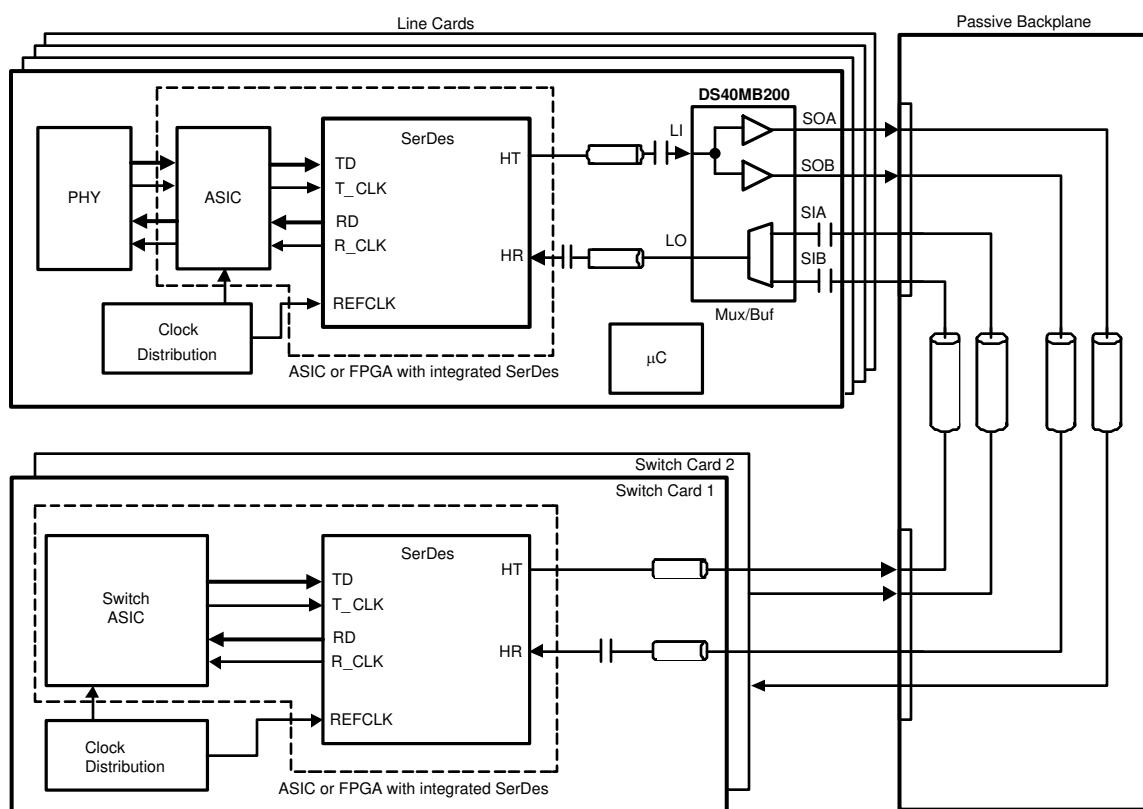

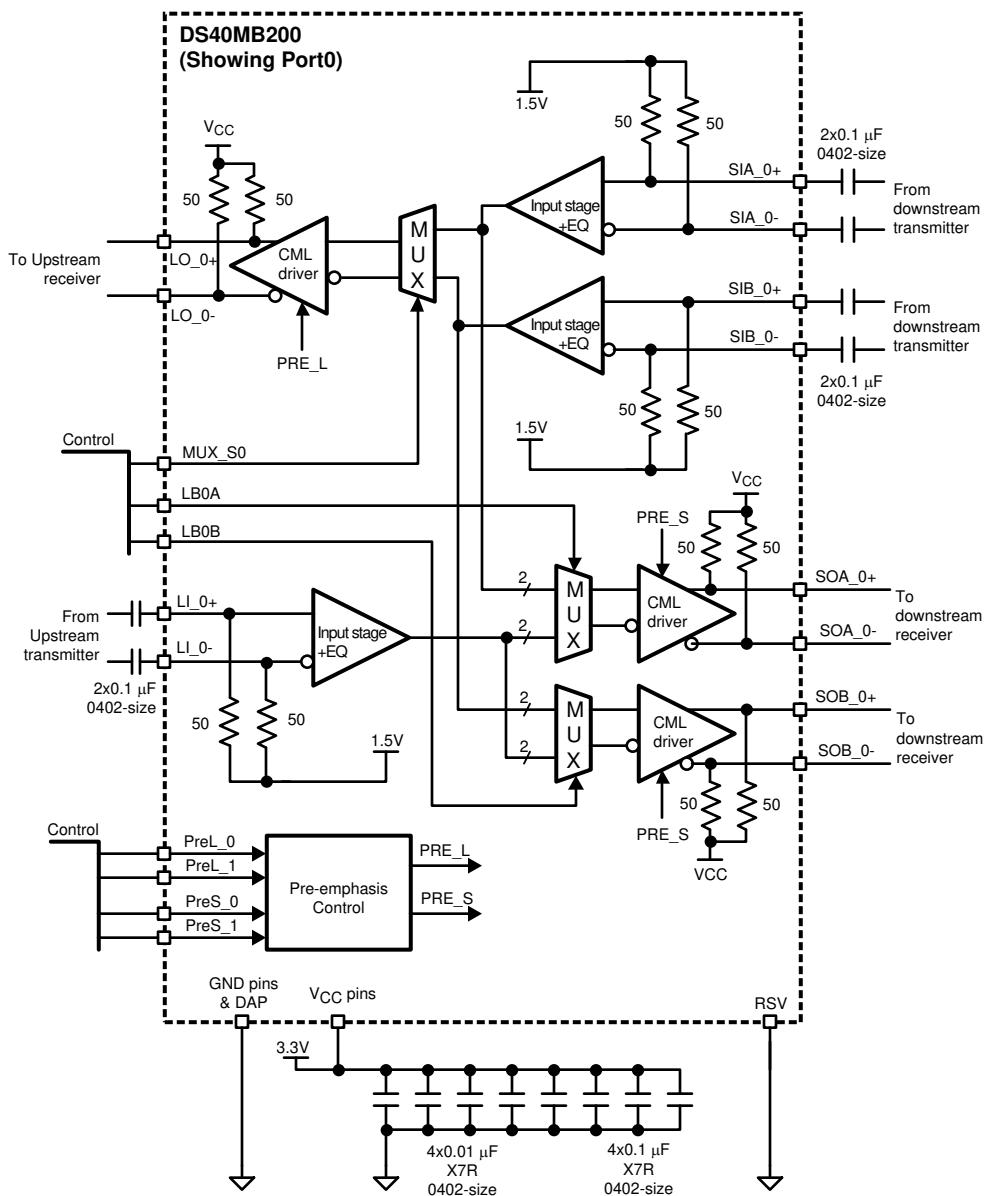

DS40MB200 デバイスは、デュアルシグナル コンディショニング 2:1 マルチプレクサ (MUX) および 1:2 ファンアウト バッファで、バックプレーン冗長性アプリケーションで使用できるように設計されています。シグナル コンディショニング 機能には、連続時間リニア イコライゼーション (CTLE) とプログラム可能な出力プリエンファシスが含まれており、FR4 バックプレーンのデータ通信を最大 4Gbps のレートまで拡張できます。各入力段には固定イコライザがあり、基板配線によるシンボル間干渉歪みを低減できます。

すべての出力ドライバには、長い FR4 バックプレーンからの伝送損失を補償し、確定的なジッタを低減するため、4 つの選択可能なプリエンファシス ステップがあります。プリエンファシス レベルは、ライン側ドライバとスイッチ側ドライバで独立して制御できます。スイッチ側入力からスイッチ側出力への内部ループバック パスにより、At-Speed システム テストが可能になります。すべてのレシーバ入力は、100Ω の差動終端抵抗で内部終端されています。すべてのドライバは、V<sub>CC</sub> に対して 50Ω で内部終端されています。

## 製品情報

| 部品番号      | パッケージ (1) | 本体サイズ (公称)        |

|-----------|-----------|-------------------|

| DS40MB200 | WQFN (48) | 7.00 mm × 7.00 mm |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

最適な性能を得るには、すべての CML 入出力を AC 結合する必要があります。

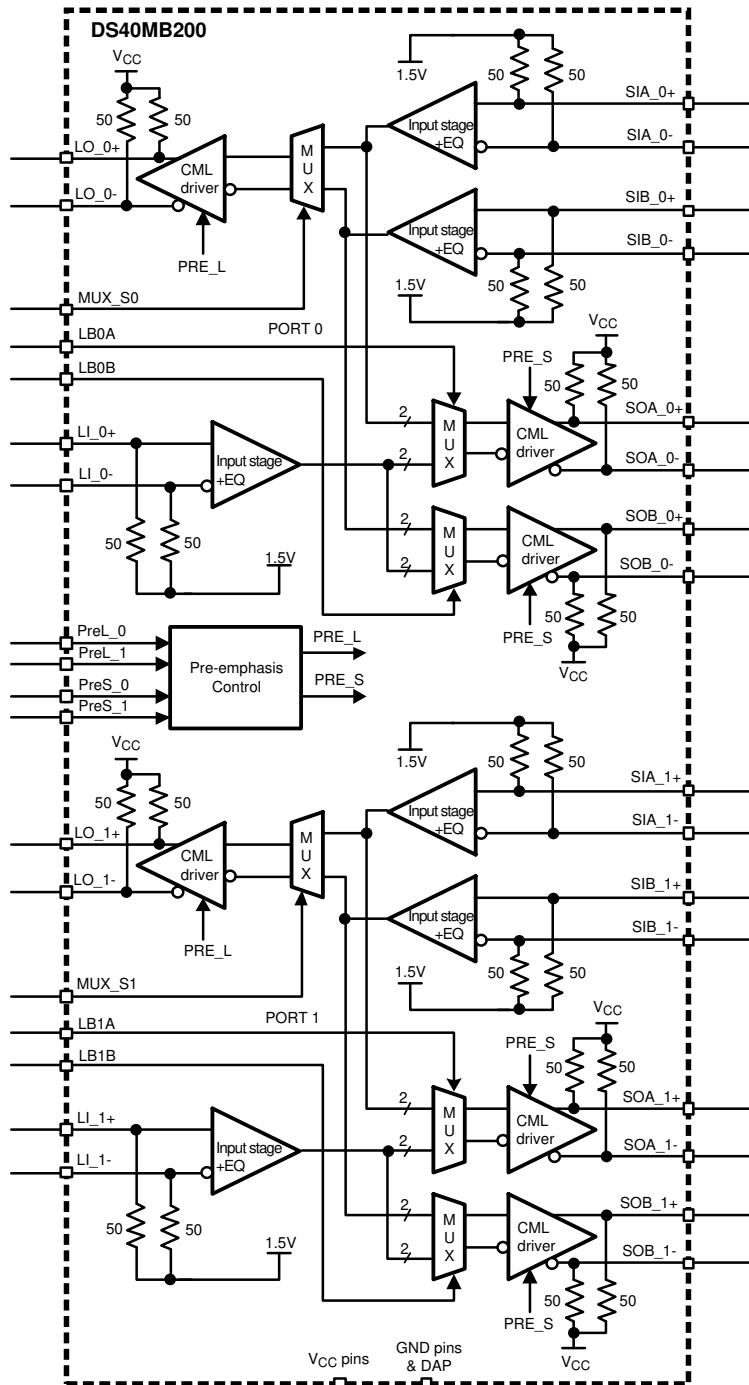

## 概略ブロック図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|              |    |                         |    |

|--------------|----|-------------------------|----|

| 1 特長         | 1  | 8 アプリケーションと実装           | 14 |

| 2 アプリケーション   | 1  | 8.1 アプリケーション情報          | 14 |

| 3 概要         | 1  | 8.2 代表的なアプリケーション        | 14 |

| 4 ピン構成および機能  | 3  | 9 電源に関する推奨事項            | 19 |

| 5 仕様         | 5  | 10 レイアウト                | 19 |

| 5.1 絶対最大定格   | 5  | 10.1 レイアウトのガイドライン       | 19 |

| 5.2 ESD 定格   | 5  | 10.2 レイアウト例             | 19 |

| 5.3 推奨動作定格   | 5  | 11 デバイスおよびドキュメントのサポート   | 21 |

| 5.4 熱に関する情報  | 5  | 11.1 ドキュメントのサポート        | 21 |

| 5.5 電気的特性    | 6  | 11.2 ドキュメントの更新通知を受け取る方法 | 21 |

| 5.6 スイッチング特性 | 7  | 11.3 サポート・リソース          | 21 |

| 5.7 代表的特性    | 9  | 11.4 商標                 | 21 |

| 6 パラメータ測定情報  | 9  | 11.5 静電気放電に関する注意事項      | 21 |

| 7 詳細説明       | 10 | 11.6 用語集                | 21 |

| 7.1 概要       | 10 | 12 改訂履歴                 | 21 |

| 7.2 機能ブロック図  | 10 | 13 メカニカル、パッケージ、および注文情報  | 22 |

| 7.3 機能説明     | 11 |                         |    |

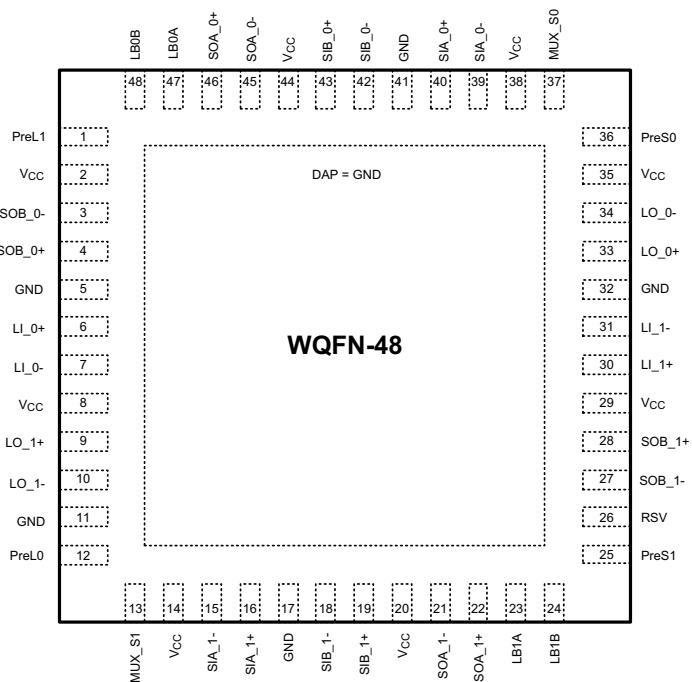

## 4 ピン構成および機能

図 4-1. NJU パッケージ 48 ピン WQFN 上面図

表 4-1. ピンの機能

| ピン                   |    | I/O <sup>(1)</sup> | 説明 <sup>(2)</sup>                                                                                 |

|----------------------|----|--------------------|---------------------------------------------------------------------------------------------------|

| 名称                   | 番号 |                    |                                                                                                   |

| <b>ライン側高速差動 I/O</b>  |    |                    |                                                                                                   |

| LI_0+                | 6  | I                  | ライン側の port_0 の反転および非反転差動入力。LI_0+ および LI_0- は、内部リファレンス電圧に内部で 50Ω を接続しています。図 1-1 を参照してください。         |

| LI_0-                | 7  |                    |                                                                                                   |

| LI_1+                | 30 | I                  | ライン側の port_1 の反転および非反転差動入力。LI_1+ および LI_1- は、内部リファレンス電圧に内部で 50Ω を接続しています。図 1-1 を参照してください。         |

| LI_1-                | 31 |                    |                                                                                                   |

| LO_0+                | 33 | O                  | ライン側の port_0 の反転および非反転差動出力。LO_0+ および LO_0- は、V <sub>CC</sub> に内部で 50Ω を接続しています。                   |

| LO_0-                | 34 |                    |                                                                                                   |

| LO_1+                | 9  | O                  | ライン側の port_1 の反転および非反転差動出力。LO_1+ および LO_1- は、V <sub>CC</sub> に内部で 50Ω を接続しています。                   |

| LO_1-                | 10 |                    |                                                                                                   |

| <b>スイッチ側高速差動 I/O</b> |    |                    |                                                                                                   |

| SIA_0+               | 40 | I                  | switch_A 側の mux_0 への反転および非反転差動入力。SIA_0+ および SIA_0- は、内部リファレンス電圧に内部で 50Ω を接続しています。図 1-1 を参照してください。 |

| SIA_0-               | 39 |                    |                                                                                                   |

| SIA_1+               | 16 | I                  | switch_A 側の mux_1 への反転および非反転差動入力。SIA_1+ および SIA_1- は、内部リファレンス電圧に内部で 50Ω を接続しています。図 1-1 を参照してください。 |

| SIA_1-               | 15 |                    |                                                                                                   |

| SIB_0+               | 43 | I                  | switch_B 側の mux_0 への反転および非反転差動入力。SIB_0+ および SIB_0- は、内部リファレンス電圧に内部で 50Ω を接続しています。図 1-1 を参照してください。 |

| SIB_0-               | 42 |                    |                                                                                                   |

| SIB_1+               | 19 | I                  | switch_B 側の mux_1 への反転および非反転差動入力。SIB_1+ および SIB_1- は、内部リファレンス電圧に内部で 50Ω を接続しています。図 1-1 を参照してください。 |

| SIB_1-               | 18 |                    |                                                                                                   |

| SOA_0+               | 46 | O                  | switch_A 側にある mux_0 の反転および非反転差動出力。SOA_0+ および SOA_0- は、V <sub>CC</sub> に内部で 50Ω を接続しています。          |

| SOA_0-               | 45 |                    |                                                                                                   |

| SOA_1+               | 22 | O                  | switch_A 側にある mux_1 の反転および非反転差動出力。SOA_1+ および SOA_1- は、V <sub>CC</sub> に内部で 50Ω を接続しています。          |

| SOA_1-               | 21 |                    |                                                                                                   |

| SOB_0+               | 4  | O                  | switch_B 側にある mux_0 の反転および非反転差動出力。SOB_0+ および SOB_0- は、V <sub>CC</sub> に内部で 50Ω を接続しています。          |

| SOB_0-               | 3  |                    |                                                                                                   |

表 4-1. ピンの機能 (続き)

| ピン                       |                                    | I/O <sup>(1)</sup> | 説明 <sup>(2)</sup>                                                                                                                                                                                                                                            |

|--------------------------|------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称                       | 番号                                 |                    |                                                                                                                                                                                                                                                              |

| SOB_1+<br>SOB_1-         | 28<br>27                           | O                  | switch_B 側にある mux_1 の反転および非反転差動出力。SOB_1+ および SOB_1- は、V <sub>CC</sub> に内部で 50Ω を接続しています。                                                                                                                                                                     |

| <b>制御 (3.3V LVC MOS)</b> |                                    |                    |                                                                                                                                                                                                                                                              |

| LB0A                     | 47                                 | I                  | LB0A をロジック Low にすると、SIA_0± から SOA_0± までの内部ループバック パスがイネーブルになります。LB0A は内部で High にプルアップされています。                                                                                                                                                                  |

| LB0B                     | 48                                 | I                  | LB0B をロジック Low にすると、SIB_0± から SOB_0± までの内部ループバック パスがイネーブルになります。LB0B は内部で High にプルアップされています。                                                                                                                                                                  |

| LB1A                     | 23                                 | I                  | LB1A をロジック Low にすると、SIA_1± から SOA_1± までの内部ループバック パスがイネーブルになります。LB1A は内部で High にプルアップされています。                                                                                                                                                                  |

| LB1B                     | 24                                 | I                  | LB1B をロジック Low にすると、SIB_1± から SOB_1± までの内部ループバック パスがイネーブルになります。LB1B は内部で High にプルアップされています。                                                                                                                                                                  |

| MUX_S0                   | 37                                 | I                  | MUX_S0 をロジック Low にすると、mux_0 を switch B に選択します。MUX_S0 は内部で High にプルアップされます。mux_0 のデフォルト状態は switch A です。                                                                                                                                                       |

| MUX_S1                   | 13                                 | I                  | MUX_S1 をロジック Low にすると、mux_1 を switch B に選択します。MUX_S1 は内部で High にプルアップされます。mux_1 のデフォルト状態は switch A です。                                                                                                                                                       |

| PREL_0<br>PREL_1         | 12<br>1                            | I                  | PREL_0 および PREL_1 は、ライン側ドライバの出力プリエンファシス (LO_0± および LO_1±) を選択します。PREL_0 および PREL_1 は内部で High にプルアップされます。ライン側のプリエンファシス レベルについては、表 7-3 を参照してください。                                                                                                              |

| PRES_0<br>PRES_1         | 36<br>25                           | I                  | PRES_0 および PRES_1 は、スイッチ側ドライバ (SOA_0±, SOB_0±, SOA_1±, SOB_1±) の出力プリエンファシスを選択します。PRES_0 および PRES_1 は内部で High にプルアップされます。スイッチ側のプリエンファシス レベルについては、表 7-4 を参照してください。                                                                                             |

| RSV                      | 26                                 | I                  | 出荷時テストをサポートするための予約ピン。このピンはオープンのままにするか、GND に接続する、あるいは外付けプルダウン抵抗を介して GND に接続することができます。                                                                                                                                                                         |

| <b>電源</b>                |                                    |                    |                                                                                                                                                                                                                                                              |

| GND                      | 5, 11, 17,<br>32, 41               | P                  | グラウンド基準。各グラウンドピンは、低インダクタンスのパスを経由してグラウンド プレーンに接続する必要があり、通常、GND ピンのランディング パッドのできるだけ近くに配置されたビアを使用します。                                                                                                                                                           |

| GND                      | DAP                                | P                  | ダイアタッチ パッド (DAP) は、WQFN-48 パッケージの底面、中央にある金属コントクトです。グラウンド インピーダンスを低減し、パッケージの放熱性能を向上させるため、少なくとも 4 つのビアを使用して GND プレーンに接続する必要があります。                                                                                                                              |

| V <sub>CC</sub>          | 2, 8, 14, 20,<br>29, 35, 38,<br>44 | P                  | V <sub>CC</sub> = 3.3V ± 5%。<br>各 V <sub>CC</sub> ピンは、低インダクタンスのパスを経由して V <sub>CC</sub> プレーンに接続する必要があり、通常、V <sub>CC</sub> ピンのランディング パッドのできるだけ近くに配置されたビアを使用します。<br>各 V <sub>CC</sub> ピンとグラウンド プレーンの間に、0.01μF または 0.1μF の X7R、0402 サイズのバイパス コンデンサを接続することを推奨します。 |

(1) I = 入力、O = 出力、P = 電源

(2) すべての CML 入力または出力は AC 結合する必要があります。

## 5 仕様

### 5.1 絶対最大定格

(1) (2) を参照

|                   | 最小値  | 最大値            | 単位 |

|-------------------|------|----------------|----|

| 電源電圧 ( $V_{CC}$ ) | -0.3 | 4              | V  |

| CMOS/TTL 入力電圧     | -0.3 | $V_{CC} + 0.3$ | V  |

| CML 入出力電圧         | -0.3 | $V_{CC} + 0.3$ | V  |

| 接合部温度             |      | 125            | °C |

| リード温度 (半田付け、4 秒)  |      | 260            | °C |

| 保管温度、 $T_{stg}$   | -65  | 150            | °C |

- (1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについての話で、絶対最大定格において、またはこのデータシートの「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。絶対最大定格の状態が長時間続くと、デバイスの信頼性に影響を与える可能性があります。

- (2) 防衛または航空宇宙仕様のデバイスをお求めの場合は、供給状況および仕様についてテキサス・インスツルメンツの営業所または販売代理店にお問い合わせください。

### 5.2 ESD 定格

|                  | 値                                                                | 単位    |

|------------------|------------------------------------------------------------------|-------|

| $V_{(ESD)}$ 静電放電 | 人体モデル (HBM)、1.5kΩ、100pF、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup> | ±6000 |

|                  | マシン モデル (MM)、JEDEC 規格 JESD22-A115-A に準拠                          | ±250  |

- (1) JEDEC のドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

### 5.3 推奨動作定格

|                        | 最小値   | 公称値 | 最大値   | 単位               |

|------------------------|-------|-----|-------|------------------|

| 電源電圧 ( $V_{CC}$ - GND) | 3.135 | 3.3 | 3.465 | V                |

| 電源ノイズの振幅 (10Hz~2GHz)   |       |     | 20    | mV <sub>PP</sub> |

| 周囲温度                   | 0     |     | 85    | °C               |

| ケース温度                  |       |     | 100   | °C               |

### 5.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup>                     | DS40MB200  | 単位   |

|------------------------------------------|------------|------|

|                                          | NJU (WQFN) |      |

|                                          | 48 ピン      |      |

| $R_{\theta JA}$ 接合部から周囲への熱抵抗             | 32.3       | °C/W |

| $R_{\theta JC(top)}$ 接合部からケース (上面) への熱抵抗 | 15.2       | °C/W |

| $R_{\theta JB}$ 接合部から基板への熱抵抗             | 9          | °C/W |

| $\Psi_{JT}$ 接合部から上面への特性パラメータ             | 0.2        | °C/W |

| $\Psi_{JB}$ 接合部から基板への特性パラメータ             | 9          | °C/W |

| $R_{\theta JC(bot)}$ 接合部からケース (底面) への熱抵抗 | 2.5        | °C/W |

- (1) 従来および最新の熱測定基準の詳細については、アプリケーション レポート『半導体および IC パッケージの熱評価基準』、[SPRA953](#) を参照してください。

## 5.5 電気的特性

推奨動作電源電圧および温度範囲内 (特に記述のない限り)

| パラメータ                | テスト条件                                              | 最小値                                                                                                                                                                                                                                                                                                | 標準値 <sup>(1)</sup>   | 最大値            | 単位        |

|----------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------|-----------|

| <b>LVC MOS DC 仕様</b> |                                                    |                                                                                                                                                                                                                                                                                                    |                      |                |           |

| $V_{IH}$             | High レベル入力電圧                                       | 2                                                                                                                                                                                                                                                                                                  |                      | $V_{CC} + 0.3$ | V         |

| $V_{IL}$             | Low レベル入力電圧                                        | -0.3                                                                                                                                                                                                                                                                                               |                      | 0.8            | V         |

| $I_{IH}$             | High レベル入力電流                                       | $V_{IN} = V_{CC}$                                                                                                                                                                                                                                                                                  | -10                  |                | $\mu A$   |

| $I_{IL}$             | Low レベル入力電流                                        | $V_{IN} = GND$                                                                                                                                                                                                                                                                                     | 75                   | 94             | $\mu A$   |

| $R_{PU}$             | プル High 抵抗                                         |                                                                                                                                                                                                                                                                                                    | 35                   |                | $k\Omega$ |

| <b>レシーバの仕様</b>       |                                                    |                                                                                                                                                                                                                                                                                                    |                      |                |           |

| $V_{ID}$             | 差動入力電圧範囲                                           | AC 結合した差動信号。<br>このパラメータの製品テストは行つ<br>ていません。                                                                                                                                                                                                                                                         | 1.25Gbps 未満          | 100            | 1750      |

|                      |                                                    |                                                                                                                                                                                                                                                                                                    | 1.25Gbps ~ 3.125Gbps | 100            | 1560      |

|                      |                                                    |                                                                                                                                                                                                                                                                                                    | 3.125Gbps 超          | 100            | 1200      |

| $V_{ICM}$            | レシーバ入力の同相モー<br>ド電圧                                 | グランドを基準としてレシーバ入力で測定。                                                                                                                                                                                                                                                                               |                      | 1.3            | V         |

| $R_{ITD}$            | 入力差動終端                                             | IN+ または IN- の間のオンチップ差動終端。                                                                                                                                                                                                                                                                          | 84                   | 100            | 116       |

| <b>ドライバの仕様</b>       |                                                    |                                                                                                                                                                                                                                                                                                    |                      |                |           |

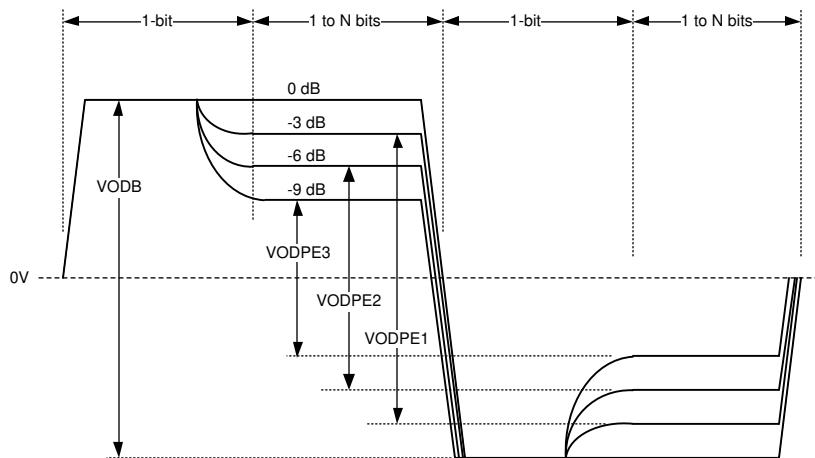

| $V_{ODB}$            | プリエンファシスなしの出<br>力差動電圧スイング                          | $R_L = 100\Omega \pm 1\%$<br>$PRES\_1 = PRES\_0 = 0$<br>$PREL\_1 = PREL\_0 = 0$<br>ドライバプリエンファシスはディセーブル。<br>K28.7 パターンを 4Gbps で実行します。<br>テスト回路については、「 <a href="#">AC テスト回路</a> 」を参照してください。                                                                                                          | 1000                 | 1200           | 1400      |

| $V_{PE}$             | 出力プリエンファシス電圧<br>比<br>$20 \times \log (VODPE/VODB)$ | $R_L = 100\Omega \pm 1\%$<br>K28.7 パターンを<br>4Gbps で実行 <sup>(2)</sup><br>$x = S$ (スイッチ側プリエンファシス<br>制御)<br>$x = L$ (ライン側プリエンファシス制<br>御)<br>、波形については「 <a href="#">ドライバのプリエ<br/>ンファシス差動波形 (4 つのプリエ<br/>ンファシス ステップすべてを表示)</a> 」<br>を参照してください。<br>テスト回路については、「 <a href="#">AC テスト<br/>回路</a> 」を参照してください。 | PREx_[1:0] = 00      |                | 0         |

|                      |                                                    |                                                                                                                                                                                                                                                                                                    | PREx_[1:0] = 01      |                | -3        |

|                      |                                                    |                                                                                                                                                                                                                                                                                                    | PREx_[1:0] = 10      |                | -6        |

|                      |                                                    |                                                                                                                                                                                                                                                                                                    | PREx_[1:0] = 11      |                | -9        |

|                      |                                                    |                                                                                                                                                                                                                                                                                                    |                      |                | dB        |

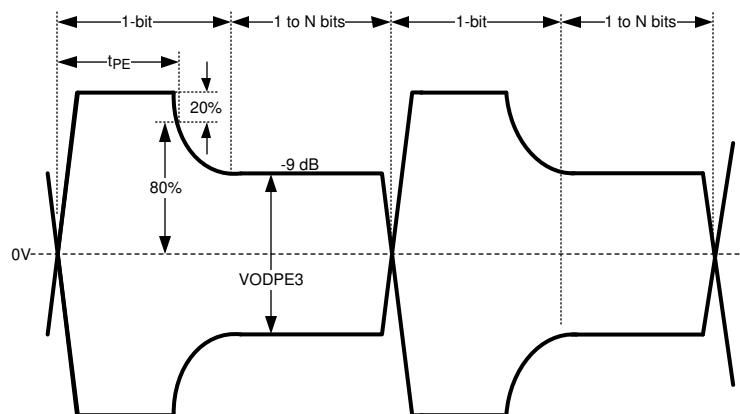

| $t_{PE}$             | プリエンファシス幅 <sup>(3)</sup>                           | -9dB プリエンファシスレベルでテスト、 $PREx[1:0] = 11$<br>$x = S$ (スイッチ側プリエンファシス制御)<br>$x = L$ (ライン側プリエンファシス制御)<br>測定条件については「 <a href="#">出力プリエンファシス期間のテスト条件</a> 」を<br>参照してください。                                                                                                                                   | 125                  | 200            | 250       |

| $R_{OTSE}$           | 出力の終端                                              | OUT+ または OUT- から $V_{CC}$ までのオンチップ終端 <sup>(4)</sup>                                                                                                                                                                                                                                                | 42                   | 50             | 58        |

| $R_{OTD}$            | 出力差動終端                                             | OUT+ と OUT- の間のオンチップ差動終端 <sup>(4)</sup>                                                                                                                                                                                                                                                            |                      | 100            |           |

| $\Delta R_{OTSE}$    | 出力終端抵抗のミスマッ<br>チ                                   | OUT+ と OUT- の出力終端のミスマッチ <sup>(4)</sup>                                                                                                                                                                                                                                                             |                      |                | 5%        |

| $V_{OCM}$            | 出力同相電圧                                             |                                                                                                                                                                                                                                                                                                    |                      | 2.7            | V         |

| <b>消費電力</b>          |                                                    |                                                                                                                                                                                                                                                                                                    |                      |                |           |

| $P_D$                | 消費電力                                               | $V_{DD} = 3.465V$<br>すべての出力は $100\Omega \pm 1\%$ で終端されます。<br>$PREL\_1 = 0$ , $PRES\_1 = 0$<br>PRBS $2^7 - 1$ パターンを 4Gbps で実行                                                                                                                                                                       |                      | 1              | W         |

## 5.5 電気的特性 (続き)

推奨動作電源電圧および温度範囲内 (特に記述のない限り)

| パラメータ             |                                  | テスト条件                                                                                 | 最小値                    | 標準値 <sup>(1)</sup> | 最大値 | 単位                |

|-------------------|----------------------------------|---------------------------------------------------------------------------------------|------------------------|--------------------|-----|-------------------|

| <b>AC 特性</b>      |                                  |                                                                                       |                        |                    |     |                   |

| RJ                | デバイスのランダム ジッタ <sup>(5) (3)</sup> | テスト回路については、「 <a href="#">AC テスト回路</a> 」を参照してください。<br>1-0 の交互パターン。<br>プリエンファシスはディセーブル。 | 1.25Gbps 時             |                    | 2   | ps <sub>rms</sub> |

|                   |                                  |                                                                                       | 4Gbps 時                |                    | 2   |                   |

| DJ                | デバイスの確定的ジッタ <sup>(6) (3)</sup>   | テスト回路については、「 <a href="#">AC テスト回路</a> 」を参照してください。<br>プリエンファシスはディセーブル。                 | 4Gbps 時、<br>PRBS7 パターン |                    | 30  | ps <sub>p-p</sub> |

| DR <sub>MAX</sub> | 最大データレート <sup>(3)</sup>          | 1-0 の交互パターンでテスト済み                                                                     |                        | 4                  |     | Gbps              |

- (1)  $V_{CC} = 3.3V$ 、 $T_A = 25^\circ C$  で測定された標準パラメータ。これらは参考用であり、実製品でのテストは行っていません。

(2) K28.7 パターンは、K28.7 コードグループ {001111 1000} の 10 ビット反復パターンです。K28.5 パターンは、+K28.5 および -K28.5 コードグループ {110000 0101 001111 1010} の 20 ビット反復パターンです。

(3) 設計と統計分析による特性により規定されています。

(4) IN+ と IN- は、DS40MB200 の多くの相補入力のペアの 1 つを指す一般名です。OUT+ と OUT- は、DS40MB200 の相補出力の多くのペアの 1 つを指す一般名です。差動入力電圧  $V_{ID}$  は  $|IN+ - IN-|$  として定義されます。差動出力電圧  $V_{OD}$  は  $|OUT+ - OUT-|$  として定義されます。

(5) デバイス出力のランダム ジッタは、デバイスによるランダム ジッタの寄与の測定値です。この値は、式  $\sqrt{RJ_{OUT}^2 - RJ_{IN}^2}$  で導出されます。ここで、 $RJ_{OUT}$  はデバイスの出力で測定されたランダム ジッタ (ps<sub>rms</sub>) で、 $RJ_{IN}$  はデバイスを駆動するパターン ジェネレータのランダム ジッタです。

(6) デバイス出力の確定的ジッタは、デバイスから発生する確定的ジッタの測定値です。これは式  $(DJ_{OUT} - DJ_{IN})$  で導出されます。ここで、 $DJ_{OUT}$  はデバイスの出力で測定されたピーク ツー ピークの確定的ジッタ (ps<sub>p-p</sub>) で、 $DJ_{IN}$  はデバイスを駆動するパターン ジェネレータのピーク ツー ピークの確定的ジッタです。

## 5.6 スイッチング特性

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ             |                           | テスト条件                                                             | 最小値 | 標準値 <sup>(1)</sup> | 最大値 | 単位 |

|-------------------|---------------------------|-------------------------------------------------------------------|-----|--------------------|-----|----|

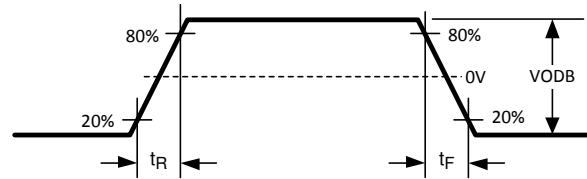

| t <sub>R</sub>    | Low から High への差動遷移時間      | 100MHz においてクロック類似のパターンで、差動出力電圧の 20%~80% の範囲で測定。プリエンファシスはディセーブル。   |     | 80                 |     | ps |

|                   | High から Low への差動遷移時間      |                                                                   |     | 80                 |     | ps |

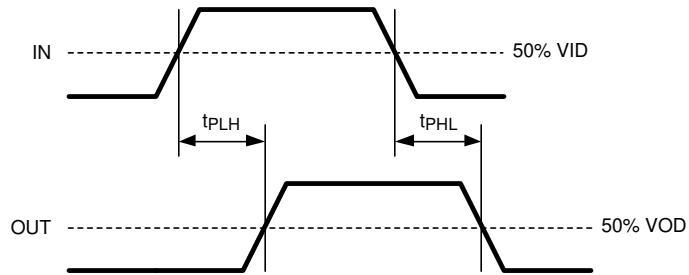

| t <sub>PLH</sub>  | Low から High の差動伝搬遅延       | 入力から出力への差動電圧の 50% で測定。                                            | 0.5 | 2                  | ns  |    |

| t <sub>PHL</sub>  | High から Low への差動伝搬遅延      |                                                                   | 0.5 | 2                  | ns  |    |

| t <sub>SKP</sub>  | パルス スキュー <sup>(2)</sup>   | t <sub>PHL</sub> -t <sub>PLH</sub>                                |     | 20                 |     | ps |

| t <sub>SKO</sub>  | 出力スキュー <sup>(3) (2)</sup> | 同じデバイス内のデータ パス間の伝搬遅延の差。                                           |     | 200                |     | ps |

| t <sub>SKPP</sub> | 部品間スキュー <sup>(2)</sup>    | 同じ条件で動作しているデバイスからの同じ出力間での伝搬遅延の差。                                  |     | 500                |     | ps |

| t <sub>SM</sub>   | MUX の切り替え時間               | マルチプレクサ制御またはループバック制御の $V_{IH}$ または $V_{IL}$ から、有効な差動出力の 50% まで測定。 | 1.8 | 6                  | ns  |    |

- (1)  $V_{CC} = 3.3V$ 、 $T_A = 25^\circ C$  で測定される標準パラメータ。これらは参考用であり、実製品でのテストは行っていません。

(2) 設計と統計分析による特性により規定されています。

(3) t<sub>SKO</sub> は、同じポートのスイッチ A とスイッチ B 間のデータパス、およびポート 0 とポート 1 間の同様のデータパス間の伝播遅延の大きさの差です。たとえば、SIA\_0± から LO\_0±、SIB\_0± から LO\_0±、SIA\_1± から LO\_1±、SIB\_1± から LO\_1± までのデータ パス間の出力スキューです。もう 1 つの例は、LI\_0± から SOA\_0±、LI\_0± から SOB\_0±、LI\_1± から SOA\_1±、LI\_1± から SOB\_1± までのデータ パス間の出力スキューです。t<sub>SKO</sub> は、同じポートのループバック パス、およびポート 0 とポート 1 の間の類似データ パス間の遅延スキューも指します。たとえば、データ パス SIA\_0± から SOA\_0±、SIB\_0± から SOB\_0±、SIA\_1± から SOA\_1±、SIB\_1± から SOB\_1± の間の出力スキューです。

図 5-1. ドライバ出力遷移時間

図 5-2. 入力から出力への伝搬遅延

図 5-3. 出力プリエンファシス期間のテスト条件

## 5.7 代表的特性

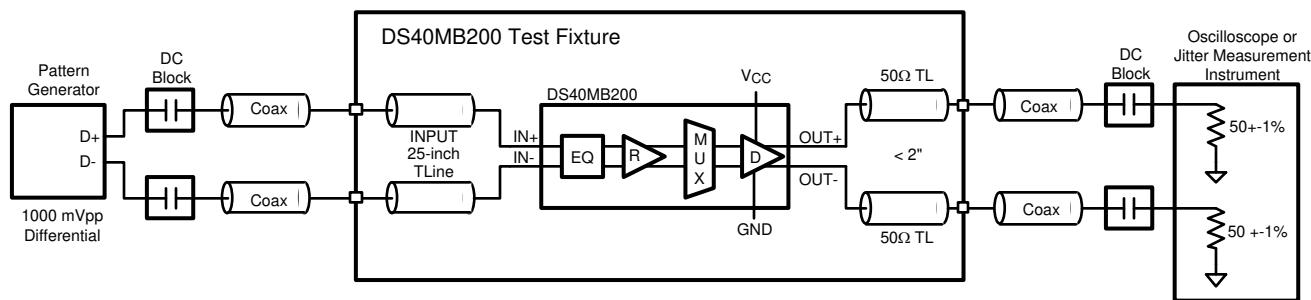

## 6 パラメータ測定情報

図 6-1. AC 測定回路

## 7 詳細説明

### 7.1 概要

DS40MB200 は信号コンディショニング 2:1 マルチプレクサおよび 1:2 バッファで、1~4Gbps のエンコードまたはスカラーブルド データレートでポート冗長性をサポートするよう設計されています。DS40MB200 は、信号到達範囲の延長をサポートするために、受信入力のイコライザ、および出力のプリエンファシス制御を実行します。

### 7.2 機能ブロック図

## 7.3 機能説明

DS40MB200 マルチプレクサ バッファは、いくつかの重要なブロックで構成されています。

- CML 入力および EQ

- マルチプレクサとループバック制御

- CML ドライバとプリエンファシス制御

### 7.3.1 CML 入力およびEQ

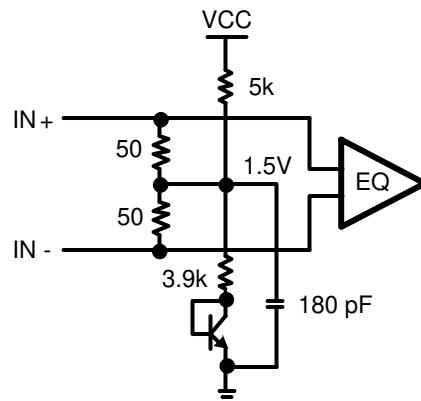

高速入力は **IN+** および **IN-** で約 1.3V に自己バイアスされ、AC カップリング用に設計されます。内部レシーバ入力終端およびバイアス回路の詳細については、「[レシーバ入力の終端およびバイアス回路](#)」を参照してください。

図 7-1. レシーバ入力終端およびバイアス回路

入力は、LVDS、LVPECL、CML など、ほとんどの AC カップリング差動信号と互換性があります。DS40MB200 は、1000Mbps 未満のデータ速度、または CML の入力または出力に DC バイアスが印加された状態で動作するようには設計されていません。ほとんどの高速リンクは DC バランス用にエンコードされ、AC カップリング コンデンサを含めるように規定されているため、DS40MB200 を制限なくデータパスに直接挿入できます。理想的な AC カップリング コンデンサの値は、多くの場合、シリアル リンクに組み込まれている最低周波数成分に基づいています。AC カップリング コンデンサの標準値の範囲は 100~1000nF です。スクランブルされたデータを含む一部の仕様では、最適な性能を得るために、より大きなコンデンサが必要になる場合があります。AC カップリング コンデンサの周囲および内部での望ましくない寄生効果を低減するために、本体サイズ 0402 を推奨します。[AC テスト回路](#)に、AC テスト回路内の AC カップリング コンデンサの配置を示します。

各入力段には固定イコライザがあり、短いバックプレーン パターン (約 10 インチのバックプレーン) による約 5dB (2GHz) の伝送損失を補償するイコライズが行われます。

### 7.3.2 マルチプレクサとループバック制御

表 7-1 および [表 7-2](#) に、DS40MB200 マルチプレクサおよびループバックの設定方法の詳細を示します。

表 7-1. 多重化制御の論理表

| ピン            | ピンの値      | MUX 関数                               |

|---------------|-----------|--------------------------------------|

| <b>MUX_S0</b> | 0         | MUX_0 select switch_B input, SIB_0±. |

|               | 1 (デフォルト) | MUX_0 select switch_A input, SIA_0±. |

| <b>MUX_S1</b> | 0         | MUX_1 select switch_B input, SIB_1±. |

|               | 1 (デフォルト) | MUX_1 select switch_A input, SIA_0±. |

表 7-2. ループバック制御の論理表

| ピン   | ピンの値      | ループバック機能                         |

|------|-----------|----------------------------------|

| LB0A | 0         | SIA_0± から SOA_0± へのループバックをイネーブル。 |

|      | 1 (デフォルト) | 通常モード。ループバックはディセーブル。             |

| LB0B | 0         | SIB_0± から SOB_0± へのループバックをイネーブル。 |

|      | 1 (デフォルト) | 通常モード。ループバックはディセーブル。             |

| LB1A | 0         | SIA_1± から SOA_1± へのループバックをイネーブル。 |

|      | 1 (デフォルト) | 通常モード。ループバックはディセーブル。             |

| LB1B | 0         | SIB_1± から SOB_1± へのループバックをイネーブル。 |

|      | 1 (デフォルト) | 通常モード。ループバックはディセーブル。             |

### 7.3.3 CML ドライバとプリエンファシス制御

出力ドライバにはプリエンファシス (ドライバ側のイコライゼーション) があり、駆動しているバックプレーンの伝送損失を補償します。このドライバは、バックプレーン端で低周波数と高周波数のパルスがほぼ同じ振幅に達するように出力信号を調整し、振幅のばらつきによって生じる確定的ジッタを最小限に抑えます。DS40MB200 では、異なる長さのバックプレーンに対応するため、0、-3、-6、-9dB の範囲で 4 つのステップのプリエンファシスをユーザーが選択できます。図 1-1 に、ドライバのプリエンファシス波形を示します。プリエンファシス持続時間は公称 200ps で、4Gbps で 0.8 ユニットインターバル (UI) に対応します。スイッチ側とライン側のプリエンファシスレベルは、個別にプログラム可能です。

図 7-2. ドライバのプリエンファシス差動波形 (4 つのプリエンファシス ステップすべてを表示)

表 7-3. ライン側のプリエンファシス制御

| PreL_[1:0]  | プリエンファシス レベル (mV <sub>PP</sub> (VODB) 単位) | ディエンファシス レベル (mV <sub>PP</sub> (VODPE) 単位) | プリエンファシス (dB (VODPE/VODB) 単位) | FR4 ボードの標準的なパターン |

|-------------|-------------------------------------------|--------------------------------------------|-------------------------------|------------------|

| 0 0         | 1200                                      | 1200                                       | 0                             | 10 inches        |

| 0 1         | 1200                                      | 850                                        | -3                            | 20 inches        |

| 1 0         | 1200                                      | 600                                        | -6                            | 30 inches        |

| 1 1 (デフォルト) | 1200                                      | 426                                        | -9                            | 40 inches        |

表 7-4. スイッチ側のプリエンファシス制御

| PreS_[1:0] | プリエンファシス レベル (mV <sub>PP</sub> (VODB) 単位) | ディエンファシス レベル (mV <sub>PP</sub> (VODPE) 単位) | プリエンファシス (dB (VODPE/VODB) 単位) | FR4 ボードの標準的なパターン |

|------------|-------------------------------------------|--------------------------------------------|-------------------------------|------------------|

| 0 0        | 1200                                      | 1200                                       | 0                             | 10 inches        |

**表 7-4. スイッチ側のプリエンファシス制御 (続き)**

| PreS_[1:0]     | プリエンファシス レベル (mV <sub>PP</sub><br>(VODB) 単位) | デイエンファシス レベル (mV <sub>PP</sub><br>(VODPE) 単位) | プリエンファシス (dB<br>(VODPE/VODB) 単位) | FR4 ボードの標準的<br>な<br>パターン |

|----------------|----------------------------------------------|-----------------------------------------------|----------------------------------|--------------------------|

| 0 1            | 1200                                         | 850                                           | -3                               | 20 inches                |

| 1 0            | 1200                                         | 600                                           | -6                               | 30 inches                |

| 1 1<br>(デフォルト) | 1200                                         | 426                                           | -9                               | 40 inches                |

## 8 アプリケーションと実装

### 注

以下のアプリケーションに関するセクションの情報は、テキサス・インストルメンツの部品仕様の一部ではなく、テキサス・インストルメンツはこれらの情報の正確性や完全性を保証しません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 アプリケーション情報

DS40MB200 は 2:1 マルチプレクサおよび 1:2 バッファで、最大 4Gbps で入力データをイコライズして、送信プリエンプアシス制御により全体の信号到達範囲を改善します。マルチプレクサ バッファとしての DS40MB200 は、ポートの共有や冗長性の他、ルートおよびデータ接続のオンザフライ再構成を必要とする設計に最適です。

### 8.2 代表的なアプリケーション

図 1-1 と 図 1-1 に DS40MB200 の代表的なアプリケーションを示します。

図 8-1. システム図 (ポート 0 のデータ パスを表示)

図 8-2. DS40MB200 接続ブロック図 (ポート 0 のデータ パスを表示)

### 8.2.1 設計要件

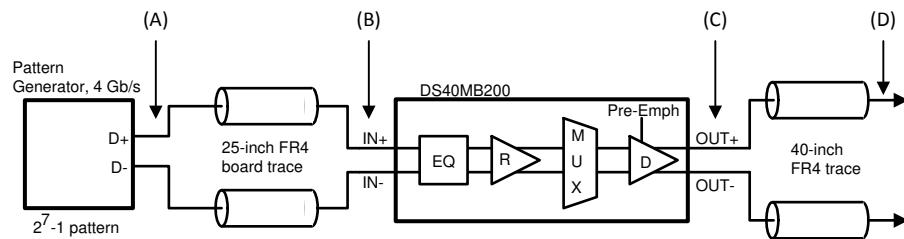

標準的な設計では、DS40MB200 の入力の短いバックプレーン パターンは均一で、DS40MB200 の出力の長いパターンも均一です。このアプリケーション例では、短いバックプレーンリンクの代わりに 25 インチ FR4 結合のマイクロストリップ基板パターンが使用されています。図 1-1 に、この例のブロック図を示します。

図 8-3. DS40MB200 アプリケーション例のブロック図

25 インチのマイクロストリップ基板パターンでは、375MHz と 1.875GHz の間で約 6dB の減衰が発生し、短いバックプレーン伝送ラインの伝送損失に近くなっています。25 インチのマイクロストリップは、AC 測定のために、パターン ジェネレータと DS40MB200 の差動入力の間に接続されています。

表 8-1. 入力パターンのパラメータ

| パターン長     | 仕上げパターン幅 W | パターン間の間隔 | 誘電体高さ H | 比誘電率 $\epsilon_R$ | 正接損失  |

|-----------|------------|----------|---------|-------------------|-------|

| 25 inches | 8.5mil     | 11.5mil  | 6mil    | 3.8               | 0.022 |

出力パターンの長さは、システム要件によって異なる場合があります。この例では、類似のパターン幅、間隔、誘電特性を持つ 40 インチの FR4 パターンが DS40MB200 の出力に配置されています。

他の高速設計と同様に、全体的な性能に影響を及ぼす要因は多数あります。設計中に検討および検証する必要のある重要な部分のリストを以下に示します。

- 100Ω のインピーダンス パターンを使用します。一般的に、これらは配線長の違いを緩和するために疎結合されています。

- 反射を最小限に抑えるため、各チャネル セグメントのレシーバ端の近くに AC カップリング コンデンサを配置します。

- AC カップリング コンデンサの最大本体サイズは 0402 です。

- ドリルで背面にコネクタのビアと信号ビアを穴開けし、スタブの長さを最小化。

- リターン電流の低インダクタンス パスを確保するため、基準プレーン ビアを使用します。

## 8.2.2 詳細な設計手順

最適な設計のためには、受信データを正しくルーティングし、最高の信号品質を提供するように DS40MB200 を設定する必要があります。次の設計手順に従う必要があります。

1. DS40MB200 は、システム要件を満たすために正しいマルチプレクサおよびバッファ ルートを提供するように設定する必要があります。適切なマルチプレクサ制御設定を行うには、[表 7-1](#) を参照してください。バッファ制御設定を構成するには、[表 7-2](#) を参照してください。たとえば、設計者がスイッチ カード A (SIA0\_0±) の入力をライン カード (LO\_0±) の出力にルーティングする場合を考えます。これを実現するには、MUX\_S0 = 1 に設定します (SIA0\_0± を選択)。ラインカード出力からスイッチカードへの反対方向では、ラインカードからの入力がスイッチカード A (SOA\_0±) とスイッチカード B (SOB\_0±) の両方にバッファされるように、LB0A = 1 および LB0B = 1 を設定します。

2. DS40MB200 は、チャネル全体の減衰に対してオフセット位置に配置されるように設計されています。性能を最適化するために、マルチプレクサ バッファの送信プリエンファシスを調整して、パターン長の到達範囲を延長すると同時に、ソリッド アイの開口部を回復することができます。ラインカード側またはスイッチカード側の送信プリエンファシスを調整するには、[表 7-3](#) および [表 7-4](#) に記載されている、DS40MB200 出力に接続された FR4 ボード配線の長さに応じた推奨プリエンファシス制御設定を参照してください。たとえば、40 インチの FR4 の配線がスイッチカード出力に接続されている場合、VOD = 1200mVpp と -9dB の送信プリエンファシスに対しては PreS\_[1:0] = (1, 1) を設定します。

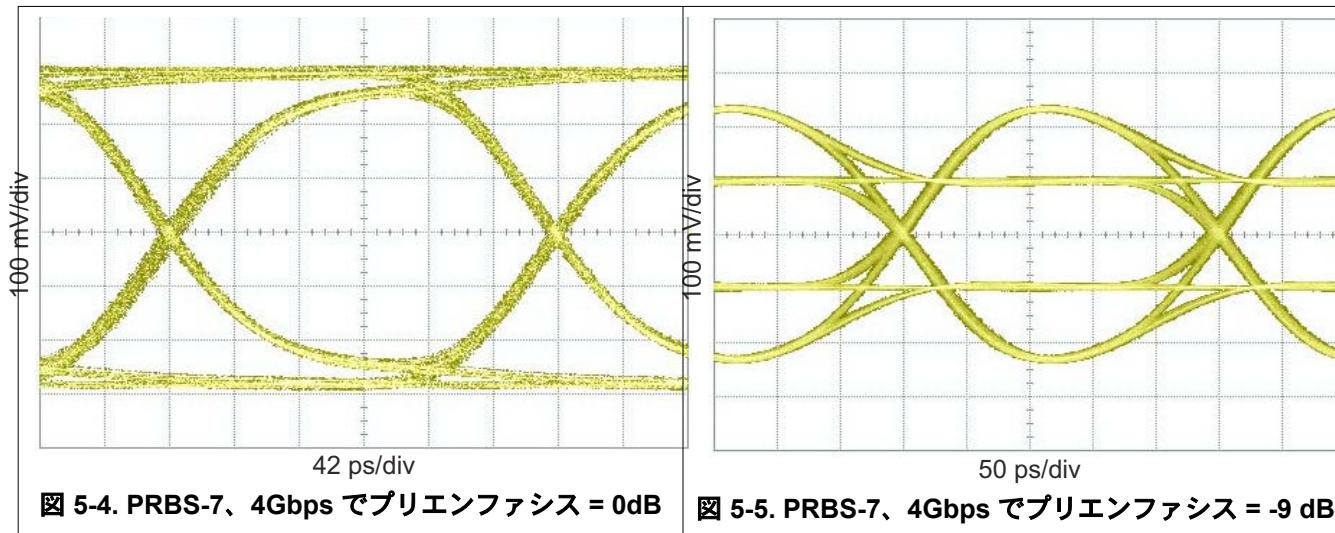

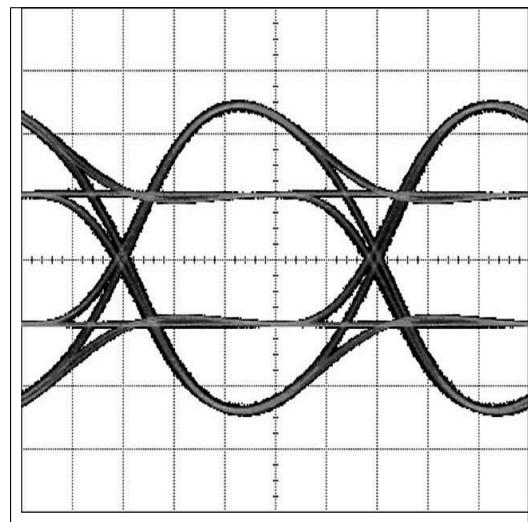

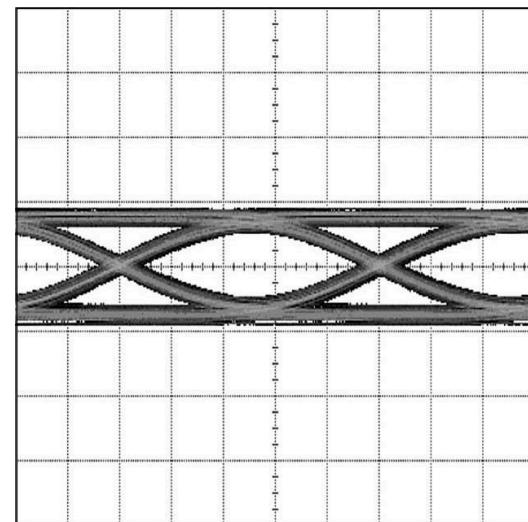

### 8.2.3 アプリケーション曲線

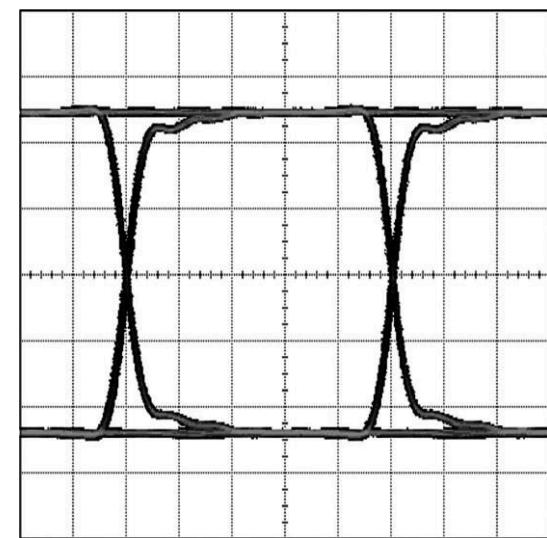

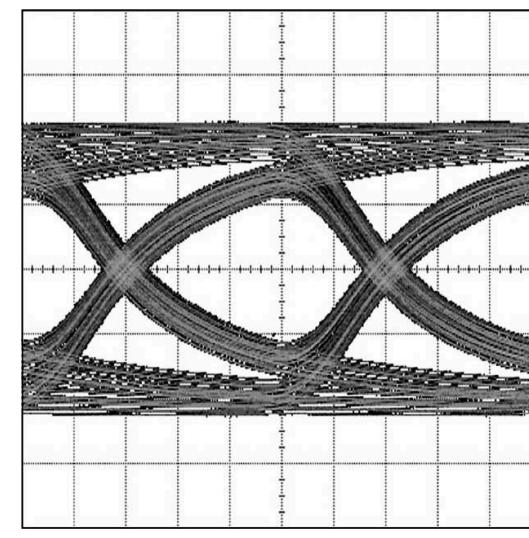

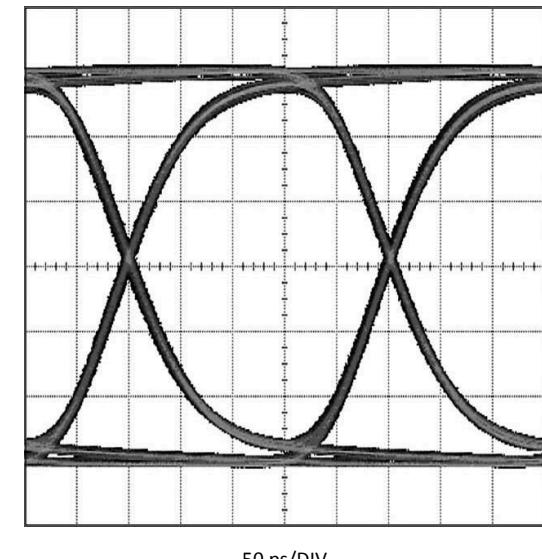

図 1-1 から 図 1-1 に、データパスのさまざまな場所でのシグナル インテグリティの変化を示します。これらの測定位置は、図 1-1 に示すラベル付きのポイントに戻って参照することができます。

- ポイント (A): ソースパターン ジェネレータの出力信号

- ポイント (B): ソースからの FR4 配線の 25 インチ後の DS40MB200 への入力

- ポイント (C): DS40MB200 ドライバの出力

- ポイント (D): DS40MB200 ドライバからの FR4 配線の 40 インチ後の信号

ソース信号は、4Gbps の PRBS-7 パターンです。長い出力配線の場合、-9dB のプリエンファシスを追加することで、FR4 出力配線の 40 インチ後のアイが大幅に改善されます。

図 8-4. ポイント (A) で測定されたアイ

図 8-5. ポイント (B) で測定されたアイ

図 8-6. ポイント (C) で測定されたアイ、Pre-Emph = 0dB

図 8-7. ポイント (D) で測定されたアイ、Pre-Emph = 0dB

図 8-8. ポイント (C) で測定されたアイ、Pre-Emph =

-9 dB

図 8-9. ポイント (D) で測定されたアイ、Pre-Emph =

-9 dB

## 9 電源に関する推奨事項

電源 ( $V_{CC}$ ) ピンとグランド (GND) ピンは、プリント基板の隣接する層で配線されている電源プレーンに接続する必要があります。 $V_{CC}$  および GND プレーンが分散容量を持つ低インダクタンス電源を形成するように、誘電体の層の厚さを最小限に抑える必要があります。バイパスコンデンサを適切に使用して、電源バイパスに細心の注意を払う必要があります。0.01 $\mu$ F または 0.1 $\mu$ F のバイパスコンデンサは、 $V_{CC}$  ピンのできるだけ近くに配置できるように、各  $V_{CC}$  ピンに接続する必要があります。0402 サイズなど、より本体サイズの小さなコンデンサを使用すると、部品を適切に配置しやすくなります。詳細については、図 1-1 の  $V_{CC}$  ピン接続を参照してください。

## 10 レイアウト

### 10.1 レイアウトのガイドライン

プリント基板は、電源層とグランド層を含む 4 層以上のものを採用してください。差動相互接続には通常、近接結合した 100 $\Omega$  の差動ラインを推奨します。近接結合したラインでは、カッピングノイズはレシーバ端でコモンモードとして現れるため除去されます。WQFN 型パッケージに関する情報は、テキサス・インスツルメンツの『AN-1187 リードレスリードフレームパッケージ (LLP)』(SNOA401) を参照してください。

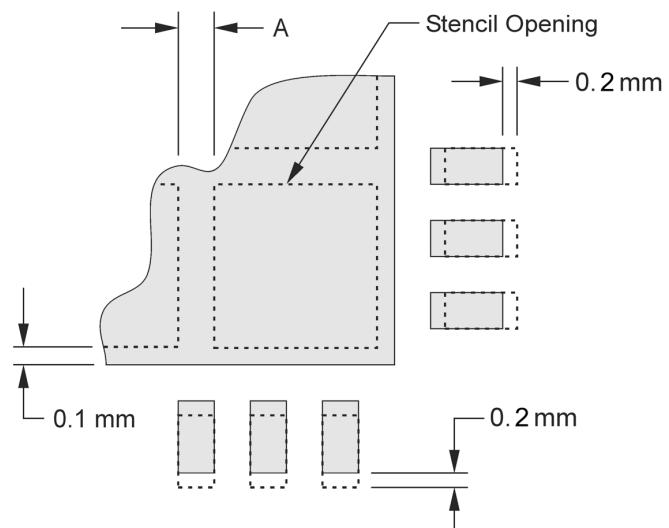

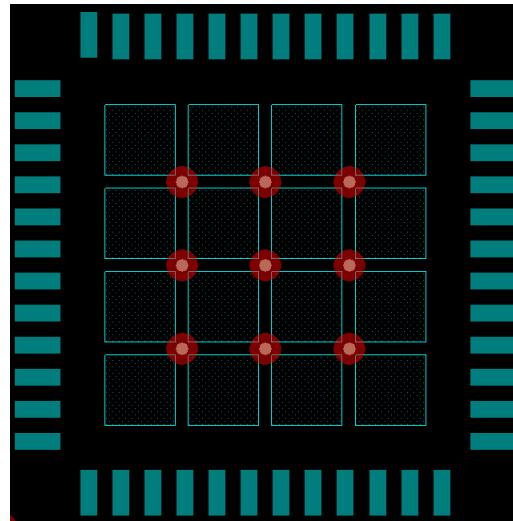

### 10.2 レイアウト例

アーチャの面積比や製造プロセスなどのステンシルパラメータは、ペーストの堆積に大きな影響を与えます。基板の組み立て歩留まりを向上させるため、WQFN パッケージを配置する前にステンシルを検査することを強くお勧めします。ビアとアーチャの開口部を注意深く監視しないと、半田が DAP を通って不均等に流れる可能性があります。図 1-1 に、アーチャ開口部とビア位置のステンシルパラメータを示します。DS40MB200 DAP のレイアウト例を図 1-1 に示します。ここでは、DAP に 16 個のステンシル開口部が使用され、また GND へのビアが 9 カ所あります。

図 10-1. プルバックの無い WQFN、1 列分の参考図

表 10-1. DS40MB200 のプルバックの無い WQFN ステンシルアーチャ概要

| デバイス      | ピン数 | MKT DWG | PCB の I/O パッド サイズ (mm) | PCB ピッチ (mm) | PCB DAP サイズ (mm) | ステンシル I/O アーチャ (mm) | ステンシル DAP アーチャ (mm) | DAP アーチャ開口部の数 | DAP アーチャ間のギャップ (寸法 A mm) |

|-----------|-----|---------|------------------------|--------------|------------------|---------------------|---------------------|---------------|--------------------------|

| DS40MB200 | 48  | SQA48A  | 0.25 × 0.6             | 0.5          | 5.1 × 5.1        | 0.25 × 0.7          | 1.1 × 1.1           | 16            | 0.2                      |

図 10-2. 48 ピン WQFN ステンシルのピアと開口部の配置例

## 11 デバイスおよびドキュメントのサポート

### 11.1 ドキュメントのサポート

#### 11.1.1 関連資料

関連資料については、以下を参照してください。

- 『AN-1187 リードレスリードフレームパッケージ(LLP)』(SNOA401)

### 11.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 11.3 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの [使用条件](#) を参照してください。

### 11.4 商標

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 11.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 11.6 用語集

[テキサス・インスツルメンツ用語集](#) この用語集には、用語や略語の一覧および定義が記載されています。

## 12 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision J (January 2016) to Revision K (March 2024) | Page |

|-------------------------------------------------------------------|------|

| ドキュメント全体にわたって表、図、相互参照の採番方法を更新.....                                | 1    |

| Changes from Revision I (March 2013) to Revision J (January 2016)                                                                                                                          | Page |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 「ピン構成と機能」セクション、「ストレージ条件」表、「ESD 定格」表、「熱に関する情報」表、「パラメータ測定情報」セクション、「機能説明」セクション、「アプリケーションと実装」セクション、「電源に関する推奨事項」セクション、「レイアウト」セクション、「デバイスおよびドキュメントのサポート」セクション、「メカニカル、パッケージ、および注文情報」セクションを追加..... | 1    |

| 最新のモデル結果に従って熱情報を変更.....                                                                                                                                                                    | 5    |

| 最近の測定により基板パターン減衰の推定値を変更.....                                                                                                                                                               | 15   |

## 13 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は指定したデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、左側のナビゲーションを参照してください。

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ（データシートを含みます）、設計リソース（リファレンス デザインを含みます）、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかる テキサス・インスツルメンツ製品の関連資料などのいづれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2024, Texas Instruments Incorporated

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins  | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| DS40MB200SQ/NOPB      | Active        | Production           | WQFN (NJU)   48 | 250   SMALL T&R       | Yes         | SN                                   | Level-3-260C-168 HR               | 0 to 85      | 40MB200             |

| DS40MB200SQ/NOPB.A    | Active        | Production           | WQFN (NJU)   48 | 250   SMALL T&R       | Yes         | SN                                   | Level-3-260C-168 HR               | 0 to 85      | 40MB200             |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

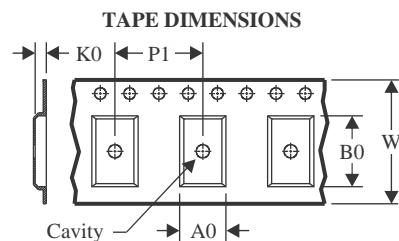

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

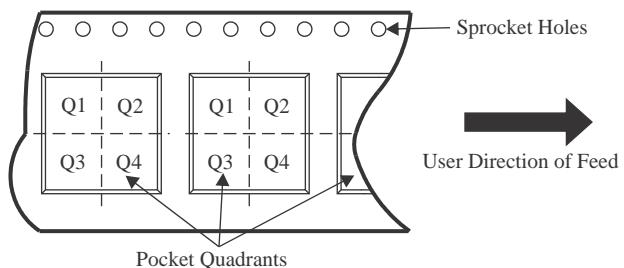

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

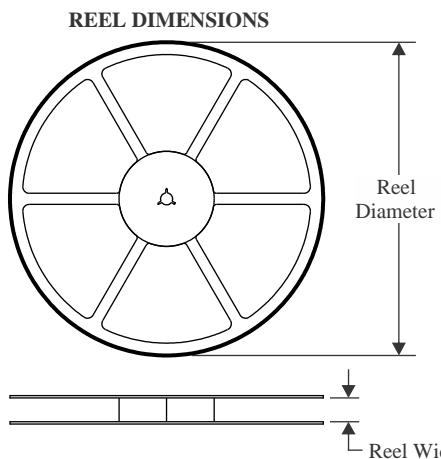

| Device           | Package Type | Package Drawing | Pins | SPQ | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|------------------|--------------|-----------------|------|-----|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| DS40MB200SQ/NOPB | WQFN         | NJU             | 48   | 250 | 178.0              | 16.4               | 7.3     | 7.3     | 1.3     | 12.0    | 16.0   | Q1            |

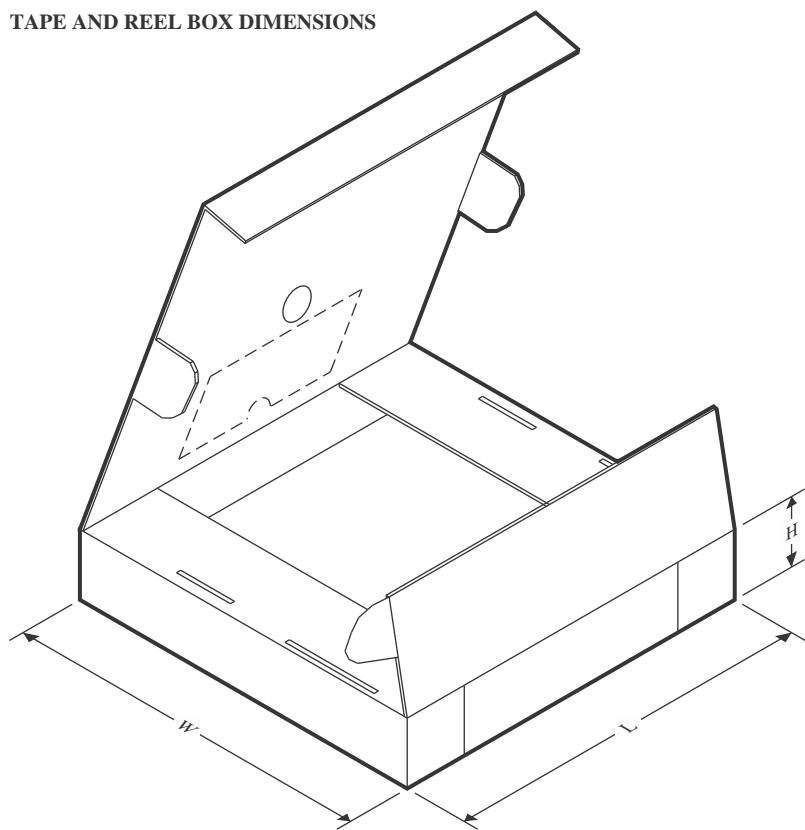

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device           | Package Type | Package Drawing | Pins | SPQ | Length (mm) | Width (mm) | Height (mm) |

|------------------|--------------|-----------------|------|-----|-------------|------------|-------------|

| DS40MB200SQ/NOPB | WQFN         | NJU             | 48   | 250 | 208.0       | 191.0      | 35.0        |

## MECHANICAL DATA

NJU0048D

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月