# DS90C383

***DS90C383/DS90CF384 +3.3V Programmable LVDS Transmitter 24-Bit Flat Panel

Display (FPD) Link-65 MHz, +3.3V LVDS Receiver 24-Bit Flat Panel Display

(FPD) Link-65 MHz***

Literature Number: JAJS920

ご注意：この日本語データシートは参考資料として提供しており、内容が最新でない場合があります。製品のご検討およびご採用に際しては、必ず最新の英文データシートをご確認ください。

2000年11月

# DS90C383/DS90CF384 + 3.3V LVDS レシーバ 24-Bit Flat Panel Display (FPD) Link-65MHz

## DS90C383/DS90CF384

- + 3.3V プログラマブル LVDS トランスミッタ 24-Bit Flat Panel Display (FPD) Link-65MHz

- + 3.3V LVDS レシーバ 24-Bit Flat Panel Display (FPD) Link-65MHz

### 概要

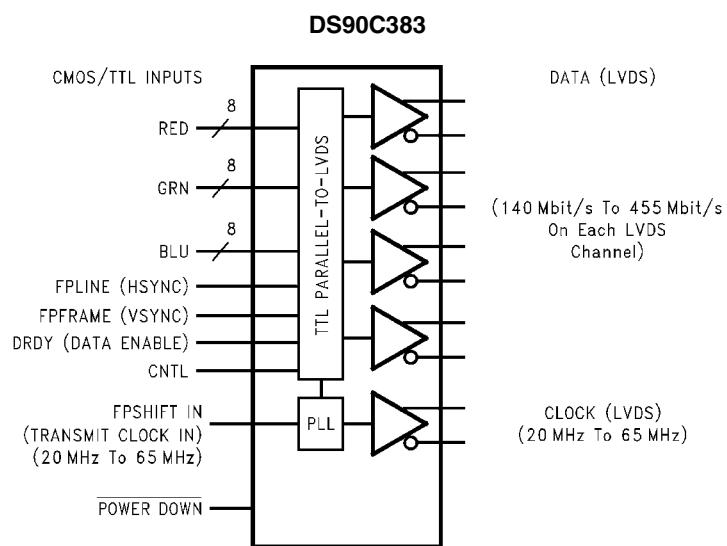

トランスミッタ DS90C383 は、28ビットの LVC MOS/LVTTL 入力パラレルデータを、4組の LVDS (Low Voltage Differential Signaling) シリアルデータに変換します。また、クロック信号も、トランスミッタ PLL 回路で位相調整され 1組の LVDS データに変換します。28ビットの入力データは、クロック信号のサイクル毎にサンプリングされ伝送されます。レシーバ DS90CF384 は、4組の LVDS シリアルデータを 28ビットの LVC MOS/LVTTL 出力パラレルデータに復元します。クロック周波数 65MHz 時、24ビットの RGB データと、4ビットの LCD タイミング及び制御信号 (FPLINE, FPFRAME, DRDY, CNTL) は、LVDS データ 1 チャネルあたり、455Mbps のスピードになり、トータル 227MB/s で伝送されます。トランスミッタは種々のグラフィック・コントローラと容易にインターフェースできるようプログラマブル・データ・ストローブ・エッジを採用しています。データ・サンプリング・エッジは、ピン入力により立ち上がりまたは立ち下がりエッジを選択できます。立ち上がりエッジ・サンプリングに設定しても、立ち下がりエッジのレシーバ (DS90CF384 等) と追加部品なしにインターフェース可能です。また、両デバイスは 64 ピン、0.8mm ピッチの FBGA (fine pitch ball grid array) パッケージでも供給され、これによりプリント基板上で占める面積を TSSOP パッケージに比べて 44% 減少させることができます。

このチップセットはバス幅が広く高速な TTL インタフェースで問題となっている EMI やケーブル・サイズを解決するには理想的なチップセットです。

### 特長

- クロック周波数 20 ~ 65MHz に対応

- プログラマブル・データ・ストローブ・エッジ (DS90C383)

- 3.3V 単一電源

- 250mW (Typ) チップセット (Tx + Rx) 消費電力

- 消費電力を低減するパワーダウン・モード (< 0.5mW)

- シングル・ピクセル XGA (1024 × 768) 対応

- VGA, SVGA, XGAもしくはXGA以上の高解像度をサポート

- 227MB/s の高速転送

- 1.8Gbps の高速伝送

- バス幅の低減によりケーブル、コネクタを小型化可能

- 低 EMI を実現する 290mV 信号振幅

- PLL は外付け部品不要

- 高密度実装を可能にする 56 ピン TSSOP パッケージ

- 64 ピン、0.8mm ピッチの FBGA パッケージでも供給

- 立ち下がりエッジ・データ・ストローブ・レシーバ

- TIA/EIA-644 LVDS 標準準拠

- ESD 耐圧 7kV 以上

### ブロック図

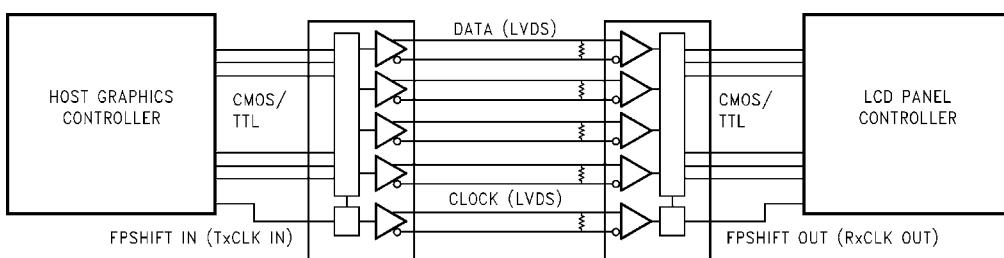

Typical Application

TRI-STATE® はナショナルセミコンダクター社の登録商標です。

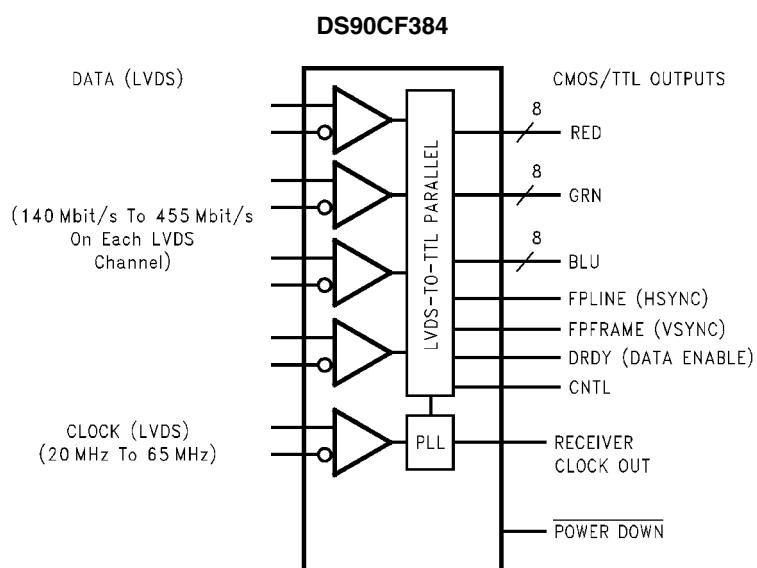

**ブロック図 (つづき)**

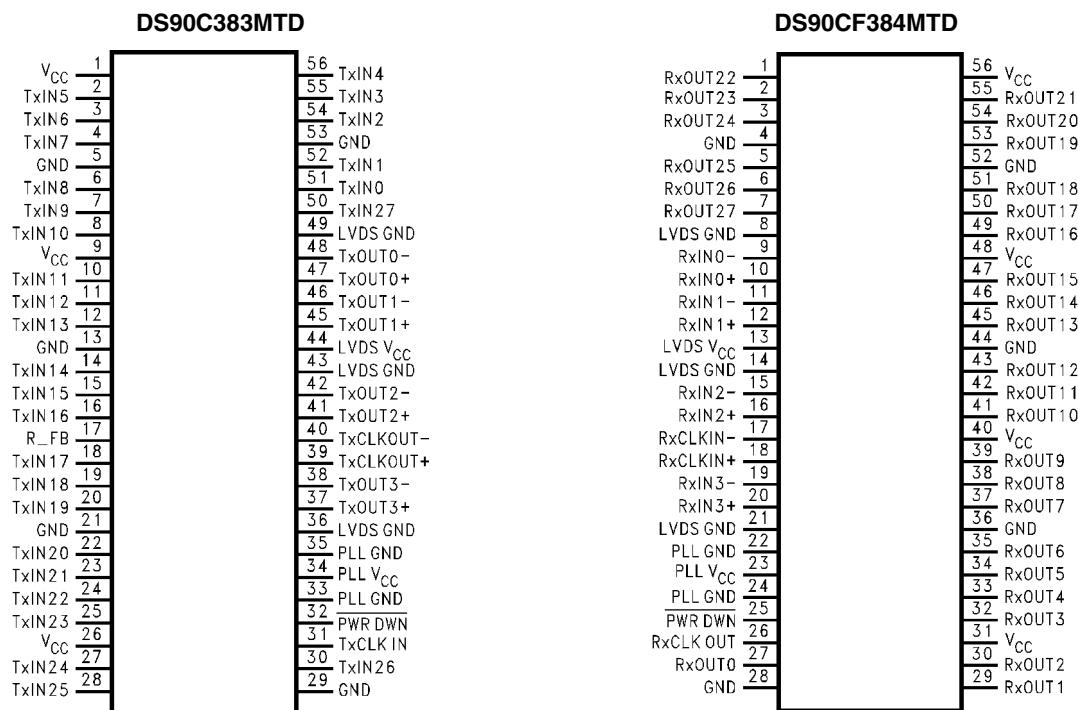

**Order Number DS90C383MTD or DS90C383SLC**

See NS Package Number MTD56 or SLC64A

**Order Number DS90CF384MTD or DS90CF384SLC**

See NS Package Number MTD56 or SLC64A

**絶対最大定格 (Note 1)**

本データシートには軍用・航空宇宙用の規格は記載されていません。

関連する電気的信頼性試験方法の規格を参照下さい。

|                           |                             |                              |                      |

|---------------------------|-----------------------------|------------------------------|----------------------|

| 電源電圧 ( $V_{CC}$ )         | - 0.3V ~ + 4V               | SLC64A パッケージ :               |                      |

| CMOS/TTL 入力電圧             | - 0.3V ~ ( $V_{CC}$ + 0.3V) | DS90C383SLC                  | 2.0W                 |

| CMOS/TTL 出力電圧             | - 0.3V ~ ( $V_{CC}$ + 0.3V) | DS90CF384SLC                 | 2.0W                 |

| LVDS レシーバ入力電圧             | - 0.3V ~ ( $V_{CC}$ + 0.3V) | *周囲温度 + 25 を超える場合は、          |                      |

| LVDS ドライバ出力電圧             | - 0.3V ~ ( $V_{CC}$ + 0.3V) | DS90C383MTD                  | 12.5mW/              |

| LVDS 出力短絡時間               | 連続                          | DS90CF384MTD                 | 12.4mW/              |

| PN 接合温度                   | + 150                       | DS90C383SLC                  | 10.2mW/              |

| 保存温度範囲                    | - 65 ~ + 150                | DS90CF384SLC                 | 10.2mW/              |

| 許容リード温度 (TSSOP ハンダ付け、4 秒) | + 260                       | を減じてください。                    |                      |

| ハンダ付け温度 (FBGA、20 秒)       | + 220                       | ESD 耐圧<br>(HBM、1.5k 、 100pF) | > 7kV                |

| 最大パッケージ許容損失 (+ 25 のとき)    |                             |                              |                      |

| MTD56 (TSSOP) パッケージ :     |                             |                              |                      |

| DS90C383MTD               | 1.63 W                      | 電源電圧 ( $V_{CC}$ )            | 3.0 3.3 3.6 V        |

| DS90CF384MTD              | 1.61 W                      | 動作周囲温度 ( $T_A$ )             | - 40 + 25 + 85       |

|                           |                             | レシーバ入力電圧範囲                   | 0 2.4 V              |

|                           |                             | 電源ノイズ電圧 ( $V_{CC}$ )         | 100 mV <sub>PP</sub> |

**電気的特性**

特記のない限り、推奨動作電源電圧および動作温度範囲に対して適用。

| Symbol                                | Parameter                                              | Conditions                                                      | Min                    | Typ       | Max       | Units         |

|---------------------------------------|--------------------------------------------------------|-----------------------------------------------------------------|------------------------|-----------|-----------|---------------|

| <b>LVCMOS/LVTTL DC SPECIFICATIONS</b> |                                                        |                                                                 |                        |           |           |               |

| $V_{IH}$                              | High Level Input Voltage                               |                                                                 | 2.0                    |           | $V_{CC}$  | V             |

| $V_{IL}$                              | Low Level Input Voltage                                |                                                                 | GND                    |           | 0.8       | V             |

| $V_{OH}$                              | High Level Output Voltage                              | $I_{OH} = - 0.4 \text{ mA}$                                     | 2.7                    | 3.3       |           | V             |

| $V_{OL}$                              | Low Level Output Voltage                               | $I_{OL} = 2 \text{ mA}$                                         |                        | 0.06      | 0.3       | V             |

| $V_{CL}$                              | Input Clamp Voltage                                    | $I_{CL} = - 18 \text{ mA}$                                      |                        | - 0.79    | - 1.5     | V             |

| $I_{IN}$                              | Input Current                                          | $V_{IN} = V_{CC}, \text{GND, } 2.5\text{V or } 0.4\text{V}$     |                        | $\pm 5.1$ | $\pm 10$  | $\mu\text{A}$ |

| $I_{OS}$                              | Output Short Circuit Current                           | $V_{OUT} = 0\text{V}$                                           |                        | - 60      | - 120     | mA            |

| <b>LVDS DC SPECIFICATIONS</b>         |                                                        |                                                                 |                        |           |           |               |

| $V_{OD}$                              | Differential Output Voltage                            | $R_L = 100$                                                     | 250                    | 345       | 450       | mV            |

| $V_{OD}$                              | Change in $V_{OD}$ between complimentary output states |                                                                 |                        |           | 35        | mV            |

| $V_{OS}$                              | Offset Voltage (Note 4)                                |                                                                 | 1.125                  | 1.25      | 1.375     | V             |

| $V_{OS}$                              | Change in $V_{OS}$ between complimentary output states |                                                                 |                        |           | 35        | mV            |

| $I_{OS}$                              | Output Short Circuit Current                           | $V_{OUT} = 0\text{V}, R_L = 100$                                |                        | - 3.5     | - 5       | mA            |

| $I_{OZ}$                              | Output TRI-STATE® Current                              | $\text{Power Down} = 0\text{V}, V_{OUT} = 0\text{V or } V_{CC}$ |                        | $\pm 1$   | $\pm 10$  | $\mu\text{A}$ |

| $V_{TH}$                              | Differential Input High Threshold                      | $V_{CM} = + 1.2\text{V}$                                        |                        |           | $\pm 100$ | mV            |

| $V_{TL}$                              | Differential Input Low Threshold                       |                                                                 | - 100                  |           |           | mV            |

| $I_{IN}$                              | Input Current                                          | $V_{IN} = + 2.4\text{V}, V_{CC} = 3.6\text{V}$                  |                        |           | $\pm 10$  | $\mu\text{A}$ |

|                                       |                                                        | $V_{IN} = 0\text{V}, V_{CC} = 3.6\text{V}$                      |                        |           | $\pm 10$  | $\mu\text{A}$ |

| <b>TRANSMITTER SUPPLY CURRENT</b>     |                                                        |                                                                 |                        |           |           |               |

| ICCTW                                 | Transmitter Supply Current                             | $R_L = 100$ ,<br>$C_L = 5 \text{ pF}$ ,                         | $f = 32.5 \text{ MHz}$ |           | 31        | 45 mA         |

|                                       |                                                        | Worst Case Pattern                                              | $f = 37.5 \text{ MHz}$ |           | 32        | 50 mA         |

## 電気的特性 (つづき)

特記のない限り、推奨動作電源電圧および動作温度範囲に対して適用。

| Symbol                            | Parameter                                  | Conditions                                                                | Min            | Typ | Max | Units      |

|-----------------------------------|--------------------------------------------|---------------------------------------------------------------------------|----------------|-----|-----|------------|

| <b>TRANSMITTER SUPPLY CURRENT</b> |                                            |                                                                           |                |     |     |            |

|                                   |                                            | (Figure 1, 3), $T_A = -40$ to $+85$                                       | $f = 65$ MHz   |     | 42  | 55 mA      |

| ICCTG                             | Transmitter Supply Current<br>16 Grayscale | $R_L = 100$ ,<br>$C_L = 5$ pF,                                            | $f = 32.5$ MHz |     | 23  | 35 mA      |

|                                   |                                            | 16 Grayscale Pattern                                                      | $f = 37.5$ MHz |     | 28  | 40 mA      |

|                                   |                                            | (Figure 2, 3), $T_A = -40$ to $+85$                                       | $f = 65$ MHz   |     | 31  | 45 mA      |

| ICCTZ                             | Transmitter Supply Current<br>Power Down   | Power Down = Low<br>Driver Outputs in TRI-STATE® under<br>Power Down Mode |                |     | 10  | 55 $\mu$ A |

| <b>RECEIVER SUPPLY CURRENT</b>    |                                            |                                                                           |                |     |     |            |

| ICCRW                             | Receiver Supply Current<br>Worst Case      | $C_L = 8$ pF,<br>Worst Case Pattern                                       | $f = 32.5$ MHz |     | 49  | 65 mA      |

|                                   |                                            | (Figure 1, 4), $T_A = -40$ to $+85$                                       | $f = 37.5$ MHz |     | 53  | 70 mA      |

|                                   |                                            |                                                                           | $f = 65$ MHz   |     | 78  | 105 mA     |

| ICCRG                             | Receiver Supply Current,<br>16 Grayscale   | $C_L = 8$ pF,<br>16 Grayscale Pattern                                     | $f = 32.5$ MHz |     | 28  | 45 mA      |

|                                   |                                            | (Figure 2, 4), $T_A = -40$ to $+85$                                       | $f = 37.5$ MHz |     | 30  | 47 mA      |

|                                   |                                            |                                                                           | $f = 65$ MHz   |     | 43  | 60 mA      |

| ICCRZ                             | Receiver Supply Current<br>Power Down      | Power Down = Low<br>Receiver Outputs Stay Low during<br>Power Down Mode   |                |     | 10  | 55 $\mu$ A |

**Note 1:** 「絶対最大定格」とは、この範囲を超えるとデバイスの安全性が保証されないリミット値をいい、これらのリミット値でデバイスが動作することを意味するものではありません。電気的特性の表にデバイスの実動作条件を記載しています。

**Note 2:** 代表値 (Typ) は全て  $V_{CC} = 3.3$ V、および  $T_A = +25$  で得られる最も標準的な数値です。

**Note 3:** デバイス端子に流れ込む電流は正、デバイス端子から流れ出る電流は負と定義されます。 $V_{OD}$  と  $V_{OD}$  以外、全ての電圧値はグラウンド端子を基準とします。

**Note 4:**  $V_{OS}$  は以前は  $V_{CM}$  と表記されていました。

## トランスマッタ・スイッチング特性

特記のない限り、推奨動作電源電圧および動作温度範囲に対して適用。

| Symbol | Parameter                                                      | Min          | Typ   | Max  | Units    |

|--------|----------------------------------------------------------------|--------------|-------|------|----------|

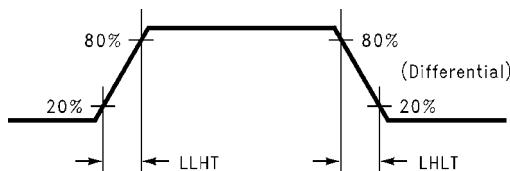

| LLHT   | LVDS Low-to-High Transition Time (Figure 3)                    |              | 0.75  | 1.5  | ns       |

| LHLT   | LVDS High-to-Low Transition Time (Figure 3)                    |              | 0.75  | 1.5  | ns       |

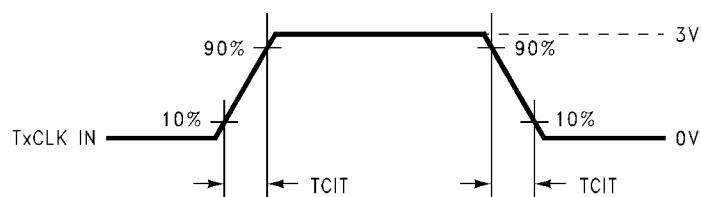

| TCIT   | TxCLK IN Transition Time (Figure 5)                            |              |       | 5    | ns       |

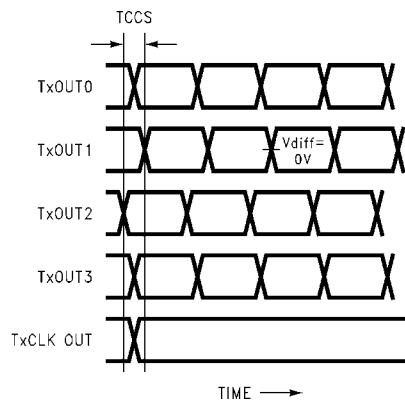

| TCCS   | TxOUT Channel-to-Channel Skew (Figure 6)                       |              | 250   |      | ps       |

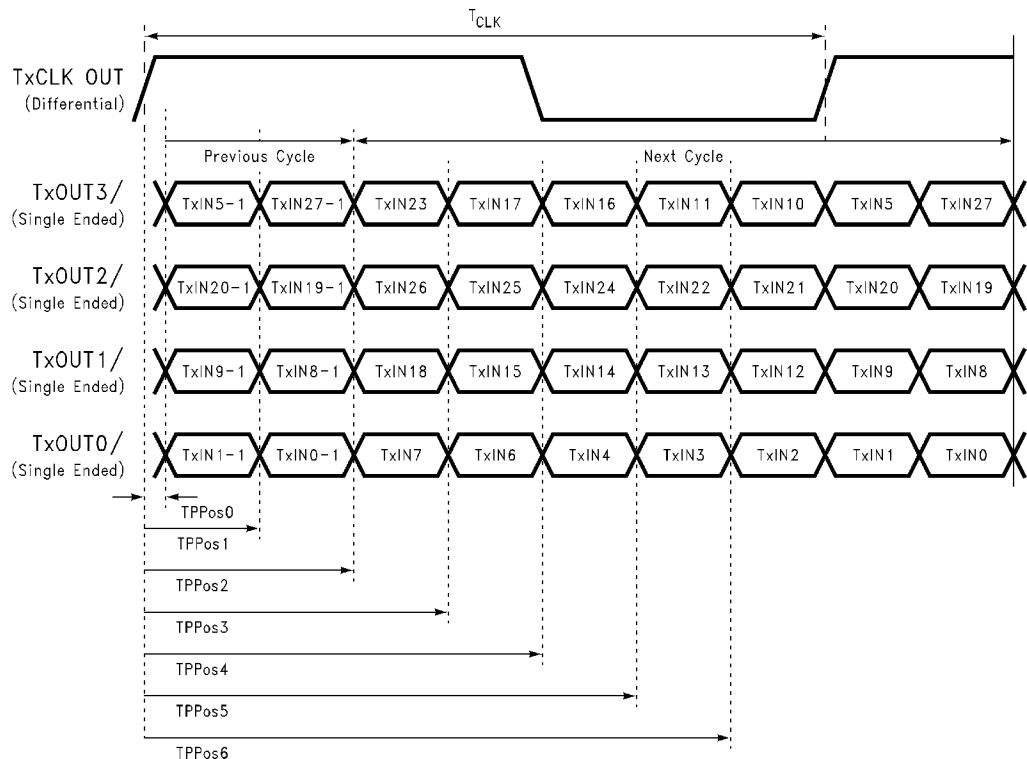

| TPPos0 | Transmitter Output Pulse Position for Bit 0 (Figure 17)        | $f = 65$ MHz | - 0.4 | 0    | 0.3 ns   |

| TPPos1 | Transmitter Output Pulse Position for Bit 1                    |              | 1.8   | 2.2  | 2.5 ns   |

| TPPos2 | Transmitter Output Pulse Position for Bit 2                    |              | 4.0   | 4.4  | 4.7 ns   |

| TPPos3 | Transmitter Output Pulse Position for Bit 3                    |              | 6.2   | 6.6  | 6.9 ns   |

| TPPos4 | Transmitter Output Pulse Position for Bit 4                    |              | 8.4   | 8.8  | 9.1 ns   |

| TPPos5 | Transmitter Output Pulse Position for Bit 5                    |              | 10.6  | 11   | 11.3 ns  |

| TPPos6 | Transmitter Output Pulse Position for Bit 6                    |              | 12.8  | 13.2 | 13.5 ns  |

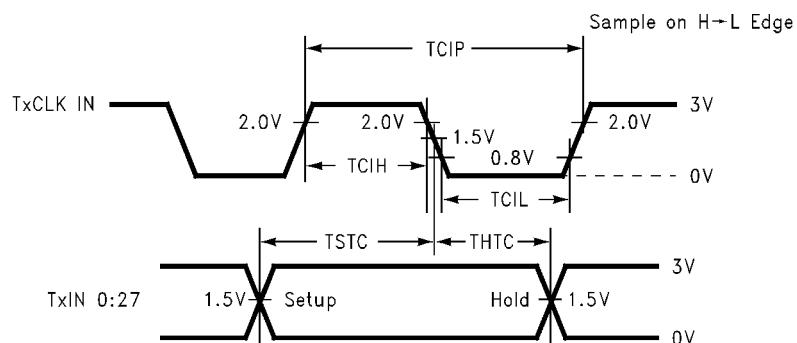

| TCIP   | TxCLK IN Period (Figure 7)                                     |              | 15    | T    | 50 ns    |

| TCIH   | TxCLK IN High Time (Figure 7)                                  |              | 0.35T | 0.5T | 0.65T ns |

| TCIL   | TxCLK IN Low Time (Figure 7)                                   |              | 0.35T | 0.5T | 0.65T ns |

| TSTC   | TxIN Setup to TxCLK IN (Figure 7)                              | $f = 65$ MHz | 2.5   |      | ns       |

| THTC   | TxIN Hold to TxCLK IN (Figure 7)                               |              | 0     |      | ns       |

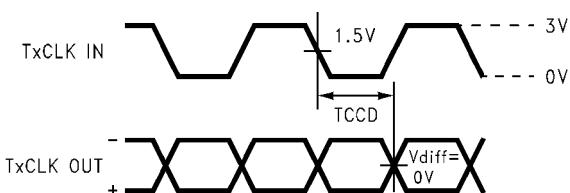

| TCCD   | TxCLK IN to TxCLK OUT Delay @ 25 , $V_{CC} = 3.3$ V (Figure 9) |              | 3.0   | 3.7  | 5.5 ns   |

## トランミッタ・スイッチング特性(つづき)

特記のない限り、推奨動作電源電圧および動作温度範囲に対して適用

| Symbol | Parameter                                   | Min | Typ | Max | Units |

|--------|---------------------------------------------|-----|-----|-----|-------|

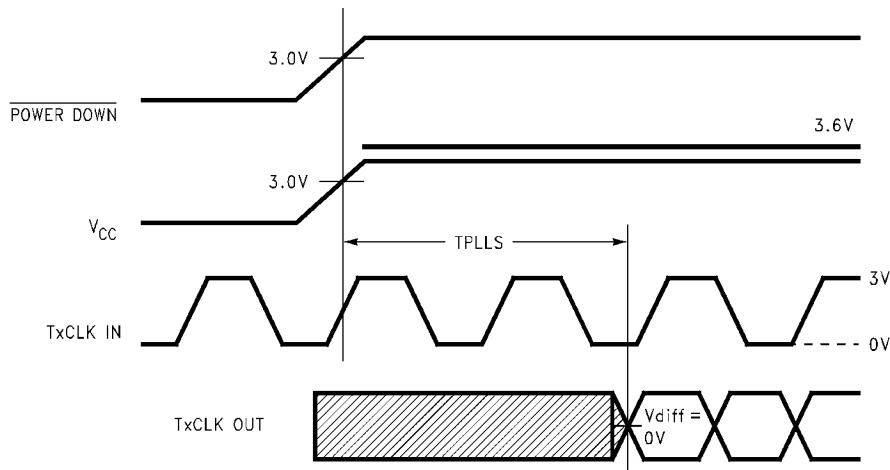

| TPLLS  | Transmitter Phase Lock Loop Set (Figure 11) |     |     | 10  | ms    |

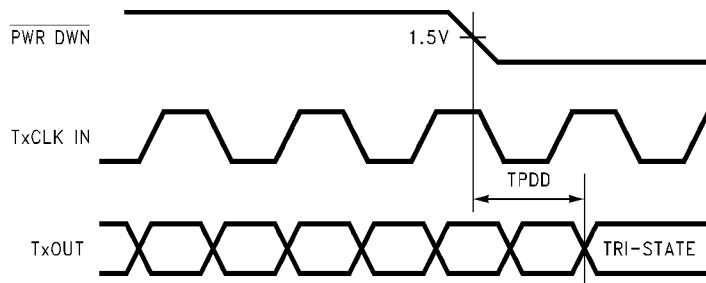

| TPDD   | Transmitter Power Down Delay (Figure 15)    |     |     | 100 | ns    |

## レシーバ・スイッチング特性

特記のない限り、推奨動作電源電圧および動作温度範囲に対して適用。

| Symbol | Parameter                                                      | Min                  | Typ  | Max  | Units |               |

|--------|----------------------------------------------------------------|----------------------|------|------|-------|---------------|

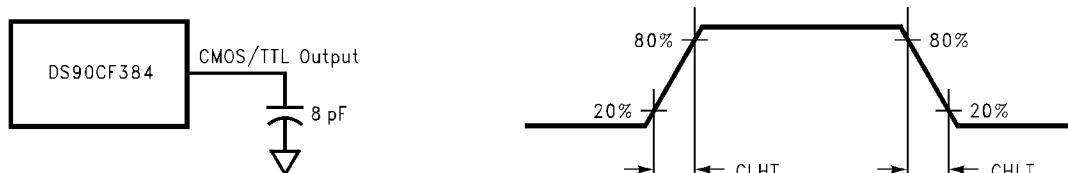

| CLHT   | CMOS/TTL Low-to-High Transition Time (Figure 4)                |                      | 2.2  | 5.0  | ns    |               |

| CHLT   | CMOS/TTL High-to-Low Transition Time (Figure 4)                |                      | 2.2  | 5.0  | ns    |               |

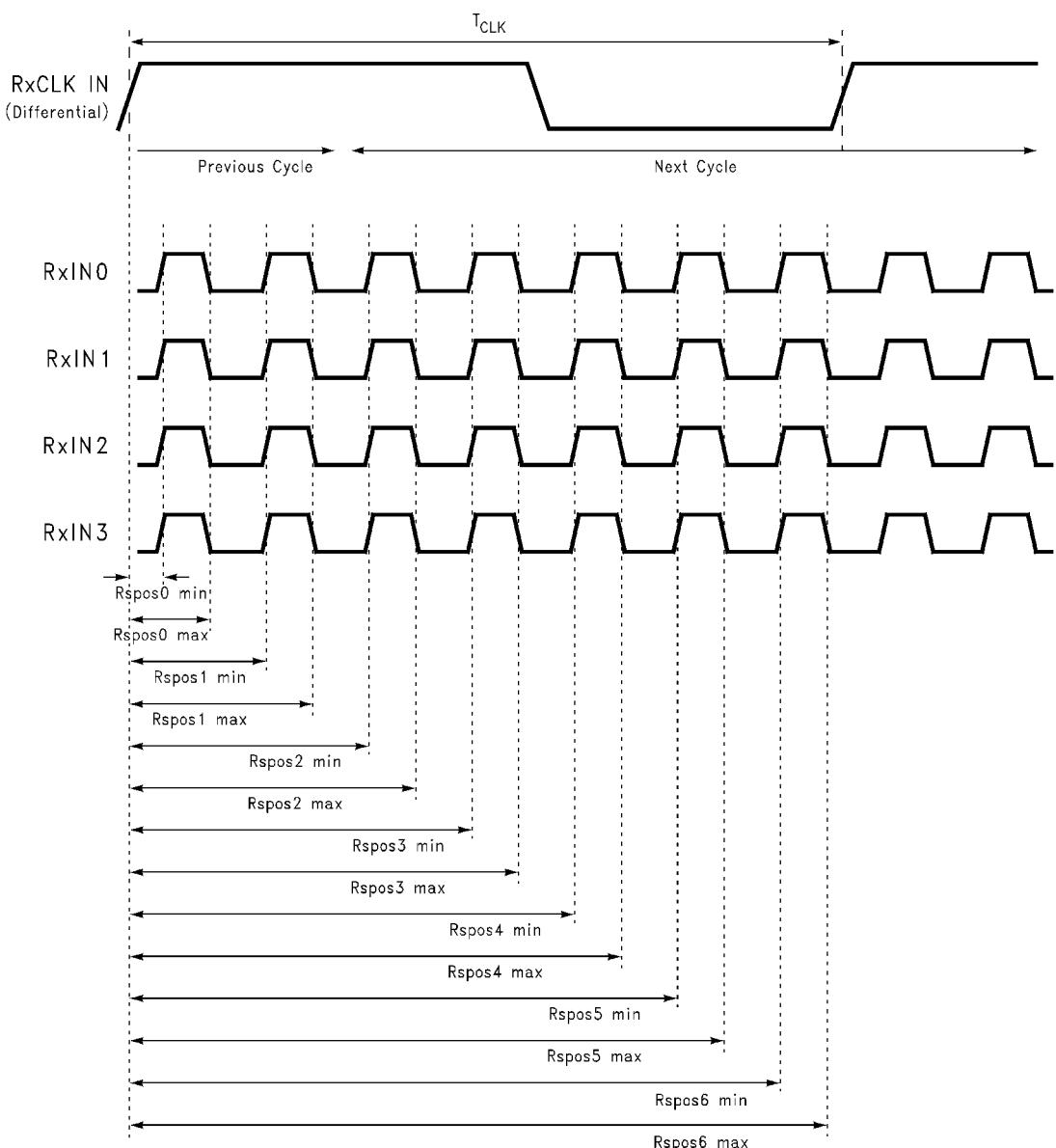

| RSPos0 | Receiver Input Strobe Position for Bit 0 (Figure 18)           | $f = 65 \text{ MHz}$ | 0.7  | 1.1  | 1.4   | ns            |

| RSPos1 | Receiver Input Strobe Position for Bit 1                       |                      | 2.9  | 3.3  | 3.6   | ns            |

| RSPos2 | Receiver Input Strobe Position for Bit 2                       |                      | 5.1  | 5.5  | 5.8   | ns            |

| RSPos3 | Receiver Input Strobe Position for Bit 3                       |                      | 7.3  | 7.7  | 8.0   | ns            |

| RSPos4 | Receiver Input Strobe Position for Bit 4                       |                      | 9.5  | 9.9  | 10.2  | ns            |

| RSPos5 | Receiver Input Strobe Position for Bit 5                       |                      | 11.7 | 12.1 | 12.4  | ns            |

| RSPos6 | Receiver Input Strobe Position for Bit 6                       |                      | 13.9 | 14.3 | 14.6  | ns            |

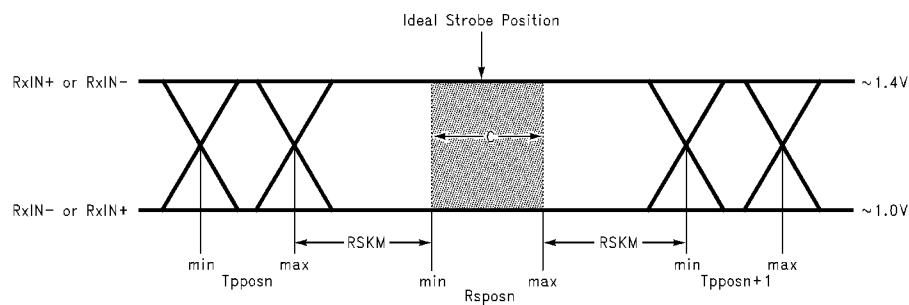

| RSKM   | RxIN Skew Margin (Note 5)(Figure 19)                           | $f = 65 \text{ MHz}$ | 400  |      |       | ps            |

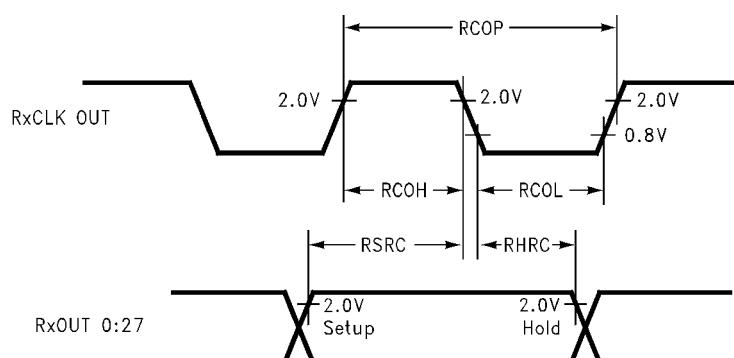

| RCOP   | RxCLK OUT Period (Figure 8)                                    |                      | 15   | T    | 50    | ns            |

| RCOH   | RxCLK OUT High Time (Figure 8)                                 |                      | 7.3  | 8.6  |       | ns            |

| RCOL   | RxCLK OUT Low Time (Figure 8)                                  |                      | 3.45 | 4.9  |       | ns            |

| RSRC   | RxOUT Setup to RxCLK OUT (Figure 8)                            |                      | 2.5  | 6.9  |       | ns            |

| RHRC   | RxOUT Hold to RxCLK OUT (Figure 8)                             |                      | 2.5  | 5.7  |       | ns            |

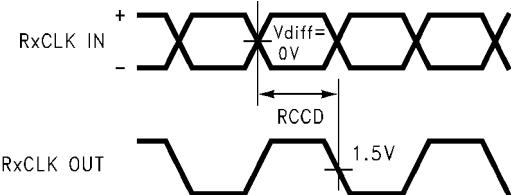

| RCCD   | RxCLK IN to RxCLK OUT Delay @ 25 , $V_{CC} = 3.3V$ (Figure 10) |                      | 5.0  | 7.1  | 9.0   | ns            |

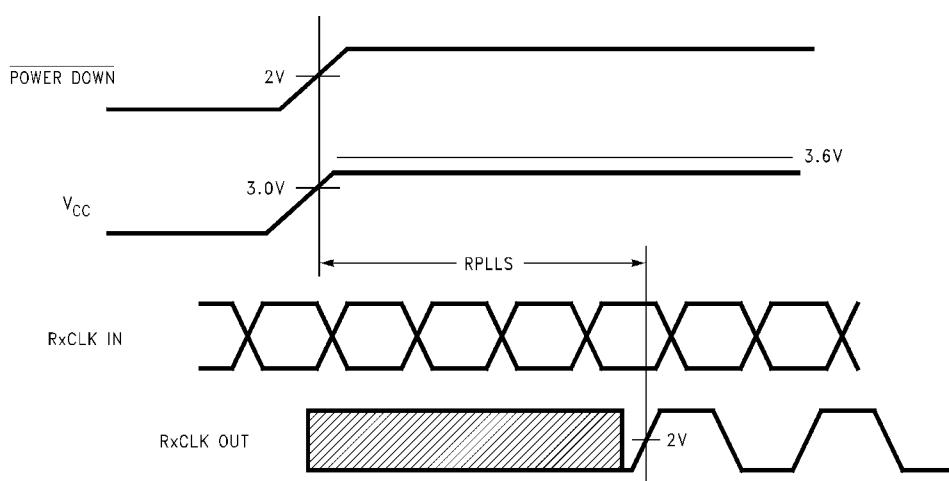

| RPLLS  | Receiver Phase Lock Loop Set (Figure 12)                       |                      |      |      | 10    | ms            |

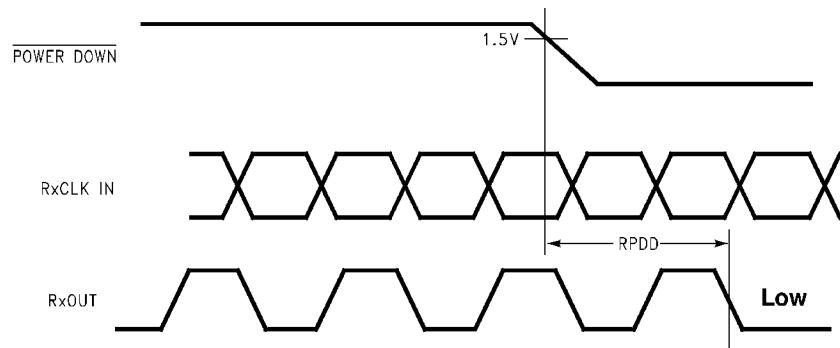

| RPDD   | Receiver Power Down Delay (Figure 16)                          |                      |      |      | 1     | $\mu\text{s}$ |

Note 5: レシーバ・スキュー・マージンはレシーバ入力でのサンプリングに必要な有効データ範囲と定義されます。このマージンはトランミッタ・パルス・ポジション (TPPos min と max) とレシーバの入力セットアップ / ホールドタイム ( 内部データ・サンプリング長 - RSPos ) により導き出されています。このマージンは LVDS 配線スキュー、ケーブル・スキュー ( タイプと長さにより異なります。 ) とクロック・ジャッタ (250ps 以下 ) により減少します。

## AC タイミング図

FIGURE 1. “Worst Case” Test Pattern

## AC タイミング図 (つづき)

| Device Pin Name    | Signal  | Signal Pattern   | Signal Frequency   |

|--------------------|---------|------------------|--------------------|

| TxCLK IN/RxCLK OUT | Dot CLK | [Signal Pattern] | f                  |

| TxIN0/RxOUT0       | R0      | [Signal Pattern] | f/16               |

| TxIN1/RxOUT1       | R1      | [Signal Pattern] | f/8                |

| TxIN2/RxOUT2       | R2      | [Signal Pattern] | f/4                |

| TxIN3/RxOUT3       | R3      | [Signal Pattern] | f/2                |

| TxIN4/RxOUT4       | R4      | [Signal Pattern] | Steady State, Low  |

| TxIN5/RxOUT5       | R7      | [Signal Pattern] | Steady State, Low  |

| TxIN6/RxOUT6       | R5      | [Signal Pattern] | Steady State, Low  |

| TxIN7/RxOUT7       | G0      | [Signal Pattern] | Steady State, Low  |

| TxIN8/RxOUT8       | G1      | [Signal Pattern] | f/16               |

| TxIN9/RxOUT9       | G2      | [Signal Pattern] | f/8                |

| TxIN10/RxOUT10     | G6      | [Signal Pattern] | f/4                |

| TxIN11/RxOUT11     | G7      | [Signal Pattern] | f/2                |

| TxIN12/RxOUT12     | G3      | [Signal Pattern] | Steady State, Low  |

| TxIN13/RxOUT13     | G4      | [Signal Pattern] | Steady State, Low  |

| TxIN14/RxOUT14     | G5      | [Signal Pattern] | Steady State, Low  |

| TxIN15/RxOUT15     | B0      | [Signal Pattern] | Steady State, Low  |

| TxIN16/RxOUT16     | B6      | [Signal Pattern] | f/16               |

| TxIN17/RxOUT17     | B7      | [Signal Pattern] | f/8                |

| TxIN18/RxOUT18     | B1      | [Signal Pattern] | f/4                |

| TxIN19/RxOUT19     | B2      | [Signal Pattern] | f/2                |

| TxIN20/RxOUT20     | B3      | [Signal Pattern] | Steady State, Low  |

| TxIN21/RxOUT21     | B4      | [Signal Pattern] | Steady State, Low  |

| TxIN22/RxOUT22     | B5      | [Signal Pattern] | Steady State, Low  |

| TxIN23/RxOUT23     | RES     | [Signal Pattern] | Steady State, Low  |

| TxIN24/RxOUT24     | HSYNC   | [Signal Pattern] | Steady State, High |

| TxIN25/RxOUT25     | VSYNC   | [Signal Pattern] | Steady State, High |

| TxIN26/RxOUT26     | EN      | [Signal Pattern] | Steady State, High |

| TxIN27/RxOUT27     | R6      | [Signal Pattern] | Steady State, High |

FIGURE 2. "16 Grayscale" Test Pattern (Note 6, 7, 8, 9)

Note 6: ワースト・ケース・パターンはデバイスのデジタル回路、LVDS I/O と TTL I/O が最もトグルするように考えられています。

Note 7: 16 階調テスト・パターンは LCD ディスプレイの代表的パターンにおけるデバイスの消費電力を算定するためのものです。このパターンは 16 の縦ストライプのグループがディスプレイに並ぶように信号を近似しています。

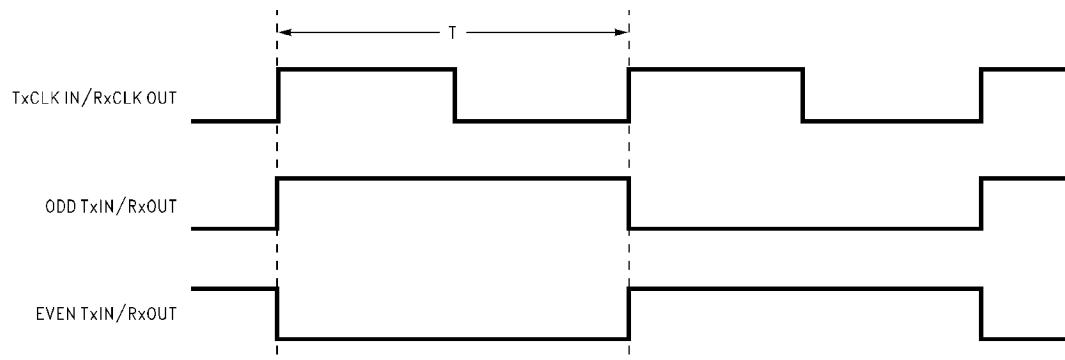

Note 8: Figure 1、Figure 2 ともに立ち下がりエッジ・ストローブの場合です (TxCLK IN/RxCLK OUT)。

Note 9: 推奨ヒアサインですが、独自のアサインにする事も可能です。

FIGURE 3. DS90C383 (Transmitter) LVDS Output Load and Transition Times

FIGURE 4. DS90CF384 (Receiver) CMOS/TTL Output Load and Transition Times

## AC タイミング図(つづき)

FIGURE 5. DS90C383 (Transmitter) Input Clock Transition Time

$V_{diff} = 0V$  で測定。

TCCS は最初の LVDS エッジの最も早いエッジと最も遅いエッジで測定されます。

TxCLK ディファレンシャル出力のうち Low から High のエッジを測定。

FIGURE 6. DS90C383 (Transmitter) Channel-to-Channel Skew

FIGURE 7. DS90C383 (Transmitter) Setup/Hold and High/Low Times (Falling Edge Strobe)

FIGURE 8. DS90CF384 (Receiver) Setup/Hold and High/Low Times

## AC タイミング図 (つづき)

FIGURE 9. DS90C383 (Transmitter) Clock In to Clock Out Delay (Falling Edge Strobe)

FIGURE 10. DS90CF384 (Receiver) Clock In to Clock Out Delay

FIGURE 11. DS90C383 (Transmitter) Phase Lock Loop Set Time

FIGURE 12. DS90CF384 (Receiver) Phase Lock Loop Set Time

## AC タイミング図 (つづき)

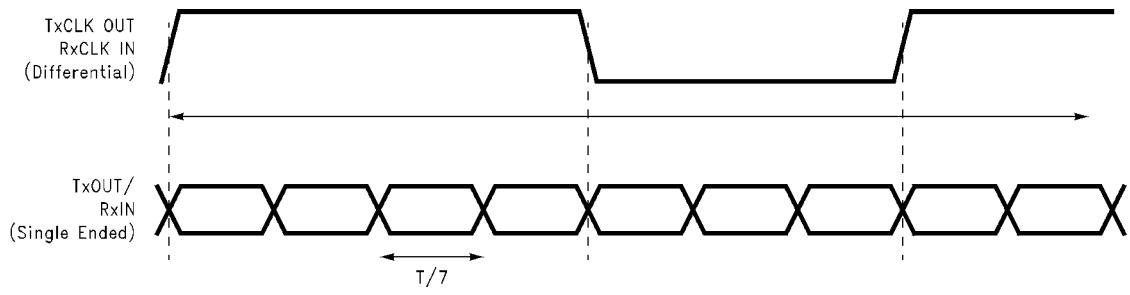

FIGURE 13. Seven Bits of LVDS in Once Clock Cycle

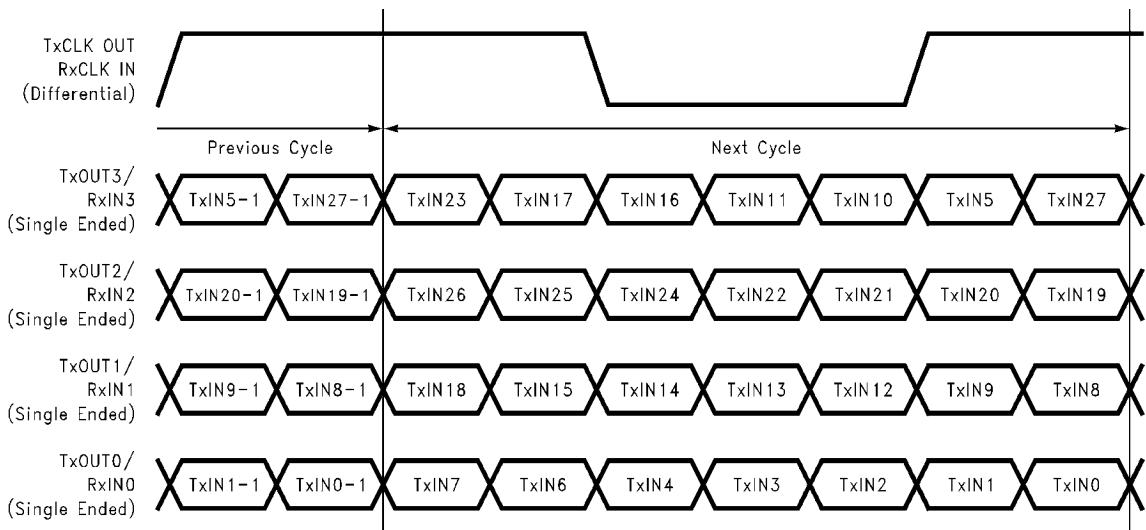

FIGURE 14. 21 Parallel TTL Data Inputs Mapped to LVDS Outputs

FIGURE 15. Transmitter Power Down Delay

## AC タイミング図 (つづき)

FIGURE 16. Receiver Power Down Delay

FIGURE 17. Transmitter LVDS Output Pulse Position Measurement

## AC タイミング図(つづき)

FIGURE 18. Receiver LVDS Input Strobe Position

## AC タイミング図 (つづき)

C セットアップ / ホールド・タイム ( 内部データ・サンプリング長 ) は  $R_{pos}$  ( レシーバ入力ストローブ・ポジション ) min と max により定義されます。

$T_{ppos}$  トランスマッタ出力パルス・ポジション (min と max)

RSKM ケーブル・スキー + ソース・クロック・ジッタ ( 連続する 2 クロック間 ) ( Note 10 ) + ISI ( 伝送波形干渉 ) ( Note 11 )

ケーブル・スキー 通常 10 ~ 40ps/300mm、ケーブルにより異なります。

Note 10: 65MHz 動作時のジッタは 250ps 以下にしてください。

Note 11: ISI は内部配線

FIGURE 19. Receiver LVDS Input Skew Margin

### アプリケーション情報

DS90C383 と DS90CF384 は既存の 5VFPD-Link のトランスマッタ / レシーバ・ペア (DS90CR583, DS90CR584, DS90CF583 および DS90CF584) と互換性があります。5V から 3.3V システムへ移行される際には、次の事に注意してください。

1. 電源を 5V から 3.3V へ変更し、トランスマッタとレシーバの全電源ピン ( $V_{CC}$ , LVDS  $V_{CC}$ , PLL  $V_{CC}$ ) に供給してください。システムから 5V 電源をなくし、既存の 3V 電源から電源を供給することができます。

2. DS90C383 にはストローブ・エッジを選択するピンがあります。この選択ピンは 17 番ピンで、5V の製品では  $V_{CC}$  が割当られています。このピンを  $V_{CC}$  へプルアップした場合は、立ち上がりストローブに設定されます。現システムで立ち上がりエッジの DS90CR583 が使用されている場合は、3.3V のトランスマッタの選択ピンによるレイアウト変更は必要ありません。 $V_{CC}$  は 17 番ピンに接続されており、デバイスは 5V と同様に立ち上がりエッジ・ストローブに設定されます。

**5V 立ち下がりエッジトランスマッタ(DS90CF583)の場合は若干の変更が必要となります。** 17 番ピンに継続して  $V_{CC}$  が接続されている場合は立ち下がりエッジ・ストローブに設定されません。正しく動作させるにはグラウンドへ接続またはオープンにしてください。未接続 ( オープン ) の場合は、内部でプルダウンされているため立ち下がり動作に設定されます。

3. DS90C383 の入力ピンと制御入力ピンには 3.3VTTL/CMOS 信号を入力してください。5V 信号入力耐圧はありません。

## DS90C383 TSSOP パッケージ端子説明 FPD リンク・トランスマッタ

| 端子名                  | I/O | No. | 説明                                                                                                                      |

|----------------------|-----|-----|-------------------------------------------------------------------------------------------------------------------------|

| TxIN                 | I   | 28  | TTL レベル入力。これには、8 ビットの Red、8 ビットの Green、8 ビットの Blue、および 4 ビットの制御信号 FPLINE、FPFRAME、DRDY (HSYNC、VSYNC、Data Enable) が含まれます。 |

| TxOUT +              | O   | 4   | 正の LVDS 差動データ出力                                                                                                         |

| TxOUT -              | O   | 4   | 負の LVDS 差動データ出力                                                                                                         |

| FPSHIFT IN           | I   | 1   | TTL レベルのクロック入力。立ち下がりエッジがデータ取り込みに使用されます。端子名は TxCLK IN です。                                                                |

| R_FB                 | I   | 1   | プログラム可能なエッジ・ストローブ選択                                                                                                     |

| RTxCLK OUT +         | O   | 1   | 正の LVDS 差動クロック出力                                                                                                        |

| TxCLK OUT -          | O   | 1   | 負の LVDS 差動クロック出力                                                                                                        |

| PWR DOWN             | I   | 1   | TTL レベル入力。入力が Low にアサートされると、出力は TRI-STATE になり、パワー・ダウン時に低電流となります。                                                        |

| V <sub>CC</sub>      | I   | 3   | TTL 入力用の電源ピン                                                                                                            |

| GND                  | I   | 4   | TTL 入力用のグラウンド・ピン                                                                                                        |

| PLL V <sub>CC</sub>  | I   | 1   | PLL 用の電源ピン                                                                                                              |

| PLL GND              | I   | 2   | PLL 用のグラウンド・ピン                                                                                                          |

| LVDS V <sub>CC</sub> | I   | 1   | LVDS 出力用の電源ピン                                                                                                           |

| LVDS GND             | I   | 3   | LVDS 出力用のグラウンド・ピン                                                                                                       |

## DS90C383SLC SLC64A (FBGA) パッケージ端子要約 FPD リンク・トランスマッタ

| 端子名                  | I/O | No. | 説明                                                               |

|----------------------|-----|-----|------------------------------------------------------------------|

| TxIN                 | I   | 28  | TTL レベル入力                                                        |

| TxOUT +              | O   | 4   | 正の LVDS 差動データ出力                                                  |

| TxOUT -              | O   | 4   | 負の LVDS 差動データ出力                                                  |

| TxCLK IN             | I   | 1   | TTL レベルのクロック入力。立ち上がりエッジがデータ取り込みに使用されます。端子名は TxCLK IN です。         |

| TxCLK OUT +          | O   | 1   | 正の LVDS 差動クロック出力                                                 |

| TxCLK OUT -          | O   | 1   | 負の LVDS 差動クロック出力                                                 |

| PWR DWN              | I   | 1   | TTL レベル入力。入力が Low にアサートされると、出力は TRI-STATE になり、パワー・ダウン時に低電流となります。 |

| R_FB                 | I   | 1   | プログラム可能なエッジ・ストローブ選択。High = 立ち上がりエッジ、Low = 立ち下がりエッジ               |

| V <sub>CC</sub>      | I   | 3   | TTL 入力用の電源ピン                                                     |

| GND                  | I   | 5   | TTL 入力用のグラウンド・ピン                                                 |

| PLL V <sub>CC</sub>  | I   | 1   | PLL 用の電源ピン                                                       |

| PLL GND              | I   | 2   | PLL 用のグラウンド・ピン                                                   |

| LVDS V <sub>CC</sub> | I   | 2   | LVDS 出力用の電源ピン                                                    |

| LVDS GND             | I   | 4   | LVDS 出力用のグラウンド・ピン                                                |

| NC                   |     | 6   | 未接続                                                              |

## DS90C383SLC SLC64A (FBGA) パッケージ端子説明 FPD リンク・トランスマッタ

| 端子別 |            |     | 端子タイプ別 |          |     |

|-----|------------|-----|--------|----------|-----|

| 端子  | 端子名        | タイプ | 端子     | 端子名      | タイプ |

| A1  | TxIN27     | I   | D3     | GND      | G   |

| A2  | TxOUT0 -   | O   | E4     | GND      | G   |

| A3  | TxOUT0 +   | O   | E8     | GND      | G   |

| A4  | LVDS VCC   | P   | G1     | GND      | G   |

| A5  | LVDS VCC   | P   | G6     | GND      | G   |

| A6  | TxCLKOUT - | O   | B3     | LVDS GND | G   |

## DS90C383SLC SLC64A (FBGA) パッケージ端子説明 FPD リンク・トランスマッタ(つづき)

| 端子別 |            |     | 端子タイプ別 |            |     |

|-----|------------|-----|--------|------------|-----|

| 端子  | 端子名        | タイプ | 端子     | 端子名        | タイプ |

| A7  | TxCLKOUT + | O   | B4     | LVDS GND   | G   |

| A8  | TxOUT3 +   | O   | B7     | LVDS GND   | G   |

| B1  | TxIN1      | I   | D5     | LVDS GND   | G   |

| B2  | TxIN0      | I   | C6     | PLL GND    | G   |

| B3  | LVDS GND   | G   | D6     | PLL GND    | G   |

| B4  | LVDS GND   | G   | D7     | PWR DWN    | I   |

| B5  | TxOUT2 -   | O   | G5     | R_FBF      | I   |

| B6  | TxOUT3 -   | O   | C8     | TxCLKIN    | I   |

| B7  | LVDS GND   | G   | B2     | TxIN0      | I   |

| B8  | NC         |     | B1     | TxIN1      | I   |

| C1  | TxIN3      | I   | D2     | TxIN2      | I   |

| C2  | NC         |     | C1     | TxIN3      | I   |

| C3  | NC         |     | D1     | TxIN4      | I   |

| C4  | TxOUT1 -   | O   | F1     | TxIN5      | I   |

| C5  | TxOUT2 +   | O   | E2     | TxIN6      | I   |

| C6  | PLL GND    | G   | E3     | TxIN7      | I   |

| C7  | PLL VCC    | P   | G2     | TxIN8      | I   |

| C8  | TxCLKIN    | I   | H1     | TxIN9      | I   |

| D1  | TxIN4      | I   | G3     | TxIN10     | I   |

| D2  | TxIN2      | I   | H3     | TxIN11     | I   |

| D3  | GND        | G   | F4     | TxIN12     | I   |

| D4  | TxOUT1 +   | O   | G4     | TxIN13     | I   |

| D5  | LVDS GND   | G   | H4     | TxIN14     | I   |

| D6  | PLL GND    | G   | H5     | TxIN15     | I   |

| D7  | PWD DWN    | I   | E5     | TxIN16     | I   |

| D8  | TxIN26     | I   | F5     | TxIN17     | I   |

| E1  | VCC        | P   | H6     | TxIN18     | I   |

| E2  | TxIN6      | I   | H7     | TxIN19     | I   |

| E3  | TxIN7      | I   | H8     | TxIN20     | I   |

| E4  | GND        | G   | G7     | TxIN21     | I   |

| E5  | TxIN16     | I   | F7     | TxIN22     | I   |

| E6  | VCC        | P   | G8     | TxIN23     | I   |

| E7  | TxIN24     | I   | E7     | TxIN24     | I   |

| E8  | GND        | G   | F8     | TxIN25     | I   |

| F1  | TxIN5      | I   | D8     | TxIN26     | I   |

| F2  | NC         |     | A1     | TxIN27     | I   |

| F3  | NC         |     | A6     | TxCLKOUT - | O   |

| F4  | TxIN12     | I   | A7     | TxCLKOUT + | O   |

| F5  | TxIN17     | I   | A2     | TxOUT0 -   | O   |

| F6  | NC         |     | A3     | TxOUT0 +   | O   |

| F7  | TxIN22     | I   | C4     | TxOUT1 -   | O   |

| F8  | TxIN25     | I   | D4     | TxOUT1 +   | O   |

| G1  | GND        | G   | B5     | TxOUT2 -   | O   |

| G2  | TxIN8      | I   | C5     | TxOUT2 +   | O   |

| G3  | TxIN10     | I   | B6     | TxOUT3 -   | O   |

| G4  | TxIN13     | I   | A8     | TxOUT3 +   | O   |

| G5  | R_FBF      | I   | A4     | LVDS VCC   | P   |

| G6  | GND        | G   | A5     | LVDS VCC   | P   |

## DS90C383SLC SLC64A (FBGA) パッケージ端子説明 FPD リンク・トランスマッタ (つづき)

| 端子別 |        |     | 端子タイプ別 |         |     |

|-----|--------|-----|--------|---------|-----|

| 端子  | 端子名    | タイプ | 端子     | 端子名     | タイプ |

| G7  | TxIN21 | I   | C7     | PLL VCC | P   |

| G8  | TxIN23 | I   | E1     | VCC     | P   |

| H1  | TxIN9  | I   | E6     | VCC     | P   |

| H2  | VCC    | P   | H2     | VCC     | P   |

| H3  | TxIN11 | I   | B8     | NC      |     |

| H4  | TxIN14 | I   | C2     | NC      |     |

| H5  | TxIN15 | I   | C3     | NC      |     |

| H6  | TxIN18 | I   | F2     | NC      |     |

| H7  | TxIN19 | I   | F3     | NC      |     |

| H8  | TxIN20 | I   | F6     | NC      |     |

G: グラウンド

I: 入力

O: 出力

P: 電源

NC: 未接続

## DS90CF384 MTD56 TSSOP パッケージ端子説明 FPD リンク・レシーバ

| 端子名                  | I/O | No. | 説明                                                                                                                             |

|----------------------|-----|-----|--------------------------------------------------------------------------------------------------------------------------------|

| RxIN +               | I   | 4   | 正の LVDS 差動データ入力                                                                                                                |

| RxIN -               | I   | 4   | 負の LVDS 差動データ入力                                                                                                                |

| RxOUT                | O   | 28  | TTL レベル入力。これには、8 ビットの Red、8 ビットの Green、8 ビットの Blue、および 4 ビットの制御信号 FPLINE、FPFRAME、DRDY、CNTL (HSYNC、VSYNC、Data Enable、他) が含まれます。 |

| RxCLK IN +           | I   | 1   | 正の LVDS 差動クロック出力                                                                                                               |

| RxCLK IN -           | I   | 1   | 負の LVDS 差動クロック出力                                                                                                               |

| FPSHIFT OUT          | O   | 1   | TTL レベルのクロック出力。立ち下がりエッジがデータ取り込みに使用されます。端子名は RxCLK OUT です。                                                                      |

| PWR DOWN             | I   | 1   | TTL レベル入力。入力が Low にアサートされると、レシーバ出力は、Low になります。                                                                                 |

| V <sub>CC</sub>      | I   | 4   | TTL 出力用の電源ピン                                                                                                                   |

| GND                  | I   | 5   | TTL 出力用のグラウンド・ピン                                                                                                               |

| PLL V <sub>CC</sub>  | I   | 1   | PLL 用の電源ピン                                                                                                                     |

| PLL GND              | I   | 2   | PLL 用のグラウンド・ピン                                                                                                                 |

| LVDS V <sub>CC</sub> | I   | 1   | LVDS 入力用の電源ピン                                                                                                                  |

| LVDS GND             | I   | 3   | LVDS 入力用のグラウンド・ピン                                                                                                              |

## DS90CF384 64 ピン FBGA パッケージ端子説明 FPD リンク・レシーバ

| 端子名                  | I/O | No. | 説明                                                                                                                             |

|----------------------|-----|-----|--------------------------------------------------------------------------------------------------------------------------------|

| RxIN +               | I   | 4   | 正の LVDS 差動データ入力                                                                                                                |

| RxIN -               | I   | 4   | 負の LVDS 差動データ入力                                                                                                                |

| RxOUT                | O   | 28  | TTL レベル入力。これには、8 ビットの Red、8 ビットの Green、8 ビットの Blue、および 4 ビットの制御信号 FPLINE、FPFRAME、DRDY、CNTL (HSYNC、VSYNC、Data Enable、他) が含まれます。 |

| RxCLK IN +           | I   | 1   | 正の LVDS 差動クロック出力                                                                                                               |

| RxCLK IN -           | I   | 1   | 負の LVDS 差動クロック出力                                                                                                               |

| FPSHIFT OUT          | O   | 1   | TTL レベルのクロック出力。立ち下がりエッジがデータ取り込みに使用されます。端子名は RxCLK OUT です。                                                                      |

| PWR DOWN             | I   | 1   | TTL レベル入力。入力が Low にアサートされると、レシーバ出力は、Low になります。                                                                                 |

| V <sub>CC</sub>      | I   | 4   | TTL 出力用の電源ピン                                                                                                                   |

| GND                  | I   | 5   | TTL 出力用のグラウンド・ピン                                                                                                               |

| PLL V <sub>CC</sub>  | I   | 1   | PLL 用の電源ピン                                                                                                                     |

| PLL GND              | I   | 2   | PLL 用のグラウンド・ピン                                                                                                                 |

| LVDS V <sub>CC</sub> | I   | 2   | LVDS 入力用の電源ピン                                                                                                                  |

## DS90CF384 64 ピン FBGA パッケージ端子説明 FPD リンク・レシーバ(つづき)

| 端子名      | I/O | No. | 説明                |

|----------|-----|-----|-------------------|

| LVDS GND | I   | 4   | LVDS 入力用のグラウンド・ピン |

| NC       |     | 6   | 未接続               |

## DS90CF384 64 ピン、FBGA パッケージ端子定義 FPD リンク・レシーバ

| 端子別 |          |     | 端子タイプ別 |           |     |

|-----|----------|-----|--------|-----------|-----|

| 端子  | 端子名      | タイプ | 端子     | 端子名       | タイプ |

| A1  | RxOUT17  | O   | A4     | GND       | G   |

| A2  | VCC      | P   | B1     | GND       | G   |

| A3  | RxOUT15  | O   | B6     | GND       | G   |

| A4  | GND      | G   | D8     | GND       | G   |

| A5  | RxOUT12  | O   | E3     | GND       | G   |

| A6  | RxOUT8   | O   | E5     | LVDS GND  | G   |

| A7  | RxOUT7   | O   | G3     | LVDS GND  | G   |

| A8  | RxOUT6   | O   | G7     | LVDS GND  | G   |

| B1  | GND      | G   | H5     | LVDS GND  | G   |

| B2  | NC       |     | F6     | PLL GND   | G   |

| B3  | RxOUT16  | O   | G8     | PLL GND   | G   |

| B4  | RxOUT11  | O   | E6     | PWR DWN   | I   |

| B5  | VCC      | P   | H6     | RxCLKIN - | I   |

| B6  | GND      | G   | H7     | RxCLKIN + | I   |

| B7  | RxOUT5   | O   | H2     | RxIN0 -   | I   |

| B8  | RxOUT3   | O   | H3     | RxIN0 +   | I   |

| C1  | RxOUT21  | O   | F4     | RxIN1 -   | I   |

| C2  | NC       |     | G4     | RxIN1 +   | I   |

| C3  | RxOUT18  | O   | G5     | RxIN2 -   | I   |

| C4  | RxOUT14  | O   | F5     | RxIN2 +   | I   |

| C5  | RxOUT9   | O   | G6     | RxIN3 -   | I   |

| C6  | RxOUT4   | O   | H8     | RxIN3 +   | I   |

| C7  | NC       |     | E7     | RxCLKOUT  | O   |

| C8  | RxOUT1   | O   | E8     | RxOUT0    | O   |

| D1  | VCC      | P   | C8     | RxOUT1    | O   |

| D2  | RxOUT20  | O   | D7     | RxOUT2    | O   |

| D3  | RxOUT19  | O   | B8     | RxOUT3    | O   |

| D4  | RxOUT13  | O   | C6     | RxOUT4    | O   |

| D5  | RxOUT10  | O   | B7     | RxOUT5    | O   |

| D6  | VCC      | P   | A8     | RxOUT6    | O   |

| D7  | RxOUT2   | O   | A7     | RxOUT7    | O   |

| D8  | GND      | G   | A6     | RxOUT8    | O   |

| E1  | RxOUT22  | O   | C5     | RxOUT9    | O   |

| E2  | RxOUT24  | O   | D5     | RxOUT10   | O   |

| E3  | GND      | G   | B4     | RxOUT11   | O   |

| E4  | LVDS VCC | P   | A5     | RxOUT12   | O   |

| E5  | LVDS GND | G   | D4     | RxOUT13   | O   |

| E6  | PWR DWN  | I   | C4     | RxOUT14   | O   |

| E7  | RxCLKOUT | O   | A3     | RxOUT15   | O   |

| E8  | RxOUT0   | O   | B3     | RxOUT16   | O   |

| F1  | RxOUT23  | O   | A1     | RxOUT17   | O   |

## DS90CF384 64 ピン、FBGA パッケージ端子定義 FPD リンク・レシーバ (つづき)

| 端子別 |           |     | 端子タイプ別 |          |     |

|-----|-----------|-----|--------|----------|-----|

| 端子  | 端子名       | タイプ | 端子     | 端子名      | タイプ |

| F2  | RxOUT26   | O   | C3     | RxOUT18  | O   |

| F3  | NC        |     | D3     | RxOUT19  | O   |

| F4  | RxIN1 -   | I   | D2     | RxOUT20  | O   |

| F5  | RxIN2 +   | I   | C1     | RxOUT21  | O   |

| F6  | PLL GND   | G   | E1     | RxOUT22  | O   |

| F7  | PLL VCC   | P   | F1     | RxOUT23  | O   |

| F8  | NC        |     | E2     | RxOUT24  | O   |

| G1  | RxOUT25   | O   | G1     | RxOUT25  | O   |

| G2  | NC        |     | F2     | RxOUT26  | O   |

| G3  | LVDS GND  | G   | H1     | RxOUT27  | O   |

| G4  | RxIN1 +   | I   | E4     | LVDS VCC | P   |

| G5  | RxIN2 -   | I   | H4     | LVDS VCC | P   |

| G6  | RxIN3 -   | I   | F7     | PLL VCC  | P   |

| G7  | LVDS GND  | G   | A2     | VCC      | P   |

| G8  | PLL GND   | G   | B5     | VCC      | P   |

| H1  | RxOUT27   | O   | D1     | VCC      | P   |

| H2  | RxIN0 -   | I   | D6     | VCC      | P   |

| H3  | RxIN0 +   | I   | B2     | NC       |     |

| H4  | LVDS VCC  | P   | C2     | NC       |     |

| H5  | LVDS GND  | G   | C7     | NC       |     |

| H6  | RxCLKIN - | I   | F3     | NC       |     |

| H7  | RxCLKIN + | I   | F8     | NC       |     |

| H8  | RxIN3 +   | I   | G2     | NC       |     |

G: グラウンド

I: 入力

O: 出力

P: 電源

NC: 未接続

## Pin Diagrams for TSSOP Packages

TABLE 1. Programmable Transmitter

| Pin  | Condition              | Strobe Status       |

|------|------------------------|---------------------|

| R_Fb | R_Fb = V <sub>CC</sub> | Rising edge strobe  |

| R_Fb | R_Fb = GND             | Falling edge strobe |

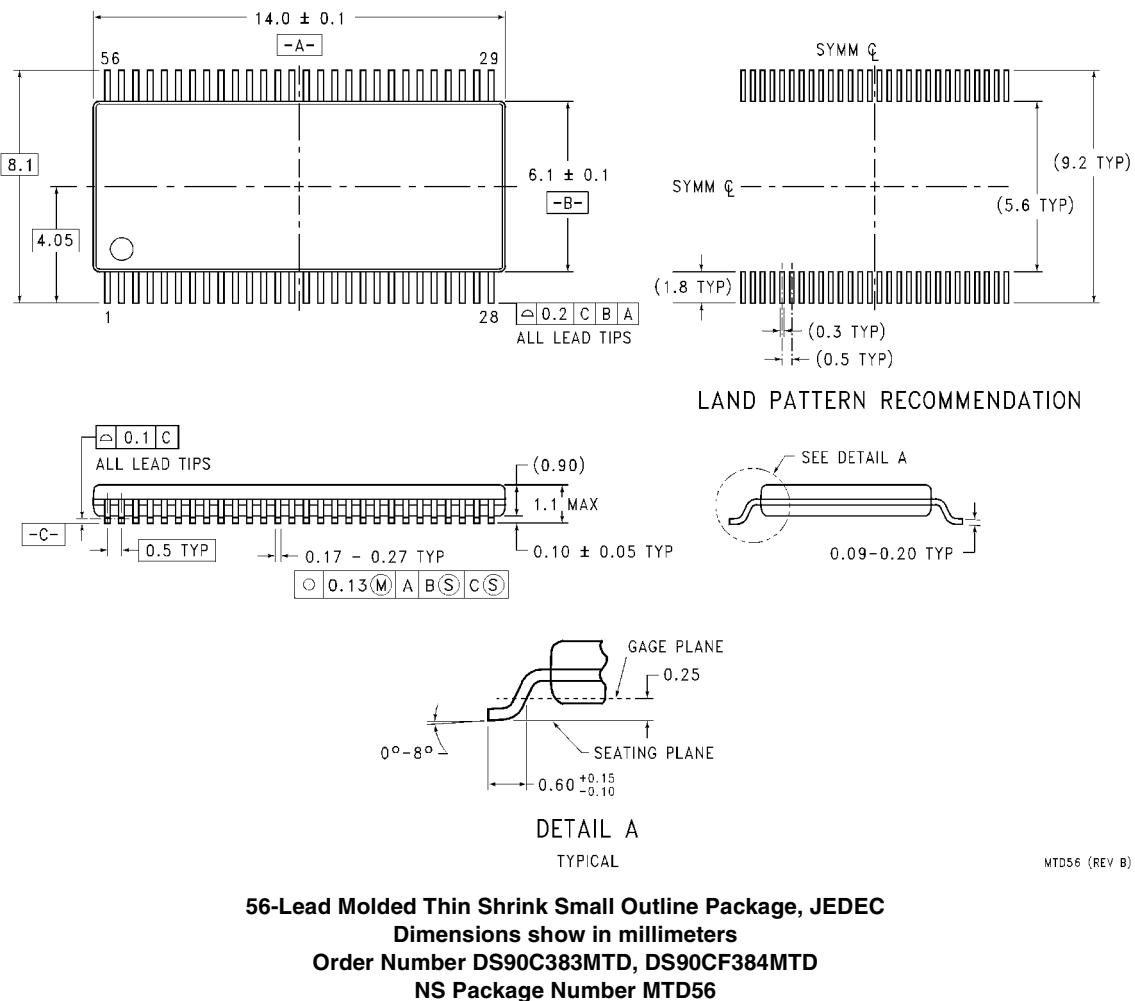

## 外形寸法図 単位は millimeters

**56-Lead Molded Thin Shrink Small Outline Package, JEDEC

Dimensions show in millimeters

Order Number DS90C383MTD, DS90CF384MTD

NS Package Number MTD56**

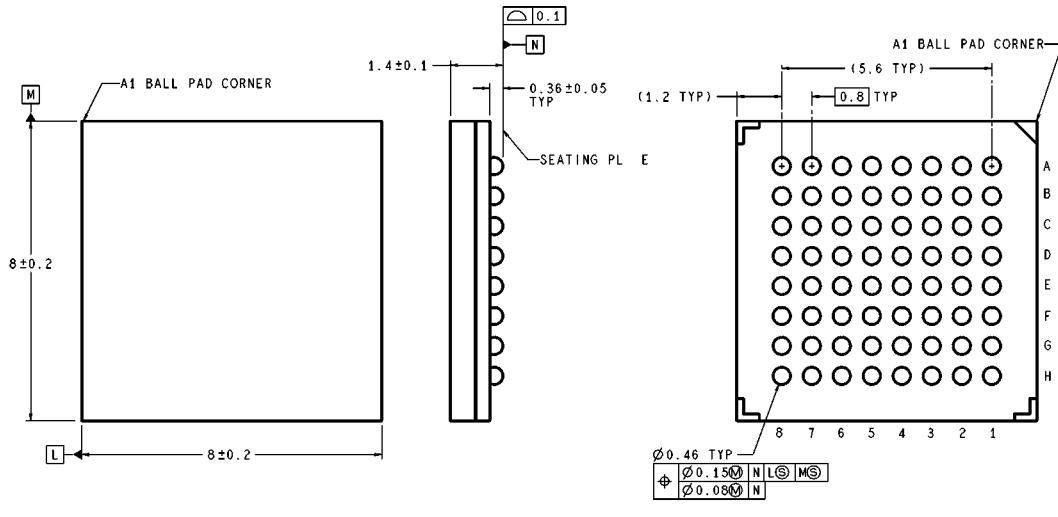

## 外形寸法図 単位は millimeters (つづき)

DIMENSIONS ARE IN MILLIMETERS

SLC64A (Rev B)

**64 ball, 0.8mm fine pitch ball grid array (FBGA) Package**

**Dimensions show in millimeters only**

**Order Number DS90CF384SLC or DS90C383SLC**

**NS Package Number SLC64A**

## 生命維持装置への使用について

弊社の製品はナショナルセミコンダクター社の書面による許可なくしては、生命維持用の装置またはシステム内の重要な部品として使用することはできません。

1. 生命維持用の装置またはシステムとは (a) 体内に外科的に使用されることを意図されたもの、または (b) 生命を維持あるいは支持するものをいい、ラベルにより表示される使用法に従って適切に使用された場合に、これの不具合が使用者に身体的障害を与えると予想されるものをいいます。

2. 重要な部品とは、生命維持にかかわる装置またはシステム内のすべての部品をいい、これの不具合が生命維持用の装置またはシステムの不具合の原因となりそれらの安全性や機能に影響を及ぼすことが予想されるものをいいます。

## ナショナルセミコンダクター ジャパン株式会社

本社 / 〒135-0042 東京都江東区木場2-17-16 TEL.(03)5639-7300

技術資料（日本語／英語）はホームページより入手可能です。 その他のお問い合わせはフリーダイヤルをご利用下さい。

<http://www.national.com/JPN/>

フリーダイヤル 0120-666-116

# ご注意

日本テキサス・インスツルメンツ株式会社（以下TIJといいます）及びTexas Instruments Incorporated（TIJの親会社、以下TIJないしTexas Instruments Incorporatedを総称してTIといいます）は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIJとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIJの標準販売契約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIJとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。TI製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI製部品を使用したお客様の製品及びアプリケーションについて想定される危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明しておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならぬ場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、かつその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの默示的保証を無効にし、かつ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任も負いません。

TIは、TIの製品が、安全でないことが致命的となる用途ないしアプリケーション（例えば、生命維持装置のように、TI製品に不良があった場合に、その不良により相当な確率で死傷等の重篤な事故が発生するようなもの）に使用されることを認めておりません。但し、お客様とTIの双方の権限有る役員が書面でそのような使用について明確に合意した場合は除きます。たとえTIがアプリケーションに関連した情報やサポートを提供したとしても、お客様は、そのようなアプリケーションの安全面及び規制面から見た諸問題を解決するために必要とされる専門的知識及び技術を持ち、かつ、お客様の製品について、またTI製品をそのような安全でないことが致命的となる用途に使用することについて、お客様が全ての法的責任、規制を遵守する責任、及び安全に関する要求事項を満足させる責任を負っていることを認め、かつそのことに同意します。さらに、もし万一、TIの製品がそのような安全でないことが致命的となる用途に使用されたことによって損害が発生し、TIないしその代表者がその損害を賠償した場合は、お客様がTIないしその代表者にその全額の補償をするものとします。

TI製品は、軍事的用途もしくは宇宙航空アプリケーションないし軍事的環境、航空宇宙環境にて使用されるようには設計もされていませんし、使用されることを意図されておりません。但し、当該TI製品が、軍需対応グレード品、若しくは「強化プラスティック」製品としてTIが特別に指定した製品である場合は除きます。TIが軍需対応グレード品として指定した製品のみが軍需品の仕様書に合致いたします。お客様は、TIが軍需対応グレード品として指定していない製品を、軍事的用途もしくは軍事的環境下で使用することは、もっぱらお客様の危険負担においてなされるということ、及び、お客様がもっぱら責任をもって、そのような使用に関して必要とされる全ての法的要件及び規制上の要求事項を満足させなければならないことを認め、かつ同意します。

TI製品は、自動車用アプリケーションないし自動車の環境において使用されるようには設計もされていませんし、また使用されることを意図されておりません。但し、TIがISO/TS 16949の要求事項を満たしていると特別に指定したTI製品は除きます。お客様は、お客様が当該TI指定品以外のTI製品を自動車用アプリケーションに使用しても、TIは当該要求事項を満たしていなかったことについて、いかなる責任も負わないことを認め、かつ同意します。

Copyright © 2011, Texas Instruments Incorporated

日本語版 日本テキサス・インスツルメンツ株式会社

## 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。

### 1. 静電気

- 素手で半導体製品単体を触らないこと。どうしても触る必要がある場合は、リストストラップ等で人体からアースをとり、導電性手袋等をして取り扱うこと。

- 弊社出荷梱包単位（外装から取り出された内装及び個装）又は製品単品で取り扱いを行う場合は、接地された導電性のテーブル上で（導電性マットにアースをとったもの等）、アースをした作業者が行うこと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

- 前記のリストストラップ・導電性手袋・テーブル表面及び実装装置類の接地等の静電気帯電防止措置は、常に管理されその機能が確認されていること。

### 2. 溫・湿度環境

- 温度：0～40°C、相対湿度：40～85%で保管・輸送及び取り扱いを行うこと。（但し、結露しないこと。）

- 直射日光があたる状態で保管・輸送しないこと。

### 3. 防湿梱包

- 防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装すること。

### 4. 機械的衝撃

- 梱包品（外装、内装、個装）及び製品単品を落下させたり、衝撃を与えないこと。

### 5. 熱衝撃

- はんだ付け時は、最低限260°C以上の高温状態に、10秒以上さらさないこと。（個別推奨条件がある時はそれに従うこと。）

### 6. 汚染

- はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質（硫黄、塩素等ハロゲン）のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。（不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。）

以上