# DS90URxxx-Q1 5MHz～43MHz、DC 平衡型、24 ビット、FPD-Link II シリアライザ およびデシリアライザチップセット

## 1 特長

- 18 ビット色深度のディスプレイをサポート

- 5MHz～43MHz のピクセルクロック

- 車載グレード製品 (AEC-Q100 グレード 2) 認定済み

- 24:1 のインターフェイス圧縮

- DC バランシングと埋め込みクロックにより、AC 結合データ伝送をサポート

- 最大 10m のシールドツイストペアケーブルを駆動可能

- 基準クロック不要 (デシリアライザ)

- ISO 10605 ESD (8kV HBM を上回る ESD 構造) に適合

- ホットプラグに対応

- EMI 低減 - スペクトラム拡散入力に対応するシリアルリンク。シリアルリンクでのデータのランダム化とシャッフル。調整可能な PTO (段階的ターンオン) LVCMOS 出力を備えたデシリアライザ

- @Speed BIST (内蔵セルフテスト) により、LVDS 伝送経路を検証

- トランシミッタとレシーバの両方を個別にパワーダウン制御

- 電源電圧範囲: 3.3V ±10%

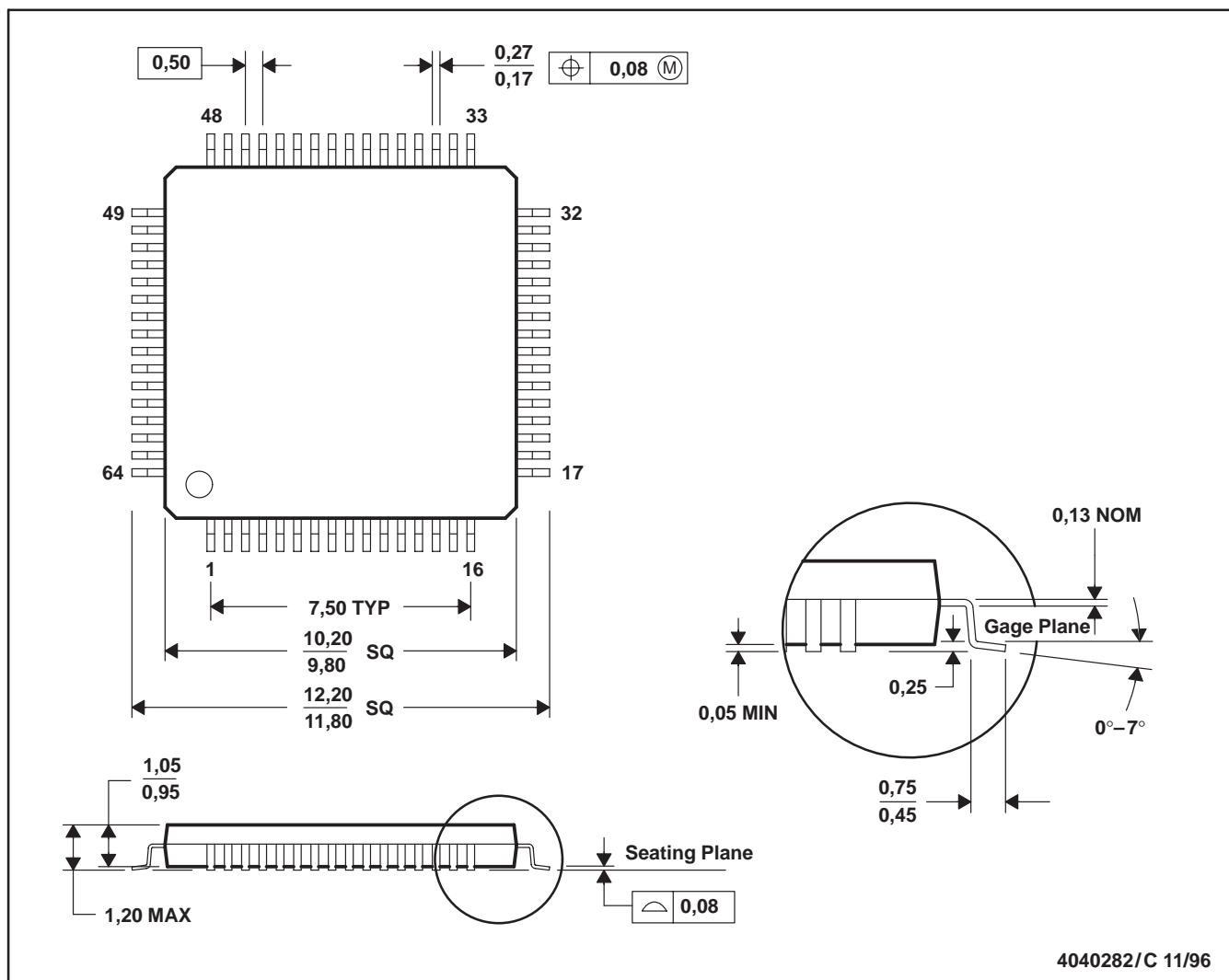

- トランシミッタ用 48 ピン TQFP パッケージとレシーバ用 64 ピン TQFP パッケージ

- 温度範囲: -40°C～105°C

- DS90C241/DS90C124 との下位互換モード

## 2 アプリケーション

- 車載用集中情報ディスプレイ

- 車載用インストルメントクラスタディスプレイ

- 車載用ヘッドアップディスプレイ

- リモートカメラベースの運転支援システム

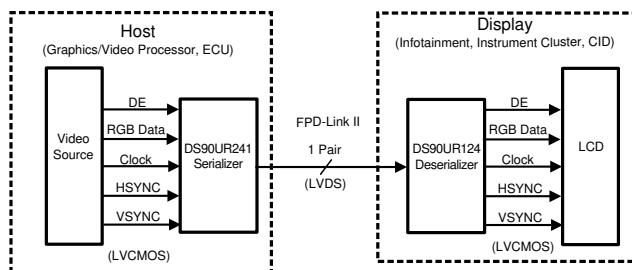

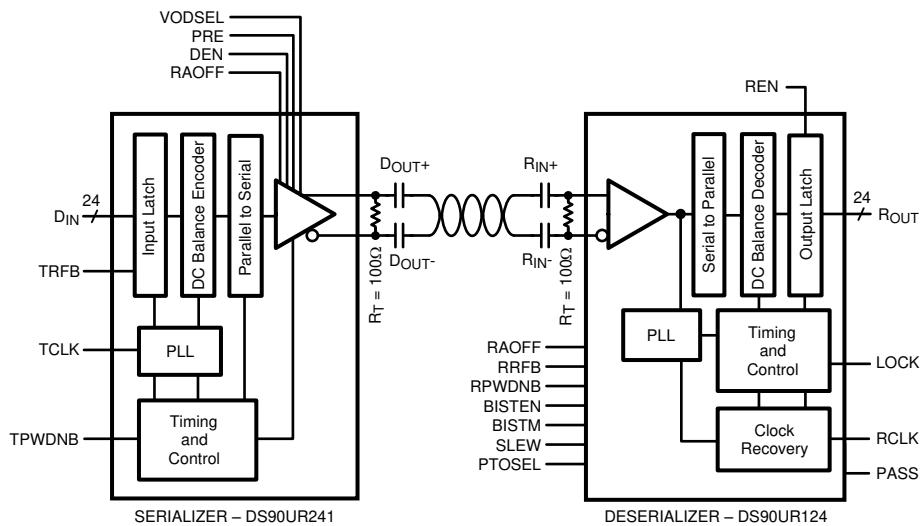

アプリケーション図

## 3 概要

DS90URxxx-Q1 チップセットは、24 ビットのパラレルバスを、クロック情報が埋め込まれた、完全に透過的なデータ / 制御 FPD-Link II LVDS シリアルストリームに変換します。このチップセットは、18 ビット色深度(RGB666)、「HS, VS, DE」、3 つの追加汎用データチャネルを必要とするディスプレイのグラフィカルデータを駆動するために設計されています。この単一のシリアルストリームにより、パラレルデータとクロックバスの間でスキーの問題が排除されるため、PCB 上の配線およびケーブルで 24 ビットのデータバスを簡単に転送できます。本デバイスを使うと、データバスを狭くでき、PCB レイヤ、ケーブル幅、コネクタのサイズとピン数のすべてを削減できるため、システムコストを低減できます。

DS90URxxx-Q1 は、高速 I/O に FPD-Link II LVDS 方式を採用しています。FPD-Link II LVDS は、シリアル伝送バス上で確実にデータを転送するための低消費電力かつ低ノイズの環境を提供します。動作周波数範囲について、シリアルライザの出力エッジレートを最適化することにより、さらに EMI が低減されます。

さらに、このデバイスにはプリエンファシス機能があり、損失の多いケーブル上で長距離の伝送を行えるよう信号をブーストできます。内部の DC バランスされたエンコードおよびデコードを使用して、AC カッピング相互接続に対応できます。テキサス・インスツルメンツ独自のランダムロックを使うと、シリアルライザのパラレルデータは、REFCLK を必要とせずに、デシリアルライザに対してランダム化されます。

### 製品情報

| 部品番号         | パッケージ <sup>(1)</sup> | 本体サイズ(公称) <sup>(2)</sup> |

|--------------|----------------------|--------------------------|

| DS90UR124-Q1 | TQFP (64)            | 10.00mm × 10.00mm        |

| DS90UR241-Q1 | TQFP (48)            | 7.00mm × 7.00mm          |

- 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

- パッケージサイズ(長さ × 幅)は公称値であり、該当する場合はピンも含まれます。

ブロック図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール(機械翻訳)を使用していることがあり、TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                             |    |                        |    |

|-----------------------------|----|------------------------|----|

| 1 特長                        | 1  | 6 詳細説明                 | 19 |

| 2 アプリケーション                  | 1  | 6.1 概要                 | 19 |

| 3 概要                        | 1  | 6.2 機能ブロック図            | 19 |

| 4 ピン構成および機能                 | 3  | 6.3 機能説明               | 19 |

| 5 仕様                        | 8  | 6.4 デバイスの機能モード         | 24 |

| 5.1 絶対最大定格                  | 8  | 7 デバイスおよびドキュメントのサポート   | 34 |

| 5.2 ESD 定格                  | 8  | 7.1 デバイス サポート          | 34 |

| 5.3 推奨動作条件                  | 9  | 7.2 ドキュメントのサポート        | 34 |

| 5.4 熱に関する情報                 | 9  | 7.3 ドキュメントの更新通知を受け取る方法 | 34 |

| 5.5 電気的特性                   | 9  | 7.4 サポート・リソース          | 34 |

| 5.6 シリアライザの TCLK の入力タイミング要件 | 11 | 7.5 商標                 | 34 |

| 5.7 シリアライザのスイッチング特性         | 11 | 7.6 静電気放電に関する注意事項      | 34 |

| 5.8 デシリアライザのスイッチング特性        | 11 | 7.7 用語集                | 34 |

| 5.9 代表的特性                   | 18 | 8 改訂履歴                 | 34 |

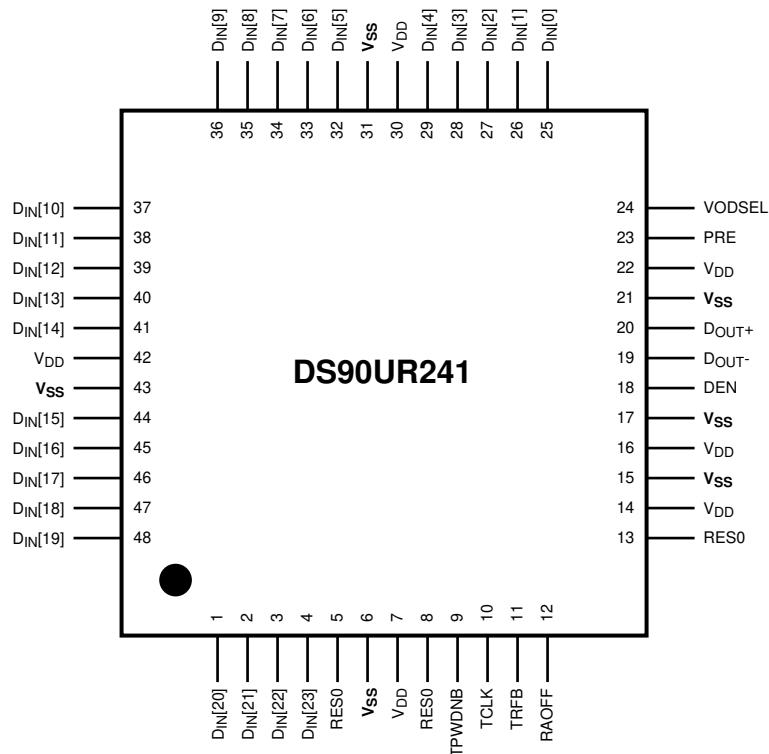

## 4 ピン構成および機能

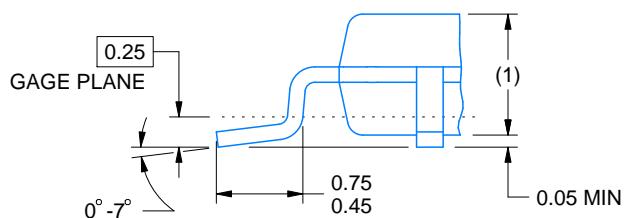

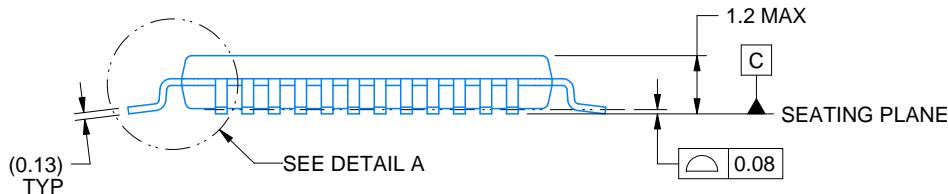

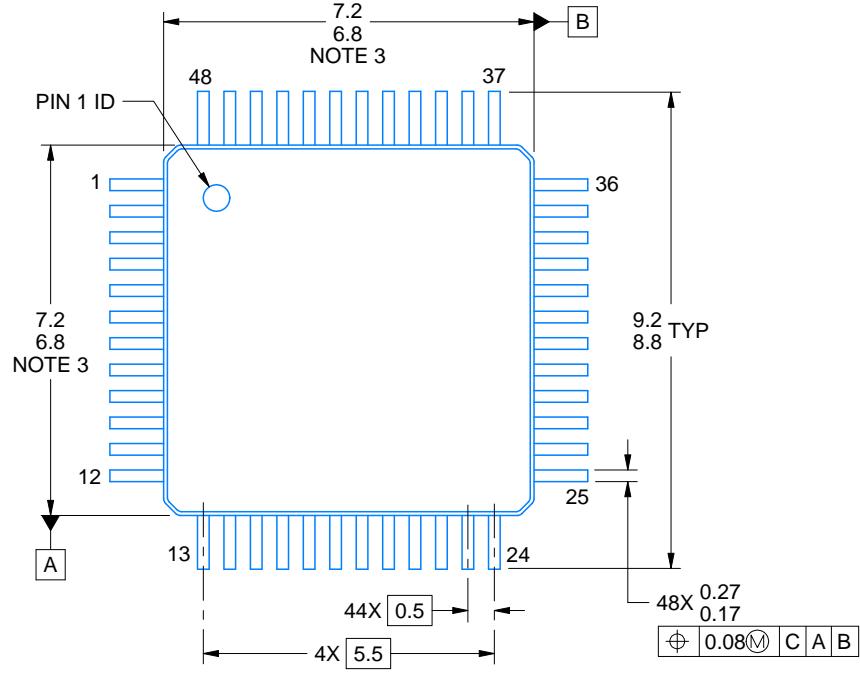

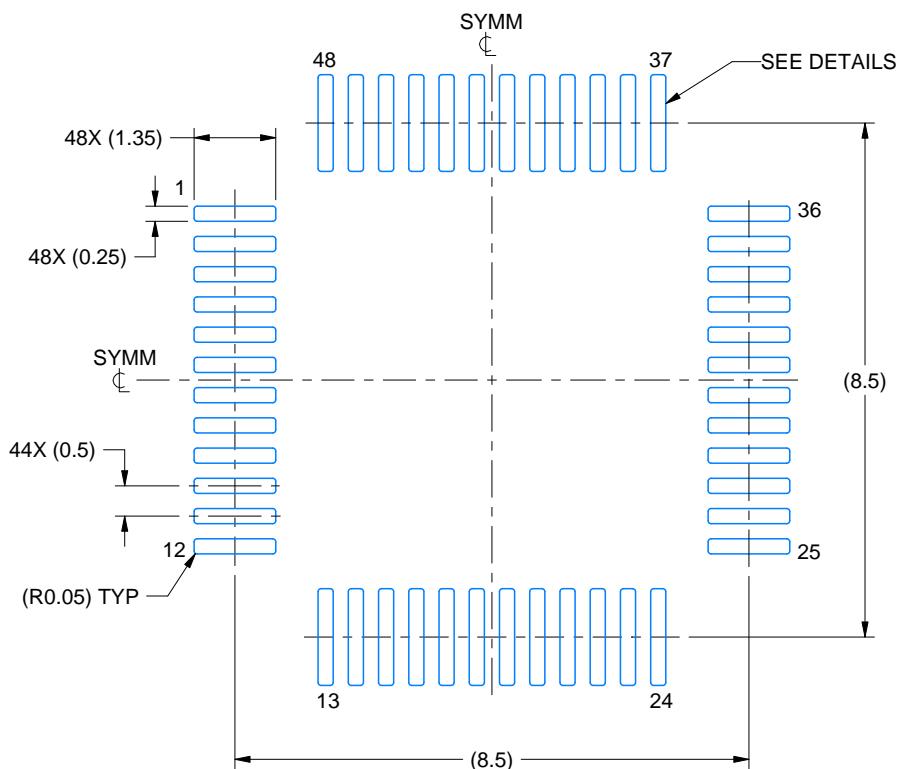

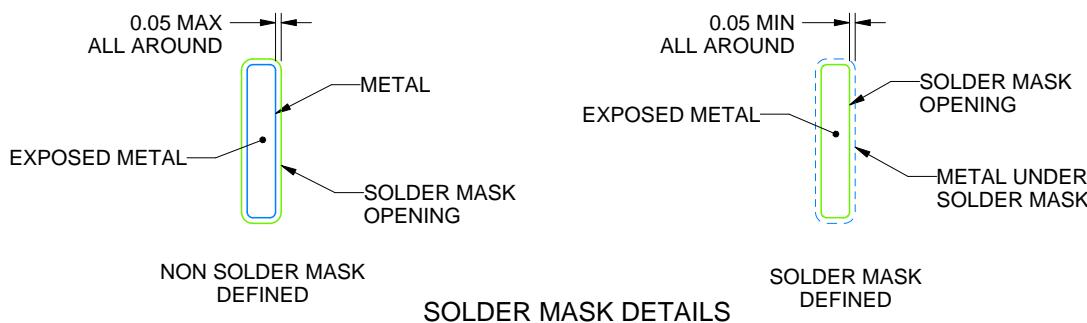

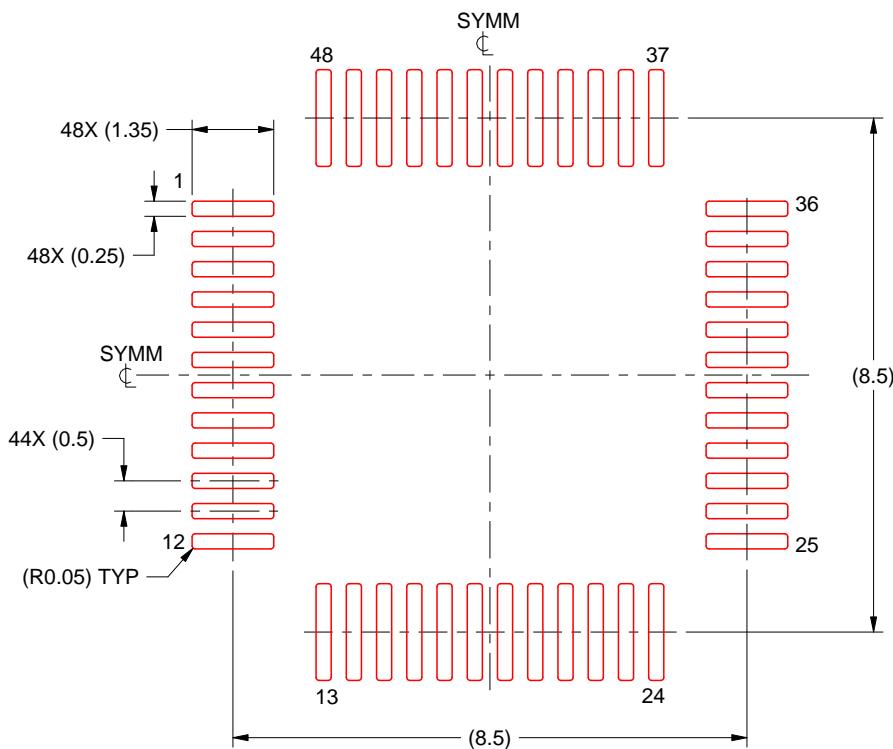

図 4-1. PFB パッケージ

48 ピン TQFP

上面図

表 4-1. ピンの機能 : PFB パッケージ

| 番号                                        | ピン<br>番号               | I/O<br>名称 | 説明                                                                                                                                                                                                                                                        |

|-------------------------------------------|------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>LVC MOS パラレル インターフェイス ピン</b>           |                        |           |                                                                                                                                                                                                                                                           |

| 4~1、<br>48~<br>44、41<br>~32、<br>29~<br>25 | D <sub>IN</sub> [23:0] | LVC MOS_I | トランシミッタのパラレル インターフェイスのデータ入力ピン。未使用の場合、Low に接続します。フロー ティングにしないでください。                                                                                                                                                                                        |

| <b>制御および構成ピン</b>                          |                        |           |                                                                                                                                                                                                                                                           |

| 18                                        | DEN                    | LVC MOS_I | トランシミッタのデータ イネーブル<br>DEN = H:LVDS ドライバ出力は有効 (オン)<br>DEN = L:LVDS ドライバ出力は無効 (オフ)。トランシミッタの LVDS ドライバの D <sub>OUT</sub> (+/-) 出力はトライス テート。PLL は動作し続けており、TCLK にロック。                                                                                           |

| 23                                        | PRE                    | LVC MOS_I | プリエンファシス レベル選択<br>PRE = NC (未接続): プリエンファシスは無効 (オフ)。<br>外部抵抗 R <sub>PRE</sub> を介して入力を V <sub>SS</sub> に接続すると、プリエンファシスが作動します。抵抗値によって、プリエンファシス レベルが決まります。推奨値 R <sub>PRE</sub> ≥ 6kΩ, I <sub>max</sub> = [48 / R <sub>PRE</sub> ], R <sub>PRE min</sub> = 6kΩ |

表 4-1. ピンの機能 : PFB パッケージ (続き)

| ピン                          |        | I/O      | 説明                                                                                                                                                                                                                                      |

|-----------------------------|--------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 番号                          | 名称     |          |                                                                                                                                                                                                                                         |

| 12                          | RAOFF  | LVCMOS_I | ランダマイザ制御入力ピン<br>RAOFF = H: DS90C124 デシリアルライザと組み合わせて使用するための下位互換モード。<br>RAOFF = L: 追加のランダム化をオン (デフォルト)。2E7 LSFR 設定を選択します。<br>詳細については、表 6-1 を参照してください。                                                                                     |

| 5, 8、<br>13                 | RES0   | LVCMOS_I | 予約済み。このピンは、Low に接続する必要があります。                                                                                                                                                                                                            |

| 9                           | TPWDNB | LVCMOS_I | トランスマッタのパワー ダウン バー<br>TPWDNB = H: トランスマッタは有効。<br>TPWDNB = L: トランスマッタはパワーダウン モード (スリープ)、LVDS ドライバの DOUT (+/-) 出力はトライステートスタンバイ モードになり、PLL はシャットダウンして消費電力を最小化します。                                                                          |

| 11                          | TRFB   | LVCMOS_I | トランスマッタのクロック エッジ選択ピン<br>TRFB = H: パラレル インターフェイス データは立ち上がりクロック エッジでストローブされます。<br>TRFB = L: パラレル インターフェイス データは立ち下がりクロック エッジでストローブされます。                                                                                                    |

| 24                          | VODSEL | LVCMOS_I | VOD レベル選択<br>VODSEL = L: LVDS ドライバ出力は $\pm 500\text{mV}$ ( $R_L = 100\Omega$ )<br>VODSEL = H: LVDS ドライバ出力は $\pm 900\text{mV}$ ( $R_L = 100\Omega$ )<br>通常のアプリケーションでは、このピンを Low に設定します。より大きい VOD が必要な長ケーブル アプリケーションでは、このピンを High に設定します。 |

| <b>LVDS シリアル インターフェイスピン</b> |        |          |                                                                                                                                                                                                                                         |

| 20                          | DOUT+  | LVDS_O   | トランスマッタ LVDS 真 (+) 出力。<br>この出力は、DOUT+ ピンに対する $100\Omega$ 負荷を接続するように設計されています。相互接続は、 $100\text{nF}$ のコンデンサを使用してこのピンと AC 結合させる必要があります。                                                                                                     |

| 19                          | DOUT-  | LVDS_O   | トランスマッタ LVDS 反転 (-) 出力<br>この出力は、DOUT- ピンに対する $100\Omega$ 負荷を接続するように設計されています。相互接続は、 $100\text{nF}$ のコンデンサを使用してこのピンと AC 結合する必要があります。                                                                                                      |

| <b>電源 / グランド ピン</b>         |        |          |                                                                                                                                                                                                                                         |

| 22                          | VDD    | VDD      | アナログ電圧電源、LVDS 出力電源                                                                                                                                                                                                                      |

| 16                          | VDD    | VDD      | アナログ電圧電源、VCO 電源                                                                                                                                                                                                                         |

| 14                          | VDD    | VDD      | アナログ電圧電源、PLL 電源                                                                                                                                                                                                                         |

| 30                          | VDD    | VDD      | デジタル電圧電源、シリアルライザ電源                                                                                                                                                                                                                      |

| 7                           | VDD    | VDD      | デジタル電圧電源、シリアルライザ ロジック電源                                                                                                                                                                                                                 |

| 42                          | VDD    | VDD      | デジタル電圧電源、シリアルライザ 入力電源                                                                                                                                                                                                                   |

| 21                          | VSS    | GND      | アナログ グランド、LVDS 出力グランド                                                                                                                                                                                                                   |

| 17                          | VSS    | GND      | アナログ グランド、VCO グランド                                                                                                                                                                                                                      |

| 15                          | VSS    | GND      | アナログ グランド、PLL グランド                                                                                                                                                                                                                      |

| 31                          | VSS    | GND      | デジタル グランド、シリアルライザ グランド                                                                                                                                                                                                                  |

| 6                           | VSS    | GND      | デジタル グランド、シリアルライザ ロジック グランド                                                                                                                                                                                                             |

| 43                          | VSS    | GND      | デジタル グランド、シリアルライザ 入力グランド                                                                                                                                                                                                                |

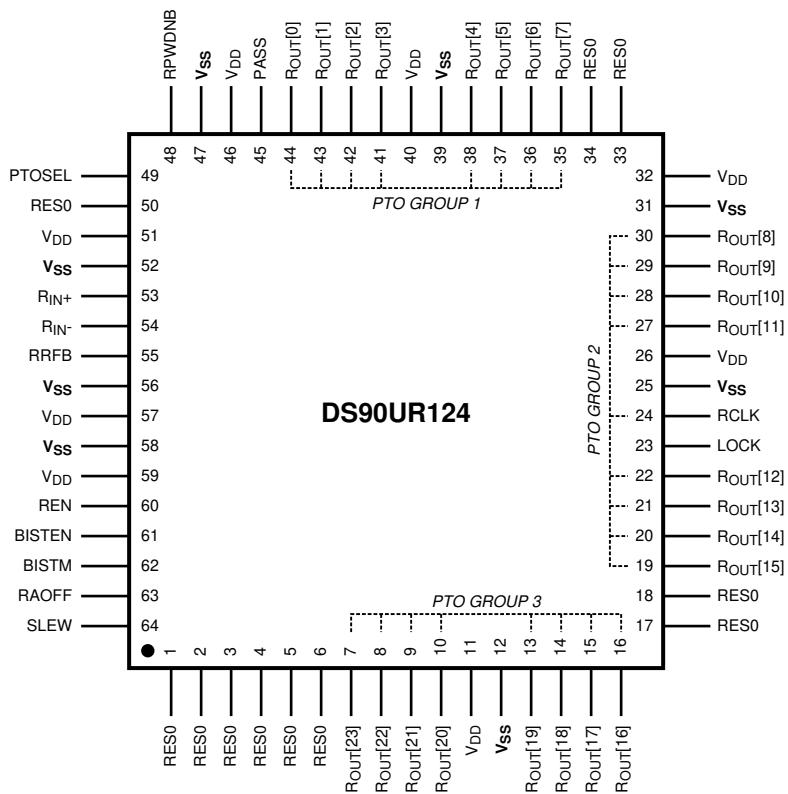

図 4-2. PAG パッケージ

64 ピン TQFP

上面図

表 4-2. ピンの機能 : PAG パッケージ

| 番号                             | ピン<br>名称    | I/O       | 説明                                                                                                                                                                                                                                            |

|--------------------------------|-------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>LVC MOS パラレル インターフェイスピン</b> |             |           |                                                                                                                                                                                                                                               |

| 24                             | RCLK        | LVC MOS_O | パラレル インターフェイスクロック出力ピン。ストローブ エッジは RRFB 構成ピンによって設定されます。                                                                                                                                                                                         |

| 35-38<br>、<br>41-44            | ROUT[7:0]   | LVC MOS_O | レシーバ パラレル インターフェイスデータ出力 - グループ 1                                                                                                                                                                                                              |

| 19-22<br>、<br>27-30            | ROUT[15:8]  | LVC MOS_O | レシーバ パラレル インターフェイスデータ出力 - グループ 2                                                                                                                                                                                                              |

| 7-10<br>、<br>13-16             | ROUT[23:16] | LVC MOS_O | レシーバ パラレル インターフェイスデータ出力 - グループ 3                                                                                                                                                                                                              |

| <b>制御および構成ピン</b>               |             |           |                                                                                                                                                                                                                                               |

| 23                             | LOCK        | LVC MOS_O | LOCK はレシーバ PLL の状態を示します。<br>LOCK = H: レシーバ PLL はロックしている。<br>LOCK = L: レシーバ PLL ロックしていない。ROUT[23:0] と RCLK はトライステート。                                                                                                                           |

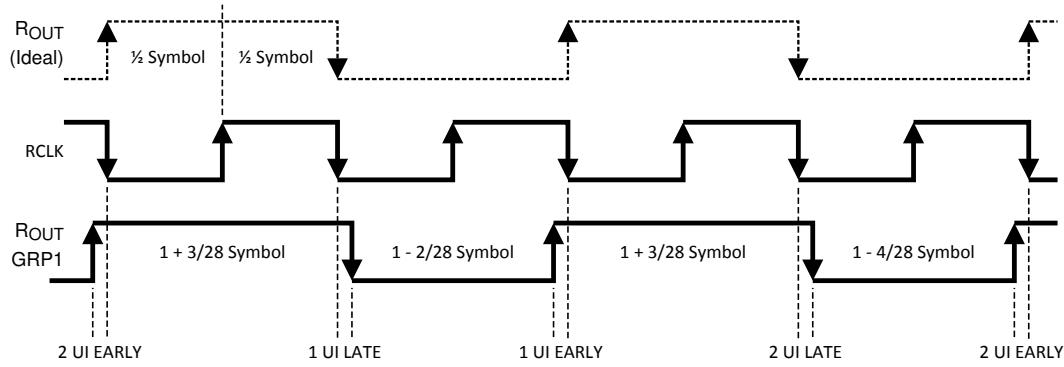

| 49                             | PTOSEL      | LVC MOS_I | プログラッシブ ターンオン動作選択<br>PTO = H: ROUT[23:0] は 8 つずつ 3 つのグループに分類されます。各グループは RCLK に対して約 ±1 UI ~ ±2 UI 離れてスイッチングします。(図 5-15)<br>PTO = L: PTO 拡散モード、ROUT[23:0] 出力は ±1 UI ~ ±2 UI 拡散し、RCLK は ±1 UI 拡散します。(図 5-16) 詳細については、「アプリケーション情報」セクションを参照してください。 |

| 63                             | RAOFF       | LVC MOS_I | ランダマイザ制御入力ピン(詳細については、表 2 を参照)<br>RAOFF = H: DS90C241 シリアルайザと組み合わせて使用するための下位互換モード。<br>RAOFF = L: 追加のランダム化をオン(デフォルト)。2E7 LSFR 設定を選択します。                                                                                                        |

表 4-2. ピンの機能 : PAG パッケージ (続き)

| ピン                          |        | I/O     | 説明                                                                                                                                                                                             |

|-----------------------------|--------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 番号                          | 名称     |         |                                                                                                                                                                                                |

| 60                          | REN    | LVCMS_I | レシーバ データ イネーブル<br>REN = H: R <sub>OUT[23:0]</sub> と RCLK は有効 (オン)。<br>REN = L: R <sub>OUT[23:0]</sub> と RCLK は無効 (オフ)。レシーバ R <sub>OUT[23:0]</sub> および RCLK 出力はトライステート。PLL は動作し続けており、TCLK にロック。 |

| 50                          | RES0   | LVCMS_I | 予約済み。このピンは、Low に接続する必要があります。                                                                                                                                                                   |

| 1~6、<br>17、<br>18、<br>33、34 | RES0   | NC      | 接続なし (オープン)。ピンは、物理的にはダイに接続されていません。ピンをオープンのままにするか、Low に接続することを推奨します。                                                                                                                            |

| 48                          | RPWDNB | LVCMS_I | レシーバ パワー ダウン バー<br>RPWDNB = H: レシーバは有効かつオン<br>RPWDNB = L: レシーバはパワーダウン モード (スリープ)、R <sub>OUT[23:0]</sub> 、RCLK、LOCK はトライステートスタンバイ モードになり、PLL はシャットダウンして消費電力を最小化します。                             |

| 55                          | RRFB   | LVCMS_I | レシーバ クロック エッジ選択ピン<br>RRFB = H: R <sub>OUT</sub> LVCMS 出力は立ち上がりクロック エッジでストロークされます。<br>RRFB = L: R <sub>OUT</sub> LVCMS 出力は立ち下がりクロック エッジでストロークされます。                                              |

| 64                          | SLEW   | LVCMS_I | LVCMS 出力スルーレート制御<br>SLEW = L: 2mA の低駆動出力 (デフォルト)<br>SLEW = H: 4mA の高駆動出力                                                                                                                       |

BIST モード ピン (詳細については、[セクション アプリケーションと実装](#) を参照)

|    |        |         |                                                                                                                                                                                            |

|----|--------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 61 | BISTEN | LVCMS_I | BIST モード イネーブル用制御ピン<br>BISTEN = L: デフォルトは Low。通常モード。<br>BISTEN = H: BIST モードが作動。BISTEN = H かつ DS90UR241 DIN[23:0] = Low またはフローティングの場合、デバイスはそれに応じて BIST モードに移行します。PASS 出力ピンのテストステータスを確認します。 |

| 62 | BISTM  | LVCMS_I | BIST モードの選択。デジタルライザを BIST 報告モードに設定する制御ピン。<br>BISTM = L: デフォルトは Low。サイクルごとのビット エラーに対応したすべての R <sub>OUT</sub> のステータス<br>BISTM = H: 累積ビット エラー数を R <sub>OUT[7:0]</sub> (最大 255 のバイナリ カウント) に表示 |

| 45 | 合格     | LVCMS_O | @Speed BIST テスト動作のためのパス フラグ出力。<br>PASS = L: BIST 失敗<br>PASS = H: BIST を有効化する前に LOCK = H。その後リンク上で $1 \times 10^{-9}$ のエラー レートを達成。                                                           |

LVDS シリアル インターフェイス ピン

|    |                  |        |                                                                                                                           |

|----|------------------|--------|---------------------------------------------------------------------------------------------------------------------------|

| 53 | R <sub>IN+</sub> | LVDS_I | レシーバ LVDS 真 (+) 入力 — この入力は、R <sub>IN+</sub> ピンに対する 100Ω 負荷を接続するように設計されています。相互接続は、100nF のコンデンサを使用してこのピンと AC 結合させる必要があります。  |

| 54 | R <sub>IN-</sub> | LVDS_I | レシーバ LVDS 反転 (-) 入力 — この入力は、R <sub>IN-</sub> ピンに対する 100Ω 負荷を接続するように設計されています。相互接続は、100nF のコンデンサを使用してこのピンと AC 結合させる必要があります。 |

電源 / グランド ピン

|    |     |     |                        |

|----|-----|-----|------------------------|

| 51 | VDD | VDD | アナログ LVDS 電源、電源        |

| 59 | VDD | VDD | アナログ電圧電源、PLL 電源        |

| 57 | VDD | VDD | アナログ電圧電源、PLL VCO 電源    |

| 32 | VDD | VDD | デジタル電圧電源、ロジック電源        |

| 46 | VDD | VDD | デジタル電圧電源、ロジック電源        |

| 40 | VDD | VDD | デジタル電圧電源、LVCMS 出力電源    |

| 26 | VDD | VDD | デジタル電圧電源、LVCMS 出力電源    |

| 11 | VDD | VDD | デジタル電圧電源、LVCMS 出力電力    |

| 52 | VSS | GND | アナログ LVDS グランド         |

| 58 | VSS | GND | アナログ グランド、PLL グランド     |

| 56 | VSS | GND | アナログ グランド、PLL VCO グランド |

**表 4-2. ピンの機能 : PAG パッケージ (続き)**

| ピン |     | I/O | 説明                       |

|----|-----|-----|--------------------------|

| 番号 | 名称  |     |                          |

| 31 | VSS | GND | デジタル グランド、ロジック グランド      |

| 47 | VSS | GND | デジタル グランド、ロジック グランド      |

| 39 | VSS | GND | デジタル グランド、LVC MOS 出力グランド |

| 25 | VSS | GND | デジタル グランド、LVC MOS 出力グランド |

| 12 | VSS | GND | デジタル グランド、LVC MOS 出力グランド |

## 5 仕様

### 5.1 絶対最大定格

自由空気での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                                 |                    |                         | 最小値             | 最大値                     | 単位   |

|---------------------------------|--------------------|-------------------------|-----------------|-------------------------|------|

| 電源電圧 ( $V_{DD}$ )               |                    |                         | -0.3            | 4                       | V    |

| LVC MOS 入力電圧                    |                    |                         | -0.3            | $V_{DD} + 0.3$          | V    |

| LVC MOS の出力電圧                   |                    |                         | -0.3            | $V_{DD} + 0.3$          | V    |

| LVDS レシーバ入力電圧                   |                    |                         | -0.3            | +3.9                    | V    |

| LVDS ドライバ出力電圧                   |                    |                         | -0.3            | +3.9                    | V    |

| LVDS 出力短絡時間                     |                    |                         |                 | 10                      | ms   |

| 接合部温度                           |                    |                         |                 | 150                     | °C   |

| リード温度 (半田付け、4 秒)                |                    |                         |                 | 260                     | °C   |

| 最大パッケージ電力放散能力<br><sup>(2)</sup> | パッケージ<br>ディレーティング: | DS90UR241 – 48L<br>TQFP | $R_{\theta JA}$ | 45.8 (4L),<br>75.4 (2L) | °C/W |

|                                 |                    |                         | $R_{\theta JC}$ | 21.0                    |      |

|                                 |                    | DS90UR124 – 64L<br>TQFP | $R_{\theta JA}$ | 42.8 (4L),<br>67.2 (2L) |      |

|                                 |                    |                         | $R_{\theta JC}$ | 14.6                    |      |

| 保管温度、 $T_{stg}$                 |                    |                         | -65             | 150                     | °C   |

(1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについての話で、絶対最大定格において、またはこのデータシートの「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。絶対最大定格の状態が長時間続くと、デバイスの信頼性に影響を与える可能性があります。

(2)  $1/R_{\theta JA}$  °C/W (+25°C以上)

### 5.2 ESD 定格

|                                |                                             |                                         | 値               | 単位 |

|--------------------------------|---------------------------------------------|-----------------------------------------|-----------------|----|

| <b>PFB パッケージの DS90UR241-Q1</b> |                                             |                                         |                 |    |

| $V_{(ESD)}$ 静電放電               | 人体モデル (HBM)、AEC Q100-002 に準拠 <sup>(1)</sup> | すべてのピン                                  | $\geq \pm 8000$ | V  |

|                                | 荷電デバイス モデル (CDM)、AEC Q100-011 準拠            | コーナー ピン (1, 12, 13, 24, 25, 36, 37, 48) | $\pm 1000$      |    |

|                                |                                             | その他のピン                                  | $\pm 1000$      |    |

|                                | (ISO10605) <sup>(2)</sup>                   | 接触放電 (20, 19)                           | $\pm 10000$     |    |

|                                |                                             | 気中放電 (20, 19)                           | $\pm 30000$     |    |

### PAG パッケージの DS90UR124-Q1

|                  |                                             |                                         |                 |   |

|------------------|---------------------------------------------|-----------------------------------------|-----------------|---|

| $V_{(ESD)}$ 静電放電 | 人体モデル (HBM)、AEC Q100-002 に準拠 <sup>(1)</sup> | すべてのピン                                  | $\geq \pm 8000$ | V |

|                  | 荷電デバイス モデル (CDM)、AEC Q100-011 準拠            | コーナー ピン (1, 16, 17, 32, 33, 48, 49, 64) | $\pm 1000$      |   |

|                  |                                             | その他のピン                                  | $\pm 1000$      |   |

|                  | (ISO10605) <sup>(2)</sup>                   | 接触放電 ( $R_{IN+}, R_{IN-}$ )             | $\pm 10000$     |   |

|                  |                                             | 気中放電 ( $R_{IN+}, R_{IN-}$ )             | $\pm 30000$     |   |

(1) AEC Q100-002 は、ANSI/ESDA/JEDEC JS-001 仕様に従って HBM ストレス試験を実施することを示しています。

(2)  $R_D = 2k\Omega$ 、 $C_S = 330pF$

## 5.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                      | 最小値 | 公称値 | 最大値  | 単位                |

|----------------------|-----|-----|------|-------------------|

| 電源電圧 ( $V_{DD}$ )    | 3.0 | 3.3 | 3.6  | V                 |

| 自由気流での動作温度 ( $T_A$ ) | -40 | 25  | 105  | °C                |

| クロック レート             | 5   |     | 43   | MHz               |

| 電源ノイズ                |     |     | ±100 | mV <sub>P-P</sub> |

## 5.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup>                            | DS90UR124-Q1 | DS90UR241-Q1 | 単位   |

|-------------------------------------------------|--------------|--------------|------|

|                                                 | PAG [TQFP]   | PFB [TQFP]   |      |

|                                                 | 64 ピン        | 48 ピン        |      |

| $R_{\theta JA}$ 接合部から周囲への熱抵抗                    | 58.1         | 64.3         | °C/W |

| $R_{\theta JC(\text{top})}$ 接合部からケース (上面) への熱抵抗 | 13.0         | 14.1         |      |

| $R_{\theta JB}$ 接合部から基板への熱抵抗                    | 30.4         | 30.2         |      |

| $\Psi_{JT}$ 接合部から上面への特性パラメータ                    | 0.3          | 0.4          |      |

| $\Psi_{JB}$ 接合部から基板への特性パラメータ                    | 30.0         | 29.8         |      |

(1) 従来および新しい熱評価基準の詳細については、『IC パッケージの熱評価基準』アプリケーション レポート、[SPRA953](#) を参照してください。

## 5.5 電気的特性

推奨動作電源電圧および温度範囲内 (特に規定のない限り)

| パラメータ                 | テスト条件                                                  | ピン / 周波数                                                                                                                         | 最小値  | 標準値       | 最大値      | 単位      |

|-----------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------|-----------|----------|---------|

| <b>LVCMOS DC 仕様</b>   |                                                        |                                                                                                                                  |      |           |          |         |

| $V_{IH}$ High レベル入力電圧 |                                                        | $Tx: D_{IN}[0:23], TCLK, TPWDNB, DEN, TRFB, RAOFF, VODSEL, RES0.$                                                                | 2    | $V_{DD}$  | V        |         |

| $V_{IL}$ Low レベル入力電圧  |                                                        | $Rx: RPWDNB, RRFB, REN, PTOSEL, BISTEN, BISTM, SLEW, RES0.$                                                                      | GND  | 0.8       | V        |         |

| $V_{CL}$ 入力クランプ電圧     | $I_{CL} = -18mA$                                       | $Tx: D_{IN}[0:23], TCLK, TPWDNB, DEN, TRFB, RAOFF, RES0.$<br>$Rx: RPWDNB, RRFB, REN, PTOSEL, BISTEN, BISTM, SLEW, RES0.$         | -0.8 | -1.5      | V        |         |

| $I_{IN}$ 入力電流         | $V_{IN} = 0V$ または $3.6V$                               | $Tx: D_{IN}[0:23], TCLK, TPWDNB, DEN, TRFB, RAOFF, RES0.$<br>$Rx: RRFB, REN, PTOSEL, BISTEN, BISTM, SLEW, RES0.$<br>$Rx: RPWDNB$ | -10  | $\pm 2$   | 10       | $\mu A$ |

| $V_{OH}$ High レベル出力電圧 | $I_{OH} = -2mA, SLEW = L$<br>$I_{OH} = -4mA, SLEW = H$ |                                                                                                                                  | 2.3  | 3         | $V_{DD}$ | V       |

| $V_{OL}$ Low レベル出力電圧  | $I_{OL} = 2mA, SLEW = L$<br>$I_{OL} = 4mA, SLEW = H$   | $Rx: R_{OUT}[0:23], RCLK, LOCK, PASS.$                                                                                           | GND  | 0.33      | 0.5      | V       |

| $I_{os}$ 出力短絡電流       | $V_{OUT} = 0V$                                         |                                                                                                                                  | -40  | -70       | -110     | $mA$    |

| $I_{oz}$ トライステート出力電流  | $RPWDNB, REN = 0V, V_{OUT} = 0V$ または $V_{DD}$          | $Rx: R_{OUT}[0:23], RCLK, LOCK, PASS.$                                                                                           | -30  | $\pm 0.4$ | 30       | $\mu A$ |

| <b>LVDS の DC 仕様</b>   |                                                        |                                                                                                                                  |      |           |          |         |

## 5.5 電気的特性 (続き)

推奨動作電源電圧および温度範囲内 (特に規定のない限り)

| パラメータ                                              | テスト条件                                                                     | ピン / 周波数                | 最小値       | 標準値       | 最大値  | 単位      |

|----------------------------------------------------|---------------------------------------------------------------------------|-------------------------|-----------|-----------|------|---------|

| $V_{TH}$                                           | $V_{CM} = 1.8V$                                                           | $R_x: R_{IN+}, R_{IN-}$ |           | 50        |      | mV      |

| $V_{TL}$                                           |                                                                           |                         | -50       |           |      | mV      |

| $I_{IN}$<br>入力電流                                   | $V_{IN} = 2.4V, V_{DD} = 3.6V$                                            |                         | $\pm 100$ | $\pm 250$ |      | $\mu A$ |

|                                                    | $V_{IN} = 0V, V_{DD} = 3.6V$                                              |                         | $\pm 100$ | $\pm 250$ |      |         |

| $V_{OD}$<br>出力差動電圧 ( $D_{OUT+}$ ) - ( $D_{OUT-}$ ) | $R_L = 100\Omega$ , プリエンファシスなし 図 5-10                                     | $V_{ODSEL} = L$         | 380       | 500       | 630  | mV      |

|                                                    |                                                                           | $V_{ODSEL} = H$         | 500       | 900       | 1100 |         |

| $\Delta V_{OD}$                                    | $R_L = 100\Omega$ , プリエンファシスなし                                            | $V_{ODSEL} = L$         |           | 1         | 50   | mV      |

| $\Delta V_{OS}$                                    |                                                                           | $V_{ODSEL} = H$         |           | 1         | 1.25 | 1.50    |

| $\Delta V_{OS}$<br>オフセット電圧                         | $R_L = 100\Omega$ , プリエンファシスなし                                            | $V_{ODSEL} = L$         |           | 3         | 50   | mV      |

|                                                    |                                                                           | $V_{ODSEL} = H$         |           | -2        | -5   | -8      |

| $I_{OS}$<br>出力短絡電流                                 | $D_{OUT} = 0V, D_{IN} = H, TPWDNB = 2.4V$                                 | $V_{ODSEL} = L$         | -4.5      | -7.9      | -14  |         |

|                                                    |                                                                           | $V_{ODSEL} = H$         |           |           |      |         |

| $I_{OZ}$<br>トライステート出力電流                            | $TPWDNB = 0V, D_{OUT} = 0V$ または $V_{DD}$                                  |                         | -15       | $\pm 1$   | 15   | $\mu A$ |

|                                                    | $TPWDNB = 2.4V, DEN = 0V$<br>$D_{OUT} = 0V$ または $V_{DD}$                  |                         | -15       | $\pm 1$   | 15   |         |

|                                                    | $TPWDNB = 2.4V, DEN = 2.4V, D_{OUT} = 0V$ または $V_{DD}$<br>ロックなし (TCLK なし) |                         | -15       | $\pm 1$   | 15   |         |

### SER/DES 電源電流 (DVDD\*、PVDD\*、AVDD\* ピン) \* デジタル、PLL、アナログ VDD

|                                            |                                                                     |                                                                |    |     |         |

|--------------------------------------------|---------------------------------------------------------------------|----------------------------------------------------------------|----|-----|---------|

| $I_{DDT}$<br>シリアライザ<br>総消費電流<br>(負荷電流を含む)  | $R_L = 100\Omega, PRE = 12k\Omega, RAOFF = H, VODSEL = L$           |                                                                | 65 | 90  | $mA$    |

|                                            | $R_L = 100\Omega, PRE = \text{オフ}, RAOFF = H, VODSEL = H$           | $f = 43MHz, \text{ランダムパター} \text{ 図 5-2}$                      | 66 | 90  |         |

|                                            |                                                                     |                                                                |    |     |         |

| $I_{DDTZ}$<br>シリアライザ<br>電源電流パワーダウン         | $TPWDNB = 0V$<br>(その他のすべての LVCMOS 入力 = 0V)                          |                                                                |    | 45  | $\mu A$ |

| $I_{DDR}$<br>デシリアライザ<br>総電源電流<br>(負荷電流を含む) | $C_L = 4pF, SLEW = H$                                               | $f = 43MHz, \text{チェックカードパター} \text{ LVCMOS 出力} \text{ 図 5-2}$ | 85 | 105 | $mA$    |

|                                            | $C_L = 4pF, SLEW = H$                                               | $f = 43MHz, \text{ランダムパター} \text{ LVCMOS 出力}$                  | 80 | 100 |         |

| $I_{DDRZ}$<br>デシリアライザ<br>電源電流パワーダウン        | $RPWDNB = 0V$<br>(その他のすべての LVCMOS 入力 = 0V, $R_{IN+}/R_{IN-} = 0V$ ) |                                                                |    | 50  | $\mu A$ |

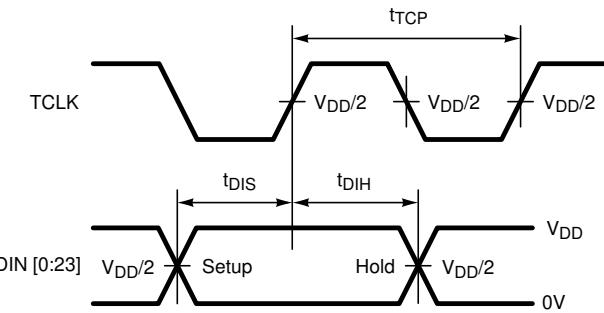

## 5.6 シリアライザの TCLK の入力タイミング要件

推奨動作電源電圧および温度範囲内 (特に規定のない限り)

|            |                |                    | 最小値   | 公称値  | 最大値       | 単位 |

|------------|----------------|--------------------|-------|------|-----------|----|

| $t_{TCP}$  | 送信クロック周期       | 図 5-5              | 23.25 | T    | 200       | ns |

| $t_{TCIH}$ | 送信クロック High 時間 |                    | 0.3T  | 0.5T | 0.7T      | ns |

| $t_{TCIL}$ | 送信クロック Low 時間  |                    | 0.3T  | 0.5T | 0.7T      | ns |

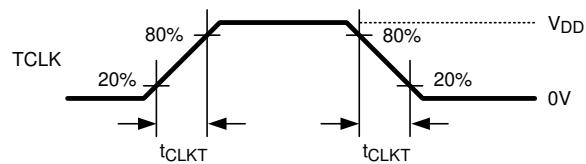

| $t_{CLKT}$ | TCLK 入力遷移時間    | 図 5-4              |       | 2.5  |           | ns |

| $t_{JIT}$  | TCLK 入力ジッタ     | $f = 43\text{MHz}$ |       |      | $\pm 100$ | ps |

|            |                | $f = 33\text{MHz}$ |       |      | $\pm 130$ |    |

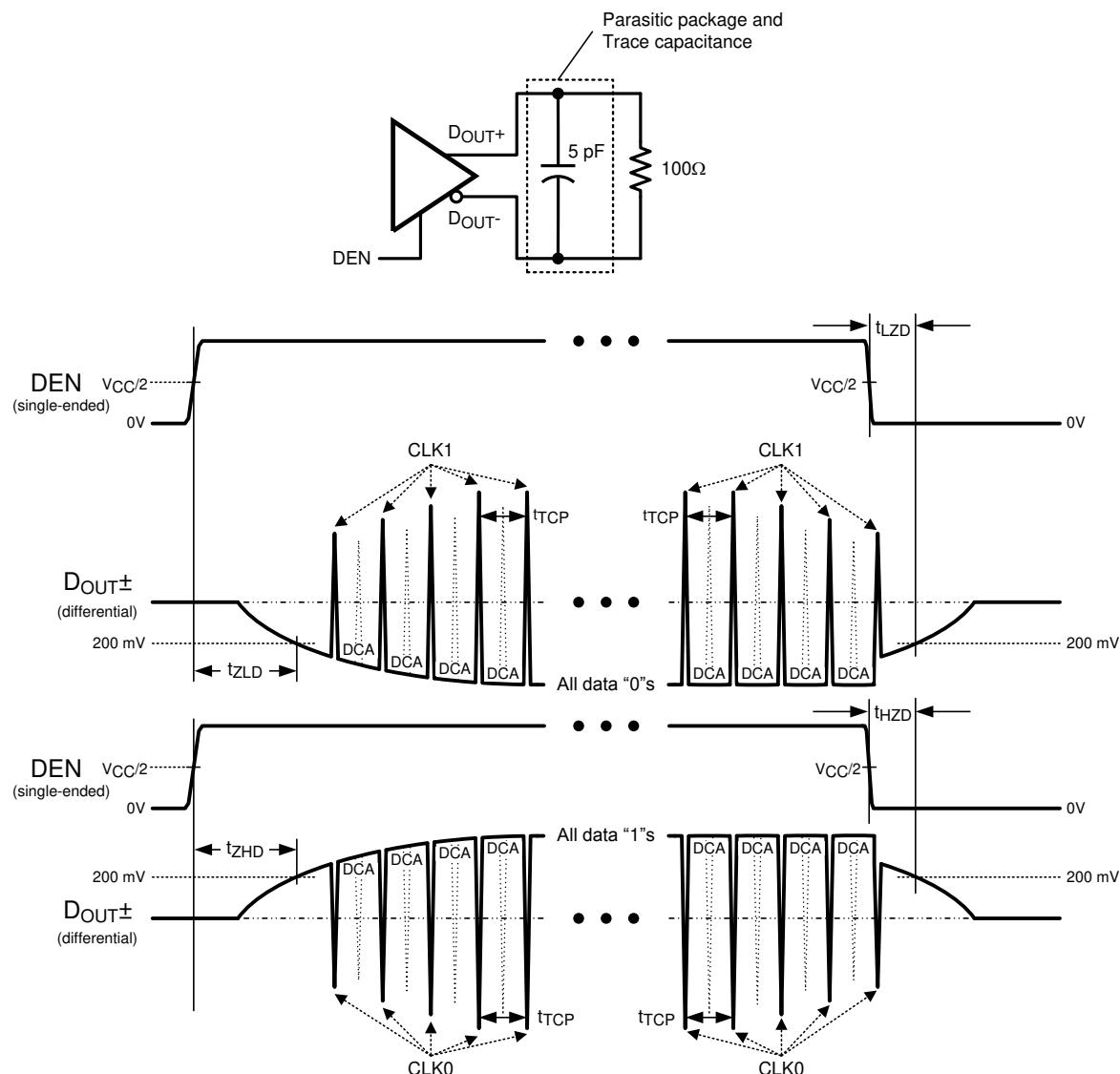

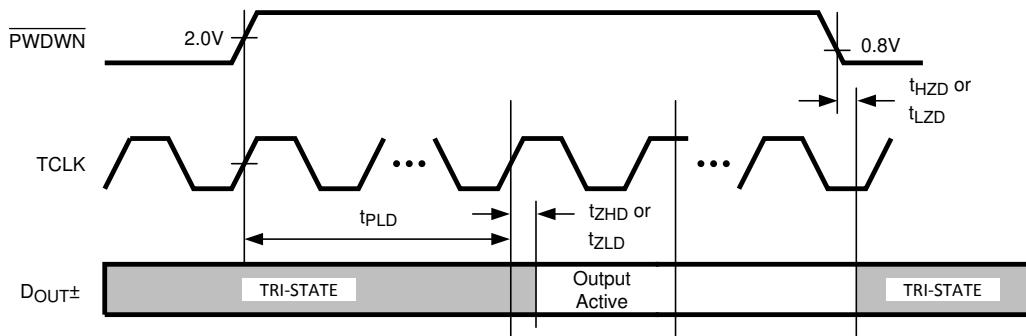

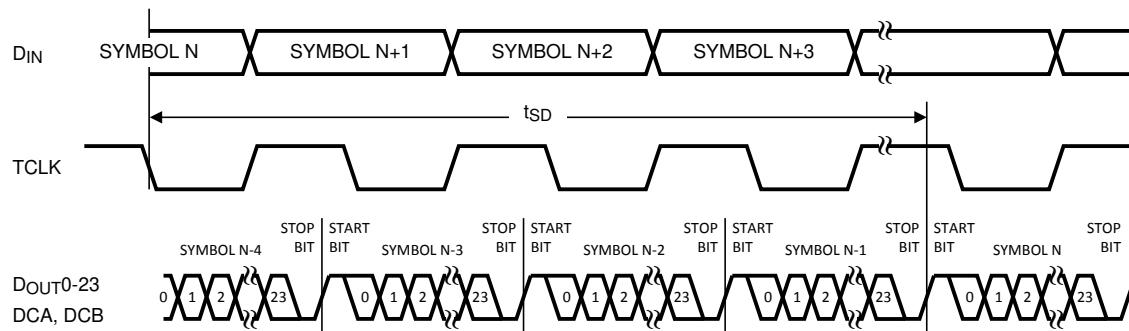

## 5.7 シリアライザのスイッチング特性

推奨動作電源電圧および温度範囲内 (特に規定のない限り)

| パラメータ       | テスト条件                                                                | 最小値                                                                                  | 標準値    | 最大値     | 単位 |

|-------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------|---------|----|

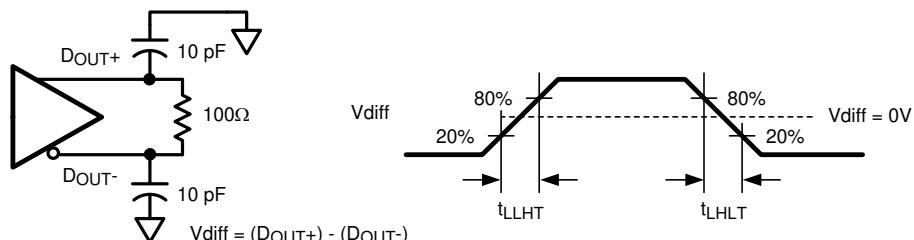

| $t_{LLHT}$  | $R_L = 100\Omega$ , VODSEL = L、GNDとの間に $C_L = 10\text{pF}$ を接続、図 5-3 | 245                                                                                  | 550    |         | ps |

| $t_{LHLT}$  |                                                                      | 264                                                                                  | 550    |         | ps |

| $t_{DIS}$   | $R_L = 100\Omega$ , GNDとの間に $C_L = 10\text{pF}$ を接続、図 5-5            | 4                                                                                    |        |         | ns |

| $t_{DIH}$   |                                                                      | 4                                                                                    |        |         | ns |

| $t_{HZD}$   | $D_{OUT\pm}$ の High からトライステートまでの遅延                                   |                                                                                      | 10     | 15      | ns |

| $t_{LZD}$   | $D_{OUT\pm}$ の Low からトライステートまでの遅延                                    |                                                                                      | 10     | 15      | ns |

| $t_{ZHD}$   | $D_{OUT\pm}$ のトライステートから High までの遅延                                   |                                                                                      | 75     | 150     | ns |

| $t_{ZLD}$   | $D_{OUT\pm}$ のトライステートから Low までの遅延                                    |                                                                                      | 75     | 150     | ns |

| $t_{PLD}$   | シリアルライザの PLL ロック時間                                                   |                                                                                      |        | 10      | ms |

| $t_{SD}$    | シリアルライザの遅延                                                           | $R_L = 100\Omega$ , PRE = オフ、RAOFF = L, TRFB = H、図 5-8                               | 3.5T+2 | 3.5T+10 | ns |

|             |                                                                      | $R_L = 100\Omega$ , PRE = オフ、RAOFF = L, TRFB = L、図 5-8                               | 3.5T+2 | 3.5T+10 |    |

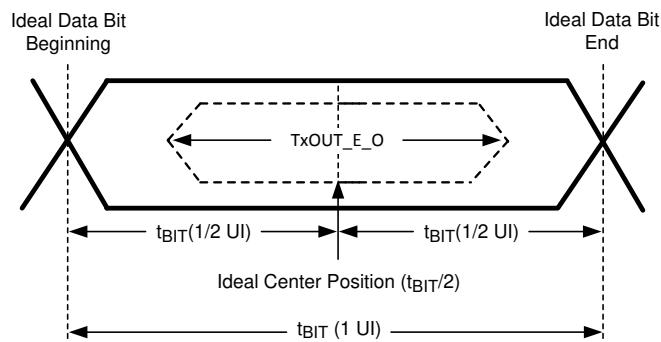

| $TxOUT_E_O$ | $TxOUT\_Eye\_Opening$ 。<br>(tBIT/2)を中心とする $TxOUT_E_O$                | 5MHz~43MHz、<br>$R_L = 100\Omega$ , GNDとの間に $C_L = 10\text{pF}$ を接続、ランダムパターン<br>図 5-9 | 0.76   | 0.84    | UI |

## 5.8 デシリアルライザのスイッチング特性

推奨動作電源電圧および温度範囲内 (特に規定のない限り)

| パラメータ     | テスト条件                     | ピン / 周波数                         | 最小値    | 標準値   | 最大値 | 単位  |

|-----------|---------------------------|----------------------------------|--------|-------|-----|-----|

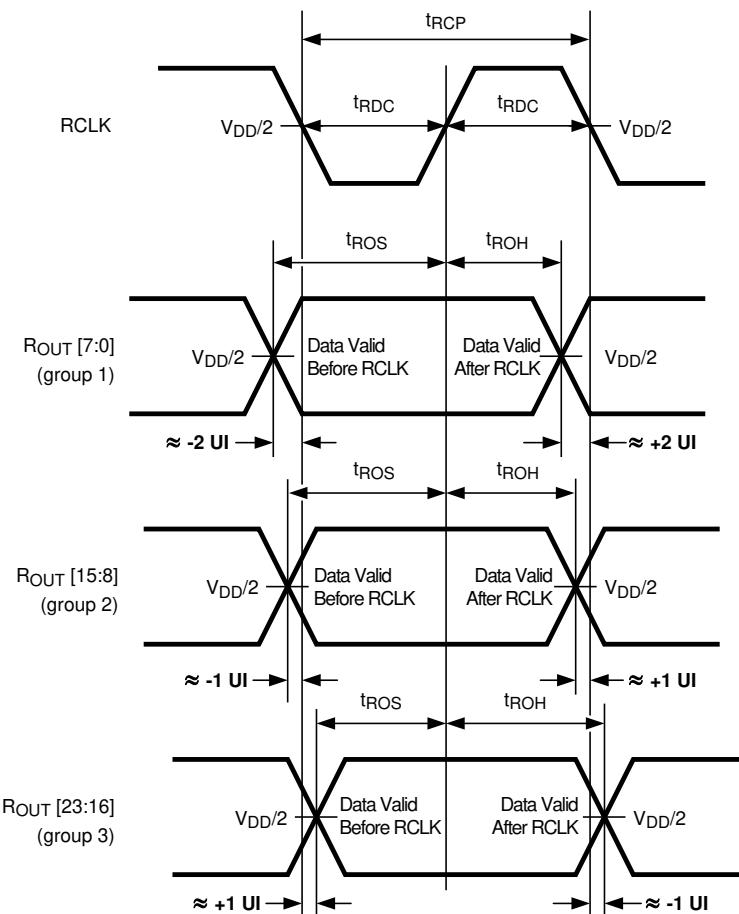

| $t_{RCP}$ | Receiver out Clock Period | $t_{RCP} = t_{TCP}$ , PTOSEL = H | RCLK   | 23.25 | T   | 200 |

| $t_{RDC}$ | RCLK Duty Cycle           | PTOSEL = H, SLEW = L             | 図 5-15 | 45%   | 50% | 55% |

## 5.8 デシリアライザのスイッチング特性(続き)

推奨動作電源電圧および温度範囲内(特に規定のない限り)

| パラメータ                                                          | テスト条件                                                                                | ピン / 周波数                                                | 最小値                                                                               | 標準値                          | 最大値 | 単位 |

|----------------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------|------------------------------|-----|----|

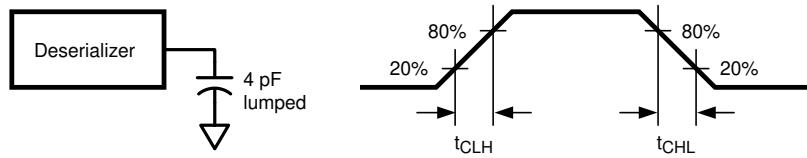

| $t_{CLH}$ LVCMOS Low-to-High Transition Time                   | $C_L = 4\text{pF}$<br>(集中負荷)、<br>$\text{SLEW} = \text{H}$                            | $R_{\text{OUT}} [0:23]$ 、<br>$\text{RCLK}, \text{LOCK}$ |                                                                                   | 1.5                          | 2.5 | ns |

| $t_{CHL}$ LVCMOS High-to-Low Transition Time                   |                                                                                      |                                                         |                                                                                   | 1.5                          | 2.5 | ns |

| $t_{CLH}$ LVCMOS Low-to-High Transition Time                   | $C_L = 4\text{pF}$<br>(集中負荷)、<br>$\text{SLEW} = \text{L}$                            | $R_{\text{OUT}} [0:23]$ 、<br>$\text{RCLK}, \text{LOCK}$ |                                                                                   | 2.0                          | 3.5 | ns |

| $t_{CHL}$ LVCMOS High-to-Low Transition Time                   |                                                                                      |                                                         |                                                                                   | 2.0                          | 3.5 | ns |

| $t_{ROS}$ $R_{\text{OUT}}$ (0:7) Setup Data to RCLK (グループ 1)   | $\text{PTOSEL} = \text{L}$ 、<br>$\text{SLEW} = \text{H}$ 、<br><a href="#">図 5-16</a> | $R_{\text{OUT}} [0:7]$                                  | $(0.35) \times \frac{(0.5 \times t_{\text{RCP}})}{t_{\text{RCP}}} - 3 \text{ UI}$ |                              |     | ns |

| $t_{ROH}$ $R_{\text{OUT}}$ (0:7) Hold Data to RCLK (グループ 1)    |                                                                                      |                                                         | $(0.35) \times \frac{(0.5 \times t_{\text{RCP}})}{t_{\text{RCP}}} - 3 \text{ UI}$ |                              |     | ns |

| $t_{ROS}$ $R_{\text{OUT}}$ (8:15) Setup Data to RCLK (グループ 2)  | $\text{PTOSEL} = \text{L}$ 、<br>$\text{SLEW} = \text{H}$ 、<br><a href="#">図 5-16</a> | $R_{\text{OUT}} [8:15]$ 、<br>$\text{LOCK}$              | $(0.35) \times \frac{(0.5 \times t_{\text{RCP}})}{t_{\text{RCP}}} - 3 \text{ UI}$ |                              |     | ns |

| $t_{ROH}$ $R_{\text{OUT}}$ (8:15) Hold Data to RCLK (グループ 2)   |                                                                                      |                                                         | $(0.35) \times \frac{(0.5 \times t_{\text{RCP}})}{t_{\text{RCP}}} - 3 \text{ UI}$ |                              |     | ns |

| $t_{ROS}$ $R_{\text{OUT}}$ (16:23) Setup Data to RCLK (グループ 3) |                                                                                      | $R_{\text{OUT}} [16:23]$                                | $(0.35) \times \frac{(0.5 \times t_{\text{RCP}})}{t_{\text{RCP}}} - 3 \text{ UI}$ |                              |     | ns |

| $t_{ROH}$ $R_{\text{OUT}}$ (16:23) Hold Data to RCLK (グループ 3)  |                                                                                      |                                                         | $(0.35) \times \frac{(0.5 \times t_{\text{RCP}})}{t_{\text{RCP}}} - 3 \text{ UI}$ |                              |     | ns |

| $t_{ROS}$ $R_{\text{OUT}}$ (0:7) Setup Data to RCLK (グループ 1)   | $\text{PTOSEL} = \text{H}$ 、<br>$\text{SLEW} = \text{H}$ 、<br><a href="#">図 5-15</a> | $R_{\text{OUT}} [0:7]$                                  | $(0.35) \times \frac{(0.5 \times t_{\text{RCP}})}{t_{\text{RCP}}} - 2 \text{ UI}$ |                              |     | ns |

| $t_{ROH}$ $R_{\text{OUT}}$ (0:7) Hold Data to RCLK (グループ 1)    |                                                                                      |                                                         | $(0.35) \times \frac{(0.5 \times t_{\text{RCP}})}{t_{\text{RCP}}} + 2 \text{ UI}$ |                              |     | ns |

| $t_{ROS}$ $R_{\text{OUT}}$ (8:15) Setup Data to RCLK (グループ 2)  |                                                                                      | $R_{\text{OUT}} [8:15]$ 、<br>$\text{LOCK}$              | $(0.35) \times \frac{(0.5 \times t_{\text{RCP}})}{t_{\text{RCP}}} + 1 \text{ UI}$ |                              |     | ns |

| $t_{ROH}$ $R_{\text{OUT}}$ (8:15) Hold Data to RCLK (グループ 2)   |                                                                                      |                                                         | $(0.35) \times \frac{(0.5 \times t_{\text{RCP}})}{t_{\text{RCP}}} + 1 \text{ UI}$ |                              |     | ns |

| $t_{ROS}$ $R_{\text{OUT}}$ (16:23) Setup Data to RCLK (グループ 3) |                                                                                      | $R_{\text{OUT}} [16:23]$                                | $(0.35) \times \frac{(0.5 \times t_{\text{RCP}})}{t_{\text{RCP}}} + 1 \text{ UI}$ |                              |     | ns |

| $t_{ROH}$ $R_{\text{OUT}}$ (16:23) Hold Data to RCLK (グループ 3)  |                                                                                      |                                                         | $(0.35) \times \frac{(0.5 \times t_{\text{RCP}})}{t_{\text{RCP}}} + 1 \text{ UI}$ |                              |     | ns |

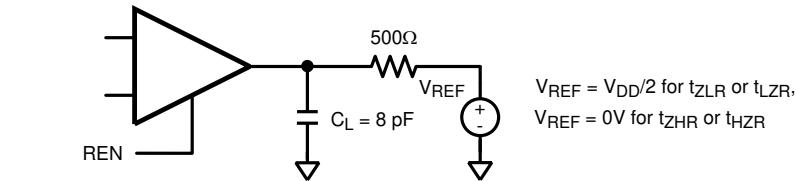

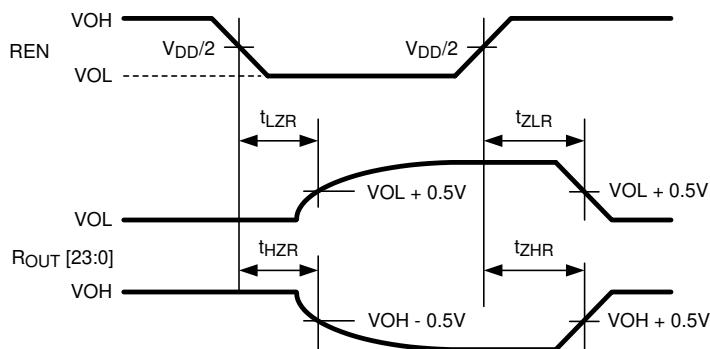

| $t_{HZR}$ HIGH to Tri-state Delay                              | $\text{PTOSEL} = \text{H}$ 、<br><a href="#">図 5-14</a>                               | $R_{\text{OUT}} [0:23]$ 、<br>$\text{RCLK}, \text{LOCK}$ |                                                                                   | 3                            | 10  | ns |

| $t_{LZR}$ LOW to Tri-state Delay                               |                                                                                      |                                                         |                                                                                   | 3                            | 10  | ns |

| $t_{ZHR}$ Tri-state to HIGH Delay                              |                                                                                      |                                                         |                                                                                   | 3                            | 10  | ns |

| $t_{ZLR}$ Tri-state to LOW Delay                               |                                                                                      |                                                         |                                                                                   | 3                            | 10  | ns |

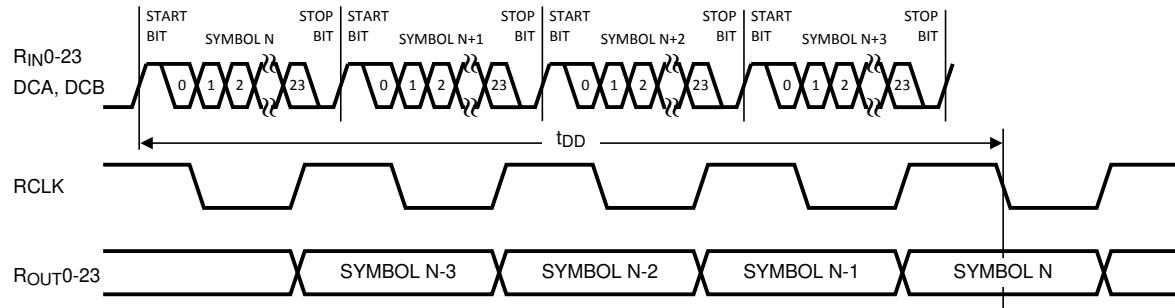

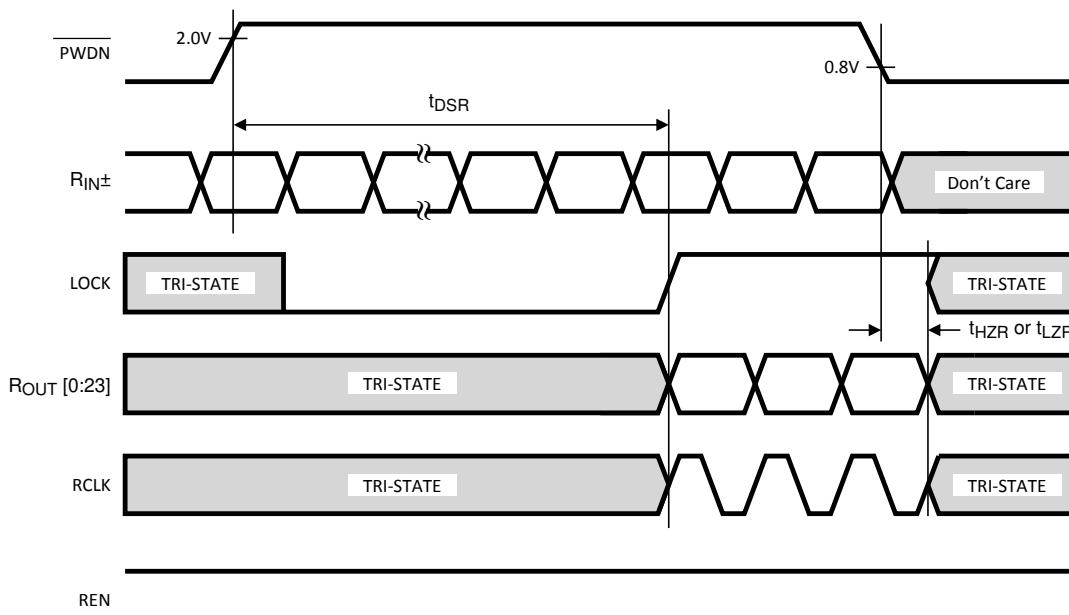

| $t_{DD}$ Deserializer Delay                                    | $\text{PTOSEL} = \text{H}$ 、<br><a href="#">図 5-12</a>                               | $\text{RCLK}$                                           | $[5 + (5/56)] \text{ T} + 3.7$                                                    | $[5 + (5/56)] \text{ T} + 8$ |     | ns |

| $t_{DSR}$ Deserializer PLL Lock Time from Powerdown            | <a href="#">図 5-14</a> を参照                                                           | 5 MHz                                                   |                                                                                   | 128k*T                       |     | ms |

|                                                                |                                                                                      | 43 MHz                                                  |                                                                                   | 128k*T                       |     |    |

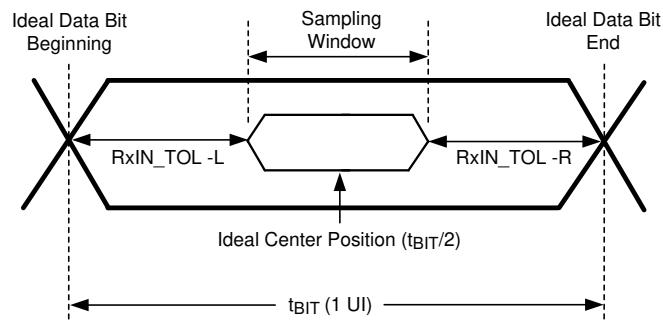

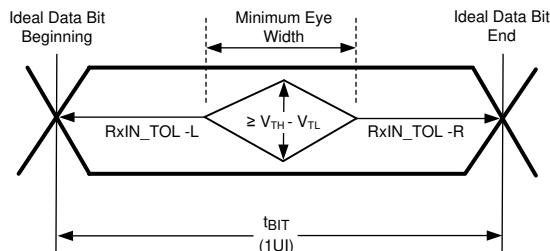

| $R_{\text{IN\_T}}$ Receiver INput TOLerance Left<br>OL-L       | <a href="#">図 5-17</a> を参照                                                           | 5MHz~43MHz                                              |                                                                                   | 0.25                         |     | UI |

| $R_{\text{IN\_T}}$ Receiver INput TOLerance Right<br>OL-R      | <a href="#">図 5-17</a> を参照                                                           | 5MHz~43MHz                                              |                                                                                   | 0.25                         |     | UI |

Device Pin Name      Signal Pattern

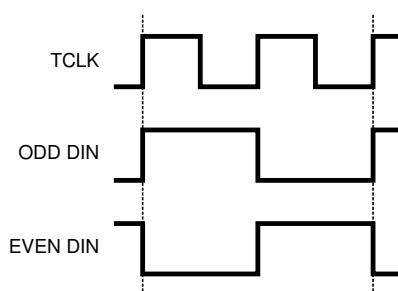

図 5-1. シリアライザ入力チェックボード パターン

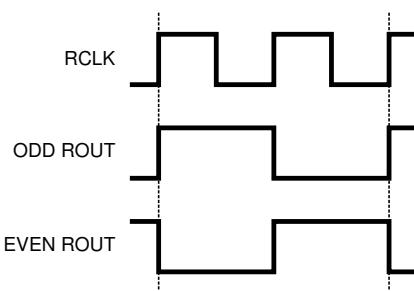

Device Pin Name      Signal Pattern

図 5-2. デシリアルライザ出力チェックボード パターン

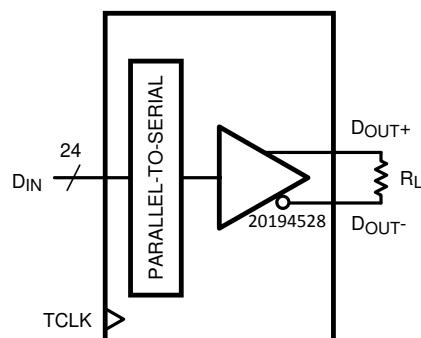

図 5-3. シリアライザの LVDS 出力負荷および遷移時間

図 5-4. シリアライザの入力クロック遷移時間

図 5-5. シリアライザのセットアップおよびホールド時間

図 5-6. シリアライザのトライステート テスト回路および遅延

図 5-7. シリアライザの PLL ロック時間、TPWDNB トライステート遅延

図 5-8. シリアライザの遅延

図 5-9. トランスマッタの出力アイ開口 (TxOUT\_E\_O)

$$VOD = (D_{OUT+}) - (D_{OUT-})$$

差動出力信号は、データ転送モードのデバイスの ( $D_{OUT+}$ ) - ( $D_{OUT-}$ ) として示されます。

図 5-10. シリアライザの  $V_{OD}$  図

図 5-11. シリアライザの LVC MOS 出力負荷および遷移時間

図 5-12. デシリアライザの遅延

NOTE:

$C_L$  includes instrumentation and fixture capacitance within 6 cm of  $R_{OUT}$  [23:0].

図 5-13. デシリアライザのトライステート テスト回路およびタイミング

図 5-14. デシリアライザの PLL ロック時間と RPWDNB トライステート遅延

図 5-15. デシリアライザのセットアップおよびホールド時間と PTO (PTOSEL = H)

グループ 1 は、「2UI 前、1UI 後、1UI 前、2UI 後」のシーケンスによって内部的にラッチされます。

グループ 2 は、「1UI 後、1UI 前、2UI 後、2UI 前」のシーケンスによって内部的にラッチされます。

グループ 3 は、「1UI 前、2UI 後、2UI 前、1UI 後」のシーケンスによって内部的にラッチされます。

図 5-16. デシリアライザのセットアップおよびホールド時間と PTO 拡張 (PTOSEL = L)

RxIN\_TOL\_L は、図の左側の理想的な (理想値を基準とした) ノイズ マージンです。

RxIN\_TOL\_R は、図の右側の理想的な (理想値を基準とした) ノイズ マージンです。

図 5-17. レシーバ入力の許容誤差 (RxIN\_TOL) とサンプリング ウィンドウ

## 5.9 代表的特性

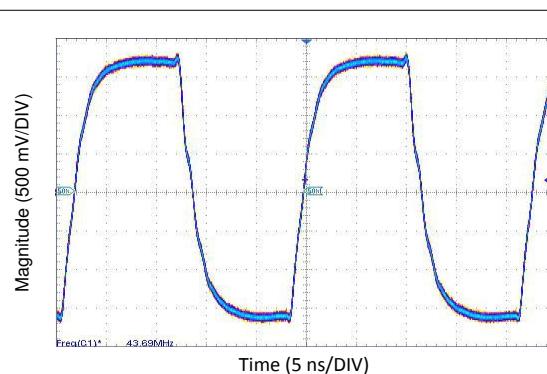

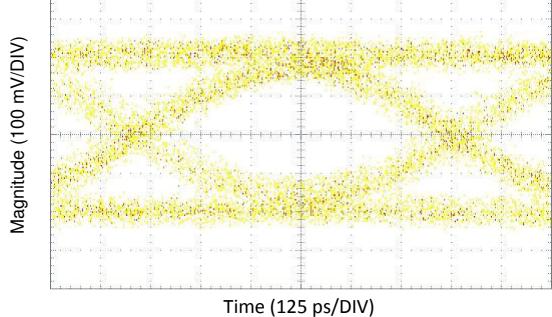

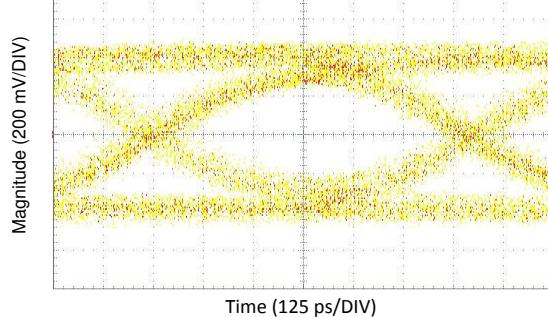

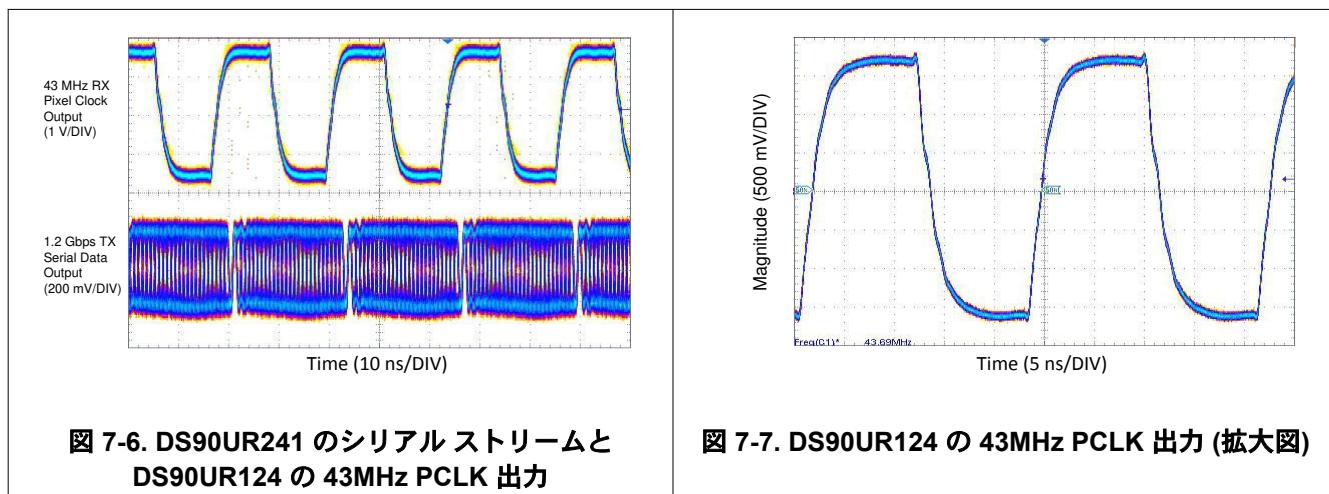

図 5-18. DS90UR241 の DOUT $\pm$  (PCLK = 43MHz、

RIN $\pm$  終端で測定)

図 5-19. DS90UR124 の PCLK 出力 (43MHz)

## 6 詳細説明

### 6.1 概要

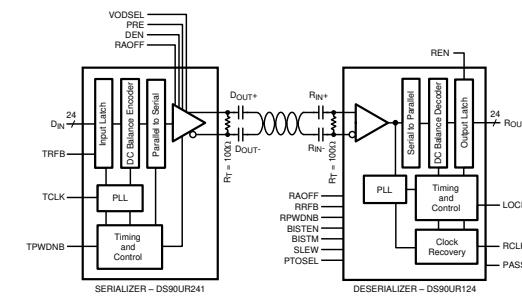

DS90UR241 シリアライザおよび DS90UR124 デシリアライザ チップセットは、120Mbps～1.03Gbps のスループットの 1 つのシリアル LVDS リンク上で 24 ビットパラレル LVC MOS データを転送する、使いやすいトランシッタ / レシーバ ベアです。DS90UR241 は、24 ビット幅のパラレル LVC MOS データを 1 つの埋め込みクロック方式高速 LVDS シリアルデータストリームに変換し、AC 結合に対応するため、そのデータを暗号化 / DC 平衡化します。DS90UR124 は LVDS シリアルデータストリームを受信し、元の 24 ビット幅パラレルデータと復元クロックに変換します。この 24 ビットシリアルライザ / デシリアルライザ チップセットは、シールド付きツイストペア (STP) を使って、5MHz～43MHz のクロック速度でデータを最大 10m まで送信するように設計されています。

デシリアルライザは、独立した基準クロック源を使わずにデータストリームにロックできるため、システムの複雑性と全体のコストを大幅に低減できます。デシリアルライザは、データパターンに関係なくシリアルライザと同期し、真の自動「プラグ アンド ロック」性能を提供します。デシリアルライザは、特別なトレーニング パターンも同期文字も使わずに、入力シリアルストリームにロックします。デシリアルライザは、入力データストリームから埋め込みクロック情報を抽出し、データの整合性を検証することで、クロックとデータを復元します。そして、データをデシリアルライズします。デシリアルライザは、クロック情報を監視し、ロック状態を判定し、ロックが発生すると LOCK 出力を High にアサートします。

また、デシリアルライザはオプションの @SPEED BIST (組み込みセルフ テスト) モード、BIST エラー フラグ、LOCK 状態報告ピンもサポートしています。ビット幅が広いパラレル出力の信号品質は、ノイズとシステム EMI を低減するため、SLEW 制御とバンクスルー (PTOSEL) 入力によって制御されます。各種アプリケーションで高い効率で動作できるように、各デバイスはパワーダウン制御機能を備えています。

### 6.2 機能ブロック図

### 6.3 機能説明

#### 6.3.1 初期化およびロック機能

DS90UR241 と DS90UR124 の初期化は、各デバイスがデータを送受信する前に確立している必要があります。初期化とは、シリアルライザの PLL とデシリアルライザの PLL を互いに同期させることを指します。シリアルライザが入力クロック源にロックした後、第 2 の (最後の) 初期化ステップとしてデシリアルライザはシリアルライザに同期します。

ステップ 1: シリアルライザとデシリアルライザの両方に  $V_{DD}$  を印加すると、それぞれの出力はトライステートに保持され、オンチップのパワーオン回路によって内部回路は無効化されます。 $V_{DD}$  が  $V_{DD\ OK}$  (約 2.2V) に達すると、シリアルライザの PLL はクロック入力に対するロック動作を開始します。シリアルライザの場合、ローカルクロックは送信クロック (TCLK) です。PLL が TCLK にロックする間、シリアルライザ出力はトライステートに保持されます。TCLK へのロックの後、シリアルライザ ブロックはデータパターンを送信することができます。シリアルデータストリームの埋め込みクロック情報に PLL がロックする間、

デシリアルライザ出力はトライステートに維持されます。また、**RIN<sub>±</sub>** ピンの入力データと同期パターンに PLL がロックするまで、デシリアルライザの **LOCK** 出力は **Low** に維持されます。

ステップ 2: シリアルライザが特別なパターンを送信しなくとも、デシリアルライザ PLL はデータストリームに対するロックを獲得します。デシリアルライザへのストリームを生成するシリアルライザは、このステップ（初期化状態）中に、ランダム（非反復）データパターンを自動的に送信します。デシリアルライザは、規定された時間内に埋め込みクロックにロックします。埋め込みクロックおよびデータリカバリ（CDR）回路は、高速受信ビットクロックを回復し、入力データをリタイミングするため、入力ビットストリームにロックします。CDR 回路には、符号化された入力ビットストリームが入力されます。シリアルライザからのランダムなデータストリームにロックするため、デシリアルライザは、立ち上がりクロックのエッジを識別するための一連の動作を実行し、データの整合性を検証し、そのストリームにロックします。このロック手順はデータパターンとは無関係であるため、総ランダムロック時間は変動する可能性があります。デシリアルライザの CDR が埋め込みクロックにロックした時点で、**LOCK** ピンが **High** になり、有効な **RCLK / データ** が output に現れます。**LOCK** 信号は、出力に現れる有効なデータと同期していることに注意します。デシリアルライザの **LOCK** ピンは、レシーバ側でデータの整合性が確立したことを確認する便利な方法です。

### 6.3.2 データ転送

シリアルライザのロックが確立された後、入力 **DIN0~DIN23** を使ってシリアルライザにデータが入力されます。データは、**TCLK** 入力にクロック同期してシリアルライザに入力されます。データをストロープするために使われる **TCLK** のエッジは、**TRFB** ピンで選択できます。**TRFB** を **High** にすると、クロッキングデータの立ち上がりエッジが選択され、**Low** にすると、立ち下がりエッジが選択されます。シリアルライザ出力 (**DOUT<sub>±</sub>**) はポイントツー ポイント接続の駆動を目的としています。

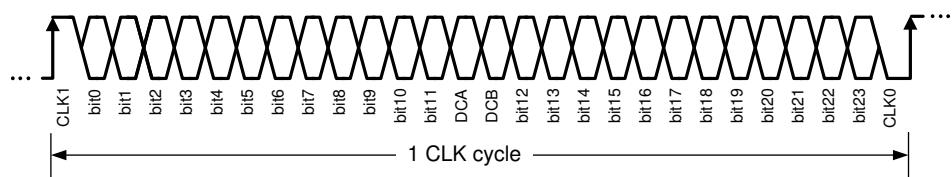

**CLK1**、**CLK0**、**DCA**、**DCB** は、1 つの LVDS シリアルデータストリームと一緒に送信される 4 つのオーバーヘッドビットです（図 7-9）。**CLK1** ビットは常に **High** であり、**CLK0** ビットは常に **Low** です。**CLK1** および **CLK0** ビットは、シリアルストリームの埋め込みクロックビットとして機能します。**DCB** は DC バランス制御ビットとして機能し、送信側でのデータの事前コーディングは不要です。この DC バランスビットは、信号ラインの短期および長期 DC バイアスを最小化するために使用されます。このビットは、データを変更しないで、またはデータを反転して、選択的に送信することで機能します。**DCA** ビットは、埋め込みデータストリームのデータの整合性を検証するために使用されます。**DCA** と **DCB** の両方のコーディング方式は統合されており、シリアルライザとデシリアルライザの中で自動的に実行されます。

本チップセットは 5MHz ~ 43MHz のクロック周波数範囲をサポートしています。クロックサイクルごとに、24 のデータビットと 4 つの追加オーバーヘッド制御ビットが送信されます。そのため、ラインレートは最大 1.20Gbps (最小 140Mbps) に達します。リンクは 86% (24/28) と非常に高効率です。25 (24 データ + 1 クロック) の信号とそれに関連するグランド信号は、1 つの LVDS ペアのみにまとめられ、25 対 1 を上回る圧縮率が実現されます。

シリアルデータストリーム内のデータ / 埋め込みクロックおよび制御ビット (24 + 4 ビット) は **TCLK** 周波数の 28 倍の周波数でシリアルライザデータ出力 (**DOUT<sub>±</sub>**) から送信されます。たとえば、**TCLK** が 43MHz の場合、シリアルレートは  $43 \times 28 = 1.20$  ギガビット/秒となります。入力データから供給されるのは 24 ビットのみであるため、シリアル「ペイロード」レートは **TCLK** 周波数の 24 倍です。たとえば、**TCLK = 43MHz** の場合、ペイロードデータレートは  $43 \times 24 = 1.03$ Gbps となります。**TCLK** はデータ源から供給され、5MHz~43MHz (公称値) の範囲内である必要があります。シリアルライザ出力 (**DOUT<sub>±</sub>**) はポイントツー ポイント接続を駆動できます（図 7-8 を参照）。イネーブル ピン (**DEN**) を **High** かつ **TPWDNB** を **High** にすると、出力はデータを送信します。**DEN** ピンを **Low** に駆動すると、出力がトライステート状態になります。

デシリアルライザチャネルがシリアルライザからの入力にロックすると、デシリアルライザは **LOCK** ピンを **High** に駆動し、有効なデータと復元クロックを同期的に出力に提供します。デシリアルライザは埋め込みクロックにロックし、それを使用して複数の内部データストロープを生成した後、復元クロックで **RCLK** ピンを駆動します。復元クロック (**RCLK** 出力ピン) は **ROUT[23:0]** ピンのデータと同期しています。**LOCK** が **High** の間、**ROUT[23:0]** のデータは有効です。それ以外の場合、**ROUT[23:0]** は無効です。**RCLK** のエッジの極性は **RRFB** 入力によって制御されます。**ROUT[23:0]**、**LOCK**、**RCLK** 出力はそれぞれ 43MHz クロックで最大 4pF の負荷を駆動します。**REN** は、デシリアルライザの **ROUTn** と **RCLK** ピンのトライステート状態を制御します。

### 6.3.3 再同期

デシリアルライザは、ロックを失うと、自動的にロックの再確立を試みます。たとえば、埋め込みクロック エッジが 1 度でも連続して検出されないと、PLL はロックを失い、LOCK ピンが Low に駆動されます。その後、デシリアルライザは動作モードに移行します。動作モードでは、デシリアルライザはランダムなデータストリームにロックしようと試みます。デシリアルライザは埋め込みクロック エッジを探し、識別し、ロック プロセスを開始します。

LOCK 信号のロジック状態は、ROUT のデータが有効かどうかを示します (High の場合、データは有効です)。システムは LOCK ピンを監視することで、ROUT のデータが有効かどうかを判断できます。

### 6.3.4 パワーダウン

パワーダウン状態は、データが転送されていないときに、シリアルライザとデシリアルライザが電力を低減するために使用できる低消費電力のスリープ モードです。TPWDNB と RPWDNB は、消費電流を  $\mu\text{A}$  レンジに低減するパワーダウン モードに、各デバイスを設定するために使われます。TPWDNB ピンが Low に駆動されると、シリアルライザはパワーダウンに入ります。パワーダウン中、PLL は停止し、出力はトライステート状態になるため、負荷電流は流れず、消費電流が減少します。パワーダウンを終了するには、TPWDNB が High に駆動される必要があります。シリアルライザがパワーダウンを終了する際、シリアルライザの PLL が初期化状態に入る前に、シリアルライザの PLL は TCLK にロックする必要があります。次に、データ転送が始まる前に、システムは初期化のための時間を確保する必要があります。RPWDNB が Low に駆動されると、デシリアルライザはパワーダウン モードに入ります。パワーダウン モード中、PLL は停止し、出力はトライステート状態になります。デシリアルライザ ブロックをパワーダウン状態から復帰させるため、システムは RPWDNB を High に駆動します。

データを転送できるようになるには、シリアルライザとデシリアルライザの両方が再初期化および再ロックする必要があります。デシリアルライザは埋め込みクロックにロックすると、初期化を実行し、LOCK High をアサートします。

### 6.3.5 トライステート

シリアルライザの場合、DEN ピンまたは TPWDNB ピンを Low に駆動すると、トライステート状態に入れます。これにより、ドライバ出力ピン (DOUT+ および DOUT-) はどちらもトライステート状態になります。DEN を High に駆動すると、他のすべての制御ピン (TPWDNB, TRFB) が静的に維持されている限り、シリアルライザは前の状態に戻ります。

REN ピンまたは RPWDNB ピンを Low に駆動すると、デシリアルライザはトライステート状態に入れます。その結果、レシーバ出力ピン (ROUT0~ROUT23) と RCLK はトライステート状態になります。LOCK 出力はアクティブのまま維持され、PLL の状態を反映します。レシーバパワーダウン (RPWDNB Low) およびパワーオフ ( $V_{DD} = 0V$ ) 中、デシリアルライザの入力ピンはハイインピーダンスです。

### 6.3.6 プリエンファシス

DS90UR241 は、長い (損失が大きい) 伝送媒体を補償するために使用されるプリエンファシス機能を備えています。遷移時に追加の出力電流を供給することでケーブル負荷効果を打ち消すユーザー選択可能なプリエンファシス機能によって、ケーブル駆動能力が改善されます。伝送距離は媒体の損失特性と品質によって制限されます。プリエンファシスは、LVDS ロジック遷移時に電流を増やすことで、ケーブル負荷効果を低減し、駆動距離を伸ばします。また、プリエンファシスは遷移の高速化、アイ開口の拡大、シグナルインテグリティの向上に役立ちます。DS90UR241 のプリエンファシス機能は、ほとんどの場合、伝送距離を最大 10m 伸ばします。

プリエンファシス機能を有効化するには、追加の電流レベルを設定するため、「PRE」ピンと  $V_{SS}$  の間に 1 つの外付け抵抗 ( $R_{PRE}$ ) を接続する必要があります。 $R_{PRE}$  の値は、 $6\text{k}\Omega$  と  $100\text{M}\Omega$  の間の値である必要があります。 $6\text{k}\Omega$  より小さい値は使用できません。「PRE」ピンの入力抵抗値を小さくすると、データ遷移中の動的電流が大きくなります。追加のソース電流は、次式で求められます。 $PRE = (R_{PRE} \geq 6\text{k}\Omega)$ ,  $I_{MAX} = [48 / R_{PRE}]$ 。たとえば、 $R_{PRE} = 15\text{k}\Omega$  の場合、プリエンファシス電流は 3.2mA 増加します。

特定の媒体に対するプリエンファシスの量は、アプリケーションの伝送距離に依存します。一般に、プリエンファシスが大きすぎると、レシーバの入力ピンにオーバーシュートまたはアンダーシュートが発生する可能性があります。これは、過剰なノイズ、クロストーク、消費電力の増加の原因となる可能性があります。ケーブル (距離) が短い場合、プリエンファシスが必要ない場合があります。各アプリケーションの適切なプリエンファシス値を決定するため、信号品質を測定することを推奨します。

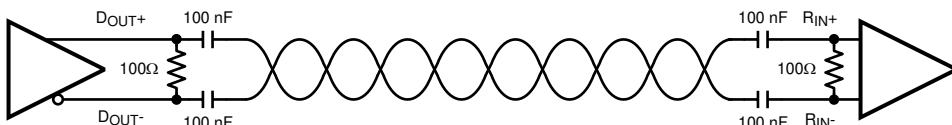

### 6.3.7 AC 結合および終端

DS90UR241 と DS90UR124 は、内部 DC 平衡化エンコード / デコード方式を使用した AC 結合相互接続をサポートしています。シリアルライザ / デシリアルライザを AC 結合アプリケーションで使用するには、外部 AC 結合コンデンサを LVDS 信号経路に直列に挿入します (図 7-8 を参照)。デシリアルライザの入力段は、内部  $V_{CM}$  を +1.8V に設定する AC バイアス回路を内蔵しており、AC 結合用に設計されています。AC 信号結合では、信号入力との AC 結合経路をコンデンサが担っています。

高速 LVDS 伝送の場合、できるだけ小さいパッケージの AC カップリング コンデンサを使用する必要があります。これにより、パッケージの寄生素子に起因する信号品質の劣化を最小限に抑えることができます。このインターフェイスで最も一般的に使用されるコンデンサの値は 100nF (0.1uF) です。NPO クラス 1 または X7R クラス 2 タイプのコンデンサを推奨します。最高のシステムレベル ESD 性能を得るには、50WVDC 以上のものを使う必要があります。

適切に動作させるには、 $DOUT\pm$  と  $RIN\pm$  の間の終端抵抗も必要です。終端抵抗は、駆動されるメディアの差動インピーダンスと等しく、かつ 90~132Ω の範囲である必要があります。100Ω は、標準的な 100Ω 伝送媒体で一般的に使用されている標準値です。この抵抗は反射を制御するのに必要とされ、同時に電流ループも完成させます。ピンからのスタブ長を最小化するため、シリアルライザの  $DOUT\pm$  出力とデシリアルライザの  $RIN\pm$  入力のできるだけ近くに抵抗を配置します。伝送ラインの差動インピーダンスと整合させるため、LVDS I/O はシリアルライザの  $DOUT\pm$  出力ピンとデシリアルライザの  $RIN\pm$  入力ピンで 100Ω の抵抗によって終端されます。

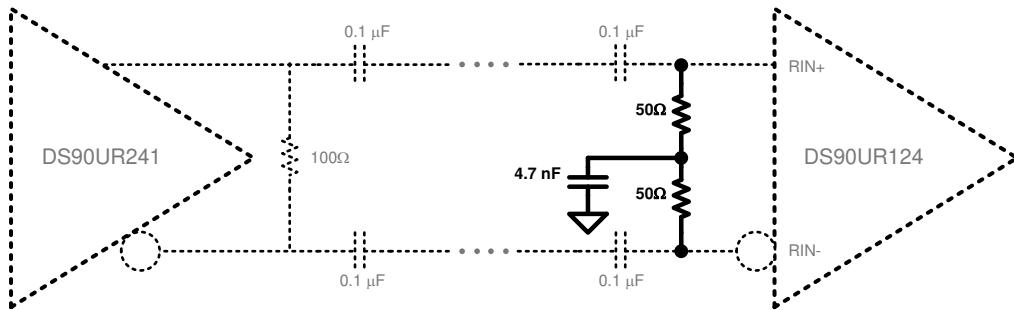

#### 6.3.7.1 レシーバ終端オプション 1

$RIN\pm$  ピンの間に 1 つの 100Ω 終端抵抗を配置します (図 7-8 を参照)。これにより、レシーバ入力での信号の終端が行われます。ノイズ耐性を向上させるため、その他の方法を使うこともできます。

#### 6.3.7.2 レシーバ終端オプション 2

EMI 耐性を向上させるため、1 つの 100Ω 抵抗の代わりに 2 つの 50Ω 抵抗を使用できます。50Ω 抵抗の中点とグランドの間に小さなコンデンサを接続します (図 7-10 を参照)。これにより、ノイズ抑制のための、高い周波数でインピーダンスが低い経路を形成します。値はそれほど重要ではありません。一般的なアプリケーションでは 4.7nF が使えます。

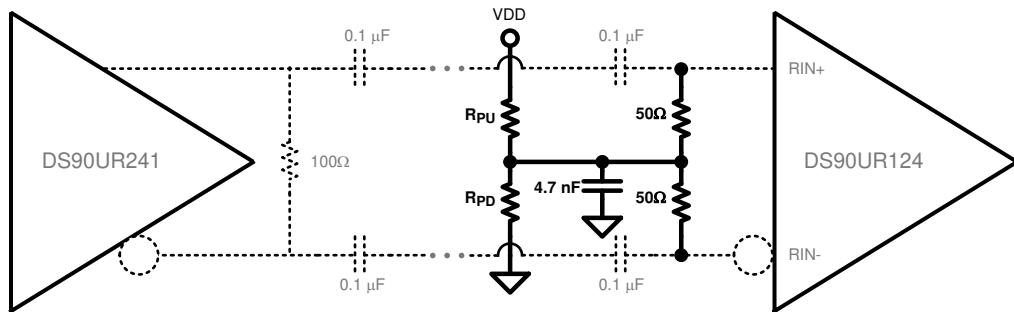

#### 6.3.7.3 レシーバ終端オプション 3

ノイズが多い環境の場合、追加の分圧器回路を中点に接続できます。これには、ノイズ抑制のための DC 低インピーダンス経路を提供するという利点があります。プルアップとプルダウンには、100Ω~2kΩ の範囲の抵抗値を使用します。中点を 1.8V にバイアスするため、抵抗値を調整します。以下に例を示します (図 7-11 を参照)。 $V_{DD} = 3.3V$ 、 $R_{pullup} = 1K\Omega$ 、 $R_{pulldown} = 1.2K\Omega$ 、または  $R_{pullup} = 100\Omega$ 、 $R_{pulldown} = 120\Omega$  (最強)。値が小さいほどより多くのバイアス電流が消費されますが、ノイズ抑制は強化されます。

### 6.3.8 信号品質向上機能

DS90UR124 デシリアルライザは 2 つの信号品質向上機能を備えています。重負荷を駆動する際に、 $SLEW$  ピンを使って LVCMOS 出力の駆動強度を高めることができます。 $SLEW$  を使うと、出力駆動強度を高電流駆動または低電流駆動に設定できます。Low (デフォルト設定) にすると 2mA の低駆動、High にすると 4mA の高駆動に設定されます。

EMI (同時スイッチング ノイズとシステム グランド バウンス) を低減するのに役立つ 2 種類の段階的ターンオン モード (固定および PTO 周波数拡散) が備わっています。PTOSEL ピンは、同時にスイッチングする出力数を制限するため、データ / クロック出力にバンク スキューを導入します。固定 PTO モードの場合、デシリアルライザの ROUT[23:0] 出力は 8 つずつ 3 つのグループに分類されます。各グループはそれぞれグループ 1、グループ 2、グループ 3 の RCLK から約 2 または 1 UI 位相を離してスイッチングします (図 5-15 を参照)。PTO 周波数拡散モードでも、ROUT[23:0] は 8 つずつ 3 つのグループに分類されます。各グループは、4 サイクルごとに、隣接するグループと位相によって分類されます (図 5-16 を参照)。PTO 周波数拡散動作モードでは、RCLK も拡散され、1 UI で分離されることに注意します。

#### 6.3.9 @SPEED-BIST テスト機能

テスト検証によってベンダーを支援するため、DS90UR241 と DS90UR124 は、システム製造とフィールド診断の両方に対応する内蔵セルフテスト (BIST) 機能を備えています。BIST モードは、特殊かつ高価な試験装置を使用せずに、高速シリアルリンク全体を実リンク速度でチェックすることを目的としています。この機能により、システム ホストはシリアルライザと

デシリアルライザの両方の診断テストを簡単に実行できます。この BIST 機能は、DS90UR124 の 2 本の制御ピンを使って簡単に構成できます。BIST モードが作動すると、内部で生成された PRBS データ パターンをシリアルライザが転送できるようになります。このパターンは、相互接続リンクを通してデシリアルライザに到達します。DS90UR124 は、データ パターンにビット エラーがないかどうか確認する PRBS パターン検証回路を内蔵しており、デシリアルライザのデータ出力ピンにエラーがあれば報告します。

@SPEED-BIST 機能は DS90UR124 デシリアルライザの 2 本の信号ピン (BISTEN と BISTM) を使用します。BISTEN ピンと BISTM ピンの組み合わせによって、BIST モードの機能が決定されます。BISTEN 信号 (High) により、デシリアルライザのテスト機能が有効化されます。BIST モードが有効化された後、デシリアルライザがデータの受け入れを開始するには、DS90UR241 シリアルライザのすべてのデータ入力チャネル DIN[23:0] をロジック Low またはフローティングに設定する必要があります。BIST 動作全体を通して、シリアルライザの入力クロック信号 (TCLK) も供給する必要があります。BISTM ピンを使って、BIST 機能のエラー報告ステータス モードを選択します。BIST がエラー ステータス モード (BISTM = Low) に構成されている場合、各 ROUT[23:0] 出力はサイクルごとのビット エラーに対応します。ビットの不一致の結果は、ROUT[23:0] データ出力ピンの各パラレル入力に示されます。BIST エラー カウント アキュムレータ モード (BISTM = High) では、ROUT[7:0] の 8 ビット カウンタを使って、検出されたエラーの数 (0~255) が表示されます。BIST テストが成功したことは、デシリアルライザの PASS ピンで報告されます。PASS ステータスが確実に有効であるためには、最初にデシリアルライザの PLL がロックしている必要があります。PASS ステータスピンは Low に維持され、伝送リンクで  $1 \times 10^{-9}$  の BER が達成されると、High に遷移します。

### 6.3.10 DS90C241, DS90C124 との下位互換モード

RAOFF ピンを使うことで、DS90C241 および DS90C124 デバイスとの下位互換モードに対応できます。DS90C241 シリアルライザと DS90C124 デシリアルライザのどちらかと接続するには、追加の LSFR コーディングを無効化するため、DS90UR241 または DS90UR124 の RAOFF ピンを High に接続する必要があります。通常動作 (DS90UR241 と DS90UR124 を直接接続) の場合、RAOFF ピンを Low に設定します。詳細については、表 6-1 と 表 6-2 を参照してください。

## 6.4 デバイスの機能モード

表 6-1. DS90UR241 シリアライザの真理値表

| TPWDNB<br>(ピン 9) | DEN<br>(ピン 18) | RAOFF<br>(ピン 12) | Tx PLL ステータス<br>(内部) | LVDS 出力<br>(ピン 19 および 20)            |

|------------------|----------------|------------------|----------------------|--------------------------------------|

| L                | X              | X                | X                    | ハイインピーダンス                            |

| H                | L              | X                | X                    | ハイインピーダンス                            |

| H                | H              | X                | 未ロック                 | ハイインピーダンス                            |

| H                | H              | L                | ロック済み                | 埋め込みクロック方式シリアル データ<br>(DS90UR124 互換) |

| H                | H              | H                | ロック済み                | 埋め込みクロック方式シリアル データ (DS90C124<br>互換)  |

表 6-2. DS90UR124 デシリアライザの真理値表

| RPWDNB<br>(ピン 48) | REN<br>(ピン 60) | RAOFF<br>(ピン 63) | Rx PLL ステータス<br>(内部) | ROUTn と RCLK<br>(ピン配置図を参照)          | LOCK<br>(ピン 23)                  |

|-------------------|----------------|------------------|----------------------|-------------------------------------|----------------------------------|

| L                 | X              | X                | X                    | ハイインピーダンス                           | ハイインピーダンス                        |

| H                 | L              | X                | X                    | ハイインピーダンス                           | L = PLL は未ロック、<br>H = PLL はロック済み |

| H                 | H              | X                | 未ロック                 | ハイインピーダンス                           | L                                |

| H                 | H              | L                | ロック済み                | データおよび RCLK アクティブ<br>(DS90UR241 互換) | H                                |

| H                 | H              | H                | ロック済み                | データおよび RCLK アクティブ<br>(DS90C241 互換)  | H                                |

## アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インストルメンツの製品仕様に含まれるものではなく、テキサス・インストルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

## 1 アプリケーション情報

### 1.1 DS90UR241 と DS90UR124 の使い方

DS90UR241/DS90UR124 シリアライザ / デシリアルライザ (SERDES) ペアは、最大 1.03Gbps のシリアル LVDS リンクを使って、24 ビット パラレル LVC MOS データを転送します。入力データのシリアル化は、データにクロックを埋め込むシリアルライザの内蔵 PLL を使って行われます。デシリアルライザは入力データ ストリームからクロック / 制御情報を抽出し、データをデシリアルライズします。デシリアルライザは、ロック状態を判定するため、入力クロック情報を監視し、LOCK 出力を High にアサートすることでロックを示します。

### 1.2 ディスプレイ アプリケーション

DS90URxxx-Q1 チップセットは、ホスト (グラフィックス プロセッサ) とディスプレイとの間のインターフェイスを目的としており、18 ビット色深度 (RGB666) と最大  $1280 \times 480$  のディスプレイ形式をサポートしています。RGB666 構成では、5~43MHz の PCLK レートのシリアルリンク上で、18 のカラー ビット (R[5:0], G[5:0], B[5:0])、ピクセル クロック (PCLK)、3 つの制御ビット (VS, HS, DE) とともに、3 つの予備ビットがサポートされています。

### 1.3 代表的なアプリケーションの接続

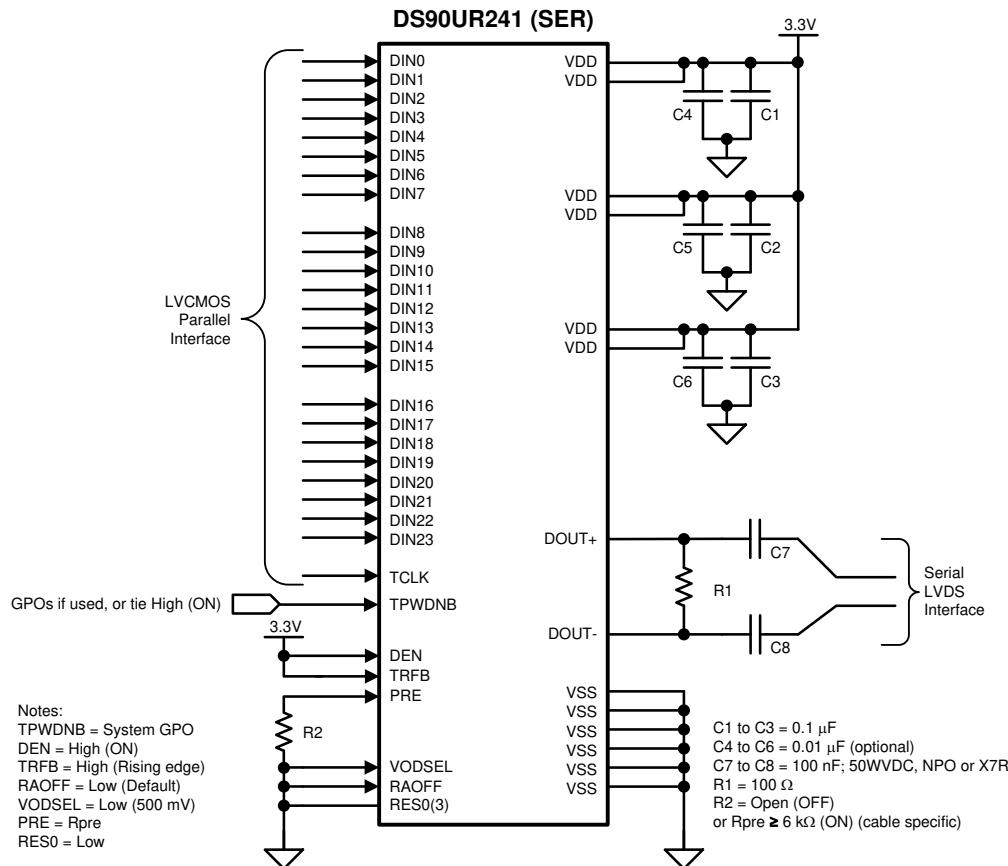

図 7-1 に、DS90UR241 シリアライザ (SER) の代表的なアプリケーションを示します。LVDS 出力では、 $100\Omega$  の終端とラインに対する  $100nF$  カップリング コンデンサが使われています。電源ピンの近くにバイパス コンデンサを配置します。ローカル バイパスとして、少なくとも 3 つの  $0.1\mu F$  コンデンサを使用する必要があります。システム GPO (汎用出力) が TPWDNB ピンを制御します。このアプリケーションでは、TCLK の立ち上がりエッジでデータをラッチするため、TRFB ピンは High に接続されています。DEN 信号も使われておらず、High に接続されています。本アプリケーションはコンパニオン デシリアルライザ (DS90UR124) と接続することを想定しており、データをスクランブル化し、リンク信号品質を向上させるため、RAOFF ピンは Low に接続されています。このアプリケーションでは、リンクは一般的なものであるため、標準 LVDS スイングに設定するために、VODSEL ピンが Low に接続されています。プリエンファシス入力は、グランドとの間に接続された抵抗を使って、アプリケーションが必要とするプリエンファシスの量を設定します。

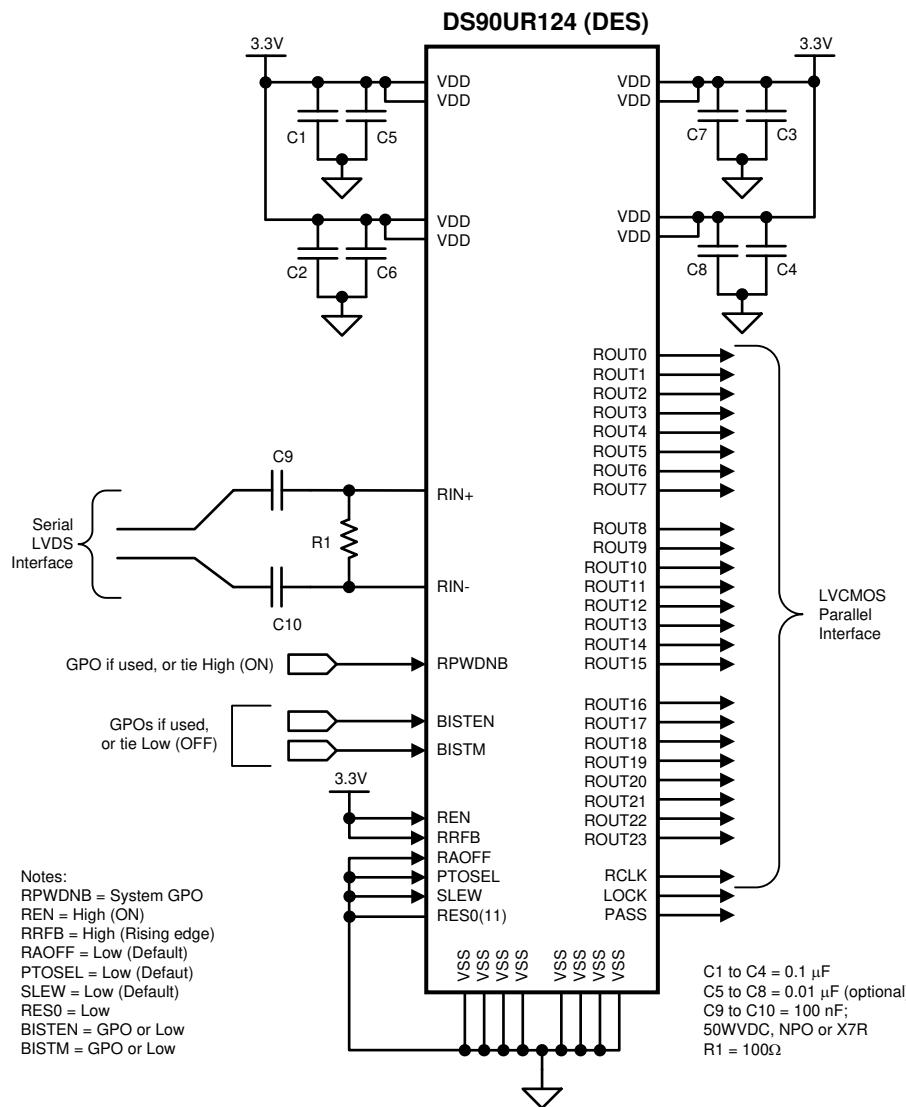

図 7-5 に、DS90UR124 デシリアルライザ (DES) の代表的なアプリケーションを示します。LVDS 入力では、 $100\Omega$  の終端とラインに対する  $100nF$  カップリング コンデンサが使われています。電源ピンの近くにバイパス コンデンサを配置します。ローカル バイパスとして、少なくとも 4 つの  $0.1\mu F$  コンデンサを使用する必要があります。システム GPO (汎用出力) が RPWDNB ピンを制御します。このアプリケーションでは、RCLK の立ち上がりエッジでデータをストローブするため、RRFB ピンは High に接続されています。REN 信号も使われておらず、High に接続されています。本アプリケーションはコンパニオン シリアルライザ (DS90UR241) と接続することを想定しており、データをデスクランブル化するため、RAOFF ピンは Low に接続されています。出力 (LVC MOS) の信号品質は SLEW ピンにより設定されます。そして、PTOSEL ピンを使って、出力バウホール間にわずかな遅延を導入することで、同時出力スイッチングを低減できます。

## 2 代表的なアプリケーション

### 2.1 DS90UR241-Q1 の代表的なアプリケーションの接続

図 7-1. DS90UR241 の接続図

#### 2.1.1 設計要件

表 7-1. DS90UR241 の設計パラメータ

| 設計パラメータ                      | 数値の例  |

|------------------------------|-------|

| VDD                          | 3.3 V |

| DOUT $\pm$ 用 AC カップリング コンデンサ | 100nF |

| DOUT $\pm$ の外部終端             | 100 Ω |

| PCLK 周波数                     | 33MHz |

#### 2.1.2 詳細な設計手順

図 7-1 に、DS90UR241 シリアライザの代表的なアプリケーションとして、33MHz、18 ビット カラー ディスプレイ アプリケーションを示します。DOUT $\pm$  出力には、外付けの直列 0.1μF AC カップリング コンデンサと高速シリアル ラインの 100Ω 並列終端を接続する必要があります。本シリアルライザは終端を内蔵していません。電源ピンの近くにバイパス コンデンサを配置します。ローカル デバイス バイパスとして、少なくとも 3 つの 0.1μF コンデンサを使用する必要があります。コンデンサの数と値は本デバイスの電源ノイズ仕様が満たされるかどうかで決まるため、追加のコンデンサが必要な場合があります。ノイズを効果的に抑制するため、VDD にフェライト ビーズが必要な場合があります。グラフィック信号源とのインターフ

エイスには 3.3V LVCMOS レベルが使われます。RC 遅延を PDB 信号に接続して、電源が安定するまでデバイスのインペーブルを遅延させます。

### 2.1.2.1 電源に関する考慮事項

シリアルライザとデシリアルライザは、すべて LVCMOS で設計されているため、本質的に低消費電力デバイスです。また、LVDS 出力の定電流源特性により、LVCMOS 設計の速度対  $I_{DD}$  曲線の勾配が最小化されます。

### 2.1.2.2 ノイズマージン

デシリアルライザのノイズマージンとは、デシリアルライザが許容でき、依然として確実にデータを回復できる入力ジッタ(位相ノイズ)の量です。各種環境およびシステム要因には以下が含まれます。

- シリアルライザ:  $V_{DD}$  ノイズ、TCLK ジッタ(ノイズ帯域幅と帯域外ノイズ)

- 媒体: ISI、 $V_{CM}$  ノイズ

- デシリアルライザ:  $V_{DD}$  ノイズ

ノイズマージンの説明図については、図 5-17 を参照してください。

### 2.1.2.3 伝送媒体

シリアルライザとデシリアルライザは、PCB 配線またはツイストペアケーブルを使ってポイントツー ポイント構成で使用されます。ポイントツー ポイント構成では、トランシミッタ / レシーバペアの両端で伝送媒体を終端する必要があります。LVDS 用相互接続は通常、 $100\Omega$  の差動インピーダンスを持っています。インピーダンスの不連続性を最小化するため、整合された差動インピーダンスを持つケーブルとコネクタを使います。ケーブルを使うほとんどのアプリケーションでは、使用データレート、許容ビットエラーレート、伝送媒体に基づいて伝送距離が決定されます。

伝送媒体の受信側で得られる信号の品質は、シリアルデータストリームの差動アイ開口を監視することで評価できます。レシーバ入力許容誤差および差動スレッショルド電圧仕様では、許容されるデータアイ開口を定義しています。DS90UR124 の入力の終端抵抗の両端の電圧を測定するには、差動プローブを使用する必要があります。図 7-2 に、アイ開口と、レシーバ入力許容誤差および差動スレッショルド電圧仕様との関係を示します。

### 2.1.2.4

図 7-2. レシーバ入力のアイ開口

### 2.1.2.5 ライブリンク挿入

本シリアルライザ / デシリアルライザ デバイスはライブ プラガブル(活線挿抜可能) アプリケーションをサポートしています。ランダムデータに対して自動的にレシーバをロックさせる「プラグ アンド ゴー」ホット挿入機能により、DS90UR124 は活線挿入イベント中にアクティブデータストリームにロックできます。

### 2.1.3 アプリケーション曲線

図 7-3. DS90UR241 の DOUT $\pm$  (1.2Gbps、RIN $\pm$  終端で測定、VODSEL = Low)

図 7-4. DS90UR241 の DOUT $\pm$  (1.2Gbps、RIN $\pm$  終端で測定、VODSEL = High)

## 2.2 DS90UR124 の代表的なアプリケーションの接続

図 7-5. DS90UR124 の接続図

### 2.2.1 設計要件

表 7-2. DS90UR124 の設計パラメータ

| 設計パラメータ                               | 数値の例  |

|---------------------------------------|-------|

| VDD                                   | 3.3 V |

| DS90UR124-Q1 の RIN± の AC カップリング コンデンサ | 100nF |

| DS90UR124-Q1 の RIN± の終端               | 100 Ω |

### 2.2.2 詳細な設計手順

図 7-5 に、DS90UR124 デシリアライザの代表的なアプリケーションとして 33MHz、18 ビット カラー ディスプレイ アプリケーションを示します。RIN± 入力には、外付けの直列 0.1μF AC カップリング コンデンサと高速シリアル ラインの 100Ω 並列終端を接続する必要があります。本デシリアライザは終端を内蔵していません。電源ピンの近くにバイパス コンデンサを配置します。ローカル デバイス バイパスとして、少なくとも 4 つの 0.1μF コンデンサを使用する必要があります。ノイ

ズを効果的に抑制するため、VDD にフェライトビーズが必要です。コンデンサの数と値は本デバイスの電源ノイズ仕様が満たされるかどうかで決まるため、追加のコンデンサが必要な場合があります。ディスプレイとのインターフェイスには 3.3V LVCMS レベルが使われます。RC 遅延を PDB 信号に接続して、電源が安定するまでデバイスのイネーブルを遅延させます。

### 2.2.3 アプリケーション曲線

図 7-6. DS90UR241 のシリアルストリームと DS90UR124 の 43MHz PCLK 出力

図 7-7. DS90UR124 の 43MHz PCLK 出力 (拡大図)

## 3 電源に関する推奨事項

このデバイスは、3.3V の入力コア電源で動作するように設計されています。デバイスによっては、内部の回路部分ごとに電源ピンとグランドピンが分離されているものがあります。電源系を分離する目的は、スイッチングノイズの影響を回路間で遮断するためです。このようなデバイスに対して、通常、プリント基板の層を分ける必要はありません。通常、ピン説明表には、どの回路ブロックをどの電源ピンペアに接続するかについての指針が記載されています。なお場合によっては、PLL のようなノイズに敏感な回路部分にクリーンな電源を供給するために、外部フィルタを用います。

## 4 レイアウト

### 4.1 レイアウトのガイドライン

#### 4.1.1 プリント基板レイアウトと電源系の注意事項

LVDS SERDES デバイスのプリント基板レイアウトおよび層構成は、デバイスに低ノイズの電源を供給するように設計する必要があります。優れたレイアウト手法としては、不要な浮遊ノイズ、帰還、干渉を最小限に抑えるために、高い周波数または高レベルの入力と出力を分離するようにします。また、2~4mil (0.05~0.1mm) 程度の薄い誘電体材料を電源層とグランド層の間に使用すると、電源系の性能を大きく改善できる場合があります。つまり、この方式によりプリント基板の層間の容量をバイパスコンデンサとして利用できるので、特に高周波の電源ノイズに対するフィルタ特性を改善する効果があります。そのため、外付けバイパスコンデンサの容量や配置について少々妥協することも可能になります。外付けバイパスコンデンサには、RF セラミックとタンタル電解の両方のタイプを含める必要があります。RF コンデンサの値は、 $0.01\mu\text{F} \sim 0.1\mu\text{F}$  の範囲を使用します。タンタルコンデンサは、 $2.2\mu\text{F} \sim 10\mu\text{F}$  の範囲のものを使用します。タンタルコンデンサの電圧定格は、使用する電源電圧の 5 倍以上にします。

寄生成分が小さい表面実装コンデンサを推奨します。1 つの電源ピンに複数のコンデンサを配置する場合は、容量が小さいコンデンサをピンの近くに配置します。また大容量コンデンサを電源の入り口部分に配置してください。低周波スイッチングノイズを平滑化する容量は  $50\mu\text{F} \sim 100\mu\text{F}$  の範囲が一般的です。電源ピンとグランドピンは電源層およびグランド層に直接接続し、またバイパスコンデンサはコンデンサの両端に設けたビアを経由して電源層およびグランド層に接続することを推奨します。電源ピンまたはグランドピンからプリント基板表面でバイパスコンデンサへ配線を行うと、寄生インダクタンスを増加させてしまいます。

外付けのバイパスコンデンサは、X7R特性の小型チップコンデンサ(0603など)を推奨します。寸法が小さいため、コンデンサの寄生インダクタンス分も小さいという利点があります。なお設計の際には、通常20MHz～30MHzの範囲にある外付けバイパスコンデンサの自己共振周波数に注意してください。また効果的なバイパスを行うために、複数のコンデンサを用いて、対象となる周波数に対する電源系のインピーダンスを下げる手法がしばしば使われます。高周波のインピーダンスを下げるため、電源ピンまたはグランドピンから各層に対して2つのビアを設けます。

デバイスによっては、内部の回路部分ごとに電源ピンとグランドピンが分離されているものがあります。電源系を分離する目的は、スイッチングノイズの影響を回路間で遮断するためです。このようなデバイスに対して、通常、プリント基板の層を分ける必要はありません。通常、ピン説明表には、どの回路ブロックをどの電源ピンペアに接続するかについての指針が記載されています。なお場合によっては、PLLのようなノイズに敏感な回路部分にクリーンな電源を供給するために、外部フィルタを用います。

プリント基板は、電源層とグランド層を含む4層以上のものを採用してください。LVCMOS信号系は、LVDS信号に結合するのを防ぐため、LVDS信号系から離して配置しなければなりません。LVDS相互接続には通常、近接結合した100Ωの差動ラインを推奨します。密結合のラインでは、カッピングノイズはレシーバ端でコモンモードとして現れるため除去されます。また、放射ノイズが少ない利点も備えます。

LVDS相互接続には終端が必要です。ポイントツー・ポイント・アプリケーションの場合、終端はデバイスの両端に配置する必要があります。ラインの差動インピーダンスに整合させるため、100Ω(公称値)とします。終端抵抗とデバイスの間に生じるスタブを最小限に抑えるため、この抵抗はトランシミッタのDOUT±出力とレシーバのRIN±入力にできるだけ近付けて配置します。

#### 4.1.2 LVDS相互接続のガイドライン

詳細は、AN-1108([SNLA008](#))とAN-905([SNLA035](#))を参照してください。

- 100Ω結合の差動ペアを使用します

- 間隔にはS/2S/3Sルールを使います。

- S = ペア内の配線間隔

- 2S = ペア間の配線間隔

- 3S = LVCMOS信号との間隔

- ビアの数は可能な限り少なくします

- 500Mbpsを上回るライン速度で動作させる場合、差動コネクタを使用します。

- 配線のバランスを維持してください。

- ペア内のスキューを可能な限り抑えてください。

- TX出力とRX入力にできる限り近い位置で終端します。

その他の一般的な設計ガイドラインとして『LVDSオーナーズマニュアル』([SNLA187](#))を提供しています(テキサス・インスツルメンツのウェブサイト[www.ti.com/lvds](http://www.ti.com/lvds)でPDFを提供しています)。

図 7-8. AC 結合アプリケーション

\* 注:ビット[0～23]は暗号化およびDC平衡化されているため、物理的に上記の位置には配置されません。

図 7-9. シングルシリアルLVDSビットストリーム\*

図 7-10. レシーバ終端オプション 2

図 7-11. レシーバ終端オプション 3

#### 4.2 レイアウト例

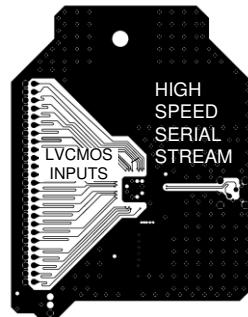

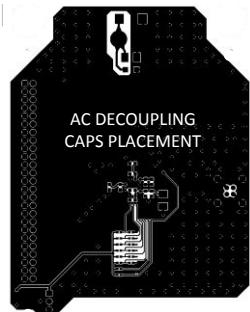

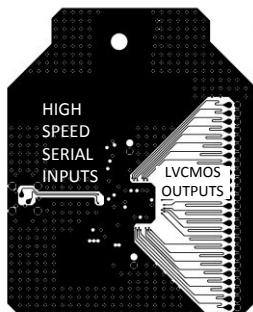

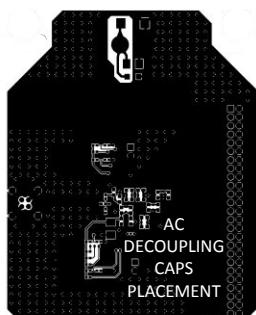

図 7-12. DS90UR241-Q1 の EMC レイアウトの例

図 7-13. DS90UR241-Q1 EMC EVM レイヤ 4

図 7-14. DS90UR124-Q1 の EMC レイアウトの例

図 7-15. DS90UR124-Q1 EMC EVM レイヤ 4

## 7 デバイスおよびドキュメントのサポート

### 7.1 デバイス サポート

### 7.2 ドキュメントのサポート

#### 7.2.1 関連資料

関連資料については、以下を参照してください。

- LVDS 相互接続のガイドライン AN-1108、[SNLA008](#)

- LVDS 相互接続のガイドライン AN-905、[SNLA035](#)

### 7.3 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 7.4 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

### 7.5 商標

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 7.6 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことをお勧めします。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 7.7 用語集

#### テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 8 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision O (April 2015) to Revision P (August 2024) | Page |

|------------------------------------------------------------------|------|

| • ドキュメント全体にわたって表、図、相互参照の採番方法を更新.....                             | 1    |

| • すべてのピンの ESD CDM 定格を +/-12.5kV から +/-1kV に変更.....               | 8    |

| Changes from Revision N (March 2013) to Revision O (April 2015)                                                                                          | Page |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • 「ESD 定格」表、「機能説明」セクション、「デバイスの機能モード」セクション、「アプリケーションと実装」セクション、「電源に関する推奨事項」セクション、「レイアウト」セクション、「デバイスおよびドキュメントのサポート」セクション、「メカニカル、パッケージ、および注文情報」セクションを追加..... | 1    |

---

| Changes from Revision M (March 2013) to Revision N (March 2013) | Page               |

|-----------------------------------------------------------------|--------------------|

| • ナショナル セミコンダクターのデータシートのレイアウトをテキサス・インスツルメンツ形式に変更.....           | <a href="#">24</a> |

---

## メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

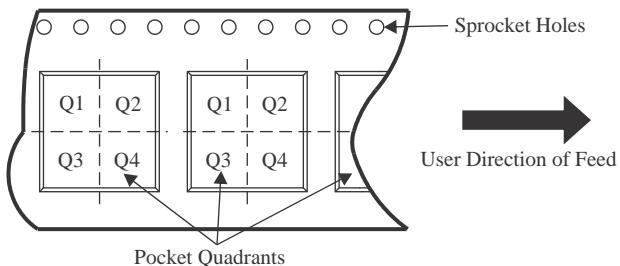

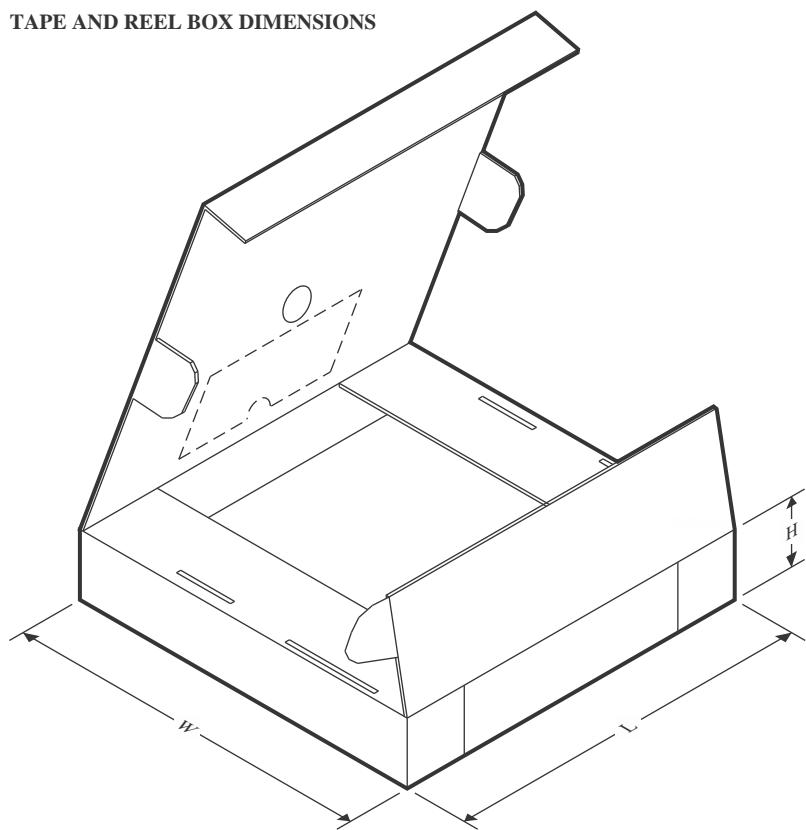

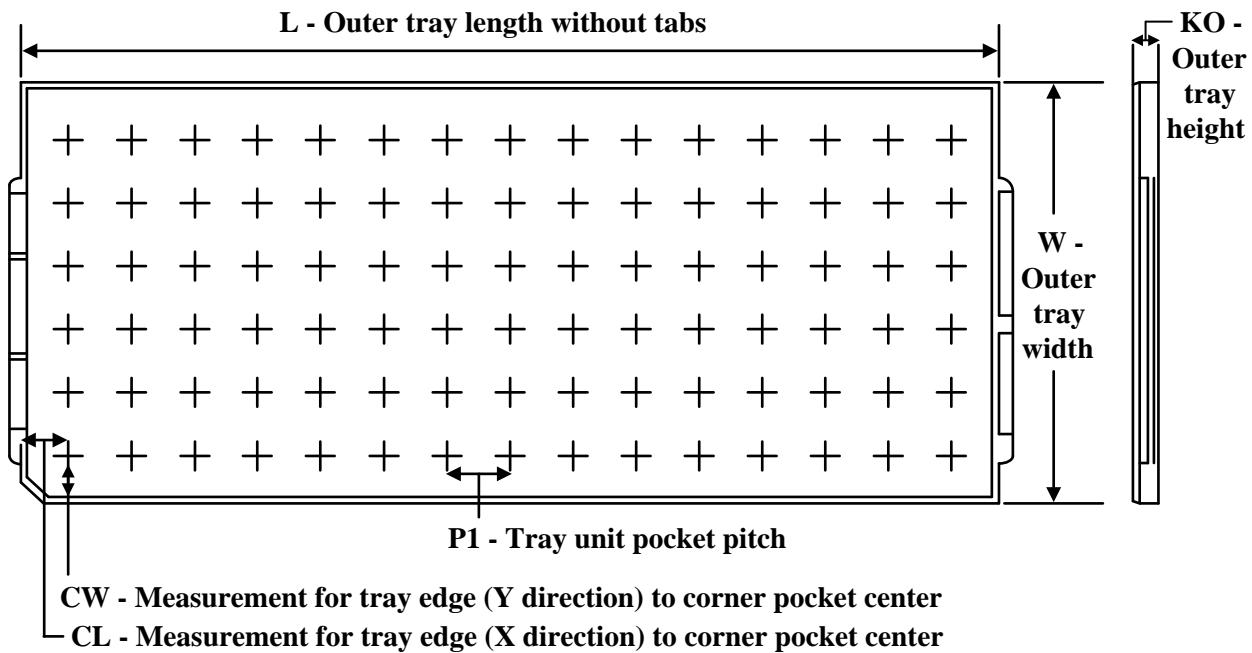

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins  | Package qty   Carrier   | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-----------------|-------------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| DS90UR124IVS/NOPB     | Active        | Production           | TQFP (PAG)   64 | 160   JEDEC TRAY (10+1) | Yes         | SN                                   | Level-3-260C-168 HR               | -40 to 105   | DS90UR124 IVS       |

| DS90UR124IVS/NOPB.A   | Active        | Production           | TQFP (PAG)   64 | 160   JEDEC TRAY (10+1) | Yes         | SN                                   | Level-3-260C-168 HR               | -40 to 105   | DS90UR124 IVS       |

| DS90UR124IVSX/NOPB    | Active        | Production           | TQFP (PAG)   64 | 1000   LARGE T&R        | Yes         | SN                                   | Level-3-260C-168 HR               | -40 to 105   | DS90UR124 IVS       |

| DS90UR124IVSX/NOPB.A  | Active        | Production           | TQFP (PAG)   64 | 1000   LARGE T&R        | Yes         | SN                                   | Level-3-260C-168 HR               | -40 to 105   | DS90UR124 IVS       |

| DS90UR124QVS/NOPB     | Active        | Production           | TQFP (PAG)   64 | 160   JEDEC TRAY (10+1) | Yes         | SN                                   | Level-3-260C-168 HR               | -40 to 105   | DS90UR124 QVS       |

| DS90UR124QVS/NOPB.A   | Active        | Production           | TQFP (PAG)   64 | 160   JEDEC TRAY (10+1) | Yes         | SN                                   | Level-3-260C-168 HR               | -40 to 105   | DS90UR124 QVS       |

| DS90UR124QVS/NOPB.B   | Active        | Production           | TQFP (PAG)   64 | 160   JEDEC TRAY (10+1) | -           | Call TI                              | Call TI                           | -40 to 105   |                     |

| DS90UR124QVSX/NOPB    | Active        | Production           | TQFP (PAG)   64 | 1000   LARGE T&R        | Yes         | SN                                   | Level-3-260C-168 HR               | -40 to 105   | DS90UR124 QVS       |

| DS90UR124QVSX/NOPB.A  | Active        | Production           | TQFP (PAG)   64 | 1000   LARGE T&R        | Yes         | SN                                   | Level-3-260C-168 HR               | -40 to 105   | DS90UR124 QVS       |

| DS90UR241IVS/NOPB     | Active        | Production           | TQFP (PFB)   48 | 250   JEDEC TRAY (10+1) | Yes         | SN                                   | Level-3-260C-168 HR               | -40 to 105   | DS90UR24 1IVS       |

| DS90UR241IVS/NOPB.A   | Active        | Production           | TQFP (PFB)   48 | 250   JEDEC TRAY (10+1) | Yes         | SN                                   | Level-3-260C-168 HR               | -40 to 105   | DS90UR24 1IVS       |

| DS90UR241IVSX/NOPB    | Active        | Production           | TQFP (PFB)   48 | 1000   LARGE T&R        | Yes         | SN                                   | Level-3-260C-168 HR               | -40 to 105   | DS90UR24 1IVS       |

| DS90UR241IVSX/NOPB.A  | Active        | Production           | TQFP (PFB)   48 | 1000   LARGE T&R        | Yes         | SN                                   | Level-3-260C-168 HR               | -40 to 105   | DS90UR24 1IVS       |

| DS90UR241IVSX/NOPB.B  | Active        | Production           | TQFP (PFB)   48 | 1000   LARGE T&R        | -           | Call TI                              | Call TI                           | -40 to 105   |                     |

| DS90UR241QVS/NOPB     | Active        | Production           | TQFP (PFB)   48 | 250   JEDEC TRAY (10+1) | Yes         | SN                                   | Level-3-260C-168 HR               | -40 to 105   | DS90UR24 1QVS       |

| DS90UR241QVS/NOPB.A   | Active        | Production           | TQFP (PFB)   48 | 250   JEDEC TRAY (10+1) | Yes         | SN                                   | Level-3-260C-168 HR               | -40 to 105   | DS90UR24 1QVS       |

| DS90UR241QVSX/NOPB    | Active        | Production           | TQFP (PFB)   48 | 1000   LARGE T&R        | Yes         | SN                                   | Level-3-260C-168 HR               | -40 to 105   | DS90UR24 1QVS       |