ISOUSB211-Q1 JAJSU29 - MARCH 2024

# ISOUSB211-Q1 High/Full/Low-Speed 絶縁型 USB リピータ

# 1 特長

- USB 2.0 準拠

- Low-Speed (1.5Mbps)、Full-Speed (12Mbps) およ び High-Speed (480Mbps) の信号処理をサポート

- 外付けの水晶振動子もクロック入力も不要

- 速度と接続の自動検出

- L1 (スリープ) と L2 (サスペンド) の低消費電力状態を サポート

- High-Speed モードでの基板配線損失を補償するため のイコライゼーションをプログラム可能

- ダウンストリーム側で CDP アドバタイズ

- 反対側に電源 OK 通知

- USB On-The-Go (OTG) および Type-C® デュアル ロール ポート (DRP) 設計のための自動ロール反転を サポート

- 「高 CMTI:100 kV/µs

- 絶縁バリアの両側で ±8kV の IEC 61000-4-2 接触放 電保護

- V<sub>BUS</sub> 電圧範囲:4.25 V~5.5 V

- 3.3V および 1.8V の内部 LDO

- CISPR 32 Class B 放射型電磁波の制限に適合

- 周囲温度範囲:-40℃~+125℃

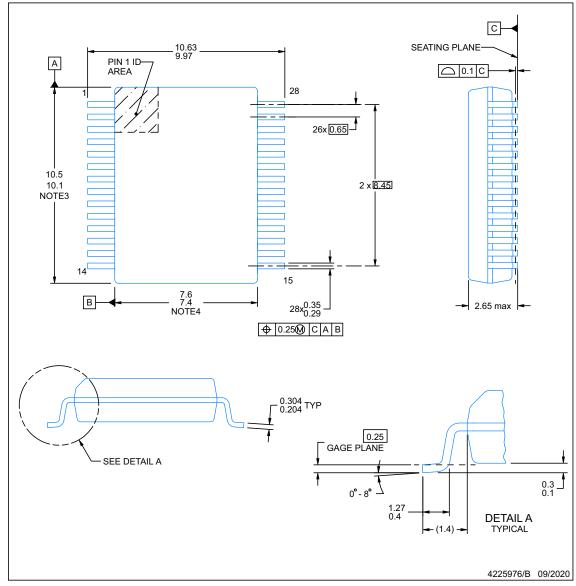

- 小型フットプリントの 28-SSOP パッケージ

- 安全関連認証:

- DIN EN IEC 60747-17 (VDE 0884-17) に準拠し た絶縁耐圧: 7071V<sub>PK</sub>の V<sub>IOTM</sub>、2121V<sub>PK</sub>の V<sub>IORM</sub> (強化絶縁型)

- UL 1577 に準拠した絶縁耐圧:5000V<sub>RMS</sub> (1分)

- IEC 62368-1、IEC 60601-1、IEC 61010-1 認証

- CQC、TUV、CSA 認証

# 2 アプリケーション

- USB ハブ、ホスト、ペリフェラル、ケーブルの絶縁

- 医療用

- ファクトリ オートメーション

- モータードライブ

- グリッド インフラ

- パワー デリバリー

- USB オーディオ

### **強化絶縁オプション**

|         | <b>-</b>                                      |

|---------|-----------------------------------------------|

| 機能      | ISOUSB211-Q1                                  |

| 保護レベル   | 強化                                            |

| サージ絶縁電圧 | 12800 V <sub>PK</sub>                         |

| 定格絶縁電圧  | 5000 V <sub>RMS</sub>                         |

| 絶縁動作電圧  | 1500V <sub>RMS</sub> /<br>2121V <sub>PK</sub> |

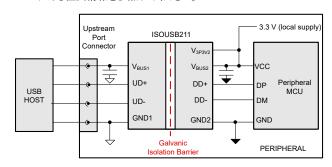

### 3 概要

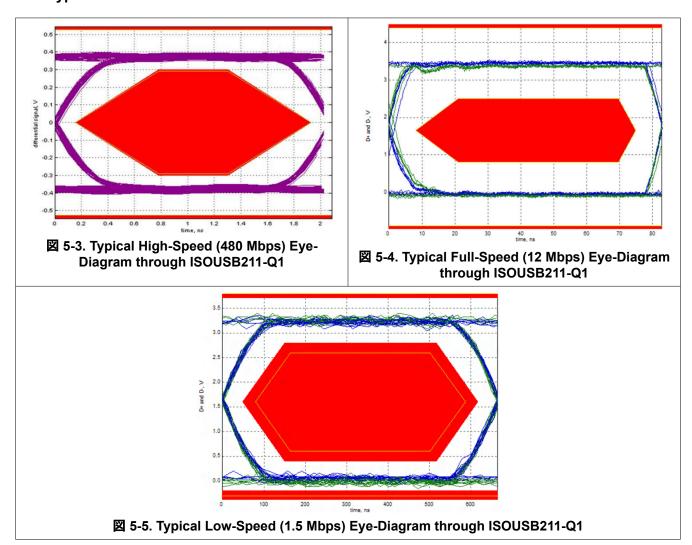

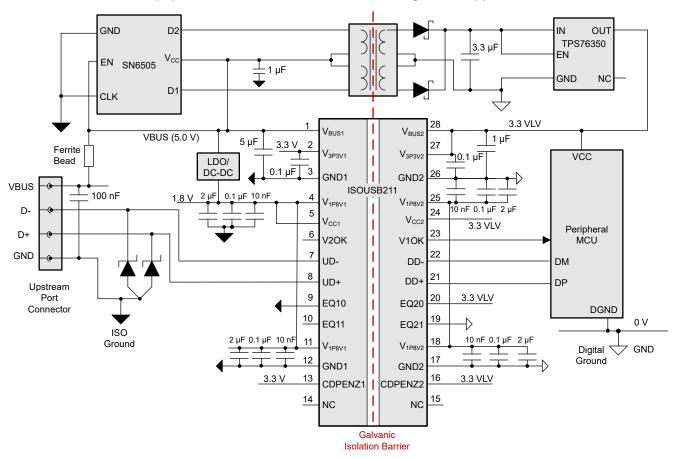

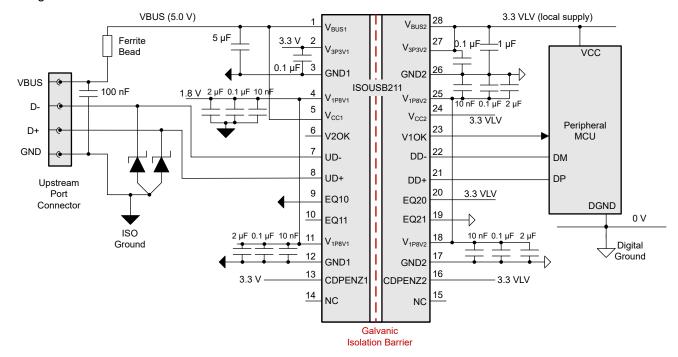

ISOUSB211-Q1 は、Low-Speed (1.5Mbps)、Full-Speed (12Mbps) および High-Speed (480Mbps) の信 号速度をサポートする、ガルバニック絶縁された USB 2.0 準拠のリピータです。このデバイスは、接続および速度の 自動検出、プルアップ / プルダウンの反映、リンク パワー マネージメント機能をサポートしているため、ドロップインに より USB ハブ、ホスト、ペリフェラル、ケーブルを絶縁でき ます。また、デバイスは自動的なロール反転もサポートしま す。切断後にアップストリーム側ポートで新しい接続が検 出されると、アップストリームおよびダウンストリームのポー ト定義が反転します。この機能を使って本デバイスは USB On-The-Go (OTG) と Type-C デュアル ロール ポート (DRP) の実装に対応できます。ISOUSB211-Q1 は、プロ グラム可能なイコライゼーション機能を内蔵しており、基板 の配線に起因する信号損失をキャンセルできるため、 USB2.0 High-Speed TX および RX アイダイアグラム テ ンプレートへの適合に役立ちます。 耐圧 5000 V<sub>RMS</sub> の二 酸化ケイ素 (SiO<sub>2</sub>) 絶縁膜を採用しており、1500V<sub>RMS</sub> の 動作電圧を実現しています。絶縁型電源と組み合わせて 使用すると、高電圧に対して保護するとともに、バスからの ノイズ電流がローカル グランドに入り込むことを防止できま す。ISOUSB211-Q1 デバイスは、強化絶縁に利用できま す。-40℃~+125℃の広い周囲温度範囲に対応していま す。このデバイスは、小型の SSOP-28 (28-DP) パッケー ジで供給されます。

### 製品情報

|              | 45CHH ID TIA |                    |

|--------------|--------------|--------------------|

| 部品番号(1)      | パッケージ        | 本体サイズ (公称)         |

| ISOUSB211-Q1 | SSOP (28) DP | 10.30 mm × 7.50 mm |

利用可能なすべてのパッケージについては、データシートの末尾 にある注文情報を参照してください。

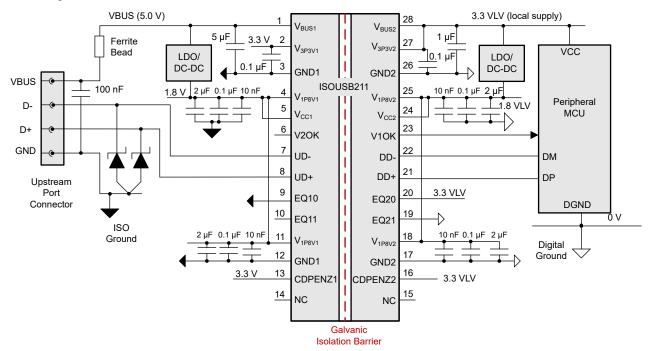

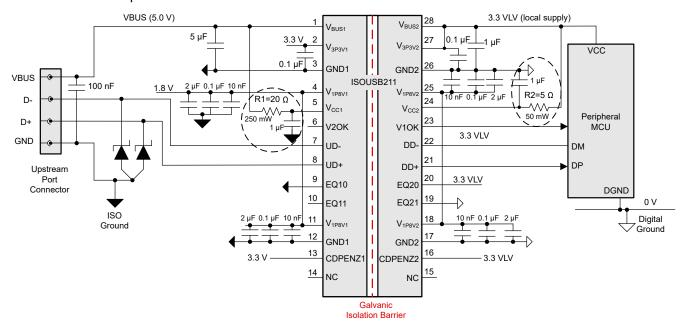

アプリケーション図

# **Table of Contents**

| 1 | 特長                                     | 1  |

|---|----------------------------------------|----|

|   | アプリケーション                               |    |

|   | 概要                                     |    |

|   | Pin Configuration and Functions        |    |

| 5 | Specifications                         | 5  |

|   | 5.1 Absolute Maximum Ratings           |    |

|   | 5.2 ESD Ratings                        |    |

|   | 5.3 Recommended Operating Conditions   |    |

|   | 5.4 Thermal Information                |    |

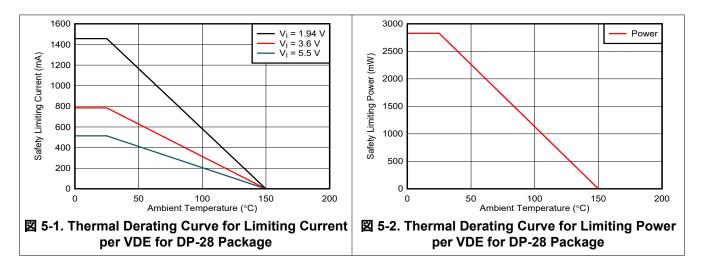

|   | 5.5 Power Ratings                      |    |

|   | 5.6 Insulation Specifications          |    |

|   | 5.7 Safety-Related Certifications      | 8  |

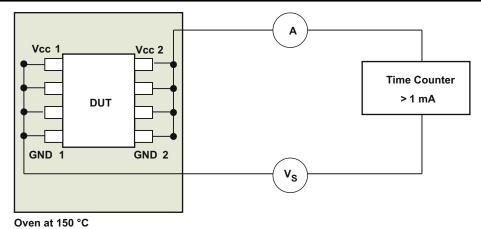

|   | 5.8 Safety Limiting Values             |    |

|   | 5.9 Electrical Characteristics         |    |

|   | 5.10 Switching Characteristics1        | 13 |

|   | 5.11 Insulation Characteristics Curves |    |

|   | 5.12 Typical Characteristics1          | 16 |

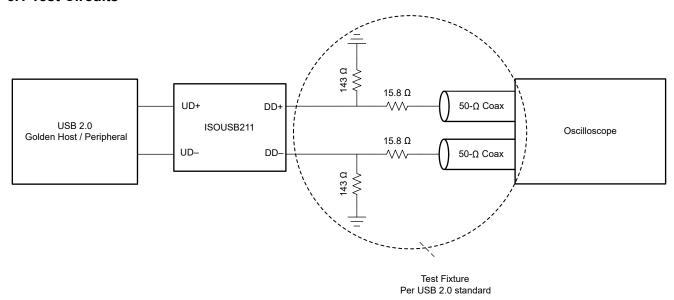

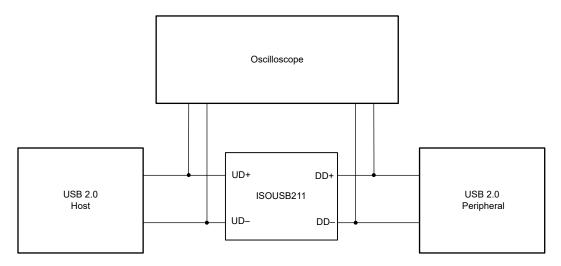

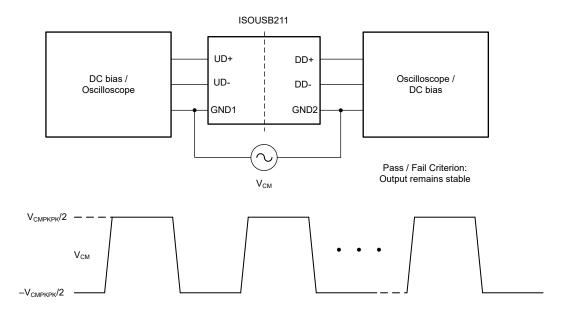

| 6 | Parameter Measurement Information1     | 17 |

|   | 6.1 Test Circuits                      | 17 |

| 7 | Detailed Description1                  | 19 |

|   | 7.1 Overview1                          |    |

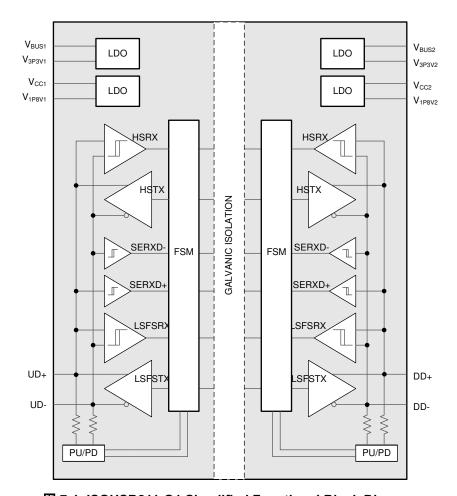

| 7.2 Functional Block Diagram                        | 19 |

|-----------------------------------------------------|----|

| 7.3 Feature Description                             |    |

| 7.4 Device Functional Modes                         |    |

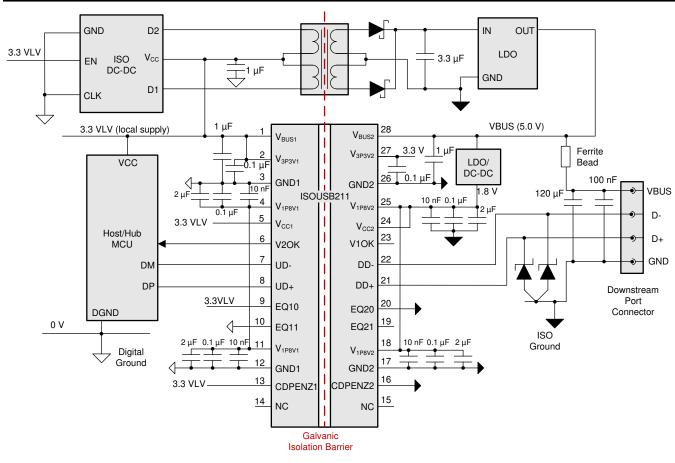

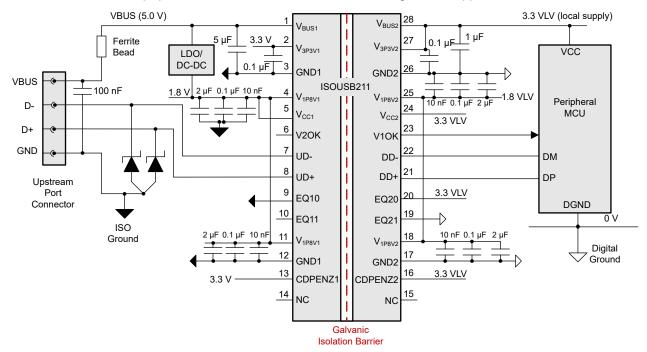

| 8 Application and Implementation                    | 24 |

| 8.1 Typical Application                             |    |

| 8.2 Meeting USB2.0 HS Eye-Diagram Specifications    |    |

| 8.3 Thermal Considerations                          | 29 |

| 8.4 Power Supply Recommendations                    | 32 |

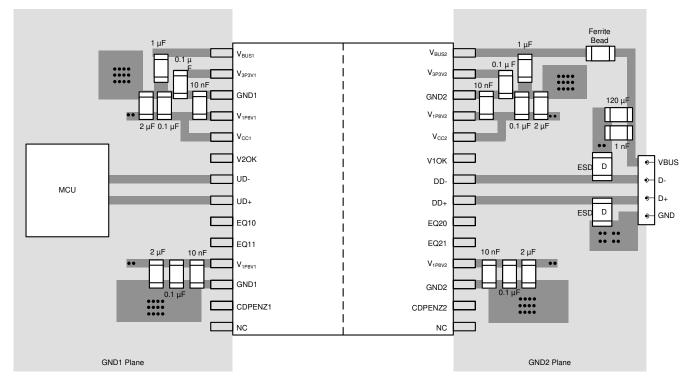

| 8.5 Layout                                          |    |

| 9 Device and Documentation Support                  |    |

| 9.1 Documentation Support                           |    |

| 9.2 Receiving Notification of Documentation Updates | 35 |

| 9.3 サポート・リソース                                       | 35 |

| 9.4 Trademarks                                      | 35 |

| 9.5 静電気放電に関する注意事項                                   | 35 |

| 9.6 用語集                                             | 35 |

| 10 Revision History                                 | 35 |

| 11 Mechanical, Packaging, and Orderable             |    |

| Information                                         | 35 |

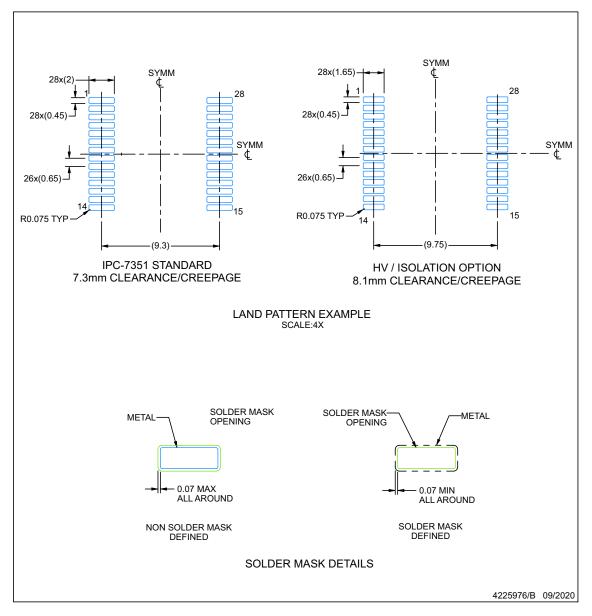

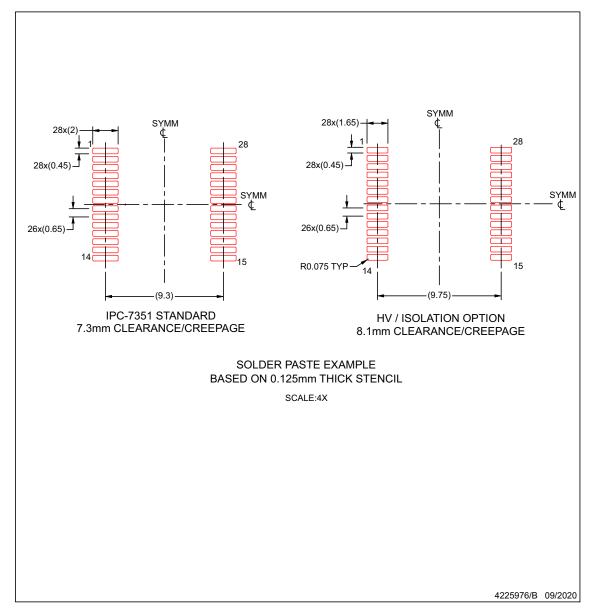

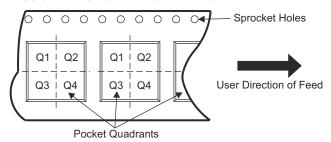

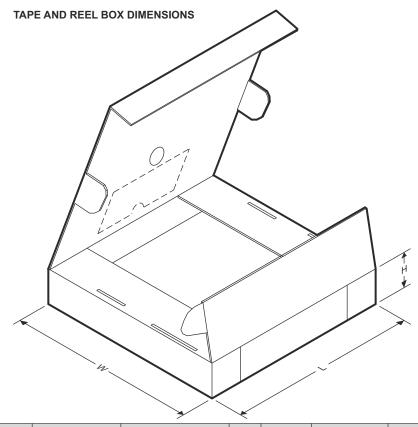

| 11.1 Tape and Reel Information                      | 39 |

|                                                     |    |

Product Folder Links: ISOUSB211-Q1

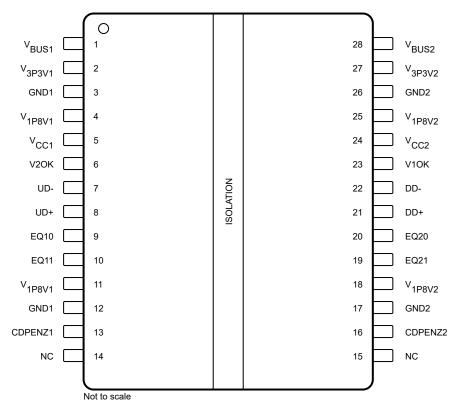

# 4 Pin Configuration and Functions

図 4-1. DP Package 28-Pin SSOP Top View

表 4-1. Pin Functions—28 Pins

| PIN |                    | I/O   | DESCRIPTION                                                                                                                                                                                                                                                                                            |  |  |

|-----|--------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NO. | NAME               | ] "/0 | DESCRIPTION                                                                                                                                                                                                                                                                                            |  |  |

| 1   | V <sub>BUS1</sub>  | _     | Input Power Supply for Side 1. If a 4.25 V to 5.5 V (example USB power bus) supply is available connect it to $V_{BUS1}$ . In this case an internal LDO generates $V_{3P3V1}$ . Else, connect $V_{BUS1}$ and $V_{3P3V1}$ to an external 3.3 V power supply.                                            |  |  |

| 2   | V <sub>3P3V1</sub> | _     | Power Supply for Side 1. If a 4.25 V to 5.5 V supply is connected to $V_{BUS1}$ connect a bypass capacitor between $V_{3P3V1}$ and GND1. In this case an internal LDO generates $V_{3P3V1}$ . Else, connect $V_{BUS1}$ and $V_{3P3V1}$ to an external 3.3 V power supply.                              |  |  |

| 3   | GND1               | _     | Ground 1. Ground reference for Isolator Side 1.                                                                                                                                                                                                                                                        |  |  |

| 4   | V <sub>1P8V1</sub> | _     | Power Supply for Side 1. If a 2.4 V to 5.5 V supply is connected to $V_{CC1}$ connect a bypass capacitor between $V_{1P8V1}$ and GND1. In this case an internal LDO generates $V_{1P8V1}$ . Else, connect $V_{CC1}$ and $V_{1P8V1}$ to an external 1.8 V power supply.                                 |  |  |

| 5   | V <sub>CC1</sub>   | _     | Input Power Supply for Side 1. If a 2.4 V to 5.5 V (example USB power bus, or a DC-DC supply derived from USB power bus) supply is available connect it to $V_{CC1}$ . In this case an internal LDO generates $V_{1P8V1}$ . Else, connect $V_{CC1}$ and $V_{1P8V1}$ to an external 1.8 V power supply. |  |  |

| 6   | V2OK               | 0     | High level on this pin indicates that side 2 is powered up.                                                                                                                                                                                                                                            |  |  |

| 7   | UD-                | I/O   | Upstream facing port D                                                                                                                                                                                                                                                                                 |  |  |

| 8   | UD+                | I/O   | Upstream facing port D+.                                                                                                                                                                                                                                                                               |  |  |

| 9   | EQ10               | I     | Equalization setting for Side 1, LSB. Logic Input.                                                                                                                                                                                                                                                     |  |  |

| 10  | EQ11               | I     | Equalization setting for Side 1, MSB. Logic Input.                                                                                                                                                                                                                                                     |  |  |

| 11  | V <sub>1P8V1</sub> | _     | Connect pin 11 to pin 4, with local bypass capacitors near pin 11.                                                                                                                                                                                                                                     |  |  |

| 12  | GND1               | _     | Ground 1. Ground reference for Isolator Side 1.                                                                                                                                                                                                                                                        |  |  |

| 13  | CDPENZ1            | ı     | Active low singal. Enables CDP advertising on UD+/UD- pins.                                                                                                                                                                                                                                            |  |  |

# 表 4-1. Pin Functions—28 Pins (続き)

|     | PIN                | - I/O | DESCRIPTION                                                                                                                                                                                                                                                                                            |  |  |

|-----|--------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NO. | NAME               | ] "/0 | DESCRIPTION                                                                                                                                                                                                                                                                                            |  |  |

| 14  | NC                 | _     | Leave floating or connect to V <sub>3P3V1</sub> .                                                                                                                                                                                                                                                      |  |  |

| 15  | NC                 | _     | Leave floating or connect to V <sub>3P3V2</sub> .                                                                                                                                                                                                                                                      |  |  |

| 16  | CDPENZ2            | I     | Active low singal. Enables CDP advertising on DD+/DD- pins.                                                                                                                                                                                                                                            |  |  |

| 17  | GND2               | _     | Ground 2. Ground reference for Isolator Side 2.                                                                                                                                                                                                                                                        |  |  |

| 18  | V <sub>1P8V2</sub> | _     | Connect pin 18 to pin 25, with local bypass capacitors near pin 18.                                                                                                                                                                                                                                    |  |  |

| 19  | EQ21               | Į.    | Equalization setting for Side 2, MSB. Logic Input.                                                                                                                                                                                                                                                     |  |  |

| 20  | EQ20               | Į     | Equalization setting for Side 2, LSB. Logic Input.                                                                                                                                                                                                                                                     |  |  |

| 21  | DD+                | I/O   | Downstream facing port D+.                                                                                                                                                                                                                                                                             |  |  |

| 22  | DD-                | I/O   | Downstream facing port D                                                                                                                                                                                                                                                                               |  |  |

| 23  | V10K               | 0     | High level on this pin indicates that side 1 is powered up.                                                                                                                                                                                                                                            |  |  |

| 24  | V <sub>CC2</sub>   | _     | Input Power Supply for Side 2. If a 2.4 V to 5.5 V (example USB power bus, or a DC-DC supply derived from USB power bus) supply is available connect it to $V_{CC2}$ . In this case an internal LDO generates $V_{1P8V2}$ . Else, connect $V_{CC2}$ and $V_{1P8V2}$ to an external 1.8 V power supply. |  |  |

| 25  | V <sub>1P8V2</sub> | _     | Power Supply for Side 1. If a 2.4 V to 5.5 V supply is connected to $V_{CC2}$ connect a bypass capacitor between $V_{1P8V2}$ and GND2. In this case an internal LDO generates $V_{1P8V2}$ . Else, connect $V_{CC2}$ and $V_{1P8V2}$ to an external 1.8 V power supply.                                 |  |  |

| 26  | GND2               | _     | Ground 2. Ground reference for Isolator Side 2.                                                                                                                                                                                                                                                        |  |  |

| 27  | V <sub>3P3V2</sub> | _     | Power Supply for Side 2. If a 4.25 V to 5.5 V supply is connected to $V_{BUS2}$ connect a bypass capacitor between $V_{3P3V2}$ and GND1. In this case an internal LDO generates $V_{3P3V2}$ . Else, connect $V_{BUS2}$ and $V_{3P3V2}$ to an external 3.3 V power supply.                              |  |  |

| 28  | V <sub>BUS2</sub>  | _     | Input Power Supply for Side 2. If a 4.25 V to 5.5 V (example USB power bus) supply is available connect it to $V_{BUS2}$ . In this case an internal LDO generates $V_{3P3V2}$ . Else, connect $V_{BUS2}$ and $V_{3P3V2}$ to an external 3.3 V power supply.                                            |  |  |

# **5 Specifications**

# 5.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)(1) (2)

|                                         |                                                                                                                  | MIN  | MAX                                    | UNIT |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------|------|----------------------------------------|------|

| V <sub>BUS1</sub> , V <sub>BUS2</sub>   | V <sub>BUS</sub> supply voltage                                                                                  | -0.3 | 6                                      | V    |

| V <sub>CC1</sub> , V <sub>CC2</sub>     | V <sub>CC</sub> supply voltage                                                                                   | -0.3 | 6                                      | V    |

| V <sub>3P3V1</sub> , V <sub>3P3V2</sub> | 3.3-V input supply voltage                                                                                       | -0.3 | 4.25                                   | V    |

| V <sub>1P8V1</sub> , V <sub>1P8V2</sub> | 1.8-V input supply voltage                                                                                       | -0.3 | 2.1                                    | V    |

| V <sub>DPDM</sub>                       | Voltage on bus pins (UD+, UD-, DD+, DD-) 1000 total number of short events and cummulative duration of 1000 hrs. | -0.3 | 6                                      | V    |

| V <sub>IO</sub>                         | IO voltage range (V*OK, EQ*, CDPENZ*)                                                                            | -0.3 | V <sub>3P3Vx</sub> +0.3 <sup>(3)</sup> | V    |

| Io                                      | Output current on output pins (V*OK)                                                                             | -10  | 10                                     | mA   |

| TJ                                      | Junction temperature                                                                                             |      | 150                                    | °C   |

| T <sub>STG</sub>                        | Storage temperature                                                                                              | -65  | 150                                    | °C   |

- (1) Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) All voltage values are with respect to the local ground terminal (GND1 or GND2) and are peak voltage values.

- (3) Maximum voltage must not exceed 4.25 V

# 5.2 ESD Ratings

| V <sub>(ESD)</sub> | Electrostatic discharge | Human body model (HBM), per AEC Q100-002 <sup>(1)</sup>                                  | ±2000 | V |

|--------------------|-------------------------|------------------------------------------------------------------------------------------|-------|---|

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | ±500  | V |

- (1) AEC Q100-002 indicates that HBM stressting shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

- (3) Pins UDP, UDM, DDP, and DDM are rated for 1500V HBM

### **5.3 Recommended Operating Conditions**

Over operating free-air temperature range (unless otherwise noted)

|                    |                                                              | MIN  | NOM | MAX  | UNIT |

|--------------------|--------------------------------------------------------------|------|-----|------|------|

| V <sub>BUSx</sub>  | V <sub>BUS</sub> input voltage (inclusive of any ripple)     | 4.25 | 5   | 5.5  | V    |

| V <sub>3P3Vx</sub> | 3.3-V input supply voltage (inclusive of any ripple)         | 3.0  | 3.3 | 3.6  | V    |

| V <sub>CCx</sub>   | Input voltage to internal 1.8V LDO (inclusive of any ripple) | 2.4  | 3   | 5.5  | V    |

| V <sub>1P8Vx</sub> | 1.8-V input supply voltage (inclusive of any ripple)         | 1.71 | 1.8 | 1.94 | V    |

| T <sub>A</sub>     | Operating free-air temperature                               | -40  |     | 125  | °C   |

| T <sub>J</sub>     | Junction temperature                                         | -55  |     | 150  | °C   |

## **5.4 Thermal Information**

|                       |                                              | ISOUSB211 |      |

|-----------------------|----------------------------------------------|-----------|------|

|                       | THERMAL METRIC(1)                            | DP (SSOP) | UNIT |

|                       |                                              | 28 PINS   |      |

| R <sub>⊙JA</sub>      | Junction-to-ambient thermal resistance       | 44.2      | °C/W |

| R <sub>OJC(top)</sub> | Junction-to-case (top) thermal resistance    | 13.9      | °C/W |

| R <sub>OJB</sub>      | Junction-to-board thermal resistance         | 19.0      | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 3.3       | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 18.4      | °C/W |

| R <sub>OJC(bot)</sub> | Junction-to-case (bottom) thermal resistance | -         | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 5.5 Power Ratings

|                 | PARAMETER                              | TEST CONDITIONS                                                                                                                                                                                                                                                                                                    | MIN | TYP | MAX  | UNIT |

|-----------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| ISOUSB211       |                                        |                                                                                                                                                                                                                                                                                                                    |     |     |      |      |

| P <sub>D</sub>  | Maximum power dissipation (both sides) | $\begin{aligned} &V_{BUS1} = V_{BUS2} = V_{CC1} = V_{CC2} = 5.5 \text{ V, T}_J \\ &= 150^{\circ}\text{C, R}_L = 50 \ \Omega \text{ each on DD- and} \\ ⅅ+ \text{ to GNDx, input a 240-MHz 50\% duty} \\ &\text{cycle adifferential 0 to 400mV swing} \\ &\text{signal on UD- and UD+} \end{aligned}$               |     |     | 1210 | mW   |

| P <sub>D1</sub> | Maximum power dissipation (side-1)     | $\begin{split} &V_{BUS1} = V_{BUS2} = V_{CC1} = V_{CC2} = 5.5 \text{ V}, \text{ T}_{J} \\ &= 150^{\circ}\text{C}, \text{ R}_{L} = 50 \Omega \text{ each on DD- and} \\ ⅅ+ \text{ to GNDx, input a 240-MHz 50\% duty} \\ &\text{cycle adifferential 0 to 400mV swing} \\ &\text{signal on UD- and UD+} \end{split}$ |     |     | 605  | mW   |

| P <sub>D2</sub> | Maximum power dissipation (side-2)     | $V_{BUS1} = V_{BUS2} = V_{CC1} = V_{CC2} = 5.5 \text{ V}, T_{J}$<br>= 150°C, R <sub>L</sub> = 50 Ω each on DD- and<br>DD+ to GNDx, input a 240-MHz 50% duty<br>cycle adifferential 0 to 400mV swing<br>signal on UD- and UD+                                                                                       |     |     | 605  | mW   |

Product Folder Links: ISOUSB211-Q1

# 5.6 Insulation Specifications

| PARAMETER                                             | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SPECIFIC ATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | UNIT                                        |

|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

|                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DP-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -                                           |

| 664-1                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                             |

| External clearance <sup>(1)</sup>                     | Side 1 to side 2 distance through air                                                                                                                                                                                                                                                                                                                                                                                                                            | >8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | mm                                          |

| External Creepage <sup>(1)</sup>                      | Side 1 to side 2 distance across package surface                                                                                                                                                                                                                                                                                                                                                                                                                 | >8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | mm                                          |

| Distance through the insulation                       | Minimum internal gap (internal clearance)                                                                                                                                                                                                                                                                                                                                                                                                                        | >21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | μm                                          |

| Comparative tracking index                            | IEC 60112; UL 746A                                                                                                                                                                                                                                                                                                                                                                                                                                               | >600                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V                                           |

| Material Group                                        | According to IEC 60664-1                                                                                                                                                                                                                                                                                                                                                                                                                                         | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                             |

| Overvoltere esteren.                                  | Rated mains voltage ≤ 600 V <sub>RMS</sub>                                                                                                                                                                                                                                                                                                                                                                                                                       | I-IV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                             |

| Overvoitage category                                  | Rated mains voltage ≤ 1000 V <sub>RMS</sub>                                                                                                                                                                                                                                                                                                                                                                                                                      | 1-111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                             |

| IEC 60747-17 (VDE 0884-17) <sup>(2)</sup>             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                             |

| Maximum repetitive peak isolation voltage             | AC voltage (bipolar)                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>PK</sub>                             |

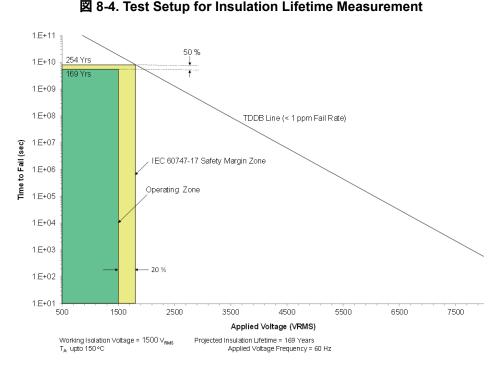

| Maximum isolation working voltage                     | AC voltage (sine wave); time-dependent dielectric breakdown (TDDB) test;                                                                                                                                                                                                                                                                                                                                                                                         | 1500                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>RMS</sub>                            |

|                                                       | DC voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>DC</sub>                             |

| Maximum transient isolation voltage                   | $V_{TEST} = V_{IOTM}$ , t = 60 s (qualification); $V_{TEST} = 1.2 \times V_{IOTM}$ , t = 1 s (100% production)                                                                                                                                                                                                                                                                                                                                                   | 8000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>PK</sub>                             |

| Maximum impulse voltage <sup>(3)</sup>                | Tested in air, 1.2/50-us waveform per IEC 62368-1                                                                                                                                                                                                                                                                                                                                                                                                                | 8000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>PK</sub>                             |