www.ti.com

# **LM101AJAN Operational Amplifiers**

Check for Samples: LM101AJAN

### **FEATURES**

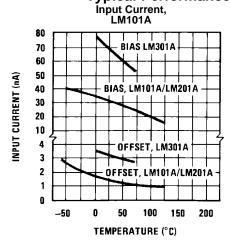

- Offset Voltage 3 mV Maximum Over **Temperature**

- Input Current 100 nA Maximum Over **Temperature**

- Offset Current 20 nA Maximum Over **Temperature**

- **Ensured Drift Characteristics**

- Offsets Ensured Over Entire Common Mode and Supply Voltage Ranges

- Slew Rate of 10 V/µS as a Summing Amplifier

### DESCRIPTION

The LM101A is a general purpose operational amplifier which features improved performance over industry standards such as the LM709. Advanced processing techniques make possible an order of magnitude reduction in input currents, and a redesign of the biasing circuitry reduces the temperature drift of input current. Improved specifications include:

- Offset voltage 3 mV maximum over temperature

- Input current 100 nA maximum over temperature

- Offset current 20 nA maximum over temperature

- Ensured drift characteristics

- Offsets ensured over entire common mode and supply voltage ranges

- Slew rate of 10V/µs as a summing amplifier

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

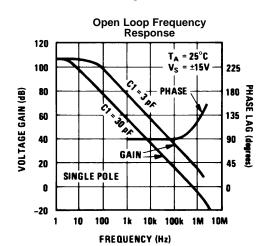

This amplifier offers many features which make its application nearly foolproof: overload protection on the input and output, no latch-up when the common mode range is exceeded, and freedom from oscillations and compensation with a single 30 pF capacitor. It has advantages over internally compensated amplifiers in that the frequency compensation can be tailored to the particular application. For example, in low frequency circuits it can be overcompensated for increased stability margin. Or the compensation can be optimized to give more than a factor of ten improvement in high frequency performance for most applications.

In addition, the device provides better accuracy and lower noise in high impedance circuitry. The low input currents also make it particularly well suited for long interval integrators or timers, sample and hold circuits and low frequency waveform generators. Further, replacing circuits where matched transistor pairs buffer the inputs of conventional IC op amps, it can give lower offset voltage and a drift at a lower cost.

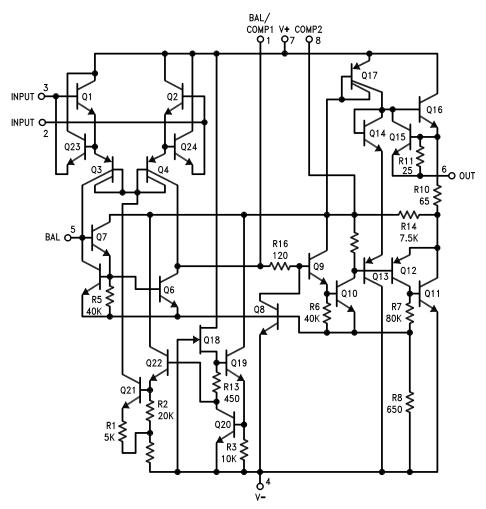

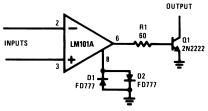

### **Schematic**

Pin connections shown are for 8-pin packages

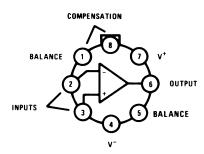

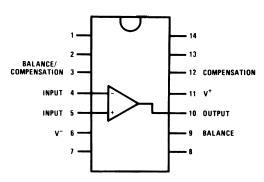

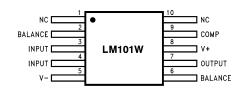

### **Connection Diagrams**

BALANCE/ 1

COMPENSATION 2

INPUT 3

V - 4

BALANCE

8 COMPENSATION

7 V +

6 OUTPUT

5 BALANCE

Pin 4 connected to case.

Figure 1. (Top View)

TO-99 Package

See Package Number LMC

Figure 3. (Top View)

CDIP Package

See NS Package Number J

Figure 2. (Top View)

CDIP Package

See Package Number NAB0008A

Figure 4. (Top View)

CLGA Package

See NS Package Number NAD0010A

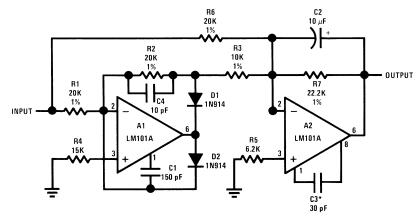

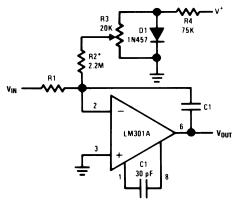

### Fast AC/DC Converter

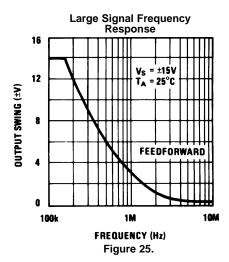

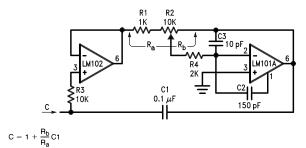

Feedforward compensation can be used to make a fast full wave rectifier without a filter.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### SNOSAJ8A-JANUARY 2006-REVISED MARCH 2013

# Absolute Maximum Ratings<sup>(1)</sup>

| TIDOCIATO MAXIMA                      |                  |                  |                         | -                               |

|---------------------------------------|------------------|------------------|-------------------------|---------------------------------|

| Supply Voltage                        |                  |                  |                         | ±22V                            |

| Differential Input Voltage            |                  |                  |                         | ±30V                            |

| Input Voltage (2)                     |                  |                  |                         | ±15V                            |

| Output Short Circuit Duration         | Continuous       |                  |                         |                                 |

| Operating Ambient Temp. Ra            | ange             |                  |                         | -55°C ≤ T <sub>A</sub> ≤ +125°C |

| T <sub>J</sub> Max                    |                  |                  |                         | 150°C                           |

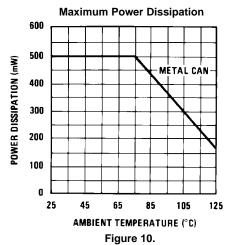

| Power Dissipation at T <sub>A</sub> = | LMC-Package      |                  | Still Air)              | 750 mW                          |

| 25°C <sup>(3)</sup>                   |                  |                  | (500 LF / Min Air Flow) | 1,200 mW                        |

|                                       | NAB0008A-Package | )                | (Still Air)             | 1,000 mW                        |

|                                       |                  |                  | (500 LF / Min Air Flow) | 1,500 mW                        |

|                                       | J-Package        |                  | (Still Air)             | 1,200mW                         |

|                                       |                  |                  | (500 LF / Min Air Flow) | 2,000mW                         |

|                                       | NAD0010A-Package | <b>e</b>         | (Still Air)             | 500mW                           |

|                                       |                  |                  | (500 LF / Min Air Flow) | 800mW                           |

|                                       |                  | LMC Daskage      | (Still Air)             | 165°C/W                         |

|                                       |                  | LMC-Package      | (500 LF / Min Air Flow) | 89°C/W                          |

|                                       |                  | NAROOOA Resisera | (Still Air)             | 128°C/W                         |

|                                       | 0                | NAB0008A-Package | (500 LF / Min Air Flow) | 75°C/W                          |

|                                       | $\theta_{JA}$    | I Dealesse       | (Still Air)             | 98°C/W                          |

| Thermal Resistance                    |                  | J-Package        | (500 LF / Min Air Flow) | 59°C/W                          |

| mermai Resistance                     |                  | NADOO10A Dookogo | (Still Air)             | 233°C/W                         |

|                                       |                  | NAD0010A-Package | (500 LF / Min Air Flow) | 155°C/W                         |

|                                       |                  | LMC-Package      |                         | 39°C/W                          |

|                                       | O (Typical)      | NAB0008A-Package |                         | 26°C/W                          |

| θ <sub>JC</sub> (Typical)             |                  | J-Package        |                         | 24°C/W                          |

|                                       |                  | NAD0010A-Package |                         | 26°C/W                          |

| Storage Temperature Range             |                  |                  |                         | -65°C ≤ T <sub>A</sub> ≤ +150°C |

| Lead Temperature (Soldering           | g, 10 sec.)      |                  |                         | 300°C                           |

| ESD Tolerance <sup>(4)</sup>          |                  |                  |                         | 3000V                           |

<sup>(1)</sup> Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating ratings indicate conditions for which the device is intended to be functional, but do no ensure specific performance limits. For ensured specifications and test conditions, see the Electrical Characteristics. The ensured specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

For supply voltages less than ±15V, the absolute maximum input voltage is equal to the supply voltage.

<sup>(3)</sup> The maximum power dissipation must be derated at elevated temperatures and is dictated by T<sub>Jmax</sub> (maximum junction temperature), θ<sub>JA</sub> (package junction to ambient thermal resistance), and T<sub>A</sub> (ambient temperature). The maximum allowable power dissipation at any temperature is P<sub>Dmax</sub> = (T<sub>Jmax</sub> - T<sub>A</sub>) / θ<sub>JA</sub> or the number given in the Absolute Maximum Ratings, whichever is lower.

(4) Human body model, 100 pF discharged through 1.5 kΩ.

# **Quality Conformance Inspection**

Mil-Std-883, Method 5005 - Group A

| Subgroup | Description         | Temp (°C) |

|----------|---------------------|-----------|

| 1        | Static tests at     | 25        |

| 2        | Static tests at     | 125       |

| 3        | Static tests at     | -55       |

| 4        | Dynamic tests at    | 25        |

| 5        | Dynamic tests at    | 125       |

| 6        | Dynamic tests at    | -55       |

| 7        | Functional tests at | 25        |

| 8A       | Functional tests at | 125       |

| 8B       | Functional tests at | -55       |

| 9        | Switching tests at  | 25        |

| 10       | Switching tests at  | 125       |

| 11       | Switching tests at  | -55       |

### **LM101JAN Electrical Characteristics DC Parameters**

The following conditions apply to all parameters, unless otherwise specified  $V_{CC}$  = ±20V,  $V_{CM}$  = 0V,  $R_S$  =  $50\Omega$

| Symbol           | Parameters                   | Conditions                                      | Notes | Min  | Max  | Unit | Sub-<br>groups |

|------------------|------------------------------|-------------------------------------------------|-------|------|------|------|----------------|

| V <sub>IO</sub>  | Input Offset Voltage         | +V <sub>CC</sub> = 35V, -V <sub>CC</sub> = -5V, |       | -2.0 | +2.0 | mV   | 1              |

|                  |                              | $V_{CM} = -15V$                                 |       | -3.0 | +3.0 | mV   | 2, 3           |

|                  |                              | +V <sub>CC</sub> = 5V, -V <sub>CC</sub> = -35V, |       | -2.0 | +2.0 | mV   | 1              |

|                  |                              | $V_{CM} = +15V$                                 |       | -3.0 | +3.0 | mV   | 2, 3           |

|                  | V <sub>CM</sub>              | $V_{CM} = 0V$                                   |       | -2.0 | +2.0 | mV   | 1              |

|                  |                              |                                                 |       | -3.0 | +3.0 | mV   | 2, 3           |

|                  |                              | $+V_{CC} = 5V, -V_{CC} = -5V,$                  |       | -2.0 | +2.0 | mV   | 1              |

|                  |                              | $V_{CM} = 0V$                                   |       | -3.0 | +3.0 | mV   | 2, 3           |

| Ю                | Input Offset Current         | +V <sub>CC</sub> = 35V, -V <sub>CC</sub> = -5V, |       | -10  | +10  | nA   | 1, 2           |

|                  |                              | $V_{CM} = -15V, R_S = 100K\Omega$               |       | -20  | +20  | nA   | 3              |

|                  |                              | +V <sub>CC</sub> = 5V, -V <sub>CC</sub> = -35V, |       | -10  | +10  | nA   | 1, 2           |

|                  |                              | $V_{CM} = +15V, R_S = 100K\Omega$               |       | -20  | +20  | nA   | 3              |

|                  |                              | $V_{CM} = 0V$ , $R_S = 100K\Omega$              |       | -10  | +10  | nA   | 1, 2           |

|                  |                              |                                                 |       | -20  | +20  | nA   | 3              |

|                  |                              | +V <sub>CC</sub> = 5V, -V <sub>CC</sub> = -5V,  |       | -10  | +10  | nA   | 1, 2           |

|                  |                              | $V_{CM} = 0V, R_S = 100K\Omega$                 |       | -20  | +20  | nA   | 3              |

| ±l <sub>IB</sub> | Input Bias Current           | $+V_{CC} = 35V, -V_{CC} = -5V,$                 |       | -0.1 | 75   | nA   | 1, 2           |

|                  |                              | $V_{CM} = -15V$ , $R_S = 100K\Omega$            |       | -0.1 | 100  | nA   | 3              |

|                  |                              | +V <sub>CC</sub> = 5V, -V <sub>CC</sub> = -35V, |       | -0.1 | 75   | nA   | 1, 2           |

|                  |                              | $V_{CM} = +15V, R_S = 100K\Omega$               |       | -0.1 | 100  | nA   | 3              |

|                  |                              | $V_{CM} = 0V$ , $R_S = 100K\Omega$              |       | -0.1 | 75   | nA   | 1, 2           |

|                  |                              |                                                 |       | -0.1 | 100  | nA   | 3              |

|                  |                              | +V <sub>CC</sub> = 5V, -V <sub>CC</sub> = -5V,  |       | -0.1 | 75   | nA   | 1, 2           |

|                  |                              | $V_{CM} = 0V$ , $R_S = 100K\Omega$              |       | -0.1 | 100  | nA   | 3              |

| +PSRR            | Power Supply Rejection Ratio | +V <sub>CC</sub> = 10V, -V <sub>CC</sub> = -20V |       | -50  | +50  | μV/V | 1              |

|                  |                              |                                                 |       | -100 | +100 | μV/V | 2, 3           |

| PSRR             | Power Supply Rejection Ratio | +V <sub>CC</sub> = 20V, -V <sub>CC</sub> = -10V |       | -50  | +50  | μV/V | 1              |

|                  |                              |                                                 |       | -100 | +100 | μV/V | 2, 3           |

# **LM101JAN Electrical Characteristics DC Parameters (continued)**

The following conditions apply to all parameters, unless otherwise specified

$V_{CC} = \pm 20V, V_{CM} = 0V, R_S = 50\Omega$

| Symbol                       | Parameters                               | Conditions                                                      | Notes              | Min  | Max  | Unit  | Sub-<br>groups |

|------------------------------|------------------------------------------|-----------------------------------------------------------------|--------------------|------|------|-------|----------------|

| CMRR                         | Common Mode Rejection Ratio              | $V_{CC} = \pm 35V$ to $\pm 5V$ ,<br>$V_{CM} = \pm 15V$          |                    | 80   |      | dB    | 1, 2, 3        |

| +V <sub>IO</sub> Adj         | Adjustment for Input Offset Voltage      |                                                                 |                    | 4.0  |      | mV    | 1, 2, 3        |

| -V <sub>IO</sub> Adj         | Adjustment for Input Offset Voltage      |                                                                 |                    |      | -4.0 | mV    | 1, 2, 3        |

| +I <sub>OS</sub>             | Output Short Circuit Current             | $+V_{CC} = 15V, -V_{CC} = -15V,$<br>t \le 25mS, $V_{CM} = -15V$ |                    | -60  |      | mA    | 1, 2, 3        |

| -l <sub>OS</sub>             | Output Short Circuit Current             | $+V_{CC} = 15V, -V_{CC} = -15V,$<br>t \le 25mS, $V_{CM} = +15V$ |                    |      | +60  | mA    | 1, 2, 3        |

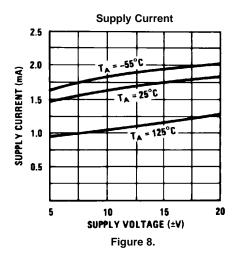

| Icc                          | Power Supply Current                     | +V <sub>CC</sub> = 15V, -V <sub>CC</sub> = -15V                 |                    |      | 3.0  | mA    | 1              |

|                              |                                          |                                                                 |                    |      | 2.32 | mA    | 2              |

|                              |                                          |                                                                 |                    |      | 3.5  | mA    | 3              |

| $\Delta V_{IO}$ / $\Delta T$ | Temperature Coefficient of Input         | -55°C ≤ T <sub>A</sub> ≤ +25°C                                  | See <sup>(1)</sup> | -18  | +18  | μV/°C | 2              |

|                              | Offset Voltage                           | +25°C ≤ T <sub>A</sub> ≤ +125°C                                 | See <sup>(1)</sup> | -15  | +15  | μV/°C | 3              |

| Δ Ι <sub>ΙΟ</sub> / ΔΤ       | Temperature Coefficient of Input         | -55°C ≤ T <sub>A</sub> ≤ +25°C                                  | See <sup>(2)</sup> | -200 | +200 | pA/°C | 2              |

|                              | Offset Current                           | +25°C ≤ T <sub>A</sub> ≤ +125°C                                 | See <sup>(2)</sup> | -100 | +100 | pA/°C | 3              |

| -A <sub>VS</sub>             | Large Signal (Open Loop) Voltage         | $R_L = 2K\Omega$ , $V_O = -15V$                                 | See (3)            | 50   |      | V/mV  | 4              |

|                              | Gain                                     |                                                                 | See <sup>(3)</sup> | 25   |      | V/mV  | 5, 6           |

|                              |                                          | $R_{L} = 10K\Omega, V_{O} = -15V$                               | See <sup>(3)</sup> | 50   |      | V/mV  | 4              |

|                              |                                          |                                                                 | See <sup>(3)</sup> | 25   |      | V/mV  | 5, 6           |

| +A <sub>VS</sub>             | Large Signal (Open Loop) Voltage         | $R_L = 2K\Omega$ , $V_O = +15V$                                 | See <sup>(3)</sup> | 50   |      | V/mV  | 4              |

|                              | Gain                                     |                                                                 | See <sup>(3)</sup> | 25   |      | V/mV  | 5, 6           |

|                              |                                          | $R_L = 10K\Omega, V_O = +15V$                                   | See <sup>(3)</sup> | 50   |      | V/mV  | 4              |

|                              |                                          |                                                                 | See <sup>(3)</sup> | 25   |      | V/mV  | 5, 6           |

| A <sub>VS</sub>              | Large Signal (Open Loop) Voltage<br>Gain | $V_{CC} = \pm 5V$ , $R_L = 2K\Omega$ , $V_O = \pm 2V$           | See <sup>(3)</sup> | 10   |      | V/mV  | 4, 5, 6        |

|                              |                                          | $V_{CC} = \pm 5V$ , $R_L = 10K\Omega$ , $V_O = \pm 2V$          | See <sup>(3)</sup> | 10   |      | V/mV  | 4, 5, 6        |

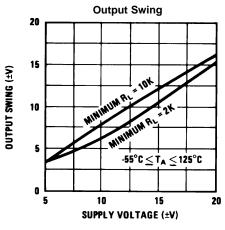

| +V <sub>OP</sub>             | Output Voltage Swing                     | $R_L = 10K\Omega$ , $V_{CM} = -20V$                             |                    | +16  |      | V     | 4, 5, 6        |

|                              |                                          | $R_L = 2K\Omega$ , $V_{CM} = -20V$                              |                    | +15  |      | V     | 4, 5, 6        |

| -V <sub>OP</sub>             | Output Voltage Swing                     | $R_L = 10K\Omega$ , $V_{CM} = 20V$                              |                    |      | -16  | V     | 4, 5, 6        |

|                              |                                          | $R_L = 2K\Omega$ , $V_{CM} = 20V$                               |                    |      | -15  | V     | 4, 5, 6        |

Submit Documentation Feedback

<sup>(1)</sup> Calculated parameter

(2) Calculated parameter

(3) Datalog reading of K = V/mV.

### **LM101AJAN Electrical Characteristics AC Parameters**

The following conditions apply to all parameters, unless otherwise specified  $% \left( 1\right) =\left( 1\right) \left( 1$

$V_{CC}=\pm 20V,\ V_{CM}=0V,\ R_S=50\Omega$

| Symbol           | Parameter       | Conditions                               | Notes | Min | Max | Units         | Sub-<br>groups |

|------------------|-----------------|------------------------------------------|-------|-----|-----|---------------|----------------|

| +SR              | Slew Rate       | $A_V = 1$ , $V_I = -5V$ to $+5V$         |       | 0.3 |     | V/µS          | 7              |

| -SR              | Slew Rate       | $A_V = 1$ , $V_I = +5V$ to -5V           |       | 0.3 |     | V/µS          | 7              |

| TR <sub>TR</sub> | Rise Time       | $A_V = 1, V_I = 50 \text{mV}$            |       |     | 800 | nS            | 7              |

| TR <sub>OS</sub> | Overshoot       | $A_V = 1, V_I = 50 \text{mV}$            |       |     | 25  | %             | 7              |

| NI <sub>BB</sub> | Noise Broadband | BW = 10Hz to 5KHz, $R_S = 0\Omega$       |       |     | 15  | $\mu V_{RMS}$ | 7              |

| NI <sub>PC</sub> | Noise Popcorn   | BW = 10Hz to 5KHz,<br>$R_S = 100K\Omega$ |       |     | 80  | $\mu V_{PK}$  | 7              |

### LM101AJAN Electrical Characteristics DC Parameters: Drift Values

The following conditions apply to all parameters, unless otherwise specified  $% \left( 1\right) =\left( 1\right) \left( 1$

$V_{CC}=\pm 20V,\ V_{CM}=0V,\ R_S=50\Omega$

Delta calculations performed on JAN S devices at group B, Subgroup 5 only.

| Symbol            | Parameter            | Conditions                         | Notes | Min  | Max | Units | Sub-<br>groups |  |

|-------------------|----------------------|------------------------------------|-------|------|-----|-------|----------------|--|

| V <sub>IO</sub>   | Input Offset Voltage | $V_{CM} = 0V$                      |       | -0.5 | 0.5 | mV    | 1              |  |

| ± I <sub>IB</sub> | Input Bias Current   | $V_{CM} = 0V$ , $R_S = 100K\Omega$ |       | -7.5 | 7.5 | nA    | 1              |  |

Product Folder Links: *LM101AJAN*

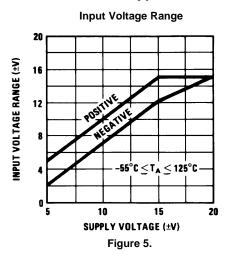

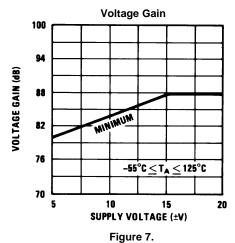

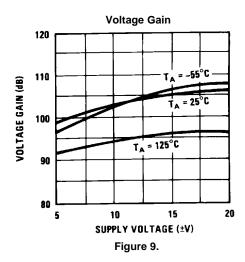

# **Typical Performance Characteristics LM101A**

Figure 6.

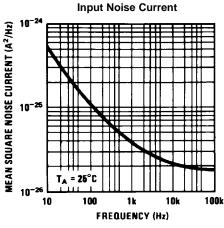

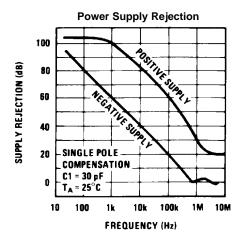

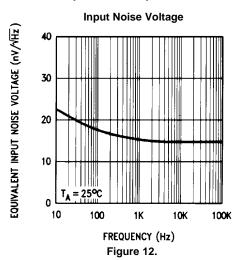

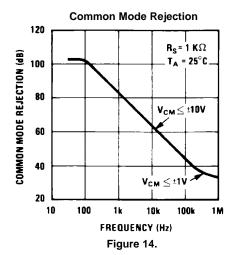

### Typical Performance Characteristics LM101A (continued)

Figure 11.

Figure 13.

Figure 15.

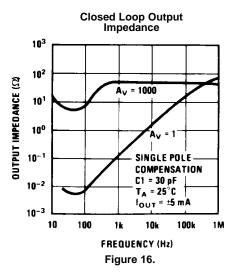

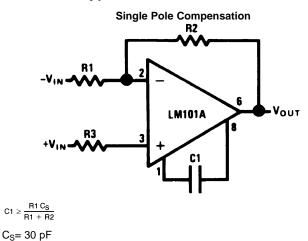

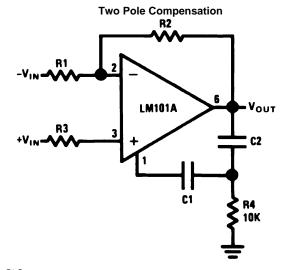

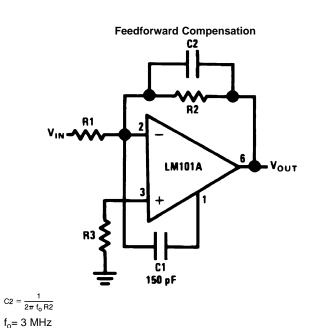

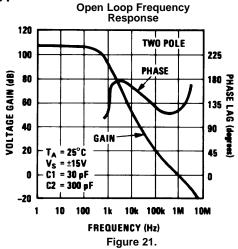

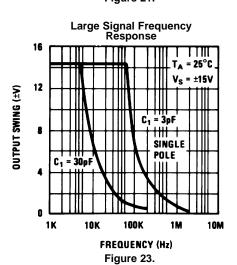

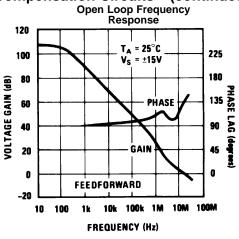

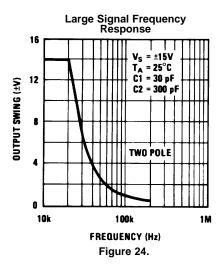

# Typical Performance Characteristics for Various Compensation Circuits<sup>(1)</sup>

$C1 \ge \frac{R1 C_S}{R1 + R2}$   $C_S = 30 \text{ pF}$ C2 = 10 C1

Figure 17.

Figure 19.

Figure 18.

Figure 20.

# Typical Performance Characteristics for Various Compensation Circuits<sup>(1)</sup> (continued)

Figure 22.

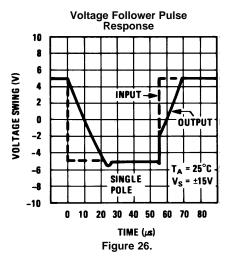

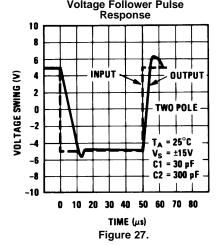

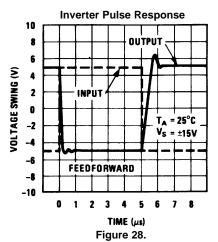

# Typical Performance Characteristics for Various Compensation Circuits<sup>(1)</sup> (continued) Voltage Follower Pulse Response Inverter Pulse Response

### TYPICAL APPLICATIONS(2)

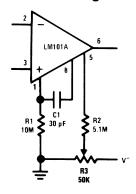

### Variable Capacitance Multiplier

†May be zero or equal to parallel combination of R1 and R2 for minimum offset.

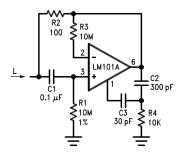

#### **Simulated Inductor**

L ≃ R1 R2 C1  $R_S = R2$  $R_P = R1$

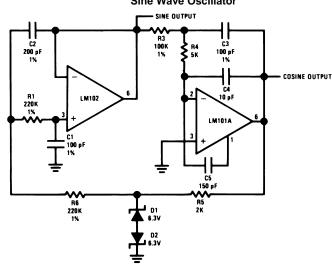

#### **Sine Wave Oscillator**

$f_0 = 10 \text{ kHz}$

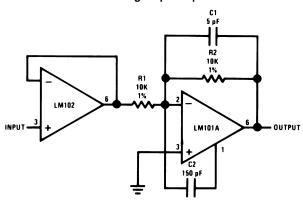

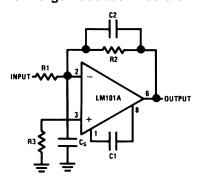

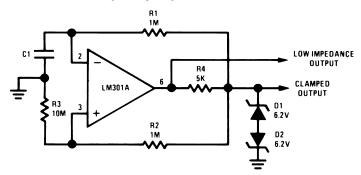

# Fast Inverting Amplifier with High Input Impedance

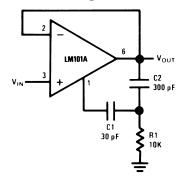

### **Integrator with Bias Current Compensation**

\*Adjust for zero integrator drift. Current drift typically 0.1 nA/°C over -55°C to +125°C temperature range.

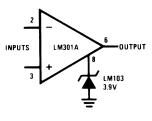

### Pin connections shown are for 8-pin packages.

# Application Hints<sup>(2)</sup>

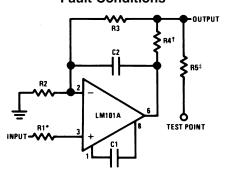

# Protecting Against Gross Fault Conditions

\*Protects input

†Protects output

‡Protects output—not needed when R4 is used.

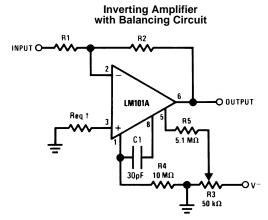

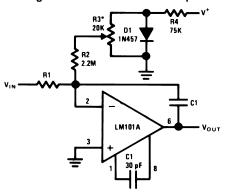

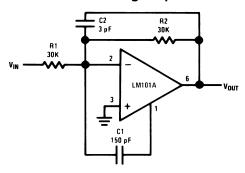

# Compensating for Stray Input Capacitances or Large Feedback Resistor

$$C2 = \frac{\text{R1 C}_{S}}{\text{R2}}$$

### **Isolating Large Capacitive Loads**

Although the LM101A is designed for trouble free operation, experience has indicated that it is wise to observe certain precautions given below to protect the devices from abnormal operating conditions. It might be pointed out that the advice given here is applicable to practically any IC op amp, although the exact reason why may differ with different devices.

Submit Documentation Feedback

When driving either input from a low-impedance source, a limiting resistor should be placed in series with the input lead to limit the peak instantaneous output current of the source to something less than 100 mA. This is especially important when the inputs go outside a piece of equipment where they could accidentally be connected to high voltage sources. Large capacitors on the input (greater than  $0.1~\mu F$ ) should be treated as a low source impedance and isolated with a resistor. Low impedance sources do not cause a problem unless their output voltage exceeds the supply voltage. However, the supplies go to zero when they are turned off, so the isolation is usually needed.

The output circuitry is protected against damage from shorts to ground. However, when the amplifier output is connected to a test point, it should be isolated by a limiting resistor, as test points frequently get shorted to bad places. Further, when the amplifier drives a load external to the equipment, it is also advisable to use some sort of limiting resistance to preclude mishaps.

Precautions should be taken to insure that the power supplies for the integrated circuit never become reversed—even under transient conditions. With reverse voltages greater than 1V, the IC will conduct excessive current, fusing internal aluminum interconnects. If there is a possibility of this happening, clamp diodes with a high peak current rating should be installed on the supply lines. Reversal of the voltage between V<sup>+</sup> and V<sup>-</sup> will always cause a problem, although reversals with respect to ground may also give difficulties in many circuits.

The minimum values given for the frequency compensation capacitor are stable only for source resistances less than 10 k $\Omega$ , stray capacitances on the summing junction less than 5 pF and capacitive loads smaller than 100 pF. If any of these conditions are not met, it becomes necessary to overcompensate the amplifier with a larger compensation capacitor. Alternately, lead capacitors can be used in the feedback network to negate the effect of stray capacitance and large feedback resistors or an RC network can be added to isolate capacitive loads.

Although the LM101A is relatively unaffected by supply bypassing, this cannot be ignored altogether. Generally it is necessary to bypass the supplies to ground at least once on every circuit card, and more bypass points may be required if more than five amplifiers are used. When feed-forward compensation is employed, however, it is advisable to bypass the supply leads of each amplifier with low inductance capacitors because of the higher frequencies involved.

# Typical Applications (3)

### Standard Compensation and Offset Balancing Circuit

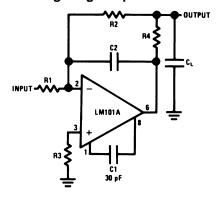

### **Fast Voltage Follower**

Power Bandwidth: 15 kHz

Slew Rate: 1V/µs

### **Fast Summing Amplifier**

Power Bandwidth: 250 kHz Small Signal Bandwiidth: 3.5 MHz

Slew Rate: 10V/µs

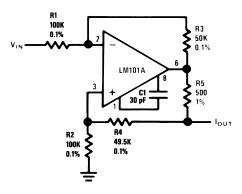

### **Bilateral Current Source**

$I_{OUT} = \frac{R3 \, V_{IN}}{R1 \, R5}$

R3 = R4 + R5

R1 = R2

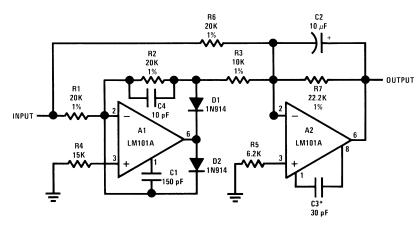

### Fast AC/DC Converter

Feedforward compensation can be used to make a fast full wave rectifier without a filter.

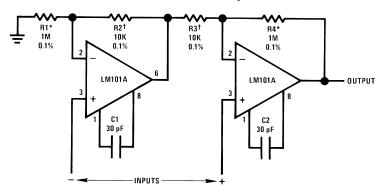

### Instrumentation Amplifier

R1 = R4; R2 = R3

$$A_V = 1 + \frac{R1}{R2}$$

\*,† Matching determines CMRR.

### **Integrator with Bias Current Compensation**

\*Adjust for zero integrator drift. Current drift typically 0.1 nA/°C over 0°C to +70°C temperature range.

# Voltage Comparator for Driving RTL Logic or High Current Driver

### **Low Frequency Square Wave Generator**

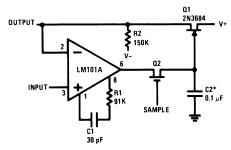

### Low Drift Sample and Hold

\*Polycarbonate-dielectric capacitor

### **REVISION HISTORY SECTION**

| Date<br>Released | Revision | Section                         | Originator | Changes                                                                                                    |

|------------------|----------|---------------------------------|------------|------------------------------------------------------------------------------------------------------------|

| 01/05/06         | A        | New Release to corporate format | L. Lytle   | 1 MDS datasheets converted into one Corp. datasheet format. MJLM101A-X Rev 1A0 datasheet will be archived. |

| 03/20/13         | А        | All                             | -          | Changed layout of National Data Sheet to TI format                                                         |

Product Folder Links: LM101AJAN

www.ti.com

om 23-Oct-2025

### **PACKAGING INFORMATION**

| Orderable part number | Status (1) | Material type | Package   Pins  | Package qty   Carrier    | <b>RoHS</b> (3) | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6)                                                   |

|-----------------------|------------|---------------|-----------------|--------------------------|-----------------|-------------------------------|----------------------------|--------------|--------------------------------------------------------------------|

| JL101ABCA             | Active     | Production    | CDIP (J)   14   | 25   TUBE                | No              | SNPB                          | Level-1-NA-UNLIM           | -55 to 125   | JL101ABCA<br>JM38510/10103BCA Q                                    |

| JL101ABGA             | Active     | Production    | TO-99 (LMC)   8 | 20   JEDEC<br>TRAY (5+1) | Yes             | Call TI                       | Level-1-NA-UNLIM           | -55 to 125   | JL101ABGA<br>JM38510/10103BGA Q<br>ACO<br>JM38510/10103BGA Q<br>>T |

| JL101ABPA             | Active     | Production    | CDIP (NAB)   8  | 40   TUBE                | No              | SNPB                          | Level-1-NA-UNLIM           | -55 to 125   | JL101ABPA Q<br>JM38510/<br>10103BPA ACO<br>10103BPA >T             |

| JM38510/10103BCA      | Active     | Production    | CDIP (J)   14   | 25   TUBE                | No              | SNPB                          | Level-1-NA-UNLIM           | -55 to 125   | JL101ABCA<br>JM38510/10103BCA Q                                    |

| JM38510/10103BGA      | Active     | Production    | TO-99 (LMC)   8 | 20   JEDEC<br>TRAY (5+1) | Yes             | Call TI                       | Level-1-NA-UNLIM           | -55 to 125   | JL101ABGA<br>JM38510/10103BGA Q<br>ACO<br>JM38510/10103BGA Q<br>>T |

| JM38510/10103BPA      | Active     | Production    | CDIP (NAB)   8  | 40   TUBE                | No              | SNPB                          | Level-1-NA-UNLIM           | -55 to 125   | JL101ABPA Q<br>JM38510/<br>10103BPA ACO<br>10103BPA >T             |

| M38510/10103BCA       | Active     | Production    | CDIP (J)   14   | 25   TUBE                | No              | SNPB                          | Level-1-NA-UNLIM           | -55 to 125   | JL101ABCA<br>JM38510/10103BCA Q                                    |

| M38510/10103BGA       | Active     | Production    | TO-99 (LMC)   8 | 20   JEDEC<br>TRAY (5+1) | Yes             | Call TI                       | Level-1-NA-UNLIM           | -55 to 125   | JL101ABGA<br>JM38510/10103BGA Q<br>ACO<br>JM38510/10103BGA Q<br>>T |

| M38510/10103BPA       | Active     | Production    | CDIP (NAB)   8  | 40   TUBE                | No              | SNPB                          | Level-1-NA-UNLIM           | -55 to 125   | JL101ABPA Q<br>JM38510/<br>10103BPA ACO<br>10103BPA >T             |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

### PACKAGE OPTION ADDENDUM

www.ti.com 23-Oct-2025

- (2) Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

- (3) RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

- (4) Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

- (5) MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

- (6) Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 21-May-2025

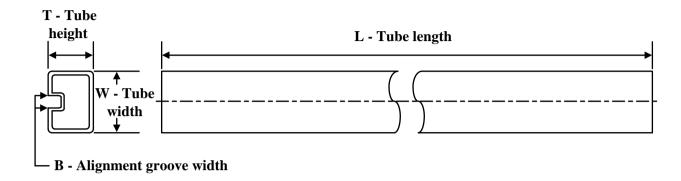

### **TUBE**

\*All dimensions are nominal

| Device           | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|------------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| JL101ABCA        | J            | CDIP         | 14   | 25  | 506.98 | 15.24  | 13440  | NA     |

| JL101ABPA        | NAB          | CDIP         | 8    | 40  | 506.98 | 15.24  | 13440  | NA     |

| JM38510/10103BCA | J            | CDIP         | 14   | 25  | 506.98 | 15.24  | 13440  | NA     |

| JM38510/10103BPA | NAB          | CDIP         | 8    | 40  | 506.98 | 15.24  | 13440  | NA     |

| M38510/10103BCA  | J            | CDIP         | 14   | 25  | 506.98 | 15.24  | 13440  | NA     |

| M38510/10103BPA  | NAB          | CDIP         | 8    | 40  | 506.98 | 15.24  | 13440  | NA     |

www.ti.com 21-May-2025

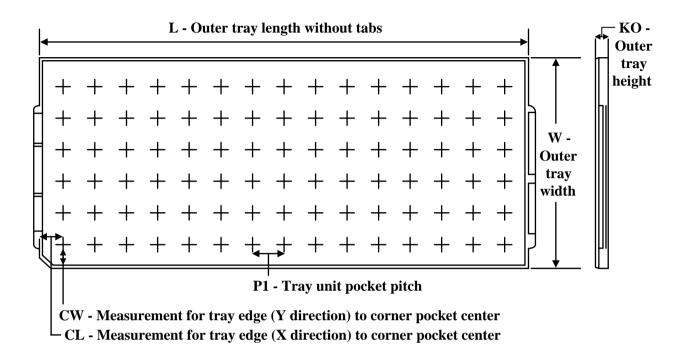

### **TRAY**

Chamfer on Tray corner indicates Pin 1 orientation of packed units.

#### \*All dimensions are nominal

| Device           | Package<br>Name | Package<br>Type | Pins | SPQ | Unit array<br>matrix | Max<br>temperature<br>(°C) | L (mm) | W<br>(mm) | Κ0<br>(μm) | P1<br>(mm) | CL<br>(mm) | CW<br>(mm) |

|------------------|-----------------|-----------------|------|-----|----------------------|----------------------------|--------|-----------|------------|------------|------------|------------|

| JL101ABGA        | LMC             | TO-CAN          | 8    | 20  | 2 X 10               | 150                        | 126.49 | 61.98     | 8890       | 11.18      | 12.95      | 18.54      |

| JM38510/10103BGA | LMC             | TO-CAN          | 8    | 20  | 2 X 10               | 150                        | 126.49 | 61.98     | 8890       | 11.18      | 12.95      | 18.54      |

| M38510/10103BGA  | LMC             | TO-CAN          | 8    | 20  | 2 X 10               | 150                        | 126.49 | 61.98     | 8890       | 11.18      | 12.95      | 18.54      |

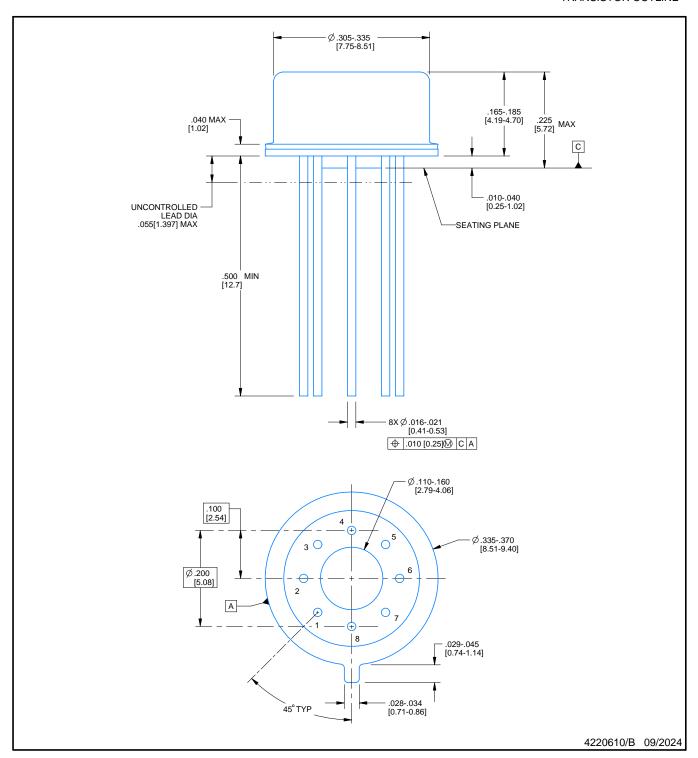

TRANSISTOR OUTLINE

### NOTES:

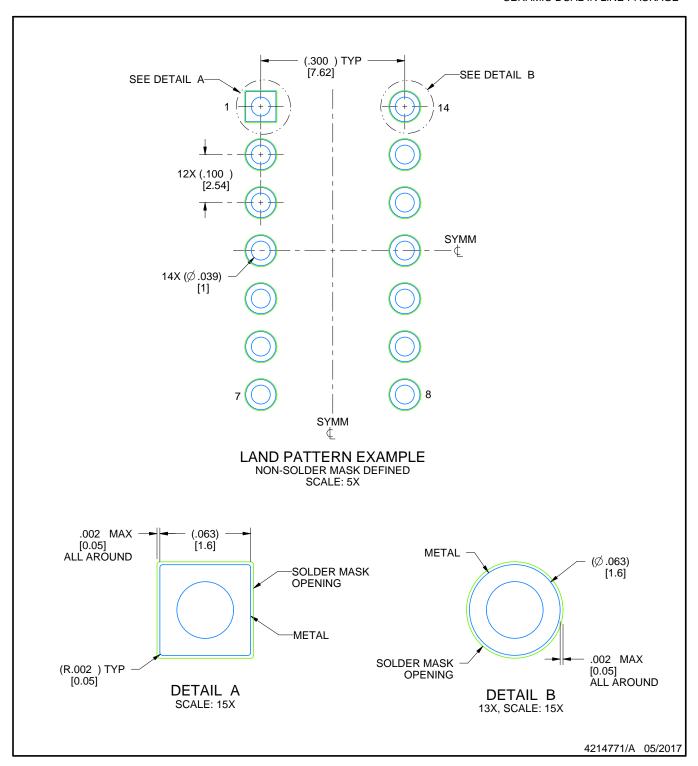

- 1. All linear dimensions are in inches [millimeters]. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. Pin numbers shown for reference only. Numbers may not be marked on package.

- 4. Reference JEDEC registration MO-002/TO-99.

TRANSISTOR OUTLINE

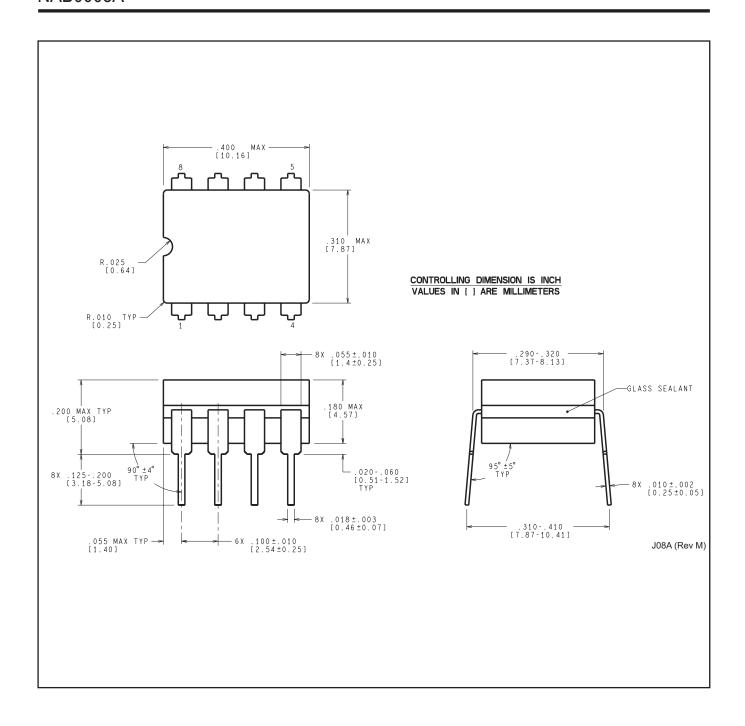

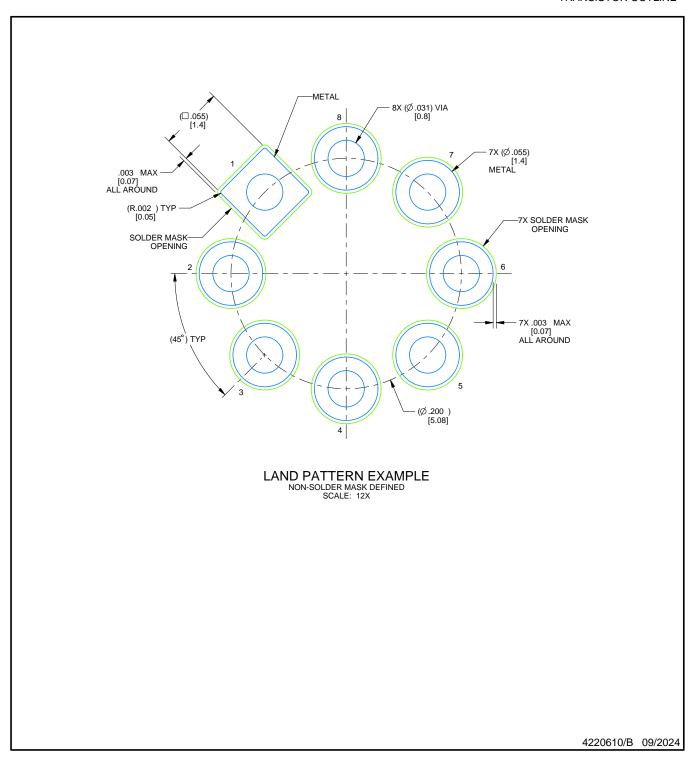

CERAMIC DUAL IN LINE PACKAGE

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

4040083-5/G

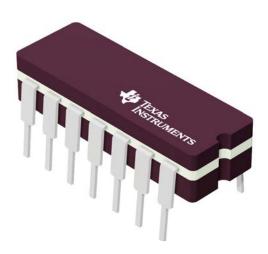

CERAMIC DUAL IN LINE PACKAGE

### NOTES:

- 1. All controlling linear dimensions are in inches. Dimensions in brackets are in millimeters. Any dimension in brackets or parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This package is hermitically sealed with a ceramic lid using glass frit.

- His package is remitted by sealed with a ceramic its using glass mit.

Index point is provided on cap for terminal identification only and on press ceramic glass frit seal only.

Falls within MIL-STD-1835 and GDIP1-T14.

CERAMIC DUAL IN LINE PACKAGE

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you fully indemnify TI and its representatives against any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale, TI's General Quality Guidelines, or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products. Unless TI explicitly designates a product as custom or customer-specified, TI products are standard, catalog, general purpose devices.

TI objects to and rejects any additional or different terms you may propose.

Copyright © 2025, Texas Instruments Incorporated

Last updated 10/2025