# LM5005 75V、2.5A 広入力電圧対応ステップダウンスイッチングレギュレータ

## 1 特長

- 高効率の DC/DC 降圧コンバータ

- 広い入力電圧範囲: 7V ~ 75V

- 出力電圧可変: 最小 1.225V

- 出力電流: 最大 2.5A

- 接合部温度範囲: -40°C ~ 125°C

- 75V、160mΩ の降圧用 MOSFET 内蔵

- EN55022 および CISPR 22 の EMI 規格に適合

- 帰還電圧精度: ±1.5%

- エミュレートされたピーク電流モード制御

- 超高速のラインおよび負荷過渡応答

- スイッチング周波数: 50kHz ~ 500kHz

- コントローラまたは周辺装置の周波数同期入力

- 低  $V_{OUT}$  の最小 PWM オン時間: 80ns

- プリバイアス出力への単調スタートアップ

- 内部高耐圧 VCC バイアス電源レギュレータ

- VCC への補助バイアス電源オプション

- 追従機能付きの設定可能なソフトスタート

- 高精度のスタンバイおよびシャットダウン入力

- ヒステリシス付きプログラマブル入力 UVLO

- リモートシャットダウンおよびスタンバイ制御

- サイクル単位の過電流保護

- VCC とゲート駆動の UVLO 保護

- ヒステリシス付きのサーマルシャットダウン保護

- 放熱強化型 20 ピン HTSSOP パッケージ

- WEBENCH® Power Designer により、LM5005 を使用するカスタム設計を作成

## 2 アプリケーション

- 高効率のポイントオブロードレギュレータ

- 通信インフラストラクチャ

- ファクトリオートメーション / 制御

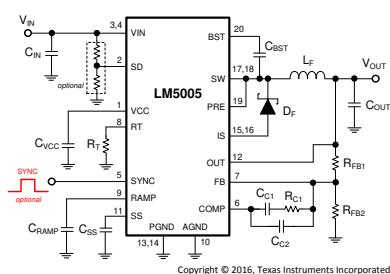

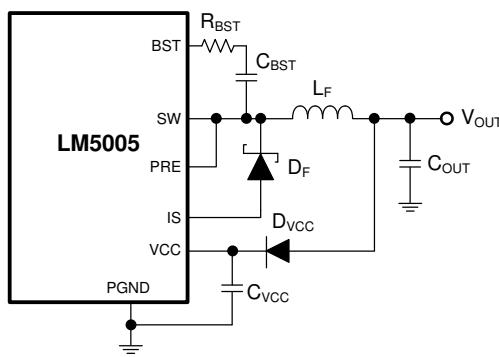

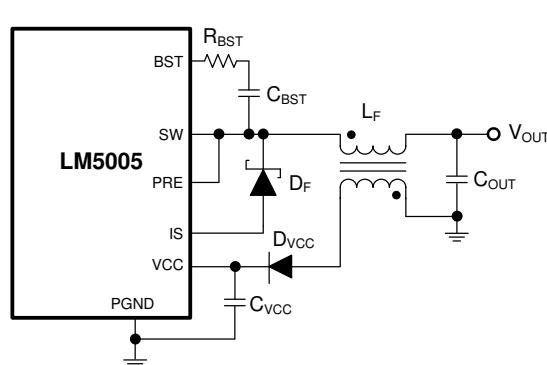

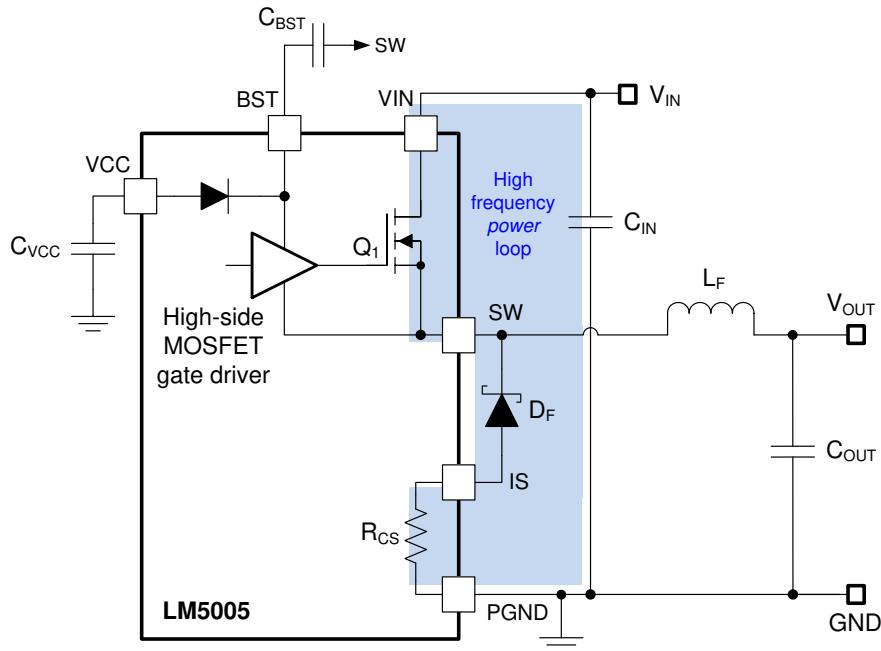

代表的なアプリケーション回路

## 3 説明

LM5005 高耐圧降圧型コンバータには、最小限の数の外付け部品で効率的な高耐圧スイッチングレギュレータを実装するため必要なすべての機能が搭載されています。この使いやすいコンバータは、7V ~ 75V の入力電圧範囲で動作し、最大 2.5A の出力電流を供給します。この制御ループアーキテクチャは、ノイズ耐性を高めるために、エミュレートされた電流ランプを用いた電流モード制御に基づいています。電流モード制御には、ラインフィードフォワードと、サイクル単位の過電流保護が組み込まれており、ループ補正が簡単に実行できます。エミュレーションによる制御ランプを使用することで、PWM回路のノイズ感受性が低下し、入力電圧の高いアプリケーションで必要な小さいデューティサイクルを確実に制御できます。

スイッチング周波数は、抵抗で 50kHz から 500kHz の範囲にプログラム可能です。EMI を低減するため、発振器同期ピンにより、複数の LM5005 レギュレータ同士を自動同期させることも、外部クロック信号に同期させることもできます。追加の保護機能として、構成可能なソフトスタート、外部電源のトラッキング、サーマルシャットダウンと自動回復、リモートシャットダウン機能が搭載されています。

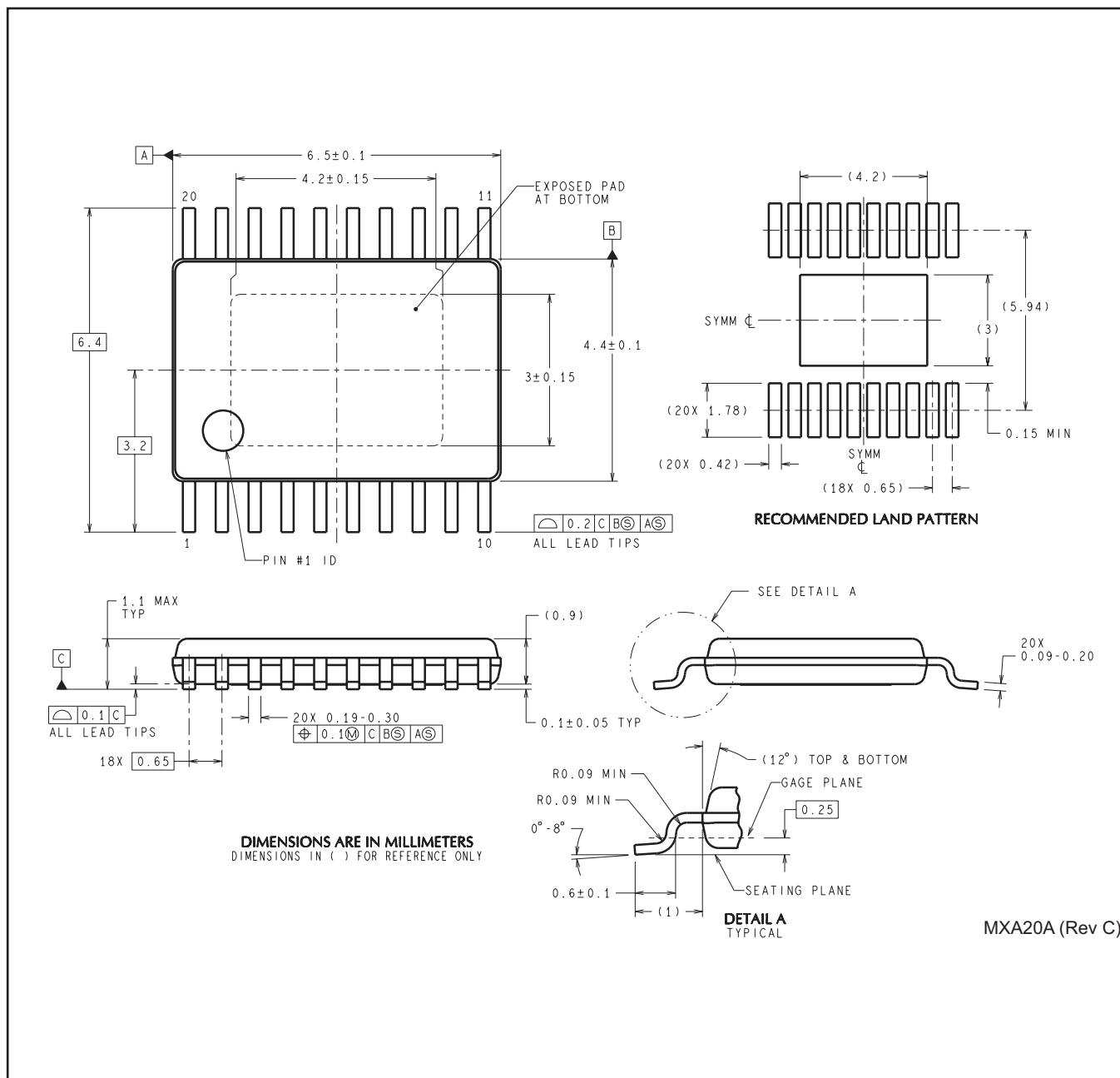

LM5005 は、放熱パッド付きの 20 ピン HTSSOP パッケージで提供されており、この露出パッドを基板に半田付けすることで、接合部から PCB への熱抵抗を低く抑えることができます。カスタムレギュレータを設計する場合は、WEBENCH® Power Designer を使用して LM5005 を構成します。

### パッケージ情報

| 部品番号   | パッケージ <sup>(1)</sup> | パッケージサイズ <sup>(2)</sup> |

|--------|----------------------|-------------------------|

| LM5005 | PWP (HTSSOP, 20)     | 6.50mm × 4.40mm         |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

(2) パッケージサイズ(長さ × 幅)は公称値であり、該当する場合はピンも含まれます。

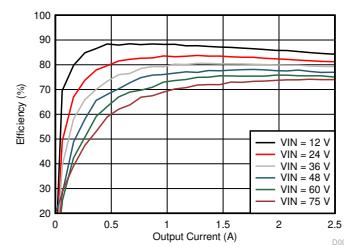

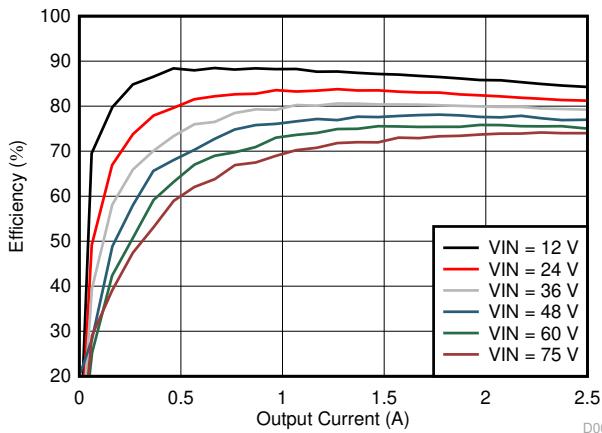

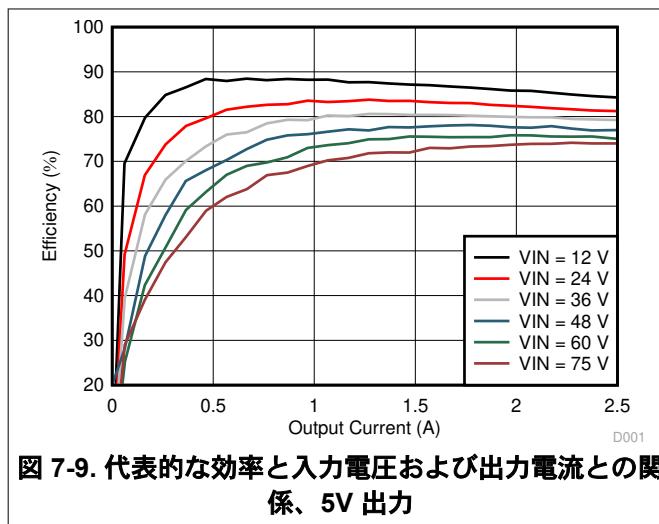

代表的な事例の効率、 $V_{OUT} = 5V$

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール(機械翻訳)を使用していることがあります。TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                          |           |                                     |           |

|--------------------------|-----------|-------------------------------------|-----------|

| <b>1 特長</b> .....        | <b>1</b>  | <b>7 アプリケーションと実装</b> .....          | <b>17</b> |

| <b>2 アプリケーション</b> .....  | <b>1</b>  | <b>7.1 アプリケーション情報</b> .....         | <b>17</b> |

| <b>3 説明</b> .....        | <b>1</b>  | <b>7.2 代表的なアプリケーション</b> .....       | <b>18</b> |

| <b>4 ピン構成および機能</b> ..... | <b>3</b>  | <b>7.3 電源に関する推奨事項</b> .....         | <b>28</b> |

| <b>5 仕様</b> .....        | <b>5</b>  | <b>7.4 レイアウト</b> .....              | <b>29</b> |

| 5.1 絶対最大定格.....          | 5         | <b>8 デバイスおよびドキュメントのサポート</b> .....   | <b>34</b> |

| 5.2 ESD 定格.....          | 5         | 8.1 サード・パーティ製品に関する免責事項.....         | 34        |

| 5.3 推奨動作条件.....          | 5         | 8.2 デバイス サポート.....                  | 34        |

| 5.4 熱に関する情報.....         | 5         | 8.3 ドキュメントのサポート.....                | 34        |

| 5.5 電気的特性.....           | 6         | 8.4 ドキュメントの更新通知を受け取る方法.....         | 35        |

| 5.6 スイッチング特性.....        | 7         | 8.5 サポート・リソース.....                  | 35        |

| 5.7 代表的特性.....           | 7         | 8.6 商標.....                         | 35        |

| <b>6 詳細説明</b> .....      | <b>10</b> | 8.7 静電気放電に関する注意事項.....              | 35        |

| 6.1 概要.....              | 10        | 8.8 用語集.....                        | 35        |

| 6.2 機能ブロック図.....         | 10        | <b>9 改訂履歴</b> .....                 | 35        |

| 6.3 機能説明.....            | 10        | <b>10 メカニカル、パッケージ、および注文情報</b> ..... | 36        |

| 6.4 デバイスの機能モード.....      | 15        |                                     |           |

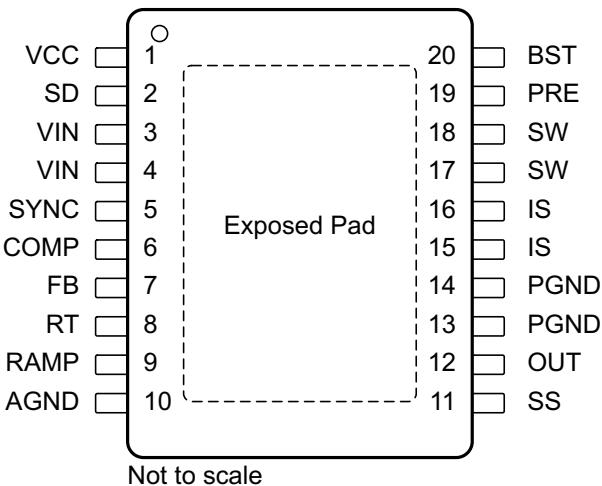

## 4 ピン構成および機能

図 4-1. PWP パッケージ 20 ピン HTSSOP 上面図

表 4-1. ピンの機能

| ピン   | タイプ <sup>(1)</sup> | 説明 |

|------|--------------------|----|

| 名称   | 番号                 |    |

| AGND | 10                 | G  |

| BST  | 20                 | P  |

| COMP | 6                  | O  |

| EP   | —                  | P  |

| FB   | 7                  | I  |

| IS   | 15, 16             | P  |

| OUT  | 12                 | I  |

| PGND | 13, 14             | G  |

| PRE  | 19                 | P  |

| RAMP | 9                  | I  |

| RT   | 8                  | I  |

| SD   | 2                  | I  |

| SS   | 11                 | I  |

| SW   | 17, 18             | P  |

表 4-1. ピンの機能 (続き)

| ピン   |      | タイプ <sup>(1)</sup> | 説明                                                                                                                                                       |

|------|------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称   | 番号   |                    |                                                                                                                                                          |

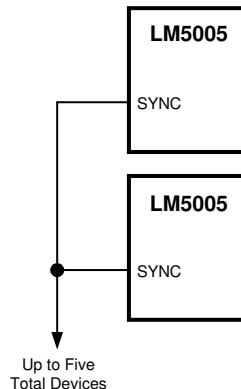

| SYNC | 5    | I/O                | 発振器の同期入力または同期出力。内部発振器は、外部プルダウン デバイスを使用して外部クロックと同期可能です。複数の LM5005 レギュレータは、SYNC ピンを接続することで同期させることができます。                                                    |

| VCC  | 1    | I                  | バイアス レギュレータの出力。VCC は VIN を 9V まで追跡します。9V を超えると、VCC は 7V にレギュレートされます。0.1µF ~ 1µF のセラミック デカップリング コンデンサが必要です。このピンに外部電圧 (7.5V ~ 14V) を印加することで、内部消費電力を低減できます。 |

| VIN  | 3, 4 | P                  | 入力供給電圧 (公称動作範囲): 7V~75V。                                                                                                                                 |

(1) G=グランド、I = 入力、O = 出力、P = 電源、I/O = 双方向

## 5 仕様

### 5.1 絶対最大定格

自由空気での動作温度範囲内 (特に記述のない限り)<sup>(1) (2)</sup>

|                           |                  | 最小値                  | 最大値 | 単位 |

|---------------------------|------------------|----------------------|-----|----|

| VIN から GND へ              |                  | 76                   |     | V  |

| BST から GND へ              |                  | 90                   |     | V  |

| PRE から GND へ              |                  | 76                   |     | V  |

| SW から GND (定常状態)          |                  | -1.5                 | 76  | V  |

| BST から VCC                |                  | 76                   |     | V  |

| VCC から GND へ              |                  | 14                   |     | V  |

| BST から SW へ               |                  | 14                   |     | V  |

| OUT から GND へ              |                  | V <sub>VIN</sub> に制限 |     | V  |

| SD, SYNC, SS, FB から GND へ |                  | 7                    |     | V  |

| 保存温度                      | T <sub>stg</sub> | -65                  | 150 | °C |

- (1) 「絶対最大定格」を超える動作は、デバイスに恒久的な損傷を与える可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用した場合、本デバイスは完全に機能するとは限らず、このことが本デバイスの信頼性、機能、性能に影響を及ぼし、本デバイスの寿命を縮める可能性があります。

- (2) 軍用/航空宇宙用仕様のデバイスをお求めの場合は、供給状況および仕様について テキサス・インストゥルメンツの販売特約店または営業所にお問い合わせください。

### 5.2 ESD 定格

|                                        |                                                        | 値     | 単位 |

|----------------------------------------|--------------------------------------------------------|-------|----|

| V <sub>(ESD)</sub> 静電放電 <sup>(3)</sup> | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>   | ±2000 | V  |

|                                        | デバイス帶電モデル (CDM)、JEDEC 仕様 JESD22-C101 準拠 <sup>(2)</sup> | ±750  |    |

- (1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

- (2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

- (3) 人体モデルは、100pF コンデンサから抵抗 1.5kΩ を介して各ピンに放電させた場合です。

### 5.3 推奨動作条件

自由空気での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                  |          | 最小値 | 最大値 | 単位 |

|------------------|----------|-----|-----|----|

| V <sub>IN</sub>  | 入力電圧     | 7   | 75  | V  |

| I <sub>OUT</sub> | 出力電流     | 0   | 2.5 | A  |

| T <sub>J</sub>   | 動作時接合部温度 | -40 | 125 | °C |

- (1) 推奨動作条件は、デバイスが機能すると想定されている条件を示します。保証された仕様および試験条件については、電気的特性を参照してください。

### 5.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup>  | LM5005              |      | 単位   |  |

|-----------------------|---------------------|------|------|--|

|                       | PWP (HTSSOP)        |      |      |  |

|                       | 20 ピン               |      |      |  |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗        | 35.2 | °C/W |  |

| R <sub>θJC(top)</sub> | 接合部からケース (上面) への熱抵抗 | 17.8 | °C/W |  |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗        | 15.5 | °C/W |  |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ    | 0.4  | °C/W |  |

| 熱評価基準 <sup>(1)</sup> |                   | LM5005 | 単位   |

|----------------------|-------------------|--------|------|

| PWP (HTSSOP)         |                   |        |      |

| 20 ピン                |                   |        |      |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ  | 15.3   | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース(底面)への熱抵抗 | 1.2    | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体およびICパッケージの熱評価基準』アプリケーションレポートを参照してください。

## 5.5 電気的特性

標準値は  $T_J = 25^\circ\text{C}$ 、 $V_{IN} = 48\text{V}$ 、 $R_T = 32.4\text{k}\Omega$  に対応します。特に記述のない限り、最小および最大の限界値は、 $-40^\circ\text{C} \sim 125^\circ\text{C}$  の接合部温度範囲全体に対するものです。<sup>(1)</sup>

| パラメータ                  | テスト条件                   | 最小値 <sup>(2)</sup>                                 | 標準値   | 最大値 <sup>(2)</sup> | 単位               |

|------------------------|-------------------------|----------------------------------------------------|-------|--------------------|------------------|

| <b>スタートアップ レギュレータ</b>  |                         |                                                    |       |                    |                  |

| $V_{CC}$ Reg           | $V_{CC}$ レギュレータ出力       | 6.85                                               | 7.15  | 7.45               | V                |

|                        | $V_{CC}$ LDO モード ターンオフ  |                                                    | 9     |                    | V                |

|                        | $V_{CC}$ 電流制限           | $V_{CC} = 0\text{V}$ 、                             | 25    |                    | mA               |

| <b>VCC 電源</b>          |                         |                                                    |       |                    |                  |

|                        | $V_{CC}$ UVLO スレッショルド   | $V_{CC}$ の増加                                       | 5.03  | 5.35               | 5.67             |

|                        | $V_{CC}$ 低電圧のヒステリシス     |                                                    | 0.25  |                    | V                |

|                        | バイアス電流 ( $I_{IN}$ )     | $FB = 1.3\text{V}$ 、                               | 2     | 4.5                | mA               |

|                        | シャットダウン電流 ( $I_{IN}$ )  | $SD = 0\text{V}$ 、                                 | 48    | 85                 | $\mu\text{A}$    |

| <b>シャットダウン スレッショルド</b> |                         |                                                    |       |                    |                  |

|                        | シャットダウン スレッショルド         | 0.47                                               | 0.7   | 0.9                | V                |

|                        | シャットダウンのヒステリシス          |                                                    | 0.1   |                    | V                |

|                        | スタンバイ スレッショルド           | 1.17                                               | 1.225 | 1.28               | V                |

|                        | スタンバイ ヒステリシス            |                                                    | 0.1   |                    | V                |

|                        | SD ブルアップ電流ソース           |                                                    | 5     |                    | $\mu\text{A}$    |

| <b>スイッチ特性</b>          |                         |                                                    |       |                    |                  |

|                        | 降圧スイッチの $R_{DS(on)}$    | 170                                                | 340   |                    | $\text{m}\Omega$ |

|                        | 昇圧 UVLO                 |                                                    | 3.8   |                    | V                |

|                        | BOOST UVLO ヒステリシス       |                                                    | 0.8   |                    | V                |

|                        | ブリチャージスイッチ $R_{DS(on)}$ | 70                                                 |       |                    | $\Omega$         |

|                        | ブリチャージスイッチオン時間          | 265                                                |       |                    | ns               |

| <b>電流制限</b>            |                         |                                                    |       |                    |                  |

|                        | サイクルごとの電流制限遅延           | $RAMP = 2.5\text{V}$ 、                             | 75    |                    | ns               |

| <b>ソフト スタート</b>        |                         |                                                    |       |                    |                  |

|                        | SS 電流ソース                | 7                                                  | 10    | 14                 | $\mu\text{A}$    |

| <b>発振器</b>             |                         |                                                    |       |                    |                  |

|                        | Frequency1              | 180                                                | 200   | 220                | kHz              |

|                        | Frequency2              | $R_T = 11\text{k}\Omega$                           | 425   | 485                | 545              |

|                        | 同期ソース インピーダンス           |                                                    | 11    |                    | $\text{k}\Omega$ |

|                        | 同期シンク インピーダンス           |                                                    | 110   |                    | $\Omega$         |

|                        | SYNC スレッショルド(立ち下がり)     |                                                    | 1.4   |                    | V                |

|                        | SYNC 周波数                | $R_T = 11\text{k}\Omega$                           | 550   |                    | kHz              |

|                        | SYNC パルス幅の最小値           |                                                    | 15    |                    | ns               |

| <b>RAMP ジェネレータ</b>     |                         |                                                    |       |                    |                  |

|                        | ランプ電流 1                 | $V_{IN} = 60\text{V}$ 、 $V_{out} = 10\text{V}$ です。 | 235   | 275                | 315              |

|                        | ランプ電流 1                 | $V_{IN} = 36\text{V}$ 、 $V_{out} = 10\text{V}$ です。 | 136   | 160                | 184              |

|                        | ランプ電流 2                 | $V_{IN} = 10\text{V}$ 、 $V_{out} = 10\text{V}$ です。 | 18    | 25                 | 32               |

標準値は  $T_J = 25^\circ\text{C}$ 、 $V_{IN} = 48\text{V}$ 、 $R_T = 32.4\text{k}\Omega$  に対応します。特に記述のない限り、最小および最大の限界値は、 $-40^\circ\text{C} \sim 125^\circ\text{C}$  の接合部温度範囲全体に対するものです。<sup>(1)</sup>

| パラメータ                      | テスト条件                   | 最小値 <sup>(2)</sup> | 標準値   | 最大値 <sup>(2)</sup> | 単位               |

|----------------------------|-------------------------|--------------------|-------|--------------------|------------------|

| <b>PWM コンパレータ</b>          |                         |                    |       |                    |                  |

| 強制オフ時間                     |                         | 416                | 500   | 575                | ns               |

| 最小オン時間                     |                         |                    | 80    |                    | ns               |

| COMP から PWM へのコンパレータ オフセット |                         |                    | 0.7   |                    | V                |

| <b>エラー アンプ</b>             |                         |                    |       |                    |                  |

| 帰還電圧                       | $V_{fb} = \text{COMP.}$ | 1.207              | 1.225 | 1.243              | $\mu\text{V}$    |

| FB バイアス電流                  |                         |                    | 10    |                    | nA               |

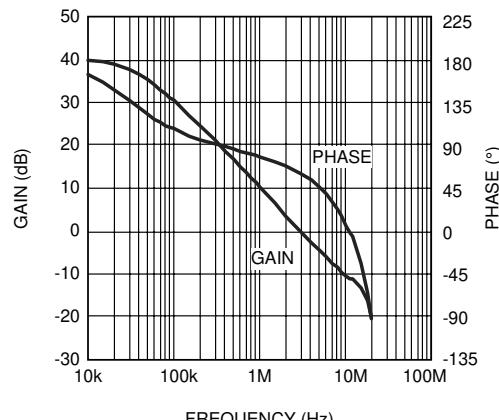

| DC ゲイン                     |                         |                    | 70    |                    | dB               |

| COMP シンク / ソース電流           |                         | 3                  |       |                    | mA               |

| ユニティ ゲイン 帯域幅               |                         |                    | 3     |                    | MHz              |

| <b>ダイオード検出抵抗</b>           |                         |                    |       |                    |                  |

| $D_{SENSE}$                |                         |                    | 42    |                    | $\text{m}\Omega$ |

| <b>サーマル シャットダウン</b>        |                         |                    |       |                    |                  |

| $T_{SD}$                   | サーマル シャットダウン スレッショルド    |                    | 165   |                    | $^\circ\text{C}$ |

| $T_{SD(HYS)}$              | サーマル シャットダウン ヒステリシス     |                    | 25    |                    | $^\circ\text{C}$ |

- (1) 接合部温度 ( $T_J, {}^\circ\text{C}$ ) は、周囲温度 ( $T_A, {}^\circ\text{C}$ ) および消費電力 (ワットでの PD) から次のように計算されます:  $T_J = T_A + (PD \times R_{\theta JA})$ 、ここで  $R_{\theta JA} ({}^\circ\text{C/W})$  は、[セクション 5.4](#) で提供されるパッケージの熱インピーダンスです。

- (2) 最小制限値および最大制限値は  $25^\circ\text{C}$  で 100% 生産テストされます。全動作温度範囲における制限値は、統計的品質管理 (SQC) 法を使用した相関により規定されています。これらの制限値を使って、テキサス インスツルメンツの平均出検品質限界 (AOQL) を計算しています。

## 5.6 スイッチング特性

自由気流での動作温度範囲内 (特に記述のない限り)。

| パラメータ         | テスト条件             | 最小値 | 標準値 | 最大値 | 単位 |

|---------------|-------------------|-----|-----|-----|----|

| $T_{ON-MIN}$  | 最小の制御可能な PWM オン時間 |     | 80  |     | ns |

| $T_{OFF-MIN}$ | 強制 PWM オフ時間       |     | 500 |     | ns |

| $T_{PRE}$     | 事前充電スイッチ オン時間     |     | 275 |     | ns |

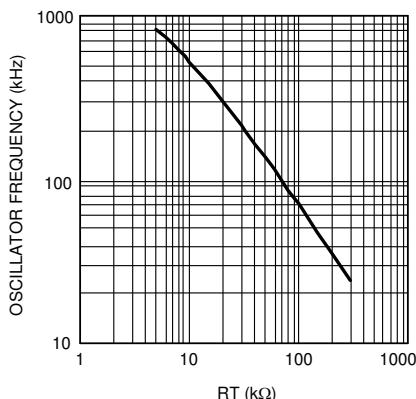

## 5.7 代表的特性

特に記述のない限り、 $V_{IN} = 48\text{V}$ 、 $V_{OUT} = 5\text{V}$  (回路設計については[代表的なアプリケーション](#)を参照)。

図 5-1. 発振器周波数と  $R_T$  との関係 $F_{OSC} = 200\text{kHz}$

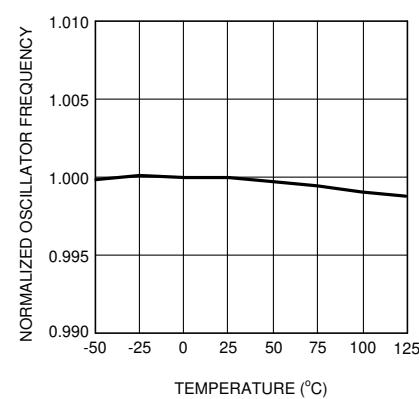

図 5-2. 発振器周波数と温度との関係

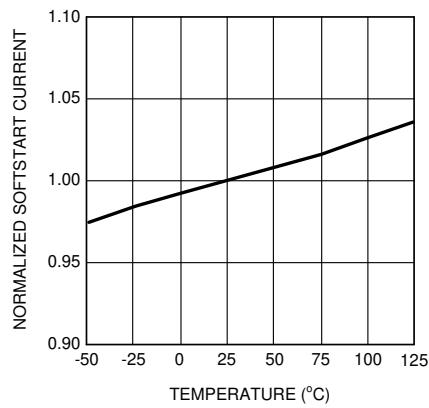

図 5-3. ソフトスタート電流と温度との関係

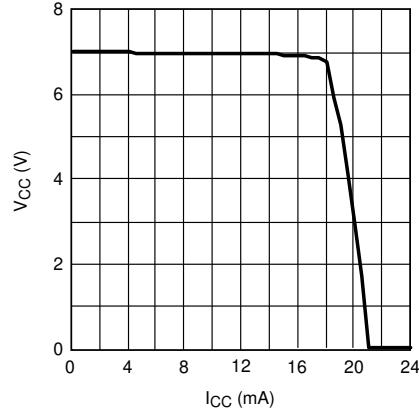

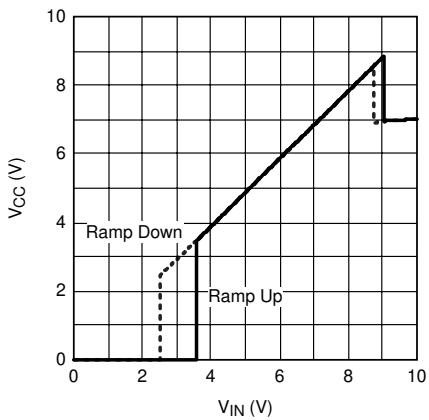

$V_{IN} = 12\text{V}$ 図 5-4.  $V_{CC}$  と  $I_{CC}$  との関係 $R_L = 7\text{k}\Omega$ 図 5-5.  $V_{CC}$  と  $V_{IN}$  との関係 $A_{VCL} = 101$

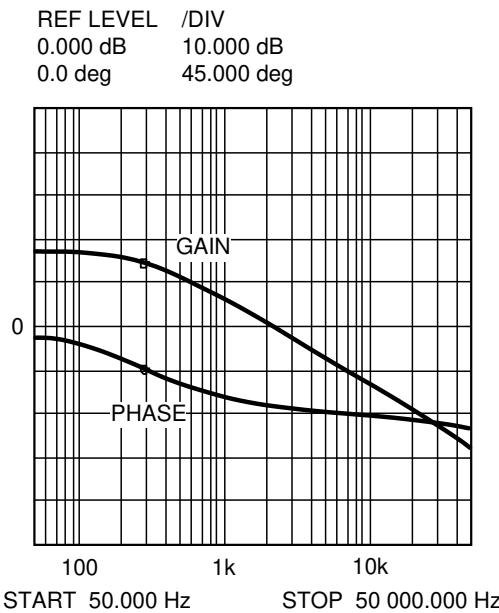

図 5-6. エラー アンプのゲインおよび位相

図 5-7. LM5005 評価ボード効率と  $I_{OUT}$  および  $V_{IN}$  との関係

## 6 詳細説明

### 6.1 概要

LM5005 の高電圧スイッチング レギュレータは、最小限の外付け部品で高効率な高電圧降圧レギュレータを実現するために必要なすべての機能を備えています。この使いやすいレギュレータは、75V の N チャネル降圧スイッチを内蔵しており、出力電流能力は 2.5A です。レギュレータ制御方式は、エミュレート電流ランプを使用した電流モード制御に基づいています。ピーク電流モード制御は、ライン フィード フォワード特性、サイクルごとの電流制限、そして簡易なループ補償を本質的に備えています。エミュレートされた制御ランプを使用することで、パルス幅変調回路のノイズ感度が減少し、入力電圧の高いアプリケーションで不可欠となる、デューティ サイクルの微細な処理を高い信頼性で実行できます。動作周波数は 50kHz ~ 500kHz の範囲でユーザーが設定可能です。発振器の同期ピンを使用すると、複数の LM5005 レギュレータを自己同期させることや、外部クロックに同期させることができます。出力電圧は、1.225V またはそれ以上に設定できます。故障保護機能には、サイクルごとの電流制限、サーマル シャットダウン、およびリモート シャットダウン機能が含まれます。このデバイスは、放熱を助ける露出パッド付きの 20 ピンの HTSSOP パッケージで供給されます。

セクション 6.2 に、LM5005 の機能ブロック図と代表的なアプリケーションを示します。LM5005 は、非安定化入力電圧から効率よく降圧する多様なアプリケーションで使用できます。このデバイスは、テレコム、産業用、および車載対応電源バス電圧範囲に最適です。

### 6.2 機能ブロック図

Copyright © 2016, Texas Instruments Incorporated

### 6.3 機能説明

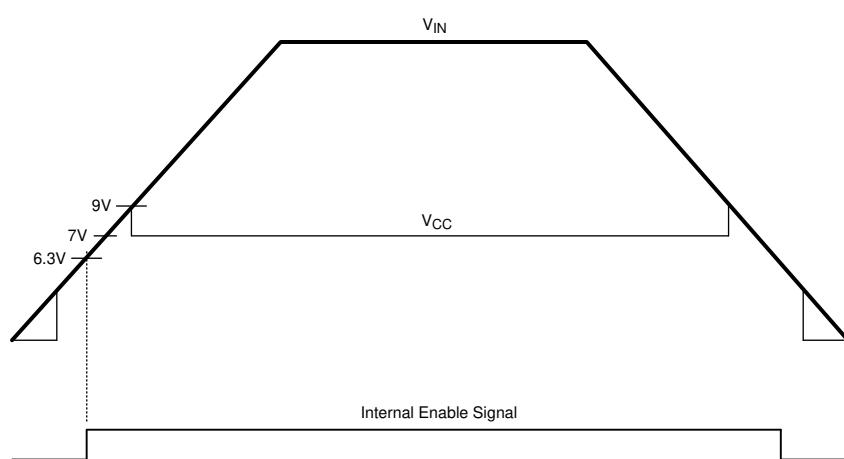

#### 6.3.1 高電圧起動レギュレータ

LM5005 にはデュアル モードの内部高耐圧起動レギュレータが内蔵されており、PWM コントローラとブートストラップ MOSFET ゲートドライバに VCC バイアス電源を供給します。VIN ピンは、最大 75V の入力電圧に直接接続します。入力電圧が 9V 未満の場合、低ドロップアウト スイッチを使用して VCC を VIN に直接接続します。この電源電圧範囲では、VCC は VIN とほぼ等しくなります。入力電圧が 9V を超える場合、低ドロップアウト スイッチは無効化され、VCC レギュレータが有効になって VCC を約 7V に維持します。このデュアルモード レギュレータを使用して、7V ~ 75V の広い動作範囲を実現しています。

VCC レギュレータの出力は、20mA に電流制限されています。電源オン時に、レギュレータは VCC ピンに接続されているコンデンサに電流を供給します。VCC ピンの電圧が VCC UVLO スレッショルドの 6.3V を超え、かつ SD ピンが 1.225V より高くなると、ソフトスタートシーケンスが開始されます。VCC が 5.3V を下回るか、SD ピンが 1.125V を下回るまでスイッチングは継続します。

IC の消費電力を低減するために、VCC ピンに補助電源電圧を印加します。補助電圧が 7.3V を超えると、内部レギュレータは実質的にシャットオフされ、IC の消費電力が低減します。VCC レギュレータシリーズのパストランジスタには、VCC と VIN との間のダイオードが含まれます。このダイオードは、通常動作において順方向バイアスとなってはなりません。したがって、補助 VCC 電圧が VIN 電圧を超えないようにする必要があります。

高電圧アプリケーションでは、VIN と PRE ピン電圧が 76V の絶対最大定格を超えないように十分注意してください。ラインまたは負荷の過渡時に、入力バスの電圧リンクが **絶対最大定格** を超えると、IC が損傷する可能性があります。PC 基板のレイアウトを丁寧に行い、VIN ピンおよび PGND ピンの近くに高品質な入力バイパスコンデンサを配置することが不可欠です。詳細については、[レイアウトガイドライン](#)を参照してください。

図 6-1. VIN と VCC のシーケンシング

### 6.3.2 シャットダウンおよびスタンバイ

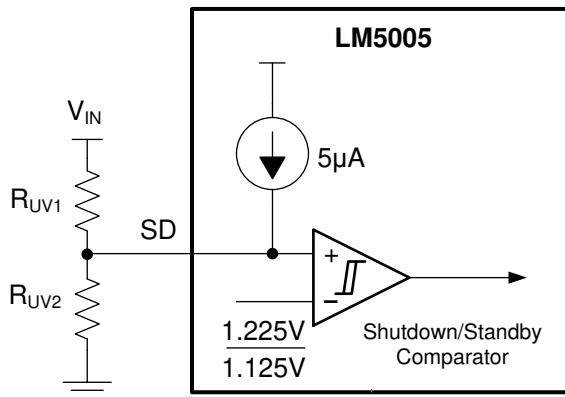

LM5005 には、デュアルレベル シャットダウン (SD) 回路が含まれています。SD ピンの電圧が 0.7V を下回ると、レギュレータは低電流シャットダウン モードになります。SD ピンの電圧が 0.7V より高く、1.225V を下回る場合、レギュレータはスタンバイ モードになります。スタンバイ モードでは、VCC レギュレータはアクティブですが、MOSFET スイッチングはディスエーブルです。SD ピン電圧が 1.225V を超えるとスイッチングが有効になり、通常動作が開始されます。内部の 5 $\mu$ A プルアップ電流源により、SD ピンがオープンのままになっている場合にレギュレータが完全に動作するように構成されます。

レギュレータの動作入力範囲を設定する場合は、VIN から GND への外付け分圧抵抗を使用します。デバイダは、VIN が望ましい動作範囲内にあるとき、SD ピンの電圧が 1.225V を超えるように設計します。外付け設定点分圧器の計算には、内部 5 $\mu$ A プルアップ電流源を含めます。シャットダウン スレッショルドとスタンバイ スレッショルドの両方に対して、0.1V のヒステリシスが含まれています。SD ピンの電圧が 7V を超えないことを必ず確認します。外付け分圧器を使用する場合、高入力電圧時に SD ピン電圧を制限するため、クランプが必要となる場合があります。

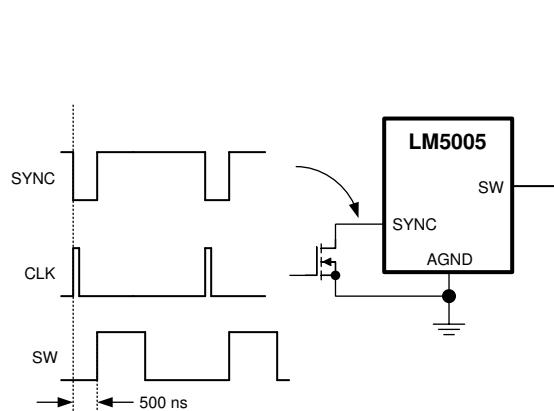

### 6.3.3 発振器と同期機能

LM5005 の発振周波数は、RT ピンと AGND ピンの間に接続する外付け抵抗  $R_T$  ひとつで設定されます。 $R_T$  抵抗は、LM5005 の RT ピンと AGND ピンの近くに配置します。目的のスイッチング周波数  $F_{SW}$  を設定するため、式 1 の  $R_T$  の抵抗を計算します。

$$R_T[\text{k}\Omega] = \frac{7407}{F_{SW}[\text{kHz}]} - 4.3 \quad (1)$$

SYNC ピンを使用して、内部発振器を外部クロックに同期させます。外部クロック信号の周波数が、 $R_T$  抵抗によって設定される LM5005 のフリーラン周波数より高くなっていることを確認します。図 6-2 にはオープンドレイン出力のクロック回路が示されており、これは SYNC ピンへの推奨インターフェイスです。クロック パルス幅が 15ns より大きいことを確認します。

Copyright © 2016, Texas Instruments Incorporated

図 6-2. 外部クロック同期

Copyright © 2016,

Texas Instruments Incorporated

図 6-3. 複数の LM5005 レギュレータの自己同期

複数の LM5005 を同期させるには、SYNC ピン同士を単純に接続するだけで構いません。この構成では、すべてのデバイスが最高周波数のデバイスに同期されます。図 6-4 の図は、LM5005 の SYNC 入出力機能を示しています。内部発振回路は、強いプルダウンと弱いプルアップ インバータを使用して SYNC ピンを駆動します。内部発振器または外部クロックによって SYNC ピンが Low に引き下げられると、発振器のランプサイクルが終了し、新しいサイクルが開始します。したがって、複数の LM5005 の SYNC ピンを接続した場合、内部クロック周波数が最も高い IC が最初に SYNC ピンを Low に引き下げ、他の IC の発振ランプサイクルを終了させます。最高にプログラムされたクロック周波数の LM5005 がコントローラとして機能し、低い発振器周波数すべてのデバイスのスイッチング周波数を制御します。

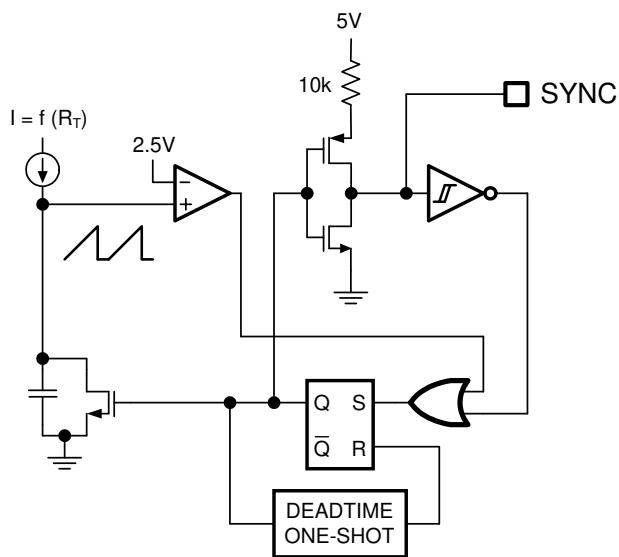

図 6-4. 発振器の概略ブロック図と SYNC I/O 回路

#### 6.3.4 エラー アンプと PWM コンパレータ

内部の高ゲイン誤差アンプは、調整された出力電圧と、内部の高精度リファレンス (1.225V) との差に比例する誤差信号を生成します。誤差増幅器の出力は COMP ピンに出ており、機能ブロック図に示されているように、COMP から FB ヘループル補償用部品 (一般的には Type-II ネットワーク) を接続できるようになっています。このネットワークにより、ユニティ周

波数に極、ゼロ、ノイズ低減の高周波極が形成されます。PWM コンパレータは、エミュレートされた電流センス信号を、RAMP 生成器から COMP ピンでのエラー アンプ出力電圧と比較します。

### 6.3.5 RAMP ジェネレータ

電流モード制御用のパルス幅変調器で使用されるランプ信号は、通常は降圧スイッチ電流から直接生成されます。このスイッチ電流は、出力インダクタ電流の正の勾配部分に対応します。この信号を PWM ランプに利用することで、単一極の応答に制御ループの伝達関数が単純化され、固有の入力電圧フィードフォワード補償が行われます。PWM 制御に降圧スイッチ電流信号を使用する場合の欠点は、回路の寄生成分に起因する大きなリーディング エッジ スパイクが発生し、フィルタリングまたはブランкиングが必要になることです。また、電流測定は大幅な伝搬遅延を発生させる可能性があります。フィルタリング、ブランкиング時間、伝搬遅延によって、実現可能な最小パルス幅が制限されます。出力電圧に比べて入力電圧が比較的大きくなる可能性のあるアプリケーションでは、レギュレーションのために小さなパルス幅とデューティサイクルを制御する必要があります。

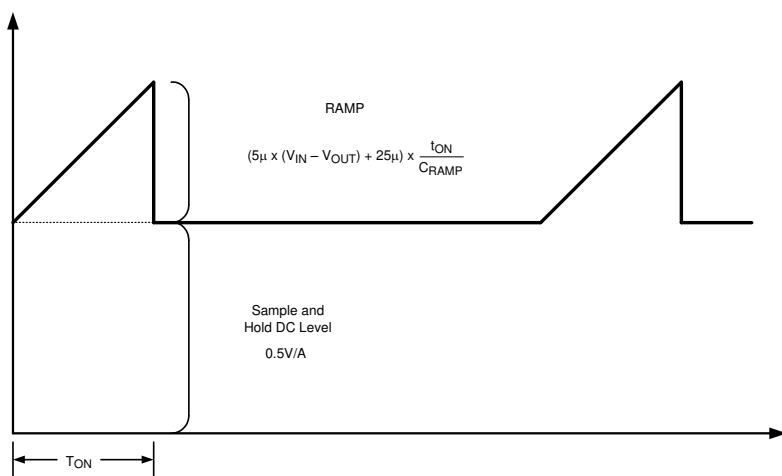

LM5005 は独自のランプ生成器を使用します。このランプ生成器は、実際に降圧スイッチ電流を測定するのではなく、電流信号を再構築します。インダクタ電流を再構築またはエミュレートすると、PWM コンパレータにランプ信号が供給され、リーディング エッジ スパイクや測定またはフィルタリング遅延が発生しません。電流の再構成は、サンプル / ホールド DC レベルとエミュレート電流ランプという 2 つの要素で構成されています。

図 6-5. エミュレートされた電流検出ランプ波形

図 6-5 に示されているサンプル / ホールドの DC レベルは、フリーホイール ショットキー ダイオードを流れる電流の測定値に基づいています。フリー ホイール ダイオードのアノード端子を LM5005 の IS ピンに接続します。ダイオード電流は、IS ピンと PGND ピンの間に内部電流検出抵抗を流れます。センス抵抗の両端の電圧レベルは、降圧スイッチの次の導通間隔が開始する直前にサンプリングおよび保持されます。ダイオード電流の検出とサンプル / ホールド回路によって、再構成された電流信号の DC レベルが生成されます。インダクタ電流の正のスロープは、RAMP ピンと AGND ピンの間に接続された外付けコンデンサと、内部の電圧制御電流源によってエミュレートされます。インダクタ電流をエミュレートするランプ電流源は、入力電圧と出力電圧の関数であり、その関係は 式 2 に示されています。

$$I_{RAMP} = 5\mu A \times [V_{IN} - V_{OUT}] + 25\mu A \quad (2)$$

RAMP コンデンサの適切な選定は、選択した出力インダクタンスに依存します。C<sub>RAMP</sub> の容量は、式 3 を用いて選択します。

$$C_{RAMP} = L_F \times 10^{-5} \quad (3)$$

ここで、

- L<sub>F</sub> は、出力インダクタンスをヘンリー単位で表したもののです

この値により、エミュレートされた電流ランプの係数は、DC レベル サンプル / ホールド (0.5V/A) の係数とほぼ等しくなります。C<sub>RAMP</sub> コンデンサは、LM5005 の RAMP ピンおよび AGND ピンのすぐ近くに配置します。

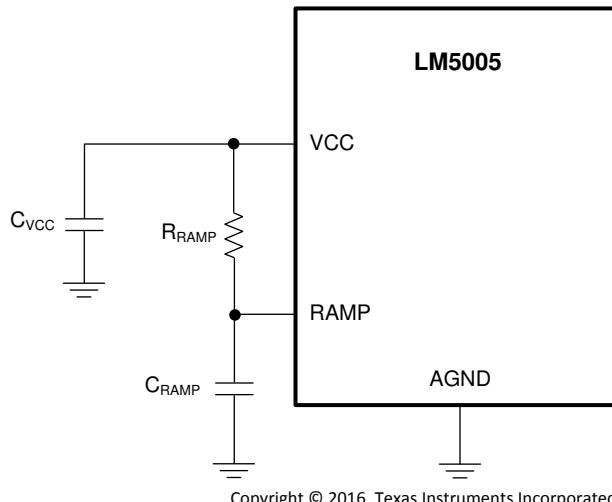

デューティ サイクルが 50% よりも大きい場合、ピーク電流モード制御回路は分数調波発振の影響を受けます。サブハーモニック発振は、通常、スイッチ ノードの電圧波形において、広いパルスと狭いパルスが交互に現れることで特徴づけられます。電流検出信号に固定スロープ電圧ランプ (スロープ補償) を追加することで、この発振を防ぐことができます。エミュレート電流源から供給されるオフセット電流の 25μA により、ランプ信号に固定スロープが追加されます。出力電圧が高く、デューティ サイクルも高い一部のアプリケーションでは、追加のスロープが必要になる場合があります。このようなアプリケーションでは、スロープ補償を強めるために、VCC ピンと RAMP ピンの間にプルアップ抵抗を追加します。

V<sub>OUT</sub> > 7.5V の場合、式 4 で最適なスロープ電流を計算します。

$$I_{OS} = V_{OUT} \times 5\mu A/V \quad (4)$$

例えば、V<sub>OUT</sub> = 10V、I<sub>OS</sub> = 50μA。

RAMP ピンから VCC へ抵抗を挿入する際は、式 5 を参照して選択します。

$$R_{RAMP} = \frac{V_{VCC}}{[I_{OS} - 25\mu A]} \quad (5)$$

図 6-6. V<sub>OUT</sub> > 7.5V のときの外部ランプ抵抗の VCC への接続

### 6.3.6 電流制限

LM5005 は、制御と過電流保護のための独自の電流監視方式を採用しています。正しく設定すると、エミュレートされた電流センス信号は、0.5V/A のスケール係数で降圧スイッチ電流に比例する信号を出力します。エミュレートされたランプ信号が、電流制限コンパレータに適用されます。エミュレートされたランプ信号が 1.75V (3.5A) を超えると、現在のサイクルが終了します (サイクルごとの電流制限)。出力インダクタンスが小さく入力電圧が高いアプリケーションでは、電流制限コンパレータの伝搬遅延により、スイッチ電流がオーバーシュートすることがあります。オーバーシュートの発生が不可避な場合、降圧スイッチのオフ時間中に、ダイオード電流サンプリング回路が過剰なインダクタ電流を検出します。サンプル / ホールド DC レベルが 1.75V の電流制限スレッショルドを超えると、降圧スイッチがディスエーブルになり、ダイオード電流サンプリング回路によってインダクタ電流が電流制限スレッショルド未満に減衰したことが検出されるまで、パルスをスキップします。このアプローチにより、電流オーバーシュート後にインダクタ電流が強制的に減衰するため、伝搬遅延またはインダクタの飽和による電流暴走状態を防止できます。

### 6.3.7 ソフトスタート機能

ソフトスタート機能は、電源投入時の突入電流が LM5005 レギュレータや入力電源に悪影響を与えるのを防ぎます。デバイスが有効化されたとき、または電源投入時に、目標レギュレーション電圧をゆっくりと立ち上げることで出力電圧のソフトスタートが実現されます。SS ピンに接続された外付けソフトスタート用コンデンサは、内部の  $10\mu\text{A}$  ソフトスタート電流源によって徐々に電圧が上昇します。ソフトスタート用コンデンサの電圧は、誤差増幅器の非反転入力に接続されています。SS ピンの電圧レベルを制限またはクランプする外付け回路を使用して、各種のシーケンシングおよびトラッキング方式を実装できます。

過温、VCC の UVLO、シャットダウンなどの故障が検出されると、ソフトスタート用コンデンサは放電されます。フォルト条件が解消されると、新しいソフトスタートシーケンスが開始されます。

### 6.3.8 MOSFET ゲート ドライバ

LM5005 は、N チャネルのハイサイド MOSFET と、それを駆動する浮遊型の高耐圧ゲートドライバを内蔵しています。このゲートドライバ回路は、内部ブートストラップダイオードと外付けブートストラップコンデンサと組み合わせて動作します。TI は、BST ピンと SW ピンの間を短い配線で接続する  $22\text{nF}$  のセラミックコンデンサを使用することを推奨しています。降圧スイッチのオフ期間中、SW 電圧はおよそ  $-0.5\text{V}$  となり、ブートストラップコンデンサは内部ブートストラップダイオードを介して VCC から充電されます。PWM デューティサイクルが高い状態で動作している場合、ブートストラップコンデンサが再充電されていることを確認するために、各サイクルごとに降圧スイッチは強制的に  $500\text{ns}$  だけオフにされます。

軽い負荷条件の下、または出力電圧が事前充電されている場合、降圧スイッチのオフ時間中、SW 電圧は Low に維持されません。インダクタ電流がゼロまで低下し、SW 電圧が上昇すると、ブートストラップコンデンサの電圧が不足し、降圧スイッチのゲートドライバが正常に動作できなくなる可能性があります。これらのアプリケーションでは、PRE ピンを SW ピンに接続してブートストラップコンデンサを事前充電します。PRE ピンと PGND ピンの間に接続された内部プリチャージ MOSFET とダイオードは、各スイッチングサイクルの開始直前に  $250\text{ns}$  だけオンになります。SW ピンが通常の負電圧レベル(連続導通モード)の場合、プリチャージ MOSFET およびダイオードに電流は流れません。

## 6.4 デバイスの機能モード

### 6.4.1 シャットダウン モード

SD ピンは、LM5005 のオン/オフ制御を行います。 $V_{SD}$  が約  $0.6\text{V}$  を下回ると、デバイスはシャットダウン モードになります。内部 LDO とスイッチングレギュレータの両方がオフになります。シャットダウン モードでの静止電流は、 $V_{IN} = 48\text{V}$  で  $60\mu\text{A}$  まで低下します。LM5005 は、VCC バイアスレールの低電圧保護も備えています。VCC 電圧が UV レッショルドを下回ると、レギュレータはオフのままになります。

### 6.4.2 スタンバイ モード

バイアス供給用のサブレギュレータは、本体のレギュレータよりも低い有効化スレッショルドを持っています。 $V_{SD}$  が  $0.6\text{V}$  を超え、スタンバイスレッショルド(通常  $1.225\text{V}$ )未満の場合、VCC 電源はオンになりレギュレーション動作を行います。 $V_{SD}$  がスタンバイスレッショルドを超えるまでは、スイッチング動作も出力電圧のレギュレーションも有効になりません。

### 6.4.3 軽負荷動作

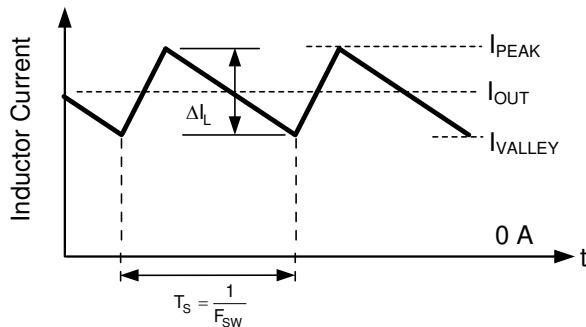

LM5005 は、軽負荷動作時に高い効率を維持します。負荷電流がインダクタのピークツーピークリップ電流の半分よりも小さくなると、その時点でデバイスは不連続導通モード(DCM)に入ります。式 6 を使用して、臨界導通境界を計算します。

$$I_{\text{BOUNDARY}} = \frac{\Delta I_L}{2} = \frac{V_{\text{OUT}} \times (1 - D)}{2 \times L_F \times F_{\text{SW}}} \quad (6)$$

インダクタ電流が 0 に達すると、SW ノードは高インピーダンスになります。降圧コンバータのインダクタと、SW ノードに存在する寄生容量によって LC タンク回路が形成されるため、SW ノードでは共振リングが発生します。軽負荷時、通常  $100\text{mA}$  未満では、スイッチングサイクルの間で複数のパルス CAN がスキップされることがあります。実質的にスイッチング周波数が低下し、軽負荷効率がさらに向上します。

#### 6.4.4 サーマルシャットダウン保護

接合部温度が最大値を超えた場合にレギュレータを保護するため、内部にサーマルシャットダウン回路が備えられています。この回路は通常  $165^{\circ}\text{C}$  でアクティブになり、レギュレータは強制的に低消費電力のリセット状態に移行し、出力ドライバとバイアス レギュレータはディスエーブルされます。この機能は、偶発的なデバイス過熱による致命的な障害を防止するために提供されます。

## 7 アプリケーションと実装

注

以下のアプリケーション情報は、TI の製品仕様に含まれるものではなく、TI ではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

## 7.1 アプリケーション情報

### 7.1.1 バイアス電力損失の低減

LM5005 は、広い入力電圧範囲に対応し、最大出力電流 2.5A を供給できる降圧レギュレータです。一般に、高い入力電圧で動作する降圧レギュレータは、かなりのバイアス電力を消費する可能性があります。V<sub>CC</sub> レギュレータは、入力電圧を降圧して、公称 7V の VCC レベルに変換する必要があります。VCC レギュレータに大きな電圧降下が生じるということは、LM5005 内部で大きな電力損失が発生することを意味します。このバイアス レギュレータの消費電力を大幅に低減できる方法はいくつかあります。

図 7-1 および図 7-2 は、出力電圧から IC をバイアスする 2 つの方法を示しています。いずれの場合も、VCC レールの初期バイアスには内部 VCC レギュレータが使用されます。出力電圧が確立すると、VCC 電圧は公称 7V のレギュレーションレベルを上回るため、内部 VCC レギュレータは実質的に無効化されます。VCC ピンに印加される電圧が、14V を超えないようにする必要があります。VCC ピンの電圧は、入力電圧  $V_{IN}$  を超えないようにする必要があります。

Copyright © 2010, Texas Instruments Incorporated

Copyright © 2018, Texas Instruments Incorporated

VCC 電圧が高いほどゲート駆動能力が増すため、パワー MOSFET のターンオン速度を抑え、SW ノードの電圧オーバー

### 7.1.2 入力電圧 UVLO 保護

SD 入力は、用途に応じた電源投入および電源遮断の要件に対応できるよう、ヒステリシス付きの入力電圧の低電圧ロックアウト (UVLO) を調整可能にしています。SD は、1.225V のバンドギャップ電圧を基準とし、100mV のヒステリシスを持つコンパレータ入力に接続されています。外部ロジック信号を使って SD 入力を駆動し、出力の ON/OFF 制御やシステムのシーケンス制御、保護用途に利用します。

Copyright © 2016, Texas Instruments Incorporated

図 7-3. ヒステリシス付きプログラマブル入力電圧 UVLO

SD ピンを使用しない場合は、内部の 5µA 電流源によってハイにプルアップされているため、ピンは開放のままにしておいてください。これにより、VCC が UVLO スレッショルドを超えて有効動作範囲内に入った際、LM5005 が自動的に起動します。しかし、図 7-3 に示されているように、入力電圧 UVLO レベルを精密に設定するために、R<sub>UV1</sub> と R<sub>UV2</sub> の抵抗分圧器を使用した方が有利となる用途が多くあります。

V<sub>IN(on)</sub> は入力電圧ターンオン スレッショルドとして機能し、V<sub>IN(off)</sub> は入力電圧スレッショルドとして機能します。式 7 と式 8 を使用して UVLO 抵抗を選択します。

$$R_{UV1} = \frac{V_{IN(off)} \times \frac{1.225V}{1.125V} - V_{IN(on)}}{5\mu A} \quad (7)$$

$$R_{UV2} = R_{UV1} \times \frac{1.225V}{V_{IN(on)} - 1.225V + 5\mu A \times R_{UV1}} \quad (8)$$

オプションのコンデンサ C<sub>UV</sub> を R<sub>UV2</sub> と並列に接続することにより、分圧器のフィルタリングを行えます。入力 UVLO レベルを低い電圧に設定した場合、入力電圧の動作範囲の上限では、SD ピンの最大電圧である 7V を超えてしまう可能性があります。この場合は、SD から AGND への小型 6.2V ツエナー ダイオードクランプを使用して、最大 SD 動作電圧を超えないようにします。

### 7.2 代表的なアプリケーション

LM5005 の部品を選択する際には、以下の設計手順を使用します。または、[WEBENCH Design Tool](#) を使用して完全な設計を生成できます。包括的な部品データベースにアクセスして、このオンライン ツールは反復的な設計手法を用いて最適化された設計を生成し、ユーザーがさまざまな設計オプションを試せるようにします。

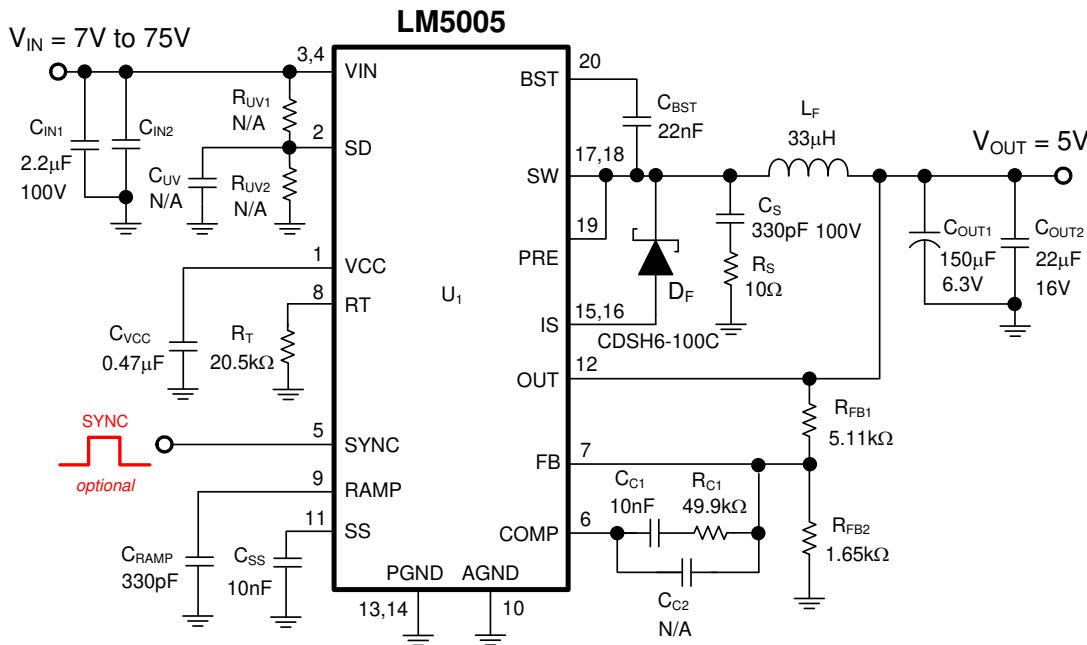

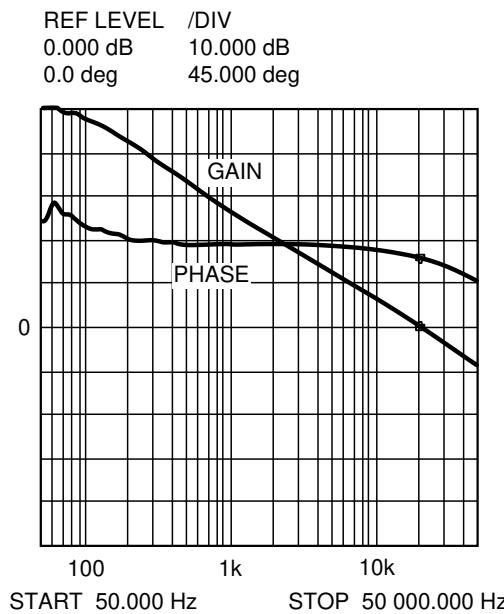

図 7-4 に、入力電圧範囲が 7V ~ 75V の 5V、2.5A レギュレータの回路図を示します。SYNC ピンをオープンにした場合のフリーラン スイッチング周波数は 300kHz です。制御ループ性能について、対象のループ クロスオーバー周波数は 55° 以上の位相マージンで 20kHz です。

Copyright © 2016, Texas Instruments Incorporated

図 7-4. LM5005 回路の回路図

### 7.2.1 設計要件

図 7-4 の代表的なアプリケーション設定を使用して、電力段と補償部品の値を生成するためのステップバイステップの例を以下に示します。

図 7-4 に示す回路は、以下の仕様で構成されています。

- $V_{IN} = 7 \text{ V} \rightarrow 75 \text{ V}$

- $V_{OUT} = 5\text{V}$

- $I_{OUT(max)} = 2.5\text{A}$

- $F_{SW} = 300\text{kHz}$

- 最小負荷電流 CCM の場合 = 250mA

- ライン レギュレーション < 1%

- ロード レギュレーション < 0.1%

この設計の部品表を [表 7-1](#) に示します。

### 7.2.2 詳細な設計手順

#### 7.2.2.1 WEBENCH® ツールによるカスタム設計

[ここをクリック](#)すると、WEBENCH® Power Designer により、LM5005 デバイスを使用するカスタム設計を作成できます。

1. 最初に、入力電圧 ( $V_{IN}$ )、出力電圧 ( $V_{OUT}$ )、出力電流 ( $I_{OUT}$ ) の要件を入力します。

2. オプティマイザのダイヤルを使用して、効率、占有面積、コストなどの主要なパラメータについて設計を最適化します。

3. 生成された設計を、テキサス・インスツルメンツが提供する他の方式と比較します。

WEBENCH Power Designer では、カスタマイズされた回路図と部品リストを、リアルタイムの価格と部品の在庫情報と併せて参照できます。

通常、次の操作を実行可能です。

- 電気的なシミュレーションを実行し、重要な波形と回路の性能を確認する

- 熱シミュレーションを実行し、基板の熱特性を把握する

- カスタマイズされた回路図やレイアウトを、一般的な CAD フォーマットで出力する

- 設計のレポートを PDF で印刷し、設計を共有する

WEBENCH ツールの詳細は、[www.ti.com/ja-jp/WEBENCH](http://www.ti.com/ja-jp/WEBENCH) でご覧になれます。

### 7.2.2.2 周波数設定抵抗 ( $R_T$ )

抵抗  $R_T$  は、スイッチング周波数を設定します。一般的に、高周波アプリケーションは小さくなりますが、損失が大きくなります。この設計例では、ソリューション サイズの小型化と高効率の両立を図るため、300kHz のスイッチング周波数を妥当な妥協点として選択しています。300kHz のスイッチング周波数に対し、式 1 を使用して  $R_T$  の値を計算します。

$R_T$  には、標準値で最も近い 20.5kΩ の抵抗を選択します。

### 7.2.2.3 インダクタ ( $L_F$ )

インダクタンスは以下に基づいています:

- スイッチング周波数

- 負荷電流

- インダクタのリップル電流

- 最小入力電圧  $V_{IN(min)}$

- 最大入力電圧 ( $V_{IN(max)}$ )

図 7-5. インダクタ電流の波形

コンバータを CCM で動作させるためには、インダクタの最大リップル電流  $ΔI_L$  が最小負荷電流の 2 倍、またはピークツーピークで 0.5A 未満であることを確認します。このリップル電流値を使用して、式 9 を使用してインダクタンスを計算します。

$$L_F = \frac{V_{OUT} \times [V_{IN(max)} - V_{OUT}]}{\Delta I_L \times F_{SW} \times \sqrt{V_{IN(max)}}} = \frac{5V \times [75V - 5V]}{0.5A \times 300kHz \times \sqrt{75V}} = 31\mu H \quad (9)$$

標準値で最も近い 33μH を使用します。別 の方法として、公称入力電圧において、インダクタのリップル電流が定格最大負荷電流の 30~50% になるようなインダクタンスを選定する方法もあります。

インダクタは、飽和を防止するため、図 7-5 の  $I_{PEAK}$  と表記されるピーク インダクタ電流の定格を満たす必要があることに注意してください。通常の負荷条件では、インダクタのピーク電流は、最大負荷電流に最大ピークツーピークリップル電流の半分を加えた値になります。過負荷状態時のピーク インダクタ電流は、公称 3.5A (最大 4.25A) に制限されます。この設計例で選定したインダクタ (表 7-1 を参照) は、余裕を見た 6.2A の飽和電流定格を備えています。このインダクタメーカーでは、飽和電流を 20°C においてインダクタンスが 30% 低下する電流と定義しています。

### 7.2.2.4 ランプ コンデンサ ( $C_{RAMP}$ )

インダクタを選択したら、式 10 を使用して、エミュレーション ランプ回路に必要な値 ( $C_{RAMP}$ ) を計算します。

$$C_{RAMP}[\mu F] = 10 \times L_F[\mu H] \quad (10)$$

$L_F$  が  $33\mu H$  の場合、推奨される  $C_{RAMP}$  は  $330\text{pF}$  です。NP0 または COG の誘電体を使用したコンデンサを使用します。

#### 7.2.2.5 出力コンデンサ ( $C_{OUT}$ )

出力コンデンサはインダクタのリップル電流を平滑化し、過渡的な負荷条件に対して電荷を供給する役割を果たします。LM5005 では幅広い種類の出力コンデンサを使用でき、さまざまな利点を得られます。最良の性能は、一般的にセラミックまたはポリマー電解タイプの部品を使用した場合に得られます。一般的なトレードオフとして、セラミックコンデンサは極めて低い ESR を提供し、出力リップル電圧やノイズスパイクを低減できる一方、電解コンデンサは過渡負荷条件に対応するため、小さな体積で大きなバルク容量を提供します。

出力コンデンサを選ぶ際に考慮すべき性能特性は、出力電圧リップルと負荷過渡応答の 2 つです。出力電圧リップルは、式 11 を使用して概算します。

$$\Delta V_{OUT} = \Delta I_L \sqrt{R_{ESR}^2 + \left[ \frac{1}{8 \times F_{SW} \times C_{OUT}} \right]^2} \quad (11)$$

ここで、

- $\Delta V_{OUT}$  = ピークツー ピークの出力電圧リップル

- $R_{ESR}$  = 出力コンデンサの実効等価直列抵抗 (ESR)

- $F_{SW}$  = スイッチング周波数

- $C_{OUT}$  = 実効出力容量

出力電圧リップルの量は、用途によって異なります。一般的には、出力リップルを定格出力電圧の 1% 未満に抑えることが推奨されています。

コンデンサは ESR が低いため、コンデンサが推奨されることもあります。しかし、コンデンサのパッケージや耐圧によっては、印加電圧により実装時の実効容量が大幅に低下することがあります。出力コンデンサの選択は、負荷過渡時の出力電圧降下にも影響を及ぼします。負荷過渡時の出力電圧のピーク偏差は、多くの要因に依存します。式 12 は、ループ帯域幅を無視する過渡ディップの近似値を計算します。

$$V_{DROOP} = \Delta I_{OUT-STEP} \times R_{ESR} + \frac{L_F \times \Delta I_{OUT-STEP}^2}{C_{OUT} \times [V_{IN} - V_{OUT}]} \quad (12)$$

ここで、

- $C_{OUT}$  = 最小必要出力容量

- $L_F$  = 降圧フィルタのインダクタンス

- $V_{DROOP}$  = ループ帯域幅の考慮を無視した場合の出力電圧偏差

- $\Delta I_{OUT-STEP}$  = 負荷ステップの変化

- $R_{ESR}$  = 出力コンデンサの ESR

- $V_{IN}$  = 入力電圧

- $V_{OUT}$  = 出力電圧の設定ポイント

出力リップルの仕様を満たすため、各コンデンサの許容差と電圧係数を確認した上で、X7R 誘電体、1210 サイズの  $22\mu F$  16V セラミックコンデンサと、 $150\mu F$  6.3V のポリマー電解コンデンサを選定しています。セラミックコンデンサは超低 ESR を実現して出力リップル電圧とノイズスパイクを低減し、電解コンデンサは過渡負荷条件において小さな体積で大きなバルク容量を実現します。

#### 7.2.2.6 ショットキー ダイオード ( $D_F$ )

すべての LM5005 アプリケーションでは、ショットキー型のフリーホイール ダイオードが必須です。ダイオードの逆方向耐圧は、最大  $V_{IN}$  に安全マージンを加えた値で選択します。超高速ダイオードは推奨されず、逆方向回復電流過渡によりレギュレータが損傷する可能性があります。LM5005 で一般的な高入力電圧・低出力電圧のアプリケーションでは、ショットキーダイオードのほぼ理想的な逆回復特性と低い順方向電圧降下が、特に重要な特性となります。

逆方向回復特性によって、降圧スイッチがオンになったときに、各サイクルで電流サージがどの程度持続するかが決まります。ショットキー ダイオードの穏やかな逆回復特性により、各サイクルのターンオン時に降圧スイッチへ生じる瞬間的なピーク電力が最小化され、その結果として降圧スイッチのスイッチング損失が大幅に低減されます。

ダイオードの順方向電圧降下は変換効率に大きく影響し、特に出力電圧が低いアプリケーションではその影響が顕著です。ダイオードの定格電流は、メーカーによって大きく異なります。ワースト ケースは、負荷短絡状態を想定したものです。この場合、ダイオードは出力電流をほぼ連続的に流します。LM5005 の場合、この電流は最大 3.5A に達する可能性があります。ワースト ケースで、ダイオードの両端で 1V 電圧降下すると仮定すると、最大ダイオード消費電力は最大 3.5W に達する可能性があります。この設計例では、DPAK パッケージの 100V、6A ショットキー ダイオードを選定しています。

#### 7.2.2.7 入力コンデンサ ( $C_{IN}$ )

レギュレータの電源電圧は、スイッチング周波数で大きなソース インピーダンスを持ちます。オン時間時にはほとんどのスイッチ電流を供給しながら、VIN ピンのリップル電圧を制限するには、高品質な入力コンデンサが必要です。降圧スイッチがオンになると、VIN ピンに流れ込む電流がインダクタ電流波形の低いピークまで徐々に増え、ピーク値まで上昇して、ターンオフ時にゼロに低下します。オン時間中の VIN に流れ込む平均電流が負荷電流です。入力容量は、RMS 電流定格と最小リップル電圧に対して選択する必要があります。必要なリップル電流定格のおおよその目安が 式 13 に示されています

$$I_{RMS} > I_{OUT} \div 2 \quad (13)$$

入力フィルタには、低 ESR のセラミック コンデンサを選択します。コンデンサの許容差や電圧ディレーティングの影響を考慮し、2.2 $\mu$ F、100V のセラミック コンデンサを 2 個使用します。LM5005 の最大定格付近でステップ状の入力電圧過渡が発生する可能性がある場合、VIN ピン ID におけるリングングやスパイクの有無について、慎重に評価する必要があります。LM5005 の最大定格付近でステップ状の入力電圧過渡が発生する可能性がある場合、追加のダンピング ネットワーク、スナバ回路、または入力電圧クランプが必要になる場合があります。

#### 7.2.2.8 VCC コンデンサ ( $C_{VCC}$ )

VCC ピンに接続されたコンデンサは、VCC レギュレータのノイズ除去と安定性を確保します。 $C_{VCC}$  の推奨値は 0.47 $\mu$ F であり、16V 以上の定格を持つ X7R 誘電体の低 ESR セラミック コンデンサを使用する必要があります。

#### 7.2.2.9 ブートストラップ コンデンサ ( $C_{BST}$ )

BST ピンと SW ピンの間に接続されたブートストラップ コンデンサは、ターンオン時に降圧スイッチのゲートを充電するためのゲート電流を供給します。 $C_{BST}$  に推奨される値は 22nF です。低 ESR で、X7R 誘電体を使用し、少なくとも 16V 定格のセラミック コンデンサを選びます。

#### 7.2.2.10 ソフトスタート コンデンサ ( $C_{SS}$ )

SS ピンに接続されたコンデンサがソフトスタート時間、つまり基準電圧および出力電圧が最終的なレギュレーション電圧に到達するまでの時間を決定します。所要のソフトスタート時間を  $t_{SS}$  とする場合、ソフトスタート用コンデンサの容量は 式 14 を用いて、またはより簡単には 式 15 を用いて計算します。

$$C_{SS} = \frac{t_{SS} \times I_{SS}}{V_{REF}} = \frac{t_{SS} \times 10\mu A}{1.225V} \quad (14)$$

$$C_{SS}[nF] = 8.16 \times t_{SS}[ms] \quad (15)$$

このアプリケーションでは、ソフトスタート時間 1.2ms に対応する 10nF の  $C_{SS}$  を選択します。

#### 7.2.2.11 帰還抵抗 ( $R_{FB1}$ 、 $R_{FB2}$ )

抵抗  $R_{FB1}$  および  $R_{FB2}$  により、出力電圧の設定点が設定されます。下側帰還抵抗  $R_{FB2}$  で選択した値に基づいて、式 16 から上側帰還抵抗  $R_{FB1}$  を計算します。

$$R_{FB1} = \frac{V_{OUT} - 1.225V}{1.225V} \times R_{FB2} \quad (16)$$

一般的に、 $R_{FB2}$  の初期値としては  $1\text{k}\Omega \sim 10\text{k}\Omega$  程度が適しています。この設計例では  $5\text{V}$  の出力設定点を実現するため、 $R_{FB1}$  には  $5.11\text{k}\Omega$  の抵抗、 $R_{FB2}$  には  $1.65\text{k}\Omega$  の抵抗を選択します。

#### 7.2.2.12 RC スナバ ( $R_S$ および $C_S$ )

パワー ダイオードの両端にスナバ回路を配置することで、スイッチング ノードのリンギングおよびスパイクが減少します。過剰なリンギングおよびスパイクは誤動作を引き起こし、出力にスパイクやノイズを結合させる場合があります。最終的には、LM5005 やフリーホイール ダイオードの定格を超える過剰なスパイクが発生すると、デバイスが損傷する可能性があります。スナバの値の選択には、実験的な手法が最適です。最初に、スナバ接続のリードが非常に短いことを確認します。LM5005 コンバータで一般的な電流レベルの場合、スナバ抵抗  $R_S$  は  $2\Omega \sim 10\Omega$  程度で十分です。スナバコンデンサの値を増やすとダンピングが増えますが、損失も大きくなります。フルロード時の SW 電圧波形に十分な減衰が得られるよう、 $C_S$  の最小値を選択します。詳細については、[EMI 低減のための PCB レイアウト](#)を参照してください。

#### 7.2.2.13 捜査部品 ( $R_{C1}$ 、 $C_{C1}$ 、 $C_{C2}$ )

これらの部品は、安定した全体ループ ゲインを得るために、エラー アンプのゲイン特性を構成します。電流モード制御の利点の一つは、 $R_{C1}$  と  $C_{C1}$  のわずか 2 つの帰還部品だけでループを閉じられる点です。全体のループ ゲインは、変調器のゲインとエラー アンプのゲインの積です。LM5005 の DC 変調器のゲインは [式 17](#) で計算できます。

$$GAIN_{MOD-DC} = G_m[MOD] \times R_{LOAD} = 2 \times R_{LOAD} \quad (17)$$

変調器の支配的な低周波数極は、負荷抵抗  $R_{LOAD}$ 、と出力容量  $C_{OUT}$  によって決定されます。この極のコーナー周波数は [式 18](#) を用いて計算します。

$$f_p[MOD] = \frac{1}{2\pi \times R_{LOAD} \times C_{OUT}} \quad (18)$$

$R_{LOAD} = 5\Omega$  および  $C_{OUT} = 177\mu\text{F}$  の場合、 $f_p(MOD) = 180\text{Hz}$  になります

$$GAIN_{MOD-DC} = 2\text{A/V} \times 5\Omega = 10 = 20\text{dB} \quad (19)$$

$R_{LOAD} = 5\Omega$ 、 $C_{OUT} = 177\mu\text{F}$  の場合のこの設計例では、実験的に測定された変調器のゲインと周波数特性との関係を [図 7-6](#) に示します。

図 7-6. PWM 変調器のゲインと位相プロット

$R_{C1}$  と  $C_{C1}$  によってエラー アンプはタイプ II 構成となり、原点に極が一つ生じ、次の位置にゼロが配置されます：

$$f_Z = 1 \div [2\pi R_{C1} C_{C1}] \quad (20)$$

エラー アンプのゼロは変調器の極を打ち消し、ループ ゲインのクロスオーバー周波数でシングル ポール応答が残ります。クロスオーバー周波数で单一極応答となる場合、位相マージン 90° の安定したループが得られます。

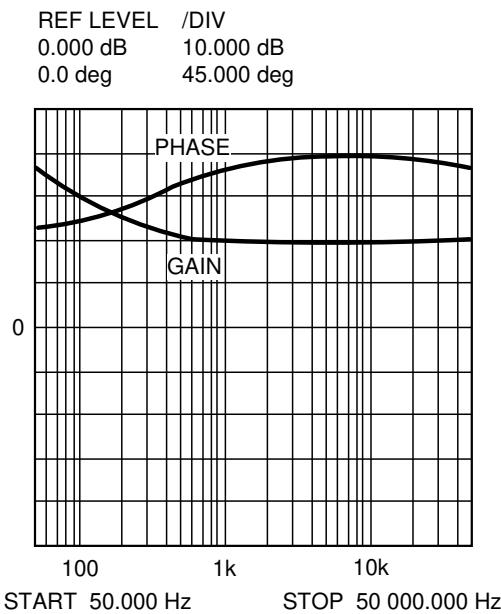

この設計例では、ループ帯域幅( クロスオーバー周波数) の目標値として 20kHz を選択します。補償ゼロ周波数  $f_Z$  は、ターゲットのクロスオーバー周波数よりも 1 枠低い位置に設定します。これにより、目的の補償ネットワークのゼロ周波数を得るために  $R_{C1}$  と  $C_{C1}$  の積が 2kHz 未満になるよう制約されます。 $R_{C1}$  を増やし、同じ比率で  $C_{C1}$  を減らすと、エラー アンプの利得が上がります。逆に、 $R_{C1}$  を減らし、同じ比率で  $C_{C1}$  を増やすと、エラー アンプのゲインは下がります。49.9kΩ の  $R_{C1}$  と 10nF の  $C_{C1}$  を選択します。これらの値により、補償回路のゼロが 320Hz に構成されます。 $f_Z$  より高い周波数での補償器のゲインは  $R_{C1}/R_{FB1}$  で、これは約 20dB です。

図 7-7 に補償器のボード線図を示します。全体のループ特性は、図 7-8 に示すように、変調器の利得と補償回路の利得を dB で加算したものとして予測されます。

図 7-7. 補償器のゲインと位相のプロット

図 7-8. 全体的なループゲインおよび位相のプロット

ネットワークアナライザが使用できる場合は、変調器のゲインを測定し、目的のループ伝達関数となるよう補償回路のゲインを設定します。ネットワークアナライザが利用できない場合は、記載されているガイドラインを使用して、エラー アンプの補償部品を設計します。性能が許容範囲内であることを確認するため、ステップ負荷過渡試験を実施します。ステップ負荷の目標は、応答が減衰した場合の最小オーバーシュートです。エラー アンプのノイズ感受性を低減するため、補償ネットワークにコンデンサ  $C_{C2}$  を追加します。このコンデンサを追加すると補償回路の伝達関数に極が一つ増えるため、 $C_{C2}$  の値が十分に小さいことを確認します。この極がループのクロスオーバー周波数より十分高い位置にあることを確認します。 $C_{C2}$  によって追加される極のおおよその位置は、式 21 に示すとおりです。

$$f_{p2} = f_Z \times C_{C1} \div C_{C2} \quad (21)$$

エラー アンプのノイズ感受性を低減する別の方法として、COMP から AGND へコンデンサを接続する方法があります。この方法を使用する場合は、 $C_{C2}$  の容量が 100pF を超えないようにします。

### 7.2.2.14 部品表

表 7-1 には、この設計例の部品表が示されています。

**表 7-1. LM5005 降圧レギュレータの部品表、 $V_{OUT} = 5V$ 、 $I_{OUT} = 2.5A$**

| 参照記号               | 説明                                          | メーカー <sup>(1)</sup> | 部品番号           | 数量 |

|--------------------|---------------------------------------------|---------------------|----------------|----|

| $C_{IN1}, C_{IN2}$ | コンデンサ、CER、 $2.2\mu F$ 、100V、X7R、1210        | TDK                 | C3225X7R2A225M | 2  |

| $C_{OUT1}$         | コンデンサ、SP、 $150\mu F$ 、6.3V、 $12m\Omega$     | Panasonic           | EEFHE0J151R    | 1  |

| $C_{OUT2}$         | コンデンサ、CER、 $22\mu F$ 、16V、X7R、1210          | TDK                 | C3225X7R1C226M | 1  |

| $C_S$              | コンデンサ、CER、 $330pF$ 、100V、0603               | Kemet               | C0603C331G1GAC | 1  |

| $C_{C1}, C_{SS}$   | コンデンサ、CER、 $10nF$ 、100V、0603                | TDK                 | C1608X7R2A103K | 2  |

| $C_{BST}$          | コンデンサ、CER、 $22nF$ 、100V、0603                | TDK                 | C1608X7R2A223K | 1  |

| $C_{VCC}$          | コンデンサ、CER、 $0.47\mu F$ 、16V、0604            | TDK                 | C1608X7R1C474M | 1  |

| $C_{RAMP}$         | コンデンサ、CER、 $330pF$ 、100V、0603               | Kemet               | C0603C331G1GAC | 1  |

| $D_F$              | ダイオード、100V、6A、ショットキー、DPAK                   | Central Semi        | CSHD6-100C     | 1  |

|                    | ダイオード、100V、6A、ショットキー (代替)                   | IR                  | 6CWQ10FN       |    |

| $L_F$              | インダクタ、 $33\mu H$ 、 $I_{SAT}$ 6.22A、DCR 60mΩ | Coiltronics/Eaton   | DR127-330-R    | 1  |

| $R_T$              | 抵抗、 $20.5k\Omega$ 、0603                     | Vishay Dale         | CRCW06032052F  | 1  |

| $R_{C1}$           | 抵抗、 $49.9k\Omega$ 、0603                     | Vishay Dale         | CRCW06034992F  | 1  |

| $R_{FB1}$          | 抵抗、 $5.11k\Omega$ 、0603                     | Vishay Dale         | CRCW06035111F  | 1  |

| $R_{FB2}$          | 抵抗、 $1.65k\Omega$ 、0603                     | Vishay Dale         | CRCW06031651F  | 1  |

| $R_S$              | 抵抗、 $10\Omega$ 、1W、1206                     | Vishay Dale         | CRCW1206100J   | 1  |

| $U_1$              | 広い VIN レギュレータ、75V、2.5A                      | デキサス・インスツルメンツ       | LM5005         | 1  |

(1) サードパーティ製品の免責事項を参照してください。

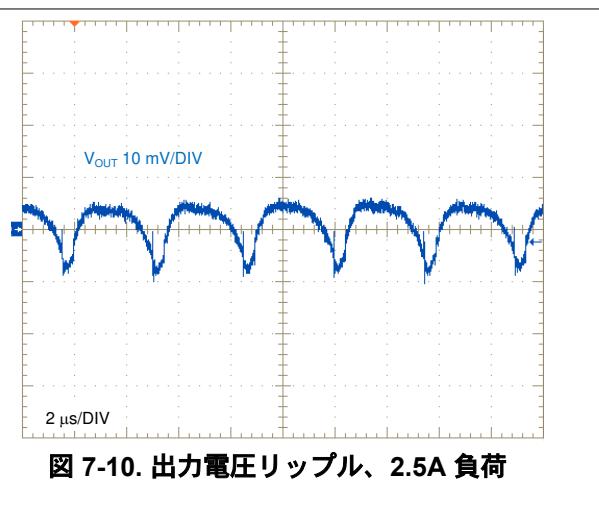

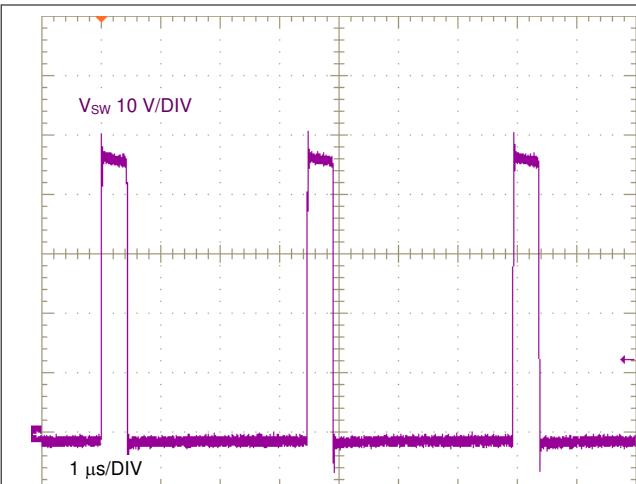

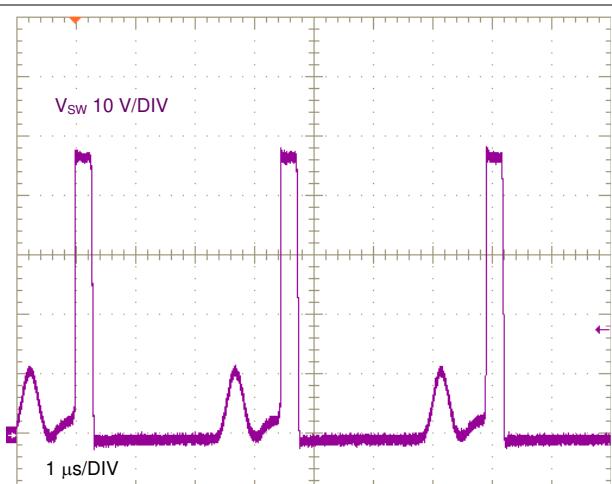

### 7.2.3 アプリケーション曲線

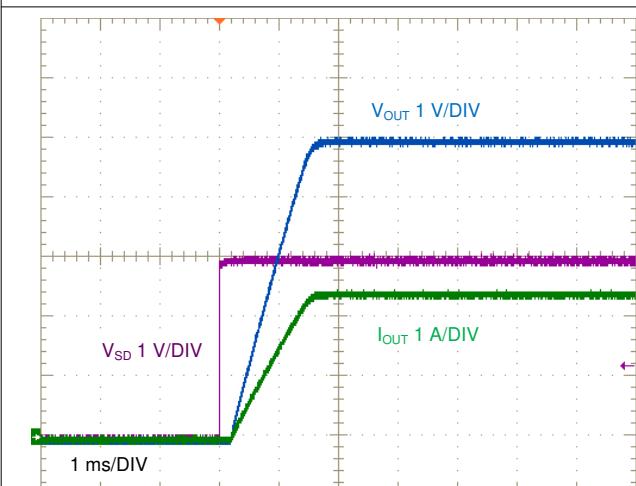

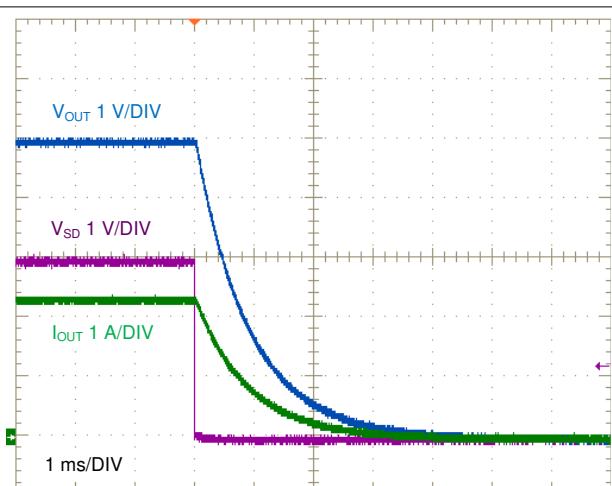

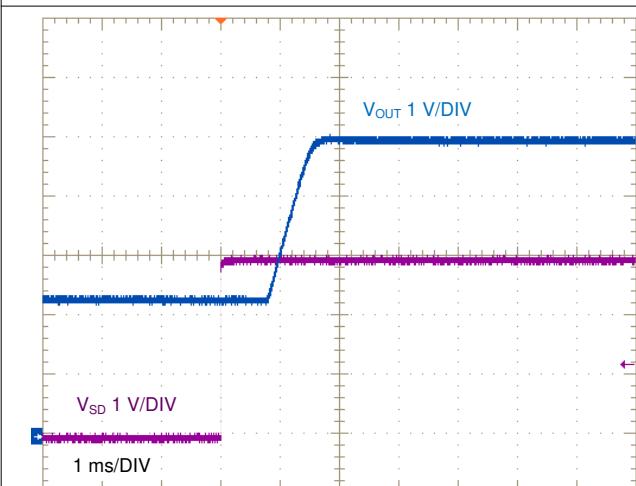

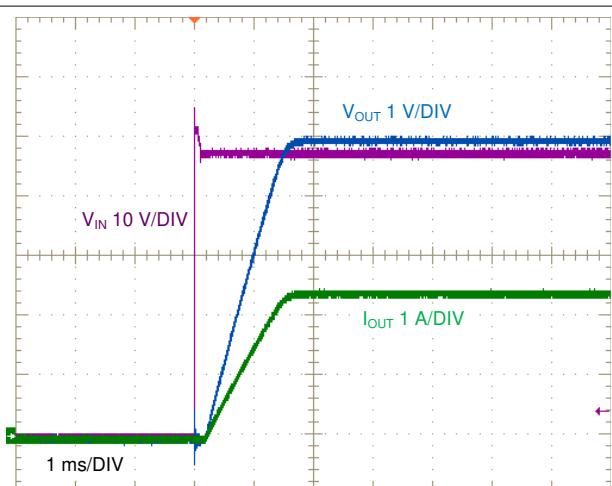

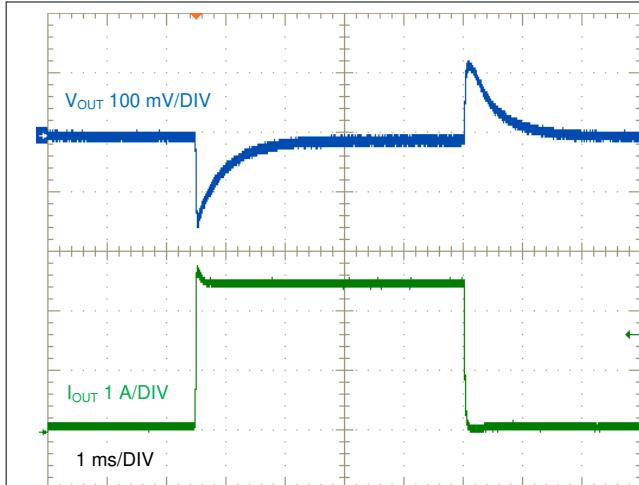

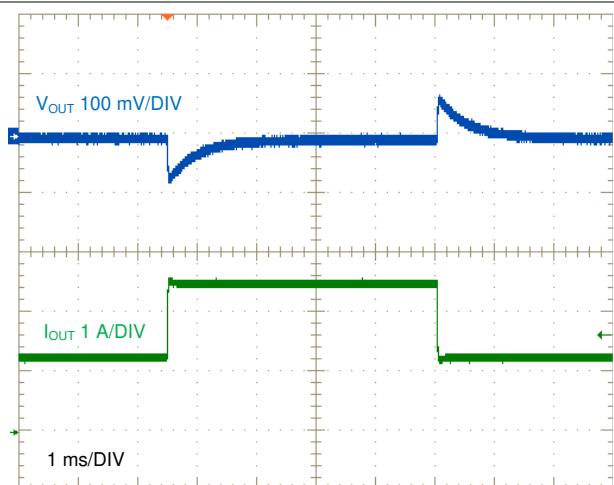

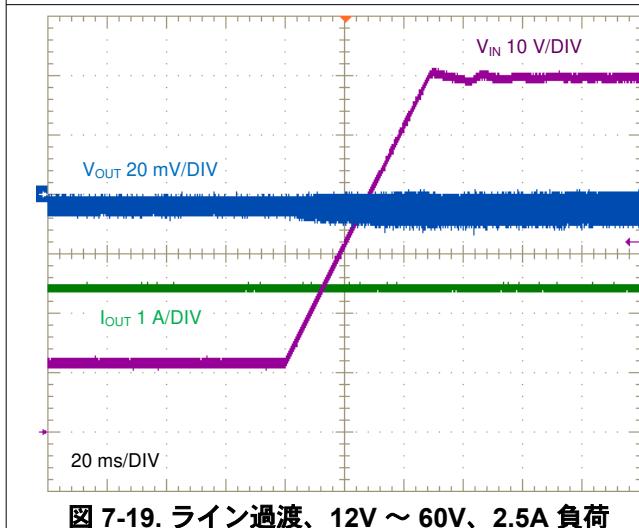

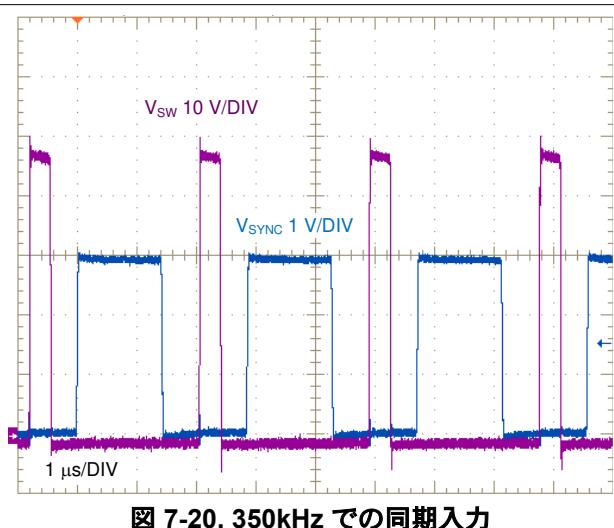

コンバータの効率と性能の波形を図 7-9 から図 7-19 に示します。特に記述のない限り、すべての波形は  $V_{IN} = 48V$  で測定されます。

図 7-11. SW ノード電圧、2.5A 負荷

図 7-12. SW ノード電圧、0.1A 負荷

図 7-13. SD ピン、2.5A の抵抗性負荷を使用した起動

図 7-14. SD ピン、2.5A の抵抗性負荷を使用したシャットダウン

図 7-15. SD ピンを使用した起動、プリバイアス出力時の動作

図 7-16. V<sub>IN</sub>、2.5A の抵抗性負荷を印加して起動

図 7-17. 負荷過渡応答、0.1A ~ 2.5A 間負荷

図 7-18. 負荷過渡応答、1.25A ~ 2.5A 間負荷

図 7-19. ライン過渡、12V ~ 60V、2.5A 負荷

図 7-20. 350kHz での同期入力

### 7.3 電源に関する推奨事項

LM5005 コンバータは、7V ~ 75V の広い入力電圧範囲で動作するように設計されています。入力電源の特性は、「**絶対最大定格**」と「**推奨動作条件**」に適合している必要があります。また、入力電源が、全負荷時のレギュレータに必要な入力電流を供給できることを確認してください。式 22 を使用して平均入力電流を推定します。

$$I_{IN} = \frac{V_{OUT} \times I_{OUT}}{V_{IN} \times \eta} \quad (22)$$

ここで、

- $\eta$  は効率です。

コンバータが高インピーダンスを持つ長い配線や PCB パターンを経由して入力電源に接続されている場合は、安定した性能を実現するため特に注意が必要です。入力ケーブルの寄生インダクタンスと抵抗は、コンバータの動作に悪影響を及ぼすことがあります。寄生インダクタンスと低 ESR のセラミック入力コンデンサを組み合わせることで、不足減衰共振回路が形成されます。この回路は、入力電源がオンとオフを周期的に切り替わるたびに、VIN で過電圧過渡が発生する可能性があります。寄生抵抗により、負荷過渡中に入力電圧が低下する場合があります。コンバータが最小入力電圧に近い値で動作している場合、この低下によって UVLO フォルトが誤って起動され、システムがリセットされる可能性があります。こうした問題を解決する最善策は、入力電源からレギュレータまでの距離を短くして、セラミックと並列にアルミニウム

製やタンタル製の入力コンデンサを使用することです。電解コンデンサの **ESR** は比較的低いため、入力共振回路は減衰し、電圧オーバーシュートを低減することができます。通常、容量の範囲が  $10\mu\text{F} \sim 47\mu\text{F}$  であれば入力を減衰させるのに十分で、大きな負荷過渡中も入力電圧を安定した状態に保持できます。

レギュレータの前に **EMI** 入力フィルタを使用することができます。ただし、設計に留意しなければ、これにより不安定な状態が起きる、または前述のような影響を及ぼすおそれがあります。[AN-2162 DC/DC コンバータ向け伝導 EMI の簡単な成功事例](#) [ユーザー ガイド](#)では、スイッチング レギュレータの入力フィルタを設計するために役立つ提案を紹介しています。

## 7.4 レイアウト

### 7.4.1 レイアウトのガイドライン

DC-DC コンバータの設計において、**PC** 基板のレイアウトは重要で欠かせない要素です。スイッチング コンバータの性能は、部品の選択だけでなく **PCB** のレイアウトにも依存します。レイアウトが不適切だと、スイッチング コンバータやその周辺回路の性能を損ない、次のような問題を引き起こします：

- **EMI**

- グランド バウンス

- パターンの導通損失

- 熱の問題

誤った信号が **DC-DC** コンバータに入り込み、出力電圧の制御不良や不安定動作を引き起こす可能性があります。高スルーレートの電流や電圧を伝導するパスが複数存在し、これらが浮遊インダクタンスや寄生容量と相互作用してノイズや **EMI** を生成したり、電源のパフォーマンスを低下させたりする可能性があります。

以下のガイドラインは、電力変換性能や熱性能を最大限に高め、不要な **EMI** の発生を最小限に抑える **PCB** を設計する際の助けとなるものです。

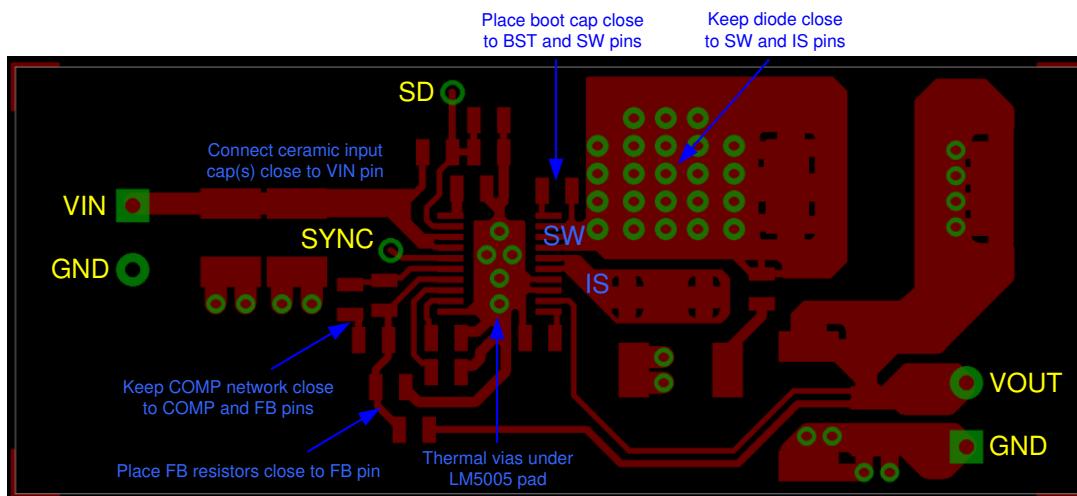

1. 降圧レギュレータには、2 つの重要な電流導通ループがあります。最初のループは、入力コンデンサから **LM5005** の **VIN** ピン、**SW** ピン、インダクタへと流れ、そこから負荷へ向かいます。2 つ目のループは、出力コンデンサの帰還端子から **LM5005** の **PGND** ピン、**IS** ピン、フリーホイール ダイオードのアノード、インダクタへと進み、そこから負荷へ向かいます。これら 2 つのループの有効面積を小さくすると、寄生インダクタンスが減少し、ノイズや予期しない動作を最小限に抑えられます。

2. 入力コンデンサは、**LM5005** の **VIN** ピンおよび **PGND** ピンにつながる露出パッドの近くに配置します。インダクタは、**SW** ピンおよび出力コンデンサのそばにできるだけ近くに配置します。[EMI 低減のための PCB レイアウト](#)で詳しく説明したように、この配置はスイッチング電流ループの面積を最小限に抑え、大電流パスの抵抗性損失を低減する役割を果たします。優れた選択肢は、**PGND** ピン、デバイスの露出パッド、および入力および出力コンデンサの帰還端子を接続する最上層にグランド プレーンを使用することです。詳細については、[AN-1748 LM5005 評価ボード ユーザーガイド](#)に記載されている基板レイアウトを参照してください。

3. スイッチ ノードの銅の面積を最小化します。2 つの **SW** ピンは、トップ層の同じプレーン上でインダクタ端子まで太いパターンで配線し、導通損失を最小限にします。インダクタは、**LM5005** に対して **PCB** の反対面に配置してもかまいませんが、インダクタの磁界がフィードバック線や補償回路などの敏感なパターンに結合しないよう十分注意してください。

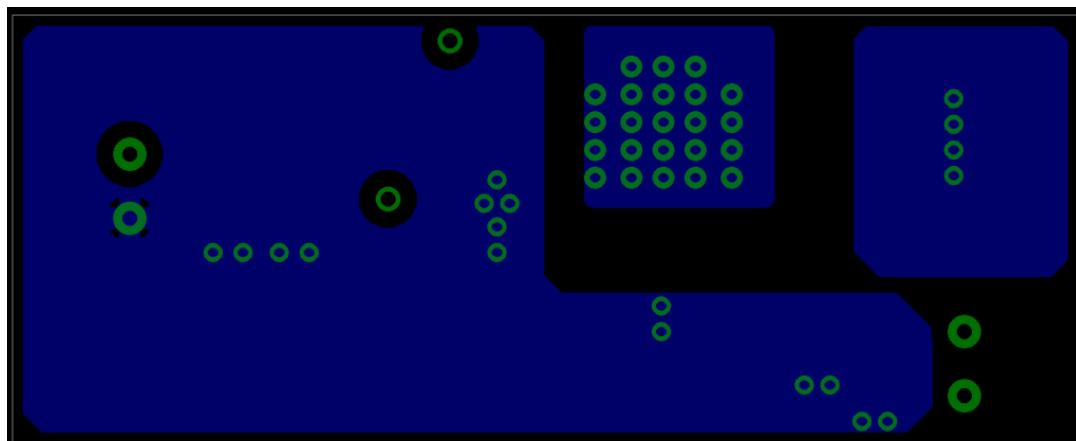

4. 特に **LM5005** やパワー ステージ部品の直下には、**PCB** の第 2 層に連続したソリッドなグランド プレーンを配置します。このプレーンは、ノイズ シールドと放熱経路として機能します。

5. コンバータの入力および出力での電圧降下を減らし、効率を向上させるために、入力側と出力側のパワーバス配線はできるだけ太く、かつ短くします。上部にある複数の銅プレーンを使用して、複数の **VIN** ピンと **PGND** ピンを互いに接続します。

6. 適切なヒートシンクのために十分な **PCB** 領域を確保します。[熱設計](#) セクションでも説明されているように、最大負荷電流や周囲温度に見合った低い  $R_{\theta JA}$  を得るために、十分な銅面積を確保します。**PCB** のトップ層とボトム層には、2 オンスの銅厚を使用し、最低でも 1 オンスは確保します。ヒートシンク ビアの配列を使用して、パッドの露出部分を **PCB** 下面のグランド プレーンに接続します。推奨されているように **PCB** に複数の銅層がある場合、これらのサーマルビアは内層の放熱用グランド プレーンにつなげます。

7. **VOUT** の制御ポイントから帰還抵抗までのセンス パターンは、**SW** ピンやインダクタから離して配線し、スイッチングノイズが帰還信号に入り込むのを防ぎます。出力電圧の設定に高い抵抗値を使っている場合、この配線のルーティングは特に重要になります。帰還配線は、インダクタや **SW** ノードの配線とは別の層に通すことが推奨されます。センスパターンとインダクタまたは **SW** ノードのポリゴンの間にグランド プレーンを挟むことで、帰還配線に対する **EMI** をさらに低減できるためです。

8. 負荷での電圧精度が重要な場合は、負荷端子で帰還電圧検出を直接行っていることを確認します。これにより、PCB プレーンおよびトレースの電圧降下を補正し、優れた出力電圧設定ポイント精度と負荷レギュレーションを実現します。帰還分圧抵抗は **FB** ノードがエラー アンプへの入力であり、ノイズに敏感なため、負荷の近くではなく **FB** ピンの近くに配置します。

9. **COMP** はノイズに敏感なノードです。補償部品は、**FB** ピンおよび **COMP** ピンのすぐ近くに配置します。

10. **R<sub>T</sub>**、**C<sub>SS</sub>**、**C<sub>RAMP</sub>**、**C<sub>VCC</sub>** の部品は、対応するピンの近くに配置します。信号部品のグランド帰還は、すべて LM5005 の **AGND** ピンに直接接続します。デバイス直下全体を覆うトップ層の銅エリアを使って、LM5005 の露出パッドで **AGND** ピンと **PGND** ピンを接続します。PCB 裏面のこの銅エリア内に複数のビアを設けて、内部のグランド プレーンに接続します。

11. その他の重要なガイドラインについては、[関連資料](#)を参照してください。

#### 7.4.1.1 EMI 低減のための PCB レイアウト

高スルーレートの電流エッジによって発生する放射 **EMI** は、スイッチング コンバータ内のパルス状電流と関連しています。パルス電流の経路がカバーする面積が大きいほど、より多くの電磁放射が発生します。放射 **EMI** を削減するための鍵は、パルス電流経路を識別し、そのパスの面積を最小化することです。

図 7-21 における重要な高周波スイッチング電力ループ (または LM5005 電力段のホットループ) は、青色で示しています。降圧コンバータのトロジ アーキテクチャ上、スイッチング遷移時に外付けショットキー ダイオードと内蔵ハイサイド MOSFET の間で電流が切り替わるため、このループには特に高い  $di/dt$  の電流が流れます。レイアウトによって生じる寄生インダクタンスや浮遊インダクタンスを抑え、**SW** ノードの過度なオーバーシュートやリンギング、ノイズ、グラウド バウンスを防ぐためにも、この実効ループ面積を最小限に抑えることが不可欠です。

一般に、MOSFET のスイッチング動作と、それに伴う波形リンギング、電力損失、デバイスへのストレス、**EMI** は、電力ループの寄生インダクタンスと関連します。そのため、スイッチング ループ面積を小さくすることで得られる総合的なメリットとして、電力 MOSFET への電圧・電流ストレスが低減されることによる信頼性と堅牢性の向上、入力電圧トランジエントに対する余裕の増大、そして **EMI** フィルタリングの容易化 (特に 30MHz を超える厳しい高周波帯域) などが挙げられます。

図 7-21. LM5005 電力段回路のスイッチング ループ

入力側の高周波セラミック バイパスコンデンサが、パルス電流の高い  $di/dt$  成分に対して主要なパスを提供します。低 ESL のセラミック バイパスコンデンサを、VIN ピンおよび PGND ピンへ低インダクタンスかつ短い配線で接続できる位置に配置します。SW をインダクタに接続するパターンは、できる限り短くし、過度の加熱なしに負荷電流を流すのに十分な幅にします。寄生抵抗を最小限に抑えるため、電流経路には短く太い配線、または銅ポリゴン(形状)を使用します。出力コンデンサはインダクタの VOUT 側に近づけて配置し、戻り接続は GND プレーンの銅を使って PGND ピンおよび LM5005 の露出パッドへ戻します。

#### 7.4.1.2 熱設計

他の電力変換デバイスと同様に、LM5005 は動作中に内部で電力を消費します。電力損失の影響によって、LM5005 の内部接合温度が周囲温度より高くなります。内部接合温度 ( $T_J$ ) は、周囲温度 ( $T_A$ )、電力損失 ( $P_D$ )、およびデバイスと PCB の組み合わせによる実効熱抵抗 ( $R_{\theta JA}$ ) の関数です。LM5005 の最大動作接合温度は  $125^{\circ}\text{C}$  であり、この値がデバイスの最大電力損失および高い周囲温度時の負荷電流の上限を規定します。式 23 および式 24 に、これらのパラメータの関係を示します。

$$P_D = P_{\text{OUT}} \times \left[ \frac{1 - \eta}{\eta} \right] - V_F \times I_{\text{OUT}} \times [1 - D] - I_{\text{OUT}}^2 \times R_{\text{DCR}} \times 1.5 \quad (23)$$

$$T_J = P_D \times \theta_{JA} + T_A \quad (24)$$

式 23 のインダクタの電力損失の近似値には、コア損失の係数 1.5 が含まれます。また、スナバが使用されている場合は、ターンオンとターンオフの両方のスイッチング遷移時に抵抗での電圧降下を観察して、電力損失を推定します。

高い周囲温度および大きな  $R_{\theta JA}$  は、利用可能な最大出力電流を低減します。接合部温度が  $165^{\circ}\text{C}$  を超えると、LM5005 はサーマル シャットダウンの開始と終了を繰り返します。サーマル シャットダウンは、ヒートシンクが不十分である、または消費電力が過剰であるという兆候である場合があります。より多くのサーマルビア、より大きな基板、または基板内の追加の熱拡散層を使用して、PCB のヒートシンクを改善します。

『半導体およびIC パッケージの熱評価基準』アプリケーション ノートで述べられているように、「熱に関する情報」に記載されている値は、アプリケーションの熱性能を見積もるための設計目的に対して常に有効ではありません。この表に示されている値は、実際のアプリケーションではめったに再現されない特定の条件下で測定されたものです。実効  $R_{\theta JA}$  は重要なパラメータであり、消費電力、周囲温度、PCB 面積、銅の放熱エリア、パッケージ直下のサーマルビアの数、空気の流

れ、周辺部品の配置など、多くの要因に依存します。LM5005 の露出パッドは、PGND に直接、熱的に接続されています。このパッドは、効果的な放熱と適切な電気的接続を確保するために、PCB の銅グランド プレーンへ直接はんだ付けする必要があります。最適な放熱 PCB 設計や、特定のアプリケーション環境における  $R_{\theta JA}$  の見積もりについては、[文書サポート](#)に記載されている資料を参考にします。

#### 7.4.1.3 グランド プレーン設計

既述のとおり、PCB の内部層のひとつを全面グランド プレーンとして使用することが推奨されます。グランド プレーンは敏感な回路やパターンのシールドとして機能するだけでなく、制御回路の低ノイズ基準電位を提供します。LM5005 の露出パッド直下にビア アレイを設け、PGND ピンをシステムのグランド プレーンに接続します。また、PGND ピンは入力コンデンサおよび出力コンデンサのリターン端子に直接接続します。PGND の配線にはスイッチング周波数におけるノイズが含まれており、負荷電流変動によりバウンドすることがあります。PGND、VIN、SW の電力系トレースは、グランド プレーンの片側に限定して配置することができます。グランド プレーンの反対側はノイズが非常に小さくなるため、敏感なアナログのパターン配線に向いています。

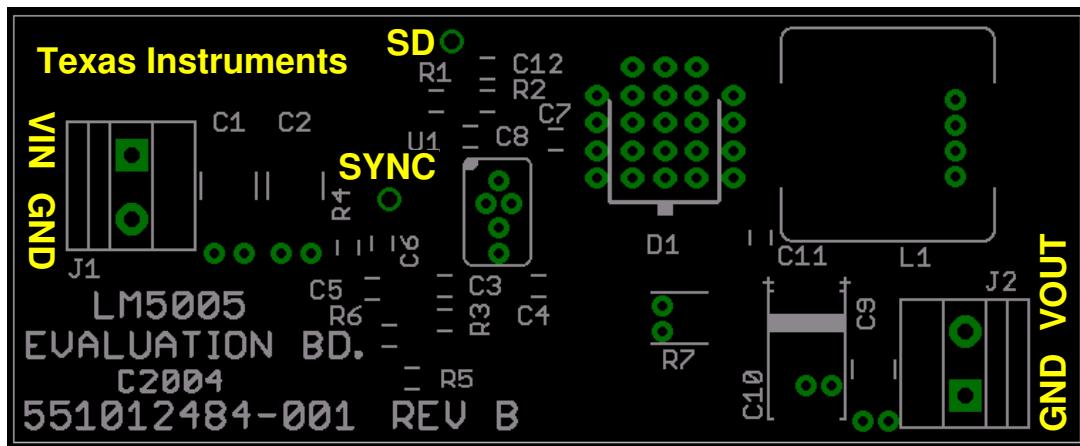

#### 7.4.2 レイアウト例

図 7-22. コンポーネント側

図 7-23. 半田面 (上面から見た図)

図 7-24. シルクスクリーン

## 8 デバイスおよびドキュメントのサポート

### 8.1 サード・パーティ製品に関する免責事項

サード・パーティ製品またはサービスに関するテキサス・インスツルメンツの出版物は、単独またはテキサス・インスツルメンツの製品、サービスと一緒に提供される場合に関係なく、サード・パーティ製品またはサービスの適合性に関する是認、サード・パーティ製品またはサービスの是認の表明を意味するものではありません。

### 8.2 デバイス サポート

#### 8.2.1 開発サポート

開発サポートについては、以下を参照してください。

- テキサス・インスツルメンツのリファレンス デザイン ライブドリについて、[TI Designs](#) を参照してください。

- TI の WEBENCH 設計環境については、[WEBENCH Design Center](#) をご覧ください

##### 8.2.1.1 WEBENCH® ツールによるカスタム設計

ここをクリックすると、WEBENCH® Power Designer により、LM5005 デバイスを使用するカスタム設計を作成できます。

1. 最初に、入力電圧 ( $V_{IN}$ )、出力電圧 ( $V_{OUT}$ )、出力電流 ( $I_{OUT}$ ) の要件を入力します。

2. オプティマイザのダイヤルを使用して、効率、占有面積、コストなどの主要なパラメータについて設計を最適化します。

3. 生成された設計を、テキサス・インスツルメンツが提供する他の方式と比較します。

WEBENCH Power Designer では、カスタマイズされた回路図と部品リストを、リアルタイムの価格と部品の在庫情報と併せて参照できます。

通常、次の操作を実行可能です。

- 電気的なシミュレーションを実行し、重要な波形と回路の性能を確認する

- 熱シミュレーションを実行し、基板の熱特性を把握する

- カスタマイズされた回路図やレイアウトを、一般的な CAD フォーマットで出力する

- 設計のレポートを PDF で印刷し、設計を共有する

WEBENCH ツールの詳細は、[www.ti.com/ja-jp/WEBENCH](http://www.ti.com/ja-jp/WEBENCH) でご覧になれます。

### 8.3 ドキュメントのサポート

#### 8.3.1 関連資料

関連資料については、以下を参照してください。

- テキサス・インスツルメンツ、[AN-1748 LM5005 評価基板 EVM ユーザー ガイド](#)

- テキサス・インスツルメンツ、[入力電圧と出力電圧の差が大きい場合の降圧レギュレータ構成マーケティング ホワイトペーパー](#)

- テキサス・インスツルメンツ、[コスト重視で要求の厳しいアプリケーションにおける広い  \$V\_{IN}\$  対応、低 EMI 同期式バック回路の価値ホワイトペーパー](#)

- Texas Instruments、[広い  \$V\_{IN}\$  に対応した電源管理 IC](#) は、設計を簡素化し、BOM コストを削減し、信頼性を向上マーケティング ホワイトペーパー

#### 8.3.1.1 PCB レイアウトについてのリソース

- テキサス・インスツルメンツ、[AN-1149『スイッチング電源のレイアウトのガイドライン』アプリケーション ノート](#)

- テキサス・インスツルメンツ、[AN-1229『SIMPLE SWITCHER® PCB レイアウト ガイドライン』アプリケーション ノート](#)

- テキサス・インスツルメンツ、[『AN-2162 DC/DC コンバータ向け伝導 EMI の簡単な成功事例』アプリケーション ノート](#)

- テキサス・インスツルメンツ、[『独自電源の構築 - レイアウトの考慮事項』セミナー](#)

- テキサス・インスツルメンツ、[『LM4360x および LM4600x による低放射 EMI レイアウトの簡単な設計』アプリケーション ノート](#)

- テキサス・インスツルメンツ、[誘導性寄生の最小化による降圧コンバータのEMIと電圧ストレスの低減アナログ デザイン・ジャーナル](#)

### 8.3.1.2 熱設計についてのリソース

- テキサス・インスツルメンツ、[AN-1520A『露出パッドで最良の熱抵抗を実現するための基板レイアウトガイド』アプリケーション・ノート](#)

- テキサス・インスツルメンツ、[AN-2020『過去ではなく、現在の議見による熱設計』アプリケーション・ノート](#)

- テキサス・インスツルメンツ、[PowerPAD™ 入門アプリケーション概要](#)

- テキサス・インスツルメンツ、[『熱特性強化型パッケージ PowerPAD™』アプリケーション・ノート](#)

- テキサス・インスツルメンツ、[半導体およびICパッケージの熱評価基準アプリケーション・ノート](#)

- テキサス・インスツルメンツ、[『LM43603 および LM43602 によるシンプルな熱設計』アプリケーション・ノート](#)

- テキサス・インスツルメンツ、[『新しい熱評価基準の解説』アプリケーション・ノート](#)

## 8.4 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

## 8.5 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの[使用条件](#)を参照してください。

## 8.6 商標

PowerPAD™ and テキサス・インスツルメンツ E2E™ are trademarks of Texas Instruments.

WEBENCH® and SIMPLE SWITCHER® are registered trademarks of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

## 8.7 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことをお勧めします。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

## 8.8 用語集

### テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 9 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision E (November 2016) to Revision F (December 2025) | Page |

|-----------------------------------------------------------------------|------|

| ドキュメント全体にわたって表、図、相互参照の採番方法を更新                                         | 1    |

| 文書全体にわたり、従来の用語「マスター」を「コントローラ」に、「スレーブ」から「ペリフェラル」に変更                    | 1    |

| $V_{CC}$ 電流制限値を以下のように更新: 20mA から 25mA                                 | 6    |

| $V_{CC}$ UVLO スレッショルドを以下のように更新: 6.35V から: 5.35V                       | 6    |

| $V_{CC}$ 低電圧ヒステリシスを以下のように更新: 1V から: 0.25V                             | 6    |

| 代表的なバイアス電流、 $I_{IN}$ 電流情報を追加                                          | 6    |

---

|                                                                        |   |

|------------------------------------------------------------------------|---|

| • バイアス電流 $I_{IN}$ の最大電流を以下のように更新: 5mA から 4.5mA.....                    | 6 |

| • 標準シャットダウン電流を以下のように更新: 60 $\mu$ A から 48 $\mu$ A.....                  | 6 |

| • 最大シャットダウン電流を以下のように更新: 100 $\mu$ A から 85 $\mu$ A.....                 | 6 |

| • プリチャージ スイッチのオン時間パラメータを追加.....                                        | 6 |

| • 降圧スイッチの $R_{ds\_on}$ を以下のように更新: 160m $\Omega$ から 170m $\Omega$ ..... | 6 |

| • 昇圧 UVLO ヒステリシスを以下のように更新: 0.56V から: 0.8V.....                         | 6 |

| • サイクルごとの電流制限遅延を以下のように更新: 100nsec から 75nsec.....                       | 6 |

---

|                                                                                                                                                          | <b>Page</b> |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| • 「ESD 定格」表、「機能説明」セクション、「デバイスの機能モード」セクション、「アプリケーションと実装」セクション、「電源に関する推奨事項」セクション、「レイアウト」セクション、「デバイスおよびドキュメントのサポート」セクション、「メカニカル、パッケージ、および注文情報」セクションを追加..... | 1           |

| • アプリケーション概略回路図の画像を削除.....                                                                                                                               | 1           |

| • 代表的なアプリケーション回路の画像を追加.....                                                                                                                              | 1           |

| • 熱に関する情報表における接合部 – 周囲間熱抵抗 $R_{\theta JA}$ の値を、次の値から変更: 40 から 35.2.....                                                                                  | 5           |

| • 熱に関する情報表における接合部 – ケース間 $R_{\theta JC(bot)}$ 値を以下の値から変更: 4 から 1.2.....                                                                                  | 5           |

| • 効率と $I_{OUT}$ および $V_{IN}$ の関係のグラフを変更.....                                                                                                             | 7           |

| • $V_{OUT} > 7.5V$ における $R_{RAMP}$ から $V_{CC}$ への図を削除.....                                                                                               | 13          |

| • $V_{OUT} > 7.5V$ のときの外部ランプ抵抗の $V_{CC}$ への接続の図を追加.....                                                                                                  | 13          |

---

## 10 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins    | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| LM5005MH/NOPB         | Active        | Production           | HTSSOP (PWP)   20 | 73   TUBE             | Yes         | Call TI   Sn                         | Level-1-260C-UNLIM                | -40 to 125   | LM5005<br>MH        |

| LM5005MH/NOPB.A       | Active        | Production           | HTSSOP (PWP)   20 | 73   TUBE             | Yes         | Call TI                              | Level-1-260C-UNLIM                | -40 to 125   | LM5005<br>MH        |

| LM5005MH/NOPB.B       | Active        | Production           | HTSSOP (PWP)   20 | 73   TUBE             | Yes         | Call TI                              | Level-1-260C-UNLIM                | -40 to 125   | LM5005<br>MH        |

| LM5005MHX/NOPB        | Active        | Production           | HTSSOP (PWP)   20 | 2500   LARGE T&R      | Yes         | SN                                   | Level-1-260C-UNLIM                | -40 to 125   | LM5005<br>MH        |

| LM5005MHX/NOPB.A      | Active        | Production           | HTSSOP (PWP)   20 | 2500   LARGE T&R      | Yes         | SN                                   | Level-1-260C-UNLIM                | -40 to 125   | LM5005<br>MH        |

| LM5005MHX/NOPB.B      | Active        | Production           | HTSSOP (PWP)   20 | 2500   LARGE T&R      | Yes         | SN                                   | Level-1-260C-UNLIM                | -40 to 125   | LM5005<br>MH        |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

---

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

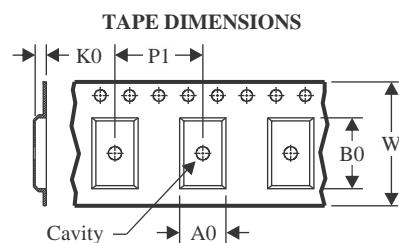

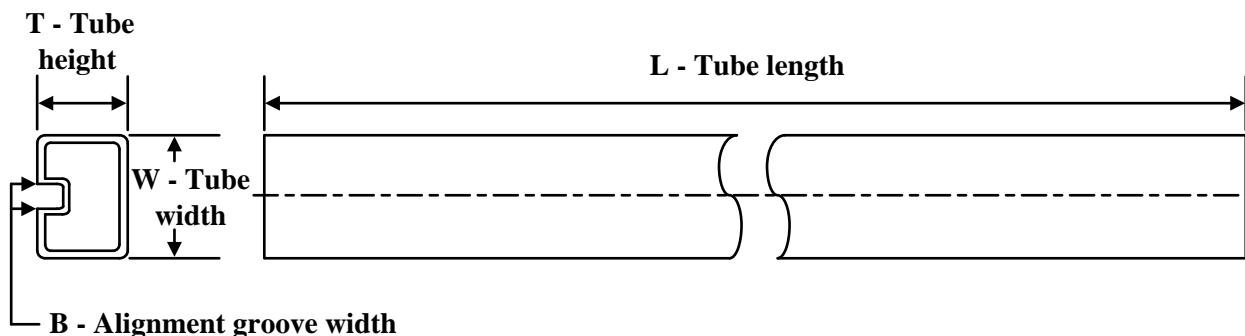

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

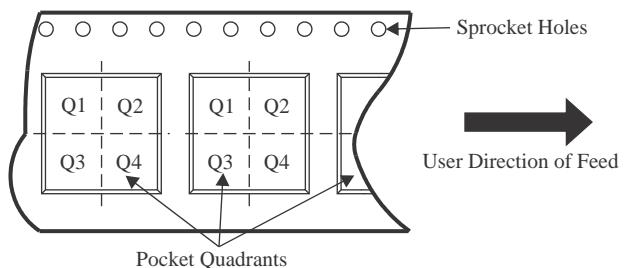

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

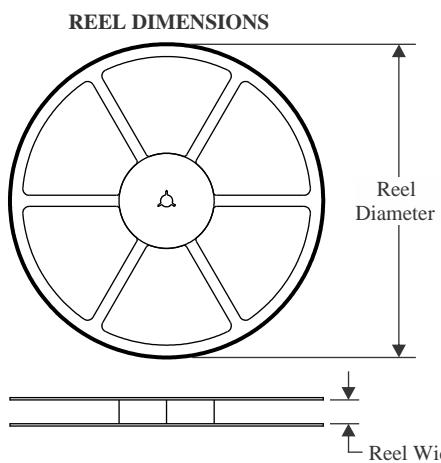

| Device         | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|----------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| LM5005MHX/NOPB | HTSSOP       | PWP             | 20   | 2500 | 330.0              | 16.4               | 6.95    | 7.0     | 1.4     | 8.0     | 16.0   | Q1            |

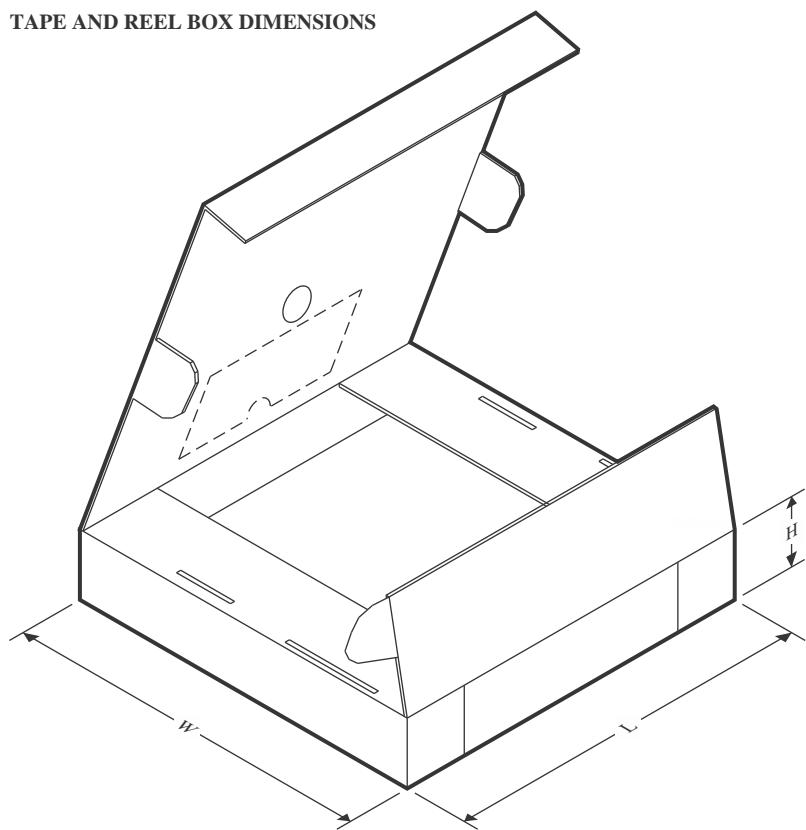

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LM5005MHX/NOPB | HTSSOP       | PWP             | 20   | 2500 | 367.0       | 367.0      | 35.0        |

**TUBE**

\*All dimensions are nominal

| Device          | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T ( $\mu$ m) | B (mm) |

|-----------------|--------------|--------------|------|-----|--------|--------|--------------|--------|

| LM5005MH/NOPB   | PWP          | HTSSOP       | 20   | 73  | 495    | 8      | 2514.6       | 4.06   |

| LM5005MH/NOPB   | PWP          | HTSSOP       | 20   | 73  | 495    | 8      | 2514.6       | 4.06   |

| LM5005MH/NOPB.A | PWP          | HTSSOP       | 20   | 73  | 495    | 8      | 2514.6       | 4.06   |

| LM5005MH/NOPB.A | PWP          | HTSSOP       | 20   | 73  | 495    | 8      | 2514.6       | 4.06   |

| LM5005MH/NOPB.B | PWP          | HTSSOP       | 20   | 73  | 495    | 8      | 2514.6       | 4.06   |

| LM5005MH/NOPB.B | PWP          | HTSSOP       | 20   | 73  | 495    | 8      | 2514.6       | 4.06   |

PWP (R-PDSO-G20)

PowerPAD™ PLASTIC SMALL OUTLINE

4073225-4/1 05/11

- NOTES:

- All linear dimensions are in millimeters.

- This drawing is subject to change without notice.

- Body dimensions do not include mold flash or protrusions. Mold flash and protrusion shall not exceed 0.15 per side.

- This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at [www.ti.com](http://www.ti.com) <<http://www.ti.com>>.

- See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

- Falls within JEDEC MO-153

PowerPAD is a trademark of Texas Instruments.

## MECHANICAL DATA

PWP0020A

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月