# LM5171-Q1 デュアルチャネル双方向コントローラ

## 1 特長

- 車載アプリケーション用に AEC-Q100 認定済み:

- デバイス温度グレード 1:-40°C~+125°C の動作時 周囲温度範囲

- デバイス HBM ESD 分類レベル 2

- デバイス CDM ESD 分類レベル C4B

- 機能安全対応**

- 機能安全システムの設計に役立つ資料を利用可能

- 最大定格は HV ポート 85V, LV ポート 80V

- 双方向電流レギュレーションの標準精度 1%

- チャネル電流監視の標準精度 1%

- 監視および診断用の I<sup>2</sup>C インターフェイス

- 3.5V 1% の基準電圧を内蔵

- 5V 10mA バイアス電源を内蔵

- ピーク 5A のハーフブリッジゲートドライバ

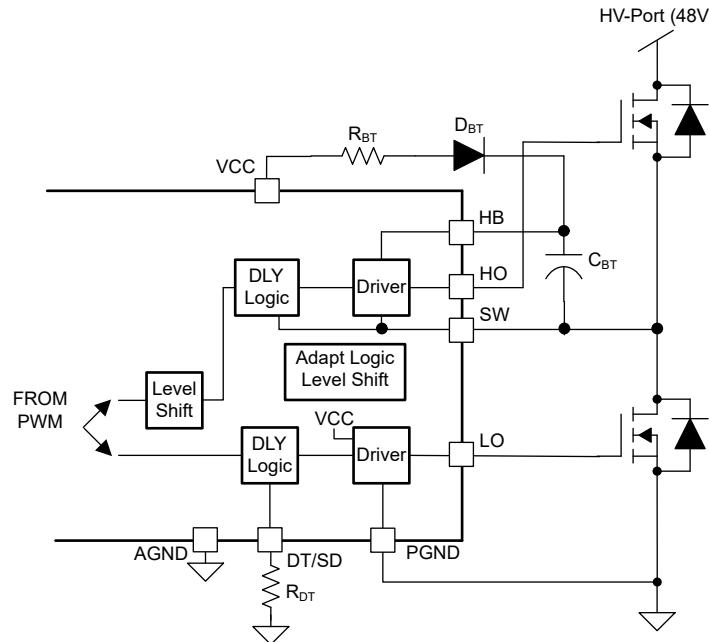

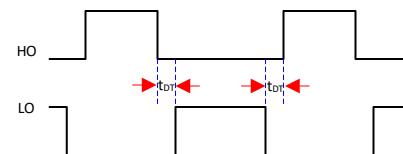

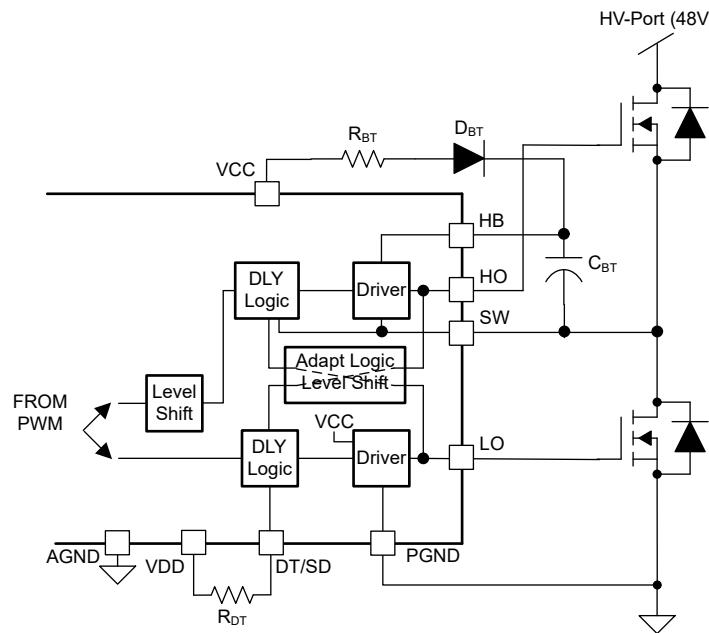

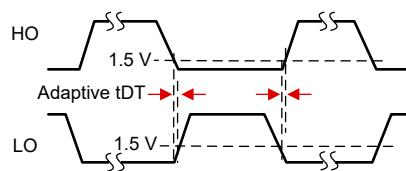

- プログラム可能またはアダプティブ デッドタイム制御

- 最大 1MHz まで、発振器の周波数をプログラム可能で、オプションとして外部クロックへの同期も可能

- 独立したチャネルリネーブル制御入力

- 電流と電圧の両方のループ制御機能を内蔵

- ピーク電流制限をサイクル単位でプログラム可能

- 過熱シャットダウン

- HV および LV ポートの過電圧保護

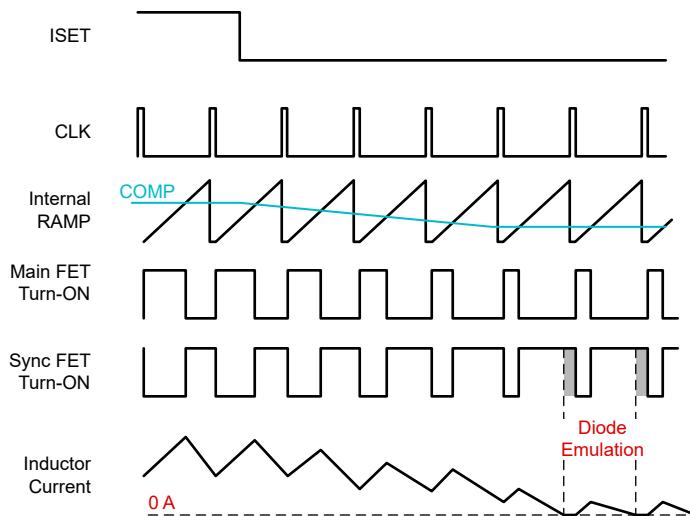

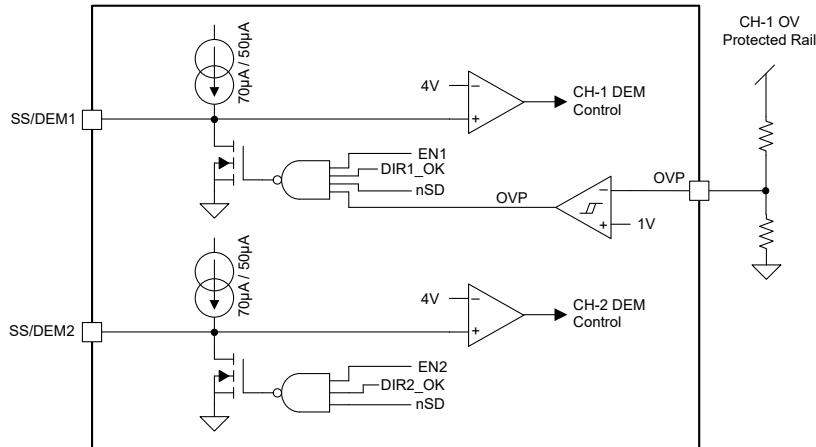

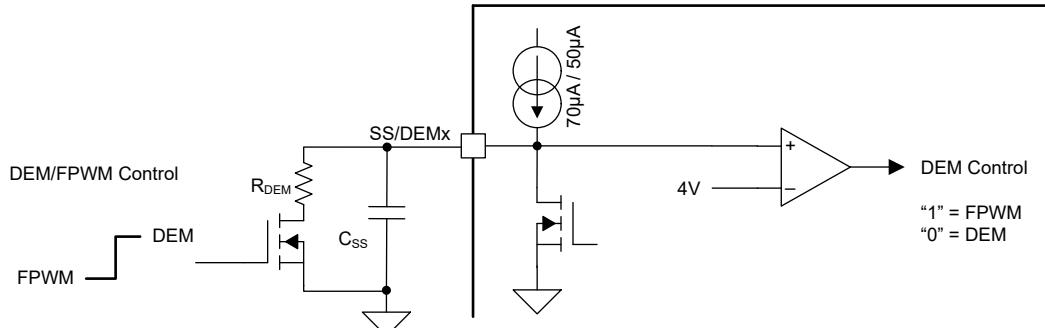

- 動的に選択可能なダイオード エミュレーションモードと強制 PWM動作モード

- ソフトスタート タイマをプログラム可能

- マルチフェーズと独立チャネルの両方の動作をサポート

- 緊急シャットダウン ラッチをサポート

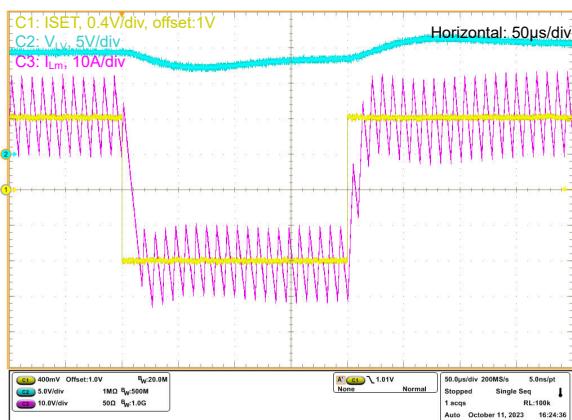

方向変更によるインダクタ電流のトラッキング

## 2 アプリケーション

- 車載用デュアルバッテリシステム

- スーパー キャパシタまたはバッテリバックアップ電力コンバータ

- スタッカブルな大電力降圧または昇圧アプリケーション

## 3 説明

LM5171-Q1 コントローラは、高電圧かつ高精度なデュアルチャネル双方向コンバータを実現するための基本的な構成要素を備えています。例として、デュアルバッテリシステムが挙げられます。LM5171-Q1 はマルチフェーズの並列動作をサポートし、各位相で平衡な電流共有を行います。また、LM5171-Q1 は独立チャネルの双方向動作もサポートしているため、多相の昇降圧、または独立した昇降圧として動作するスタンドアロンのコントローラとして多用途に使用できます。

デュアルチャネルの差動電流センスアンプと、専用のチャネル電流監視により、標準値で 1% の精度が得られます。堅牢な 5A ハーフブリッジゲートドライバは、並列 MOSFET を駆動して、チャネルあたりの電力をより大きくできます。コントローラを、ダイオードエミュレーションモード (DEM) と強制 PWM (FPWM) モードのいずれかで動作するように動的にプログラムします。多用途の保護機能には、サイクル単位の電流制限、過電圧保護、過熱保護、緊急シャットダウン ラッチが含まれます。

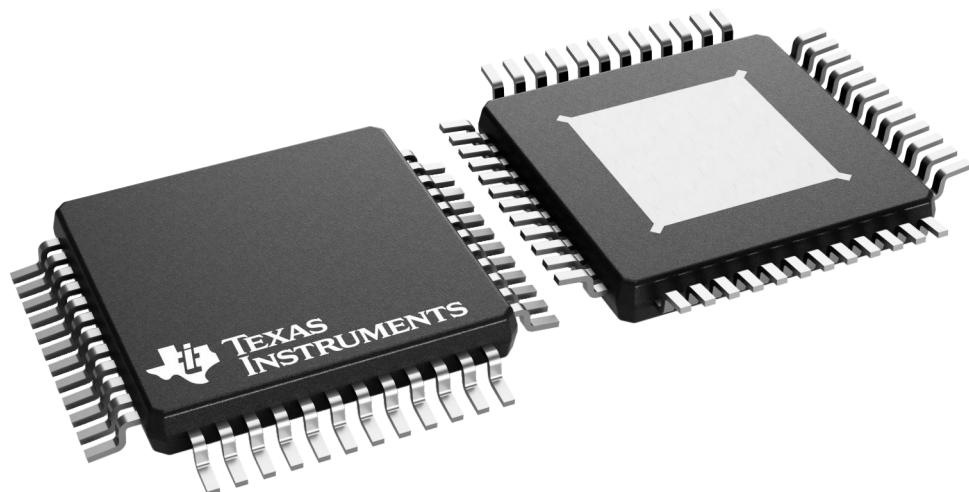

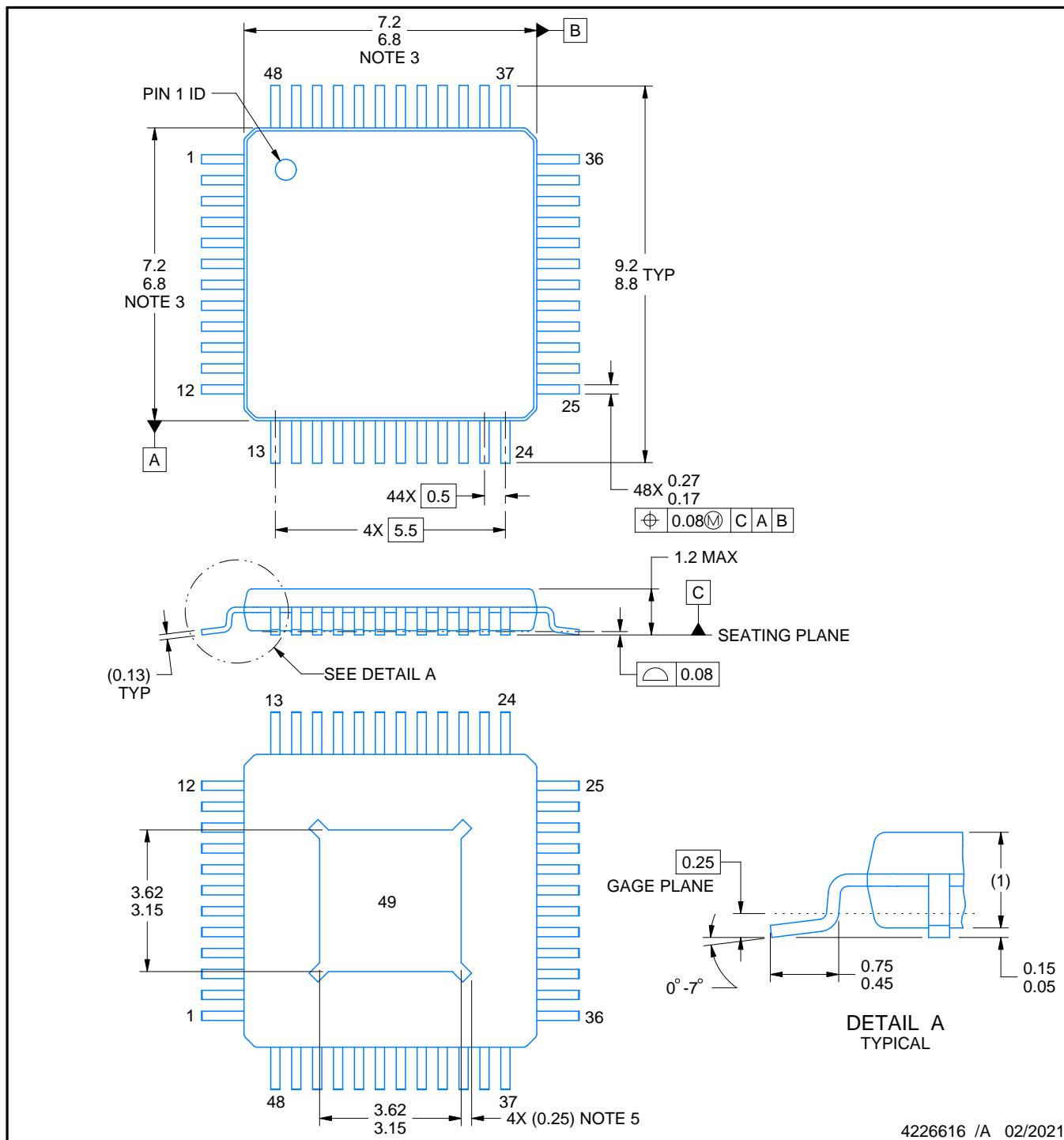

### パッケージ情報

| 部品番号      | パッケージ <sup>(1)</sup> | パッケージサイズ(公称) |

|-----------|----------------------|--------------|

| LM5171-Q1 | TQFP (48)            | 7mm × 7mm    |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

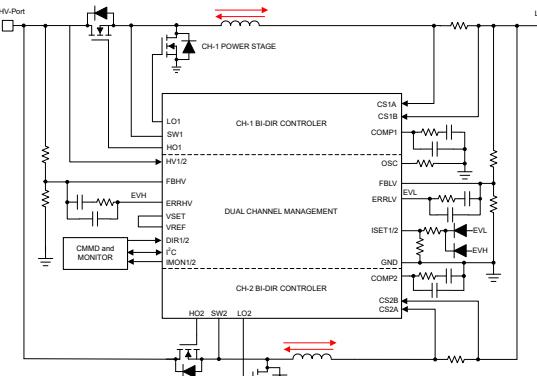

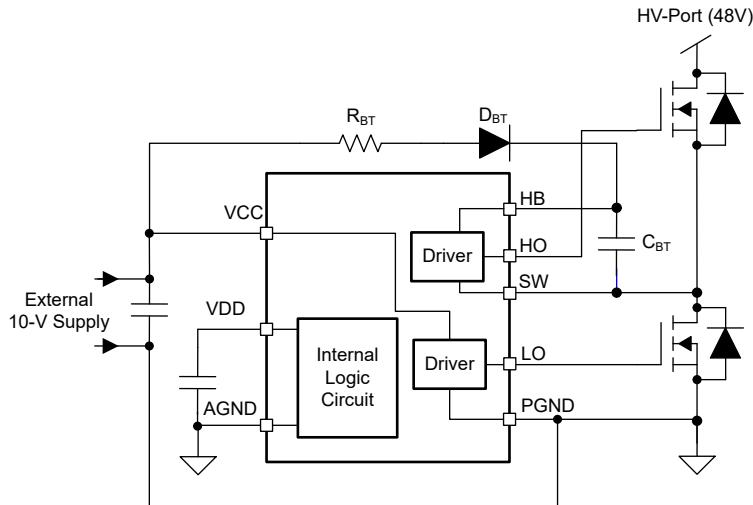

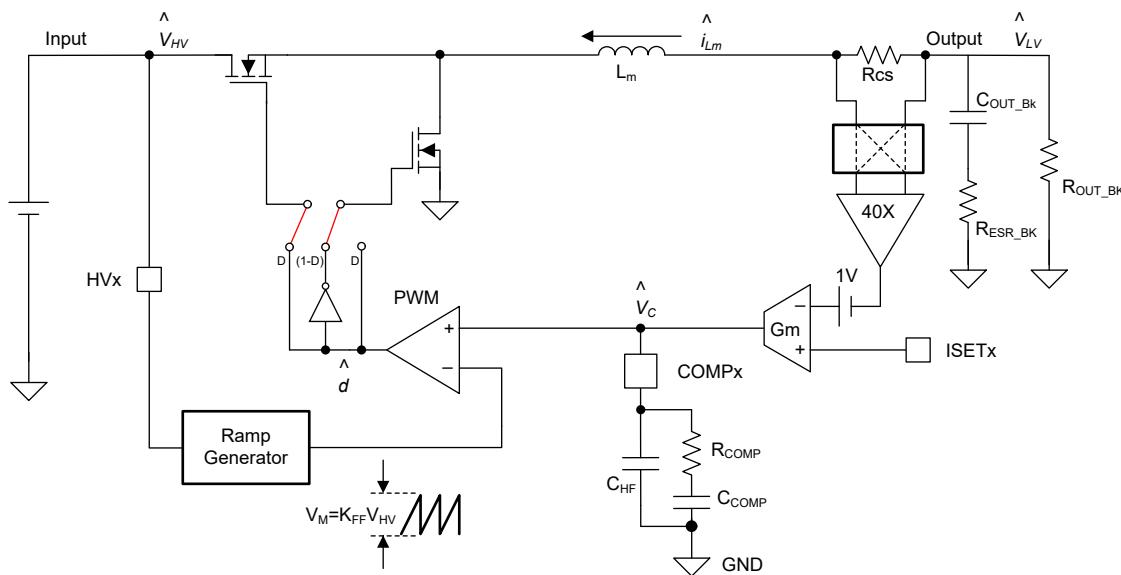

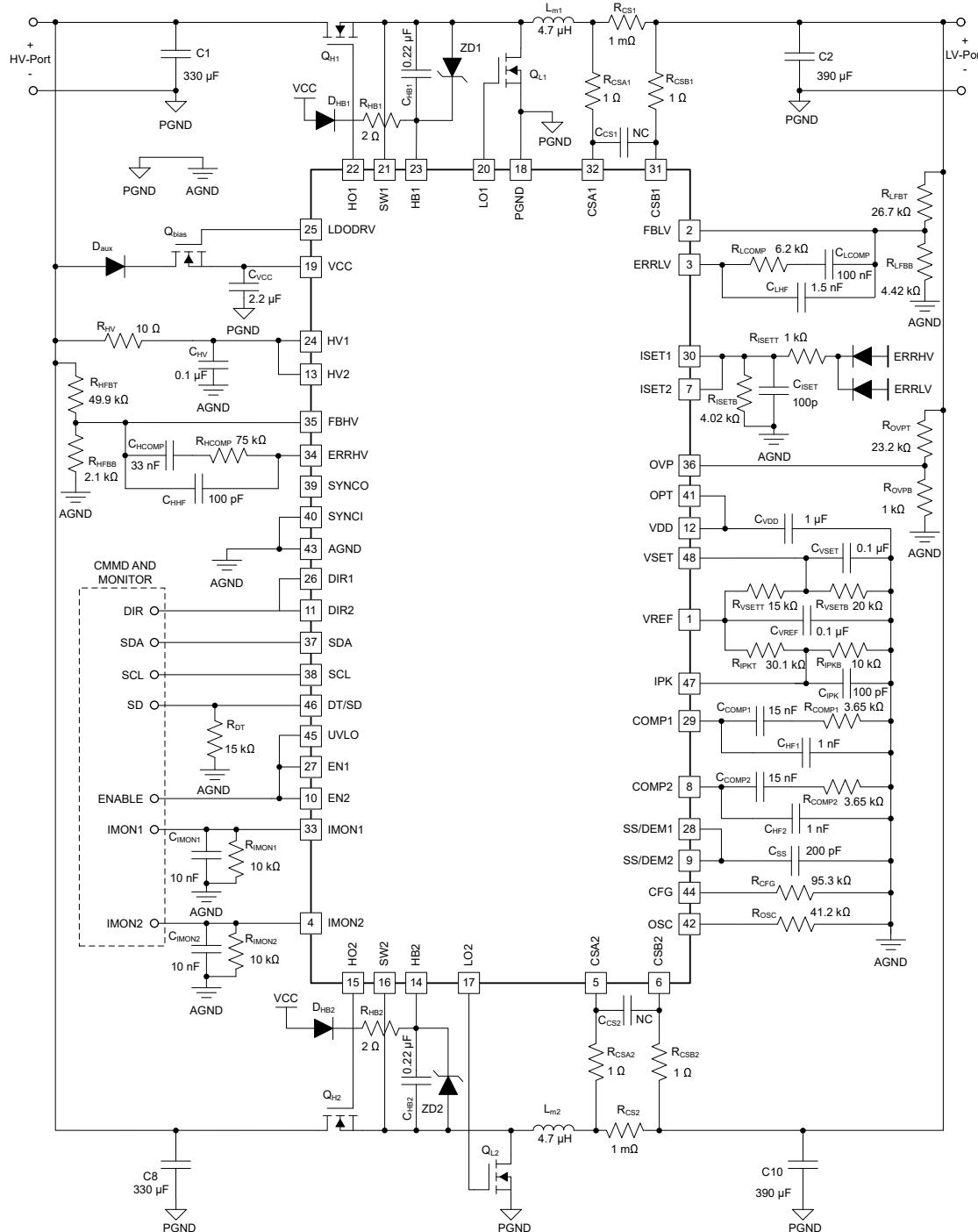

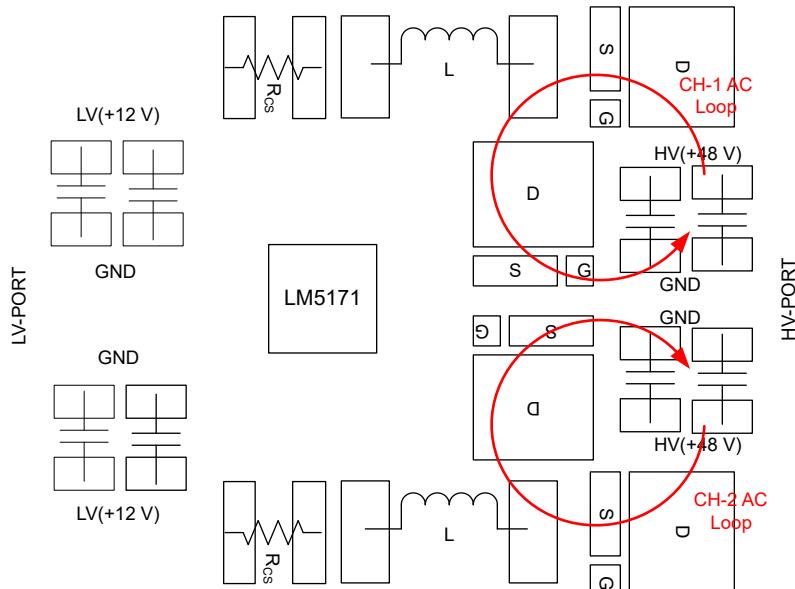

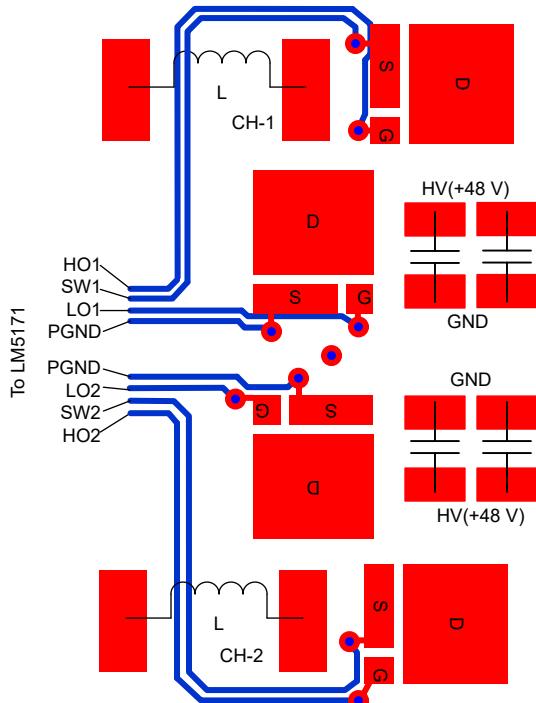

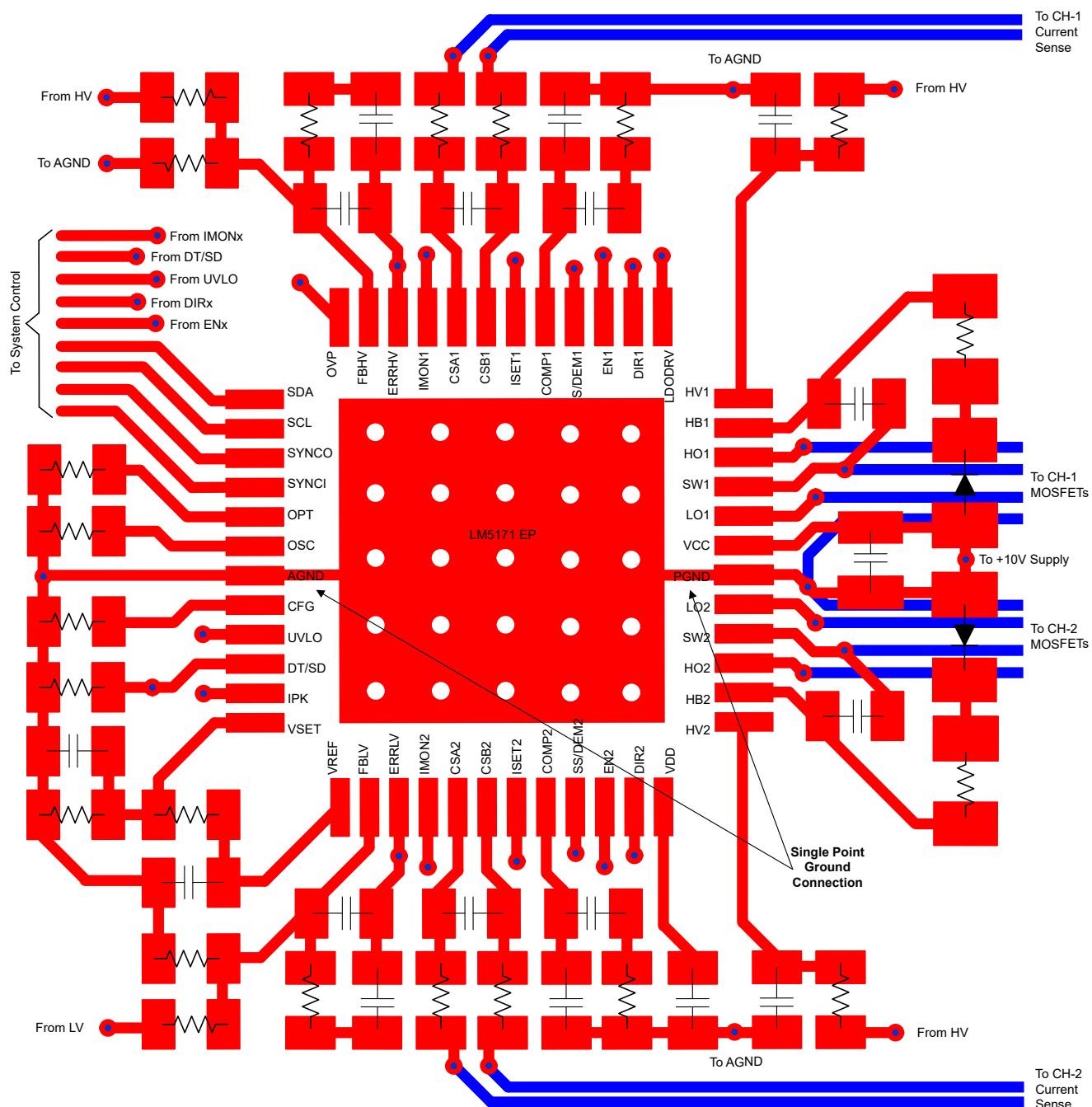

アプリケーションの簡略回路図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール(機械翻訳)を使用していることがあり、TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

English Data Sheet: SNVSC75

## 目次

|                                           |           |                                            |           |

|-------------------------------------------|-----------|--------------------------------------------|-----------|

| <b>1 特長</b>                               | <b>1</b>  | 7.7 定義されたレジスタ アドレスへの 単一書き込み                | <b>42</b> |

| <b>2 アプリケーション</b>                         | <b>1</b>  | 7.8 定義されたレジスタ アドレスから開始されるシーケン<br>シャル WRITE | <b>42</b> |

| <b>3 説明</b>                               | <b>1</b>  | 7.9 REGFIELD レジスタ                          | <b>43</b> |

| <b>4 ピン構成および機能</b>                        | <b>3</b>  |                                            |           |

| <b>5 仕様</b>                               | <b>6</b>  | <b>8 アプリケーションと実装</b>                       | <b>48</b> |

| 5.1 絶対最大定格                                | 6         | 8.1 アプリケーション情報                             | 48        |

| 5.2 ESD 定格                                | 6         | 8.2 PWM から ISET ピン                         | 57        |

| 5.3 推奨動作条件                                | 7         | 8.3 ISET クランプ                              | 57        |

| 5.4 熱に関する情報                               | 7         | 8.4 動的デッドタイム調整                             | 58        |

| 5.5 電気的特性                                 | 7         | 8.5 未使用ピンの適切な終端                            | 59        |

| 5.6 タイミング要件                               | 13        | 8.6 代表的なアプリケーション                           | 60        |

| 5.7 代表的特性                                 | 15        | 8.7 電源に関する推奨事項                             | 76        |

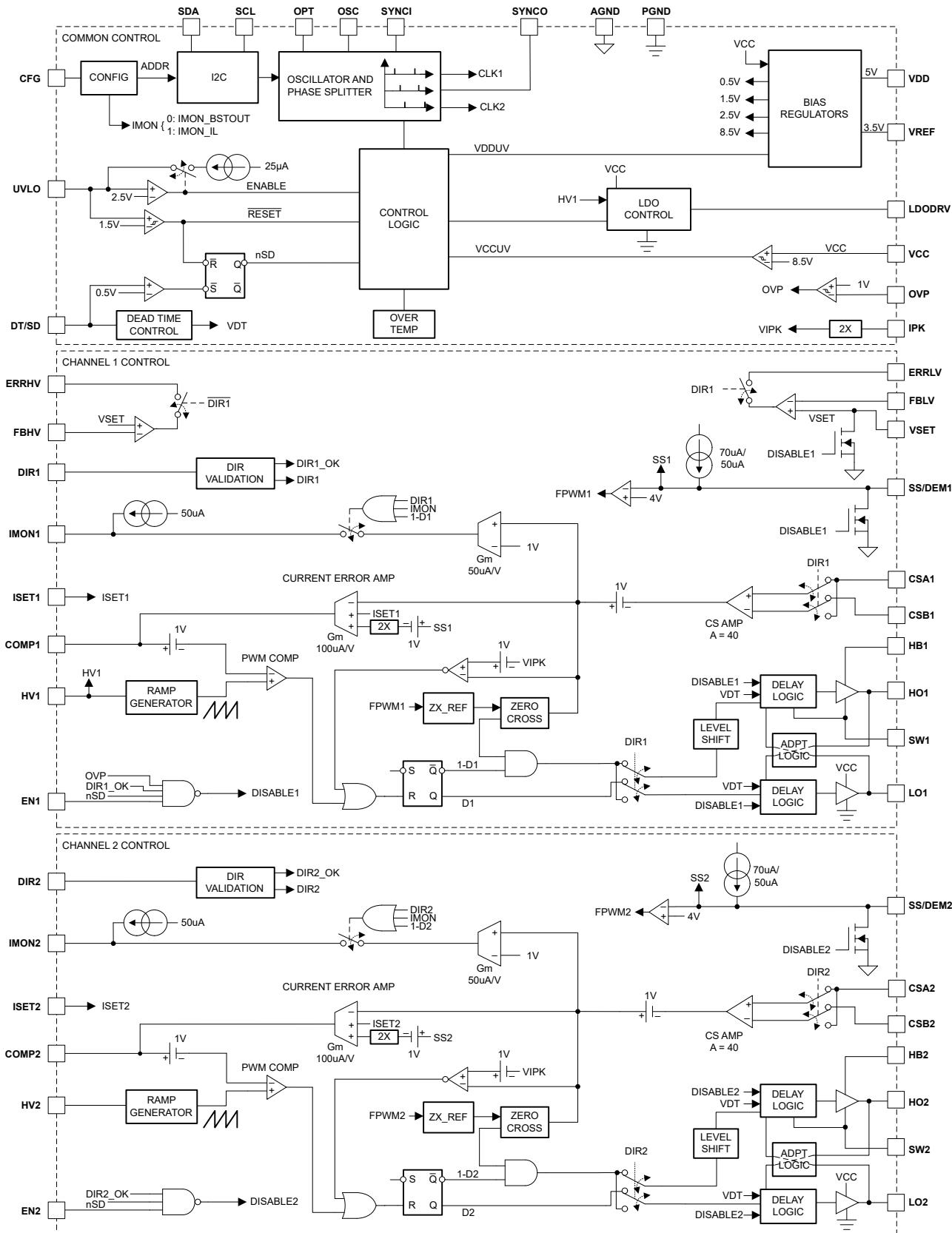

| <b>6 詳細説明</b>                             | <b>18</b> | 8.8 レイアウト                                  | 77        |

| 6.1 概要                                    | 18        | <b>9 デバイスおよびドキュメントのサポート</b>                | <b>81</b> |

| 6.2 機能ブロック図                               | 19        | 9.1 デバイス サポート                              | 81        |

| 6.3 機能説明                                  | 20        | 9.2 ドキュメントの更新通知を受け取る方法                     | 81        |

| 6.4 デバイスの機能モード                            | 39        | 9.3 サポート・リソース                              | 81        |

| <b>7 レジスタ</b>                             | <b>40</b> | 9.4 商標                                     | 81        |

| 7.1 I <sup>2</sup> C シリアル インターフェイス        | 40        | 9.5 静電気放電に関する注意事項                          | 81        |

| 7.2 I <sup>2</sup> C バス動作                 | 40        | 9.6 用語集                                    | 81        |

| 7.3 クロック ストレッチ                            | 41        | <b>10 改訂履歴</b>                             | <b>81</b> |

| 7.4 データ転送フォーマット                           | 41        | <b>11 メカニカル、パッケージ、および注文情報</b>              | <b>82</b> |

| 7.5 定義されたレジスタ アドレスからの単一読み取り               | 41        |                                            |           |

| 7.6 定義されたレジスタ アドレスから開始されるシーケン<br>シャル READ | 41        |                                            |           |

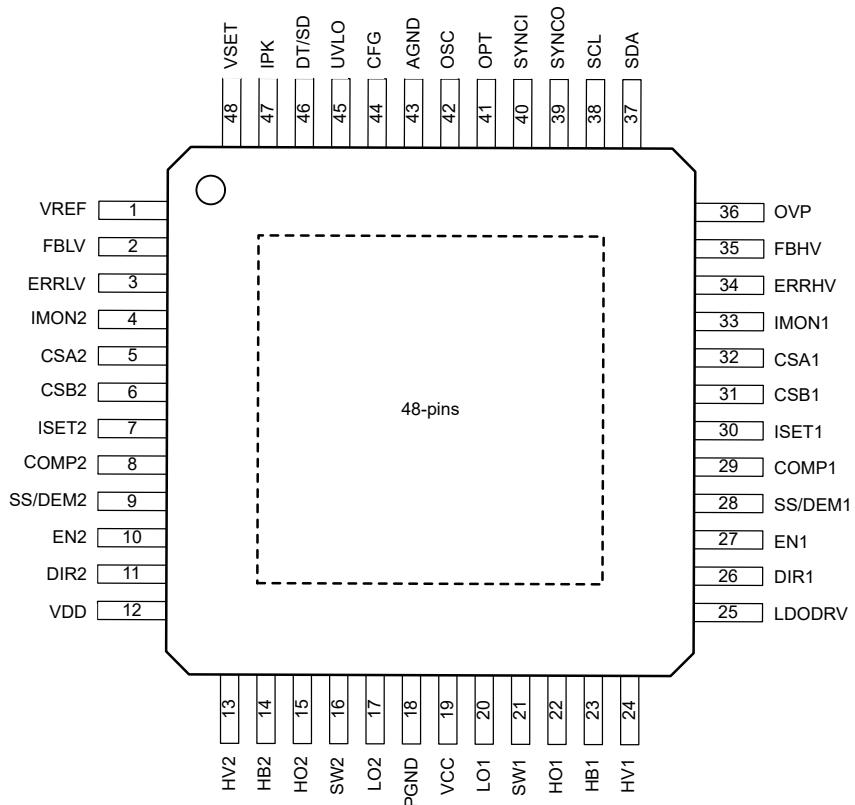

## 4 ピン構成および機能

図 4-1. LM5171-Q1 PHP パッケージ、48 ピン TQFP (上面図)

表 4-1. ピンの機能

| 番号 | ピン<br>名称 | I/O <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                                                 |

|----|----------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | VREF     | P                  | 内蔵の 3.5V +/- 1% リファレンス電圧の出力。VREF ピンと AGND の間に 0.1 $\mu$ F コンデンサを接続します。                                                                                                                                                                                                             |

| 2  | FBLV     | I                  | 降圧モードのエラー アンプの反転入力。このエラー アンプは、DIR1 が High のときアクティブになります。このアンプを使用しない場合は、FBLV と ERRLV を短絡します。                                                                                                                                                                                        |

| 3  | ERRLV    | O                  | 降圧モードのエラー アンプ出力。このエラー アンプは、DIR1 が High のときアクティブになります。このアンプを使用しない場合は、FBLV と ERRLV を短絡します。                                                                                                                                                                                           |

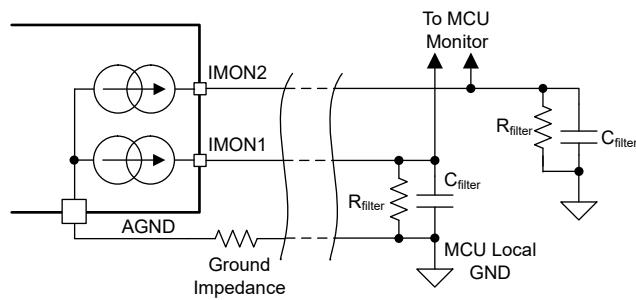

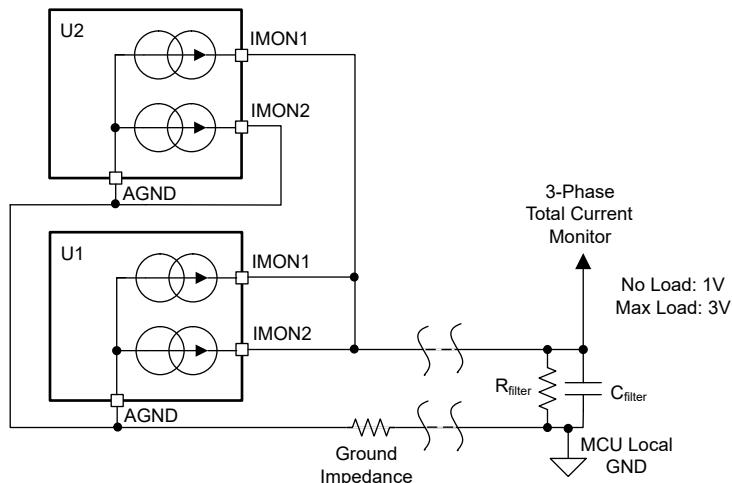

| 4  | IMON2    | O                  | CH-2 電流監視ピン。このピンから電流源が流れ出します。電流源は、CFG の選択に基づいて CH-2 インダクタ電流または CH-2 昇圧モードの出力電流に比例します。IMON2 から AGND への間に終端抵抗とフィルタ コンデンサを配置すると、CH-2 DC 電流レベルを表す DC 電圧が生成されます。IMON2 ピンの内部 50 $\mu$ A オフセット DC 電流源により、アクティブ信号がグランド ノイズよりも高く上昇し、監視のノイズ耐性が向上します。                                         |

| 5  | CSA2     | I                  | CH-2 差動電流センス入力。CH-2 電流センス抵抗は、これら 2 本のピンの間に配置されます。CSA2 ピンはパワー インダクタに、CSB2 ピンは LV ポートに接続します。                                                                                                                                                                                         |

| 6  | CSB2     | I                  |                                                                                                                                                                                                                                                                                    |

| 7  | ISET2    | I                  | CH-2 電流プログラミング ピン。ISET2 には 1V のオフセットがあります。つまり CH-2 インダクタ電流は (ISET2-1V) に比例します。DEM では、ISET2 が 1V 未満のとき、インダクタ電流は 0 になります。FPWM では、ISET2 が 1V を下回ると、インダクタ電流が反転します。                                                                                                                     |

| 8  | COMP2    | O                  | CH-2 トランジコンダクタンス (gm) エラー アンプの出力と CH-2 PWM コンパレータの反転入力。ループ補償回路をこのピンに接続します。                                                                                                                                                                                                         |

| 9  | SS/DEM2  | I                  | ISET2 ソフトスタート ピン。また、SS/DEM2 ピンは DEM と FPWM のどちらかに CH-2 を設定します。外部コンデンサにより、ソフトスタート中の SS/DEM2 ピン電圧のランプ レートが設定されます。ソフトスタート中は、SS/DEM2 が ISET2 電圧を無効にします。外部電圧ループを使用する場合は、100pF のソフトスタート コンデンサを使用します。SS/DEM2 と AGND の間に 60.4k $\Omega$ 抵抗があるため、CH-2 を DEM に設定します。CH-2 は抵抗なしで FPWM で動作します。 |

表 4-1. ピンの機能 (続き)

| 番号 | ピン<br>名称 | I/O <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                                              |

|----|----------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10 | EN2      | I                  | CH-2 イネーブルピン。EN2 を 2V より高くすると、SS/DEM2 プルダウンがオフになり、CH-2 はソフトスタートシーケンスを開始できます。EN2 を 1V 未満にプルすると、SS/DEM2 コンデンサが放電され、Low に保持されます。SS/DEM2 が放電されると、両方のチャネルのハイサイドおよびローサイドゲートドライバが Low 状態に保持されます。                                                                                       |

| 11 | DIR2     | I                  | CH-2 方向コマンド入力。DIR2 ピンを 2V より高くすると、コンバータは降圧モードに設定されます。DIR2 を 1V 未満にすると、コンバータは昇圧モードに設定されます。DIR2 ピンがオープンのままになっている場合、デバイスは無効なコマンドを検出し、MOSFET ゲートドライバが Low 状態の CH-2 を無効にします。                                                                                                         |

| 12 | VDD      | P                  | 5V 内部 LDO の出力。VDD ピンと AGND の間に 1 $\mu$ F コンデンサを接続します。                                                                                                                                                                                                                           |

| 13 | HV2      | I                  | CH-2 コントローラの HV ポートに接続します。                                                                                                                                                                                                                                                      |

| 14 | HB2      | I                  | CH-2 ハイサイドゲートドライバのブートストラップ電源。このピンと SW2 との間に、0.22 $\mu$ F コンデンサを接続します。このピンと SW2 との間にツェナーダイオードを接続して、ハイサイドドライバを過電圧から保護します。                                                                                                                                                         |

| 15 | HO2      | O                  | CH-2 ハイサイドゲートドライバ出力。短い低インダクタンスのパスを経由して、ハイサイド N チャネル MOSFET のゲートに接続します。                                                                                                                                                                                                          |

| 16 | SW2      | P                  | CH-2 スイッチングノード。ハイサイド N チャネル MOSFET のソースに直接接続します。                                                                                                                                                                                                                                |

| 17 | LO2      | O                  | CH-2 ローサイドゲートドライバ出力。短い低インダクタンスのパスを経由して、ローサイド N チャネル MOSFET のゲートに接続します。                                                                                                                                                                                                          |

| 18 | PGND     | G                  | ローサイドゲートドライバおよび VCC バイアス電源のパワー グラウンド接続ピン。                                                                                                                                                                                                                                       |

| 19 | VCC      | P                  | VCC バイアス電源ピン。VCC ピンと AGND の間に 2.2 $\mu$ F コンデンサを接続します。                                                                                                                                                                                                                          |

| 20 | LO1      | O                  | CH-1 ローサイドゲートドライバ出力。短い低インダクタンスのパスを経由して、ローサイド N チャネル MOSFET のゲートに接続します。                                                                                                                                                                                                          |

| 21 | SW1      | P                  | CH-1 スイッチングノード。ハイサイド N チャネル MOSFET のソースに直接接続します。                                                                                                                                                                                                                                |

| 22 | HO1      | O                  | CH-1 ハイサイドゲートドライバ出力。短い低インダクタンスのパスを経由して、ハイサイド N チャネル MOSFET のゲートに接続します。                                                                                                                                                                                                          |

| 23 | HB1      | I                  | CH-1 ハイサイドゲートドライバのブートストラップ電源入力。このピンと SW1 との間に、0.22 $\mu$ F コンデンサを接続します。このピンと SW1 との間にツェナーダイオードを接続して、ハイサイドドライバを過電圧から保護します。                                                                                                                                                       |

| 24 | HV1      | I                  | CH-1 コントローラの HV ポートに接続します。                                                                                                                                                                                                                                                      |

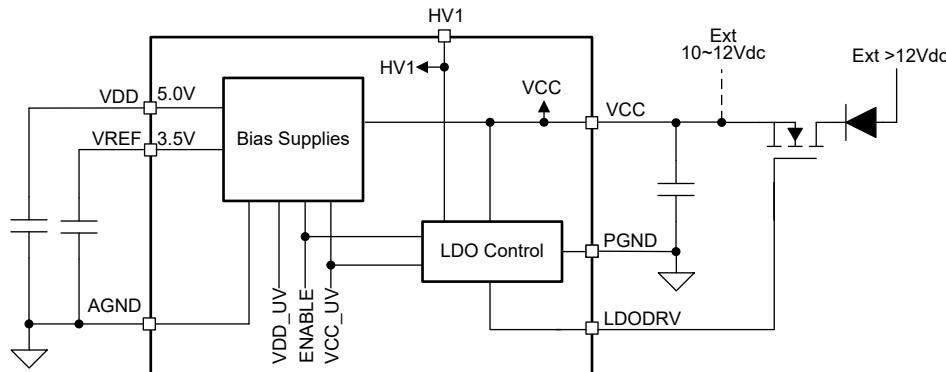

| 25 | LDODRV   | O                  | LDO MOSFET ドライバ。LDO MOSFET ゲートに接続することで、レギュレートされた 9V VCC を取得します。このピンを使用しない場合は、オープンのままにしてください。                                                                                                                                                                                    |

| 26 | DIR1     | I                  | CH-1 方向コマンド入力。DIR1 ピンを 2V より高くすると、コンバータは降圧モードに設定されます。DIR1 を 1V 未満にすると、コンバータは昇圧モードに設定されます。DIR1 ピンがオープンのままになっている場合、デバイスは無効なコマンドを検出し、MOSFET ゲートドライバが Low 状態の CH-1 を無効にします。                                                                                                         |

| 27 | EN1      | I                  | CH-1 イネーブルピン。EN1 を 2V より高くすると、SS1 プルダウンがオフになり、CH-1 はソフトスタートシーケンスを開始できます。EN1 を 1V 未満にプルすると、SS1 コンデンサが放電され、Low に保持されます。SS1 が放電されると、両方のチャネルのハイサイドおよびローサイドゲートドライバが Low 状態に保持されます。                                                                                                   |

| 28 | SS/DEM1  | I                  | ISET1 ソフトスタートピン。また、SS/DEM1 ピンは DEM と FPWM のどちらかに CH-1 を設定します。外部コンデンサにより、ソフトスタート中の SS/DEM1 ピン電圧のランプレートが設定されます。ソフトスタート中は、SS/DEM1 が ISET1 電圧を無効にします。外部電圧ループを使用する場合は、100pF のソフトスタートコンデンサを使用します。SS/DEM1 と AGND の間に 60.4k $\Omega$ 抵抗があるため、CH-1 を DEM に設定します。CH-1 は抵抗なしで FPWM で動作します。 |

| 29 | COMP1    | O                  | CH-1 トランスコンダクタンス (gm) エラー アンプの出力と CH-1 PWM コンパレータの反転入力。ループ補償回路をこのピンに接続します。                                                                                                                                                                                                      |

| 30 | ISET1    | I                  | CH-1 電流プログラミングピン。ISET1 には 1V のオフセットがあります。つまり CH-1 インダクタ電流は (ISET1-1V) に比例します。DEM では、ISET1 が 1V 未満のとき、インダクタ電流は 0 になります。FPWM では、ISET1 が 1V を下回ると、インダクタ電流が反転します。                                                                                                                   |

| 31 | CSB1     | I                  | CH-1 差動電流センス入力。CH-1 電流センス抵抗は、これら 2 本のピンの間に配置されます。CSA1 ピンはパワーアンダクタに、CSB1 ピンは LV ポートに接続します。                                                                                                                                                                                       |

| 32 | CSA1     | I                  | CH-1 電流監視ピン。このピンから電流源が流れ出します。電流源は、CFG の選択に基づいて CH-1 インダクタ電流または CH-1 昇圧モードの出力電流に比例します。IMON1 から AGND への間に終端抵抗とフィルタコンデンサを配置すると、CH-1 DC 電流レベルを表す DC 電圧が生成されます。IMON1 ピンの内部 50 $\mu$ A オフセット DC 電流源により、アクティブ信号がグランドノイズよりも高く上昇し、監視のノイズ耐性が向上します。                                        |

| 34 | ERRHV    | O                  | 昇圧モードのエラー アンプ出力。このエラー アンプは、DIR1 が Low のときにアクティブになります。                                                                                                                                                                                                                           |

表 4-1. ピンの機能 (続き)

| 番号 | ピン<br>名称 | I/O <sup>(1)</sup> | 説明                                                                                                                                                                                                                       |

|----|----------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 35 | FBHV     | I                  | 昇圧モードのエラー アンプの反転入力。このエラー アンプは、DIR1 が Low のときにアクティブになります。                                                                                                                                                                 |

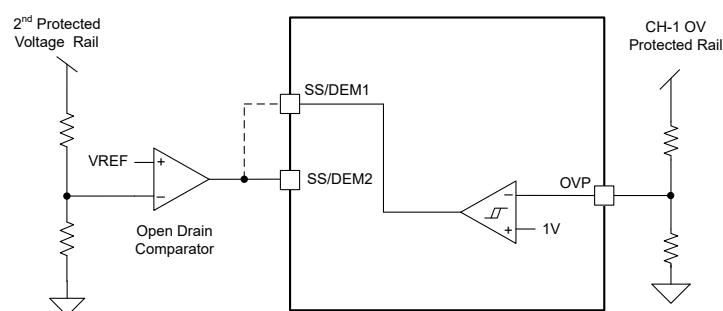

| 36 | OVP      | I                  | 内部過電圧コンバレータの反転入力。OVP ピンの電圧が 1V を上回ると、SS/DEM1 および VSET コンデンサが放電され、OVP ピンが 0.9V に低下するまで Low に保持されます。                                                                                                                       |

| 37 | SDA      | I <sup>2</sup> C   | I <sup>2</sup> C インターフェイスのデータ。SDA を使用しない場合は、10kΩ 抵抗を介して VDD にプルします。                                                                                                                                                      |

| 38 | SCL      | I                  | I <sup>2</sup> C インターフェイスのクロック。SCL を使用しない場合は、10kΩ 抵抗を介して VDD にプルします。                                                                                                                                                     |

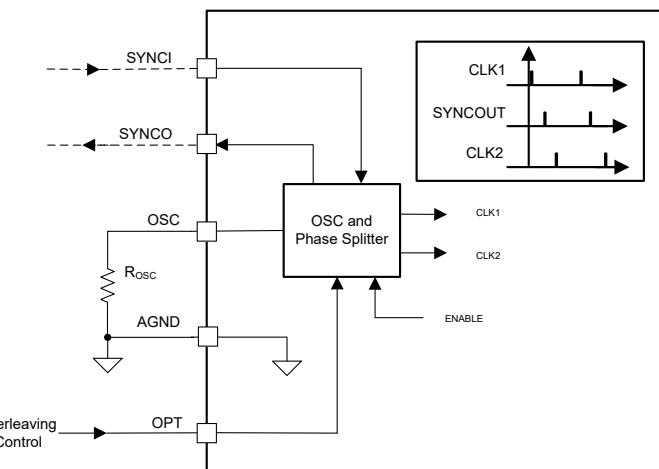

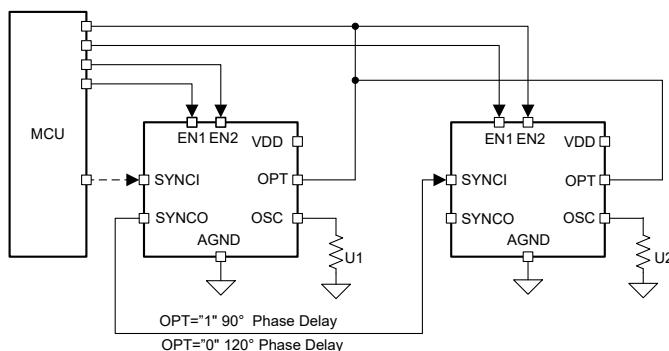

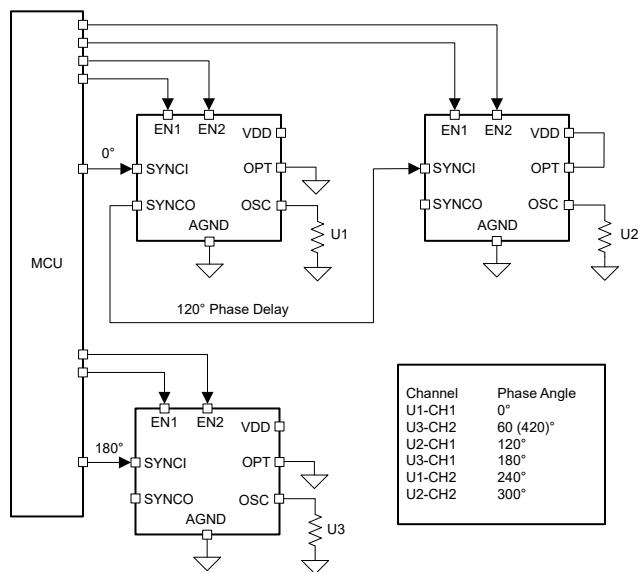

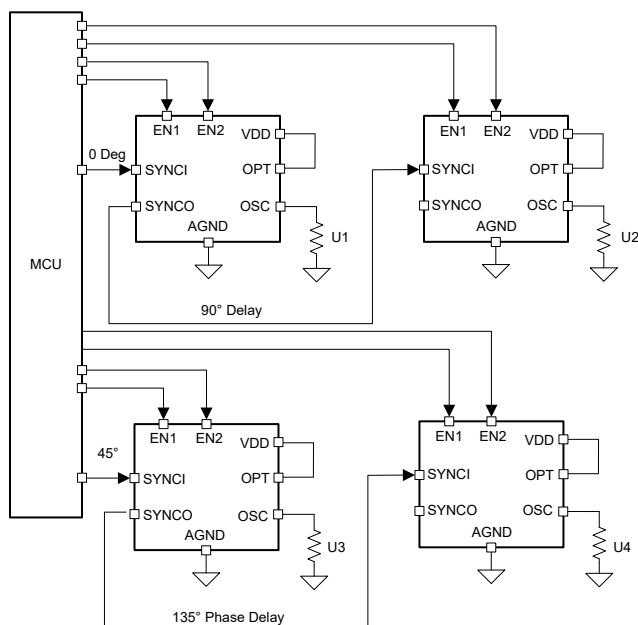

| 39 | SYNCO    | O                  | クロック同期出力ピン。3 相または 4 相構成の場合は、SYNCO をダウンストリーム デバイスの SYNCI に接続します。このピンを使用しない場合は、オープンのままにしてください。                                                                                                                             |

| 40 | SYNCI    | I                  | フリーランニング 内部発振器をオーバーライドする外部クロックの入力。未使用時は SYNCI ピンをグランドに接続します。使用しないときは、SYNCI ピンをグランドに接続するか、オープンのままにします。                                                                                                                    |

| 41 | OPT      | I                  | マルチフェーズ構成ピン。4 相動作の場合は、OPT ピンを VDD に接続します。3 相動作の場合は、OPT ピンを AGND に接続します。                                                                                                                                                  |

| 42 | OSC      | I                  | 内部発振器の周波数は、OSC と AGND 間の抵抗によってプログラムされます。                                                                                                                                                                                 |

| 43 | AGND     | G                  | アナログ グランドリファレンス。AGND をシングル ポイント接続で外部から PGND に接続し、ノイズ耐性を向上させます。                                                                                                                                                           |

| 44 | CFG      | I                  | I <sup>2</sup> C アドレスと IMON 機能選択ピン。                                                                                                                                                                                      |

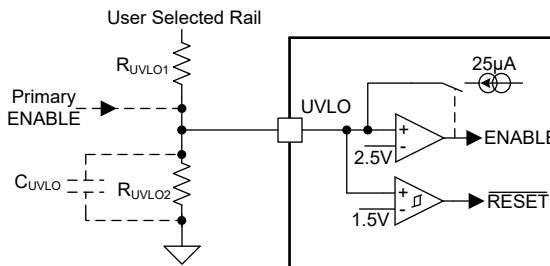

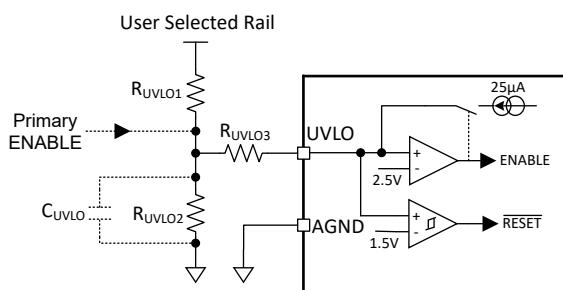

| 45 | UVLO     | I                  | UVLO ピンは、1 次側イネーブルピンとして機能します。UVLO が 1.25V を下回ると、デバイスは低静止電流シャットダウン モードになります。UVLO が 1.25V を超えて 2.5V 未満になると、デバイスは初期化モードになります。LDODRV がオンになって、外部 MOSFET を制御して VCC を生成します。VDD と VREF も確立されます。UVLO が 2.5V を超えると、デバイスの動作準備が整います。 |

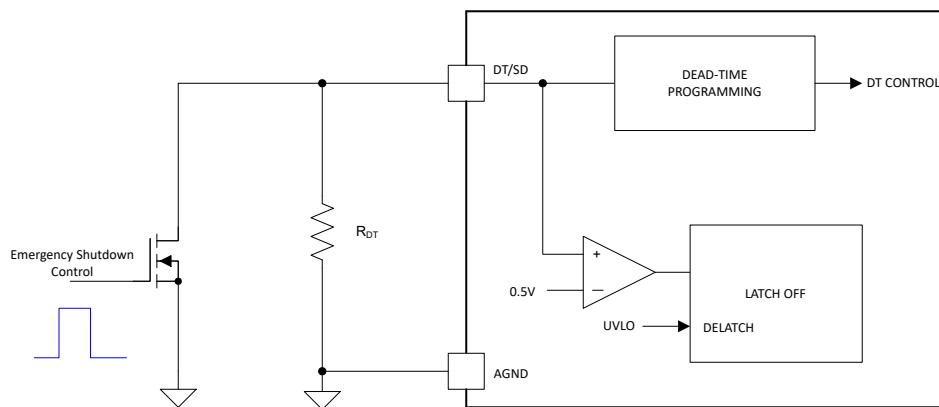

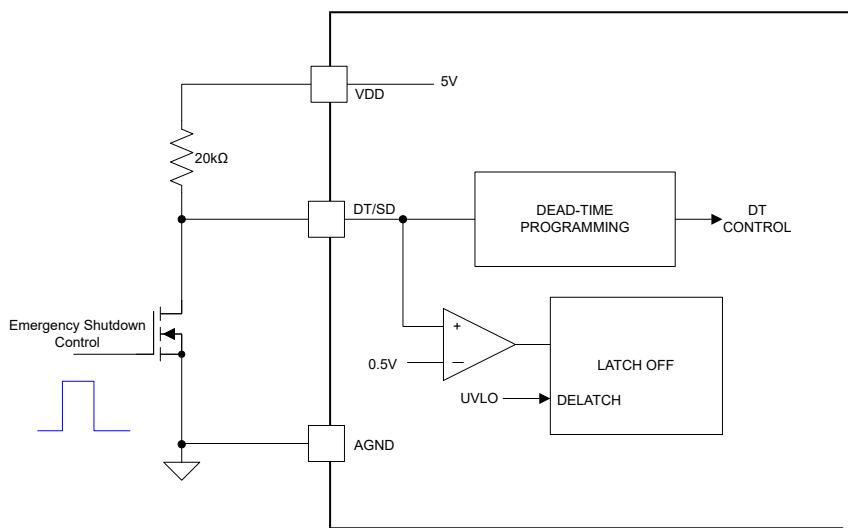

| 46 | DT/SD    | I                  | デッドタイム プログラミングと緊急ラッチ シャットダウン ピン。DT/SD と AGND の間に接続された抵抗は、ハイサイド ドライバ出力とローサイド ドライバ出力間のデッド タイムを設定します。DT ピンを VDD に接続すると、内部アダプティブ デッドタイム制御がアクティブになります。DT/SD ピンが Low になると、デバイスはラッチ シャットダウンに移行します。                              |

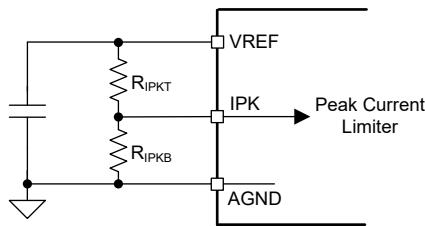

| 47 | IPK      | I                  | ピーク電流制限プログラミング ピン。IPK 電圧は、サイクル単位の電流制限コンバレータのスレッショルドを設定します。IPK 電圧を設定するには、VREF からの抵抗デバイダを使用します。                                                                                                                            |

| 48 | VSET     | I                  | 電圧エラー アンプ リファレンス入力ピン。デバイスがシャットダウンされるか、EN1 が Low になるか、または DIR1 が反転すると、VSET ピンが Low にプルされます。VREF からの抵抗デバイダを使用して、VSET ピンの電圧を設定します。電圧ループ ソフトスタートのために、コンデンサを VSET に接続します。                                                     |

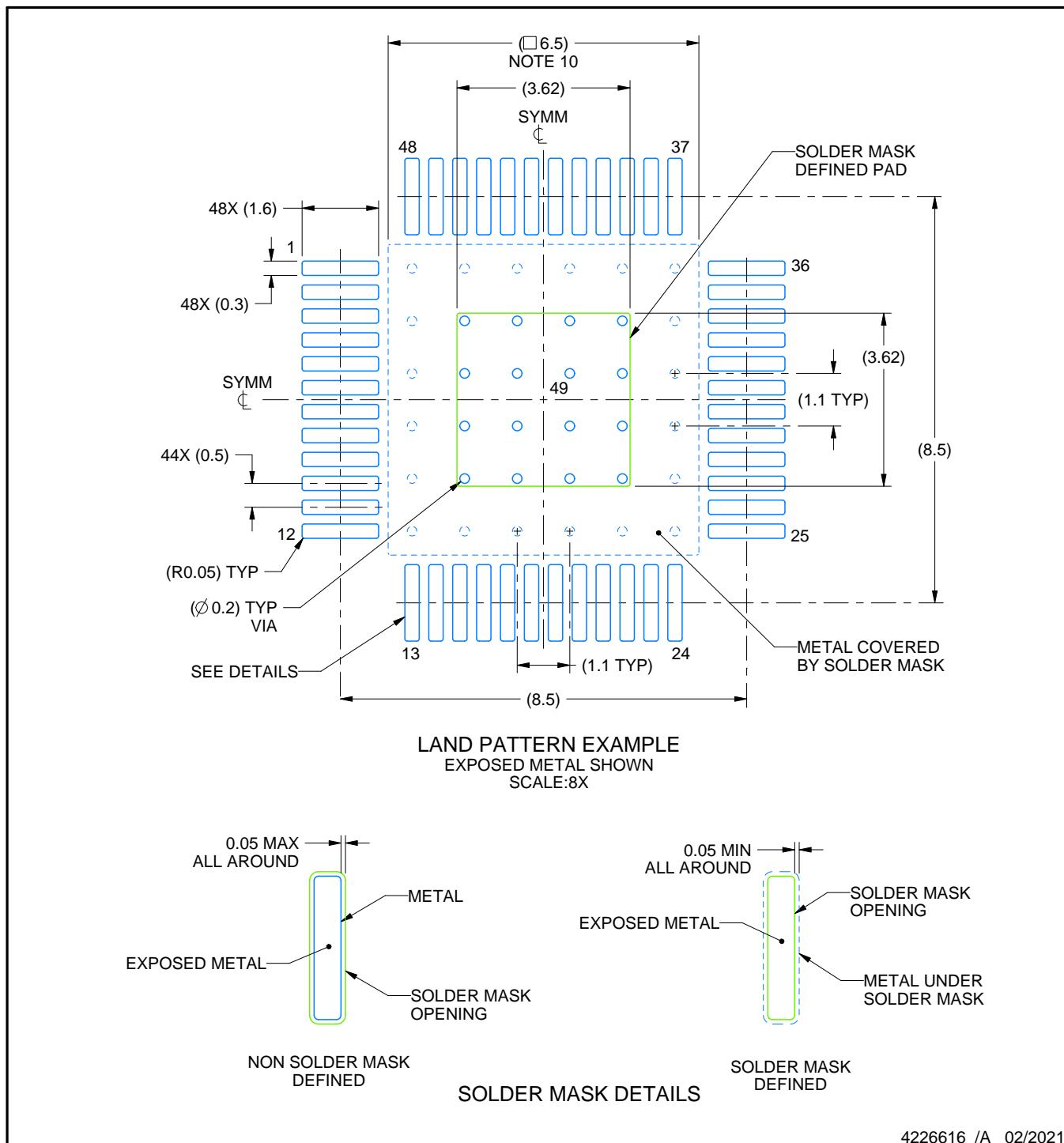

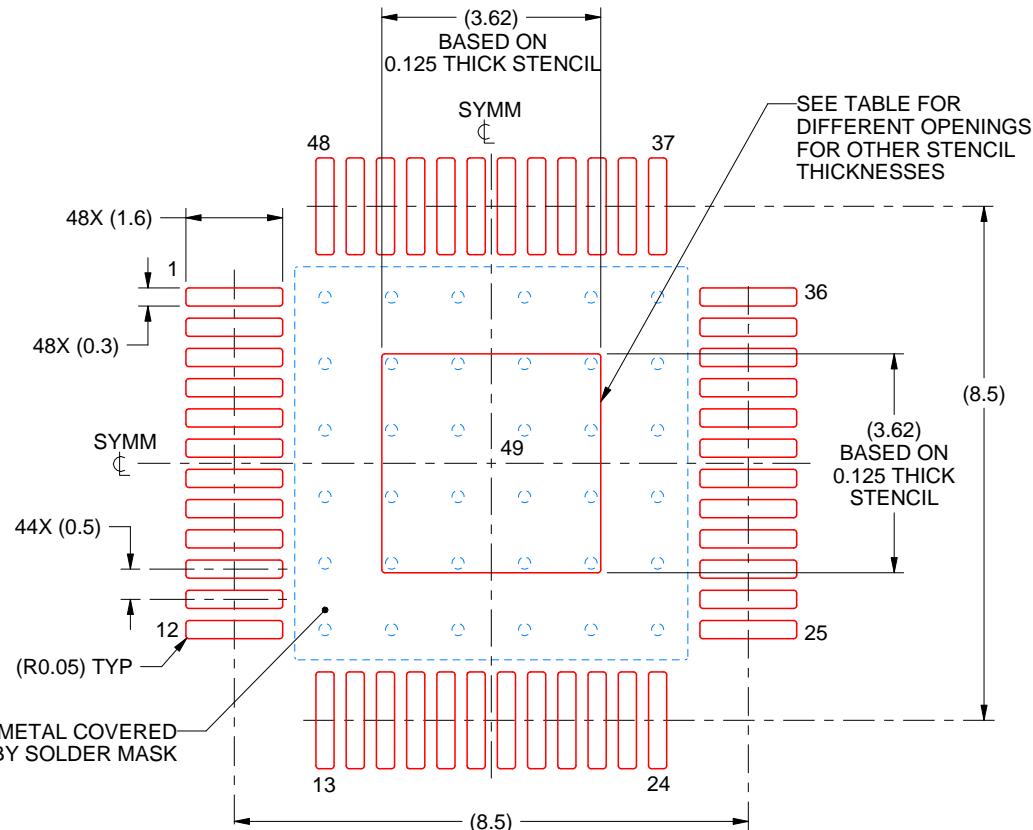

| —  | EP       | —                  | パッケージの露出パッド。熱抵抗を減らすため、大きなグランド ブレーンに半田付けします。                                                                                                                                                                              |

(1) 注: G=グランド、I=入力、O=出力、P=電源

## 5 仕様

### 5.1 絶対最大定格

接合部の動作時推奨温度範囲において<sup>(1)</sup>

|                             |                                                                                                       | 最小値  | 最大値     | 単位 |

|-----------------------------|-------------------------------------------------------------------------------------------------------|------|---------|----|

| 入力                          | HV1、HV2 から AGND へ                                                                                     | -0.3 | 85      | V  |

|                             | HV1、HV2 から AGND へ (過渡 50ns)                                                                           |      | 90      |    |

|                             | SW1、SW2 から PGND へ                                                                                     | -5   | 85      |    |

|                             | SW1、SW2 から PGND へ (過渡 20ns)                                                                           |      | 90      |    |

|                             | SW1、SW2 から PGND へ (過渡 50ns)                                                                           | -16  |         |    |

|                             | HB1 から SW1 へ、HB2 から SW2 へ                                                                             | -0.3 | 14      |    |

|                             | HO1 から SW1 へ、HO2 から SW2 へ                                                                             | -0.3 | HB+0.3  |    |

|                             | HO1 から SW1、HO2 から SW2 へ (過渡 20ns)                                                                     | -2   |         |    |

|                             | LO1、LO2 から PGND へ                                                                                     | -0.3 | VCC+0.3 |    |

|                             | LO1、LO2 から PGND へ (過渡 20ns)                                                                           | -2   |         |    |

|                             | CSA1、CSB1、CSA2、CSB2 から PGND へ                                                                         | -0.3 | 80      |    |

|                             | CSA1 から CSB1 へ、CSA2 から CSB2 へ                                                                         | -0.3 | 0.3     |    |

|                             | CFG、DIR1、DIR2、EN1、EN2、FBHV、FBLV、IPK、<br>ISET1、ISET2、OPT、OVP、SCL、SDA、SYNC1、<br>UVLO、VDD、VSET から AGND へ | -0.3 | 5.5     |    |

|                             | COMP1、COMP2、DT/SD、ERRHV、ERRLV、<br>IMON1、IMON2、OSC、SS/DEM1、SS/DEM2、<br>SYNCO、VREF から AGND へ            | -0.3 | VDD+0.3 |    |

|                             | LDODDRV から VCC へ                                                                                      | -0.3 | 5       |    |

|                             | VCC から PGND へ                                                                                         | -0.3 | 14      |    |

|                             | PGND から AGND へ                                                                                        | -0.3 | 0.3     |    |

| 接合部温度、 $T_J$ <sup>(2)</sup> |                                                                                                       | -40  | 150     | °C |

| 保管温度、 $T_{stg}$             |                                                                                                       | -55  | 150     |    |

- (1) 「絶対最大定格」外での操作は、デバイスに恒久的な損傷を引き起こす可能性があります。絶対最大定格は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用した場合、本デバイスは完全に機能するとは限らず、このことが本デバイスの信頼性、機能、性能に影響を及ぼし、本デバイスの寿命を縮める可能性があります。

- (2) 接合部温度が高くなると、動作寿命が短くなります。接合部温度が 125°Cを超えると、動作寿命が短くなります。

### 5.2 ESD 定格

|                    |      |                                                                     | 値              | 単位 |

|--------------------|------|---------------------------------------------------------------------|----------------|----|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠 <sup>(1)</sup><br>HBM ESD 分類 | ±2000          | V  |

|                    |      | 荷電デバイス モデル (CDM)、V ANSI/ESDA/JEDEC JS-002 に準拠 <sup>(2)</sup>        | すべてのピン<br>±500 |    |

|                    |      | コーナー ピン (1, 12, 13, 24, 25, 36, 37, 48)                             | ±750           |    |

- (1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。必要な予防措置を講じれば、HBM は 500V 未満の許容差で製造できます。±2000V と記載されたピンは、実際にはそれよりも高い性能を持つ場合があります。

- (2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。必要な予防措置をとれば、CDM の ESD 耐圧が 250V 未満でも製造可能です。±500V と記載されたピンは、実際にはそれよりも高い性能を持つ場合があります。

## 5.3 推奨動作条件

接合部の推奨動作温度である  $-40^{\circ}\text{C} \sim 150^{\circ}\text{C}$  の範囲内 (特に記述のない限り)<sup>(1)</sup>

|                         |                          | 最小値                   | 公称値                   | 最大値                   | 単位                 |

|-------------------------|--------------------------|-----------------------|-----------------------|-----------------------|--------------------|

| HV ポート<br>(HV1、<br>HV2) | 降圧モード                    | 3                     | 80                    | 80                    | V                  |

| HV ポート<br>(HV1、<br>HV2) | 昇圧モード                    | 3                     | 80                    | 80                    | V                  |

| LV ポート                  | 降圧モード                    | 0                     | 75                    | 75                    | V                  |

| LV ポート                  | 昇圧モード                    | 1                     | 75                    | 75                    | V                  |

| VCC                     | VCC ピンに適用可能な外部電圧         | 9.5                   | 12                    | 12                    | V                  |

| $T_J$                   | 動作時接合部温度 <sup>(2)</sup>  | -40                   | 150                   | 150                   | $^{\circ}\text{C}$ |

| $F_{\text{osc}}$        | 発振周波数                    | 50                    | 1000                  | 1000                  | kHz                |

| $F_{\text{EX\_CLK}}$    | 外部クロック周波数への同期 (最小 50kHz) | 0.8x $F_{\text{osc}}$ | 1.2x $F_{\text{osc}}$ | 1.2x $F_{\text{osc}}$ | kHz                |

| $F_{\text{EX\_CLK}}$    | SYNC1 パルス                | 50                    | 0.8/ $F_{\text{osc}}$ | 0.8/ $F_{\text{osc}}$ | ns                 |

| $t_{\text{DT}}$         | プログラマブル デッドタイム範囲         | 15                    | 200                   | 200                   | ns                 |

(1) 動作定格は、デバイスが機能する前提の条件です。仕様およびテスト条件については、「電気的特性」を参照してください。

(2) 接合部温度が高くなると、動作寿命が短くなります。接合部温度が  $125^{\circ}\text{C}$  を超えると、動作寿命が短くなります。

## 5.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup>        |                     | LM5171     | 単位                   |

|-----------------------------|---------------------|------------|----------------------|

|                             |                     | PHP (TQFP) |                      |

|                             |                     | 48 ピン      |                      |

| $R_{\theta JA}$             | 接合部から周囲への熱抵抗        | 30.7       | $^{\circ}\text{C/W}$ |

| $R_{\theta JC(\text{top})}$ | 接合部からケース (上面) への熱抵抗 | 18.8       | $^{\circ}\text{C/W}$ |

| $R_{\theta JB}$             | 接合部から基板への熱抵抗        | 13.5       | $^{\circ}\text{C/W}$ |

| $\Psi_{JT}$                 | 接合部から上面への特性パラメータ    | 0.3        | $^{\circ}\text{C/W}$ |

| $\Psi_{JB}$                 | 接合部から基板への特性パラメータ    | 13.4       | $^{\circ}\text{C/W}$ |

| $R_{\theta JC(\text{bot})}$ | 接合部からケース (底面) への熱抵抗 | 2.5        | $^{\circ}\text{C/W}$ |

(1) 従来および最新の熱評価基準の詳細については、『半導体およびIC パッケージの熱評価基準』アプリケーション レポートを参照してください。

## 5.5 電気的特性

標準値は  $T_J = 25^{\circ}\text{C}$  に対応します。最小および最大の制限値は、 $T_J = -40^{\circ}\text{C} \sim 150^{\circ}\text{C}$  の範囲で適用されます。特に記述のない限り、 $F_{\text{osc}} = 100\text{kHz}$ 、 $V_{\text{VCC}} = 10\text{V}$ 、 $V_{\text{HV1}} = V_{\text{HV2}} = V_{\text{HV-Port}} = 48\text{V}$  および  $V_{\text{LV-Port}} = 12\text{V}$  です。

| 記号                      | パラメータ                  | テスト条件                                                          | 最小値  | 標準値 | 最大値  | 単位            |

|-------------------------|------------------------|----------------------------------------------------------------|------|-----|------|---------------|

| <b>HV ポート (HV1、HV2)</b> |                        |                                                                |      |     |      |               |

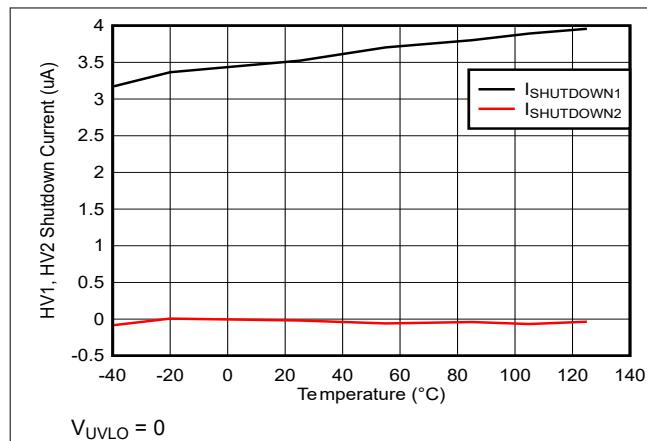

| $I_{\text{SHUTDOWN1}}$  | シャットダウン モードでの HV1 ピン電流 | $V_{\text{UVLO}} = 0\text{V}$                                  |      | 10  |      | $\mu\text{A}$ |

| $I_{\text{SHUTDOWN2}}$  | シャットダウン モードでの HV2 ピン電流 | $V_{\text{UVLO}} = 0\text{V}$                                  |      | 10  |      | $\mu\text{A}$ |

| $I_{\text{OPERATING}}$  | 動作時の HV1 および HV2 ピン電流  | $V_{\text{UVLO}} > 2.6\text{V}$ 、 $V_{\text{VCC}} > 9\text{V}$ |      | 1   |      | mA            |

| <b>VCC バイアス電源 (VCC)</b> |                        |                                                                |      |     |      |               |

| $V_{\text{VCC\_reg}}$   | VCC LDO レギュレーション設定ポイント | $V_{\text{HV1}} > 10\text{V}$                                  | 8.55 | 9   | 9.45 | V             |

| $V_{\text{CCUVLO}}$     | VCC 低電圧検出              | VCC 立ち下がり                                                      | 7.7  | 8   | 8.2  | V             |

| $V_{\text{CCHYS}}$      | VCC UVLO ヒステリシス        | VCC 立ち上がり                                                      | 8.2  | 8.5 | 8.7  | V             |

## 5.5 電気的特性 (続き)

標準値は  $T_J = 25^\circ\text{C}$  に対応します。最小および最大の制限値は、 $T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$  の範囲で適用されます。特に記述のない限り、 $\text{Fosc} = 100\text{kHz}$ 、 $\text{V}_{\text{VCC}} = 10\text{V}$ 、 $\text{V}_{\text{HV1}} = \text{V}_{\text{HV2}} = \text{V}_{\text{HV-Port}} = 48\text{V}$  および  $\text{V}_{\text{LV-Port}} = 12\text{V}$  です。

| 記号                                               | パラメータ                                                          | テスト条件                                                                                                                           | 最小値   | 標準値   | 最大値   | 単位                 |

|--------------------------------------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|--------------------|

| $I_{\text{VCC\_SD}}$                             | シャットダウン モードでの VCC シンク電流                                        | $\text{V}_{\text{UVLO}} = 0\text{V}$ 、 $\text{V}_{\text{VCC}} = 10\text{V}$                                                     |       | 25    |       | $\mu\text{A}$      |

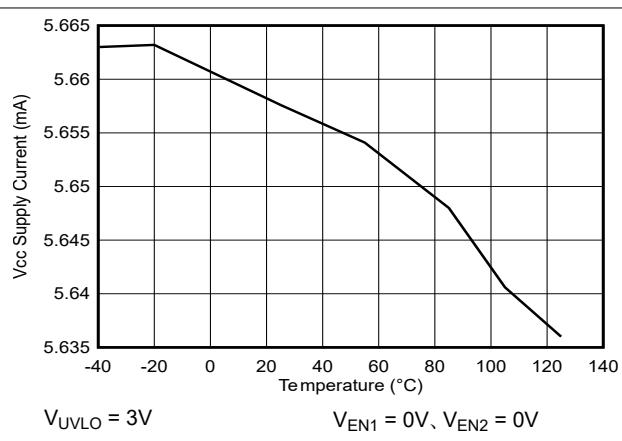

| $I_{\text{VCC\_SB}}$                             | スタンバイ時の VCC シンク電流:スイッチングなし                                     | $\text{V}_{\text{UVLO}} > 2.6\text{V}$ 、 $\text{V}_{\text{VCC}} > 9\text{V}$ 、 $\text{EN1} = \text{EN2} = 0\text{V}$            |       | 10    |       | $\text{mA}$        |

| <b>VDD アナログ バイアス電源 (VDD)</b>                     |                                                                |                                                                                                                                 |       |       |       |                    |

| $\text{V}_{\text{VDD}}$                          | VDD 電圧                                                         | $\text{V}_{\text{UVLO}} > 2.6\text{V}$ 、 $\text{V}_{\text{VCC}} > 9\text{V}$                                                    | 4.75  | 5     | 5.25  | $\text{V}$         |

| $\text{V}_{\text{DDUV}}$                         | VDD 低電圧検出                                                      | VDD 立ち下がり                                                                                                                       | 4.25  | 4.5   | 4.75  | $\text{V}$         |

| $\text{V}_{\text{DDHYS}}$                        | VDD UVLO ヒステリシス                                                | $\text{V}_{\text{DDUV}}$ を上回る VDD 立ち上がり                                                                                         | 0.1   | 0.2   | 0.3   | $\text{V}$         |

| $I_{\text{VDD}}$                                 | VDD のソース電流制限                                                   | $\text{V}_{\text{VDD}} = 4.6\text{V}$                                                                                           | 10    |       |       | $\text{mA}$        |

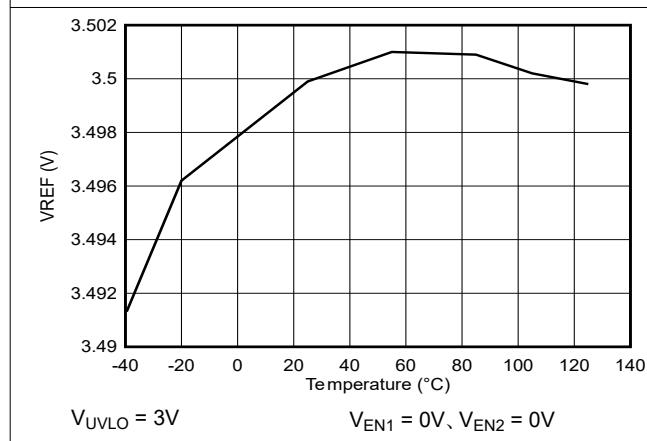

| <b>電圧リファレンス (VREF)</b>                           |                                                                |                                                                                                                                 |       |       |       |                    |

| $\text{V}_{\text{REF}}$                          | 電圧リファレンス                                                       | $\text{V}_{\text{UVLO}} > 2.6\text{V}$ 、 $\text{V}_{\text{VCC}} > 9\text{V}$ 、 $\text{V}_{\text{VDD}} > \text{V}_{\text{DDUV}}$ | 3.465 | 3.500 | 3.535 | $\text{V}$         |

| $I_{\text{VREF}}$                                | VREF のソース電流制限                                                  | $\text{V}_{\text{VREF}} = 3.5\text{V}$                                                                                          | 2     |       |       | $\text{mA}$        |

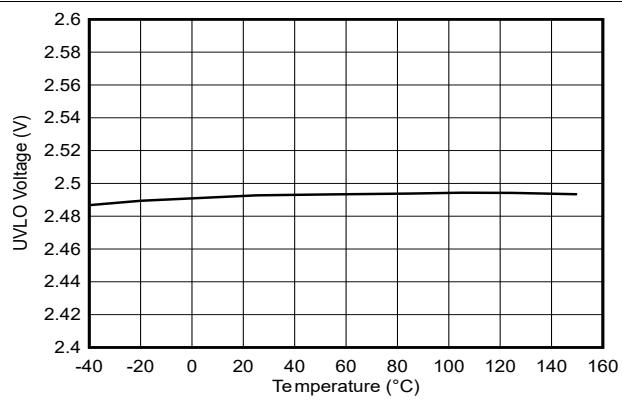

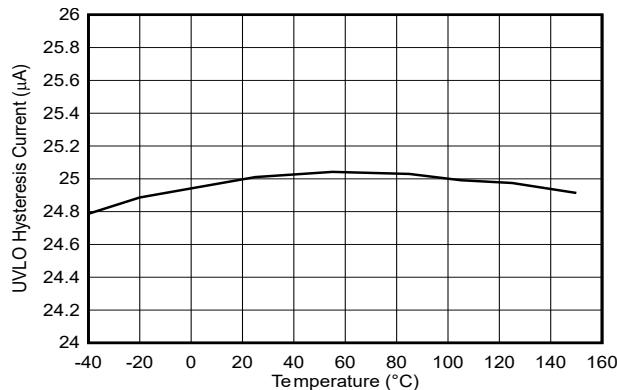

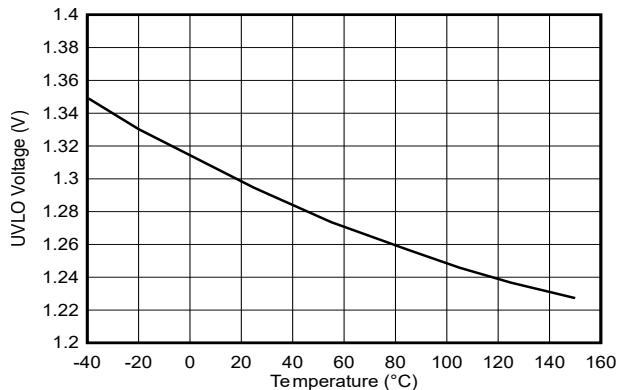

| <b>1 次側オン/オフ制御 (UVLO)</b>                        |                                                                |                                                                                                                                 |       |       |       |                    |

| $\text{V}_{\text{UVLO\_TH}}$                     | UVLO リリースレッショルド                                                | UVLO 電圧の立ち上がり                                                                                                                   | 2.4   | 2.5   | 2.6   | $\text{V}$         |

| $I_{\text{HYS}}$                                 | UVLO ヒステリシス電流                                                  | $\text{V}_{\text{UVLO}} > 2.6\text{V}$ のときの UVLO ソース電流                                                                          | 21    | 25    | 29    | $\mu\text{A}$      |

| $\text{V}_{\text{RES}}$                          | UVLO シャットダウンおよび IC リセット電圧のスレッショルド                              | UVLO 電圧の立ち下がり                                                                                                                   | 1     | 1.25  | 1.5   | $\text{V}$         |

|                                                  | UVLO シャットダウン リリース                                              | $\text{V}_{\text{RES}}$ を上回る UVLO 電圧の立ち上がり                                                                                      | 0.15  | 0.25  | 0.35  | $\text{V}$         |

| $t_{\text{UVLO}}$                                | UVLO 2.5V スレッショルド グリッヂ フィルタ                                    | UVLO 電圧の立ち上がりと立ち下がり                                                                                                             |       | 2.5   |       | $\mu\text{s}$      |

| $t_{\text{VRES}}$                                | UVLO 1.25V $\text{V}_{\text{RES}}$ スレッショルド グリッヂ フィルタ           |                                                                                                                                 |       | 5     | 10    | $\mu\text{s}$      |

|                                                  | UVLO 内部プルダウン電流                                                 |                                                                                                                                 | 25    | 100   | 250   | $\text{nA}$        |

| <b>イネーブル入力 (EN1 および EN2)</b>                     |                                                                |                                                                                                                                 |       |       |       |                    |

| $\text{V}_{\text{IL}}$                           | イネーブル入力 Low 状態                                                 | ドライバ出力ディスエーブル                                                                                                                   |       | 1.0   |       | $\text{V}$         |

| $\text{V}_{\text{IH}}$                           | イネーブル入力 High 状態                                                | ドライバ出力イネーブル                                                                                                                     | 2.0   |       |       | $\text{V}$         |

|                                                  | 内部プルダウン インピーダンス                                                | EN1、EN2 ロジック入力内部プルダウン抵抗                                                                                                         | 0.7   | 1     | 1.3   | $\text{Meg}\Omega$ |

|                                                  | EN グリッヂ フィルタ時間 (立ち上がりおよび立ち下がりエッジ)                              |                                                                                                                                 |       | 2.5   |       | $\mu\text{s}$      |

| <b>方向コマンド (DIR1, DIR2)</b>                       |                                                                |                                                                                                                                 |       |       |       |                    |

| $\text{V}_{\text{DIR1}}, \text{V}_{\text{DIR2}}$ | CH-1 と CH-2 それぞれの LV ポートから HV ポートに流れる電流のコマンド (昇圧モード 12V ~ 48V) | 外部回路によってアクティブに Low にプルされる                                                                                                       |       | 1     |       | $\text{V}$         |

| $\text{V}_{\text{DIR1}}, \text{V}_{\text{DIR2}}$ | CH-1 と CH-2 それぞれの HV ポートから LV ポートに流れる電流のコマンド (降圧モード 48V ~ 12V) | 外部回路によってアクティブに High にプルされる                                                                                                      | 2     |       |       | $\text{V}$         |

| $\text{V}_{\text{DIR1}}, \text{V}_{\text{DIR2}}$ | スタンバイ (無効な DIR コマンド)                                           | DIR ピン (DIR1 または DIR2)、アクティブ High でもアクティブ Low でもない                                                                              |       | 1.5   |       | $\text{V}$         |

|                                                  | DIR グリッヂ フィルタ (立ち上がりおよび立ち下がりエッジ)                               | 立ち上がりエッジと立下りエッジの両方                                                                                                              |       | 10    |       | $\mu\text{s}$      |

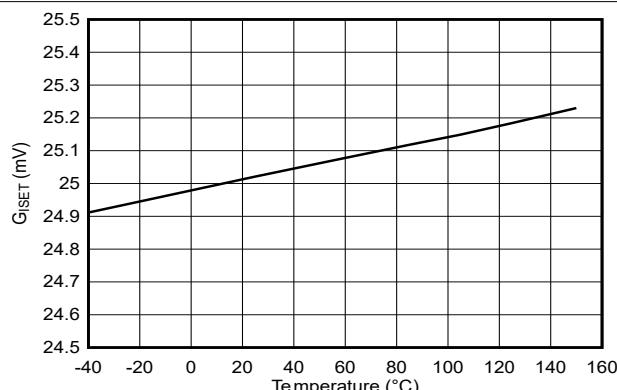

| <b>ISET INPUTS (ISET1, ISET2)</b>                |                                                                |                                                                                                                                 |       |       |       |                    |

|                                                  | ISET DC オフセット電圧                                                |                                                                                                                                 | 0.87  | 1.0   | 1.13  | $\text{V}$         |

## 5.5 電気的特性 (続き)

標準値は  $T_J = 25^\circ\text{C}$  に対応します。最小および最大の制限値は、 $T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$  の範囲で適用されます。特に記述のない限り、 $F_{\text{OSC}} = 100\text{kHz}$ 、 $V_{\text{VCC}} = 10\text{V}$ 、 $V_{\text{HV1}} = V_{\text{HV2}} = V_{\text{HV-Port}} = 48\text{V}$  および  $V_{\text{LV-Port}} = 12\text{V}$  です。

| 記号                | パラメータ                                    | テスト条件                                             | 最小値  | 標準値 | 最大値  | 単位            |

|-------------------|------------------------------------------|---------------------------------------------------|------|-----|------|---------------|

| $G_{\text{ISET}}$ | レギュレートされたインダクタの DC 電流センス電圧の ISET 電圧へのゲイン | $ V_{\text{CSA}} - V_{\text{CSB}}  = 50\text{mV}$ | 24.3 | 25  | 25.7 | $\text{mV/V}$ |

|                   | ISET 内部プルダウン電流シンク                        |                                                   |      | 75  | 200  | $\text{nA}$   |

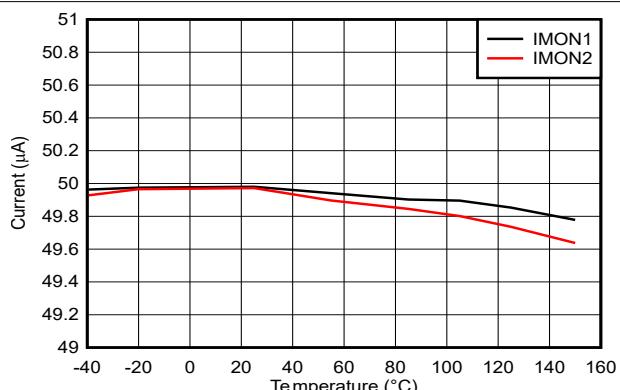

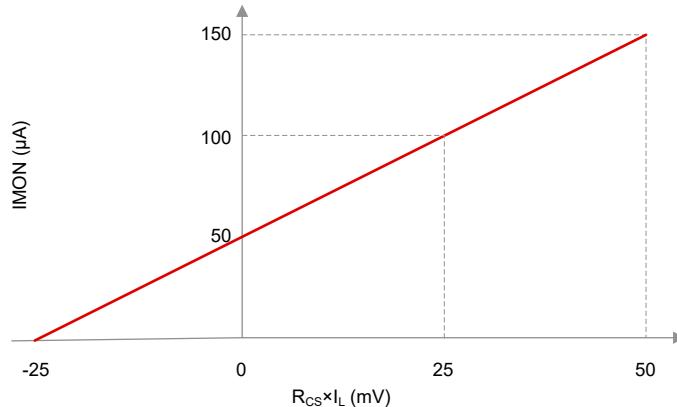

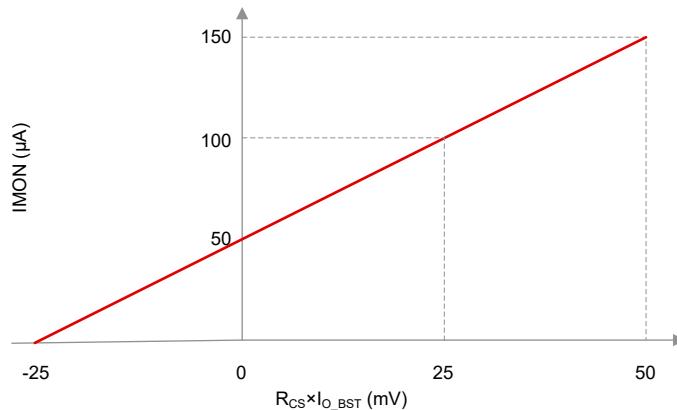

### 出力電流の監視 (IMON1, IMON2)

|  |                                         |                                                                                                                              |       |     |       |                  |

|--|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|------------------|

|  | IMON1 および IMON2 電流源のゲインとチャネル電流センス電圧との関係 | $ V_{\text{CSA}} - V_{\text{CSB}}  = 50\text{mV}$ 、CONFIG = "IMON_IL 監視"、 $V_{\text{DIR}} > 2\text{V}$                       | 1.96  | 2   | 2.04  | $\mu\text{A/mV}$ |

|  | IMON1 および IMON2 電流源のゲインとチャネル電流センス電圧との関係 | $ V_{\text{CSA}} - V_{\text{CSB}}  = 50\text{mV}$ 、CONFIG = "IMON_BSTOUT 監視"、 $V_{\text{DIR}} < 1\text{V}$ 、デューティサイクル = 0.75 | 1.96  | 2   | 2.04  | $\mu\text{A/mV}$ |

|  | IMON1 および IMON2 電流源のゲインとチャネル電流センス電圧との関係 | $ V_{\text{CSA}} - V_{\text{CSB}}  = 10\text{mV}$ 、CONFIG = "IMON_IL 監視"、 $V_{\text{DIR}} > 2\text{V}$                       | 0.475 | 0.5 | 0.525 | $\mu\text{A/mV}$ |

|  | IMON1 および IMON2 電流源のゲインとチャネル電流センス電圧との関係 | $ V_{\text{CSA}} - V_{\text{CSB}}  = 10\text{mV}$ 、CONFIG = "IMON_BSTOUT 監視"、 $V_{\text{DIR}} < 1\text{V}$ 、デューティサイクル = 0.75 | 0.475 | 0.5 | 0.525 | $\mu\text{A/mV}$ |

|  | IMON1 および IMON2 DC オフセット電流              | $ V_{\text{CSA}} - V_{\text{CSB}}  = 0\text{mV}$                                                                             | 42    | 50  | 56    | $\mu\text{A}$    |

### 電流センスアンプ (両方のチャネル)

|                      |                          |                                                                                  |      |    |      |              |

|----------------------|--------------------------|----------------------------------------------------------------------------------|------|----|------|--------------|

| $G_{\text{CS_BK1}}$  | 降圧モードでの電流センス電圧へのアンプ出力ゲイン | $ V_{\text{CSA}} - V_{\text{CSB}}  = 50\text{mV}$ 、 $V_{\text{DIR}} > 2\text{V}$ | 39   | 40 | 41   | $\text{V/V}$ |

| $G_{\text{CS_BST1}}$ | 昇圧モードでの電流センス電圧へのアンプ出力ゲイン | $ V_{\text{CSA}} - V_{\text{CSB}}  = 50\text{mV}$ 、 $V_{\text{DIR}} < 1\text{V}$ | 39   | 40 | 41   | $\text{V/V}$ |

| $G_{\text{CS_BK2}}$  | 降圧モードでの電流センス電圧へのアンプ出力ゲイン | $ V_{\text{CSA}} - V_{\text{CSB}}  = 10\text{mV}$ 、 $V_{\text{DIR}} < 1\text{V}$ | 38.4 | 40 | 41.7 | $\text{V/V}$ |

| $G_{\text{CS_BST2}}$ | 昇圧モードでの電流センス電圧へのアンプ出力ゲイン | $ V_{\text{CSA}} - V_{\text{CSB}}  = 10\text{mV}$ 、 $V_{\text{DIR}} > 2\text{V}$ | 38.4 | 40 | 41.7 | $\text{V/V}$ |

### 相互コンダクタンスアンプ (COMP1, COMP2)

|        |           |                                                                                                                                                      |      |      |      |                 |

|--------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-----------------|

| $G_m$  | 相互コンダクタンス |                                                                                                                                                      | 75   | 100  | 125  | $\mu\text{A/V}$ |

| I COMP | 出力ソース電流制限 | $V_{\text{ISET}} = 4\text{V}$ 、 $ V_{\text{CSA}} - V_{\text{CSB}}  = 0\text{mV}$                                                                     | 190  | 250  | 280  | $\mu\text{A}$   |

|        | 出力シンク電流制限 | $V_{\text{ISET}} = 0\text{V}$ 、 $V_{\text{CSA}} - V_{\text{CSB}} = 50\text{mV}$ (降圧モード) または $V_{\text{CSA}} - V_{\text{CSB}} = -50\text{mV}$ (昇圧モード) | -280 | -250 | -190 | $\mu\text{A}$   |

### 電圧ループエラーアンプ (VSET, LVFB, LVERR, HVFB, HVERR)

|                       |            |                                                                   |     |     |              |

|-----------------------|------------|-------------------------------------------------------------------|-----|-----|--------------|

| $A_{\text{OL}}$       | 開ループゲイン    | $V_{\text{VCC}} > 9\text{V}$ 、 $V_{\text{VDD}} > V_{\text{DDUV}}$ | 80  |     | $\text{dB}$  |

| $F_{\text{BW}}$       | ユニティゲイン帯域幅 |                                                                   | 2.1 |     | $\text{MHz}$ |

| $V_{\text{OS}}$       | 入力オフセット電圧  |                                                                   | 0   | 5   | $\text{mV}$  |

| $V_{\text{ERR\_MIN}}$ | 最小アンプ出力電圧  | ソース 2mA                                                           | 4   |     | $\text{V}$   |

| $V_{\text{ERR\_MAX}}$ | 最大アンプ出力電圧  | 2mA (シンク)                                                         |     | 0.5 | $\text{V}$   |

### PWM コンパレータ

|                       |                           |  |     |     |             |

|-----------------------|---------------------------|--|-----|-----|-------------|

|                       | COMP から出力までの遅延            |  | 50  |     | $\text{ns}$ |

|                       | COMP から PWM へのコンパレータオフセット |  | 1   |     | $\text{V}$  |

| $T_{\text{OFF\_MIN}}$ | 最小オフ時間                    |  | 100 | 150 | $\text{ns}$ |

## 5.5 電気的特性 (続き)

標準値は  $T_J = 25^\circ\text{C}$  に対応します。最小および最大の制限値は、 $T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$  の範囲で適用されます。特に記述のない限り、 $F_{\text{OSC}} = 100\text{kHz}$ 、 $V_{\text{VCC}} = 10\text{V}$ 、 $V_{\text{HV1}} = V_{\text{HV2}} = V_{\text{HV-Port}} = 48\text{V}$  および  $V_{\text{LV-Port}} = 12\text{V}$  です。

| 記号                              | パラメータ                                              | テスト条件                                                                                      | 最小値  | 標準値  | 最大値  | 単位               |

|---------------------------------|----------------------------------------------------|--------------------------------------------------------------------------------------------|------|------|------|------------------|

| <b>ピーク電流制限 (IPK)</b>            |                                                    |                                                                                            |      |      |      |                  |

| $G_{\text{IPK\_BK1}}$           | 電流センス電圧から IPK ピンに供給されるサイクル単位の制限スレッショルド電圧のゲイン、降圧モード | $V_{\text{IPK}} = 3\text{V}$ 、 $V_{\text{DIR}} > 2\text{V}$                                | 45   | 50   | 55   | $\text{mV/V}$    |

| $G_{\text{IPK\_BK2}}$           | 電流センス電圧から IPK ピンに供給されるサイクル単位の制限スレッショルド電圧のゲイン、降圧モード | $V_{\text{IPK}} = 1\text{V}$ 、 $V_{\text{DIR}} > 2\text{V}$                                | 45   | 50   | 55   | $\text{mV/V}$    |

| $G_{\text{IPK\_BST1}}$          | 電流センス電圧から IPK ピンに供給されるサイクル単位の制限スレッショルド電圧のゲイン、昇圧モード | $V_{\text{IPK}} = 3\text{V}$ 、 $V_{\text{DIR}} < 1\text{V}$                                | 45   | 50   | 55   | $\text{mV/V}$    |

| $G_{\text{IPK\_BST2}}$          | 電流センス電圧から IPK ピンに供給されるサイクル単位の制限スレッショルド電圧のゲイン、昇圧モード | $V_{\text{IPK}} = 1\text{V}$ 、 $V_{\text{DIR}} < 1\text{V}$                                | 45   | 50   | 55   | $\text{mV/V}$    |

| <b>過電圧保護 (OVP)</b>              |                                                    |                                                                                            |      |      |      |                  |

|                                 | OVP スレッショルド                                        |                                                                                            | 0.99 | 1    | 1.01 | $\text{V}$       |

| $\text{OVP}_{\text{HYS}}$       | OVP ヒステリシス                                         |                                                                                            |      | 100  |      | $\text{mV}$      |

| $t_{\text{OVP}}$                | OVP グリッチ フィルタ                                      |                                                                                            |      | 5    |      | $\text{us}$      |

| <b>発振器 (OSC)</b>                |                                                    |                                                                                            |      |      |      |                  |

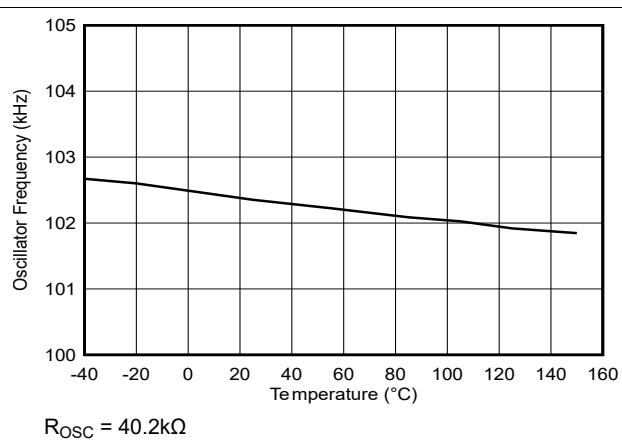

| $F_{\text{OSC}}$                | 発振器周波数 1                                           | $R_{\text{OSC}} = 41.5\text{k}\Omega$ 、 $\text{SYNCI}$ ピンに外部クロック信号なし                       | 90   | 100  | 110  | $\text{kHz}$     |

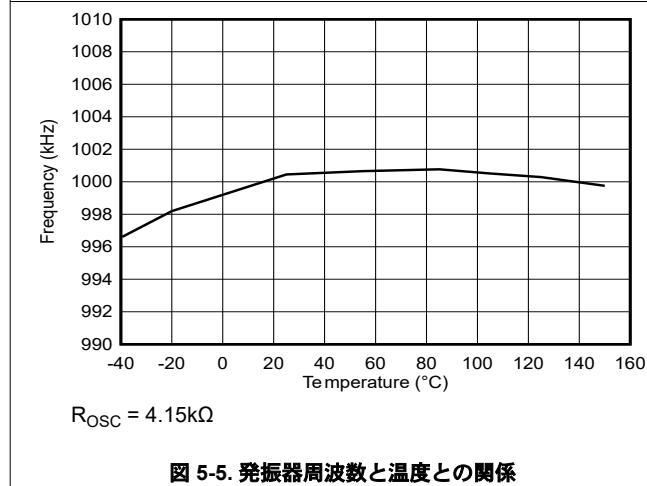

|                                 | 発振器周波数 2                                           | $R_{\text{OSC}} = 4.15\text{k}\Omega$ 、 $\text{SYNCI}$ ピンに外部クロック信号なし                       | 900  | 1000 | 1100 | $\text{kHz}$     |

| $V_{\text{OSC}}$                | OSC ピン DC 電圧                                       | OSC DC レベル                                                                                 |      | 1    |      | $\text{V}$       |

| <b>同期クロック入力 (SYNCI)</b>         |                                                    |                                                                                            |      |      |      |                  |

| $V_{\text{SYNIH}}$              | High 状態の SYNCI 入力スレッショルド                           |                                                                                            | 2    |      |      | $\text{V}$       |

| $V_{\text{SYNIL}}$              | Low 状態の SYNCI 入力スレッショルド                            |                                                                                            |      | 1    |      | $\text{V}$       |

|                                 | 同期を確立するための遅延                                       | $0.8 \times F_{\text{OSC}} < F_{\text{SYNCI}} < 1.2 \times F_{\text{OSC}}$                 | 200  | 300  |      | $\text{us}$      |

|                                 | 内部プルダウン インピーダンス                                    | $V_{\text{SYNCI}} = 2.5\text{V}$                                                           | 700  | 1000 | 1300 | $\text{k}\Omega$ |

| <b>同期クロック出力 (SYNCO)</b>         |                                                    |                                                                                            |      |      |      |                  |

| $V_{\text{SYNOH}}$              | SYNCO High 状態                                      |                                                                                            | 2.5  |      |      | $\text{V}$       |

| $V_{\text{SYNOL}}$              | SYNCO Low 状態                                       |                                                                                            |      | 0.4  |      | $\text{V}$       |

|                                 | SYNCO が High 状態のときのソース電流                           | $V_{\text{SYNCO}} = 2.5\text{V}$                                                           |      | 1    |      | $\text{mA}$      |

|                                 | SYNCO が Low 状態のときのシンク電流                            | $V_{\text{SYNCO}} = 0.5\text{V}$                                                           |      | 1    |      | $\text{mA}$      |

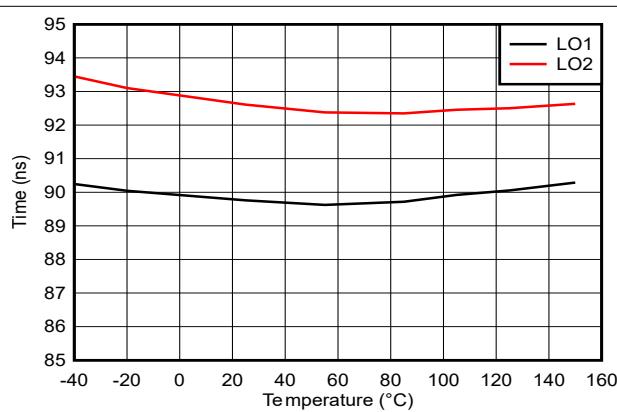

|                                 | SYNCO パルス幅                                         |                                                                                            | 60   | 90   | 120  | $\text{ns}$      |

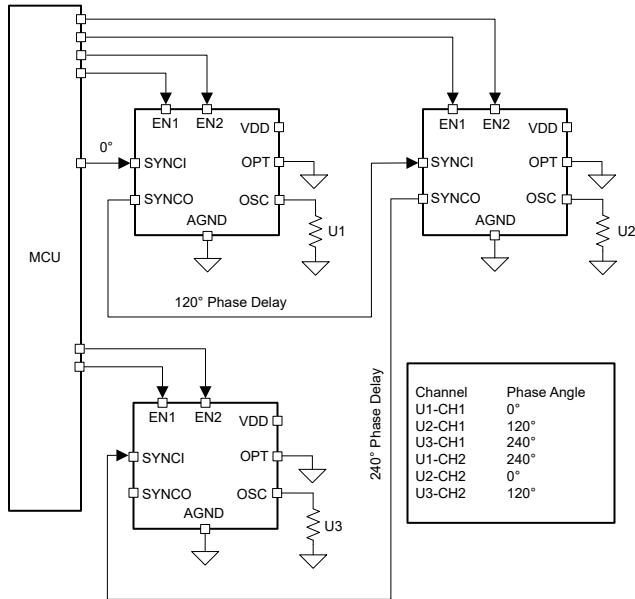

|                                 | マルチフェーズ デイジーチェーン接続の SYNCO パルス遅延                    | $V_{\text{OPT}} > 2\text{V}$ 、 $R_{\text{SYNCO}} > 61.9\text{k}\Omega$                     | 90   |      |      | 度                |

|                                 |                                                    | $V_{\text{OPT}} < 1\text{V}$ 、 $R_{\text{SYNCO}} > 61.9\text{k}\Omega$                     |      | 120  |      | 度                |

| <b>ブートストラップ (HB1, HB2)</b>      |                                                    |                                                                                            |      |      |      |                  |

| $V_{\text{HB-UV}}$              | ブートストラップ低電圧スレッショルド                                 | $(V_{\text{HB}} - V_{\text{SW}})$ 電圧立ち上がり                                                  | 6    | 6.5  | 7    | $\text{V}$       |

| $V_{\text{HB-UV-HYS}}$          | ブートストラップ低電圧ヒステリシス                                  |                                                                                            |      | 0.5  |      | $\text{V}$       |

| $I_{\text{HB-LK}}$              | ブートストラップ静止電流                                       | $V_{\text{HB}} - V_{\text{SW}} = 10\text{V}$ 、 $V_{\text{HO}} - V_{\text{SW}} = 0\text{V}$ |      | 100  |      | $\mu\text{A}$    |

| <b>ハイサイド ゲートドライバ (HO1, HO2)</b> |                                                    |                                                                                            |      |      |      |                  |

| $V_{\text{OLH}}$                | HO Low 状態出力電圧                                      | $I_{\text{HO}} = 100\text{mA}$                                                             |      | 0.1  |      | $\text{V}$       |

| $V_{\text{OHH}}$                | HO High 状態出力電圧                                     | $I_{\text{HO}} = -100\text{mA}$ 、 $V_{\text{OHH}} = V_{\text{HB}} - V_{\text{HO}}$         |      | 0.15 |      | $\text{V}$       |

## 5.5 電気的特性 (続き)

標準値は  $T_J = 25^\circ\text{C}$  に対応します。最小および最大の制限値は、 $T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$  の範囲で適用されます。特に記述のない限り、 $\text{Fosc} = 100\text{kHz}$ 、 $\text{V}_{\text{VCC}} = 10\text{V}$ 、 $\text{V}_{\text{HV1}} = \text{V}_{\text{HV2}} = \text{V}_{\text{HV-Port}} = 48\text{V}$  および  $\text{V}_{\text{LV-Port}} = 12\text{V}$  です。

| 記号                                                              | パラメータ                                                                                                                                   | テスト条件                                                                                                                                                | 最小値   | 標準値 | 最大値   | 単位   |

|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|------|

|                                                                 | HO 立ち上がり時間 (パルス振幅 10% ~ 90%)                                                                                                            | $C_{\text{LD}} = 1000\text{pF}$                                                                                                                      | 5     |     |       | ns   |

|                                                                 | HO 立ち下がり時間 (パルス振幅 10% ~ 90%)                                                                                                            | $C_{\text{LD}} = 1000\text{pF}$                                                                                                                      | 4     |     |       | ns   |

| $I_{\text{OHH}}$                                                | HO ピーク ソース電流                                                                                                                            | $\text{V}_{\text{HB}} - \text{V}_{\text{SW}} = 10\text{V}$                                                                                           | 4     |     |       | A    |

| $I_{\text{OLH}}$                                                | HO ピーク シンク電流                                                                                                                            | $\text{V}_{\text{HB}} - \text{V}_{\text{SW}} = 10\text{V}$                                                                                           | 5     |     |       | A    |

| <b>ローサイド ゲートドライバ (LO1, LO2)</b>                                 |                                                                                                                                         |                                                                                                                                                      |       |     |       |      |

| $V_{\text{OLL}}$                                                | LO Low 状態出力電圧                                                                                                                           | $I_{\text{LO}} = 100\text{mA}$                                                                                                                       | 0.1   |     |       | V    |

| $V_{\text{OHL}}$                                                | LO High 状態出力電圧                                                                                                                          | $I_{\text{LO}} = -100\text{mA}, V_{\text{OHL}} = \text{V}_{\text{VCC}} - \text{V}_{\text{LO}}$                                                       | 0.15  |     |       | V    |

|                                                                 | LO 立ち上がり時間 (パルス振幅 10% ~ 90%)                                                                                                            | $C_{\text{LD}} = 1000\text{pF}$                                                                                                                      | 5     |     |       | ns   |

|                                                                 | LO の立ち下がり時間 (パルス振幅 90% ~ 10%)                                                                                                           | $C_{\text{LD}} = 1000\text{pF}$                                                                                                                      | 4     |     |       | ns   |

| $I_{\text{OHL}}$                                                | LO ピーク ソース電流                                                                                                                            | $\text{V}_{\text{VCC}} = 10\text{V}$                                                                                                                 | 4     |     |       | A    |

| $I_{\text{OLL}}$                                                | LO ピーク シンク電流                                                                                                                            | $\text{V}_{\text{VCC}} = 10\text{V}$                                                                                                                 | 5     |     |       | A    |

| <b>CH-2 から CH-1 までのインターリープ位相遅延 (OPT)</b>                        |                                                                                                                                         |                                                                                                                                                      |       |     |       |      |

| $V_{\text{OPTL}}$                                               | OPT 入力 Low 状態                                                                                                                           | OPT="0"                                                                                                                                              |       | 1.0 |       | V    |

| $V_{\text{OPTH}}$                                               | OPT 入力 High 状態                                                                                                                          | OPT="1"                                                                                                                                              | 2.0   |     |       | V    |

|                                                                 | $\text{HO2}_{\text{rising}} - \text{HO1}_{\text{rising}}$ (降圧モード) または $\text{LO2}_{\text{rising}} - \text{LO1}_{\text{rising}}$ (昇圧モード) | デイジーチェーンインターリープ動作の 3 相の OPT = "0"                                                                                                                    | 240   |     |       | 度    |

|                                                                 | $\text{HO2}_{\text{rising}} - \text{HO1}_{\text{rising}}$ (降圧モード) または $\text{LO2}_{\text{rising}} - \text{LO1}_{\text{rising}}$ (昇圧モード) | デイジーチェーンインターリープ動作の 1, 2, 4 相の OPT = "1"                                                                                                              | 180   |     |       | 度    |

|                                                                 | 内蔵プルダウン インピーダンス                                                                                                                         |                                                                                                                                                      | 1     |     |       | MegΩ |

| <b>デッドタイムおよびラッチ シャットダウン (DT/SD)</b>                             |                                                                                                                                         |                                                                                                                                                      |       |     |       |      |

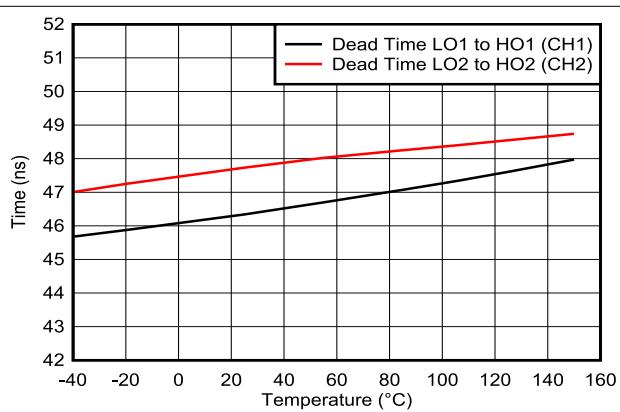

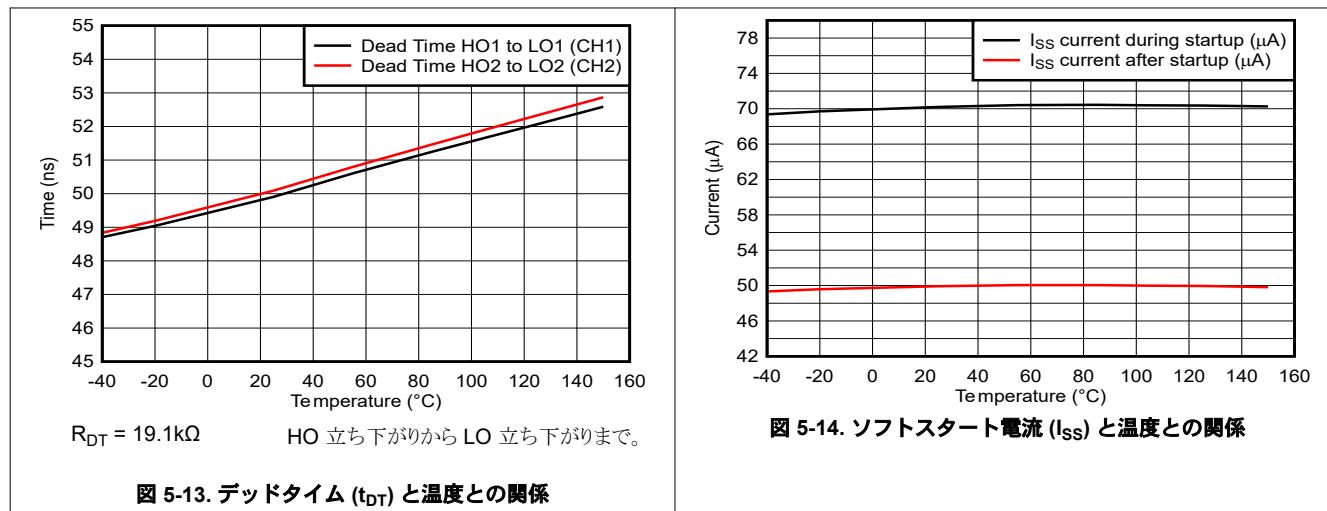

| $t_{\text{DT}}$                                                 | LO 立ち下がりエッジから HO 立ち上がりエッジまでの遅延                                                                                                          | $R_{\text{DT}} = 19.1\text{k}\Omega$                                                                                                                 | 35    | 50  | 60    | ns   |

|                                                                 | HO 立ち下がりエッジから LO 立ち上がりエッジまでの遅延                                                                                                          | $R_{\text{DT}} = 19.1\text{k}\Omega$                                                                                                                 | 35    | 50  | 65    | ns   |

| $V_{\text{DT}}$                                                 | デッドタイム プログラミングの DC 電圧レベル                                                                                                                |                                                                                                                                                      |       | 1.2 |       | V    |

|                                                                 | アダプティブ デッドタイム プログラミングの DC 電圧レベル                                                                                                         |                                                                                                                                                      | 3.1   |     |       | V    |

| $V_{\text{ADPT}}$                                               | アダプティブ デッドタイム方式のクロス出力を有効化するための HO-SW または LO-GND 電圧スレッショルド                                                                               | $\text{V}_{\text{VCC}} > 9\text{V}, (\text{V}_{\text{HB}} - \text{V}_{\text{SW}}) > 8\text{V}$ 、HO または LO 電圧の立ち下がり                                   |       | 1.5 |       | V    |

| $t_{\text{ADPT}}$                                               | LO 立ち下がりエッジから HO 立ち上がりエッジまでの遅延                                                                                                          | $V_{\text{DT}} = \text{V}_{\text{VDD}}$                                                                                                              | 28    | 40  | 75    | ns   |

|                                                                 | HO 立ち下がりエッジから LO 立ち上がりエッジまでの遅延                                                                                                          | $V_{\text{DT}} = \text{V}_{\text{VDD}}$                                                                                                              | 30    | 40  | 75    | ns   |

| $t_{\text{SD}}$                                                 | ラッチ シャットダウン グリッチ フィルタ                                                                                                                   |                                                                                                                                                      | 1.875 | 2.5 | 3.125 | μs   |

| $R_{\text{SD}}$                                                 | シャットダウン ラッチ プルダウン抵抗                                                                                                                     | 外部プルダウン NFET と直列に接続した抵抗                                                                                                                              |       | 2   |       | kΩ   |

| <b>ソフトスタート、強制 PWM、ダイオード エミュレーション プログラミング (SS/DEM1, SS/DEM2)</b> |                                                                                                                                         |                                                                                                                                                      |       |     |       |      |

| $I_{\text{SS}}$                                                 | スタートアップ時の SS 充電電流源                                                                                                                      | $\text{V}_{\text{SS}} \leq 3.3\text{V}, \text{V}_{\text{EN}} > 2\text{V}, \text{V}_{\text{UVLO}} > 2.5\text{V}, \text{DIR} < 1$ または $\text{DIR} > 2$ | 63    | 70  | 77    | μA   |

## 5.5 電気的特性 (続き)

標準値は  $T_J = 25^\circ\text{C}$  に対応します。最小および最大の制限値は、 $T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$  の範囲で適用されます。特に記述のない限り、 $F_{\text{OSC}} = 100\text{kHz}$ 、 $V_{\text{VCC}} = 10\text{V}$ 、 $V_{\text{HV1}} = V_{\text{HV2}} = V_{\text{HV-Port}} = 48\text{V}$  および  $V_{\text{LV-Port}} = 12\text{V}$  です。

| 記号                            | パラメータ                                | テスト条件                                                                                                                                    | 最小値   | 標準値   | 最大値  | 単位               |

|-------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|------|------------------|

| $I_{\text{SS}}$               | スタートアップ後の SS 充電電流源                   | $V_{\text{SS}} \geq 3.9\text{V}$ 、 $V_{\text{EN}} > 2\text{V}$ 、 $V_{\text{UVLO}} > 2.5\text{V}$ 、 $\text{DIR} < 1$ または $\text{DIR} > 2$ | 45    | 50    | 55   | $\mu\text{A}$    |

|                               | SS から gm への入力オフセット                   |                                                                                                                                          | 0.8   | 1     | 1.3  | V                |

| $R_{\text{SS}}$               | SS 放電デバイス Rds(ON)                    | $V_{\text{SS}} = 2\text{V}$                                                                                                              | 5     | 20    | 30   | $\Omega$         |

| $V_{\text{SS\_LOW}}$          | SS 放電完了スレッショルド                       | 内部ロジックによって放電された時点                                                                                                                        | 0.15  | 0.3   | 0.35 | V                |

| <b>構成 (CFG)</b>               |                                      |                                                                                                                                          |       |       |      |                  |

| $R_{\text{CFG1}}$             | I2C アドレス:b0100000。IMON = IMON_IL     |                                                                                                                                          |       | 0     |      | $\text{k}\Omega$ |

| $R_{\text{CFG2}}$             | I2C アドレス:b0100001。IMON = IMON_IL     |                                                                                                                                          | 0.316 | 0.324 |      | $\text{k}\Omega$ |

| $R_{\text{CFG3}}$             | I2C アドレス:b0100010。IMON = IMON_IL     |                                                                                                                                          | 0.649 | 0.665 |      | $\text{k}\Omega$ |

| $R_{\text{CFG4}}$             | I2C アドレス:b0100011。IMON = IMON_IL     |                                                                                                                                          | 1.1   | 1.13  |      | $\text{k}\Omega$ |

| $R_{\text{CFG5}}$             | I2C アドレス:b0100100。IMON = IMON_IL     |                                                                                                                                          | 1.65  | 1.69  |      | $\text{k}\Omega$ |

| $R_{\text{CFG6}}$             | I2C アドレス:b0100101。IMON = IMON_IL     |                                                                                                                                          | 2.43  | 2.49  |      | $\text{k}\Omega$ |

| $R_{\text{CFG7}}$             | I2C アドレス:b0100110。IMON = IMON_IL     |                                                                                                                                          | 3.32  | 3.4   |      | $\text{k}\Omega$ |

| $R_{\text{CFG8}}$             | I2C アドレス:b0100111。IMON = IMON_IL     |                                                                                                                                          | 4.53  | 4.64  |      | $\text{k}\Omega$ |

| $R_{\text{CFG9}}$             | I2C アドレス:b0100111。IMON = IMON_BSTOUT |                                                                                                                                          | 6.65  | 6.81  |      | $\text{k}\Omega$ |

| $R_{\text{CFG10}}$            | I2C アドレス:b0100110。IMON = IMON_BSTOUT |                                                                                                                                          | 10.2  | 10.5  |      | $\text{k}\Omega$ |

| $R_{\text{CFG11}}$            | I2C アドレス:b0100101。IMON = IMON_BSTOUT |                                                                                                                                          | 13.7  | 14.0  |      | $\text{k}\Omega$ |

| $R_{\text{CFG12}}$            | I2C アドレス:b0100100。IMON = IMON_BSTOUT |                                                                                                                                          | 18.7  | 19.1  |      | $\text{k}\Omega$ |

| $R_{\text{CFG13}}$            | I2C アドレス:b0100011。IMON = IMON_BSTOUT |                                                                                                                                          | 26.1  | 26.7  |      | $\text{k}\Omega$ |

| $R_{\text{CFG14}}$            | I2C アドレス:b0100010。IMON = IMON_BSTOUT |                                                                                                                                          | 37.4  | 38.3  |      | $\text{k}\Omega$ |

| $R_{\text{CFG15}}$            | I2C アドレス:b0100001。IMON = IMON_BSTOUT |                                                                                                                                          | 60.4  | 61.9  |      | $\text{k}\Omega$ |

| $R_{\text{CFG16}}$            | I2C アドレス:b0100000。IMON = IMON_BSTOUT |                                                                                                                                          | 95.3  | 97.6  |      | $\text{k}\Omega$ |

| <b>I2C インターフェイス (SLC、SDA)</b> |                                      |                                                                                                                                          |       |       |      |                  |

| $V_{\text{SDAL}}$             | SDA 入力 Low 状態                        |                                                                                                                                          |       | 1.0   |      | V                |

| $V_{\text{SDAH}}$             | SDA 入力 High 状態                       |                                                                                                                                          | 2.0   |       |      | V                |

| $V_{\text{SCLL}}$             | SCL 入力 Low 状態                        |                                                                                                                                          |       | 1.0   |      | V                |

| $V_{\text{SCLH}}$             | SCL 入力 High 状態                       |                                                                                                                                          | 2.0   |       |      | V                |

| <b>サーマル シャットダウン</b>           |                                      |                                                                                                                                          |       |       |      |                  |

| $T_{\text{J\_SD}}$            | サーマル シャットダウン                         |                                                                                                                                          | 155   | 175   |      | $^\circ\text{C}$ |

## 5.5 電気的特性 (続き)

標準値は  $T_J = 25^\circ\text{C}$  に対応します。最小および最大の制限値は、 $T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$  の範囲で適用されます。特に記述のない限り、 $F_{\text{OSC}} = 100\text{kHz}$ 、 $V_{\text{VCC}} = 10\text{V}$ 、 $V_{\text{HV1}} = V_{\text{HV2}} = V_{\text{HV-Port}} = 48\text{V}$  および  $V_{\text{LV-Port}} = 12\text{V}$  です。

| 記号 | パラメータ               | テスト条件 | 最小値 | 標準値 | 最大値 | 単位 |

|----|---------------------|-------|-----|-----|-----|----|

|    | サーマル シャットダウン ヒステリシス |       | 15  |     |     | °C |

## 5.6 タイミング要件

動作接合部温度範囲および推奨電源電圧範囲(特に記載のない限り)

|                                |                              |                             | 最小値  | 公称値                           | 最大値 | 単位  |

|--------------------------------|------------------------------|-----------------------------|------|-------------------------------|-----|-----|

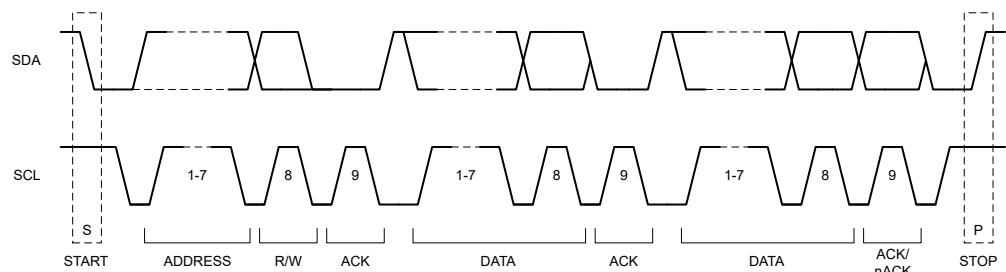

| <b>I<sup>2</sup>C インターフェイス</b> |                              |                             |      |                               |     |     |

| $f_{\text{SCL}}$               | SCL クロック周波数                  | スタンダード モード                  | 0    | 100                           |     | kHz |

|                                |                              | ファスト モード                    | 0    | 400                           |     |     |

|                                |                              | ファスト モード プラス <sup>(1)</sup> | 0    | 1000                          |     |     |

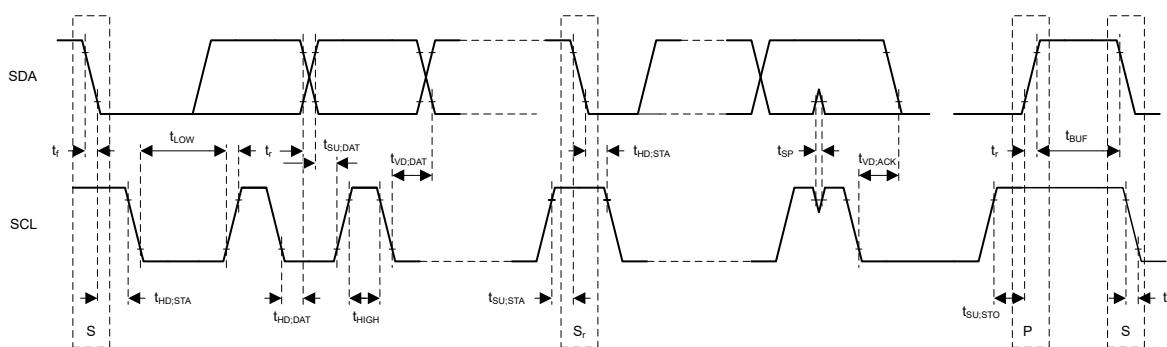

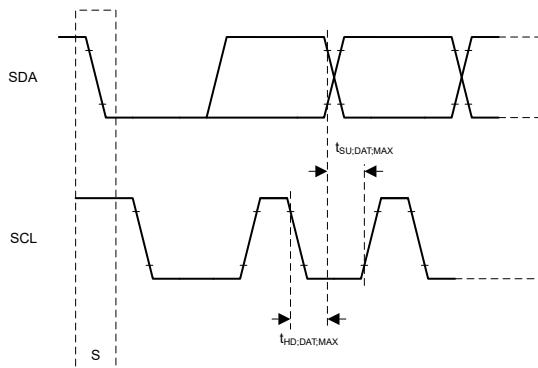

| $t_{\text{LOW}}$               | SCL クロック Low 期間              | スタンダード モード                  | 4.7  |                               |     | μs  |

|                                |                              | ファスト モード                    | 1.3  |                               |     |     |

|                                |                              | ファスト モード プラス <sup>(1)</sup> | 0.5  |                               |     |     |

| $t_{\text{HIGH}}$              | SCL クロックの High の時間           | スタンダード モード                  | 4.0  |                               |     | μs  |

|                                |                              | ファスト モード                    | 0.6  |                               |     |     |

|                                |                              | ファスト モード プラス <sup>(1)</sup> | 0.26 |                               |     |     |

| $t_{\text{BUF}}$               | 停止条件と開始条件<br>の間のバス フリー時間     | スタンダード モード                  | 4.7  |                               |     | μs  |

|                                |                              | ファスト モード                    | 1.3  |                               |     |     |

|                                |                              | ファスト モード プラス <sup>(1)</sup> | 0.5  |                               |     |     |

| $t_{\text{SU:STA}}$            | 繰り返し START<br>条件のセットアップ時間    | スタンダード モード                  | 4.7  |                               |     | μs  |

|                                |                              | ファスト モード                    | 0.6  |                               |     |     |

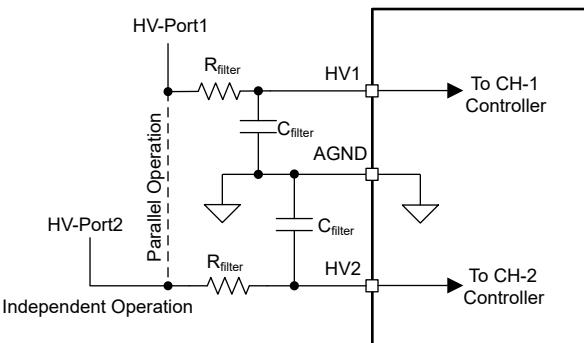

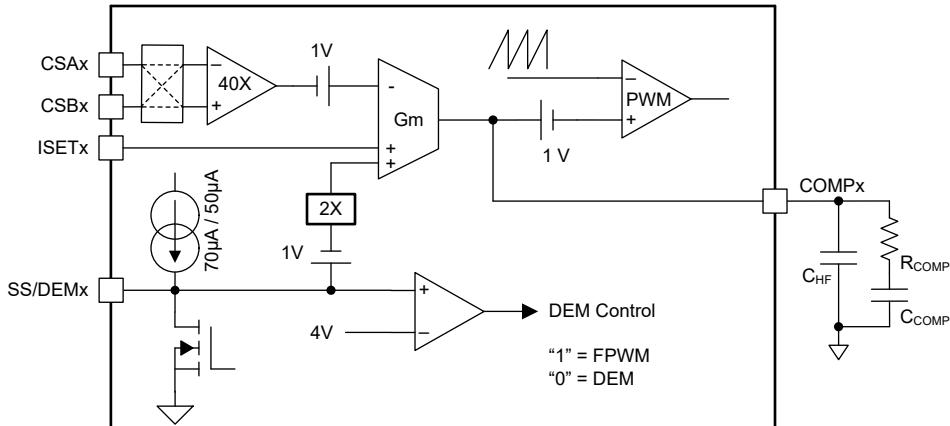

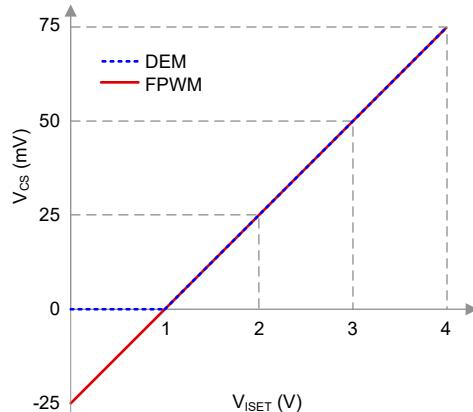

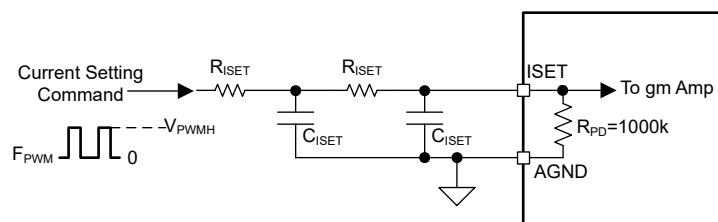

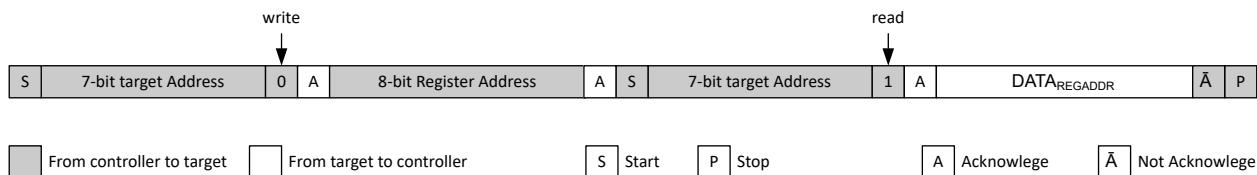

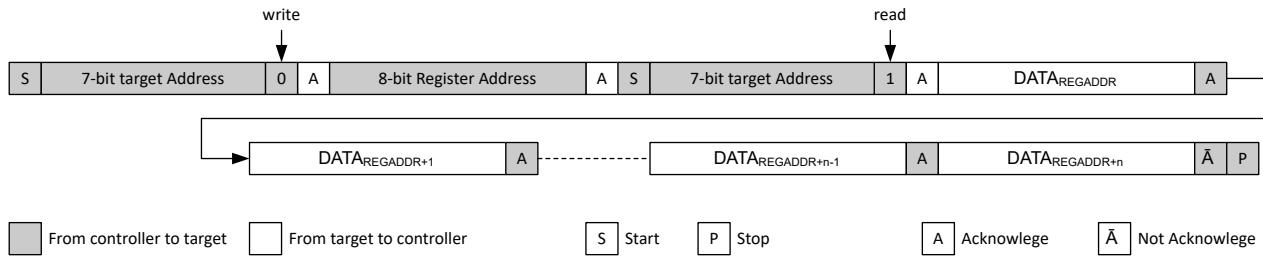

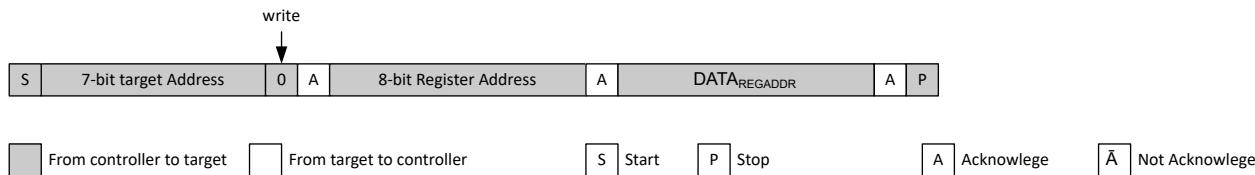

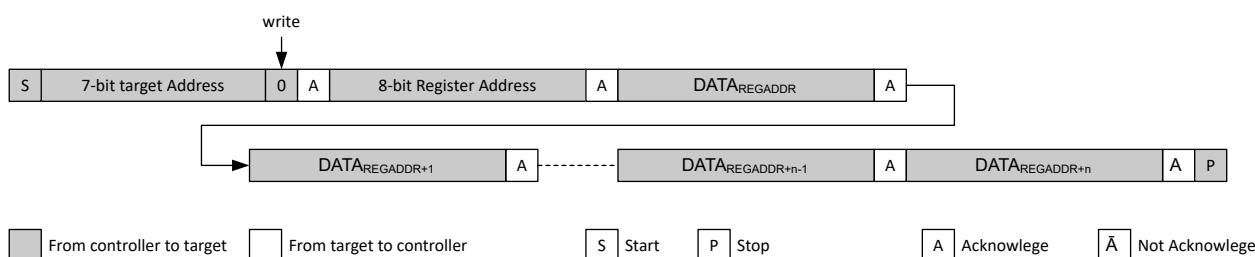

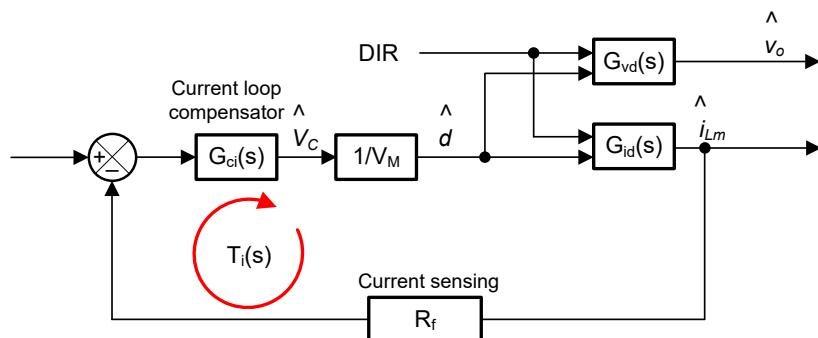

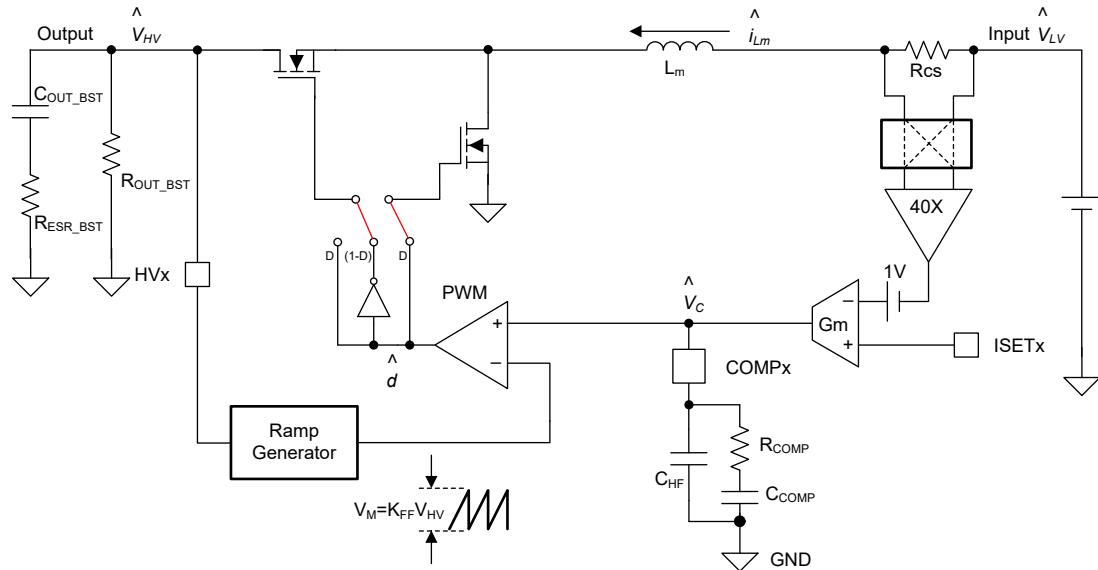

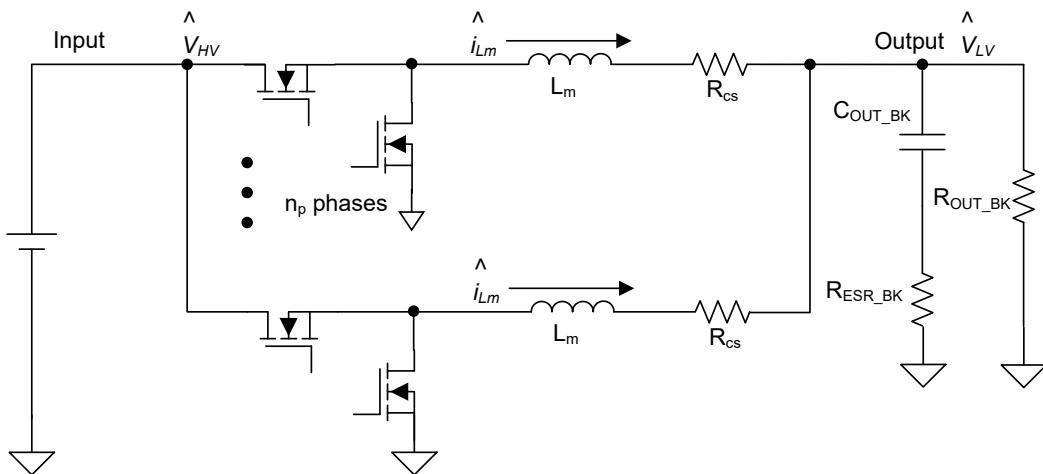

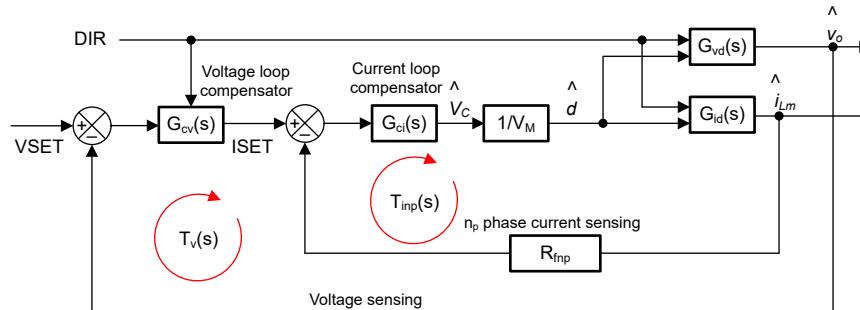

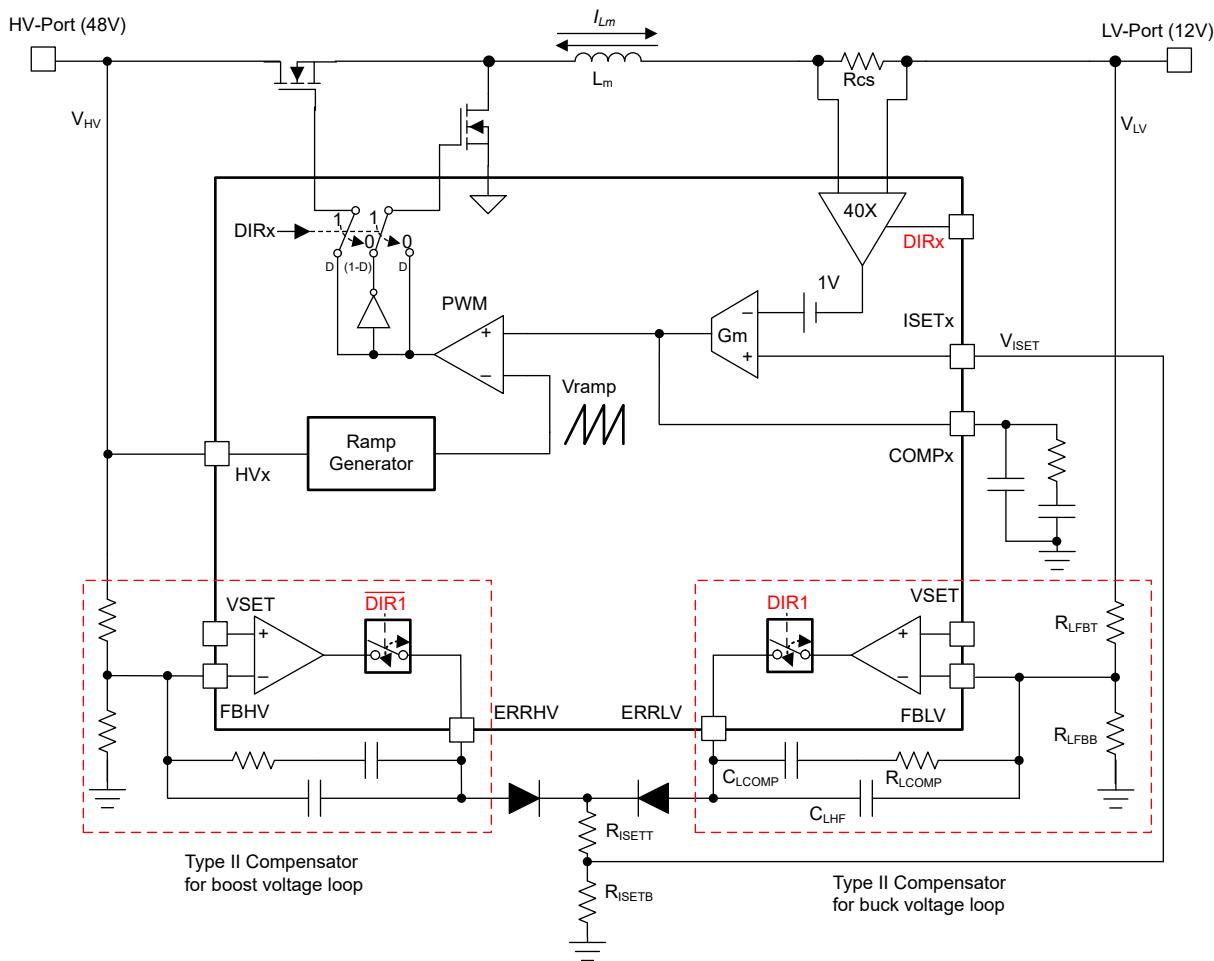

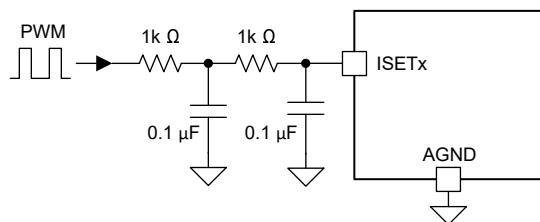

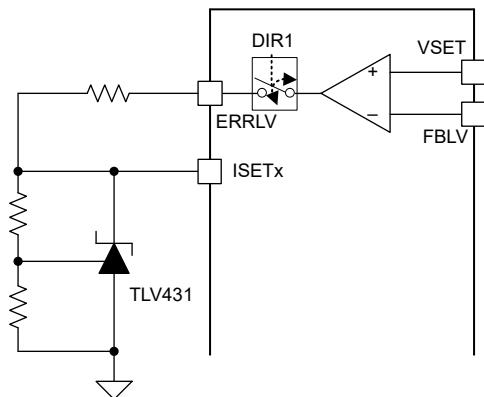

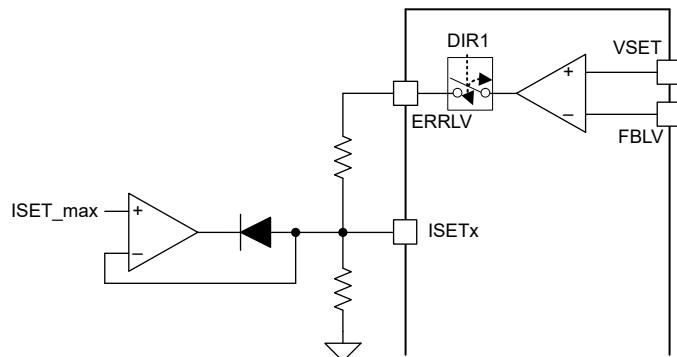

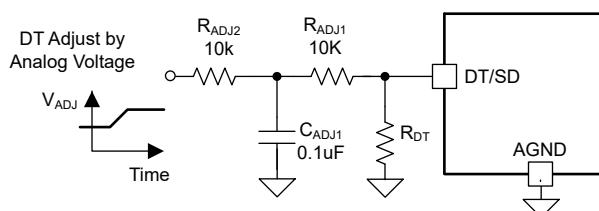

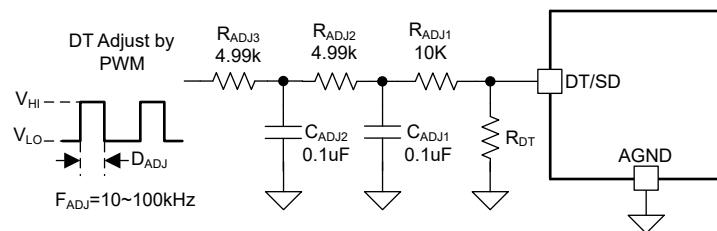

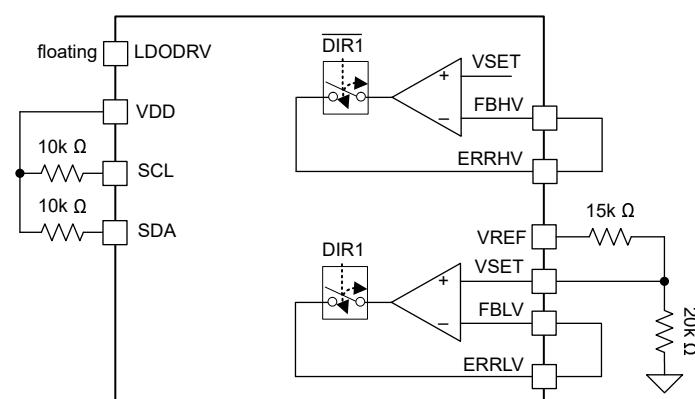

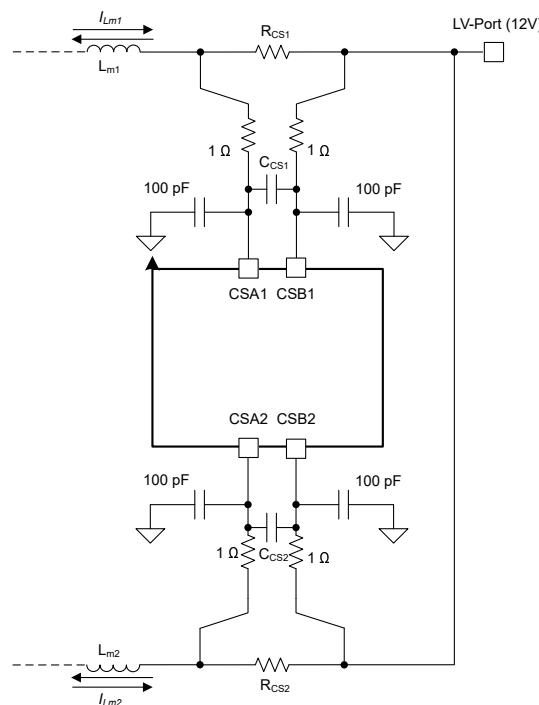

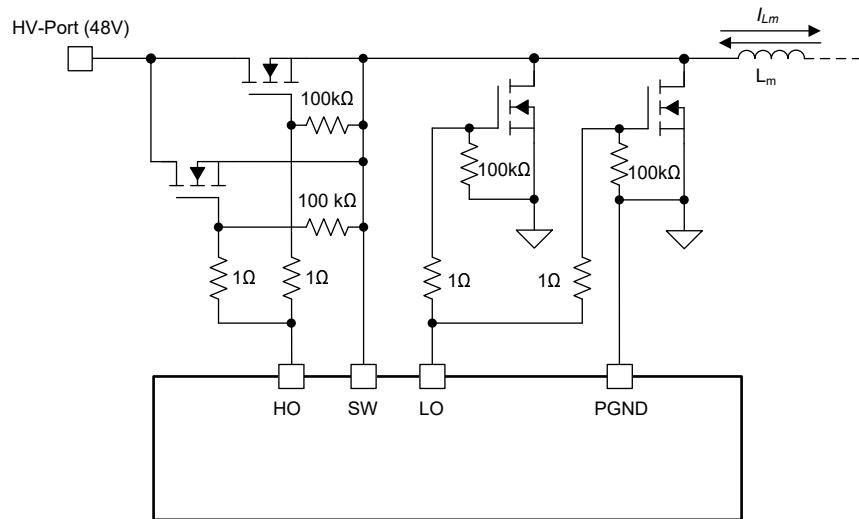

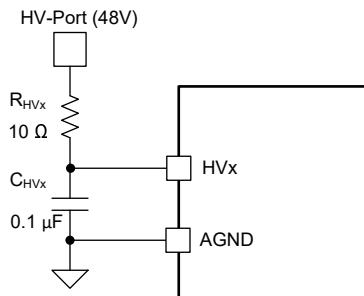

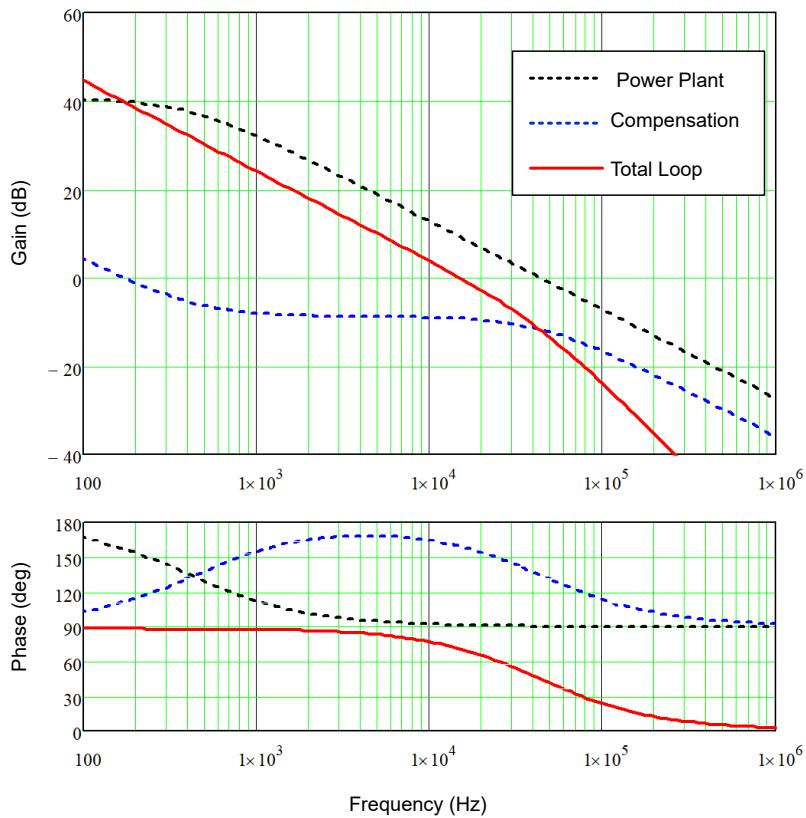

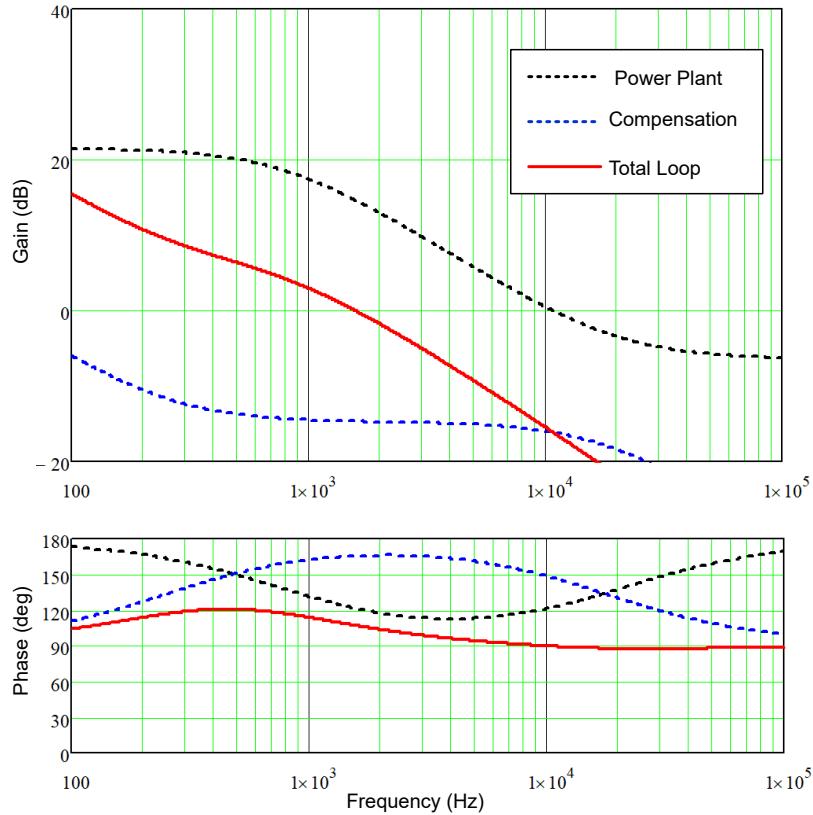

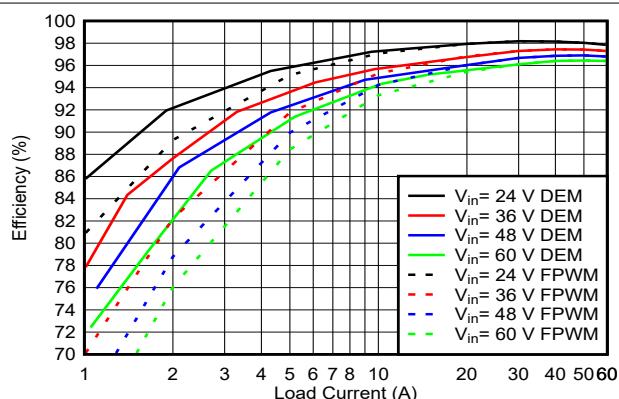

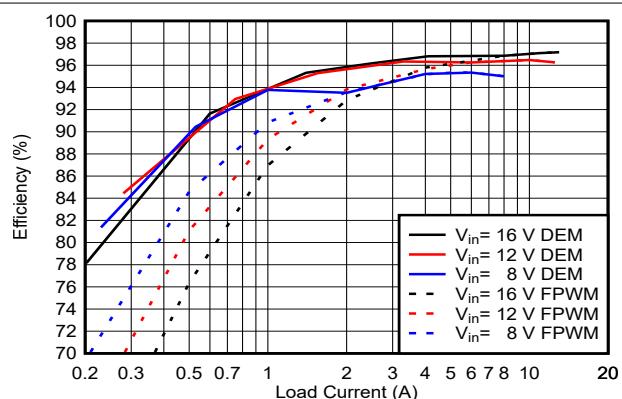

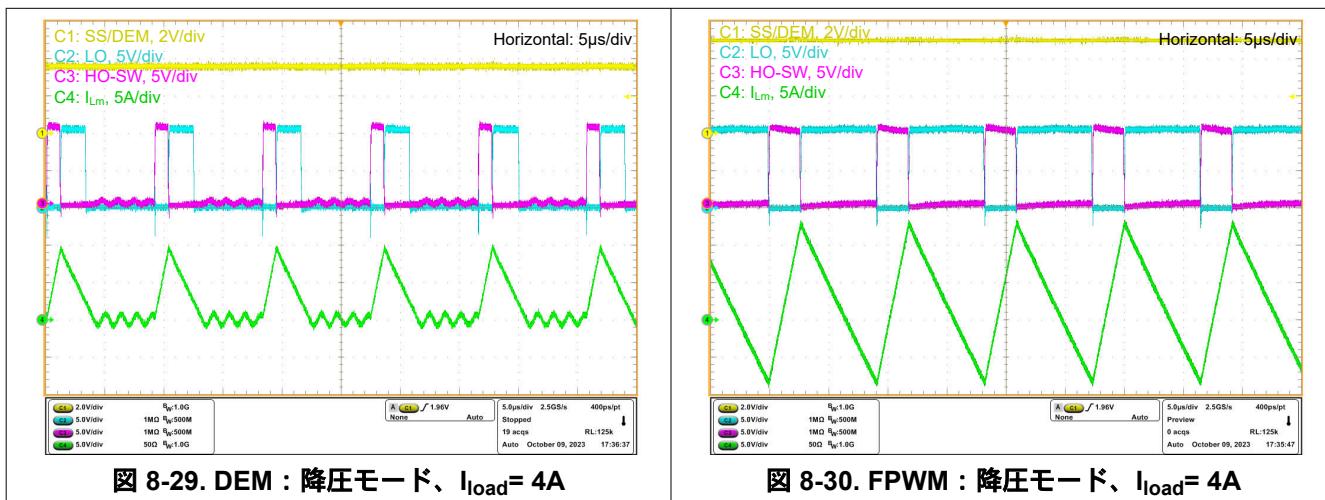

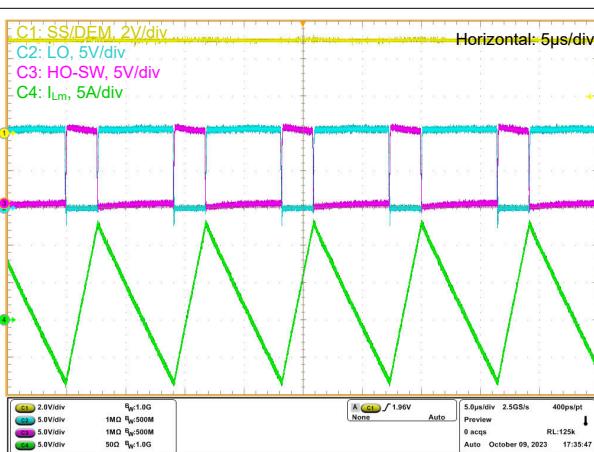

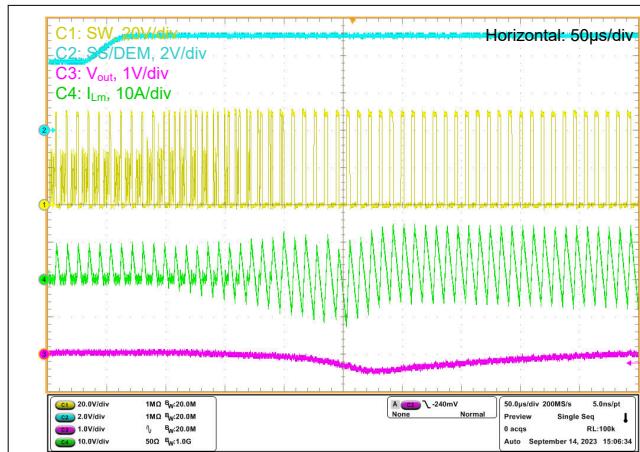

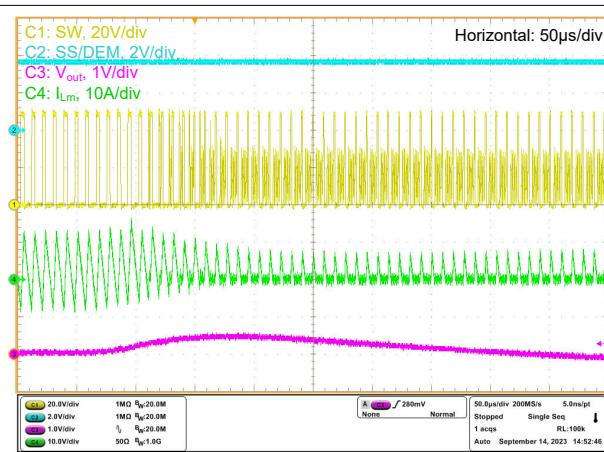

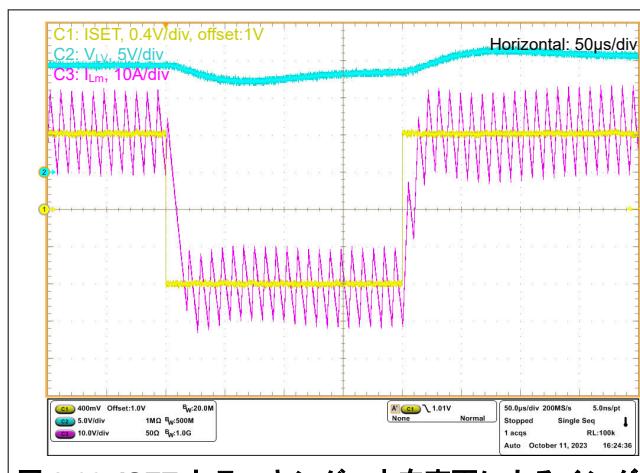

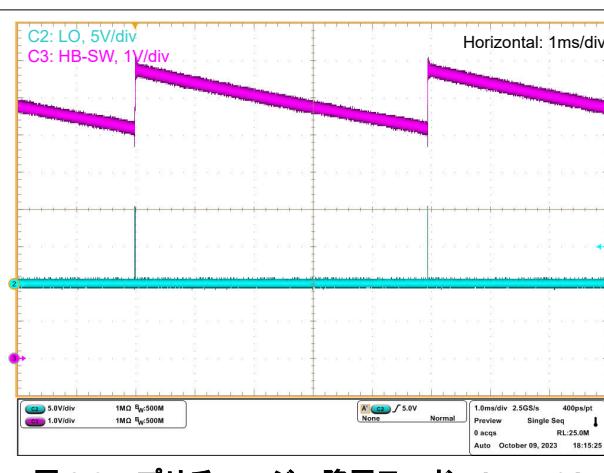

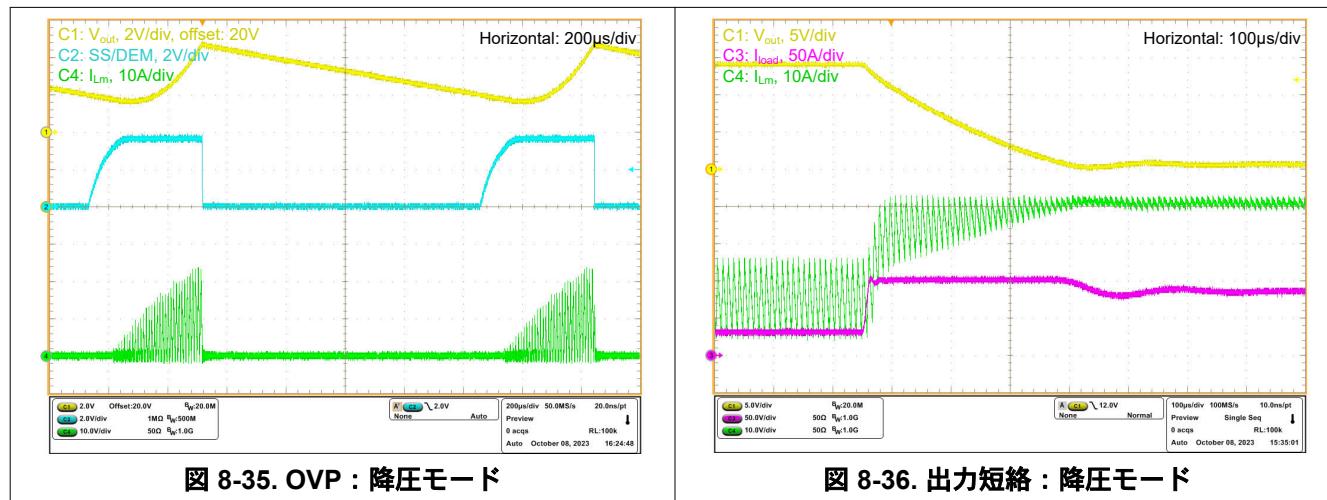

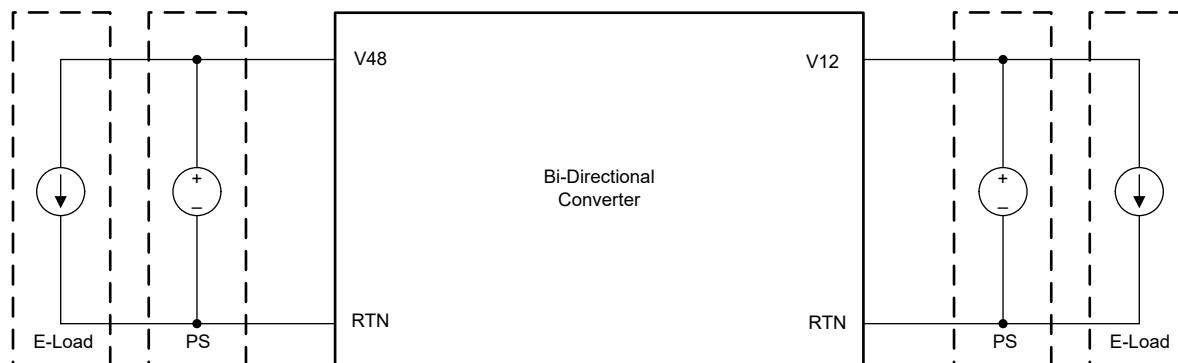

|                                |                              | ファスト モード プラス <sup>(1)</sup> | 0.26 |                               |     |     |