# サーバー管理用 PI ループ ファン制御機能付き LM94 TruTherm™ ハードウェア モニタ

## 1 特長

- 8 ビット  $\Sigma\Delta$  ADC

- 16 個の電源を監視

- 4 個のリモート サーマル ダイオードと 2 個の LM60 を監視

- 新しい TruTherm 技術による高精度サーマル ダイオード測定のサポート

- 内部周囲温度センシング

- 温度読み出しに基づくファン昇圧サポート付きプログラマブル自律ファン制御

- タコメータ制限エラー イベント発生時のファン昇圧サポート

- 13 ステップのルックアップ テーブル、PI 制御ループ、またはその両方の組み合わせに基づくファン制御

- Tcontrol をサポートする PI ファン制御ループ

- 温度読み出しデジタル フィルタ

- 0.5°C デジタル 温度センサ 分解能

- ファン制御用 0.0625°C フィルタ 温度分解能

- 2 つの PWM ファン速度制御出力

- 4 つのファン タコメータ入力

- デュアル プロセッサ 熱スロットリング (PROCHOT) の監視

- VRD10.2/11 をサポートするデュアル動的 VID 監視 (プロセッサごとに 6 つの VID または 7 つの VID)

- 8 つの汎用 I/O:

- 4 つはファン タコメータ入力として構成可能

- 2 つはプロセッサ THERMTRIP に接続するように構成可能

- 2 つは IERR 信号の監視に使用可能な標準 GPIO

- 2 つの汎用入力を使用して VRD11 の 7 番目の VID 信号を監視可能

- すべての監視値の制限レジスタ比較

- 2 線式シリアル デジタル インターフェイス、SMBus 2.0 準拠

- バイト / ブロックの読み出しと書き込みをサポート

- 選択可能なスレーブ アドレス (トライレベル ピンで 3 つのアドレスから 1 つを選択)

- ALERT 出力で割り込みモードまたはコンパレータ モードをサポート

- 2.5V リファレンス 電圧出力

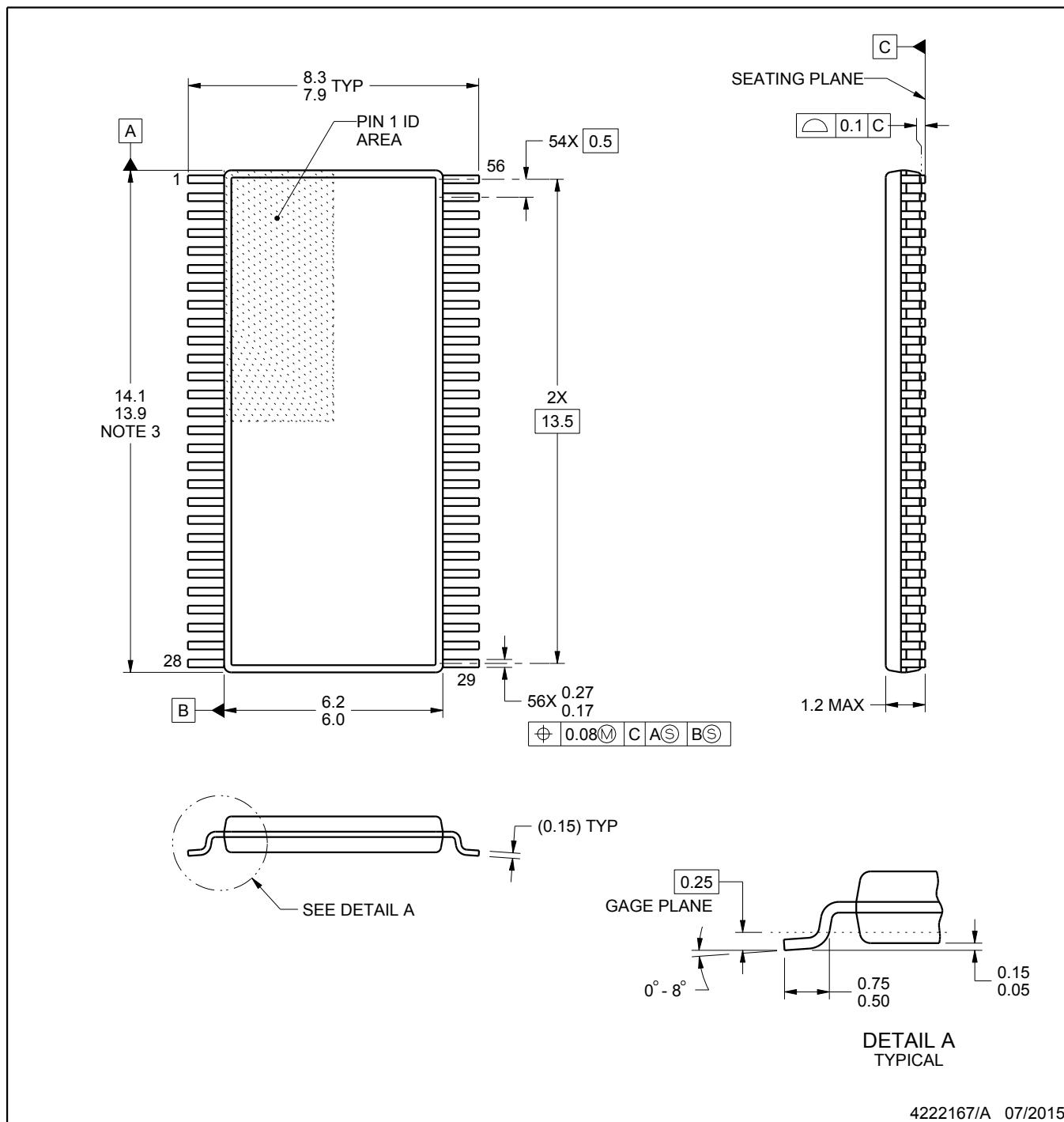

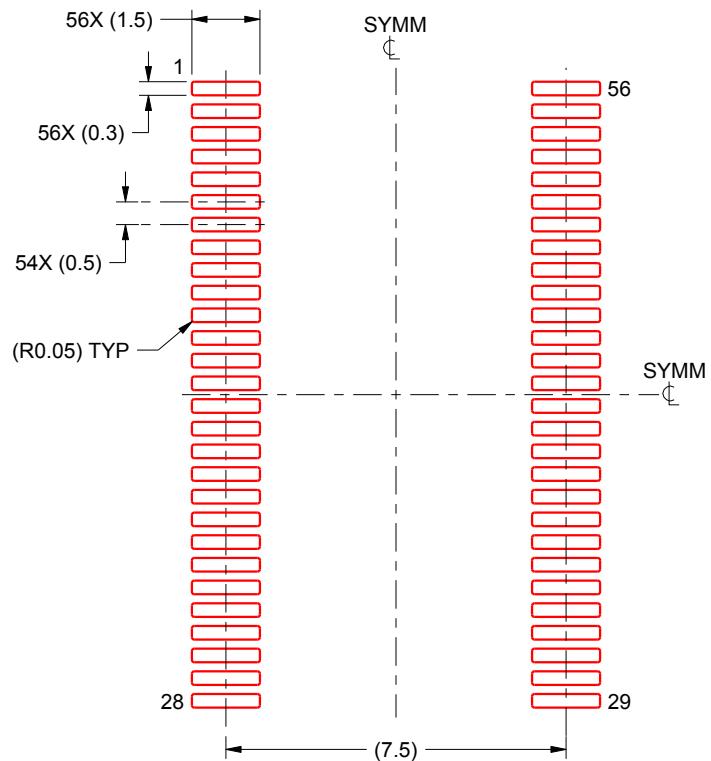

- 56 ピン TSSOP パッケージ

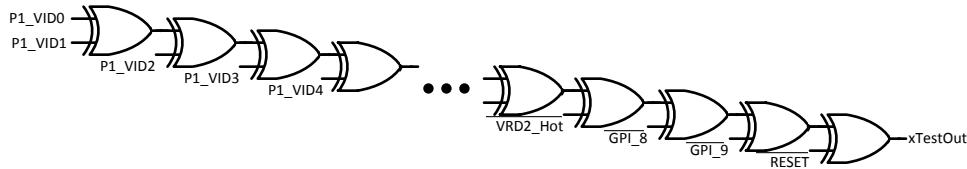

- XOR ツリー テスト モード

## 主な仕様:

- 電圧測定精度 ... $\pm 2\%$  FS (最大)

- 温度分解能 ...9 ビット、0.5°C

- 温度センサ精度 ... $\pm 2.5\%$  (最大)

- 温度範囲:

- LM94 動作 ...0°C ~ +85°C

- リモート温度精度 ...0°C ~ +125°C

- 電源電圧 ...+3.0V ~ +3.6V

- 電源電流 ...1.6 mA

## 2 アプリケーション

- サーバー

- ワークステーション

- マルチプロセッサ ベースの機器

## 3 概要

LM94 ハードウェア モニタには、SMBus 2.0 互換の 2 線式デジタル インターフェイスが搭載されています。LM94 は、 $\Sigma\Delta$  ADC を使用して、4 つのリモート ダイオード接続トランジスタの温度、自身のダイの温度、16 の電源電圧を測定します。LM94 には新しい TruTherm 技術が採用されており、サブミクロン プロセスでのプロセッサの高精度サーマル ダイオード測定をサポートしています。

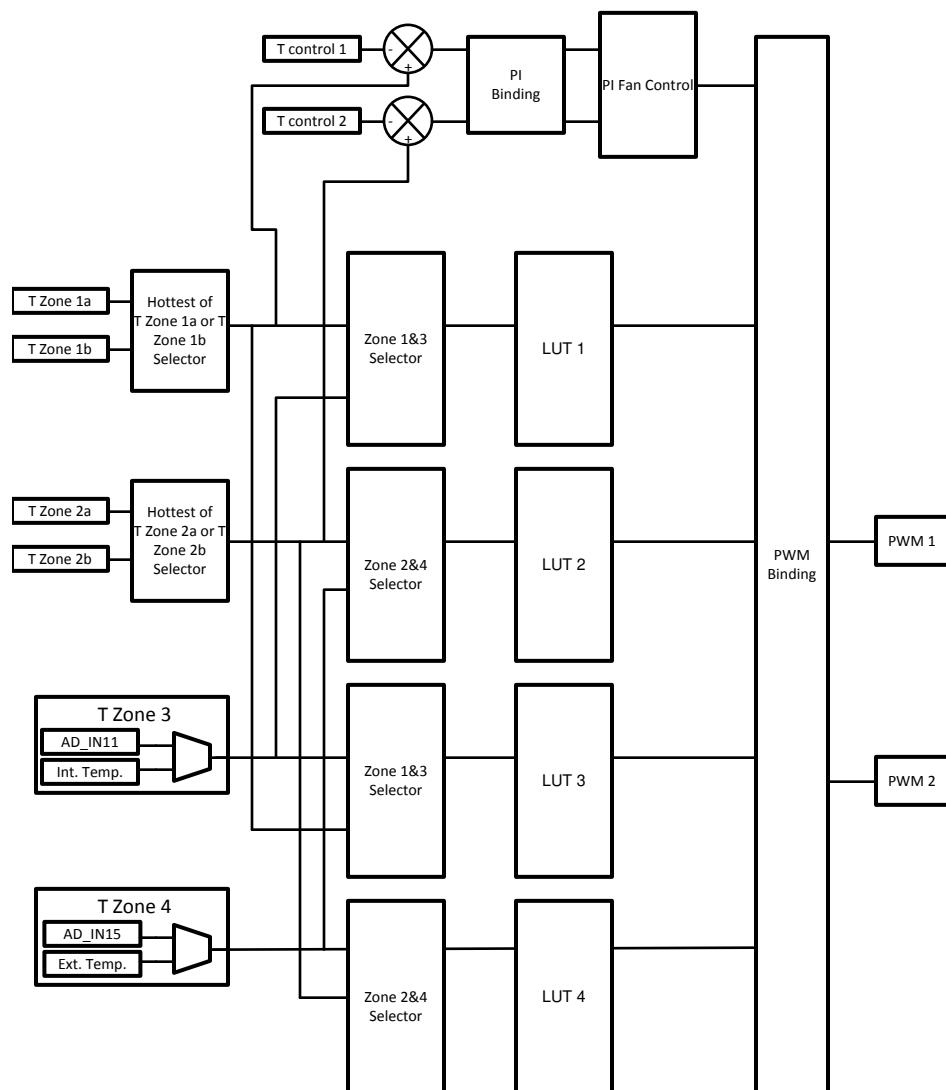

ファン速度を設定するために、LM94 には 2 つの PWM 出力があり、それぞれが最大で 6 つの温度ゾーンによって制御されています。ファン制御アルゴリズムは、ルックアップ テーブル、PI (比例 / 積分) 制御ループ、またはその両方の組み合わせに基づくことができます。LM94 にはデジタル フィルタが搭載されており、温度測定値を平滑化し、音響ノイズを最小限に抑えてファン速度を最適に制御することができます。LM94 にはファン速度を測定するための 4 つのタコメータ入力があり、すべての測定値に対して、制限レジスタとステータス レジスタが搭載されています。

LM94 は、LM93 などの従来のマザーボード サーバー管理 ASIC の機能を基にしています。また、VRD10/11 と PROCHOT に対する動的 Vccp 監視の測定と制御のサポートも追加されており、デュアル プロセッサ Xeon クラスのマザーボードを最小限の外付け部品で監視するように設計されています。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあります。TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

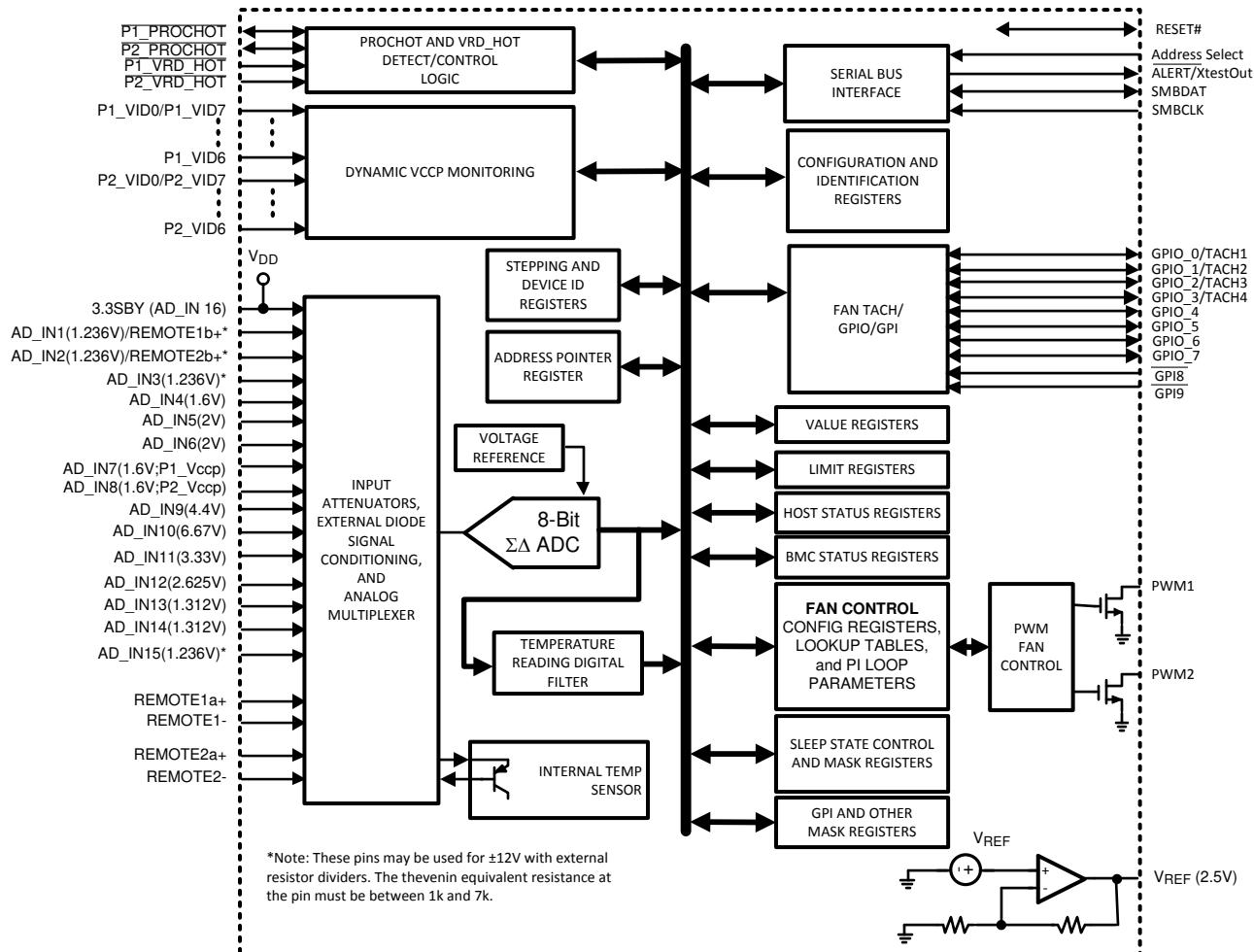

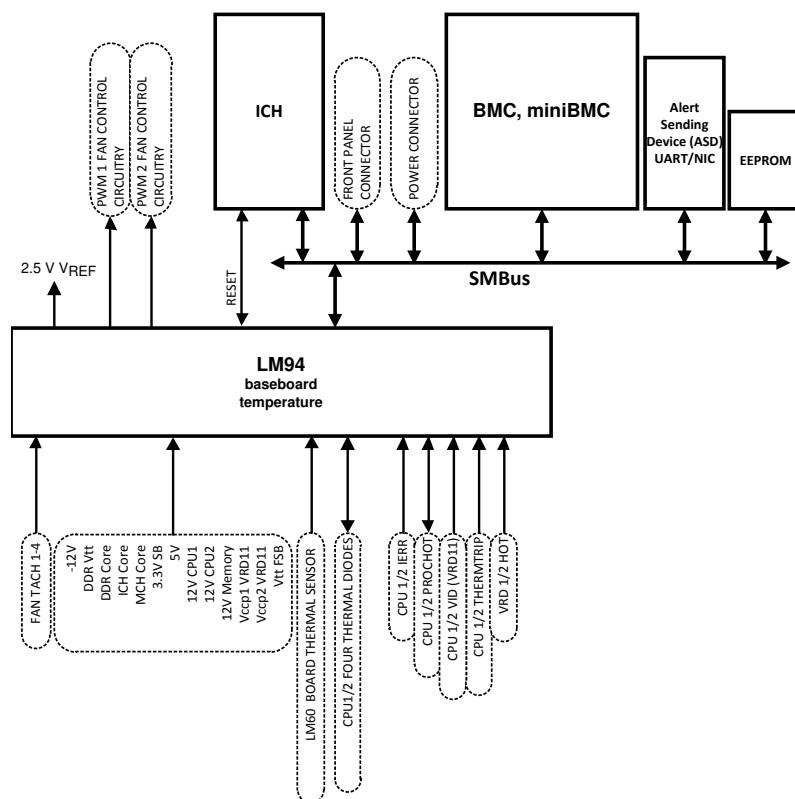

### 3.1 機能ブロック図

LM94 ハードウェアのブロック図を以下に示します。ハードウェアの実装は、シングルチップ ASIC ソリューションです。

## 目次

|                |    |                              |     |

|----------------|----|------------------------------|-----|

| 1 特長           | 1  | 7 アプリケーションと実装                | 105 |

| 2 アプリケーション     | 1  | 7.1 アプリケーション情報               | 105 |

| 3 概要           | 1  | 7.2 代表的なアプリケーション             | 109 |

| 3.1 機能ブロック図    | 2  | 8 レイアウト                      | 113 |

| 4 ピン構成および機能    | 3  | 8.1 推奨される実装                  | 113 |

| 4.1 サーバーに関する用語 | 6  | 8.2 ノイズを最小限に抑えるための PCB レイアウト | 114 |

| 5 仕様           | 8  | 9 デバイスおよびドキュメントのサポート         | 115 |

| 5.1 絶対最大定格     | 8  | 9.1 ドキュメントのサポート              | 115 |

| 5.2 動作定格       | 8  | 9.2 ドキュメントの更新通知を受け取る方法       | 115 |

| 5.3 DC 電気的特性   | 9  | 9.3 サポート・リソース                | 115 |

| 5.4 AC 電気的特性   | 12 | 9.4 商標                       | 115 |

| 6 詳細説明         | 15 | 9.5 静電気放電に関する注意事項            | 115 |

| 6.1 概要         | 15 | 9.6 用語集                      | 115 |

| 6.2 機能説明       | 15 | 10 改訂履歴                      | 115 |

| 6.3 プログラミング    | 35 | 11 メカニカル、パッケージ、および注文情報       | 115 |

| 6.4 レジスタ       | 45 |                              |     |

## 4 ピン構成および機能

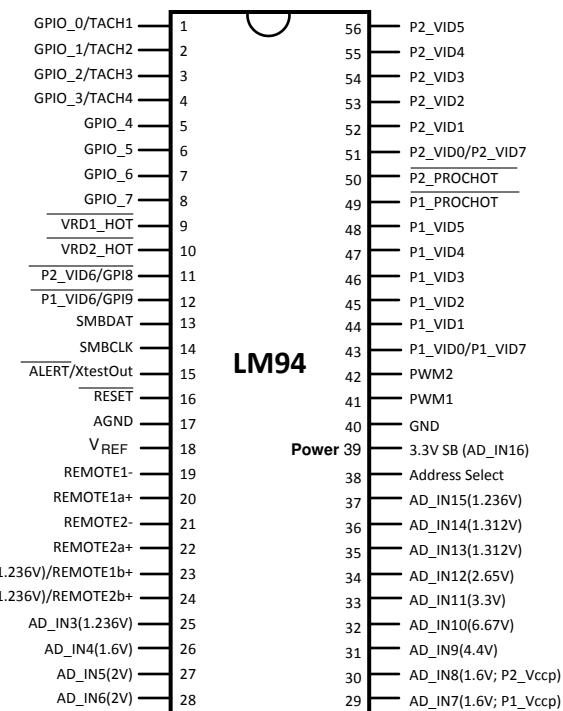

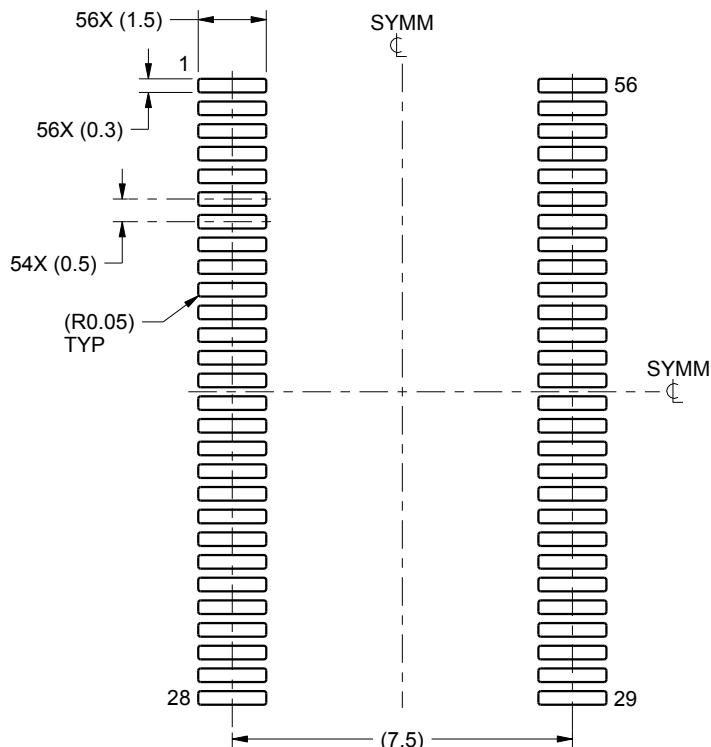

図 4-1. 56 ピン TSSOP パッケージ (パッケージ番号 DGG0056A を参照) 上面図

表 4-1. ピンの説明(1)

| 記号           | ピン番号 | 種類                  | 機能                                          |

|--------------|------|---------------------|---------------------------------------------|

| GPIO_0/TACH1 | 1    | デジタル I/O (オープンドレイン) | ファンタコメータ入力または汎用オープンドレイン デジタル I/O として構成できます。 |

| GPIO_1/TACH2 | 2    | デジタル I/O (オープンドレイン) | ファンタコメータ入力または汎用オープンドレイン デジタル I/O として構成できます。 |

表 4-1. ピンの説明<sup>(1)</sup> (続き)

| 記号                       | ピン番号 | 種類                                     | 機能                                                                                                                                                                                                                                     |

|--------------------------|------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO_2/TACH3             | 3    | デジタル I/O (オープンドレイン)                    | ファンタコメータ入力または汎用オープンドレイン デジタル I/O として構成できます。                                                                                                                                                                                            |

| GPIO_3/TACH4             | 4    | デジタル I/O (オープンドレイン)                    | ファンタコメータ入力または汎用オープンドレイン デジタル I/O として構成できます。                                                                                                                                                                                            |

| GPIO_4 /<br>P1_THERMTRIP | 5    | デジタル I/O (オープンドレイン)                    | 汎用オープンドレイン デジタル I/O。CPU の <u>THERMTRIP</u> 信号を監視し、他のエラーをマスクするように構成できます。TTL 入力ロジックレベルと AGTL 互換入力ロジックレベルをサポートしています。                                                                                                                      |

| GPIO_5 /<br>P2_THERMTRIP | 6    | デジタル I/O (オープンドレイン)                    | 汎用オープンドレイン デジタル I/O。CPU の <u>THERMTRIP</u> 信号を監視し、他のエラーをマスクするように構成できます。TTL 入力ロジックレベルと AGTL 互換入力ロジックレベルをサポートしています。                                                                                                                      |

| GPIO_6                   | 7    | デジタル I/O (オープンドレイン)                    | CPU1 <u>IERR</u> の状態または汎用オープンドレイン デジタル I/O の検出に使用できます。TTL 入力ロジックレベルと AGTL 互換入力ロジックレベルをサポートしています。                                                                                                                                       |

| GPIO_7                   | 8    | デジタル I/O (オープンドレイン)                    | CPU2 <u>IERR</u> の状態または汎用オープンドレイン デジタル I/O の検出に使用できます。TTL 入力ロジックレベルと AGTL 互換入力ロジックレベルをサポートしています。                                                                                                                                       |

| VRD1_HOT                 | 9    | デジタル入力                                 | CPU1 電圧レギュレータ <u>HOT</u> 。TTL 入力ロジックレベルと AGTL 互換入力ロジックレベルをサポートしています。                                                                                                                                                                   |

| VRD2_HOT                 | 10   | デジタル入力                                 | CPU2 電圧レギュレータ <u>HOT</u> 。TTL 入力ロジックレベルと AGTL 互換入力ロジックレベルをサポートしています。                                                                                                                                                                   |

| P2_VID6/ GPI8            | 11   | デジタル入力                                 | CPU2 VID6 入力。エラー イベントをトリガする汎用入力としても使用できます。TTL 入力ロジックレベルと AGTL 互換入力ロジックレベルをサポートしています。                                                                                                                                                   |

| P1_VID6/ GPI9            | 12   | デジタル入力                                 | CPU1 VID6 入力。エラー イベントをトリガする汎用入力としても使用できます。TTL 入力ロジックレベルと AGTL 互換入力ロジックレベルをサポートしています。                                                                                                                                                   |

| SMBDAT                   | 13   | デジタル I/O (オープンドレイン)                    | 双方向システム管理バス データ。出力は 5V 許容のオープンドレインとして構成されます。SMBus 2.0 準拠。                                                                                                                                                                              |

| SMBCLK                   | 14   | デジタル入力                                 | システム管理バス クロック。オープンドレイン出力で駆動され、5V 許容。SMBus 2.0 準拠。                                                                                                                                                                                      |

| ALERT/XtestOut           | 15   | デジタル出力 (オープンドレイン)                      | エラー イベントの発生を通知するために割り込み駆動システムで使用されるオープンドレイン <u>ALERT</u> 出力。マスクされたエラー イベントは <u>ALERT</u> 出力をアクティブにすることはありません。 <u>XOR</u> ツリー テスト モードでは、 <u>XOR</u> ツリー出力として機能します。                                                                      |

| RESET                    | 16   | デジタル I/O (オープンドレイン)                    | LM94 に最初に電源が印加されたときのオープンドレイン リセット出力。3.3V スタンバイで電力供給されるデバイスのリセットとして使用されます。リセット後のこのピンは、リセット入力になります。詳細については「 <u>セクション 7.1.2</u> 」を参照。使用しない場合は、LM94 の誤動作を防止するために、このピンは外部プルアップ抵抗に接続する必要があります。                                               |

| AGND                     | 17   | GROUND 入力                              | アナログ グラウンド。デジタル グラウンドとアナログ グラウンドはチップで接続し、両方を低ノイズのシステム グラウンドに接続する必要があります。アナログ グラウンドとデジタル グラウンドの間に電圧差があると、正しい結果が得られないことがあります。                                                                                                            |

| V <sub>REF</sub>         | 18   | アナログ出力                                 | 2.5V、外部 ADC リファレンス電圧、または V <sub>REF</sub> リファレンス電圧として使用                                                                                                                                                                                |

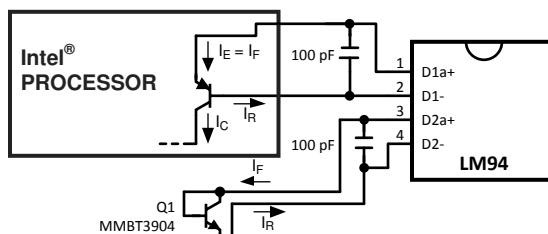

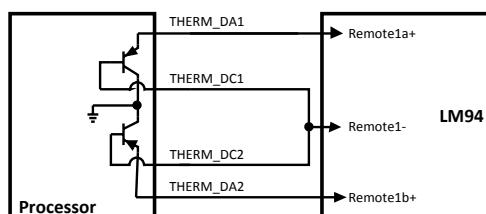

| REMOTE1-                 | 19   | リモート サーマル ダイオード_1- 入力 (CPU1 THERMDC)   | これは両方の CPU1 サーマル ダイオードからの負入力 (電流シンク) です。Pentium プロセッサの THERMDC ピンまたはダイオード接続の MMBT3904 NPN トランジスタのエミッタに接続されています。サーマル ダイオード電圧測定のために A/D への負入力として機能します。100pF コンデンサはオプションであり、REMOTE1- と REMOTE1+ の間に接続できます。                                |

| REMOTE1a+                | 20   | リモート サーマル ダイオード_1+ I/O (CPU1 THERMDA1) | これは、最初の CPU1 サーマル ダイオードへの正の接続です。サーマル ダイオード電圧測定のために A/D への正入力として機能します。また、サーマル ダイオードを順方向にバイアスする電流源出力としても機能します。Pentium プロセッサの THERMDA ピンまたはダイオード接続の MMBT3904 NPN トランジスタのベースに接続されています。100pF コンデンサはオプションであり、REMOTE1- と各 REMOTE1+ の間に接続できます。 |

表 4-1. ピンの説明<sup>(1)</sup> (続き)

| 記号                | ピン番号 | 種類                                     | 機能                                                                                                                                                                                                                                                              |

|-------------------|------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REMOTE2-          | 21   | リモート サーマル ダイオード_2 - 入力 (CPU2 THERMDC)  | これは両方の CPU2 サーマル ダイオードからの負入力 (電流シンク) です。Pentium プロセッサの THERMDC ピンまたはダイオード接続された MMBT3904 NPN トランジスタのエミッタに接続されています。サーマル ダイオード電圧測定用の AD への負入力として機能します。100pF コンデンサはオプションで、REMOTE2- と各 REMOTE2+ の間に接続できます。                                                           |

| REMOTE2a+         | 22   | リモート サーマル ダイオード_2+ I/O (CPU2 THERMDA1) | これは、最初の CPU2 サーマル ダイオードへの正の接続です。サーマル ダイオード電圧測定のために A/D への正入力として機能します。また、サーマル ダイオードを順方向にバイアスする電流源出力としても機能します。Pentium プロセッサの THERMDA ピンまたはダイオード接続の MMBT3904 NPN トランジスタのベースに接続されています。100pF コンデンサはオプションであり、REMOTE2- と REMOTE2+ の間に接続できます。                           |

| AD_IN1/REMOTE1b+  | 23   | アナログ入力 (+12V1 または CPU1 THERMDA2)       | CPU1 電圧レギュレータ用、+12V レール 1 監視用アナログ入力。公称 $\frac{3}{4}$ スケールの読み取りで 12V がを 0.927V に減衰するような外部減衰抵抗が必要です。このピンは、CPU1 の 2 番目の正のサーマル ダイオード入力としても機能します。                                                                                                                    |

| AD_IN2/REMOTE2b+  | 24   | アナログ入力 (+12V2 または CPU2 THERMDA2)       | CPU2 電圧レギュレータ用、+12V レール 2 監視用アナログ入力。公称 $\frac{3}{4}$ スケールの読み取りで 12V がを 0.927V に減衰するような外部減衰抵抗が必要です。このピンは、CPU2 の 2 番目の正のサーマル ダイオード入力としても機能します。                                                                                                                    |

| AD_IN3            | 25   | アナログ入力 (+12V3)                         | メモリ / 3GIO スロット用、+12V レール 3 用アナログ入力。公称 $\frac{3}{4}$ スケールの読み取りで 12V がを 0.927V に減衰するような外部減衰抵抗が必要です。                                                                                                                                                              |

| AD_IN4            | 26   | アナログ入力 (FSB_Vtt)                       | 1.2V 監視用アナログ入力、公称 $\frac{3}{4}$ スケール読み取り                                                                                                                                                                                                                        |

| AD_IN5            | 27   | アナログ入力 (3GIO/PXH/MCH_Core)             | 1.5V 監視用アナログ入力、公称 $\frac{3}{4}$ スケール読み取り                                                                                                                                                                                                                        |

| AD_IN6            | 28   | アナログ入力 (ICH_Core)                      | 1.5V 監視用アナログ入力、公称 $\frac{3}{4}$ スケール読み取り                                                                                                                                                                                                                        |

| AD_IN7 (P1_Vccp)  | 29   | アナログ入力 (CPU1_Vccp)                     | +Vccp (プロセッサ電圧) 監視用アナログ入力。                                                                                                                                                                                                                                      |

| AD_IN8 (P2_Vccp)  | 30   | アナログ入力 (CPU2_Vccp)                     | +Vccp (プロセッサ電圧) 監視用アナログ入力。                                                                                                                                                                                                                                      |

| AD_IN9            | 31   | アナログ入力 (+3.3V)                         | +3.3V 監視用アナログ入力、公称 $\frac{3}{4}$ スケール読み取り                                                                                                                                                                                                                       |

| AD_IN10           | 32   | アナログ入力 (+5V)                           | +5V 監視用アナログ入力、シルバー ボックス電源監視、公称 $\frac{3}{4}$ スケール読み取り                                                                                                                                                                                                           |

| AD_IN11           | 33   | アナログ入力 (SCSI_Core)                     | +2.5V 監視用アナログ入力、公称 $\frac{3}{4}$ スケール読み取り。この入力の読み取り値はファン制御ロジックに送ることができますため、このピンは LM60 などのアナログ温度センサの監視にも使用できます。                                                                                                                                                  |

| AD_IN12           | 34   | アナログ入力 (Mem_Core)                      | +1.969V 監視用アナログ入力、公称 $\frac{3}{4}$ スケール読み取り。                                                                                                                                                                                                                    |

| AD_IN13           | 35   | アナログ入力 (Mem_Vtt)                       | +0.984V 監視用アナログ入力、公称 $\frac{3}{4}$ スケール読み取り。                                                                                                                                                                                                                    |

| AD_IN14           | 36   | アナログ入力 (Gbit_Core)                     | +0.984V S/B 監視用アナログ入力、公称 $\frac{3}{4}$ スケール読み取り。                                                                                                                                                                                                                |

| AD_IN15           | 37   | アナログ入力 (-12V)                          | -12V 監視用アナログ入力。正のレベルへのスケーリングには外付け抵抗が必要です。1.236V でのフルスケール読み取り、公称 $\frac{3}{4}$ スケール読み取り。この入力の読み取り値はファン制御ロジックに送ることができますため、このピンは LM60 などのアナログ温度センサの監視にも使用できます。                                                                                                     |

| Address Select    | 38   | 3 レベル アナログ入力                           | この入力は、LM94 の SMBus スレーブ アドレスの下位 2 ビットを選択します。                                                                                                                                                                                                                    |

| 3.3V SB (AD_IN16) | 39   | POWER (V <sub>DD</sub> ) +3.3V スタンバイ電力 | LM94 の V <sub>DD</sub> 電源入力。通常、+3.3V スタンバイ電力に接続されています。低消費電力状態での監視が必要ない場合は、LM94 に +3.3V で電力供給できますが、他のピンよりも先にこの入力に電力供給する必要があります。このピンは、3.3V スタンバイ (SB) 電圧を監視するアナログ入力としても機能します。このピンは、100pF と並列に 0.1μF でバイパスする必要があります。10μF のバブル容量がすぐそばにあり、100pF が電源ピンに最も近くなければなりません。 |

| GND               | 40   | グランド                                   | デジタル グランド。デジタル グランドとアナログ グランドはチップで接続し、両方を低ノイズのシステム グランドに接続する必要があります。アナログ グランドとデジタル グランドの間に電圧差があると、正しい結果が得られないことがあります。                                                                                                                                           |

表 4-1. ピンの説明<sup>(1)</sup> (続き)

| 記号              | ピン番号 | 種類                      | 機能                                                                                  |

|-----------------|------|-------------------------|-------------------------------------------------------------------------------------|

| PWM1            | 41   | デジタル出力 (オープン<br>ドレイン)   | ファン制御出力 1。                                                                          |

| PWM2            | 42   | デジタル出力 (オープン<br>ドレイン)   | ファン制御出力 2。                                                                          |

| P1_VID0/P1_VID7 | 43   | デジタル入力                  | プロセッサからの電圧識別信号。TTL 入力ロジック レベルと AGTL 互換入力ロジック レベルをサポートしています。                         |

| P1_VID1         | 44   | デジタル入力                  | プロセッサからの電圧識別信号。TTL 入力ロジック レベルと AGTL 互換入力ロジック レベルをサポートしています。                         |

| P1_VID2         | 45   | デジタル入力                  | プロセッサからの電圧識別信号。TTL 入力ロジック レベルと AGTL 互換入力ロジック レベルをサポートしています。                         |

| P1_VID3         | 46   | デジタル入力                  | プロセッサからの電圧識別信号。TTL 入力ロジック レベルと AGTL 互換入力ロジック レベルをサポートしています。                         |

| P1_VID4         | 47   | デジタル入力                  | プロセッサからの電圧識別信号。TTL 入力ロジック レベルと AGTL 互換入力ロジック レベルをサポートしています。                         |

| P1_VID5         | 48   | デジタル入力                  | プロセッサからの電圧識別信号。TTL 入力ロジック レベルと AGTL 互換入力ロジック レベルをサポートしています。                         |

| P1_PROCHOT      | 49   | デジタル I/O (オープン<br>ドレイン) | 双方向レベル シフタ経由で CPU1 <b>PROCHOT</b> (プロセッサ ホット) 信号に接続されています。TTL 入力ロジック レベルをサポートしています。 |

| P2_PROCHOT      | 50   | デジタル I/O (オープン<br>ドレイン) | 双方向レベル シフタ経由で CPU2 <b>PROCHOT</b> (プロセッサ ホット) 信号に接続されています。TTL 入力ロジック レベルをサポートしています。 |

| P2_VID0/P2_VID7 | 51   | デジタル入力                  | プロセッサからの電圧識別信号。TTL 入力ロジック レベルと AGTL 互換入力ロジック レベルをサポートしています。                         |

| P2_VID1         | 52   | デジタル入力                  | プロセッサからの電圧識別信号。TTL 入力ロジック レベルと AGTL 互換入力ロジック レベルをサポートしています。                         |

| P2_VID2         | 53   | デジタル入力                  | プロセッサからの電圧識別信号。TTL 入力ロジック レベルと AGTL 互換入力ロジック レベルをサポートしています。                         |

| P2_VID3         | 54   | デジタル入力                  | プロセッサからの電圧識別信号。TTL 入力ロジック レベルと AGTL 互換入力ロジック レベルをサポートしています。                         |

| P2_VID4         | 55   | デジタル入力                  | プロセッサからの電圧識別信号。TTL 入力ロジック レベルと AGTL 互換入力ロジック レベルをサポートしています。                         |

| P2_VID5         | 56   | デジタル入力                  | プロセッサからの電圧識別信号。TTL 入力ロジック レベルと AGTL 互換入力ロジック レベルをサポートしています。                         |

(1) オーバースコアは、信号がアクティブ Low (Not) であることを示します。

#### 4.1 サーバーに関する用語

|       |                                              |

|-------|----------------------------------------------|

| A/D   | A/D コンバータ                                    |

| ACPI  | Advanced Configuration and Power Interface   |

| ALERT | 注意フラグが立てられたイベントが発生したことをバス マスターに通知する SMBus 信号 |

| ASF   | Alert Standard Format                        |

| BMC   | ベースボード管理コントローラ                               |

| BW    | 帯域幅                                          |

| DIMM  | デュアル インライン メモリ モジュール                         |

| DP    | デュアル プロセッサ                                   |

| ECC   | エラー チェックと訂正                                  |

| FRU   | 現場交換可能ユニット                                   |

| FSB   | フロント サイド バス                                  |

| FW    | ファームウェア                                      |

|                  |                                                                                                    |

|------------------|----------------------------------------------------------------------------------------------------|

| Gb               | ギガビット                                                                                              |

| GB               | ギガバイト                                                                                              |

| Gbe              | ギガビット イーサネット                                                                                       |

| GPI              | 汎用入力                                                                                               |

| GPIO             | 汎用 I/O                                                                                             |

| HW               | ハードウェア                                                                                             |

| I <sup>2</sup> C | 内部集積回路 (バス)                                                                                        |

| LAN              | ローカル エリア ネットワーク                                                                                    |

| LSb              | 最下位ビット                                                                                             |

| LSB              | 下位バイト                                                                                              |

| LVDS             | 低低電圧差動信号伝送                                                                                         |

| LUT              | ルックアップ テーブル                                                                                        |

| Mb               | メガビット                                                                                              |

| MB               | メガバイト                                                                                              |

| MP               | マルチプロセッサ                                                                                           |

| MSb              | 最上位ビット                                                                                             |

| MSB              | 最上位バイト                                                                                             |

| MTBF             | 平均故障間隔                                                                                             |

| MTTR             | 平均修復時間                                                                                             |

| NIC              | ネットワーク インターフェイス カード (イーサネット カード)                                                                   |

| OS               | オペレーティング システム                                                                                      |

| P/S              | 電源                                                                                                 |

| PCI              | PCI ローカル バス                                                                                        |

| PDB              | パワー ディストリビューション ボード                                                                                |

| POR              | パワーオン リセット                                                                                         |

| PS               | 電源                                                                                                 |

| SMBCLK と SMBDAT  | これらの信号は SMBus インターフェイスを構成しています (データおよびクロック)。詳細については、「 <a href="#">セクション 6.3.1</a> 」セクションを参照してください。 |

| VRD              | 電圧レギュレータ ダウン - CPU の V <sub>ccp</sub> 電圧を調整します。                                                    |

## 5 仕様

### 5.1 絶対最大定格

(1) (2) (3) を参照

|                                                                                                                   |            |                            |

|-------------------------------------------------------------------------------------------------------------------|------------|----------------------------|

| 正電源電圧 ( $V_{DD}$ )                                                                                                |            | 6.0V                       |

| デジタル入出力ピンの電圧                                                                                                      |            | -0.3V~6.0V                 |

| +5V 入力の電圧                                                                                                         |            | -0.3V~6.667V               |

| 正のリモート ダイオード入力、<br>AD_IN1 入力、AD_IN2 入力、<br>AD_IN3 入力、AD_IN15 入力の電圧                                                |            | -0.3V~(+ $V_{DD}$ + 0.05V) |

| 他のアナログ電圧入力の<br>電圧                                                                                                 |            | -0.3V~+6.0V                |

| サーマル ダイオード負入力の<br>入力電流                                                                                            |            | ±1 mA                      |

| すべてのピンの入力電流 (4)                                                                                                   |            | ±10mA                      |

| パッケージ入力電流 (4)                                                                                                     |            | ±100 mA                    |

| 最大接合部温度 (5)<br>( $T_{JMAX}$ )                                                                                     |            | 150 °C                     |

| ESD 感受性 (6)                                                                                                       | 人体モデル      | 3 kV                       |

|                                                                                                                   | マシン モデル    | 300V                       |

|                                                                                                                   | 荷電デバイス モデル | 750V                       |

| 保管温度(7)                                                                                                           |            | -65°C~+150°C               |

| ハンダ付け仕様については、 <a href="http://www.ti.com/packaging">www.ti.com/packaging</a> にあるプロダクト フォルダと SNOA549 を参照してください。(8) |            |                            |

- (1) 絶対最大定格は、それを超えるとデバイスに損傷を与える可能性がある制限値を示します。動作定格はデバイスが機能する条件を示しますが、特定の性能限界を保証するものではありません。保証された仕様および試験条件については、各電気的特性を参照してください。保証された仕様は、記載されているテスト条件にのみ適用されます。記載されているテスト条件で本デバイスを動作させないと、一部の性能特性が低下する可能性があります。

- (2) 特に記述のない限り、すべての電圧は GND を基準に測定されます。

- (3) 防衛または航空宇宙仕様のデバイスをお求めの場合は、供給状況および仕様についてテキサス・インスツルメンツの営業所または販売代理店にお問い合わせください。

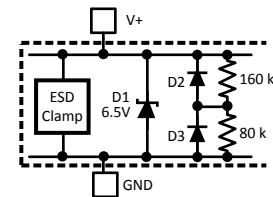

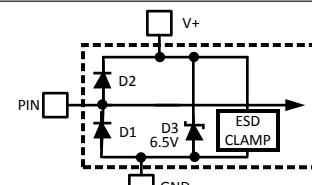

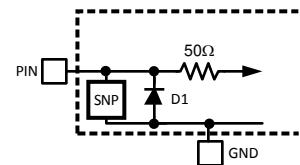

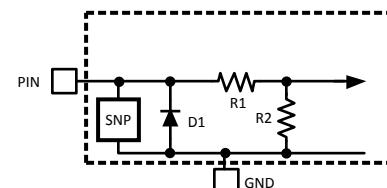

- (4) ピンの入力電圧 ( $V_{IN}$ ) が電源を超える場合 ( $V_{IN} < (GND$  または  $AGND$ ) または  $V_{IN} > V_{DD}$ 、アナログ電圧入力を除く)、そのピンの電流を 10mA に制限する必要があります。パッケージの最大入力電流定格が 100mA であるため、入力電流 10mA で電源を超えて問題を起さないピンの数は 10 本に制限されます。LM94 のピンの寄生部品および ESD 保護回路を以下に示します。回路 C と回路 D に示すように、ピン D+ とピン D- に存在する寄生ダイオード D1 が順バイアスされないように注意してください。50mV を超えるバイアスは、温度測定値を誤らせる可能性があります。D1 と ESD クランプは、回路 B に示すように、V+ ( $V_{DD}$ , AD\_IN16) と GND の間に接続されます。SNP は、スナップバック デバイスの略称です。

- (5) 標準的なパラメーターは  $T_J = T_A = 25^\circ\text{C}$  におけるもので、最も可能性の高いパラメータ基準値を表します。

- (6) 人体モデルでは、100pF が 1.5kΩ 抵抗経由で放電されます。マシン モデルでは、200pF が各ピンに直接放電されます。荷電デバイス モデル (CDM) は、ピンがゆっくりと電荷を帯び (自動アセンブラーのフィーダーを滑り落ちるデバイスなど)、その後急速に放電される様子をシミュレートします。

- (7) リフロー温度プロファイルは、鉛フリーと鉛フリー以外のパッケージでは異なります。

- (8) その他の推奨事項および、表面実装デバイスのハンダ付け方法については、URL <http://www.ti.com/packaging> を参照してください。

### 5.2 動作定格

(1) (2) を参照してください。

|                     |                                 |

|---------------------|---------------------------------|

|                     | $T_{MIN} \leq T_A \leq T_{MAX}$ |

| 動作温度範囲              | 0°C ≤ $T_A$ ≤ +85°C             |

| 公称電源電圧              | 3.3V                            |

| 電源電圧範囲 ( $V_{DD}$ ) | +3.0V~+3.6V                     |

| VID0-VID5           | -0.05V~+5.5V                    |

| デジタル入力電圧範囲          | -0.05V~(+ $V_{DD}$ + 0.05V)     |

(1) (2) を参照してください。

パッケージ熱抵抗

(3)

79°C/W

- (1) 絶対最大定格は、それらを超えるとデバイスに損傷を与える可能性がある制限値を示します。動作定格はデバイスが機能する条件を示しますが、特定の性能限界を保証するものではありません。保証された仕様および試験条件については、各電気的特性を参照してください。保証された仕様は、記載されているテスト条件にのみ適用されます。記載されているテスト条件で本デバイスを動作させないと、一部の性能特性が低下する可能性があります。

- (2) 特に記述のない限り、すべての電圧は GND を基準に測定されます。

- (3) 高温での最大電力散逸の定格を下げる必要があり、 $T_{JMAX}$ 、 $\theta_{JA}$ 、および周囲温度  $T_A$  により決定されます。任意の温度での最大許容電力散逸は、 $P_{D MAX} = (T_{JMAX} - T_A) / \theta_{JA}$  です。1 オンスの銅箔 PCB に取り付けた場合の LM94 の  $\theta_{JA}$  およびエアフローを変えた場合の  $\theta_{JA}$  を以下の表に示します。

| エアフロー               | 接合部から周囲への熱抵抗、 $\theta_{JA}$ |

|---------------------|-----------------------------|

| 0 m/s               | 79 °C/W                     |

| 1.14 m/s (225 LFPM) | 62 °C/W                     |

| 2.54 m/s (500 LFPM) | 52 °C/W                     |

### 5.3 DC 電気的特性

特に記述のない限り、以下の仕様は  $+3.0V_{DC}$ ~ $+3.6V_{DC}$  に適用されます。太字の制限値は動作範囲の  $T_{MIN}$ ~ $T_{MAX}$  にわたる  $T_A = T_J$  に適用されます。その他のすべての制限値は、特に記述のない限り、 $T_A = T_J = 25^\circ C$  に適用されます。 $T_A$  は LM94 の周囲温度、 $T_J$  は LM94 の接合部温度、 $T_D$  はサーマル・ダイオードの接合部温度です。

| パラメータ                | テスト条件                        | 標準値<br>(1) | 制限値<br>(2)  | 単位<br>(制限) |

|----------------------|------------------------------|------------|-------------|------------|

| <b>電源特性</b>          |                              |            |             |            |

| 電源電流                 | 変換、インターフェイスとファンが非アクティブ、ピーク電流 | 2          | <b>2.75</b> | mA (最大値)   |

|                      | 変換、インターフェイスとファンが非アクティブ、平均電流  | 1.6        |             | mA         |

| パワーオン リセットのスレッショルド電圧 |                              | 2          | <b>1.6</b>  | V (最小値)    |

|                      |                              |            | <b>2.7</b>  | V (最大値)    |

### 温度 / デジタル コンバータの特性

|                                                                            |                                                                                   |         |                             |          |

|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------|---------|-----------------------------|----------|

| 全範囲にわたるローカル温度精度                                                            | $0^\circ C \leq T_A \leq 85^\circ C$                                              | $\pm 2$ | <b><math>\pm 3</math></b>   | °C (最大値) |

|                                                                            | $T_A = +55^\circ C$                                                               | $\pm 1$ | <b><math>\pm 2.5</math></b> | °C (最大値) |

| ローカル温度分解能                                                                  |                                                                                   | 1       |                             | °C       |

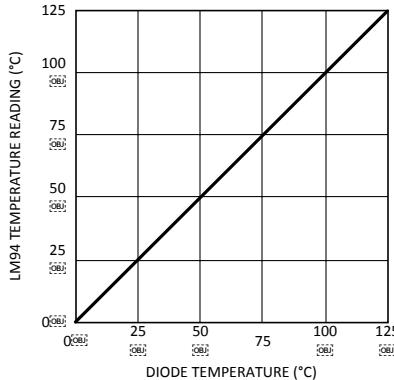

| 全範囲にわたるリモート サーマル ダイオード温度精度、<br>90nm または 65nm プロセスの標準的な Pentium プロセッサ向け (3) | $0^\circ C \leq T_A \leq 85^\circ C$<br>および $0^\circ C \leq T_D \leq 100^\circ C$ |         | <b><math>\pm 3</math></b>   | °C (最大値) |

|                                                                            | $0^\circ C \leq T_A \leq 85^\circ C$<br>および $T_D = 70^\circ C$                    |         | <b><math>\pm 2.5</math></b> | °C (最大値) |

| リモート サーマル ダイオード温度精度、90nm または<br>65nm プロセスの標準的な Pentium プロセッサが向け (3)        | $0^\circ C \leq T_A \leq 85^\circ C$<br>および $25^\circ C \leq T_D \leq 70^\circ C$ | $\pm 1$ |                             | °C       |

| リモート温度分解能                                                                  |                                                                                   | 1       |                             | °C       |

| サーマル ダイオードソース電流                                                            | 高レベル                                                                              | 172     | <b>230</b>                  | μA (最大値) |

|                                                                            | 低レベル                                                                              | 10.75   |                             | μA       |

| サーマル ダイオードの電流比                                                             |                                                                                   | 16      |                             |          |

| $T_C$                                                                      | 総監視サイクル時間                                                                         |         | <b>100</b>                  | ms (最大値) |

### A/D 電圧測定コンバータの特性

|     |                 |  |  |                           |              |

|-----|-----------------|--|--|---------------------------|--------------|

| TUE | 総合未調整誤差 (4) (5) |  |  | <b><math>\pm 2</math></b> | FS の % (最大値) |

|-----|-----------------|--|--|---------------------------|--------------|

### 5.3 DC 電気的特性 (続き)

特に記述のない限り、以下の仕様は  $+3.0V_{DC}$ ~ $+3.6V_{DC}$  に適用されます。太字の制限値は動作範囲の  $T_{MIN}$ ~ $T_{MAX}$  にわたる  $T_A = T_J$  に適用されます。その他のすべての制限値は、特に記述のない限り、 $T_A = T_J = 25^\circ C$  に適用されます。 $T_A$  は LM94 の周囲温度、 $T_J$  は LM94 の接合部温度、 $T_D$  はサーマル・ダイオードの接合部温度です。

| パラメータ                                                                                                   |                                                          | テスト条件                                   | 標準値<br><sup>(1)</sup>     | 制限値<br><sup>(2)</sup>                                            | 単位<br>(制限)          |

|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------------------------------------|---------------------------|------------------------------------------------------------------|---------------------|

| DNL                                                                                                     | 微分非直線性                                                   |                                         | <b><math>\pm 1</math></b> |                                                                  | LSB                 |

| PSS                                                                                                     | 電源 ( $V_{DD}$ ) 感度                                       |                                         | <b><math>\pm 1</math></b> |                                                                  | %/V (FS に対する)       |

| $T_C$                                                                                                   | 総監視サイクル時間                                                |                                         |                           | <b>100</b>                                                       | ms (最大値)            |

|                                                                                                         | 分圧抵抗を用いた入力の入力抵抗                                          |                                         | 200                       | <b>140</b>                                                       | k $\Omega$ (最小値)    |

|                                                                                                         | AD_IN1~AD_IN3 および AD_IN15 のアナログ入力一<br>ヶ電流 <sup>(6)</sup> |                                         |                           | 60                                                               | nA (最大値)            |

| リファレンス出力 ( $V_{REF}$ ) の特性                                                                              |                                                          |                                         |                           |                                                                  |                     |

|                                                                                                         | 精度                                                       |                                         |                           | <b><math>\pm 1</math></b>                                        | % (最大値)             |

| $V_{REF}$                                                                                               | 出力電圧 <sup>(7)</sup>                                      |                                         | 2.500                     | <b>2.525</b><br><b>2.475</b>                                     | V (最大値)<br>V (最小値)  |

|                                                                                                         | ロード レギュレーション                                             | $I_{SOURCE} = -2mA$<br>$I_{SINK} = 2mA$ | 0.1                       |                                                                  | %                   |

| デジタル出力: PWM1、PWM2                                                                                       |                                                          |                                         |                           |                                                                  |                     |

| $I_{OL}$                                                                                                | 最大電流シンク                                                  |                                         |                           | <b>8</b>                                                         | mA (最小値)            |

| $V_{OL}$                                                                                                | 出力 LOW 電圧                                                | $I_{OUT} = 8.0 \text{ mA}$              |                           | <b>0.4</b>                                                       | V (最大値)             |

| デジタル出力:すべて                                                                                              |                                                          |                                         |                           |                                                                  |                     |

| $V_{OL}$                                                                                                | 出力低電圧 (過度の電流が流れると、自己発熱を引き起こし、内部温度精度が低下させるので注意すること。)      | $I_{OUT} = 4.0 \text{ mA}$              |                           | <b>0.4</b>                                                       | V (最小値)             |

|                                                                                                         |                                                          | $I_{OUT} = 6 \text{ mA}$                |                           | <b>0.55</b>                                                      | V (最小値)             |

| $I_{OH}$                                                                                                | High レベル出力一ヶ電流                                           | $V_{OUT} = V_{DD}$                      | 0.1                       | <b>10</b>                                                        | $\mu\text{A}$ (最大値) |

| $I_{OTMAX}$                                                                                             | すべてのデジタル出力の最大合計シンク電流                                     |                                         |                           | <b>32</b>                                                        | mA (最大値)            |

| $C_O$                                                                                                   | デジタル出力容量                                                 |                                         | 20                        |                                                                  | pF                  |

| デジタル入力:すべて                                                                                              |                                                          |                                         |                           |                                                                  |                     |

| $V_{IH}$                                                                                                | アドレス選択を除く入力高電圧 <sup>(8)</sup>                            |                                         |                           | <b>2.1</b>                                                       | V (最小値)             |

| $V_{IL}$                                                                                                | アドレス選択を除く入力低電圧 <sup>(8)</sup>                            |                                         |                           | <b>0.8</b>                                                       | V (最大値)             |

| $V_{IH}$                                                                                                | アドレス選択の入力高電圧 <sup>(8)</sup>                              |                                         |                           | <b>90% <math>V_{DD}</math></b>                                   | V (最小値)             |

| $V_{IM}$                                                                                                | アドレス選択の入力中電圧                                             |                                         |                           | <b>43% <math>V_{DD}</math></b><br><b>57% <math>V_{DD}</math></b> | V (最小)<br>V (最大)    |

| $V_{IL}$                                                                                                | アドレス選択の入力低電圧 <sup>(8)</sup>                              |                                         |                           | <b>10% <math>V_{DD}</math></b>                                   | V (最大値)             |

| $V_{HYST}$                                                                                              | DC ヒステリシス                                                |                                         | 0.3                       |                                                                  | V                   |

| $I_{IH}$                                                                                                | 入力高電流                                                    | $V_{IN} = V_{DD}$                       |                           | <b>-10</b>                                                       | $\mu\text{A}$ (最小値) |

| $I_{IL}$                                                                                                | 入力低電流                                                    | $V_{IN} = 0V$                           |                           | <b>10</b>                                                        | $\mu\text{A}$ (最大値) |

| $C_{IN}$                                                                                                | デジタル入力容量                                                 |                                         | 20                        |                                                                  | pF                  |

| デジタル入力: P1_VIDx、P2_VIDx、GPI_9、GPI_8、GPIO_7、GPIO_6、GPIO_5、GPIO_4 (レジスタ BEh GPI/VID レベル制御の各ビットが設定されている場合) |                                                          |                                         |                           |                                                                  |                     |

| $V_{IH}$                                                                                                | 代替入力高電圧 (AGTL+ 対応)                                       |                                         |                           | <b>0.8</b>                                                       | V (最小値)             |

### 5.3 DC 電気的特性 (続き)

特に記述のない限り、以下の仕様は  $+3.0V_{DC} \sim +3.6V_{DC}$  に適用されます。太字の制限値は動作範囲の  $T_{MIN} \sim T_{MAX}$  にわたる  $T_A = T_J$  に適用されます。その他のすべての制限値は、特に記述のない限り、 $T_A = T_J = 25^\circ C$  に適用されます。 $T_A$  は LM94 の周囲温度、 $T_J$  は LM94 の接合部温度、 $T_D$  はサーマル・ダイオードの接合部温度です。

| パラメータ    | テスト条件              | 標準値<br>(1) | 制限値<br>(2) | 単位<br>(制限) |

|----------|--------------------|------------|------------|------------|

| $V_{IL}$ | 代替入力低電圧 (AGTL+ 対応) |            | <b>0.4</b> | V (最大値)    |

- (1) 標準的なパラメーターは  $T_J = T_A = 25^\circ C$  におけるもので、最も可能性の高いパラメータ基準値を表します。

- (2) 制限値はテキサス・インスツルメンツの平均出検品質限界 (AOQL) で規定されています。

- (3) 本仕様の初版公開時点 (2006 年 1 月) では、TruTherm を選択した場合、90nm または 65nm プロセスの Pentium または Xeon プロセッサに適用されます。TruTherm を選択しない場合、本仕様は MMBT3904 に適用されます。この仕様には、ダイオードの理想性と直列抵抗パラメータのばらつきに起因する誤差が含まれています。

- (4) 総監視サイクル時間には、すべての温度と電圧の変換が含まれます。

- (5) TUE (総合未調整誤差) には、ADC のオフセット、ゲイン、および直線性の誤差が含まれます。

- (6) リーク電流は  $20^\circ C$ ごとに約 2 倍になります。

- (7) 40mA の合計デジタル I/O 電流は、 $V_{ref}$  に 6mV のオフセットを引き起こす可能性があります。

- (8) タイミング仕様は、TTL ロジックレベル、立ち下がりエッジでは  $V_{IL} = 0.4V$ 、立ち上がりエッジでは  $V_{IH} = 2.4V$  でテストされます。TRI-STATE 出力電圧は強制的に 1.4V になります。

## 5.4 AC 電気的特性

特に記述のない限り、以下の仕様は  $+3.0V_{DC} \sim +3.6V_{DC}$  に適用されます。太字の制限値は動作範囲の  $T_A = T_J = T_{MIN} \sim T_{MAX}$  に適用されます。その他すべての制限値は、特に記述のない限り、 $T_A = T_J = 25^\circ C$  に適用されます。

| パラメータ                     | テスト条件                                               | 標準値<br><sup>(1)</sup> | 制限値<br><sup>(2)</sup>     | 単位<br>(制限)           |

|---------------------------|-----------------------------------------------------|-----------------------|---------------------------|----------------------|

| <b>ファン RPM からデジタルへの特性</b> |                                                     |                       |                           |                      |

| カウンタ分解能                   |                                                     | 14                    |                           | ビット                  |

| ファン タコメータ パルス数に基づく        |                                                     | 2                     |                           | パルス                  |

| カウンタ周波数                   |                                                     | 22.5                  |                           | kHz                  |

| 精度                        |                                                     |                       | <b>±6</b>                 | % (最大値)              |

| <b>PWM 出力の特性</b>          |                                                     |                       |                           |                      |

| 周波数の許容誤差                  |                                                     |                       | <b>±6</b>                 | % (最大値)              |

| デューティ サイクルの許容誤差           |                                                     | <b>±2</b>             | <b>±6</b>                 | % (最大値)              |

| <b>リセット入力 / 出力の特性</b>     |                                                     |                       |                           |                      |

| 電源オン時の出力パルス幅              |                                                     |                       | <b>250</b><br><b>330</b>  | ms (最小値)<br>ms (最大値) |

| 最小入力パルス幅                  |                                                     |                       | <b>10</b>                 | μs (最小値)             |

| リセット出力立ち下がり時間             | 1.6V ~ 0.4V のロジック レベル                               |                       | <b>1</b>                  | μs (最大値)             |

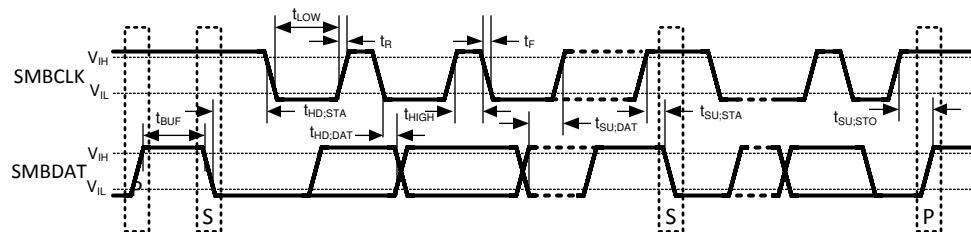

| <b>SMBus タイミングの特性</b>     |                                                     |                       |                           |                      |

| $t_{SMBCLK}$              | SMBCLK (クロック) クロック周波数                               |                       | <b>10</b><br><b>100</b>   | kHz (最小)<br>kHz (最大) |

| $t_{BUF}$                 | STOP 条件と START 条件間の SMBus 解放時間                      |                       | <b>4.7</b>                | μs (最小値)             |

| $t_{HD;STA}$              | (繰り返し) START 条件の後のホールド時間。この期間が経過した後、最初のクロックが生成されます。 |                       | <b>4.0</b>                | μs (最小値)             |

| $t_{SU;STA}$              | 繰り返し START 条件のセットアップ時間                              |                       | <b>4.7</b>                | μs (最小値)             |

| $t_{SU;STO}$              | STOP 条件のセットアップ時間                                    |                       | <b>4.0</b>                | μs (最小値)             |

| $t_{SU;DAT}$              | SMBCLK が High になるまでのデータ入力のセットアップ時間                  |                       | <b>250</b>                | ns (最小値)             |

| $t_{HD;DAT}$              | SMBCLK が Low になった後のデータ出力ホールド時間                      |                       | <b>300</b><br><b>1075</b> | ns (最小値)<br>ns (最大値) |

| $t_{LOW}$                 | SMBCLK Low 期間                                       |                       | <b>4.7</b><br><b>50</b>   | μs (最小値)<br>μs (最大値) |

| $t_{HIGH}$                | SMBCLK High 期間                                      |                       | <b>4.0</b><br><b>50</b>   | μs (最小値)<br>μs (最大値) |

| $t_R$                     | 立ち上がり時間                                             |                       | <b>1</b>                  | μs (最大値)             |

特に記述のない限り、以下の仕様は  $+3.0V_{DC} \sim +3.6V_{DC}$  に適用されます。太字の制限値は動作範囲の  $T_A = T_J = T_{MIN} \sim T_{MAX}$  に適用されます。その他すべての制限値は、特に記述のない限り、 $T_A = T_J = 25^\circ\text{C}$  に適用されます。

| パラメータ         |                                                                            | テスト条件            | 標準値<br>(1) | 制限値<br>(2)             | 単位<br>(制限)                 |

|---------------|----------------------------------------------------------------------------|------------------|------------|------------------------|----------------------------|

| $t_f$         | 立ち下がり時間                                                                    |                  |            | <b>300</b>             | ns (最大値)                   |

| $t_{TIMEOUT}$ | シリアルバスインターフェイスをアイドル状態にリセットするために必要な、SMBCLK または SMBDAT が Low になっている時間のタイムアウト |                  | 31         | <b>25</b><br><b>35</b> | ms<br>ms (最小値)<br>ms (最大値) |

| $t_{POR}$     | パワーオンリセット後にデバイスが動作可能な状態になるまでの時間                                            | $V_{DD} > +2.8V$ |            | <b>500</b>             | ms (最大値)                   |

| $C_L$         | SMBCLK および SMBDAT の容量性負荷                                                   |                  |            | <b>400</b>             | pF (最大値)                   |

(1) 標準的なパラメーターは  $T_J = T_A = 25^\circ\text{C}$  におけるもので、最も可能性の高いパラメータ基準値を表します。

(2) 制限値はテキサス・インスツルメンツの平均出検品質限界 (AOQL) で規定されています。

| 記号                    | ピン番号 | 回路                | すべての入力回路 |

|-----------------------|------|-------------------|----------|

| GPIO_0/TACH1          | 1    | A                 |          |

| GPIO_1/TACH2          | 2    | A                 |          |

| GPIO_2/TACH3          | 3    | A                 |          |

| GPIO_3/TACH4          | 4    | A                 |          |

| GPIO_4 / P1_THERMTRIP | 5    | A                 |          |

| GPIO_5 / P2_THERMTRIP | 6    | A                 |          |

| GPIO_6                | 7    | A                 |          |

| GPIO_7                | 8    | A                 |          |

| VRD1_HOT              | 9    | A                 |          |

| VRD2_HOT              | 10   | A                 |          |

| SCSI_TERM1            | 11   | A                 |          |

| SCSI_TERM2            | 12   | A                 |          |

| SMBDAT                | 13   | A                 |          |

| SMBCLK                | 14   | A                 |          |

| ALERT/XtestOut        | 15   | A                 |          |

| RESET                 | 16   | A                 |          |

| AGND                  | 17   | B (内部で GND ピンに短絡) |          |

| $V_{REF}$             | 18   | A                 |          |

| REMOTE1-              | 19   | C                 |          |

| REMOTE1+              | 20   | D                 |          |

| REMOTE2-              | 21   | C                 |          |

| REMOTE+               | 22   | D                 |          |

図 5-1. 回路 A

図 5-2. 回路 B

| 記号                                        | ピン番号 | 回路               | すべての入力回路 |

|-------------------------------------------|------|------------------|----------|

| AD_IN1                                    | 23   | D                |          |

| AD_IN2                                    | 24   | D                |          |

| AD_IN3                                    | 25   | D                |          |

| AD_IN4                                    | 26   | E                |          |

| AD_IN5                                    | 27   | E                |          |

| AD_IN6                                    | 28   | E                |          |

| AD_IN7                                    | 29   | E                |          |

| AD_IN8                                    | 30   | E                |          |

| AD_IN9                                    | 31   | E                |          |

| AD_IN10                                   | 32   | E                |          |

| AD_IN11                                   | 33   | E                |          |

| AD_IN12                                   | 34   | E                |          |

| AD_IN13                                   | 35   | E                |          |

| AD_IN14                                   | 36   | E                |          |

| AD_IN15                                   | 37   | D                |          |

| ADDR_SEL                                  | 38   | A                |          |

| AD_IN16/V <sub>DD</sub> (V <sub>+</sub> ) | 39   | B                |          |

| GND                                       | 40   | B (内部でAGNDピンに短絡) |          |

| PWM1                                      | 41   | A                |          |

| PWM2                                      | 42   | A                |          |

| P1_VID0                                   | 43   | A                |          |

| P1_VID1                                   | 44   | A                |          |

| P1_VID2                                   | 45   | A                |          |

| P1_VID3                                   | 46   | A                |          |

| P1_VID4                                   | 47   | A                |          |

| P1_VID5                                   | 48   | A                |          |

| P1_PROCHOT                                | 49   | A                |          |

| P2_PROCHOT                                | 50   | A                |          |

| P2_VID0                                   | 51   | A                |          |

| P2_VID1                                   | 52   | A                |          |

| P2_VID2                                   | 53   | A                |          |

| P2_VID3                                   | 54   | A                |          |

| P2_VID4                                   | 55   | A                |          |

| P2_VID5                                   | 56   | A                |          |

図 5-3. 回路 C

図 5-4. 回路 D

図 5-5. 回路 E

## 6 詳細説明

### 6.1 概要

LM94 では、16 チャネルの電圧監視、4 つのリモート サーマル ダイオード モニタ、内部 / ローカル周囲温度センサ、2 つの PROCHOT モニタ、4 つのファン タコメータ、8 つの GPIO、エラー イベントのマスク用 THERMTRIP モニタ、2 セットの 7 VID 入力、ALERT 出力、および関連するすべての制限レジスタが 1 つのチップに搭載されており、システム管理バス (SMBus) 経由でベースボードの他の部分と通信します。また、LM94 は 2 つの PWM 出力と関連するファン制御ロジックも搭載しており、システム ファンの速度を制御できます。ファン制御ロジックには、ルックアップ テーブルと PI (比例 / 積分) ループ コントローラの 2 つがあります。ルックアップ テーブルと PI コントローラは対話型であるため、ファンは必要な最高速度で動作します。温度やファン タコメータのエラー イベントが発生すると、PWM 出力は自動的にデューティサイクルを 100% に昇圧するようにプログラムすることができます。ファン タコメータ エラーが発生したときにファンが昇圧状態になる最小時間を設定するタイマが内蔵されています。

LM94 はテキサス・インスツルメンツの TruTherm 技術を採用しており、90nm プロセス以下のプロセッサの高精度なリモートダイオードの読み取りしが可能です。外付けサーマル ダイオードと内蔵温度センサの読み取り値は、LSb が 0.5°C の 9 ビットの 2 の補数デジタル値として、フィルタ温度読み取り値は、LSb が 0.0625°C の 12 ビットの 2 の補数デジタル値として表示されます。

4 つを除くすべてのアナログ入力には、内部スケーリング抵抗が含まれています。 $\pm 12V$  を測定するには、外部スケーリング抵抗が必要です。入力は 8 ビットのデジタル値に変換され、正の電圧では  $\frac{3}{4}$  スケール、負の電圧では  $\frac{1}{4}$  スケールで公称電圧が表示されます。アナログ入力は、ベースボードに常駐する VRD と、SSI 準拠の電源から供給される標準的な電圧レールの両方に接続することを想定しています。

LM94 は、動的に変動する一連の VID 入力を関連する Vccp アナログ入力に接続し、リアルタイムでウインドウ比較を行い、故障判定を行うロジックを備えています。VRD10、VRD10 拡張、VRD11 の電圧マッピングは、LM94 によってサポートされています。VRD10 モードが選択されている場合、GPI8 と GPI9 を使用して外部エラー フラグを検出でき、その状態はステータス レジスタに反映されます。

エラー イベントは、ミラー化された 2 セットのステータス レジスタ (BMC エラー ステータス レジスタとホスト ステータス レジスタ) にキャプチャされるため、2 つのコントローラが干渉することなくステータス情報にアクセスできます。

LM94 の ALERT 出力は、割り込みモードまたはコンパレータ モードの動作をサポートしています。コンパレータ モードは熱監視のみに機能するものです。

LM94 には多数の内部レジスタが用意されています。詳細については本書の「[セクション 6.4](#)」セクションを参照してください。

### 6.2 機能説明

#### 6.2.1 監視サイクル時間

LM94 は電源供給されると、各温度測定の後にアナログ電圧測定が順番に繰り返され、それが連続的にループします。総監視サイクル時間は、ほとんどの外部マイクロコントローラがレジスタ値を読み出すのに必要な時間であるため、100ms 以下です。

各測定値は、制限レジスタに格納されている値と比較されます。測定値がプログラムされた制限に反すると、B\_Error ステータス レジスタおよび H\_Error ステータス レジスタの対応するステータス ビットが設定されます。

PROCHOT、タコメータ、および動的 VID/Vccp 監視は、アナログおよび温度の監視サイクルとは無関係に実行されます。

#### 6.2.2 $\Sigma\Delta$ A/D 固有の平均化

$\Sigma\Delta$  A/D アーキテクチャは、入力信号をフィルタ処理します。1 回の変換中に入力電圧の多くのサンプルが取得され、これらのサンプルが実質的に平均化されて最終的な結果が得られます。 $\Sigma\Delta$  A/D の出力は、サンプリング間隔中の信号の平均値です。電圧測定の場合、サンプルは 1.5ms の間蓄積されます。温度測定の場合、サンプルは 8.4ms の間蓄積されます。

### 6.2.3 温度監視

LM94 のリモート ダイオードの対象となるのは、90nm プロセスの **Xeon** クラス プロセッサに搭載されている組み込みサーマル ダイオードですが、90nm または 65nm プロセスの **Intel** ベース プロセッサでも動作します。LM94 は、テキサス・インスツルメンツの **TruTherm** 技術を採用した高度なサーマル ダイオード入力段を備えており、サブミクロン対応ジオメトリのサーマル ダイオードで見られる理想性のばらつきを低減できます。サーマル ダイオード入力段には内部アナログ フィルタリングが組み込まれているため、外付けサーマル ダイオード フィルタ コンデンサの必要性を最小限に抑えることができます。さらに、サーマル ダイオード温度読み取り用にデジタル フィルタが搭載されています。

場合によっては、**Xeon** プロセッサに搭載されている組み込みサーマル ダイオードを使用する代わりに、ダイオード接続の **2N3904** トランジスタ タイプを使用することもできます。例としては、コレクタとベースがサーマル ダイオードの **REMOTE+** ピンに、エミッタがサーマル ダイオードの **REMOTE-** ピンに接続された **MMBT3904** があります。**MMBT3904** は表面実装デバイスであり、熱質量が非常に小さいため、実装されているボードの温度が測定されます。理想性と直列抵抗は、ダイオードによって異なります。そのため、LM94 には **2N3904** または **Xeon** プロセッサの間でキャリブレーションを選択できるレジスタ サポートがあります。LM94 は、90nm または 65nm プロセスの一般的な **Intel** プロセッサや **2N3904** トランジスタ用に最適化されています。他のタイプのトランジスタを使用することもできますが、さらにエラーが発生する可能性があり、その場合は適切なゾーン調整オフセット レジスタをプログラムすることで修正することができます。

LM94 は、4 つの異なるソースから温度データを収集します。

- 4 つの外付けダイオード (プロセッサに組み込みまたはディスクリート)

- 1 つの内蔵ダイオード (LM94 に内蔵)

- AD\_IN11 ピンまたは AD\_15 ピンに接続された LM60 などの 2 つのアナログ温度センサ

- 温度値は、**SMBus** から LM94 レジスタに外部から書き込むことができます。

これらの値はすべて、同時である必要はありませんが、ファンの制御や制限値との比較などに使用できます。

温度値レジスタは、アドレス 06h-09h、50h-55h、10h-23h にあります。便宜上、温度ソースはゾーンと呼ばれています。

| ゾーン     | 説明                                                                             |

|---------|--------------------------------------------------------------------------------|

| ゾーン 1a  | プロセッサ 1 リモート ダイオード 1<br>(REMOTE1a+、REMOTE1-)                                   |

| Zone 1b | プロセッサ 1 リモート ダイオード 2<br>(REMOTE1b+、REMOTE1-)                                   |

| ゾーン 2a  | プロセッサ 2 リモート ダイオード 1<br>(REMOTE2a+、REMOTE2-)                                   |

| Zone 2b | プロセッサ 2 リモート ダイオード 2<br>(REMOTE2b+、REMOTE2-)                                   |

| ゾーン 3   | 内蔵 LM94 オンチップ センサまたは外付け LM60 アナログ センサを AD_IN11 に接続し、 <b>SMBus</b> 経由の書き込みも受け入れ |

| ゾーン 4   | 外部デジタル温度値は <b>SMBus</b> のレジスタへの書き込み 53h による、または外付け LM60 アナログセンサーを AD_IN15 に接続  |

#### 6.2.3.1 リモート ダイオードの **TruTherm** モード

プロセッサのリモート サーマル ダイオードは、より正確にはトランジスタであると言えます。LM93 ではリモート ダイオードをダイオードとして扱っていたため、精度に誤差が生じていました。これらの誤差は、プロセッサのジオメトリが微細化するにつれてより顕著になっています。LM94 は、リモート デバイスをトランジスタとして扱う新しい **TruTherm** 技術を採用することで、リモート ダイオードをセンスできます。**TruTherm** モードは、90nm 以下のジオメトリのプロセッサに対してより高い精度を発揮します。LM94 は引き続き従来のダイオード方式をサポートしており、**2N3904** トランジスタ タイプ用に較正されています。

### 6.2.3.2 溫度データの形式

LM94 の温度データのほとんどは、次の 3 つの形式で表されます。

- 8 ビットの 2 の補数バイトで、LSb は  $1.0^{\circ}\text{C}$  に等しい形式です。これは温度測定だけでなく、温度制限レジスタや一部の構成レジスタにも適用されます。

| 温度 <sup>(1)</sup> | 2 進       | 16 進 |

|-------------------|-----------|------|

| +125°C            | 0111 1101 | 7Dh  |

| +25°C             | 0001 1001 | 19h  |

| +1.0°C            | 0000 0001 | 01h  |

| 0°C               | 0000 0000 | 00h  |

| -1.0°C            | 1111 1111 | FFh  |

| -25°C             | 1110 0111 | E7h  |

| -55°C             | 1100 1001 | C9h  |

| -127°C            | 1000 0001 | 81h  |

(1) 値 80h は制限レジスタで特別な意味を持ち、温度チャネルがマスクされていることを示します。他にも、80h の温度読み取り値はサーマル ダイオード フォルトを示します。

- 9 ビットの 2 の補数ワードで、LSb は  $0.5^{\circ}\text{C}$  に等しい形式です。これはフィルタなし温度測定拡張分解能値レジスタに適用されます。

| 温度       | 2 進       |           | 16 進   |

|----------|-----------|-----------|--------|

|          | MSB       | LSB       |        |

| +125.5°C | 0111 1101 | 1000 0000 | 7D 80h |

| +25.5°C  | 0001 1001 | 1000 0000 | 19 80h |

| +0.5°C   | 0000 0000 | 1000 0000 | 00 80h |

| 0°C      | 0000 0000 | 0000 0000 | 00 00h |

| -0.5°C   | 1111 1111 | 1000 0000 | FF 80h |

| -25.5°C  | 1110 0111 | 1000 0000 | E7 80h |

| -55.5°C  | 1100 1001 | 1000 0000 | C9 80h |

| -127.5°C | 1000 0001 | 1000 0000 | 81 80h |

- 12 ビットの 2 の補数ワードで、LSb は  $0.0625^{\circ}\text{C}$  に等しい形式です。これは拡張フィルタ温度測定拡張分解能値レジスタに適用されます。

| 温度          | 2 進       |           | 16 進   |

|-------------|-----------|-----------|--------|

|             | MSB       | LSB       |        |

| +125.0625°C | 0111 1101 | 0001 0000 | 7D 10h |

| +25.0625°C  | 0001 1001 | 0001 0000 | 19 10h |

| +1.0625°C   | 0000 0001 | 0001 0000 | 01 10h |

| 0°C         | 0000 0000 | 0000 0000 | 00 00h |

| -0.0625°C   | 1111 1111 | 1111 0000 | FF F0h |

| -25.0625°C  | 1110 0111 | 1111 0000 | E7 F0h |

| -55.0625°C  | 1100 1001 | 1111 0000 | C9 F0h |

| -127.0625°C | 1000 0000 | 1111 0000 | 80 F0h |

ファン制御構成レジスタの中には、4ビットを使用し、符号なしバイナリ形式のものがあります。この4ビット形式の詳細については、「[セクション 6.2.18](#)」の構成レジスタの説明を参照してください。

### 6.2.3.3 サーマルダイオード フォルトステータス

LM94 は、リモートサーマルダイオードを使用してフォルト(開路または短絡)を示します。リモートダイオード変換が更新される前に、リモートダイオードのステータスは、開路または短絡の状態であるかどうかチェックされます。このようなフォルト状態が発生した場合、ステータスレジスタにステータスビットが設定されます。短絡とは、ダイオードピンが相互に接続されている状態を指します。開路または短絡が検出されると、対応する温度レジスタが 80h に設定されます。

### 6.2.4 ファン昇圧のイベントエラー

温度昇圧エラーイベントやタコメータエラーイベントにより、ファン制御 PWM 出力がフルオンになる可能性があります。温度昇圧エラーイベントが発生すると、両方の PWM 出力がフルオンになり、タコメータイベントが PWM1 または PWM2 にバインディングされる可能性があります。

4つの温度ゾーンのいずれかがそのゾーンの温度のファン昇圧制限を超えると、ファン昇圧温度イベントが発生します。温度が昇圧制限を超えた場合、昇圧制限から昇圧ヒステリシスを引いた値まで下がらなければ、昇圧状態は無効となりません。ゾーン 1 とゾーン 2 のデフォルト設定は 60°C で、ゾーン 3 とゾーン 4 のデフォルト設定は 35°C です。

タコメータエラー昇圧機能は、タコメータファン昇圧制御レジスタを介して有効になります。PWM バインディングビットに対するタコメータの設定に応じて、マスクされていないファンタコメータエラーイベントが検出されると、PWM 出力の 1つまたは両方が 100% デューティサイクルになります。タコメータ読み取り値がそのファンタコメータ制限レジスタで設定された値を超えると、ファンタコメータエラーイベントが発生します。エラーイベントが終了すると、PWM 出力は、タコメータファン昇圧制御レジスタにプログラムされたタコメータ昇圧タイムアウトの間、100% のデューティサイクルを維持します。このタイムアウトの途中でタコメータエラーイベントが再発した場合、タコメータ昇圧タイムアウトの時間間隔はリセットされ、エラーイベントが終了すると再開されます。

### 6.2.5 電圧監視

LM94 には、電圧監視のための入力があります。スケーリングは、 $\pm 12V$  を除くすべての入力で、正しい値がおよそ 3/4 スケールまたは 10 進数で 192 を指すようになっています。スケーリングは、 $\pm 12V$  を除く内部分圧抵抗を使用して実現されます。これらの入力の標準的な入力抵抗は  $200k\Omega$  です。入力電圧は、8ビットのデルタシグマ ( $\Delta\Sigma$ ) A/D によって変換されます。デルタシグマ A/D アーキテクチャは、アナログ入力信号の固有のフィルタリングとスパイク平滑化を実現します。

$\pm 12V$  入力は、外部でスケーリングする必要があります。これらの入力に  $1.236V$  を印加すると、フルスケールの読み出しが行われます。最適な性能を得るには、 $+12V$  は公称  $\frac{3}{4}$  フルスケールの読み出しが行われるようにスケーリングし、 $-12V$  は公称  $\frac{1}{4}$  スケールの読み出しが行われるようにスケーリングする必要があります。ピンのテブナン抵抗は、 $1k\Omega$  ~  $7k\Omega$  の間に維持する必要があります。

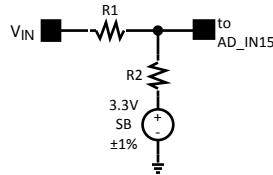

$-12V$  の監視は難易度が高いです。外部オフセット電圧と外付け抵抗を使用して、 $-12V$  レールを AD 入力の正の入力電圧領域にすることが必要です。LM94 デバイスの電源レールをオフセット電圧として使用することを推奨します。この電圧は通常、 $\pm 1\%$  精度のリニアレギュレータを経由して、P/S 5V のスタンバイ電圧レールから導出されます。3.3V のスタンバイ電圧が存在しないとシステムをオンにできないため、この方法では、 $-12V$  レールが存在するときにオフセット電圧が存在すると仮定できます。

表 6-1. 電圧とレジスタ読み出しの関係

| ピン     | 通常使用    | 公称電圧   | 公称電圧でのレジスタ読み出し | 最大電圧   | 最大電圧でのレジスタ読み出し | 最小電圧 | 最小電圧でのレジスタ読み出し | 絶対最大範囲                      |

|--------|---------|--------|----------------|--------|----------------|------|----------------|-----------------------------|

| AD_IN1 | +12V1   | 0.927V | C0h            | 1.236V | FFh            | 0V   | 00h            | -0.3V~( $+V_{DD} + 0.05V$ ) |

| AD_IN2 | +12V2   | 0.927V | C0h            | 1.236V | FFh            | 0V   | 00h            | -0.3V~( $+V_{DD} + 0.05V$ ) |

| AD_IN3 | +12V3   | 0.927V | C0h            | 1.236V | FFh            | 0V   | 00h            | -0.3V~( $+V_{DD} + 0.05V$ ) |

| AD_IN4 | FSB_Vtt | 1.20V  | C0h            | 1.60V  | FFh            | 0V   | 00h            | -0.3V~+6.0V                 |

表 6-1. 電圧とレジスタ読み出しの関係 (続き)

| ピン      | 通常<br>使用  | 公称<br>電圧 | 公称電圧で<br>の<br>レジスタ<br>読み出し | 最大<br>電圧 | 最大電圧で<br>の<br>レジスタ<br>読み出し | 最小<br>電圧 | 最小電圧で<br>の<br>レジスタ<br>読み出し | 絶対<br>最大<br>範囲                   |

|---------|-----------|----------|----------------------------|----------|----------------------------|----------|----------------------------|----------------------------------|

| AD_IN5  | 3GIO      | 1.5V     | C0h                        | 2V       | FFh                        | 0V       | 00h                        | -0.3V~+6.0V                      |

| AD_IN6  | ICH_Core  | 1.5V     | C0h                        | 2V       | FFh                        | 0V       | 00h                        | -0.3V~+6.0V                      |

| AD_IN7  | Vccp1     | 1.20V    | C0h                        | 1.60V    | FFh                        | 0V       | 00h                        | -0.3V~+6.0V                      |

| AD_IN8  | Vccp2     | 1.20V    | C0h                        | 1.60V    | FFh                        | 0V       | 00h                        | -0.3V~+6.0V                      |

| AD_IN9  | +3.3V     | 3.30V    | C0h                        | 4.40V    | FFh                        | 0V       | 00h                        | -0.3V~+6.0V                      |

| AD_IN10 | +5V       | 5.0V     | C0h                        | 6.667V   | FAh                        | 0V       | 00h                        | -0.3V~+6.5V                      |

| AD_IN11 | SCSI_Core | 2.5V     | C0h                        | 3.333V   | FFh                        | 0V       | 00h                        | -0.3V~+6.0V                      |

| AD_IN12 | Mem_Core  | 1.969V   | C0h                        | 2.625V   | FFh                        | 0V       | 00h                        | -0.3V~+6.0V                      |

| AD_IN13 | Mem_Vtt   | 0.984V   | C0h                        | 1.312V   | FFh                        | 0V       | 00h                        | -0.3V~+6.0V                      |

| AD_IN14 | Gbit_Core | 0.984V   | C0h                        | 1.312V   | FFh                        | 0V       | 00h                        | -0.3V~+6.0V                      |

| AD_IN15 | -12V      | 0.309V   | 40h                        | 1.236V   | FFh                        | 0V       | 00h                        | -0.3V~(+V <sub>DD</sub> + 0.05V) |

| AD_IN16 | +3.3V S/B | 3.3V     | C0h                        | 3.6V     | D1h                        | 3.0V     | AEh                        | -0.3V~+6.0V                      |

この表に示されている公称電圧は、標準値のみです。異なる公称電圧の電圧レールでも監視は行えますが、公称値でのレジスタの読み出しは C0h ではなくなります。たとえば、公称 2.5V の Mem\_Core レールを AD\_IN12 で監視したり、1.2V の Mem\_VTT レールを AD\_IN13 で監視したりできます。

AD\_IN16 は LM94 の電源ピンでもあるため、この AD 入力には特別な制限が適用されます。LM94 の指定された動作電圧範囲は 3.0V~3.6V であるため、このピンへの電圧入力はこの制限によって限定されます。致命的な損傷を防ぐために、このピンに 6V を超える電圧を印加しないように注意する必要があります。

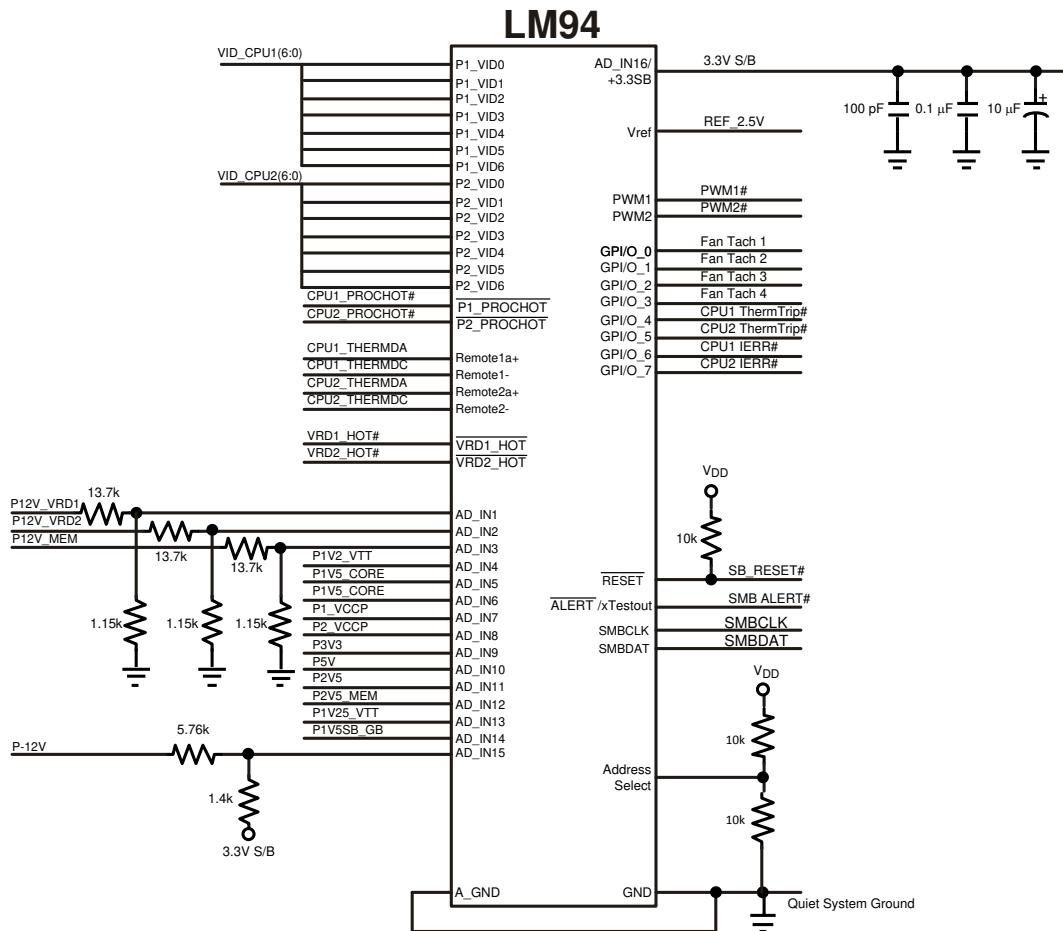

### 6.2.6 +12V 電源レール用推奨外部スケーリング抵抗

+12V 入力には外部スケーリング抵抗が必要です。この抵抗は、12V を 0.927V までスケールダウンする必要があります。

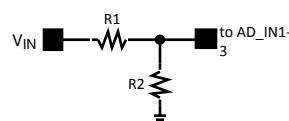

図 6-1. +12V 電源入力に必要な外部スケーリング抵抗

R1 と R2 の必要な比率を計算するには、次の式を使用します。

$$\frac{R1}{R2} = \frac{12}{0.927} - 1 = 11.04498 \quad (1)$$

極端な温度でのリーク電流が原因の誤差を最小限に抑えるため、分圧器の等価テブナン抵抗は 1k~7k の範囲にすることを推奨します。この抵抗の最適値は、R1 = 13.7kΩ と R2 = 1.15kΩ です。これにより、比率は 11.94498 となり、理論値から +0.27% の偏差が生じます。また、抵抗の許容誤差は ±1% 以上であることを推奨します。

電圧値レジスタの各 LSB は、 $12V/192 = 62.5mV$  に相当します。+12V 電源入力の実際の電圧を計算するには、次の式を使用します。

$$V_{IN} = (8\text{-bit value register code}) \times (62.5 \text{ mV}) \quad (2)$$

### 6.2.7 -12V 電源入力用の推奨外部スケーリング回路

-12V 入力には、公称入力電圧 -12V を +0.309V にレベルシフトするための外付け抵抗が必要です。

図 6-2. -12V 電源入力用の必要な外付けレベルシフト抵抗

+3.3V スタンバイ電圧を、レベルシフトのリファレンスとして使用します。したがって、この電圧の許容誤差は -12V の読み取り精度に直接影響します。比率誤差を最小限に抑えるためには、±1% よりも厳しい許容誤差を使用する必要があります。極端な温度でのリーク電流による誤差を最小限に抑えるため、分圧器の等価テブナン抵抗は 1k~7k の範囲にすることを推奨します。R1 と R2 の比率を計算するには、次の式を使用します。

$$\frac{R1}{R2} = \frac{(V_{IN} - V_{REF})}{(AD\_IN - V_{REF})} - 1 \quad (3)$$

ここで、 $V_{IN}$  は公称入力電圧 -12V、 $V_{REF}$  はリファレンス電圧 +3.3V、 $AD\_IN$  は AD 入力で  $\frac{1}{4}$  スケールの読み出しに必要な電圧、または 0.309V です。

したがって、この場合は次のようにになります。

$$\frac{R1}{R2} = \frac{(-12 - 3.3)}{(0.309 - 3.3)} - 1 = 4.11535 \quad (4)$$

標準的な 1% 抵抗値を R1 5.76 kΩ、R2 1.4 kΩ とすると、R1 と R2 の比率は 4.1143 になります。

入力電圧  $V_{IN}$  は、値レジスタの読み出し (VR) を使って、次の式で計算できます。

$$V_{IN} = \frac{R1}{R2} = \left( \frac{VR}{256} + 1 \right) \times \left[ \left( 1.236V \times \frac{VR}{256} \right) - 3.3V \right] + 3.3V = (24.69 \text{ mV} \times VR) - 13.5771V \quad (5)$$

以下の表は、-12V 付近の値レジスタ読み出しの理論的な電圧値をまとめたものです。

| 値レジスタ | $V_{IN}$ | -12V からの % Δ |

|-------|----------|--------------|

| 15    | -13.2068 | -10.0563     |

| 16    | -13.1821 | -9.8505      |

| 17    | -13.1574 | -9.6448      |

| 18    | -13.1327 | -9.4390      |

| 19    | -13.1080 | -9.2332      |

| 20    | -13.0833 | -9.0275      |

| 21    | -13.0586 | -8.8217      |

| 22    | -13.0339 | -8.6159      |

| 23    | -13.0092 | -8.4101      |

| 24    | -12.9845 | -8.2044      |

| 25    | -12.9598 | -7.9986      |

| 26    | -12.9351 | -7.7928      |

| 27    | -12.9104 | -7.5871      |

| 値レジスタ | V <sub>IN</sub> | -12V からの % Δ |

|-------|-----------------|--------------|

| 28    | -12.8858        | -7.3813      |

| 29    | -12.8611        | -7.1755      |

| 30    | -12.8364        | -6.9698      |

| 31    | -12.8117        | -6.7640      |

| 32    | -12.7870        | -6.5582      |

| 33    | -12.7623        | -6.3524      |

| 34    | -12.7376        | -6.1467      |

| 35    | -12.7129        | -5.9409      |

| 36    | -12.6882        | -5.7351      |

| 37    | -12.6635        | -5.5294      |

| 38    | -12.6388        | -5.3236      |

| 39    | -12.6141        | -5.1178      |

| 40    | -12.5894        | -4.9121      |

| 41    | -12.5648        | -4.7063      |

| 42    | -12.5401        | -4.5005      |

| 43    | -12.5154        | -4.2947      |

| 44    | -12.4907        | -4.0890      |

| 45    | -12.4660        | -3.8832      |

| 46    | -12.4413        | -3.6774      |

| 47    | -12.4166        | -3.4717      |

| 48    | -12.3919        | -3.2659      |

| 49    | -12.3672        | -3.0601      |

| 50    | -12.3425        | -2.8544      |

| 51    | -12.3178        | -2.6486      |

| 52    | -12.2931        | -2.4428      |

| 53    | -12.2684        | -2.2370      |

| 54    | -12.2438        | -2.0313      |

| 55    | -12.2191        | -1.8255      |

| 56    | -12.1944        | -1.6197      |

| 57    | -12.1697        | -1.4140      |

| 58    | -12.1450        | -1.2082      |

| 59    | -12.1203        | -1.0024      |

| 60    | -12.0956        | -0.7967      |

| 61    | -12.0709        | -0.5909      |

| 62    | -12.0462        | -0.3851      |

| 63    | -12.0215        | -0.1793      |

| 64    | -11.9968        | 0.0264       |

| 65    | -11.9721        | 0.2322       |

| 66    | -11.9474        | 0.4380       |

| 67    | -11.9228        | 0.6437       |

| 68    | -11.8981        | 0.8495       |

| 69    | -11.8734        | 1.0553       |

| 70    | -11.8487        | 1.2610       |

| 71    | -11.8240        | 1.4668       |

| 72    | -11.7993        | 1.6726       |

| 73    | -11.7746        | 1.8784       |

| 値レジスタ | V <sub>IN</sub> | -12V からの % Δ |

|-------|-----------------|--------------|

| 74    | -11.7499        | 2.0841       |

| 75    | -11.7252        | 2.2899       |

| 76    | -11.7005        | 2.4957       |

| 77    | -11.6758        | 2.7014       |

| 78    | -11.6511        | 2.9072       |

| 79    | -11.6264        | 3.1130       |

| 80    | -11.6018        | 3.3188       |

| 81    | -11.5771        | 3.5245       |

| 82    | -11.5524        | 3.7303       |

| 83    | -11.5277        | 3.9361       |

| 84    | -11.5030        | 4.1418       |

| 85    | -11.4783        | 4.3476       |

| 86    | -11.4536        | 4.5534       |

| 87    | -11.4289        | 4.7591       |

| 88    | -11.4042        | 4.9649       |

| 89    | -11.3795        | 5.1707       |

| 90    | -11.3548        | 5.3765       |

| 91    | -11.3301        | 5.5822       |

| 92    | -11.3054        | 5.7880       |

| 93    | -11.2807        | 5.9938       |

| 94    | -11.2561        | 6.1995       |

| 95    | -11.2314        | 6.4053       |

| 96    | -11.2067        | 6.6111       |

| 97    | -11.1820        | 6.8168       |

| 98    | -11.1573        | 7.0226       |

| 99    | -11.1326        | 7.2284       |

| 100   | -11.1079        | 7.4342       |

| 101   | -11.0832        | 7.6399       |

| 102   | -11.0585        | 7.8457       |

| 103   | -11.0338        | 8.0515       |

| 104   | -11.0091        | 8.2572       |

| 105   | -10.9844        | 8.4630       |

| 106   | -10.9597        | 8.6688       |

| 107   | -10.9351        | 8.8745       |

| 108   | -10.9104        | 9.0803       |

| 109   | -10.8857        | 9.2861       |

| 110   | -10.8610        | 9.4919       |

| 111   | -10.8363        | 9.6976       |

| 112   | -10.8116        | 9.9034       |

| 113   | -10.7869        | 10.1092      |

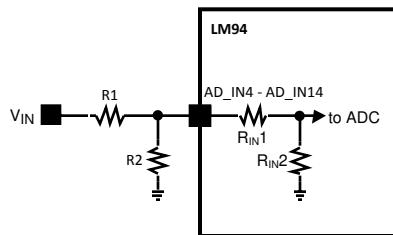

### 6.2.8 他のアナログ入力への外付けスケーリング抵抗の追加

AD\_IN1～AD\_IN3 および AD\_IN15 を除くすべてのアナログ入力には、内部分圧抵抗が含まれています。内部分圧抵抗に起因する誤差を考慮すると、外付けスケーリング抵抗で AD\_IN4～AD\_IN14 の入力をさらにスケーリングできます。図 6-3 に示す内部抵抗  $R_{IN1} + R_{IN2}$  は、外付け分圧抵抗に最小 140kΩ の抵抗性負荷を与えます。

図 6-3. 内部抵抗、 $R_{IN1} + R_{IN2}$

### 6.2.9 VID を使用した動的 Vccp 監視

AD\_IN7 (CPU1 Vccp) 入力と AD\_IN8 (CPU2 Vccp) 入力は、P1\_VIDx 入力と P2\_VIDx 入力を使用して動的に監視され、制限を決定するものです。動的比較は、静的にプログラムされた制限を使用する静的比較とは無関係に動作します。LM94 は、4 種類の VID 動作モードを備えた Intel CPU 搭載マザーボードで使用される電圧レギュレータ (VRM または VRD) の 3 種類の仕様をサポートしています。サポートされている電圧レギュレータ仕様は、VRD10/VRM10、VRD10.2 拡張、VRD11/VRM11 で、本書ではそれぞれ VRD10 仕様、VRD10.2 仕様、VRD11 仕様と表記します。

VRD 10 仕様では、VID 信号が新しい値に変動するとき、一度に 1 LSB ずつステップし、1 ステップは  $5\mu s$  ごとに発生します。ワーストケースでは、 $100\mu s$  の間に最大 20 ステップが一度に発生する可能性があります。VRD からの Vccp 電圧は、最後の VID 変動から  $50\mu s$  以内に新しい値に安定する必要があります。LM94 では、VRD10 モードで VID の変動が  $5\mu s$  毎よりも頻繁に発生することは想定されていません。同様に、LM94 は VRD10.2 仕様と VRD11 仕様のタイミング要件をサポートできます。

VID 信号は、プログラム制御下のプロセッサ、内部熱イベント、または強制 **PROCHOT** のような外部制御によって変更することができます。

VID コードの各値によって選択されるリファレンス電圧は、さまざまな VRM / VRD 仕様に記載されています。ライン間スキューに起因する過渡的な VID 値は、LM94 では無視されます。ワーストケースのライン間スキューについては、VRM / VRD の仕様を参照してください。

LM94 は、サンプリング ウィンドウ中の VID 値を平均化し、サンプリング ウィンドウ中に VID 入力が示していた平均電圧を決定します。電圧変換サイクルの完了時に、LM94 は瞬時値ではなく、平均 VID 値に基づいて制限の比較を行います。上限は、VID で示される平均電圧に上限オフセットを加算することで決定されます。下限は、VID で示される平均電圧から下限オフセットを減算することで決定されます。AD\_IN7 (または AD\_IN8) 電圧が上限および下限を外れると、エラーイベントが生成されます。動的比較と静的比較は、100ms ごとに実行されます。平均化の時間間隔は 1.5ms です。

Vccp サンプリング ウィンドウ中の任意の時点で、VID コードによって VRD/VRM の出力をオフにする必要があることが示された場合、そのサンプルでは動的 Vccp チェックは無効になります。

比較精度は  $\pm 25mV$  であるため、この誤差を含めて比較制限を設定する必要があります。Vccp 電圧は (VID の変動により) 新しい値に安定する過程にある可能性があるため、上限と下限のオフセットを設定する際には、この安定化の過程を考慮する必要があります。

LM94 では、動的 Vccp チェックの上限電圧に制限があります。上限は  $1.5875V$  を超えることはありません。VID で示された電圧と上限オフセット電圧の合計が  $1.5875$  を超えると、上限のチェックは無効になります。

ピン 11 とピン 12 には 2 つの役割があります。VRD10 モードが選択されている場合は汎用入力として使用でき、その状態は BMC およびホストのエラー ステータス レジスタに反映されます。その他の VRD モードでは、VID6 入力として使用されます。

### 6.2.10 アナログ温度センサの監視

AD\_IN11 と AD\_IN15 の読み取り値をファン制御ロジックに送って、LM60 などの外部温度センサを簡単に使用できるようにします。これらの入力を温度センシングに使用する場合、返されるデジタル出力は符号付き形式で、MSb が反転されます。

以下の表に、バイナリ データを温度に変換するために必要な重要なパラメータを示します。

| 入力      | V NOM             | フルスケール<br>(コード 256) V | 254.5<br>コード V | mV<br>/LSb | LM60<br>°/LSb | LM50<br>°/LSb |

|---------|-------------------|-----------------------|----------------|------------|---------------|---------------|

| AD_IN11 | 2.500<br>(¼ スケール) | 3.3333                | 3.3138         | 13.0       | 2.0833        | 1.3021        |

| AD_IN15 | 0.309<br>(¼ スケール) | 1.2360                | 1.2288         | 4.8        | 0.7725        | 0.4828        |

以下の表に、AD\_IN11 または AD\_IN15 のデジタル値 (DV) を温度値に変換するための式を示します。

| 入力      | LM60 の式                      | LM50 の式                          |

|---------|------------------------------|----------------------------------|

| AD_IN11 | $(DV + 95.44) \times 2.0833$ | (6) $(DV + 89.60) \times 1.3021$ |

| AD_IN15 | $(DV + 40.18) \times 0.7725$ | (8) $(DV + 24.44) \times 0.4828$ |

以下の表に、異なる温度で LM60 を使用した場合に生成される理想的な値を示します。