# LMX2820 位相同期と JESD204B をサポートした 22.6GHz の広帯域 PLLatinum™ RF シンセサイザ

## 1 特長

- 出力周波数:45MHz～22.6GHz

- 6GHzにおいて36fsのRMSジッタ(12kHz～95MHz)

- 高性能PLL

- 性能指数:-236dBc/Hz

- 正規化1/fノイズ:-134dBc/Hz

- 整数モード・スプリアス:-95dBc( $f_{PD} = 100\text{MHz}$ )

- 高い位相検出器周波数

- 整数モード:400MHz

- 分数モード:300MHz

- プログラマブル入力マルチプライヤ

- 直接PFD入力によりオフセット・ミキシングをサポートし、PLL Nデバイダを超低ジッタに

- 2.5μsの高速VCOキャリブレーション時間

- MUTEピンにより200nsでミュート/ミュート解除を実行

- ダブルがイネーブルの状態でVCOリーク-45dBc

- 最大22.6GHzまでの外部VCOをサポート

- 複数デバイス間の出力位相の同期

- 2つの差動RF出力と1つの差動SYSREF出力によりJESD204Bをサポート

## 2 アプリケーション

- レーダーおよび電子戦

- 5Gおよびミリ波のワイヤレス・インフラストラクチャ

- マイクロ波バックホール

- 試験および計測機器

- 高速データ・コンバータのクロック供給

## 3 概要

LMX2820は高性能で広帯域のシンセサイザで、45MHz～22.6GHzの範囲のあらゆる周波数を生成できます。-236dBc/Hzという性能指数を持つ高性能PLLと高い位相検出器周波数により、帯域内ノイズと積分ジッタを非常に低く抑えることができます。高速Nデバイダにはプリデバイダがないため、スプリアスの振幅と数が大幅に低減されます。整数境界スプリアスを軽減するため、プログラマブル入力マルチプライヤも備えています。

LMX2820を使用すると、複数のデバイスの出力を同期させることができ、入力と出力の間に決定論的な遅延を必要とするアプリケーションにも対応できます。高速のキャリブレーション・アルゴリズムにより、VCOキャリブレーション時間が大幅に短縮されるため、高速の周波数ホッピングを必要とするシステムを実現できます。LMX2820は、JESD204B規格に準拠したSYSREFを生成または反復でき、高速データ・コンバータ向けの低ノイズのクロック源として使用できます。このシンセサイザは、外部VCOと組み合わせて使用することもできます。PFDの直接入力ピンが搭載され、オフセット・ミキシングをサポートしているため、低スプリアスで伝送を行えます。

このデバイスは単一の3.3V電源で動作し、LDOを内蔵しているため、オンボードの低ノイズLDOは不要です。

### 製品情報 (1)

| 部品番号    | パッケージ     | 本体サイズ(公称) |

|---------|-----------|-----------|

| LMX2820 | VQFN (48) | 7mm × 7mm |

(1) 利用可能なパッケージについては、このデータシートの末尾にある注文情報を参照してください。

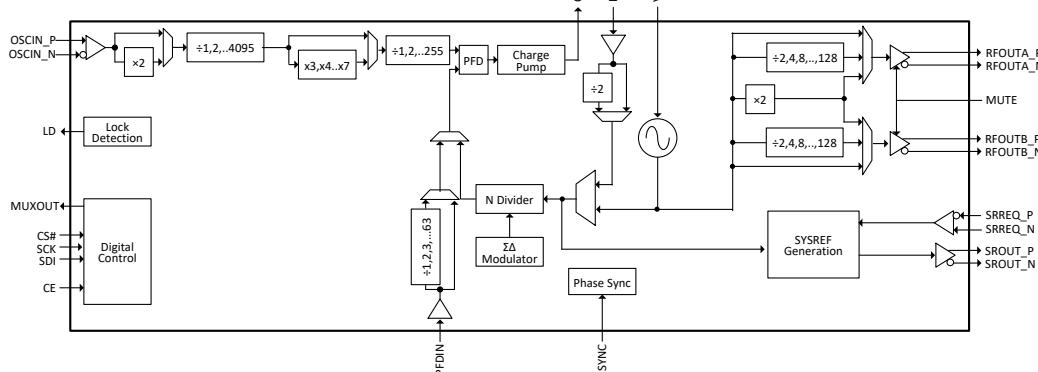

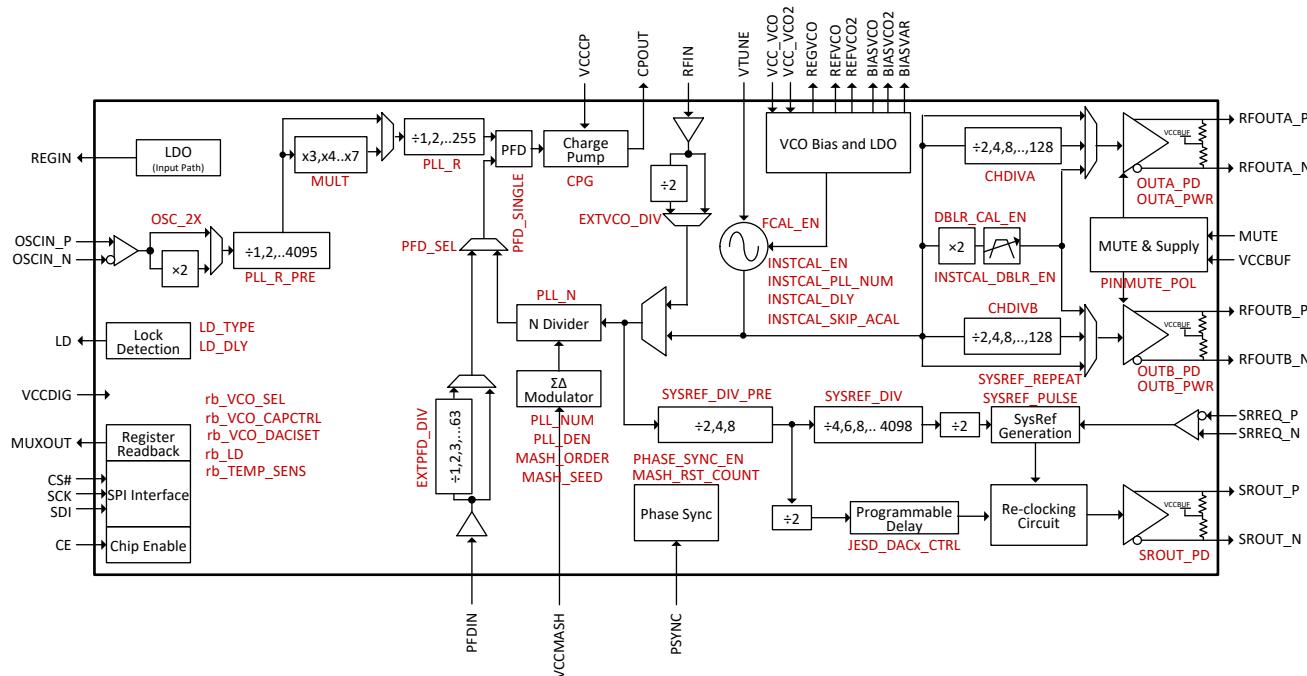

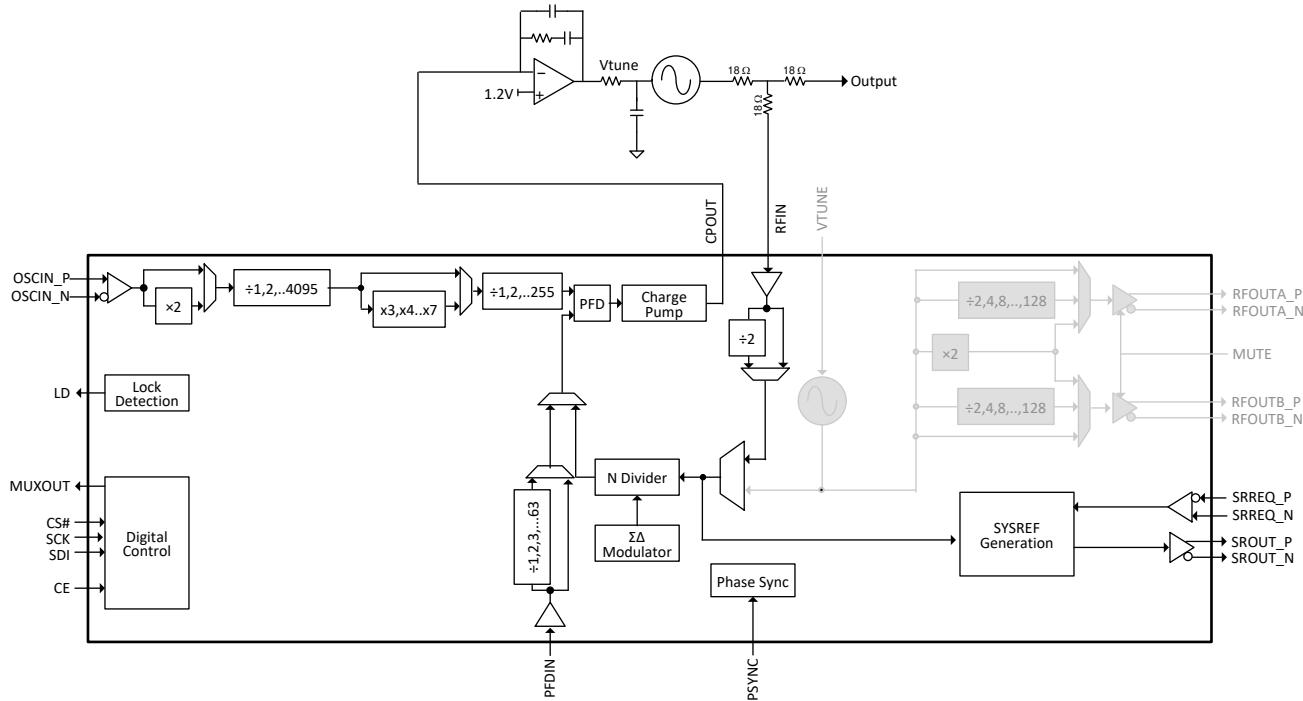

機能ブロック図

英語版のTI製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、必ず最新版の英語版をご参照ください。

## 目次

|             |    |                         |    |

|-------------|----|-------------------------|----|

| 1 特長        | 1  | 7.4 デバイスの機能モード          | 23 |

| 2 アプリケーション  | 1  | 8 アプリケーションと実装           | 26 |

| 3 概要        | 1  | 8.1 アプリケーション情報          | 26 |

| 4 改訂履歴      | 2  | 8.2 代表的なアプリケーション        | 28 |

| 5 ピン構成と機能   | 3  | 8.3 初期化およびパワーオン・シーケンス   | 30 |

| 6 仕様        | 6  | 9 電源に関する推奨事項            | 32 |

| 6.1 絶対最大定格  | 6  | 10 レイアウト                | 32 |

| 6.2 ESD 定格  | 6  | 10.1 レイアウトのガイドライン       | 32 |

| 6.3 推奨動作条件  | 6  | 10.2 レイアウト例             | 33 |

| 6.4 熱に関する情報 | 6  | 11 デバイスおよびドキュメントのサポート   | 34 |

| 6.5 電気的特性   | 7  | 11.1 ドキュメントの更新通知を受け取る方法 | 34 |

| 6.6 タイミング要件 | 10 | 11.2 サポート・リソース          | 34 |

| 6.7 代表的特性   | 11 | 11.3 商標                 | 34 |

| 7 詳細説明      | 14 | 11.4 静電気放電に関する注意事項      | 34 |

| 7.1 概要      | 14 | 11.5 用語集                | 34 |

| 7.2 機能ブロック図 | 15 | 12 メカニカル、パッケージ、および注文情報  | 34 |

| 7.3 機能説明    | 15 |                         |    |

## 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

### Changes from Revision B (December 2020) to Revision C (February 2021) Page

- |                                             |   |

|---------------------------------------------|---|

| • データシートの初版の日付を 2018 年 12 月から 2020 年 6 月に変更 | 1 |

|---------------------------------------------|---|

### Changes from Revision A (November 2020) to Revision B (December 2020) Page

- |                                                |    |

|------------------------------------------------|----|

| • PSYNC ピンの説明を変更                               | 3  |

| • V を Vpp に変更。これにより数値は 2 倍になっていますが、実際の電圧は同じです。 | 7  |

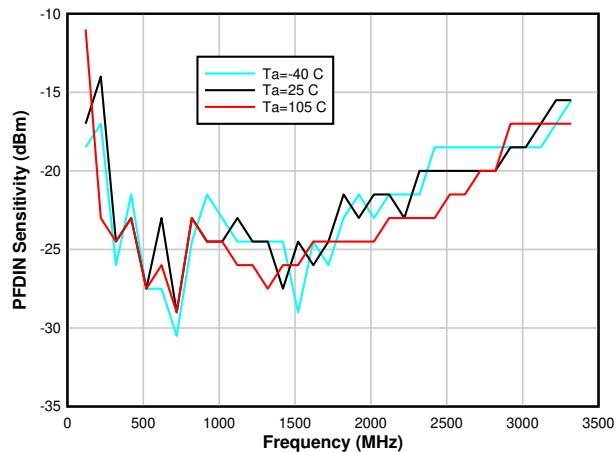

| • PFDIN 感度グラフを変更                               | 11 |

### Changes from Revision \* (June 2020) to Revision A (November 2020) Page

- |                                 |   |

|---------------------------------|---|

| • ドキュメント全体にわたって表、図、相互参照の採番方法を更新 | 1 |

| • データシートのステータスを事前情報から量産データに変更   | 1 |

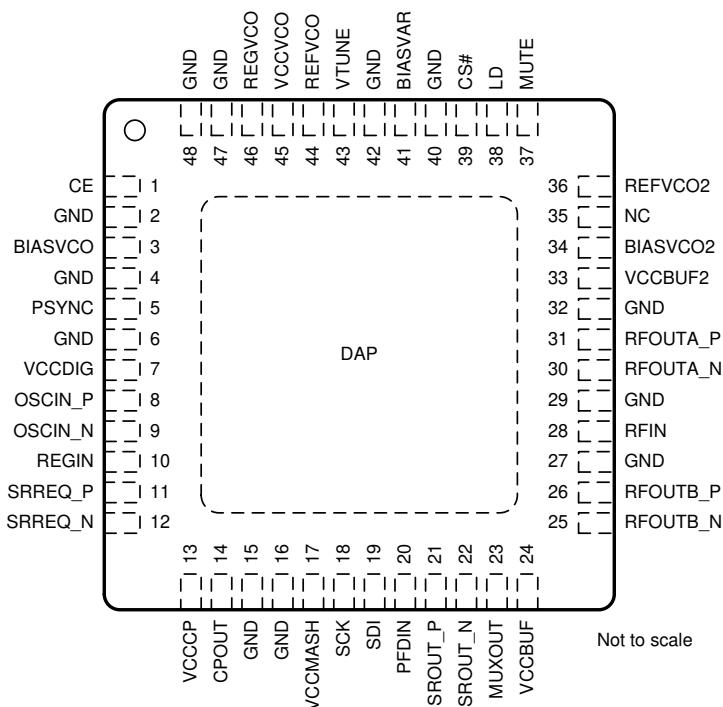

## 5 ピン構成と機能

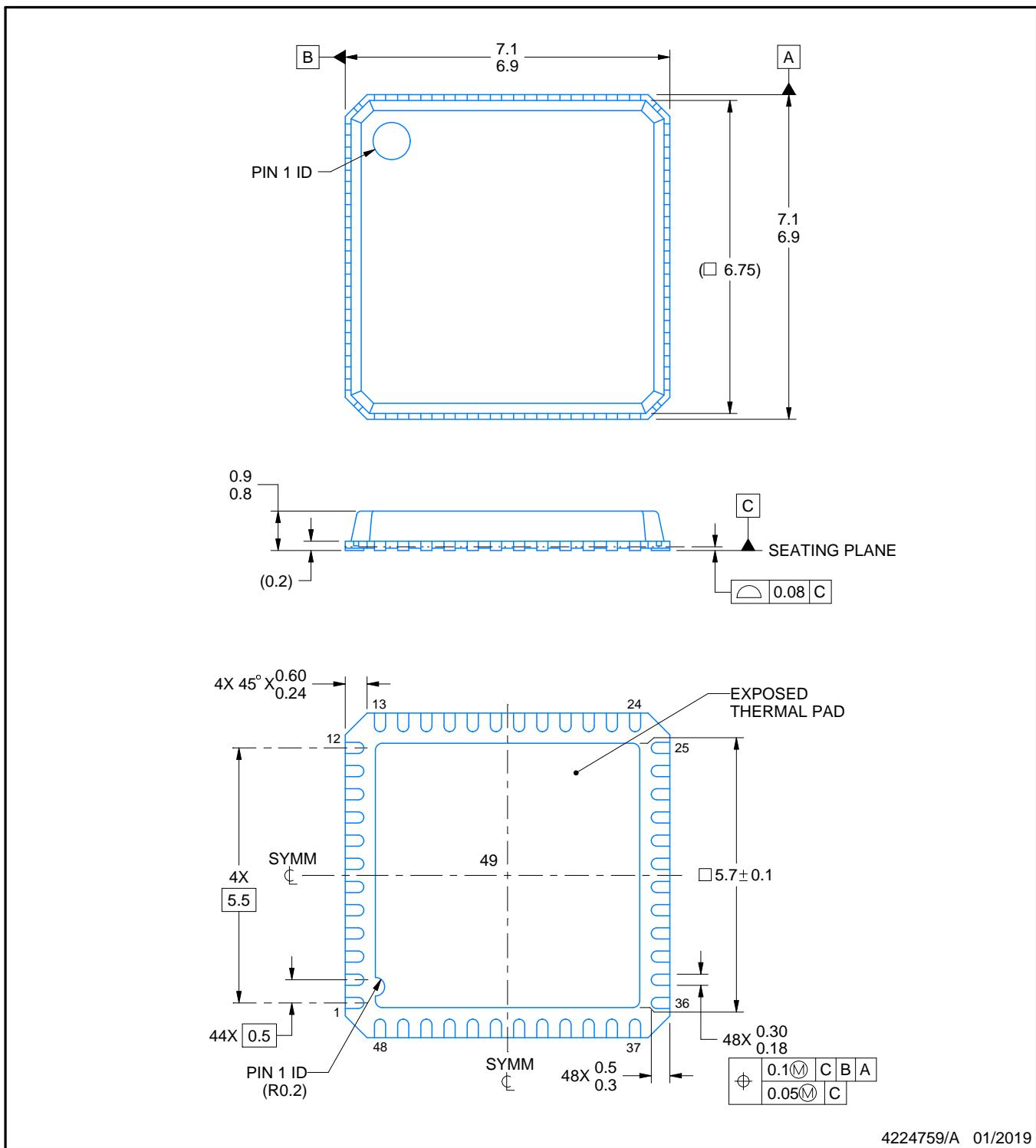

図 5-1. RTC パッケージ 48 ピン VQFN 上面図

表 5-1. ピン機能

| ピン             |                   | I/O | 説明                                                                      |

|----------------|-------------------|-----|-------------------------------------------------------------------------|

| 名前             | 番号 <sup>(1)</sup> |     |                                                                         |

| <b>電源とグランド</b> |                   |     |                                                                         |

| VCCBUF         | 24                | P   | 出力バッファ電源。グランドに接続した、低 ESR で 0.1μF と 1μF のデカップリング・コンデンサを使用して、3.3V に接続します。 |

| VCCBUF2        | 33                | P   | バッファ電源。グランドに接続した、低 ESR で 0.1μF と 1μF のデカップリング・コンデンサを使用して、3.3V に接続します。   |

| VCCCP          | 13                | P   | チャージ・ポンプ電源。グランドに接続した、1μF のデカップリング・コンデンサを使用して、3.3V に接続します。               |

| VCCDIG         | 7                 | P   | デジタル電源。グランドに接続した、低 ESR で 0.1μF と 1μF のデカップリング・コンデンサを使用して、3.3V に接続します。   |

| VCCMASH        | 17                | P   | デジタル電源。グランドに接続した、低 ESR で 0.1μF と 1μF のデカップリング・コンデンサを使用して、3.3V に接続します。   |

| VCCVCO         | 45                | P   | VCO 電源。グランドに接続した、低 ESR で 0.1μF と 1μF のデカップリング・コンデンサを使用して、3.3V に接続します。   |

表 5-1. ピン機能 (continued)

| ピン              |        | I/O | 説明                                                                                                                                         |

|-----------------|--------|-----|--------------------------------------------------------------------------------------------------------------------------------------------|

| 名前              | 番号 (1) |     |                                                                                                                                            |

| GND             | 2      | G   | グランド                                                                                                                                       |

|                 | 4      |     |                                                                                                                                            |

|                 | 6      |     |                                                                                                                                            |

|                 | 15     |     |                                                                                                                                            |

|                 | 16     |     |                                                                                                                                            |

|                 | 27     |     |                                                                                                                                            |

|                 | 29     |     |                                                                                                                                            |

|                 | 32     |     |                                                                                                                                            |

|                 | 40     |     |                                                                                                                                            |

|                 | 42     |     |                                                                                                                                            |

| DAP             | 47     | —   | 正しい動作のため、GND ピンは露出したサーマル・パッドに接続します。このサーマル・パッドは、複数のビアを使用して内部の任意の PCB グランド・プレーンに接続し、優れた熱特性を実現できます。                                           |

|                 | 48     |     |                                                                                                                                            |

| NC              | 35     | NC  | グランドに接続します。                                                                                                                                |

| バイアス / LDO バイパス |        |     |                                                                                                                                            |

| BIASVAR         | 41     | B   | VCO バラクタ・バイアス。1 $\mu$ F のデカップリング・コンデンサをグランドに接続します。                                                                                         |

| BIASVCO         | 3      | B   | VCO バイアス。低 ESR で、0.47 $\mu$ F (キャリブレーション時間を最短にする場合) から 4.7 $\mu$ F (帯域内位相ノイズを最適化する場合) までの容量のコンデンサを接続します。                                   |

| BIASVCO2        | 34     | B   | VCO バイアス。1 $\mu$ F のデカップリング・コンデンサをグランドに接続します。ピンの近くに配置します。                                                                                  |

| REFVCO2         | 36     | B   | VCO 電源基準電圧。1 $\mu$ F のデカップリング・コンデンサをグランドに接続します。                                                                                            |

| REGIN           | 10     | B   | 入力基準バス・レギュレータのデカップリング。1 $\mu$ F のデカップリング・コンデンサをグランドに接続します。ピンの近くに配置します。高周波ノイズにフィルタを適用するには、低 ESR の 0.1 $\mu$ F のデカップリング・コンデンサを追加することをお勧めします。 |

| REGVCO          | 46     | B   | VCO レギュレータ・ノード。1 $\mu$ F のデカップリング・コンデンサをグランドに接続します。                                                                                        |

| REFVCO          | 44     | B   | VCO 電源基準電圧。10 $\mu$ F のデカップリング・コンデンサをグランドに接続します。                                                                                           |

| デジタル入力          |        |     |                                                                                                                                            |

| CE              | 1      | I   | チップのイネーブル。高インピーダンスの CMOS 入力。1.8V から 3.3V までのロジック。アクティブ High で、デバイスの電源をオンにします。                                                              |

| MUTE            | 37     | I   | バッファのミュート制御。高インピーダンスの CMOS 入力。1.8V から 3.3V までのロジック。                                                                                        |

| PSYNC           | 5      | I   | 位同期期で、入力信号レベルは構成可能です。直列の 100 $\Omega$ とともに PSYNC 信号に接続するか、使用しない場合は GND に接続します。                                                             |

| CS#             | 39     | I   | SPI ラッチ。高インピーダンスの CMOS 入力。1.8V から 3.3V までのロジック。                                                                                            |

| SCK             | 18     | I   | SPI クロック。高インピーダンスの CMOS 入力。1.8V から 3.3V までのロジック。                                                                                           |

| SDI             | 19     | I   | SPI データ。高インピーダンスの CMOS 入力。1.8V から 3.3V までのロジック。                                                                                            |

| アナログ入力          |        |     |                                                                                                                                            |

| OSCIN_P         | 8      | I   | 基準入力クロック (+)。高インピーダンスのセルフバイアス・ピン。AC カップリングが必要です。使用しない場合は、50 $\Omega$ の抵抗を介してグランドに AC カップリングします。                                            |

| PFDIN           | 20     | I   | 外部 PFD 入力。セルフバイアス・ピン。AC カップリングと、外部の 50 $\Omega$ 抵抗でグランドに接続されている必要があります。                                                                    |

| RFIN            | 28     | I   | 外部 VCO 入力。内部で 50 $\Omega$ 終端されています。AC カップリングが必要です。                                                                                         |

| OSCIN_N         | 9      | I   | 基準入力クロック (-)。高インピーダンスのセルフバイアス・ピン。AC カップリングが必要です。使用しない場合は、50 $\Omega$ の抵抗を介してグランドに AC カップリングします。                                            |

| SRREQ_P         | 11     | I   | 差動 SYSREF 入力クロック (+)。AC および DC カップリングをサポートします。                                                                                             |

**表 5-1. ピン機能 (continued)**

| ピン        |                   | I/O   | 説明                                               |

|-----------|-------------------|-------|--------------------------------------------------|

| 名前        | 番号 <sup>(1)</sup> |       |                                                  |

| VTUNE     | 43                | I     | VCO 調整電圧入力。1.5nF 以上のコンデンサを VCO グランドに接続します。       |

| SRREQ_N   | 12                | I     | 差動 SYSREF 入力クロック (-)。AC および DC カップリングをサポートします。   |

| <b>出力</b> |                   |       |                                                  |

| CPOUT     | 14                | O     | チャージ・ポンプの出力。ループ・フィルタの C1 を、このピンの近くに接続することを推奨します。 |

| LD        | 38                | O     | ロック検出出力。3.3V ロジック。                               |

| MUXOUT    | 23                | O     | SPI 読み戻し出力。3.3V ロジック。CE = Low のときは高インピーダンスです。    |

| RFOUTA_N  | 30                | O, PU | 差動出力 A (-)。内部 50Ω プルアップ。AC カップリングが必要です。          |

| RFOUTA_P  | 31                | O, PU | 差動出力 A (+)。内部 50Ω プルアップ。AC カップリングが必要です。          |

| RFOUTB_N  | 25                | O, PU | 差動出力 B (-)。内部 50Ω プルアップ。AC カップリングが必要です。          |

| RFOUTB_P  | 26                | O, PU | 差動出力 B (+)。内部 50Ω プルアップ。AC カップリングが必要です。          |

| SROUT_N   | 22                | O, PU | 差動 SYSREF 出力 (-)。内部 50Ω プルアップ。                   |

| SROUT_P   | 21                | O, PU | 差動 SYSREF 出力 (+)。内部 50Ω プルアップ。                   |

(1) 各ピンの I/O タイプの定義は次のとおりです。

- P = 電源

- G = グランド

- NC = 接続なし。このピンはグランドに接続するか、どこにも接続しません。

- B = バイアス / LDO バイパス

- I = 入力

- O = 出力

- PU = プルアップ

## 6 仕様

### 6.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|                  |         | 最小値  | 最大値                   | 単位 |

|------------------|---------|------|-----------------------|----|

| V <sub>CC</sub>  | 電源電圧    | -0.3 | 3.6                   | V  |

| V <sub>IN</sub>  | IO 入力電圧 |      | V <sub>CC</sub> + 0.3 | V  |

| T <sub>J</sub>   | 接合部温度   |      | 150                   | °C |

| T <sub>stg</sub> | 保管温度    | -65  | 150                   | °C |

(1) 絶対最大定格を上回るストレスが加わった場合、本製品に永続的な損傷が発生する可能性があります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を超える状態で本製品が正常に動作することを暗黙的に示すものではありません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

### 6.2 ESD 定格

|                    |       | 値                                                              | 単位    |

|--------------------|-------|----------------------------------------------------------------|-------|

| V <sub>(ESD)</sub> | 静電気放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、すべてのピン <sup>(1)</sup>   | ±2000 |

|                    |       | デバイス帶電モデル (CDM)、JEDEC 仕様 JESD22-C101 に準拠、すべてのピン <sup>(2)</sup> | ±750  |

(1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

(2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

### 6.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                 |       | 最小値  | 公称値 | 最大値  | 単位 |

|-----------------|-------|------|-----|------|----|

| T <sub>A</sub>  | 周囲温度  | -40  |     | 85   | °C |

| T <sub>J</sub>  | 接合部温度 |      |     | 125  | °C |

| V <sub>CC</sub> | 電源電圧  | 3.15 | 3.3 | 3.45 | V  |

### 6.4 热に関する情報

| 熱評価基準 <sup>(1)</sup>  |                     | LMX2820    | 単位   |

|-----------------------|---------------------|------------|------|

|                       |                     | RTC (VQFN) |      |

|                       |                     | 48 ピン      |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗        | 21.5       | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース (上面) への熱抵抗 | 9.5        | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗        | 6.0        | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への熱特性パラメータ   | 0.1        | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への熱特性パラメータ   | 5.9        | °C/W |

| R <sub>θJC(bot)</sub> | 接合部からケース (底面) への熱抵抗 | 0.6        | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション・レポートを参照してください。

## 6.5 電気的特性

$3.15V \leq V_{CC} \leq 3.45V$ 、 $-40^{\circ}C \leq T_A \leq 85^{\circ}C$ 。標準値は  $V_{CC} = 3.3V$ 、 $25^{\circ}C$ でのものです(特に記述のない限り)。

| パラメータ            | テスト条件                  | 最小値                               | 標準値  | 最大値   | 単位     |

|------------------|------------------------|-----------------------------------|------|-------|--------|

| <b>電源電圧</b>      |                        |                                   |      |       |        |

| $I_{CC}$         | 電源電流                   | 1つの RF 直接出力 (1)                   | 500  |       | mA     |

|                  |                        | 1つの分周された RF 出力 (2)                | 580  |       |        |

|                  |                        | 1つの RF 出力、VCO ダブルギネーブル(3)         | 590  |       |        |

|                  |                        | RFIN 外部フィードバック・モード、内部 VCO         | 530  |       |        |

|                  |                        | PFDIN 外部フィードバック・モード、内部 VCO (5)    | 455  |       |        |

|                  |                        | 外部 VCO モード (4)                    | 290  |       |        |

| $I_{CCPOR}$      | パワーオン・リセット電流           |                                   | 234  |       |        |

| $I_{CPD}$        | パワーダウン電流               |                                   | 10   |       |        |

| <b>入力信号バス</b>    |                        |                                   |      |       |        |

| $f_{OSCin}$      | OSCin の入力周波数           | OSC_2X = 0 (ダブルがバイパスされる)          | 5    | 1400  | MHz    |

|                  |                        | OSC_2X = 1 (ダブルが有効)、シングルエンド入力バッファ | 5    | 250   |        |

| $V_{OSCin}$      | OSCin 入力電圧 (6)         | シングルエンド入力バッファ                     | 0.3  | 3.6   | Vpp    |

|                  |                        | 差動入力バッファ                          | 0.1  | 1     |        |

| $f_{MULTin}$     | マルチプライヤの入力周波数          |                                   | 30   | 70    | MHz    |

| $f_{MULTout}$    | マルチプライヤの出力周波数          | MULT $\geq 3$                     | 180  | 250   |        |

| <b>PLL</b>       |                        |                                   |      |       |        |

| $f_{PD}$         | 位相検出器の周波数 (7)          | 整数チャネル                            | 5    | 400   | MHz    |

|                  |                        | 1 次および 2 次変調器                     | 5    | 300   |        |

|                  |                        | 3 次変調器                            | 5    | 225   |        |

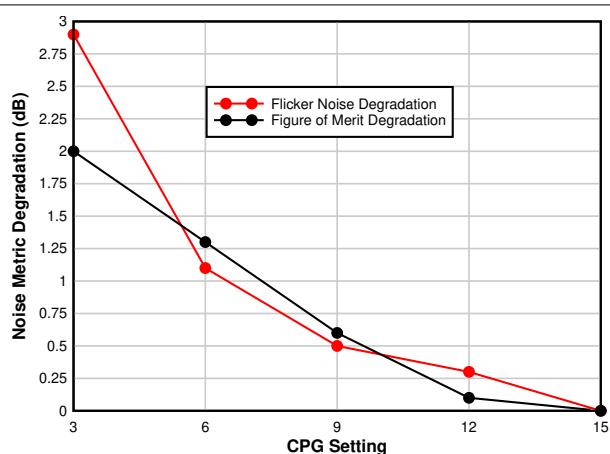

| $I_{CPout}$      | チャージ・ポンプの電流            | CPG = 1                           | 1.4  |       | mA     |

|                  |                        | CPG = 8                           | 2.8  |       |        |

|                  |                        | CPG = 4                           | 5.6  |       |        |

|                  |                        | CPG = 12                          | 8.4  |       |        |

|                  |                        | CPG = 15                          | 15.4 |       |        |

| $PN_{PLL\_1/f}$  | 正規化された PLL 1/f ノイズ (8) |                                   | -134 |       | dBc/Hz |

| $PN_{PLL\_Flat}$ | 正規化された PLL ノイズ・フロア (8) | 整数チャネル (9)                        | -236 |       |        |

|                  |                        | 分数チャネル (10)                       | -236 |       |        |

| $f_{RFIN}$       | RFIN の入力周波数            |                                   | 1000 | 22600 | MHz    |

| $P_{RFIN}$       | RFIN の入力電力             |                                   | -10  | 5     | dBm    |

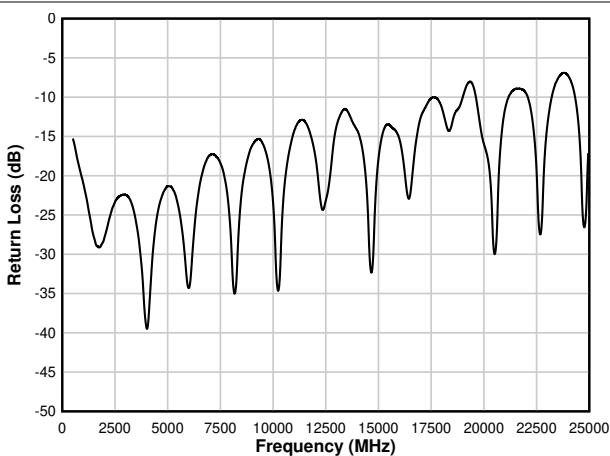

| $RL_{RFIN}$      | RFIN リターン・ロス           | $2GHz \leq f_{RFIN} \leq 22GHz$   |      | -8    | dB     |

| $f_{PFDIN}$      | PFDIN の入力周波数           |                                   | 20   | 2000  | MHz    |

| $V_{PFDIN}$      | PFDIN 入力電圧             |                                   | 0.2  | 2     | Vpp    |

| <b>VCO</b>       |                        |                                   |      |       |        |

| $f_{VCO}$        | VCO 周波数                |                                   | 5650 | 11300 | MHz    |

3.15V  $\leq V_{CC} \leq$  3.45V、-40°C  $\leq T_A \leq$  85°C。標準値は  $V_{CC} = 3.3V$ 、25°Cでのものです (特に記述のない限り)。

| パラメータ               |                  | テスト条件                                                                                                                         | 最小値    | 標準値    | 最大値 | 単位 |

|---------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------|--------|--------|-----|----|

| PN <sub>VCO</sub>   | 開ループ VCO 位相ノイズ   | $f_{VCO} = 6.0\text{GHz}$                                                                                                     | 10kHz  | -77.0  |     |    |

|                     |                  |                                                                                                                               | 100kHz | -110.3 |     |    |

|                     |                  |                                                                                                                               | 1MHz   | -131.9 |     |    |

|                     |                  |                                                                                                                               | 10MHz  | -151.0 |     |    |

|                     |                  |                                                                                                                               | 100MHz | -159.5 |     |    |

|                     |                  | $f_{VCO} = 6.8\text{GHz}$                                                                                                     | 10kHz  | -76.5  |     |    |

|                     |                  |                                                                                                                               | 100kHz | -109.3 |     |    |

|                     |                  |                                                                                                                               | 1MHz   | -130.7 |     |    |

|                     |                  |                                                                                                                               | 10MHz  | -149.8 |     |    |

|                     |                  |                                                                                                                               | 100MHz | -159.3 |     |    |

|                     |                  | $f_{VCO} = 7.6\text{GHz}$                                                                                                     | 10kHz  | -75.8  |     |    |

|                     |                  |                                                                                                                               | 100kHz | -108.5 |     |    |

|                     |                  |                                                                                                                               | 1MHz   | -130.2 |     |    |

|                     |                  |                                                                                                                               | 10MHz  | -149.2 |     |    |

|                     |                  |                                                                                                                               | 100MHz | -159.2 |     |    |

|                     |                  | $f_{VCO} = 8.4\text{GHz}$                                                                                                     | 10kHz  | -74.7  |     |    |

|                     |                  |                                                                                                                               | 100kHz | -107.6 |     |    |

|                     |                  |                                                                                                                               | 1MHz   | -129.4 |     |    |

|                     |                  |                                                                                                                               | 10MHz  | -148.8 |     |    |

|                     |                  |                                                                                                                               | 100MHz | -159.0 |     |    |

|                     |                  | $f_{VCO} = 9.4\text{GHz}$                                                                                                     | 10kHz  | -76.0  |     |    |

|                     |                  |                                                                                                                               | 100kHz | -105.5 |     |    |

|                     |                  |                                                                                                                               | 1MHz   | -128.0 |     |    |

|                     |                  |                                                                                                                               | 10MHz  | -147.4 |     |    |

|                     |                  |                                                                                                                               | 100MHz | -157.9 |     |    |

|                     |                  | $f_{VCO} = 10.2\text{GHz}$                                                                                                    | 10kHz  | -75.9  |     |    |

|                     |                  |                                                                                                                               | 100kHz | -105.6 |     |    |

|                     |                  |                                                                                                                               | 1MHz   | -127.5 |     |    |

|                     |                  |                                                                                                                               | 10MHz  | -146.8 |     |    |

|                     |                  |                                                                                                                               | 100MHz | -157.6 |     |    |

|                     |                  | $f_{VCO} = 11.2\text{GHz}$                                                                                                    | 10kHz  | -75.4  |     |    |

|                     |                  |                                                                                                                               | 100kHz | -104.4 |     |    |

|                     |                  |                                                                                                                               | 1MHz   | -126.4 |     |    |

|                     |                  |                                                                                                                               | 10MHz  | -145.8 |     |    |

|                     |                  |                                                                                                                               | 100MHz | -156.5 |     |    |

| K <sub>VCO</sub>    | VCO ゲイン          | $f_{VCO} = 6.0\text{GHz}$                                                                                                     |        | 95     |     |    |

|                     |                  | $f_{VCO} = 6.8\text{GHz}$                                                                                                     |        | 108    |     |    |

|                     |                  | $f_{VCO} = 7.6\text{GHz}$                                                                                                     |        | 131    |     |    |

|                     |                  | $f_{VCO} = 8.4\text{GHz}$                                                                                                     |        | 140    |     |    |

|                     |                  | $f_{VCO} = 9.4\text{GHz}$                                                                                                     |        | 149    |     |    |

|                     |                  | $f_{VCO} = 10.2\text{GHz}$                                                                                                    |        | 156    |     |    |

|                     |                  | $f_{VCO} = 11.2\text{GHz}$                                                                                                    |        | 139    |     |    |

| t <sub>VCOcal</sub> | VCO のキャリブレーション時間 | $f_{OSCin} = f_{PD} = 100\text{MHz}$ 、<br>5.65GHz と 11.3GHz の間で切り替え、<br>インスタント・キャリブレーションを使用、<br>VbiasVCO ピンに 0.47μF のコンデンサを接続 |        | 2.5    |     | μs |

$3.15V \leq V_{CC} \leq 3.45V$ 、 $-40^{\circ}C \leq T_A \leq 85^{\circ}C$ 。標準値は  $V_{CC} = 3.3V$ 、 $25^{\circ}C$  のものです (特に記述のない限り)。

| パラメータ                                            |                               | テスト条件                                                | 最小値                                                           | 標準値            | 最大値 | 単位      |

|--------------------------------------------------|-------------------------------|------------------------------------------------------|---------------------------------------------------------------|----------------|-----|---------|

| $ \Delta_{TC}L $                                 |                               | 許容される温度ドリフト (11)                                     | $VCO$ の再キャリブレーションなし、 $-40^{\circ}C \leq T_A \leq 85^{\circ}C$ |                | 125 | °C      |

| <b>RF 出力</b>                                     |                               |                                                      |                                                               |                |     |         |

| $f_{OUT}$                                        | RF 出力周波数                      |                                                      | 45                                                            | 22600          | MHz |         |

| $P_{OUT}$                                        | シングルエンド出力電力 (12)              | $f_{OUT} = 22GHz$                                    | 3                                                             |                |     | dBm     |

|                                                  |                               | $f_{OUT} = 11GHz$                                    | 5                                                             |                |     |         |

|                                                  |                               | $f_{OUT} \leq 5.5GHz$                                | 6                                                             |                |     |         |

| $H_{1/2}$                                        | 1/2 調波 (13)                   | $f_{OUT} = 2 \times f_{VCO} = 22GHz$                 | -45                                                           |                |     | dBc     |

| $H_{3/2}$                                        | 3/2 調波                        | $f_{OUT} = 2 \times f_{VCO} = 11.3GHz \sim 22.6GHz$  | -65                                                           |                |     |         |

| H2                                               | 2 次高調波                        | $f_{VCO} = f_{OUT} = 11GHz$                          | -20                                                           |                |     |         |

|                                                  |                               | $f_{VCO} = 11GHz, f_{OUT} = 5.5GHz$                  | -35                                                           |                |     |         |

| H3                                               | 3 次高調波                        | $f_{OUT} = 2 \times f_{VCO} = 11.3GHz \sim 22.6GHz$  | -25                                                           |                |     |         |

|                                                  |                               | $f_{VCO} = f_{OUT} = 11GHz$                          | -20                                                           |                |     |         |

| $P_{MUTE}$                                       | 出力がミュート状態のときのシングルエンド出力電力 (12) | $f_{OUT} = 22GHz$                                    | -32                                                           |                |     | dBm     |

|                                                  |                               | $f_{OUT} = 11GHz$                                    | -32                                                           |                |     |         |

|                                                  |                               | $f_{OUT} = 5.5GHz$                                   | -53                                                           |                |     |         |

| $t_{MUTE}$                                       | MUTE のイネーブル時間                 | $f_{OUT} = 11GHz$                                    | 200                                                           |                |     | ns      |

| $t_{unMUTE}$                                     | MUTE のディスエーブル時間               | $f_{OUT} = 11GHz$                                    | 200                                                           |                |     |         |

| isoCH                                            | チャネル間絶縁                       | $f_{OUTA} = 11GHz, f_{OUTB} = 5.5GHz, OUTx\_PWR = 7$ | -40                                                           |                |     | dBc     |

| <b>位相同期</b>                                      |                               |                                                      |                                                               |                |     |         |

| $f_{OSCin SYNC}$                                 | OSCin の入力周波数、SYNC 付き          | カテゴリ 3                                               | 5                                                             | 200            | MHz |         |

| <b>デジタル・インターフェイス (CE、SCK、SDI、CS#、PSYNC、MUTE)</b> |                               |                                                      |                                                               |                |     |         |

| $V_{IH}$                                         | High レベル入力電圧                  |                                                      | 1.2                                                           | $V_{CC}$       |     | V       |

| $V_{IL}$                                         | Low レベル入力電圧                   |                                                      |                                                               | 0.6            |     |         |

| $I_{IH}$                                         | High レベル入力電流                  | CS#、MUTE、CE                                          |                                                               | 25             |     | $\mu A$ |

|                                                  |                               | SCK、SDI、PSYNC                                        |                                                               | 70             |     |         |

| $I_{IL}$                                         | Low レベル入力電流                   |                                                      | -1                                                            |                |     |         |

| $V_{OH}$                                         | High レベル出力電圧                  | MUXout、LD                                            | 負荷電流 = -3mA                                                   | $V_{CC} - 0.5$ |     | V       |

| $V_{OL}$                                         | Low レベル出力電圧                   |                                                      | 負荷電流 = 3mA                                                    |                | 0.4 |         |

- (1)  $f_{OSCin} = f_{PD} = 100MHz, f_{VCO} = f_{OUT} = 11GHz, P_{OUT} = 0dBm, OSC\_2X = 0, MULT = 1$ 。

- (2)  $f_{OSCin} = f_{PD} = 100MHz, f_{VCO} = 11GHz, f_{OUT} = 5.5GHz, P_{OUT} = 0dBm, OSC\_2X = 0, MULT = 1$ 。

- (3)  $f_{OSCin} = f_{PD} = 100MHz, f_{VCO} = 11GHz, f_{OUT} = 22GHz, P_{OUT} = 0dBm, OSC\_2X = 1, MULT = 1$ 。

- (4)  $f_{OSCin} = f_{PD} = 100MHz, f_{RFin} = 11GHz, f_{OUT} = 11GHz$  (外部 VCO から)、 $OSC\_2X = 0, MULT = 1$ 。

- (5)  $f_{OSCin} = f_{PD} = 100MHz, f_{PFDin} = 2GHz, f_{OUT} = 11GHz$  (外部 VCO から)、 $OSC\_2X = 0, MULT = 1$ 。

- (6) OSCin 入力電圧の定義については、「アプリケーション」セクションを参照してください。

- (7) VCO 周波数が低い場合、N デバイダの最小値によって位相検出器の周波数が制限される可能性があります。

- (8) 広いループ帯域幅を使用して、高スルーレートのクリーンな OSCin 信号で測定。ノイズ指標は、無限のループ帯域幅について、PLL ノイズを次のようにモデル化します:  $PLL\_Total = 10 \log[10(PLL\_Flat/10) + 10(PLL\_Flicker/10)]$ 、 $PLL\_Flat = PN1Hz + 20 \log(N) + 10 \times \log(f_{PD})$ 、 $PLL\_Flicker = PN10kHz - 10 \log(Offset / 10kHz) + 20 \log(f_{OUT} / 1GHz)$ 。

- (9)  $f_{OSCin} = 100MHz, f_{PD} = 200MHz, f_{VCO} = f_{OUT} = 11GHz$ 。

- (10)  $f_{OSCin} = f_{PD} = 100MHz, f_{VCO} = f_{OUT} = 10.999GHz$ 、分数分母 = 1000。

- (11) 実製品の検査は行っていません。特性により保証されています。許容温度ドリフトとは、本デバイスを初期温度でプログラミングすれば、その温度ドリフトが発生しても再プログラミングすることなく本デバイスをロック状態に維持できる温度ドリフトを意味します。許容温度ドリフトは温度によって増減する可能性があり、本仕様は本デバイスの推奨動作範囲外の温度には適用されません。

- (12) RF 出力差動ペア・ピンのどちらかで測定し、未使用的ピンは  $50\Omega$  終端します。詳細については、「アプリケーション」セクションを参照してください。

- (13) 1 つの RF 出力がアクティブな場合。JSO-51-471/6S バランを使用して差動で測定されます。条件に応じてこの値がどのように変化するかについては、代表的な性能プロットを参照してください。

## 6.6 タイミング要件

$3.15V \leq V_{CC} \leq 3.45V$ 、 $-40^{\circ}C \leq T_A \leq 85^{\circ}C$ 。標準値は  $V_{CC} = 3.3V$ 、 $25^{\circ}C$  のものです (特に記述のない限り)。

| パラメータ                           | テスト条件                  | 最小値 | 公称値 | 最大値 | 単位  |

|---------------------------------|------------------------|-----|-----|-----|-----|

| <b>シリアル・インターフェイスの書き込みタイミング</b>  |                        |     |     |     |     |

| $f_{SCK}$                       | SCK 周波数                |     |     | 40  | MHz |

| $t_{CE}$                        | SCK から CSB Lowまでの時間    |     | 5   |     | ns  |

| $t_{CS}$                        | SDI から SCK までのセットアップ時間 |     | 2   |     | ns  |

| $t_{CH}$                        | SDI から SCK までのホールド時間   |     | 2   |     | ns  |

| $t_{CWH}$                       | SCK パルス幅 High          |     | 10  |     | ns  |

| $t_{CWL}$                       | SCK パルス幅 Low           |     | 10  |     | ns  |

| $t_{CES}$                       | CSB から SCK までのセットアップ時間 |     | 10  |     | ns  |

| $t_{EWH}$                       | CSB パルス幅 High          |     | 3   |     | ns  |

| <b>シリアル・インターフェイスの読み出しタイミング</b>  |                        |     |     |     |     |

| $f_{SCK}$                       | SCK 周波数                |     |     | 40  | MHz |

| $t_{CE}$                        | SCK から CSB Lowまでの時間    |     | 5   |     | ns  |

| $t_{CS}$                        | SDI から SCK までのセットアップ時間 |     | 2   |     | ns  |

| $t_{CH}$                        | SDI から SCK までのホールド時間   |     | 2   |     | ns  |

| $t_{CWH}$                       | SCK パルス幅 High          |     | 10  |     | ns  |

| $t_{CWL}$                       | SCK パルス幅 Low           |     | 10  |     | ns  |

| $t_{CES}$                       | CSB から SCK までのセットアップ時間 |     | 10  |     | ns  |

| $t_{EWH}$                       | CSB パルス幅 High          |     | 3   |     | ns  |

| $t_{OD}$                        | SCK から MUXout までの遅延時間  |     |     | 10  | ns  |

| <b>SYNC および SYSREFREQ タイミング</b> |                        |     |     |     |     |

| $t_{CS}$                        | ピンから OSCin までのセットアップ時間 |     | 2.5 |     | ns  |

| $t_{CH}$                        | ピンから OSCin までのホールド時間   |     | 2   |     | ns  |

## 6.7 代表的特性

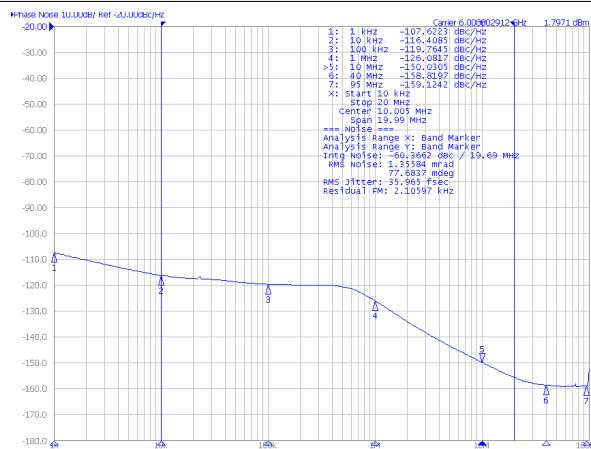

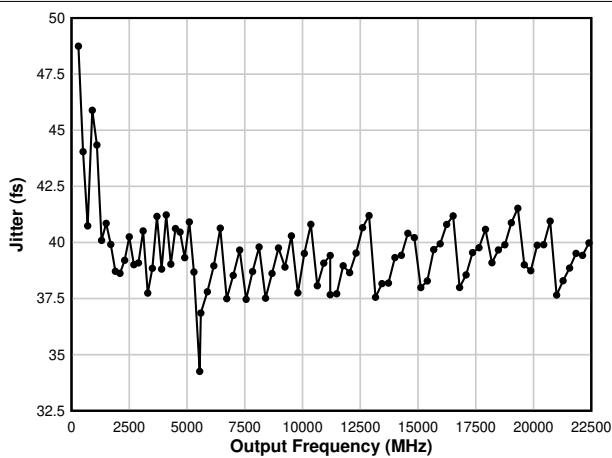

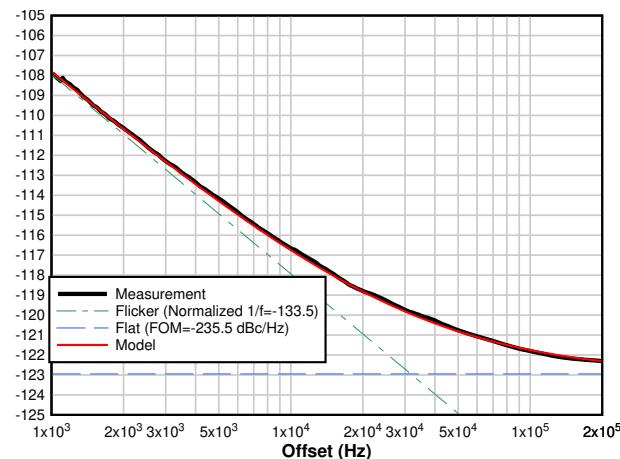

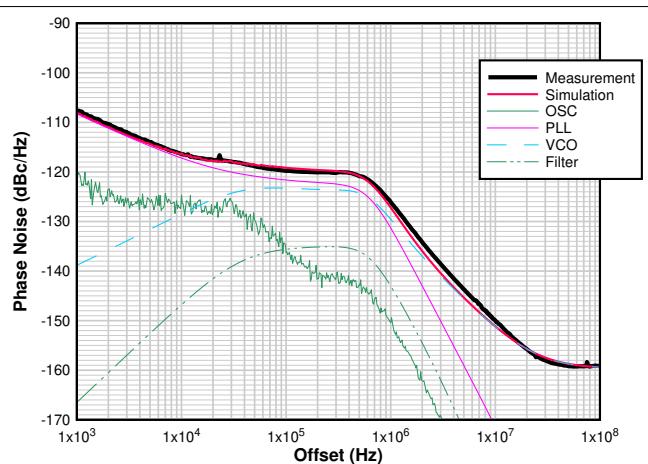

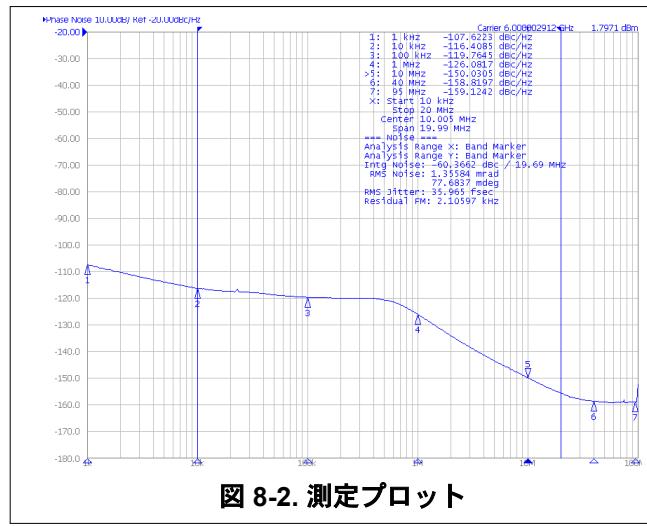

$f_{\text{OUT}} = 6\text{GHz}$ 、 $f_{\text{PD}} = 200\text{MHz}$ 、ジッタ = 36fs、12kHz~20MHz

図 6-1. 閉ループのノイズ

統合範囲は 12kHz~20MHz

図 6-2. 統合ジッタ

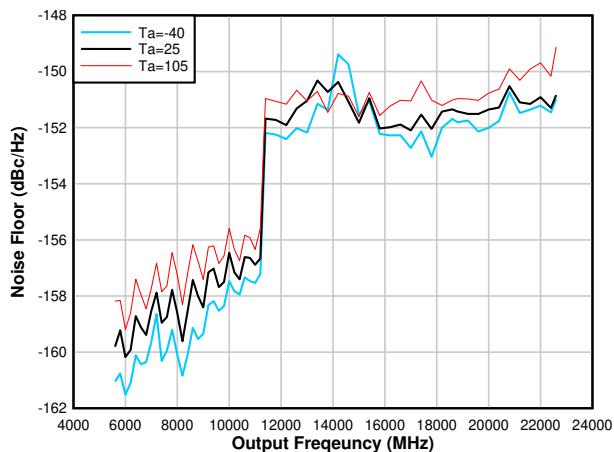

図 6-3. ノイズ・フロア

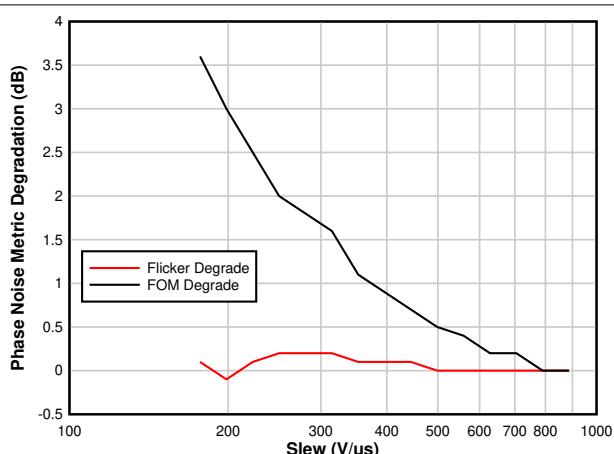

$f_{\text{osc}} = 100\text{MHz}$ 、 $f_{\text{PD}} = 200\text{MHz}$ 、 $f_{\text{OUT}} = 6\text{GHz}$ 、OSC\_2X = 1

入力ダブルを使用すると、PLL ノイズ指標がわずかに低下します。

図 6-4. PLL ノイズ指標

図 6-5. PLL ノイズ指標の低下と OSCin スルーレートとの関係

図 6-6. PLL ノイズ指標の低下とチャージ・ポンプのゲインとの関係

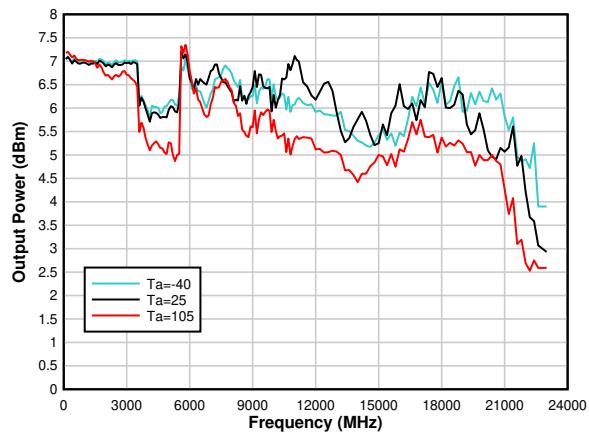

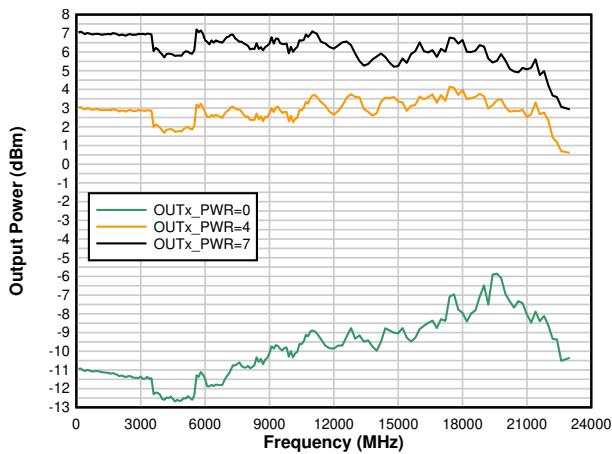

シングルエンド、OUTx\_PWR = 7、基板損失をディエンベッド

図 6-7. 出力電力と温度との関係

図 6-8. 出力電力と OUTx\_PWR との関係

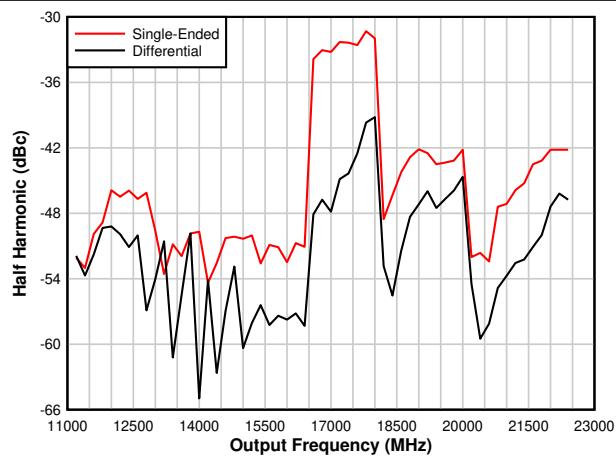

図 6-9. ダブルを有効にしたときの出力の 1/2 調波

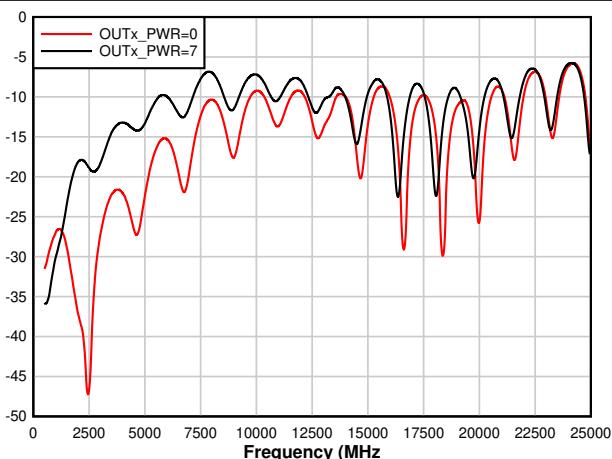

図 6-10. RF 出力のリターン・ロス

図 6-11. PFDIN ピンの入力感度

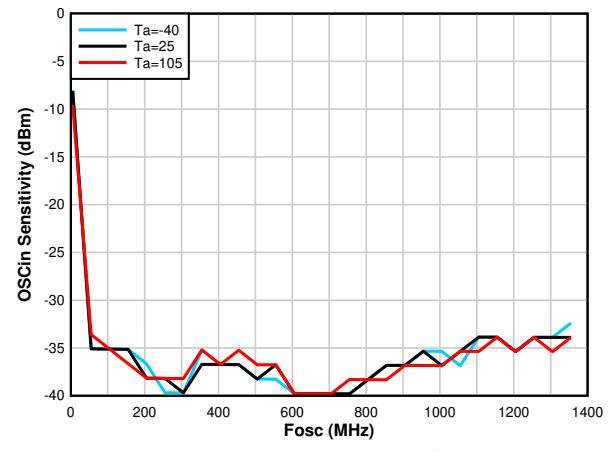

図 6-12. OSCin の入力感度

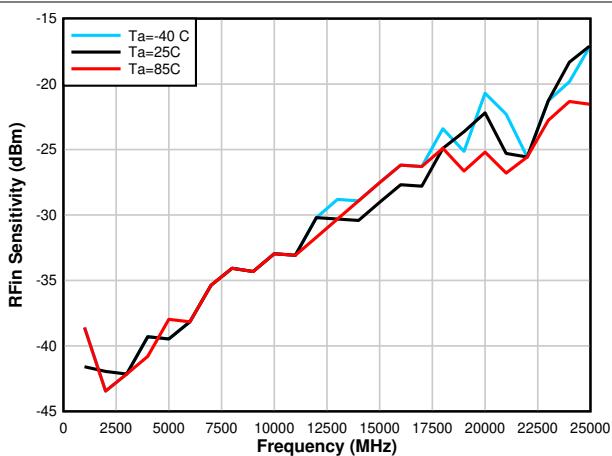

図 6-13. RFIN の入力感度

図 6-14. RFIN のリターン・ロス

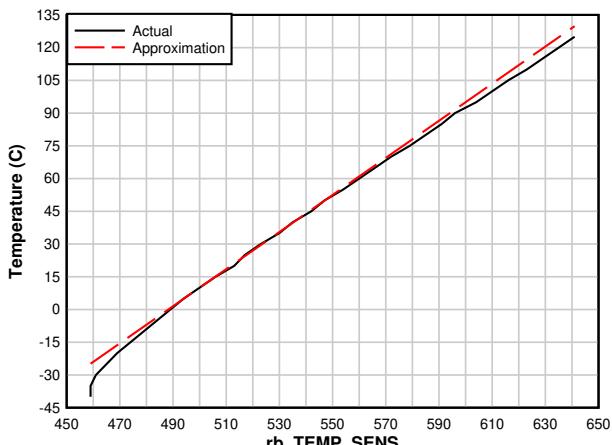

近似値 =  $0.85 * \text{rb\_TEMP\_SENS} - 415$

図 6-15. 温度センサの読み戻し

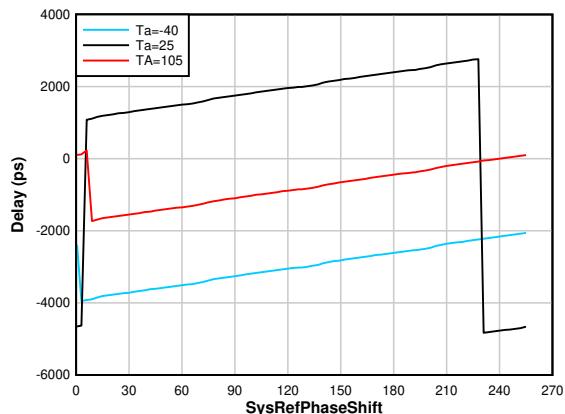

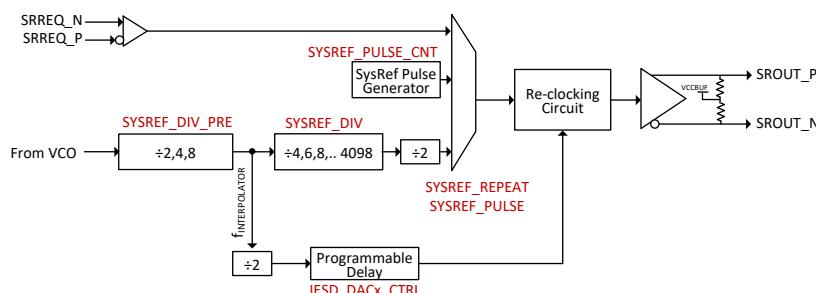

$f_{VCO}=8.4\text{GHz}$ 、SYSREF\_DIV\_PRE = 8、ステップ・サイズ = 7.6ps

図 6-16. SysRef 遅延と温度との関係

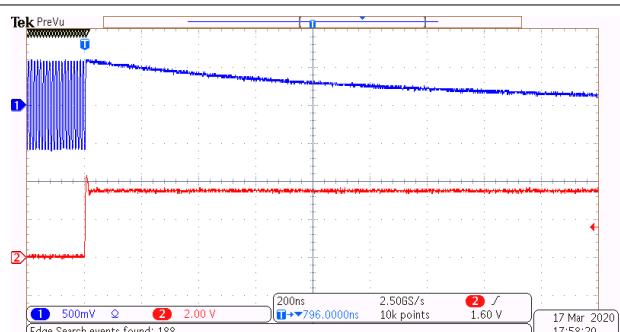

出力は 200ns を十分に下回る時間でミュートされます。

図 6-17. MUTE ピンの出力ディスエーブル時間

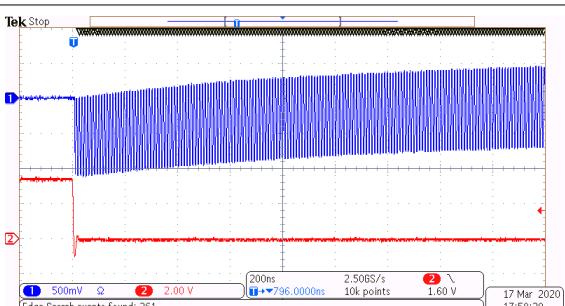

出力は 200μs 未満でミュート解除されます。より小さい AC カップリング・コンデンサを使用している場合、DC バイアス・レベルはさらに速く安定します。

図 6-18. MUTE ピンの出力イネーブル時間

## 7 詳細説明

### 7.1 概要

LMX2820 は、VCO と出力デバイダを内蔵した高性能で広帯域の周波数シンセサイザです。VCO は 5.65GHz～11.3GHz で動作し、出力デバイダおよびダブルと組み合わせることで、45MHz～22.6GHz の範囲の任意の周波数を生成できます。入力バスには、2 つのデバイダと 1 つのマルチプライヤがあり、周波数を柔軟に計画できます。また、マルチプライヤで周波数を整数境界から遠ざけると、スプリアスを低減できます。PLL は分数 N PLL で、最高 3 次までのプログラム可能なデルタ・シグマ変調器が搭載されています。分数分母は 32 ビット長でプログラムでき、1Hz 未満の分解能で微細な周波数ステップを容易に実現でき、1/3、7/1000 などの正確な分数も実現できます。位相周波数検出器は、分数モードでは 300MHz、整数モードでは 400MHz まで使用できますが、N デバイダの最小値も考慮する必要があります。決定論的または調整可能な位相が要求されるアプリケーションでは、PSYNC ピンを使用して、OSCIN ピンと RFOUT ピンとの位相関係を決定論的にできます。この設定を行うと、VCO 周期を分数分母で除算した、ごく細かいステップで、位相を調整できます。超高速の VCO キャリブレーションは、周波数をスイープする必要がある、または周波数が突然変化するアプリケーション用に設計されたものです。JESD204B サポートとして、SROUT 出力を使用して差動 SYSREF 出力を作成できます。この出力は単一のパルスまたは一連のパルスで、出力信号の立ち上がりエッジから、プログラムにより決定された距離だけ離れて発生します。LMX2820 デバイスは 3.3V 単一電源のみで動作します。内蔵 LDO によって内部電源が供給されるため、高性能の外部 LDO は不要です。SPI インターフェイスのデジタル・ロジックは、1.8V～3.3V の電圧レベルと互換性があります。デバイダ、マルチプライヤ、分数設定の範囲のいくつかを、表 7-1 に示します。

**表 7-1. デバイダ、マルチプライヤ、分数設定**

| ブロック     | サブブロック      | フィールド          | 最小値         | 最大値                       | 備考                                                                                        |

|----------|-------------|----------------|-------------|---------------------------|-------------------------------------------------------------------------------------------|

| 入力バス     | ダブル         | OSC_2X         | 0<br>(= 1X) | 1 (= 2X)                  | 低ノイズのダブルを使用して、位相検出器の周波数を高くすることで位相ノイズを改善し、スプリアスを回避できます。                                    |

|          | プリ R デバイダ   | PLL_R_PRE      | 1           | 4095                      | プリ R デバイダは、入力マルチプライヤやポスト R デバイダに対して、周波数が高すぎる場合のみ使用してください。                                 |

|          | 入力マルチプライヤ   | MULT           | 3           | 7                         | 入力マルチプライヤはスプリアスを回避するため効果的ですが、PLL ノイズが増加します。                                               |

|          | ポスト R デバイダ  | PLL_R          | 1           | 255                       | このデバイダの最高入力周波数は、 $PLL\_R = 2$ で 500MHz、 $PLL\_R > 2$ で 250MHz です。必要なら、プリ R デバイダを使用してください。 |

| N デバイダ   | N デバイダ      | PLL_N          | $\geq 12$   | 32767                     | 最小分周値は、変調器の次数、VCO 周波数 / コア、および内部 / 外部 VCO の選択によって決定されます。                                  |

|          | 分数分子        | PLL_NUM        | 1           | $2^{32} - 1 = 4294967295$ | PLL_NUM は PLL_DEN より小さくする必要があります。                                                         |

|          | 分数分母        | PLL_DEN        | 1           | $2^{32} - 1 = 4294967295$ | 分数分母はプログラム可能で、1 から $2^{32} - 1$ までの範囲で任意の値に設定できます。固定の分母ではありません。                           |

|          | 分数の次数       | MASH_ORDER     | 0           | 3                         | 分数の次数は 0 から 3 までの範囲でプログラムでき、0 は整数モードです。                                                   |

| PFDIN バス | PFD 入力デバイダ  | EXT_PFD_DIV    | 1           | 63                        |                                                                                           |

| 外部 VCO   | 外部 VCO デバイダ | EXT_VCO_DIV    | 1           | 2                         | VCO 周波数が 11.3GHz を超える場合は、2 で分周します。それ以外の場合は 1 で分周します（バイパス）。                                |

| SYSREF   | プレデバイダ      | SYSREF_DIV_PRE | 1           | 4                         | 1、2、4 のみをサポートします。このブロックには、2 による分周が追加されています。プレデバイダの合計値は $2 \times SYSREF\_DIV\_PRE$ です。    |

|          | デバイダ        | SYSREF_DIV     | 0           | 2047                      | 総合分周値は $2 + SYSREF\_DIV$ です。                                                              |

|          | 追加デバイダ      | なし             | 4           | 4                         | 4 に固定のデバイダです。                                                                             |

表 7-1. デバイダ、マルチプライヤ、分数設定 (continued)

| ブロック | サブブロック    | フィールド  | 最小値 | 最大値   | 備考                                                                                      |

|------|-----------|--------|-----|-------|-----------------------------------------------------------------------------------------|

| 出力   | OUTA デバイダ | CHDIVA | 2   | 128   | 2 のべき乗によるデバイダで、2、4、8、16、32、64、128 をサポートしています。                                           |

|      | OUTB デバイダ | CHDIVB | 2   | 128   | 2 のべき乗によるデバイダで、2、4、8、16、32、64、128 をサポートしています。                                           |

|      | 出力周波数     | n/a    | 45  | 22600 | 5.65GHz より低い周波数では、チャネル・デバイダが使用されます。5.65~11.23GHz は直接 VCO です。11.3~22.6GHz では出力ダブルを使用します。 |

## 7.2 機能ブロック図

## 7.3 機能説明

### 7.3.1 基準発振器入力

OSCIN ピンは、本デバイスへの周波数基準入力として使用されます。入力は高インピーダンスで、ピンに AC カップリング・キャップが必要です。CMOS クロックまたは XO は、シングルエンド接続で OSCIN ピンを駆動できます。差動クロック入力もサポートされているため、TI の LMK シリーズ・クロック・デバイスなどの高性能システム・クロック・デバイスと簡単に接続できます。OSCIN 信号は、VCO のキャリブレーションでクロックとして使用されるため、VCO のキャリブレーションが必要なときは、OSCIN ピンに正しい基準信号を印加する必要があります。

### 7.3.2 入力パス

基準パスは、OSCIN ダブル (OSC\_2X)、プリ R デバイダ、マルチプライヤ (MULT)、およびポスト R デバイダで構成されます。OSCIN ダブル (OSC\_2X) は、低い OSCIN の周波数を 2 倍に上げることができます。プリ R (PLL\_R\_PRE) およびポスト R (PLL\_R) のデバイダはどちらも周波数を分周して下げ、マルチプライヤ (MULT) は周波数を倍増して上げます。マルチプライヤを追加する目的は、整数境界スプリアスを小さくすること、または位相検出器周波数を上げることです。位相検出器の周波数  $f_{PD}$  は、式 1 で計算されます。

$$f_{PD} = f_{OSC} \times OSC\_2X \times MULT / (PLL\_R\_PRE \times PLL\_R) \quad (1)$$

### 7.3.2.1 入力バス・ダブラ (OSC\_2X)

OSCIN ダ布拉を使用すると、入力基準周波数を 2 倍にできます (最高 500MHz まで)。このダ布拉はノイズが最小限に抑えられており、位相検出器の周波数を上げて位相ノイズを改善し、スプリアスを回避するために役立ちます。位相検出器の周波数を高くすると、PLL 位相ノイズのフラットな部分が改善されます。入力バス・ダ布拉を使用するときは、いくつかの考慮事項があります。

- ダ布拉は、入力信号の立ち上がりエッジと立ち下がりエッジの両方で動作します。

- デューティ・サイクルは 50% に近くする必要があります。そうでない場合、スプリアスが非常に大きくなります。

- 入力バス・ダ布拉を使用すると、PLL のフリッカ・ノイズや性能指数が約 1dB 低下します。しかし、位相検出器周波数を上げることの利点は、この短所を上回ります。

### 7.3.2.2 プリ R デバイダ (PLL\_R\_PRE)

プリ R デバイダは、プログラム可能なマルチプライヤ (MULT) またはポスト R デバイダの入力に対して入力周波数が高すぎる場合に、入力周波数を下げるため使用されます。

### 7.3.2.3 プログラマブル入力マルチプライヤ (MULT)

MULT は、位相検出器の周波数をシフトして整数境界スプリアスを回避するために有用です。マルチプライヤでは、3、4、5、6、7 で乗算できます。入力マルチプライヤを使う際は、以下の点を考慮します。

- プログラマブル入力マルチプライヤは、入力バス・ダ布拉と同時に使用できません。

- プログラマブル入力マルチプライヤを使用すると、PLL 性能指数が約 8dB 低下します。これは PLL ノイズの改善ではなく、スプリアスの低減が目的です。

- プログラマブル入力マルチプライヤは、VCO 周波数が OSCIN 周波数の倍数に近くない場合に最も効果的です。

### 7.3.2.4 R デバイダ (PLL\_R)

ポスト R デバイダは、周波数をさらに位相検出器の周波数に分周します。PLL\_R = 2 で使用すると、このデバイダの最大入力周波数は 500MHz に制限されます。PLL\_R > 2 で使用すると、このデバイダの最大周波数は 250MHz に制限されます。

### 7.3.3 PLL 位相検出器とチャージ・ポンプ

位相検出器は、R デバイダと N デバイダの出力を比較し、2 つの信号が位相内で同期するまで、位相誤差に対応する補正電流を生成します。このチャージ・ポンプの電流はソフトウェアによって多くの異なるレベルにプログラム可能で、PLL の閉ループ帯域幅を変更できます。詳細については、「[セクション 8.1](#)」を参照してください。位相検出器の極性は、アクティブ・ループ・フィルタ・アプリケーションに合わせて構成可能です。

### 7.3.4 N デバイダとフラクショナル回路

この完全 N デバイダは、VCO 周波数を位相検出器周波数 ( $f_{PD}$ ) に分周します。この N デバイダの総合的な分周値 (総合 N 分周値) を変えると、VCO の出力周波数が変わります。総合 N 分周値は、式 2 に示すように整数部と分数部で構成されます。

$$N_{\text{Total}} = N_{\text{Integer}} + N_{\text{Fractional}} = \text{PLL\_N} + (\text{PLL\_NUM} / \text{PLL\_DEN}) \quad (2)$$

#### 7.3.4.1 整数 N 分周部 (PLL\_N)

分数と高周波数を処理するための総合 N 分周値の要件から、変調器の次数と VCO の周波数に基づく制限が存在します。

内部 VCO を使用する場合、N 分周の真の最小値は VCO コアによって決まります。VCO コアの周波数はプロセスによって多少変化するため、VCO コアについてのワーストケースの想定に基づいて計算を行うのが妥当です。

表 7-2. 内部 VCO の最小 N 分周値

| $f_{VCO}$    | ワーストケースのコア | MASH_ORDER = 0 | MASH_ORDER = 1 | MASH_ORDER = 2 | MASH_ORDER = 3 |

|--------------|------------|----------------|----------------|----------------|----------------|

| 5.65~6.35GHz | VCO1       | 12             | 18             | 19             | 24             |

| 6.35~7.3GHz  | VCO2       | 14             | 21             | 22             | 26             |

**表 7-2. 内部 VCO の最小 N 分周値 (continued)**

| $f_{VCO}$    | ワーストケースのコア | MASH_ORDER = 0 | MASH_ORDER = 1 | MASH_ORDER = 2 | MASH_ORDER = 3 |

|--------------|------------|----------------|----------------|----------------|----------------|

| 7.3~8.1GHz   | VCO3       | 16             | 23             | 24             | 26             |

| 8.1~9.0GHz   | VCO4       | 16             | 26             | 27             | 29             |

| 9.0~9.8GHz   | VCO5       | 18             | 28             | 29             | 31             |

| 9.8~10.6GHz  | VCO6       | 18             | 30             | 31             | 33             |

| 10.6~11.3GHz | VCO7       | 20             | 33             | 34             | 36             |

外部 VCO では、最小 N 分周がわずかに異なります。VCO 周波数が 11.3GHz より高い場合、EXTVCO\_DIV ビットをセットして、VCO 周波数を 2 で割る必要があります。

**表 7-3. 外部 VCO の最小 N デバイダ**

| $f_{RFIN} / (RFIN デバイダ)$ | MASH_ORDER = 0 | MASH_ORDER = 1 | MASH_ORDER = 2 | MASH_ORDER = 3 |

|--------------------------|----------------|----------------|----------------|----------------|

| 0.5~4GHz                 | 12             | 12             | 14             | 20             |

| 4~5.5GHz                 | 12             | 15             | 18             | 24             |

| 5.5~7GHz                 | 14             | 18             | 20             | 26             |

| 7~8.5GHz                 | 16             | 23             | 24             | 26             |

| 8.5~10GHz                | 20             | 28             | 29             | 35             |

| 10GHz~11.3GHz            | 20             | 32             | 33             | 35             |

#### 7.3.4.2 分数 N 分周部 (PLL\_NUM および PLL\_DEN)

N デバイダには分数補償が含まれており、 $1 \sim (2^{32} - 1)$  のあらゆる分数分母を実現できます。総合 N 分周値の分数部分は  $N_{Fractional} = PLL\_NUM / PLL\_DEN$  です。分母が大きいほど、出力の分解能ステップは細かくなります。たとえば、 $f_{PD} = 200MHz$  の場合、出力は  $200MHz / (2^{32} - 1) = 0.047Hz$  のステップでインクリメントできます。

#### 7.3.4.3 変調器の次数 (MASH\_ORDER)

分数変調器の次数はプログラマブルで、スプリアスに影響を与えます。理論的には、分数変調器の次数が大きいほど、低周波数のスプリアス・エネルギーが高周波数にプッシュされます。ただし、高次の変調器を使用するとノイズが増え、最小 N 分周比が大きくなります。変調器の次数が 1 より多い場合、FDEN の値によってはサブフラクショナル・スプリアスが発生することがあります。FDEN は、分数  $PLL\_NUM / PLL\_DEN$  を約分した後の分母の値です。

**表 7-4. MASH\_ORDER の選択に関する大まかなガイドライン**

| MASH_ORDER | 使用に適した状況                                                                                                                                                                                                                |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 整数モード      | 整数モード (MASH_ORDER = 0) は、分数回路が不要な場合に適しています。このモードでは、N デバイダの値を最小にできる利点があります。MASH_SEED が整数モードのときは、出力位相をシフトできないことに注意してください。                                                                                                 |

| 1 次変調器     | 1 次変調器は、分数分母が小さい状況に適しています。理論的には、 $FDEN < 7$ の場合、1 次変調器ですべての分数スプリアスが最小になります。分数が 2 で除算可能な場合はサブフラクショナル・スプリアスが存在し、プライマリ・スプリアスのレベルとのトレードオフになります。 $f_{PD} / FDEN$ のオフセットにあるプライマリ分数スプリアスがループ帯域幅を大きく外れている場合は、このモードが多くの場合には適切です。 |

| 2 次変調器     | 2 次変調器はスプリアスについて優れています。 $FDEN$ が奇数の場合、サブフラクショナル・スプリアスがないため、 $FDEN > 8$ の場合と $FDEN$ が奇数の場合、この点が有用な可能性があります。 $FDEN$ が、たとえば 1000000 のように非常に大きい場合、分数が十分にランダム化される可能性が高いため、3 次変調器によって N 分周値が過度に制限されなければ、検討する価値があります。          |

| 3 次変調器     | $FDEN > 9$ の場合と、 $FDEN$ が 3 で割り切れない場合、一般的な目的について、3 次変調器を出発点として検討してください。                                                                                                                                                 |

#### 7.3.5 LD ピンのロック検出

ロック検出は、PLL がロックされているかどうかを大まかに示すものです。キャリブレーション・ステータスと間接 VTUNE という 2 つの一般的なタイプのロック検出をサポートしています。VCO がキャリブレーションを開始すると、キャリブレーション・ステータスのロック検出が Low で開始されます。LD\_VTUNE\_EN = 1 の場合は、追加の 4xLD\_DLY 位相検出器サ

イクルが、この遅延に追加されます。間接的な VTUNE ロック検出は、VTUNE ピンでの実際の電圧を模倣する間接的な内部電圧を作り出すことで行われます。この電圧が範囲外になると、VTUNE ロック検出が Low になります。キャリブレーション・ステータスと VTUNE ロック検出を組み合わせることもできます。フル・アシスト・モードやインスタンント・キャリブレーションなど、VCO キャリブレーションがバイパスされる状況では、このロック検出は VTUNE 機能のみを果たします。

### 7.3.6 MUXOUT ピンと読み戻し

読み戻しは、デバイスのステータスに関する情報を取得するために便利です。読み戻しが可能なフィールドは次のとおりです。

1. レジスタの値をそのまま読み出し、プログラミングが正しいことを確認する。

2. VCO ロック検出のステータス (rb\_LD)。

3. VCO のキャリブレーション情報 (rb\_VCO\_SEL, rb\_VCO\_CAPCTRL, rb\_VCO\_DACISET)。

4. ダイの温度 (rb\_TEMP\_SENS)。この機能を使用するには、TEMPSENSE = 1 を設定します。読み戻した温度は、式 3 で計算します。

$$\text{温度 } [^{\circ}\text{C}] = 0.85 \times \text{rb\_TEMP\_SENSE} - 415 \quad (3)$$

測定精度は  $\pm 5^{\circ}\text{C}$  です。

### 7.3.7 内部 VCO

LMX2820 には完全統合型 VCO が搭載されています。VCO はループ・フィルタから電圧を受け取り、周波数に変換します。VCO の周波数と他の周波数との間には、 $f_{\text{VCO}} = f_{\text{PD}} \times (\text{PLL\_N} + \text{PLL\_NUM} / \text{PLL\_DEN})$  という関係があります。

#### 7.3.7.1 VCO のキャリブレーション

VCO のチューニング・ゲインを減らして VCO の位相ノイズ性能を向上させるため、VCO の周波数範囲はいくつかの異なる周波数帯域に分周されています。5.65~11.3GHz の範囲は 1 オクターブをカバーしているため、デバイダは下限よりも低い周波数を扱えば済みます。このため、目標出力周波数に対して正しい周波数帯域を決定するための周波数キャリブレーションが必要となります。周波数のキャリブレーション・ルーチンは、R0 レジスタに FCAL\_EN = 1 がプログラムされると、常にアクティブになります。VCO のキャリブレーションを開始する前に、有効な OSCIN 信号が存在する必要があります。VCO には内部振幅のキャリブレーション・アルゴリズムも搭載されており、位相ノイズを最適化します。このアルゴリズムは、R0 レジスタがプログラムされたときにも常にアクティブになります。最適な内部設定は、温度によって変化します。連続ロック ΔTCL の最大許容ドリフトは、電気的仕様に記載されています。このデバイスにおいて、125°C という数字は、推奨動作条件の下で動作させた場合に決してロックを失わないことを意味しています。

##### 7.3.7.1.1 VCO のゲインおよび範囲の決定

VCO のゲインはコアによって異なり、温度やプロセスによっても変化しますが、VCO のゲインの予測値については、表 7-5 に示す大まかなガイドラインがあります。

表 7-5. VCO のゲインと範囲の概要

| VCO コア | Fmin (MHz) | Fmax (MHz) | KvcoMax | KvcoMin |

|--------|------------|------------|---------|---------|

| VCO1   | 5650       | 6350       | 84      | 115     |

| VCO2   | 6350       | 7300       | 94      | 131     |

| VCO3   | 7300       | 8100       | 123     | 156     |

| VCO4   | 8100       | 9000       | 132     | 169     |

| VCO5   | 9000       | 9800       | 131     | 163     |

| VCO6   | 9800       | 10600      | 152     | 185     |

| VCO7   | 10600      | 11300      | 130     | 151     |

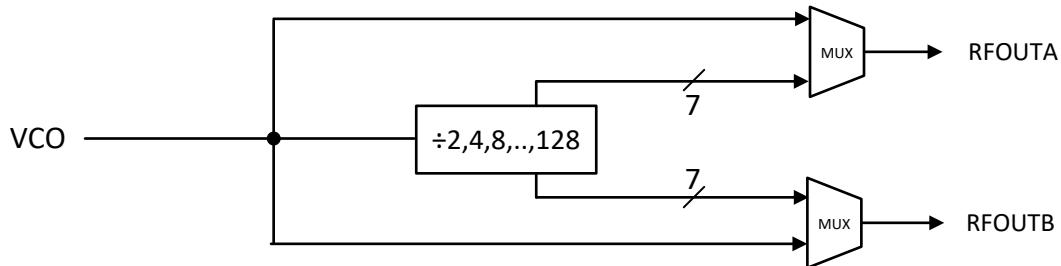

### 7.3.8 チャネル・デバイダ

チャネル・デバイダは実際には単一のデバイダで、複数のセグメントとタップ・ポイントがあり、RFOUTA と RFOUTB の間で共有されます。通常は、それぞれの分周値を別々に設定できますが、片方の出力について分周値 128 が選択される場合は例外として、もう 1 つの出力にも同じ分周値を指定する必要があります (ただし、チャネル・デバイダのバイパスは

可能です。それぞれの出力周波数が異なる場合、高い周波数の出力には、もう 1 つの出力と等しい周波数オフセットの場所に、分数調波スプリアスが発生することに注意してください。

図 7-1. チャネル・デバイダ

### 7.3.9 出力周波数ダブル

周波数ダブルは、VCO 周波数の 2 倍の出力周波数を生み出すために使用されるもので、**OUTx\_MUX = 2** のときに選択されます。VCO 周波数を 2 倍にすると、基本の（2 倍にならない）VCO 周波数が出力にリーカし、分数調波（0.5X）になります。これらの分数調波を最小化するために、調整可能なフィルタがあります。このフィルタは出力周波数を追跡し、この分数調波や、他の不要な高調波（1.5X、2X、3X など）をフィルタで排除します。この調整可能なフィルタのキャリブレーションは、VCO のキャリブレーションが完了すると自動的にトリガされます。

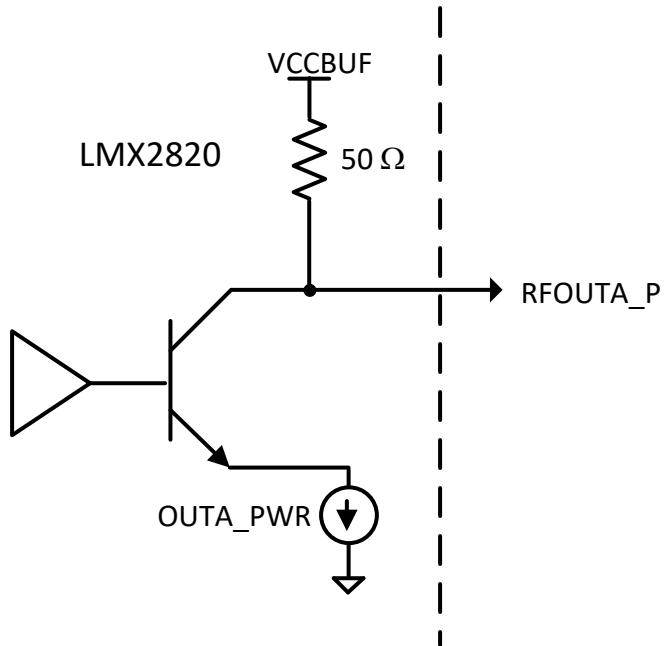

### 7.3.10 出力バッファ

出力バッファはオープンコレクタ・アキテクチャですが、デバイスには  $50\Omega$  のプルアップ抵抗が内蔵されています。低周波数では、出力インピーダンスが  $50\Omega$  と想定して問題ありませんが、周波数が高くなると寄生成分によって出力インピーダンスが変化する可能性があります。**OUTx\_PWR** プログラミング・フィールドはエミッタ電流を設定し、電力レベルを調整します。

図 7-2. 出力バッファの構造

### 7.3.11 パワーダウン・モード

LMX2820 は、CE ピンまたは POWERDOWN ビットを使用してパワーオンおよびパワーダウンできます。パワーダウン・モードでは、デバイスの大半がシャットダウンされます。ただし、パワーダウン・モードでは、デバイスにプログラミング情報が維持されており、電源ピンに引き続き電力が供給されていればプログラムも可能です。これによって、内部 LDO もパワ

一ダウントするため、POWERDOWNとともにレジスタ R0 をプログラムすると、FCAL\_EN = 1 の場合には VCO の再キャリブレーションが行われることに注意してください。この場合は、この動作が適切なバイアス・レベルの LDO で行われることを確保するため、レジスタ R0 を FCAL\_EN = 1 で再プログラミングする必要があります。インスタンス・キャリブレーションを使用する場合、レジスタ R0 の追加プログラミングは不要です。

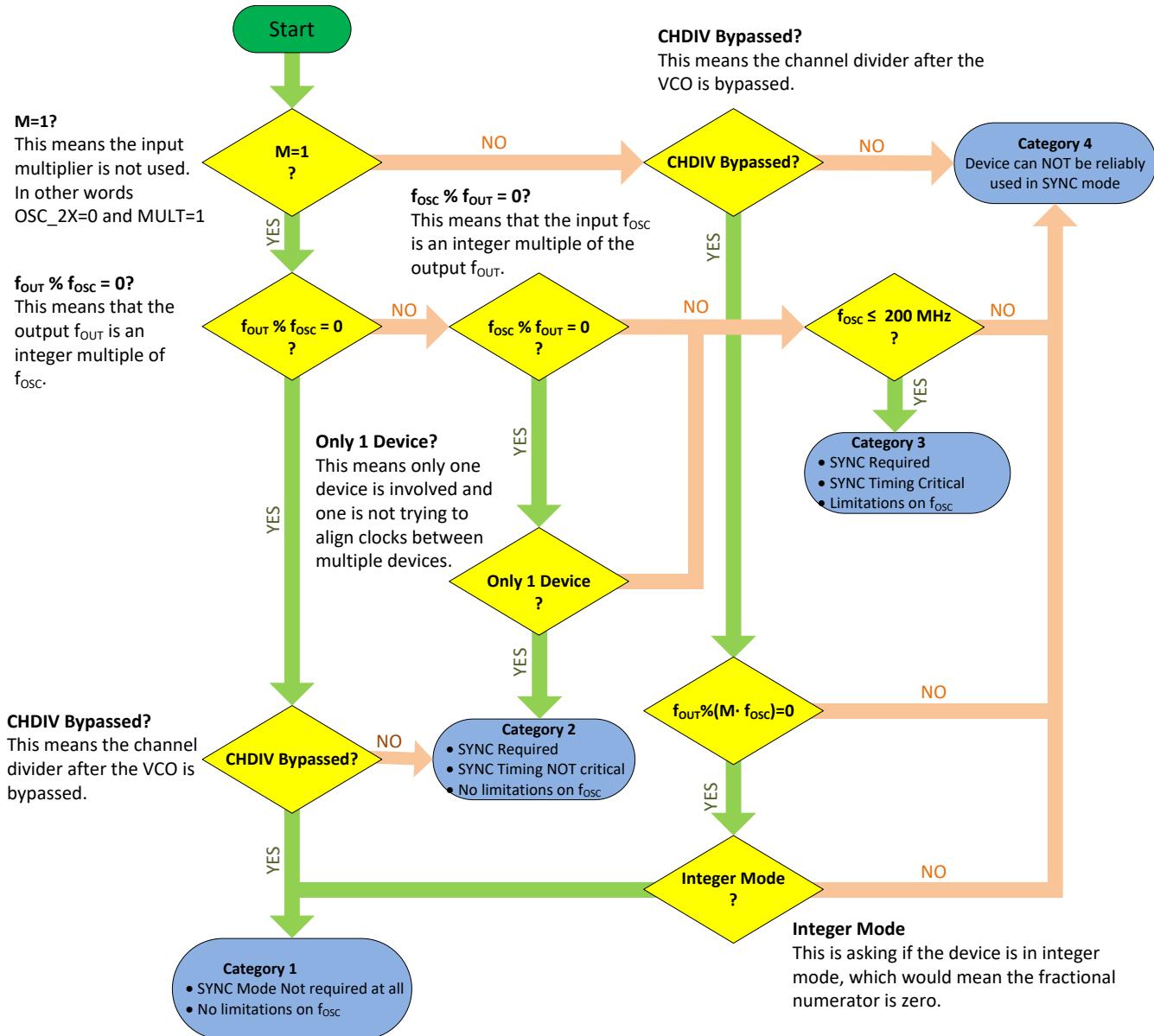

### 7.3.12 複数デバイスでの位相同期

多くの状況において、デバイスに決定論的な位相が存在することを確保するため、同期パルスが必要になります。位相同期の要件は、セットアップ条件によって異なります。同期パルスのタイミングが重要でない場合は、INPIN\_IGNORE ビットを切り替えることで、ソフトウェアにより行うことができます。タイミングが重要な場合はピンで行う必要があります。この場合、OSCIN ピンのセットアップおよびホールド時間も重要となります。以下のセクションでは、入力および出力周波数に応じた位相同期のカテゴリについて説明します。

#### 7.3.12.1 同期のカテゴリ

図 7-3. 同期のフローチャート

### 7.3.12.2 位相調整

#### 7.3.12.2.1 MASH\_SEED を使った位相シフト

MASH\_SEED ワードは、デルタ・シグマ変調器を使用して、入力基準電圧に対して出力信号の位相をシフトできます。SYNC パルスが（ソフトウェアまたはピンで）送信されるか、MASH が MASH\_RST\_N でリセットされると、この位相シフトは初期位相の 0 から開始されます。位相シフトは、MASH\_SEED に基づいて計算できます。

$$\text{度単位の位相シフト} = 360 \times (\text{MASH_SEED} / \text{PLL_DEN} / \text{CHDIV}) \quad (4)$$

MASH\_SEED には、いくつかの考慮事項があります。

- 位相シフトは PLL\_NUM = 0 で実行できますが、MASH\_ORDER は 0 より大きくする必要があります。

- MASH\_ORDER = 1 の場合、位相シフトは MASH\_SEED が PLL\_DEN の倍数のときのみ発生します。

- MASH\_SEED > 0 を設定すると、分数スプリアスに影響する可能性があります。PLL\_NUM = 0 で使用すると、分数スプリアスが発生することがあります。0 以外の分子で使用した場合、スプリアスが減る場合も、増える場合もあります。この効果は、TI の PLLatinum Sim ツールを使用してシミュレーションできます。

#### 7.3.12.2.2 静的と動的な位相調整の比較

MASH\_SEED ワードのプログラミングは累積的です。すなわち、プログラムされた値は現在の値に加算されます。MASH\_RST\_N ビットまたは VCO が再キャリブレーションされるとき、現在の値は常に MASH\_SEED に設定されます。静的な位相調整では、MASH\_SEED ワードを目的の値に設定し、MASH\_RST\_N ビットをトグルして、その値を適用します。動的な位相調整では、MASH\_SEED を小さい値に設定し、MASH\_SEED ワードを繰り返しプログラムして、MASH\_SEED の累積値に追加します。

#### 7.3.12.2.3 位相調整への微調整

位相同期とは、電源投入サイクルごと、および特定のプログラミング手順が実行されているときに、同じ位相関係を実現するプロセスを意味します。ただし、出力周波数が高く、周期が短い場合、できるだけ正確な結果を得るために、いくつかの調整を行うことがあります。位相同期の整合性が変化する原因として考えられるのは、VCO キャリブレーションで別の VCO コアとコンデンサが選択されることだけです。この場合、差異が約 10ps のバイモーダル分散が発生することがあります。この 10ps の差異が望ましくない場合は、インスタント・キャリブレーションをベースとする VCO キャリブレーションか、フル・アシスト VCO キャリブレーションを行うことで排除できます。

デバイスでの遅延時間は部品によって異なり、60ps 程度が考えられます。この部品ごとの差異は、MASH\_SEED によって調整できます。デバイスでの遅延の変動も +2.5ps/°C 程度で変化しますが、同じボード上のデバイスも同様の温度になっている可能性が高いため、ある程度同じ結果になります。要約すると、デバイスの遅延は部品内で一貫するように設計でき、残る誤差は MASH\_SEED を使用して調整できます。これが問題になるのは一般に、出力周波数が高く、周期が短い場合のみです。

### 7.3.13 SYSREF

LMX2820 は SYSREF 出力信号を生成でき、この信号は f<sub>OUT</sub> と同期され、遅延をプログラム可能です。この出力は、単一パルス、一連のパルス、または連続的なパルス・ストリームのいずれかです。SYSREF 機能を使用するには、最初に PHASE\_SYNC\_EN = 1 を設定して、PLL を同期モードにする必要があります。

図 7-4. SYSREF の機能図

SYSREF 機能では、SYSREF\_DIV\_PRE デバイダを使用して  $f_{INTERPOLATOR}$  が生成されます。この周波数は、SRREQ ピンの立ち上がり / 立ち下がりエッジのリクロックに使用されます。マスター・モードでは、 $f_{INTERPOLATOR}$  がさらに  $2 \times$  SYSREF\_DIV で除算され、有限な一連または連続的なパルス・ストリームが生成されます。

この遅延時間は、JESD\_DAC1\_CTRL、JESD\_DAC2\_CTRL、JESD\_DAC3\_CTRL、JESD\_DAC4\_CTRL ワードを使用してプログラムできます。これらのワードを連結して「SysRefPhaseShift」という大きなワードにすると、相対遅延が判明します。これらのワードの合計は常に 63 にする必要があります。遅延ステップのサイズは次のとおりです。

$$\text{SysRefDelayStepSize} = \text{SYSREF\_DIV\_PRE} / (126 * f_{VCO})$$

**表 7-6. SysRefPhaseShift と JESD\_DACx\_CTRL との比較**

| SysRefPhaseShift | JESD_DAC1_CTRL | JESD_DAC2_CTRL | JESD_DAC3_CTRL | JESD_DAC4_CTRL |

|------------------|----------------|----------------|----------------|----------------|

| 0                | 63             | 0              | 0              | 0              |

| 1                | 62             | 1              | 0              | 0              |

| ...              | ...            | ...            | 0              | 0              |

| 62               | 1              | 62             | 0              | 0              |

| 63               | 0              | 63             | 0              | 0              |

| 64               | 0              | 62             | 1              | 0              |

| ...              | 0              | ...            | ...            | 0              |

| 125              | 0              | 1              | 62             | 0              |

| 126              | 0              | 0              | 63             | 0              |

| 127              | 0              | 0              | 62             | 1              |

| ...              | 0              | 0              | ...            | ...            |

| 188              | 0              | 0              | 1              | 62             |

| 189              | 0              | 0              | 0              | 63             |

| 190              | 1              | 0              | 0              | 62             |

| ...              | ...            | 0              | 0              | ...            |

| 251              | 62             | 0              | 0              | 1              |

SysRefPhaseShift の値が最も小さいときに遅延が最も小さくなるとは限りません。つまり、最も長い遅延から最も短い遅延への突然の移行が起きる、折り返し効果が発生することがあります。この突然の移行が発生するコードは、主に  $f_{VCO}$  と SYSREF\_DIV\_PRE によって決定されます。

### 7.3.14 高速 VCO キャリブレーション

VCO がキャリブレーションに要する時間を短縮できます。VCO キャリブレーションの一般的な方法を、表 7-7 に示します。

**表 7-7. VCO キャリブレーションのタイプ**

| キャリブレーションのタイプ    | 説明                                                                                                                                                                              |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| アシストなし           | VCO キャリブレーションを高速化する作業は行いませんが、ユーザー指定の VCO_SEL、VCO_DACISET、VCO_CAPCTRL の値は VCO キャリブレーションの開始点に影響します。                                                                               |

| 部分アシスト           | 周波数を変更するごとに、FCAL_EN ビットをチェックする前に、データシートに指定された値に基づいて、VCO コア (VCO_SEL)、帯域 (VCO_CAPCTRL)、振幅 (VCO_DACISET) の初期開始点をユーザーが指定します。                                                       |

| フル・アシスト          | VCO コア (VCO_SEL)、振幅設定 (VCO_DACISET)、周波数帯域 (VCO_CAPCTRL) をユーザーが決定し、値を手動で設定します。2 つの周波数ポイントの差が 5MHz 以内で、同じ VCO コア上にある場合、ユーザーは線形補間を使用して、それら 2 点間の任意の周波数に対して VCO 振幅とキャップ・コードを設定できます。 |

| インスタンス・キャリブレーション | ユーザーがデバイスを初期化して、インスタンス・キャリブレーションを生成します。デバイスに電力が供給されている間は、このインスタンス・キャリブレーションを使用して、非常に高速な VCO キャリブレーションを行えます                                                                      |

### 7.3.15 ダブル・バッファリング (シャドウ・レジスタ)

ダブル・バッファリング (別名シャドウ・レジスタ) を使うと複数のレジスタに書き込むことができますが、その時点ではこれらのレジスタは実際には有効化されません。その後 R0 レジスタがプログラムされると、これらのレジスタが有効になります。この機能は、周波数の急速な変更が行われ、かつ複数のレジスタへの書き込みが必要な場合に特に役立ちます。DBLBUF\_EN = 1 の場合、PLL\_N、PLL\_NUM、PLL\_DEN、MULT、PLL\_R、PLL\_R\_PRE、MASH\_ORDER、PFD\_DLY の各レジスタでダブル・バッファリングが有効になります。

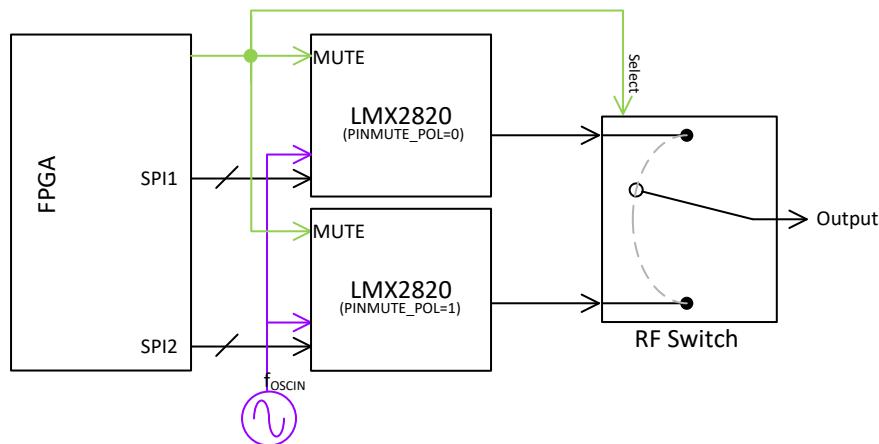

### 7.3.16 出力ミュート・ピンとピンポン手法

出力バッファは、MUTE ピンによりミュートまたはミュート解除できます。このピンの極性は、PINMUTE\_POL ビットでプログラミ可能です。出力がミュートになっている場合、PLL はロック状態を維持するため、複数のシンセサイザを組み合わせてロック時間を短縮できます。出力がミュートになっている PLL は、プログラミング・コマンドを受け入れたり、新しい周波数にロックしたりできます。出力がミュートになると、不要な信号は大幅に減衰し、RF スイッチを使用するとさらに減衰できます。

図 7-5. 出力ミュート・ピン

## 7.4 デバイスの機能モード

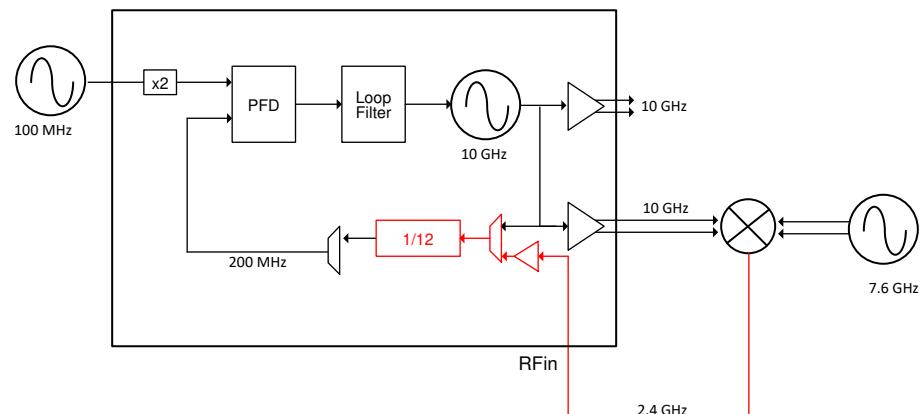

LMX2820 には 6 つの基本モードがあり、内部 VCO と外部 VCO の使用を選択できるほか、VCO の出力を 3 つの方法で位相検出器に送信できます。

表 7-8. デバイスの機能モードの概要

| VCO モード | フィードバック・モード     | 備考                                                                                                                               |

|---------|-----------------|----------------------------------------------------------------------------------------------------------------------------------|

| 内部      | 内部フィードバック       | 内部 VCO を使用し、VCO は内部で位相検出器にフィードバックします。                                                                                            |

|         | PFDIN 外部フィードバック | 内部 VCO を使用しますが、出力は外部ミキサーでダウンコンバートされ、PFDIN ピンに供給されます。                                                                             |

|         | RFIN 外部フィードバック  | 内部 VCO を使用し、出力は外部ミキサーでダウンコンバートされ、RFIN ピンに供給されます。                                                                                 |

| 外部      | 内部フィードバック       | 一部のアプリケーション、特に狭帯域のものでは、外部 VCO のほうが内部 VCO より位相ノイズ性能に優れている可能性があります。外部 VCO を使用することで、出力デバイスやダブルが不要になる場合、これによって位相ノイズや高調波を軽減することができます。 |

|         | PFDIN 外部フィードバック | 理論的には、外部 VCO を外部位相検出器とともに使用し、位相ノイズを最低限にできます。このモードを最大限に活用するには、高性能のソース、ミキサー、VCO が必要です。                                             |

|         | RFIN 外部フィードバック  | 外部 VCO を使用し、出力は外部ミキサーでダウンコンバートされ、RFIN ピンに供給されます。                                                                                 |

### 7.4.1 外部 VCO モード

LMX2820 は外部 VCO と組み合わせて使えますが、SYSREF 機能は使えるものの、出力バッファは使えないことに注意します。チャージ・ポンプの最大出力電圧は約 2.5V ですが、ほとんどの VCO について、この電圧は十分ではありません。そのため、アクティブ・フィルタを推奨します。アクティブ・フィルタは、チャージ・ポンプ電圧を約 1.2V に維持することで、より高い出力電圧を供給できます。VCO 周波数が 11.3GHz よりも高い場合、EXTVCODIV ビットを 1 に設定する必要があります。それ以外の場合、0 に設定します。

図 7-6. 外部 VCO モード

外部 VCO を使用する場合は、PFD\_DLY ワードを表 7-9 に示すように手動で設定する必要があります。内蔵 VCO では、このワードをプログラムする必要はありません。PFD\_DLY を手動で設定するには、PFD\_DLY\_MANUAL = 1 にする必要があります。

表 7-9. 外部 VCO モードでの PFD\_DLY\_SEL の設定

| $f_{RFIN} / (RFIN \text{ デバイダ})$ | MASH_ORDER = 0 | MASH_ORDER = 1 | MASH_ORDER = 2 | MASH_ORDER = 3 |

|----------------------------------|----------------|----------------|----------------|----------------|

| 0.5~4GHz                         | 1              | 1              | 2              | 4              |

| 4~5.5GHz                         | 2              | 2              | 3              | 5              |

| 5.5~7GHz                         | 3              | 3              | 4              | 6              |

| 7~8.5GHz                         | 4              | 4              | 5              | 7              |

| 8.5~10GHz                        | 5              | 5              | 6              | 8              |

| > 10GHz                          | 6              | 6              | 7              | 9              |

### 7.4.2 外部フィードバック入力ピン

LMX2820 では、外部ミキサーとクリーンなソースを使用して、VCO 周波数をダウンコンバートし、PLL ノイズを低減するオプションを利用できます。この周波数は、RFIN ピンまたは PFDIN ピンから入力できます。

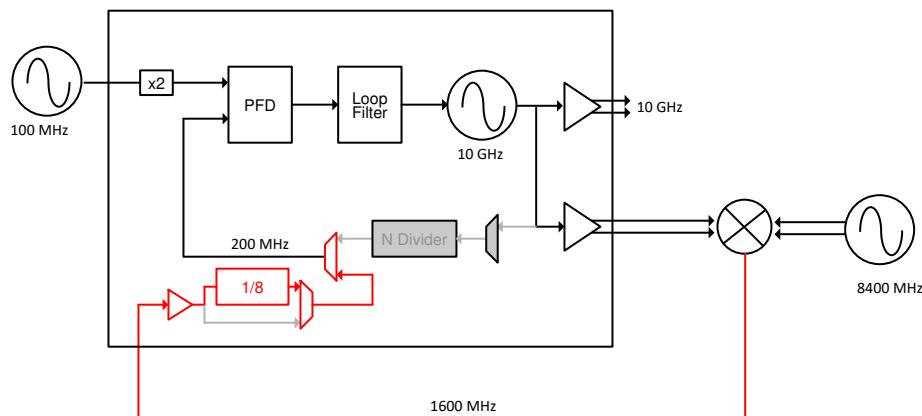

#### 7.4.2.1 PFDIN の外部フィードバック・モード

PFDIN ピンを使用すると、ミキサーで VCO 周波数を外部からダウンコンバートし、N デバイダの値を大幅に下げることができます。EXTPFD\_DIV では、位相ノイズを最小限に抑えるため、分周値を 1 まで下げるすることができます。PFDIN ピンを

使用するときは、PFD\_SINGLE = 3 を設定し、シングル PFD モードを有効にする必要があります。この設定により、PLL の性能指数は約 3dB 低下しますが、フィードバック・デバイダを 1 まで下げるすることができます。最小の N デバイダを利用できない場合は、RFIN ピンの使用を検討してください。この方法では最小 N 分周値が大きくなりますが、PLL 性能指数は低下しません。

図 7-7. PFDIN ピンと内部 VCO を使用した外部フィードバック

#### 7.4.2.2 RFIN 外部フィードバック・モード

RFIN ピンを使用して、N デバイダの値をさらに低くすることもできます。この機能は、フィードバック分周値が高い場合や、分数回路が必要な場合に有用です。外部フィードバックに PFDIN ピンを使用する場合と同様に、シングル PFD モードを使用する必要はありません。

図 7-8. RFIN ピンと内部 VCO を使用した外部フィードバック

## 8 アプリケーションと実装

### 注

以下のアプリケーション情報は、TI の製品仕様に含まれるものではなく、TI ではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 アプリケーション情報

#### 8.1.1 未使用ピンの処理

アプリケーションによっては、すべてのピンが必要とは限りません。[表 8-1](#) は、これらの未使用ピンの処理方法についての説明です。

**表 8-1. 未使用ピンの処理**

| 状況          | 適用されるピン               | 備考                                                                                                                |

|-------------|-----------------------|-------------------------------------------------------------------------------------------------------------------|

| シングル・エンド入力  | OSCIN_N               | このピンは、 $50\Omega$ の抵抗を通して GND に AC カップリングします。スプリアスを最適化するには、OSCIN_P と OSCIN_N から外を見た時に観測されるインピーダンスをほぼ同じにする必要があります。 |

| シングルエンド出力   | RFOUTA_N, RFOUTB_N    | このピンは、使用されている出力と同等の負荷を接続して終端します。この負荷は通常、グランドに対して AC 結合した $50\Omega$ の抵抗です。これは、高調波を最小限に抑えるためです。                    |

| 未使用の入力      | RFIN, PFDIN, SRREQ ピン | これらのピンはフローティング状態のままでかまいません。この機能は、ソフトウェアでパワーダウンできます。                                                               |

| 未使用の出力      | RFOUT ピン、SROUT ピン     | これらのピンはフローティング状態のままでかまいません。この機能は、ソフトウェアでパワーダウンできます。                                                               |

| 未使用のデジタル・ピン | 入力ピン                  | これらのピンは、グランドに接続します。                                                                                               |

#### 8.1.2 外部ループ・フィルタ

LMX2820 は特定用途向けの外部ループ・フィルタを必要とし、PLLatinum Sim によって構成できます。LMX2820 では、VTUNE ピンから外側を見たときのインピーダンスが重要です。このインピーダンスは、3 次フィルタでは部品 C3、2 次フィルタでは C1 により決定されます。このピンのシャント容量が  $1.5nF$  以上である場合、VCO 位相ノイズは理想的な値に近くなります。容量がこれより小さい場合、 $100kHz \sim 1MHz$  領域の VCO 位相ノイズが劣化します。このコンデンサは、VTUNE ピンの近くに配置する必要があります。

#### 8.1.3 インスタント・キャリブレーションの使用

インスタント・キャリブレーションにより、デバイスは非常に高速な VCO のキャリブレーションを  $2.5\mu s$  で行い、同じキャリブレーション設定 (rb\_VCO\_SEL, rb\_VCO\_DACISET, rb\_VCO\_CAPCTRL) を選択できます。この機能の初期化後は、オーバーヘッドなしに VCO 周波数を変更できます。デバイスの電源を最初にオンにしたときに、この初期化を行う必要がありますが、電源ピンから電力が供給されている限りは設定が保持されます。詳しい手順について、以下に示します。

1. デバイスの電源を通常どおりオンにします。

2.  $INSTCAL_DLY = t_{DLY} \times f_{osc}$  (MHz 単位) /  $2^{CAL\_CLK\_DIV}$  をプログラムします。 $t_{DLY}$  はインスタント・キャリブレーションに必要なタイムアウト回数で、ピン 3 のバイアス・コンデンサに基づいています。

**表 8-2. インスタント・キャリブレーションのタイムアウトの決定**

| ピン 3 の容量    | PLL の 1/f ノイズ劣化 | 最小 $t_{DLY}$                      |

|-------------|-----------------|-----------------------------------|

| $0.47\mu F$ | 1dB             | $2.5\mu s$                        |

| C           | $0 \sim 1dB$    | $2.5\mu s \times C / (0.47\mu F)$ |

**表 8-2. インスタント・キャリブレーションのタイムアウトの決定 (continued)**

| ピン 3 の容量 | PLL の 1/f ノイズ劣化 | 最小 $t_{DLY}$ |

|----------|-----------------|--------------|

| 4.7μF    | 0dB             | 25μs         |

3. レジスタ R1 をインスタント・キャリブレーション用にプログラムします。

- INSTCAL\_EN = 1 を設定します。INSTCAL\_EN を 0 から 1 に切り替えるアクションは、インスタント・キャリブレーション設定をリセットし、レジスタ R0 が次に FCAL\_EN = 1 にプログラムされたとき設定を生成するよう、部品を設定します。

- 出力ダブルを使用する場合は、INSTCAL\_DBLR\_EN = 1 を設定します。使用しない場合は 0 に設定します。

4. デバイスが 5.65GHz を出力するようプログラムします。

5. INSTCAL\_PLL\_NUM =  $2^{32} \times (\text{PLL\_NUM} / \text{PLL\_DEN})$  をプログラムします。

6. キャリブレーション設定を生成するため、FCAL\_EN = 1 を R0 に書き込みます。

7. デバイスを 5.65GHz にロックするため、FCAL\_EN = 0 を R0 に書き込みます。

8. ロック検出が High に移行するまで待ちます。

これで、デバイスが初期化された特定の位相検出器周波数について、デバイスが初期化されました。デバイスに電力が供給され続け、位相検出器の周波数が変化しない限り、以後の周波数変更はインスタント・キャリブレーションで行うことができます。インスタント・キャリブレーションの初期化後に周波数を変更するには、以下を行います。

1. INSTCAL\_PLL\_NUM、PLL\_N、PLL\_NUM、PLL\_DEN の値を書き込みます。

2. R0 を書き込んでキャリブレーションをトリガします (DBLR\_CAL\_EN = 0、FCAL\_EN = 0 の値を書き込みます)。

## 8.2 代表的なアプリケーション

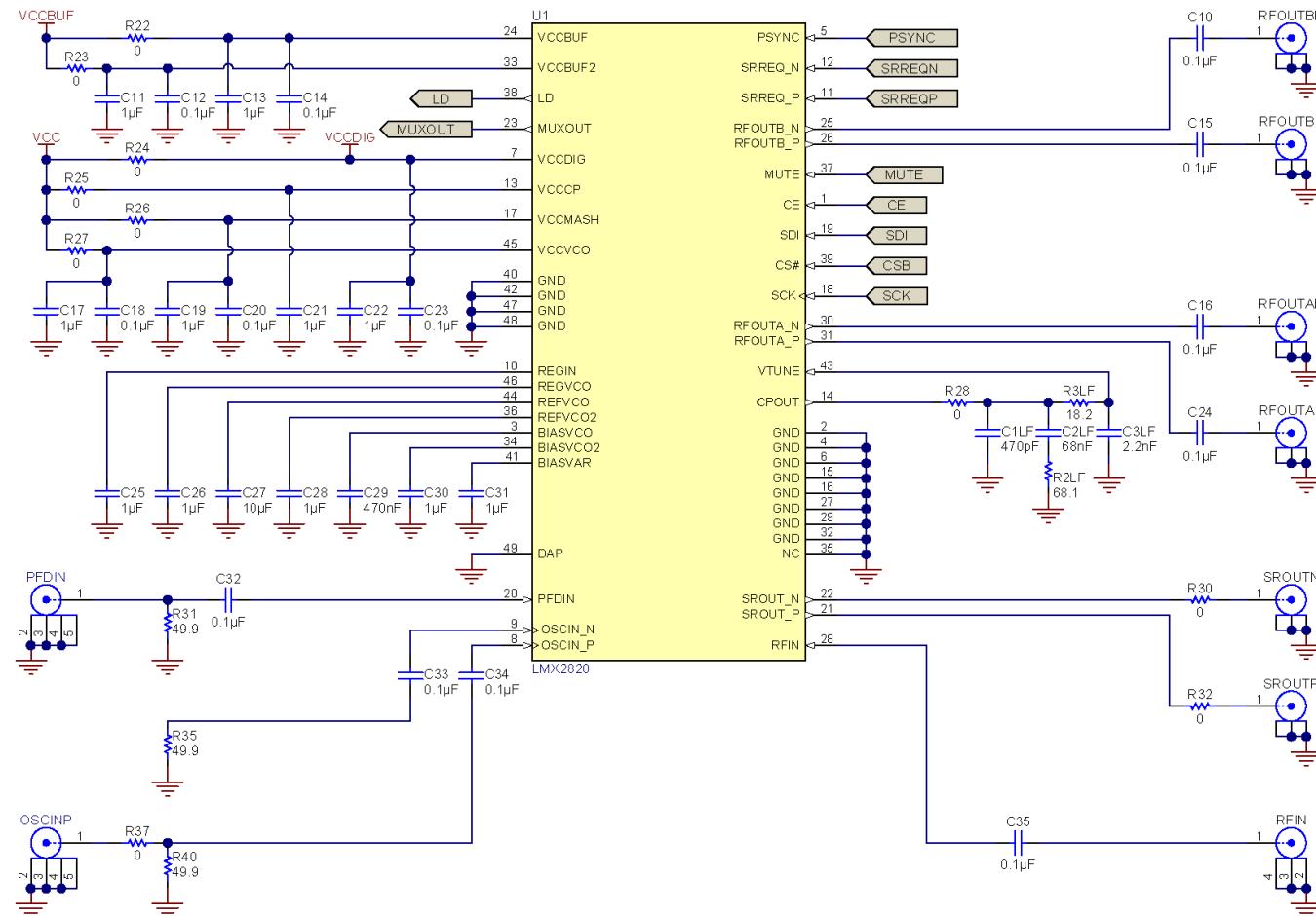

図 8-1. 代表的なアプリケーション回路図

### 8.2.1 設計要件

ループ・フィルタの設計は複雑であるため、通常はソフトウェアで処理されます。PLLatinum Sim ソフトウェアは、設計とシミュレーションのための優れたリソースです。今回の場合には整数設計が想定されており、多くのクロック供給アプリケーションの場合と同様に、最適なジッタを実現するよう設計されます。この例では、100MHz のクロックから 6GHz の出力を生成することを想定します。この場合にエンジニアは、ループ・フィルタの設計に進む前に、VCO 周波数と位相検出器を選択する必要があります。

VCO 周波数は 5.65~11.3GHz の範囲内の必要があります。出力周波数はこの範囲内に分周するか、または選択した VCO 周波数の 2 倍にする（この場合は 11.3GHz よりも高くなります）必要があります。ここでは、VCO 周波数を 6GHz と想定します。次のステップとして、位相検出器の周波数を選択します。位相検出器周波数は、入力周波数の約数である必要があります。または、OSC\_2X 機能を使用する場合は 2 倍の周波数にすることもできます。また、位相検出器周波数が VCO 周波数の約数である場合、スプリアス性能は大幅に向上升します。位相検出器の周波数を 200MHz に設定し、OSC\_2X ダブルを使用すると、整数モードでデバイスを使用でき、優れた位相ノイズ性能が得られます。

**表 8-3. 設計パラメータ**

| 記号        | 説明                            | 値    | 単位  |

|-----------|-------------------------------|------|-----|

| $f_{osc}$ | 指定された入力周波数。                   | 100  | MHz |

| $f_{out}$ | 指定された出力周波数。                   | 6000 | MHz |

| $f_{vco}$ | 出力周波数を生成するために選択された VCO 周波数。   | 6000 | MHz |

| $f_{PD}$  | 最良のノイズ性能を得るために選択された位相検出器の周波数。 | 200  | MHz |

### 8.2.2 詳細な設計手順

周波数を決定した後、ループ・フィルタを設計する必要があります。特定の帯域幅における位相ノイズ（ジッタ）の統合は、信号対雑音比に変換される性能仕様です。ループ帯域幅の内側の位相ノイズは主に PLL により決定され、ループ帯域幅の外側の位相ノイズは主に VCO により決定されます。

一般に、ループ帯域幅がこれら 2 つの交差するポイントに設計されている場合、ジッタは最も小さくなります。ループ・フィルタの設計で位相マージンが高いほど、ループ帯域幅でのピークが小さくなり、ジッタも小さくなります。これに対するトレードオフは、設計時に長いロック時間とスプリアスも考慮する必要があることです。

PLLatinum Sim ソフトウェアはループ・フィルタの設計に非常に便利で、TI の Web サイトから入手できます。[表 8-4](#) の結果は、このツールを使用して得られたものです。

**表 8-4. PLLatinum Sim による結果**

| 部品 | 値   | 単位       |

|----|-----|----------|

| C1 | 390 | pF       |

| C2 | 68  | nF       |

| C3 | 1.8 | nF       |

| R2 | 68  | $\Omega$ |

| R3 | 18  | $\Omega$ |

### 8.2.3 アプリケーション曲線

実際の位相ノイズの結果では、ジッタは 36fs と優れた値が示されています。

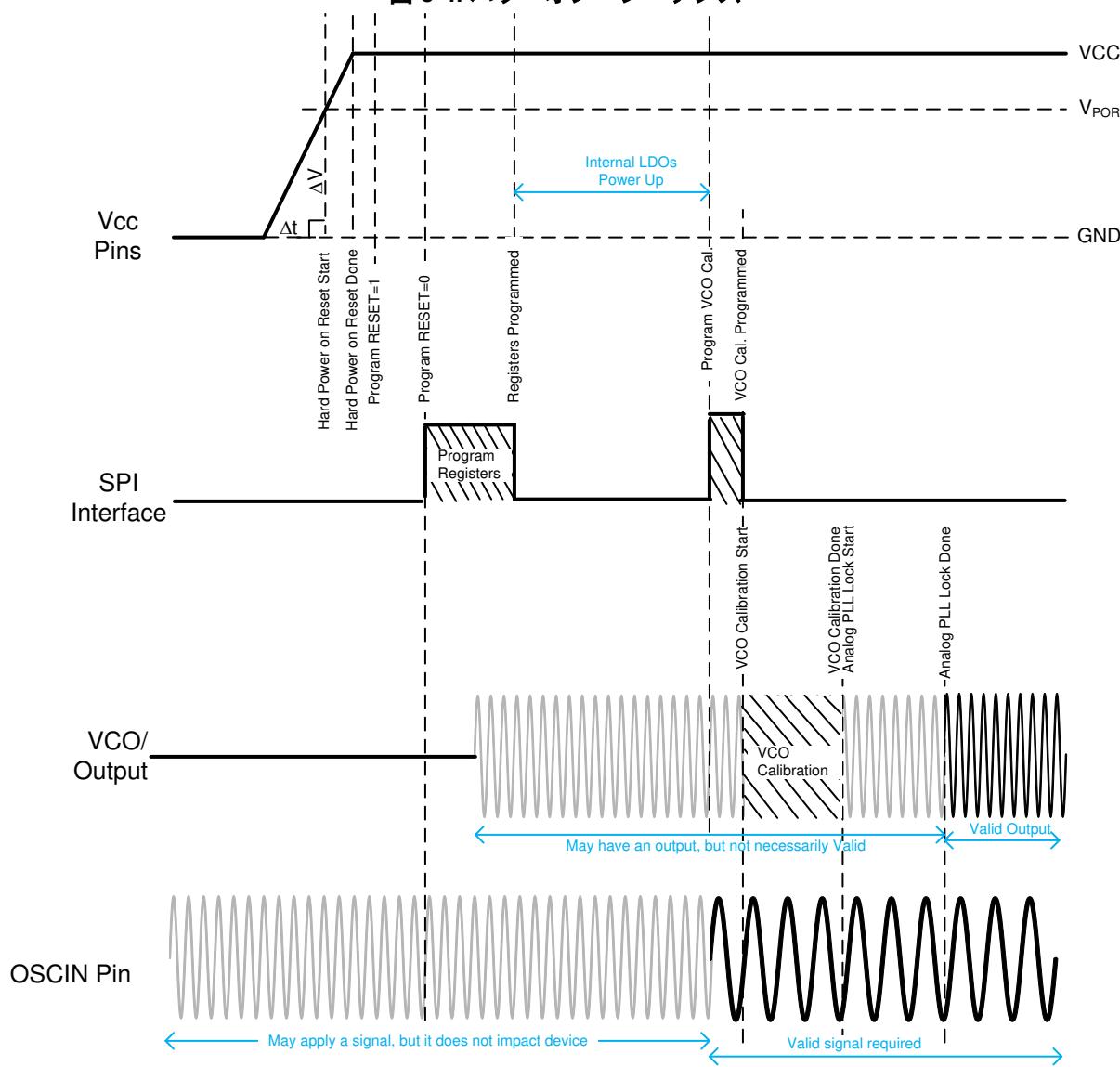

## 8.3 初期化およびパワーオン・シーケンス

本デバイスを正しく動作させるには、正しいパワーオン・シーケンスを実行する必要があります。

- 電源投入時に、パワーオン・リセット (POR) 回路によって、レジスタとステート・マシンがデフォルト状態にリセットされます。

- プログラミングを行う前に、VCC\_CP、VCC\_VCO、VCC\_VCO2、VCC\_MASH、VCC\_BUF の電圧は最低動作電圧である 3.15V を超えている必要があります。

- POR 回路により本デバイスは初期化されますが、RESET ビットを 1 から 0 に切り替えることでソフトウェア・リセットを手動で実行することを推奨します。これは、内部のステート・マシン、バイアス・レベル、およびデバイス全体の電流を安定した開始条件にリセットするために必要です。このリセットに要する時間は 1μs 未満です。

- レジスタを降順でプログラムします。レジスタ R0 を最後にプログラムします。これにより、本デバイスは目的の状態に設定されます。

- 内部 LDO の電源がオンになるまで、10ms 待ちます。

- LDO が安定化された状態で VCO キャリブレーションを実行するため、R0 レジスタをもう一度書き込みます。この操作を、チップ内の LDO が適切なレベルに達する前に行つた場合、そのキャリブレーションは無効です。また、VCO キャリブレーションは入力基準電圧に基づいて行われるため、入力基準電圧が安定し、正確であることが重要です。入力基準電圧を先に印加しても、本デバイスは破損しません。これは、インスタント・キャリブレーションのありなしの両方のキャリブレーション方法に適用されます。

- VCO が較正された後、周波数は目標値に近づきますが、正確ではありません。VCO のデジタル・キャリブレーションに加えて、アナログ・ロック時間で周波数をセトリングする必要があります。

- アナログ PLL ロックが完了した後で、出力が有効になります。その前に信号が出力されることがあります、その周波数は有効でない可能性があります。

図 8-4. パワーオン・シーケンス

## 9 電源に関する推奨事項

分母スプリアスが大きな問題となる場合は、これらの各電源ピンにフェライト・ビーズを取り付けて、スプリアスを多少低減できます。このデバイスには LDO が内蔵されており、電源ノイズへの耐性が強化されています。このデバイスは、TPS62150 などの外部 DC/DC 降圧型コンバータにより駆動できます。電源フィルタリングを行うには、各ピンにどの程度の電流が流れるかの概要を理解しておくことが有用です。この値は構成によって大きく変化しますが、一般的な値を次の表に示します。

**表 9-1. ピンごとの消費電流 (mA 単位)**

| 条件                         | 合計  | VCCDIG | VCCCP | VCCMASH | VCCBUF | VCCVCO |

|----------------------------|-----|--------|-------|---------|--------|--------|

| 1 つの直接 RF 出力               | 420 | 23     | 5     | 5       | 124    | 263    |

| 1 つの分周 RF 出力               | 580 | 21     | 13    | 96      | 212    | 238    |

| 1 つの RF 出力、VCO ダブラー        | 590 | 20     | 12    | 89      | 238    | 231    |

| RFIN 外部フィードバック・モード、内部 VCO  | 530 | 18     | 12    | 90      | 170    | 240    |

| PFDIN 外部フィードバック・モード、内部 VCO | 455 | 18     | 10    | 79      | 110    | 238    |

| 外部 VCO モード                 | 290 | 19     | 9     | 92      | 54     | 116    |

| パワー・リセット電流                 | 234 | 10     | 6     | 48      | 24     | 146    |

| パワーダウン電流                   | 10  | 2      | 0     | 1       | 6      | 1      |

## 10 レイアウト

### 10.1 レイアウトのガイドライン

一般に、レイアウトのガイドラインは他のほとんどの PLL デバイスと同様です。いくつか固有のガイドラインが存在するので、以下に示します。

- GND ピンはパッケージで、DAP に戻るよう配線できます。

- OSCIN ピンは内部的にバイアスされており、AC 結合する必要があります。

- SRREQ ピンを使用しない場合は、DAP に接地できます。

- 200kHz~1MHz の範囲で最適な VCO 位相ノイズを実現するには、VTUNE ピンに最も近いコンデンサを最低 1.5nF にするのが理想的です。この容量が大きいコンデンサが必要なことから、ループの帯域幅が制限される可能性があるため、VCO 位相ノイズを犠牲にして、この値を (たとえば 1nF に) 減らすことができます。

- シングルエンド出力が必要な場合、反対側にも同じ負荷が必要です。しかし、使用する側の配線は、補完側をビアにより基板の反対側に配線することで最適化できます。こちらの側でも、使用される側と負荷が等価に見えるようにします。

- デバイスの DAP が、多くのビアで十分に接地されていることを確認してください。可能なら全面銅箔にします。

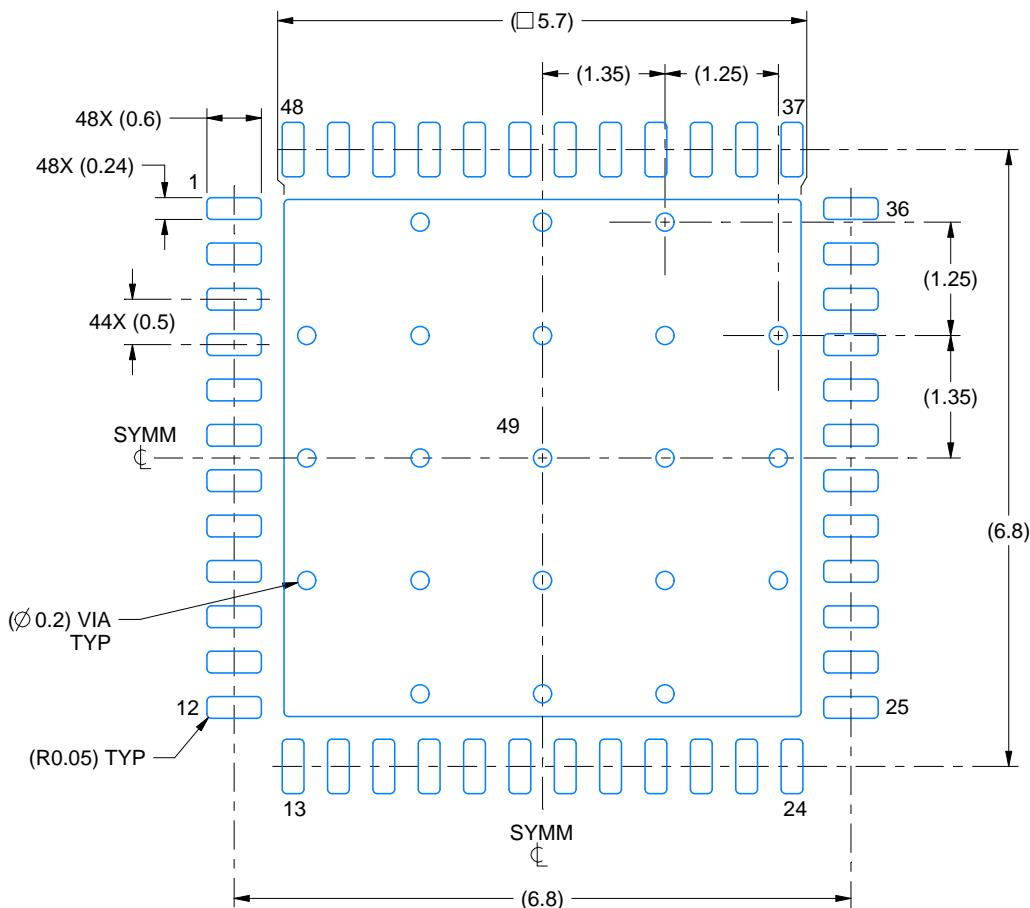

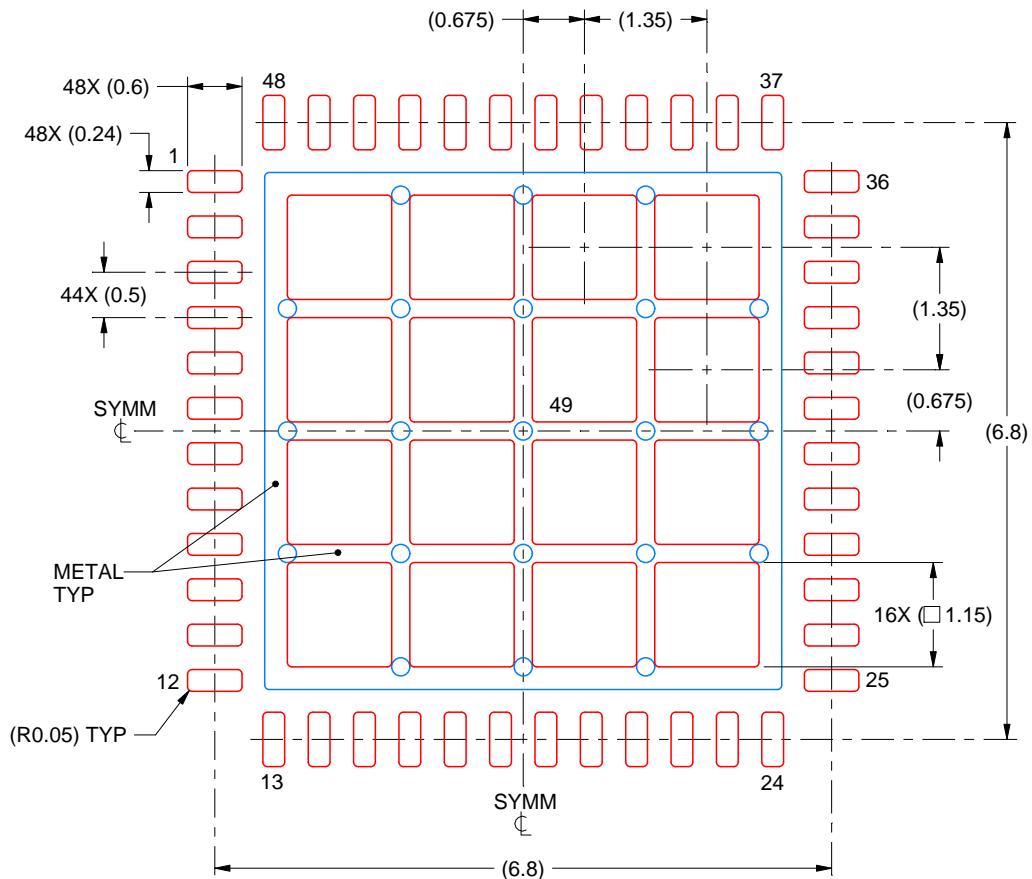

- LMX2820 の露出パッドと同じサイズのサーマル・パッドを取り付けます。放熱性能を最大にするため、サーマル・パッドにビアを追加します。

- より低損失の誘電体 (Rogers 4350B など) を使用して、最適な出力電力を実現します。

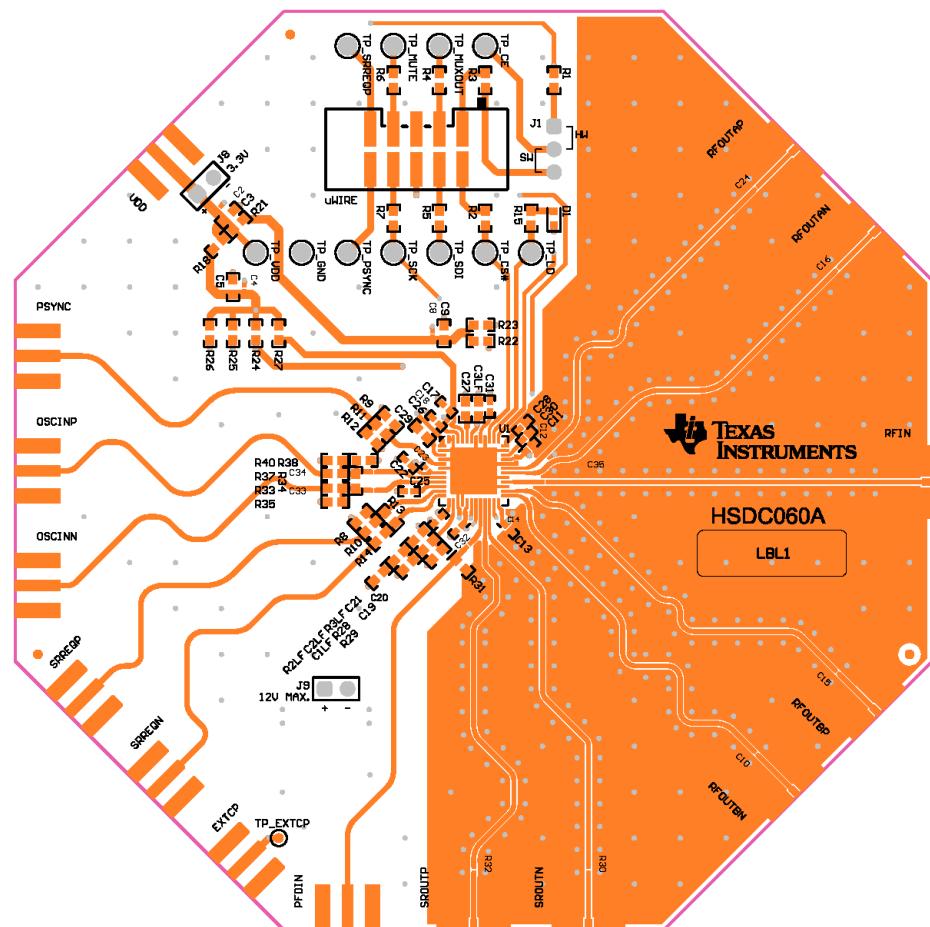

## 10.2 レイアウト例

このレイアウトでは、すべてのループ・フィルタ (C1LF, C2LF, C3LF, R2LF, R3LF) が基板の上面にあります。C3LF は、VTUNE ピンのすぐ横にあります。この C3LF コンデンサがオープンになる場合、ループ・コンデンサの 1 つをこの場所に移動することをお勧めします。たとえば、2 次ループ・フィルタが使用されているとき、技術的に C3LF はオープンです。しかし、3 次ループ・フィルタ用に設計されている、このレイアウト例では、C1LF をオープンにし、C1LF に設定するはずだったものを C3LF に設定するのが最適です。

図 10-1. レイアウト例

## 11 デバイスおよびドキュメントのサポート

### 11.1 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[ti.com](http://ti.com) のデバイス製品フォルダを開いてください。「更新の通知を受け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

### 11.2 サポート・リソース

[TI E2E™ サポート・フォーラム](#)は、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、該当する貢献者により、現状のまま提供されるものです。これらは TI の仕様を構成するものではなく、必ずしも TI の見解を反映したものではありません。[TI の使用条件](#)を参照してください。

### 11.3 商標

PLLatinum™ is a trademark of Texas Instruments.

TI E2E™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 11.4 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことをお勧めします。正しい ESD 対策をとらないと、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 11.5 用語集

#### TI 用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 12 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに対して提供されている最新のデータです。このデータは予告なく変更されることがあります。ドキュメントが改訂される場合もあります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

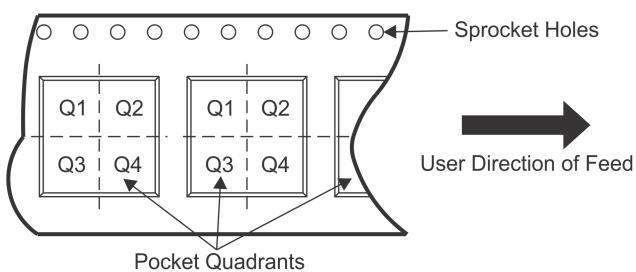

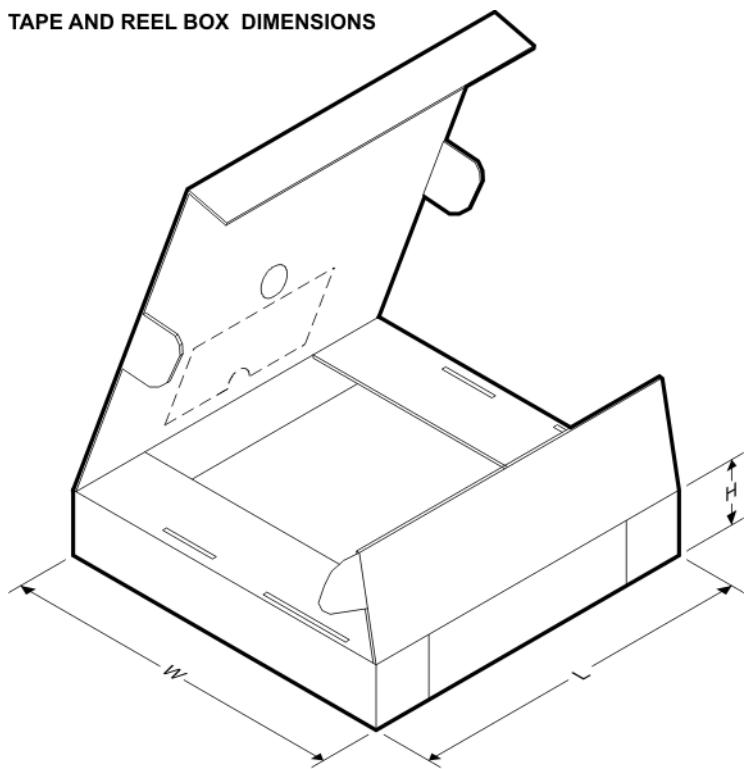

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins  | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| LMX2820RTCR           | Active        | Production           | VQFN (RTC)   48 | 2500   LARGE T&R      | Yes         | NIPDAUAG                             | Level-3-260C-168 HR               | -40 to 85    | LMX2820             |

| LMX2820RTCR.B         | Active        | Production           | VQFN (RTC)   48 | 2500   LARGE T&R      | Yes         | NIPDAUAG                             | Level-3-260C-168 HR               | -40 to 85    | LMX2820             |

| LMX2820RTCT           | Active        | Production           | VQFN (RTC)   48 | 250   SMALL T&R       | Yes         | NIPDAUAG                             | Level-3-260C-168 HR               | -40 to 85    | LMX2820             |

| LMX2820RTCT.B         | Active        | Production           | VQFN (RTC)   48 | 250   SMALL T&R       | Yes         | NIPDAUAG                             | Level-3-260C-168 HR               | -40 to 85    | LMX2820             |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.