## LV14340 40V、3.5A、2MHz、降圧型コンバータ

### 1 特長

- 新製品を利用可能:

- LMR51440 4~36V、4A、200kHz~1.1MHz 同期整流コンバータ

- 市場投入の迅速化:

- TLV13640 3~36V、4A、200kHz~2.2MHz パワーモジュール

- 4V ~ 40V の入力電圧範囲

- 3.5A の連続出力電流

- 100mΩ ハイサイド MOSFET

- 最小オン時間: 100ns

- 電流モード制御

- 調整可能なスイッチング周波数: 200kHz~2MHz

- 外部クロックへの周波数同期

- 使いやすさを実現した内部補償

- 高いデューティサイクルでの動作をサポート

- 高精度イネーブル入力

- 1μA のシャットダウン電流

- 過熱 / 過電圧 / 短絡保護

- PowerPAD™ 付き 8 ピン SOIC パッケージ

### 2 アプリケーション

- 車載用バッテリ・レギュレーション

- 産業用電源

- テレコムおよびデータコム・システム

- バッテリ駆動システム

### 3 概要

LV14340 は、ハイサイド MOSFET を内蔵した 40V、3.5A の降圧型レギュレータです。4V~40V という幅広い入力範囲により、産業用から車載用まで、非レギュレーション電源からの電源調整を行うさまざまなアプリケーション向けに設計されています。調整可能なスイッチング周波数の範囲が広いため、効率と外付け部品のサイズを最適化できます。内部ループ補償により、ユーザーはループ補償を設計する煩雑な作業から解放されます。また、本デバイスの外付け部品の数も最小限で済みます。高精度のイネーブル入力により、レギュレータの制御とシステムの電源シーケンスが単純化されます。このデバイスには、サイクル単位の電流制限、熱センシング、過剰な消費電力によるサーマルシャットダウン、出力過電圧保護などの保護機能も組み込まれています。

LV14340 は、熱抵抗を下げるための露出パッドを備えた 8 ピン HSOIC パッケージで供給されます。

#### パッケージ情報

| 部品番号    | パッケージ (1)      | パッケージ サイズ (2) |

|---------|----------------|---------------|

| LV14340 | DDA (HSOIC, 8) | 4.9mm × 6mm   |

(1) 詳細については、[セクション 10](#) を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値で、該当する場合はピンも含まれます。

## 目次

|              |    |                        |    |

|--------------|----|------------------------|----|

| 1 特長         | 1  | 6.3 機能説明               | 10 |

| 2 アプリケーション   | 1  | 6.4 デバイスの機能モード         | 17 |

| 3 概要         | 1  | 7 アプリケーションと実装          | 18 |

| 4 ピン構成と機能    | 3  | 7.1 アプリケーション情報         | 18 |

| 5 仕様         | 4  | 7.2 代表的なアプリケーション       | 18 |

| 5.1 絶対最大定格   | 4  | 7.3 電源に関する推奨事項         | 23 |

| 5.2 ESD 定格   | 4  | 7.4 レイアウト              | 23 |

| 5.3 推奨動作条件   | 4  | 8 デバイスおよびドキュメントのサポート   | 25 |

| 5.4 熱に関する情報  | 5  | 8.1 ドキュメントの更新通知を受け取る方法 | 25 |

| 5.5 電気的特性    | 5  | 8.2 サポート・リソース          | 25 |

| 5.6 スイッチング特性 | 6  | 8.3 商標                 | 25 |

| 5.7 代表的特性    | 7  | 8.4 静電気放電に関する注意事項      | 25 |

| 6 詳細説明       | 9  | 8.5 用語集                | 25 |

| 6.1 概要       | 9  | 9 改訂履歴                 | 25 |

| 6.2 機能ブロック図  | 10 | 10 メカニカル、パッケージ、および注文情報 | 26 |

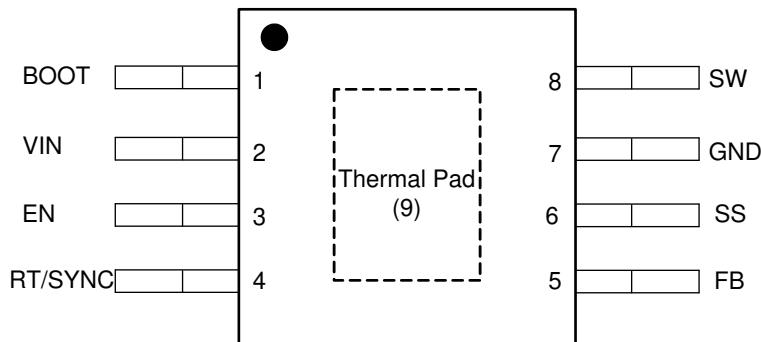

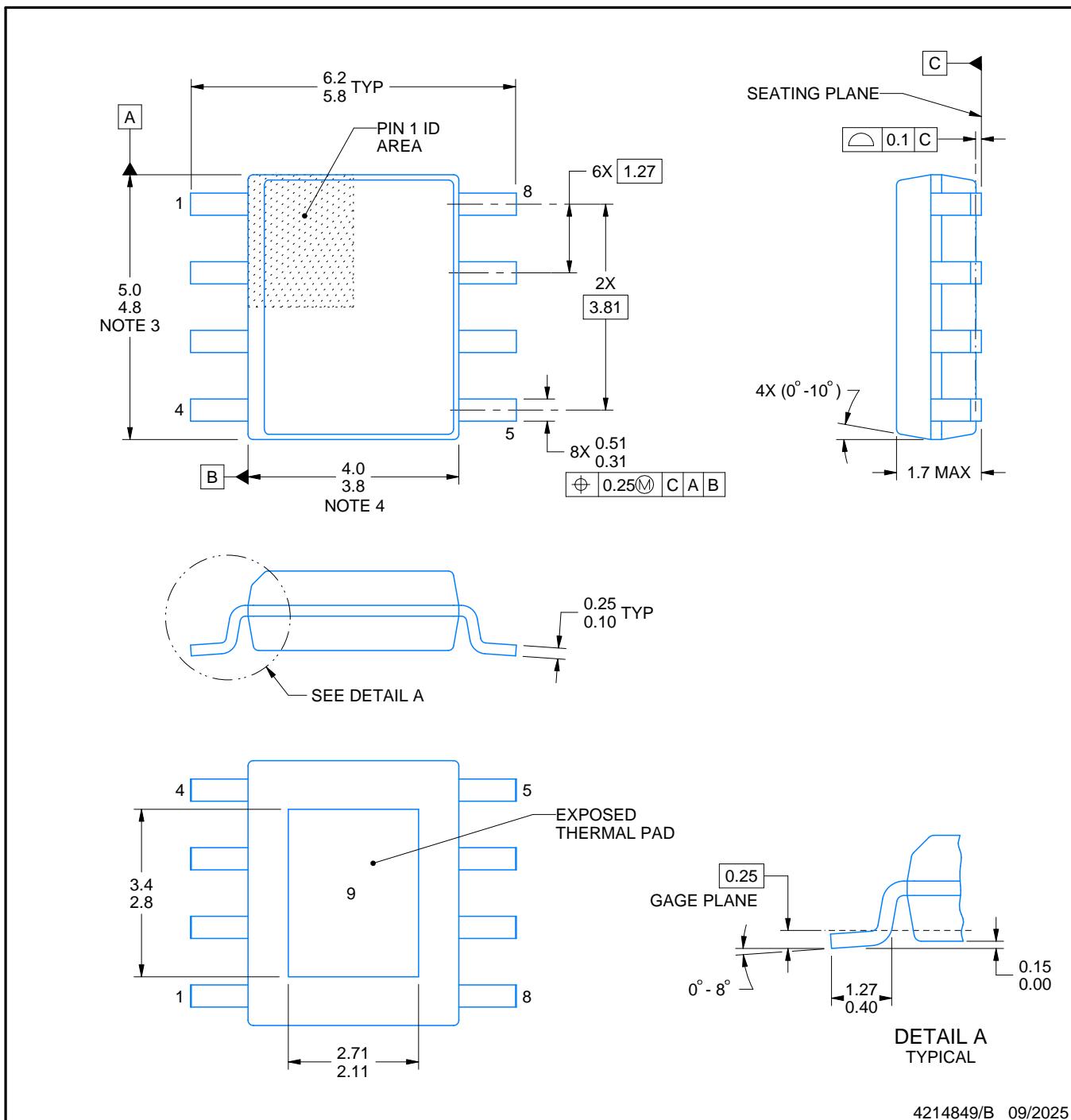

## 4 ピン構成と機能

図 4-1. DDA パッケージ 8 ピン SOIC 上面図

表 4-1. ピンの機能

| ピン        |    | タイプ (1) | 説明                                                                                                                                                                                                                                                         |

|-----------|----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称        | 番号 |         |                                                                                                                                                                                                                                                            |

| BOOT      | 1  | P       | 下限側 MOSFET ドライバのブートストラップ・コンデンサを接続。BOOT と SW の間に高品質の $0.1\mu\text{F}$ のコンデンサを接続します。                                                                                                                                                                         |

| VIN       | 2  | P       | 電源およびバイパス・コンデンサ $C_{IN}$ に接続します。VIN ピンから高周波バイパス $C_{IN}$ および GND へのバスは、できる限り短くする必要があります。                                                                                                                                                                   |

| EN        | 3  | A       | 内部プルアップ電流源搭載イネーブル・ピン。ディスエーブルにするには、1.2V 未満にプルダウンします。イネーブルにするには、オープンにするか、VIN に接続します。2 個の抵抗を使用して入力の低電圧誤動作防止を調整します。 <a href="#">イネーブルおよび可変低電圧誤動作防止</a> を参照してください。                                                                                              |

| RT / SYNC | 4  | A       | 抵抗タイミングまたは外部クロック入力。スイッチング周波数を設定するために、グランドへの外付け抵抗を使用すると、内部アンプによってこのピンが固定電圧に保持されます。このピンを PLL の上限スレッショルドより高くプルアップすると、モード遷移が発生し、ピンは同期入力となります。内部アンプはディスエーブルになり、このピンは内部 PLL への高インピーダンス・クロック入力となります。クロック・エッジが停止すると、内部アンプが再びイネーブルになり、動作モードは抵抗を使用して周波数プログラミングに戻ります。 |

| FB        | 5  | A       | 帰還入力ピン。帰還分圧回路に接続して、 $V_{OUT}$ を設定します。動作中は、このピンをグランドに短絡しないでください。                                                                                                                                                                                            |

| SS        | 6  | A       | ソフト・スタート制御ピン。コンデンサに接続して、ソフト・スタート時間を設定します。                                                                                                                                                                                                                  |

| GND       | 7  | G       | システム・グランド・ピン                                                                                                                                                                                                                                               |

| SW        | 8  | P       | レギュレータのスイッチング出力。下限側パワー MOSFET に内部接続されています。パワー・インダクタに接続します。                                                                                                                                                                                                 |

| サーマル・パッド  | 9  | G       | これは内部チップの主要な放熱経路となります。PCB のグランド・プレーンに接続する必要があります。                                                                                                                                                                                                          |

(1) A = アナログ、P = 電源、G = グランド

## 5 仕様

### 5.1 絶対最大定格

接合部の動作時推奨温度である -40°C~125°Cにおいて (特に記述のない限り) <sup>(1)</sup>

|                 |                    | 最小値  | 最大値 | 単位 |

|-----------------|--------------------|------|-----|----|

| 入力電圧            | VIN、EN から GND へ    | -0.3 | 44  | V  |

|                 | BOOT から GND へ      | -0.3 | 49  |    |

|                 | SS から GND へ        | -0.3 | 5   |    |

|                 | FB から GND へ        | -0.3 | 5.5 |    |

|                 | RT / SYNC から GND へ | -0.3 | 3.6 |    |

| 出力電圧            | BOOT から SW へ       |      | 5.5 | V  |

|                 | SW から GND へ        | -3   | 44  |    |

| 接合部温度、 $T_J$    |                    | -40  | 150 | °C |

| 保管温度、 $T_{stg}$ |                    | -65  | 150 | °C |

- (1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについての話で、絶対最大定格において、またはこのデータシートの「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。絶対最大定格の状態が長時間続くと、デバイスの信頼性に影響を与える可能性があります。

### 5.2 ESD 定格

| パラメータ       | 説明   |                                                                  | 値     | 単位 |

|-------------|------|------------------------------------------------------------------|-------|----|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、ANSI / ESDA / JEDEC JS-001 に準拠、すべてのピン <sup>(1)</sup> | ±2000 | V  |

|             |      | デバイス帶電モデル (CDM)、JEDEC 仕様 JESD22-C101 に準拠、すべてのピン <sup>(2)</sup>   | ±500  |    |

(1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

(2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

### 5.3 推奨動作条件

接合部温度の推奨動作範囲が -40°C~125°C である場合 (特に記述のない限り)

|          |                          | 最小値 | 最大値  | 単位  |

|----------|--------------------------|-----|------|-----|

| 降圧レギュレータ | VIN                      | 4   | 40   | V   |

|          | VOUT                     | 0.8 | 32   |     |

|          | BOOT                     |     | 45   |     |

|          | SW                       | -1  | 40   |     |

|          | FB                       | 0   | 5    |     |

| 制御       | EN                       | 0   | 40   | V   |

|          | RT / SYNC                | 0   | 3.3  |     |

|          | SS                       | 0   | 3    |     |

| 周波数      | RT モードを使用したスイッチング周波数範囲   | 200 | 2000 | kHz |

|          | SYNC モードを使用したスイッチング周波数範囲 | 250 | 2000 |     |

| 温度       | 動作時の接合部温度、 $T_J$         | -40 | 125  | °C  |

## 5.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup> |                             | LV14340     | 単位   |

|----------------------|-----------------------------|-------------|------|

| DDA (HSOIC)          |                             | DDA (HSOIC) |      |

| 8 ピン                 |                             | 8 ピン        |      |

| $R_{\theta JA}$      | 接合部から周囲への熱抵抗 <sup>(2)</sup> | 43.2        | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ            | 5.2         |      |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ            | 16.4        |      |

| $R_{\theta JC(top)}$ | 接合部からケース(上面)への熱抵抗           | 52.1        |      |

| $R_{\theta JC(bot)}$ | 接合部からケース(底面)への熱抵抗           | 7.8         |      |

| $R_{\theta JB}$      | 接合部から基板への熱抵抗                | 16.4        |      |

(1) 従来および最新の熱評価基準の詳細については、『半導体およびICパッケージの熱評価基準』アプリケーションノートを参照してください。

(2) 特定の周囲温度  $T_A$  における電力定格は、最大接合部温度 ( $T_J$ ) 125°C で決定する必要があります。これについては、「推奨動作条件」セクションに示します。

## 5.5 電気的特性

特に記述のない限り、各制限値は推奨動作接合部温度 ( $T_J$ ) 範囲 (-40°C ~ +125°C) にわたって適用されます。最小値および最大値は、試験、設計、および統計的相関に基づいて規定されています。標準値は  $T_J = 25^\circ\text{C}$  における最も一般的なパラメータ基準値を表しており、参考目的にのみ提供されています。特記のない限り、次の条件が適用されます。  $V_{IN} = 4.0\text{ V} \rightarrow 40\text{ V}$

| パラメータ                   | テスト条件                | 最小値                                                                                   | 標準値            | 最大値            | 単位                   |

|-------------------------|----------------------|---------------------------------------------------------------------------------------|----------------|----------------|----------------------|

| <b>電源 (VIN ピン)</b>      |                      |                                                                                       |                |                |                      |

| $V_{IN}$                | 動作入力電圧               | 4                                                                                     |                | 40             | V                    |

| UVLO                    | 低電圧誤動作防止のスレッショルド     | 立ち上がりスレッショルド<br>ヒステリシス                                                                | 3.5<br>285     | 3.7            | 3.9 mV               |

| $I_{SHDN}$              | シャットダウン時の電源電流        | $V_{EN} = 0\text{V}, T_J = 25^\circ\text{C}, 4.0\text{V} \leq V_{IN} \leq 40\text{V}$ |                | 1.0            | 3.0 $\mu\text{A}$    |

| $I_Q$                   | 動作静止電流 (スイッチングなし)    | $V_{FB} = 1.0\text{V}, T_J = 25^\circ\text{C}$                                        |                | 300            | $\mu\text{A}$        |

| <b>イネーブル (EN ピン)</b>    |                      |                                                                                       |                |                |                      |

| $V_{EN\_TH}$            | EN スレッショルド電圧         |                                                                                       | 1.05           | 1.20           | 1.38 V               |

| $I_{EN\_PIN}$           | EN ピン電流              | イネーブル スレッショルド +50mV<br>イネーブル スレッショルド -50mV                                            |                | -4.6<br>-1.0   | $\mu\text{A}$        |

| $I_{EN\_HYS}$           | EN ヒステリシス電流          |                                                                                       |                | -3.6           | $\mu\text{A}$        |

| <b>外部設定可能なソフトスタート</b>   |                      |                                                                                       |                |                |                      |

| $I_{SS}$                | SS ピン電流              | $T_J = 25^\circ\text{C}$                                                              |                | -3.0           | $\mu\text{A}$        |

| <b>電圧リファレンス (FB ピン)</b> |                      |                                                                                       |                |                |                      |

| $V_{FB}$                | 帰還電圧                 | $T_J = 25^\circ\text{C}$<br>$T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$          | 0.744<br>0.735 | 0.750<br>0.750 | 0.756<br>0.765 V     |

| <b>下限側 MOSFET</b>       |                      |                                                                                       |                |                |                      |

| $R_{DS\_ON}$            | オン抵抗                 | $V_{IN} = 12\text{V}$                                                                 |                | 100            | 180 $\text{m}\Omega$ |

| <b>下限側 MOSFET 電流制限</b>  |                      |                                                                                       |                |                |                      |

| $I_{LIMIT}$             | 電流制限                 | $V_{IN} = 12\text{V}, T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$ , 開ループ          | 4.4            | 5.5            | 6.6 A                |

| <b>熱性能</b>              |                      |                                                                                       |                |                |                      |

| $T_{SHDN}$              | サーマル シャットダウンのスレッショルド |                                                                                       |                | 170            | $^\circ\text{C}$     |

| $T_{HYS}$               | ヒステリシス               |                                                                                       |                | 12             |                      |

## 5.6 スイッチング特性

接合部温度の推奨動作範囲が -40°C~125°C である場合 (特に記述のない限り)

| パラメータ           | テスト条件                        | 最小値                                                                   | 標準値 | 最大値 | 単位            |

|-----------------|------------------------------|-----------------------------------------------------------------------|-----|-----|---------------|

| $f_{SW}$        | スイッチング周波数                    | $R_T = 49.9\text{k}\Omega$ 、1% の精度                                    | 400 | 500 | 600           |

| $V_{SYNC\_HI}$  | SYNC クロック High レベル スレッシングノード |                                                                       | 1.7 |     | V             |

| $V_{SYNC\_LO}$  | SYNC クロック Low レベル スレッシングノード  |                                                                       |     | 0.5 |               |

| $T_{SYNC\_MIN}$ | 最小 SYNC 入力パルス幅               | 500kHz で測定、 $V_{SYNC\_HI} > 3\text{V}$ 、 $V_{SYNC\_LO} < 0.3\text{V}$ |     | 30  | ns            |

| $T_{LOCK\_IN}$  | PLL ロック イン時間                 | 500kHz で測定                                                            |     | 100 | $\mu\text{s}$ |

| $T_{ON\_MIN}$   | 最小の制御可能なオン時間                 | $V_{IN} = 12\text{V}$ 、 $I_{Load} = 1\text{A}$                        |     | 100 | ns            |

| $D_{MAX}$       | 最大デューティ サイクル                 | $f_{SW} = 200\text{kHz}$                                              |     | 97% |               |

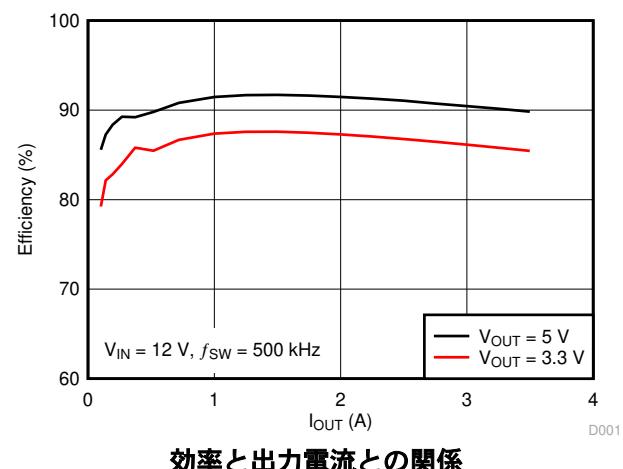

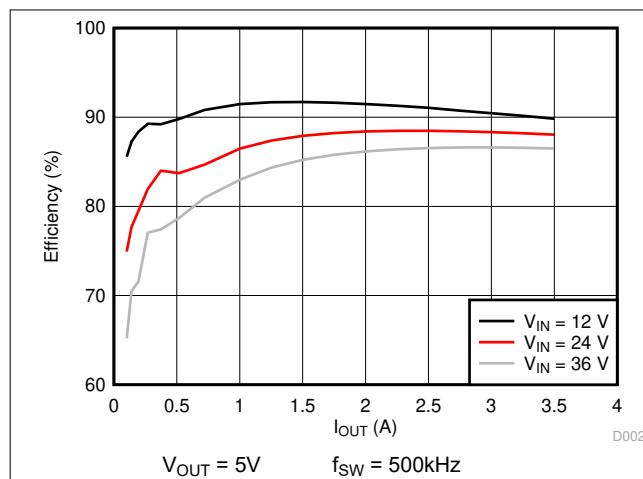

## 5.7 代表的特性

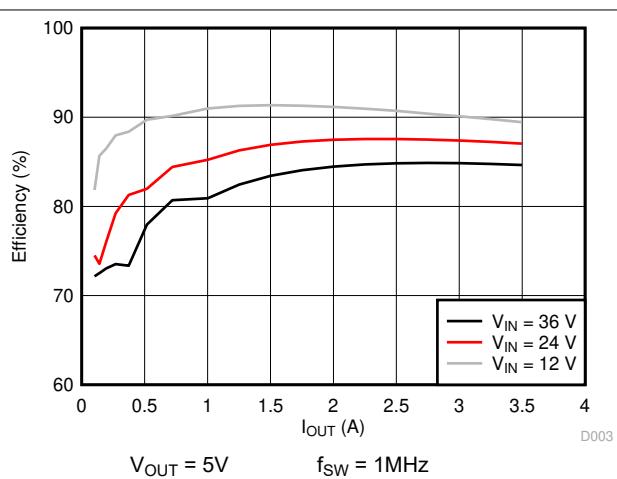

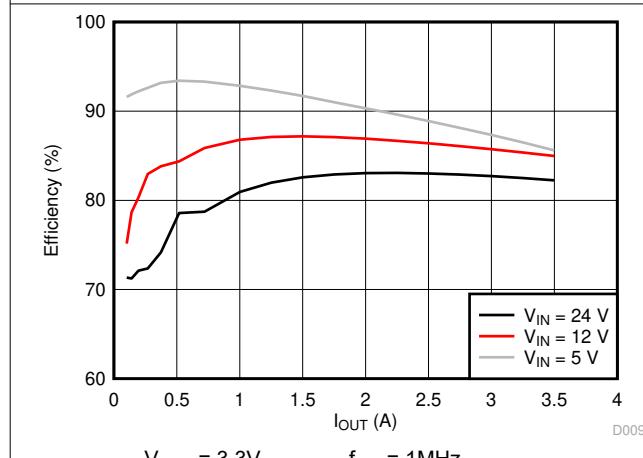

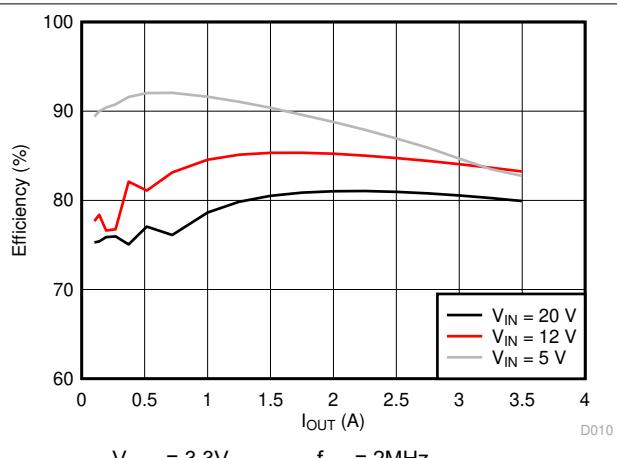

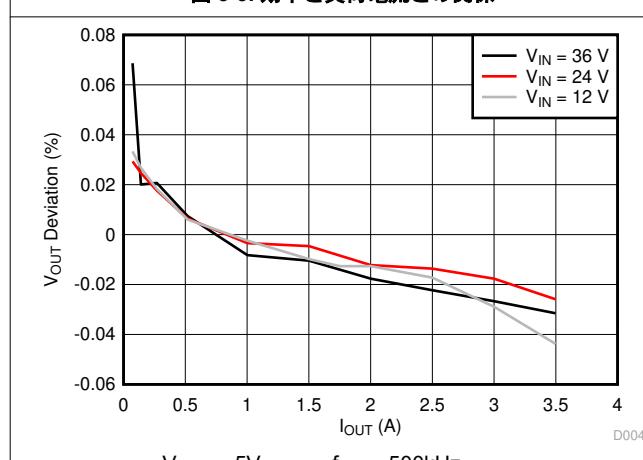

特記のない限り、次の条件が適用されます。 $V_{IN} = 12V$ 、 $f_{SW} = 500kHz$ 、 $L = 5.6\mu H$ 、 $C_{OUT} = 47\mu F \times 2$ 、 $T_A = 25^\circ C$ 。

図 5-1. 効率と負荷電流との関係

図 5-2. 効率と負荷電流との関係

図 5-3. 効率と負荷電流との関係

図 5-4. 効率と負荷電流との関係

図 5-5. ロード レギュレーション

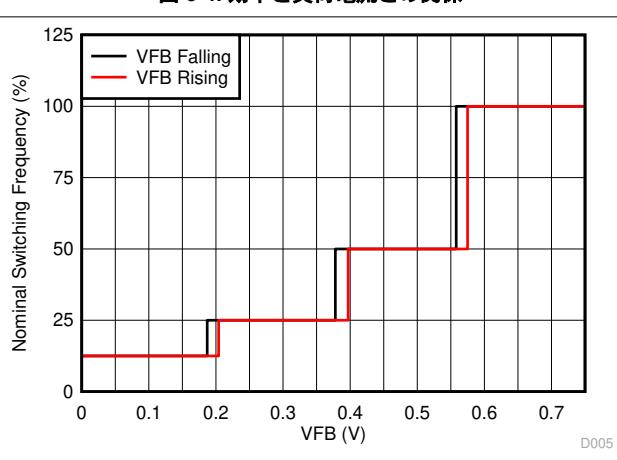

図 5-6. 周波数と  $V_{FB}$  との関係

## 5.7 代表的特性 (続き)

特記のない限り、次の条件が適用されます。 $V_{IN} = 12V$ 、 $f_{SW} = 500kHz$ 、 $L = 5.6\mu H$ 、 $C_{OUT} = 47\mu F \times 2$ 、 $T_A = 25^\circ C$ 。

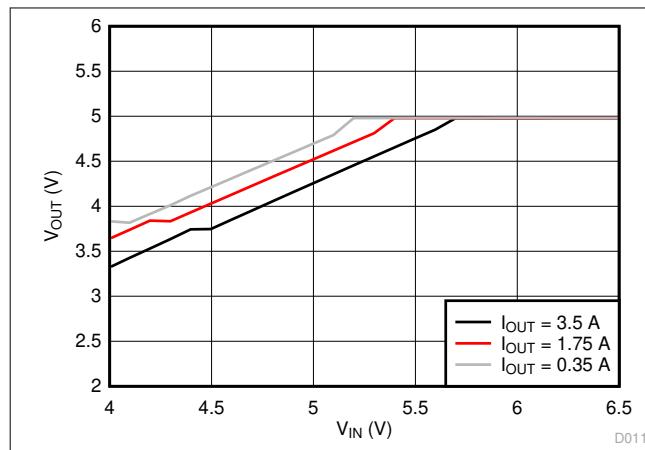

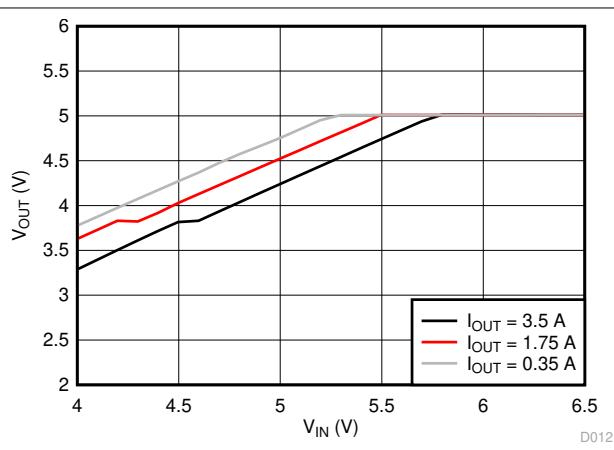

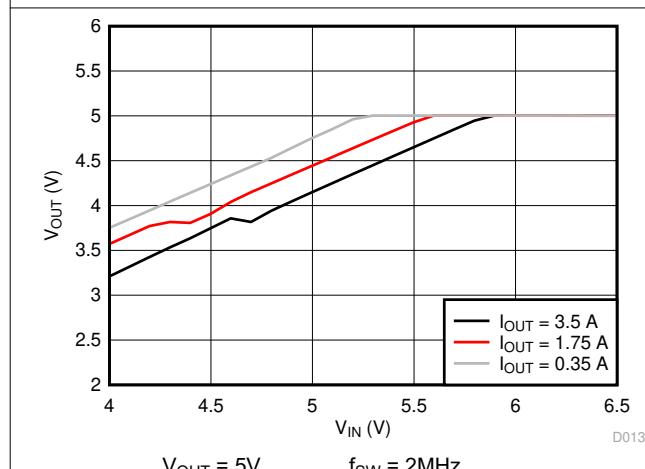

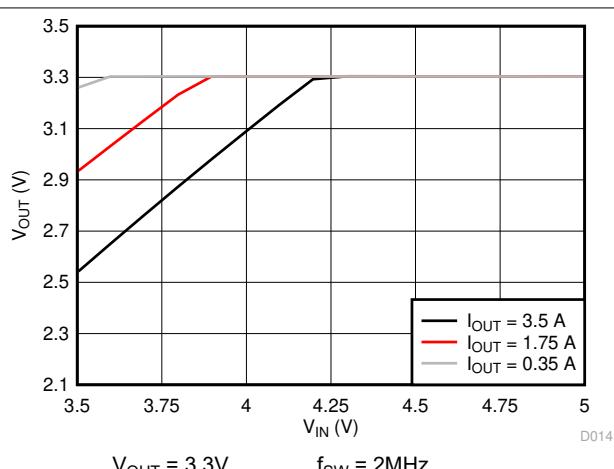

図 5-7. ドロップアウト曲線

図 5-8. ドロップアウト曲線

図 5-9. ドロップアウト曲線

図 5-10. ドロップアウト曲線

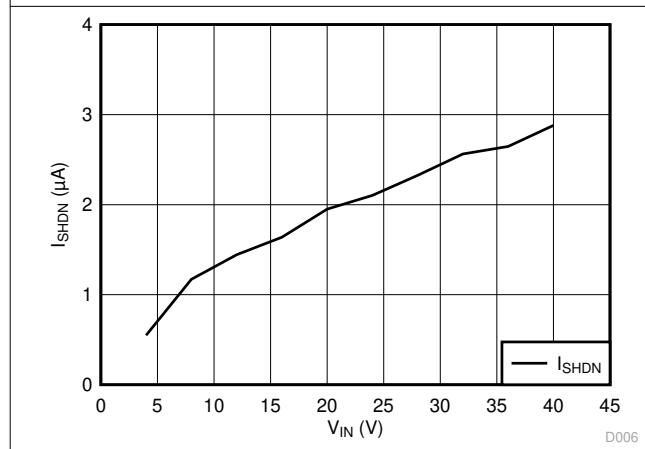

図 5-11. シャットダウン電流

$I_{OUT} = 0A$

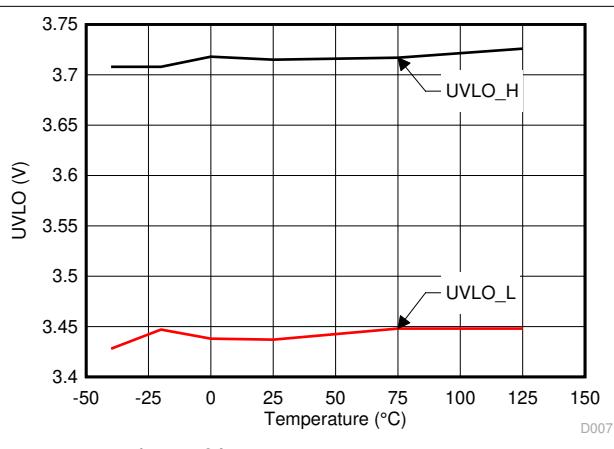

図 5-12. UVLO スレッショルド

## 6 詳細説明

### 6.1 概要

LV14340 レギュレータは、4.0V～40V の電源電圧で動作する使いやすい降圧型 DC/DC コンバータです。このデバイスには  $100\text{m}\Omega$  (標準値) の下限側 MOSFET が内蔵されており、非常に小さな設計サイズで、非常に優れた効率性と熱性能で最大 3.5A の DC 負荷電流を供給できます。無負荷時 (非スイッチング時) の動作電流の標準値は、 $300\mu\text{A}$  です。デバイスがディスエーブル時の消費電流の標準値は  $1\mu\text{A}$  です。広範な製品ファミリには、2A、5A の負荷製品がピン互換のパッケージで供給されています。

LV14340 は、固定周波数のピーク電流モード制御を実装し、軽負荷時はパルス スキップ モードを使用して高い効率を実現します。デバイスは内部で位相補償されているため、設計時間が短縮され、必要な外部部品も少なくて済みます。スイッチング周波数は、外部抵抗  $R_T$  を使用して、200kHz～2 MHz の範囲でプログラミングできます。LV14340 は 250kHz～2MHz の周波数範囲内の外部クロックと同期可能なため、デバイスを高周波数では小さな基板面積に収まるよう、または低周波数では高効率の電力変換に最適化できます。

より包括的なシステム要件に対して、高精度イネーブル、調整可能なソフトスタート時間、BOOT コンデンサ再充電回路による約 97% のデューティ サイクルなど、他のオプション機能も搭載されています。これらの機能により、幅広い範囲のアプリケーションに対応した柔軟で使いやすいプラットフォームが得られます。保護機能には、以下のものがあります。

- 過熱シャットダウン

- $V_{\text{OUT}}$  過電圧保護 (OVP)

- $V_{\text{IN}}$  低電圧誤動作防止 (UVLO)

- サイクル単位の電流制限

- 周波数フォールドバックによる短絡保護

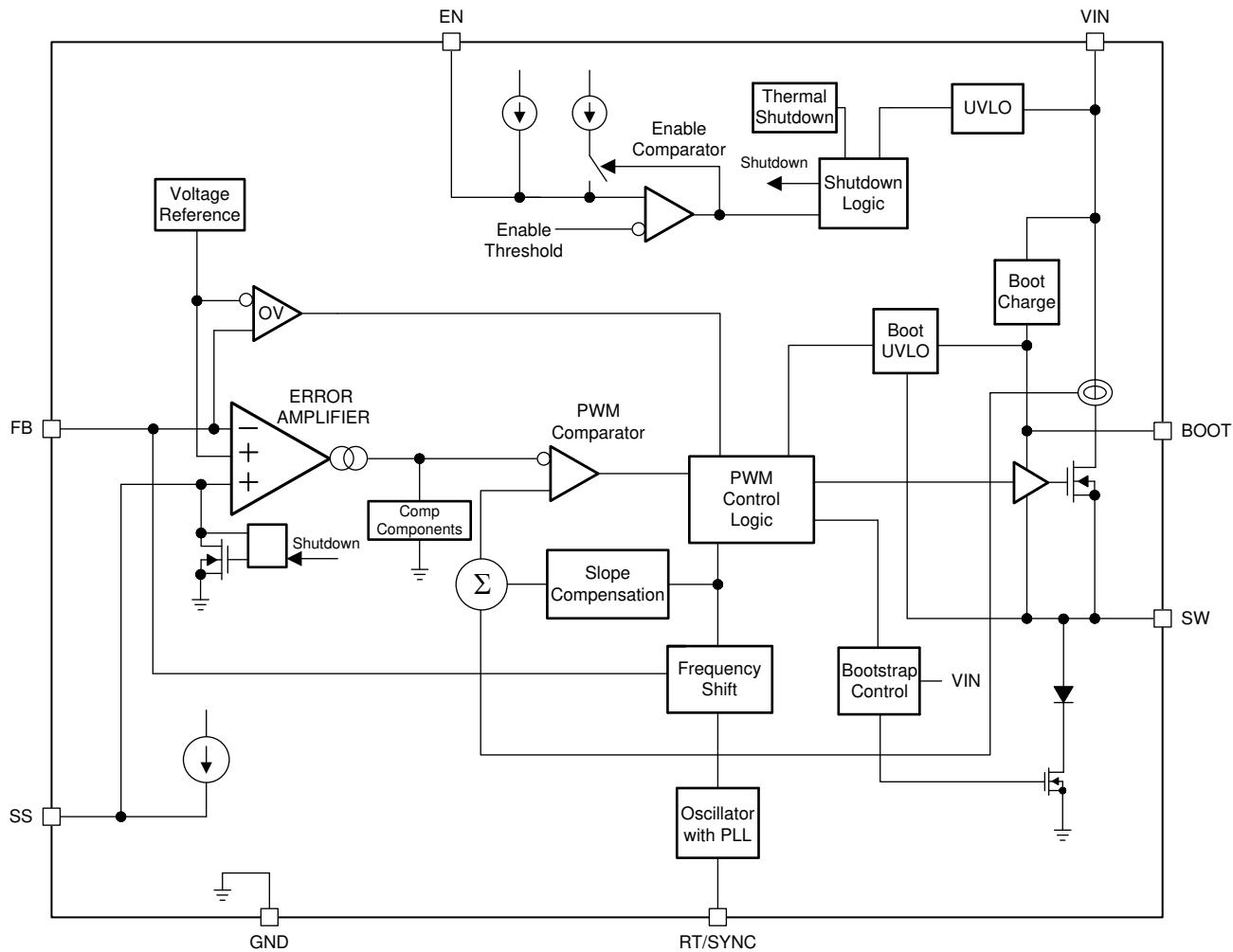

## 6.2 機能ブロック図

## 6.3 機能説明

### 6.3.1 固定周波数のピーク電流モード制御

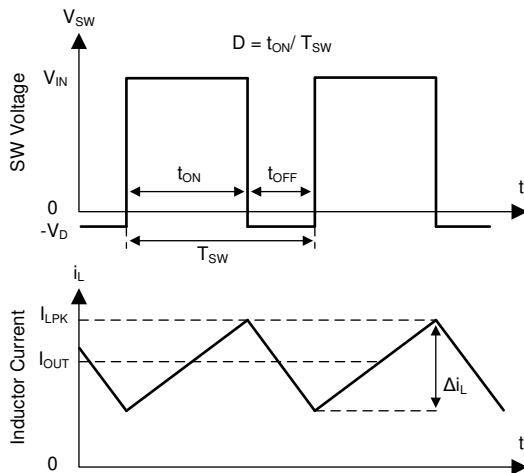

以下の LV14340 の動作の説明は、セクション 6.2 と図 6-1 の波形を指しています。LV14340 の出力電圧は、制御されたオン時間で下限側 N-MOSFET をオンにすることでレギュレートされます。下限側スイッチのオン時間中、SW ピンの電圧は約  $V_{IN}$  までスインギングし、インダクタ電流  $i_L$  は線形的に増加します ( $(V_{IN} - V_{OUT}) / L$ )。下限側スイッチがオフのとき、インダクタ電流は勾配  $-V_{OUT} / L$  のフリーホイール ダイオードを経由して放電されます。降圧コンバータの制御パラメータは、次のように定義されます。

$$\text{duty cycle } D = t_{ON} / T_{SW} \quad (1)$$

ここで、

- $t_{ON}$  は下限側スイッチのオン時間です

- $T_{SW}$  はスイッチング周期です

レギュレータ制御ループは、デューティサイクル  $D$  を調整することにより、出力電圧を一定に維持します。損失を無視できるような理想的な降圧コンバータ  $D = V_{OUT} / V_{IN}$  では、 $D$  は出力電圧に比例し、入力電圧に反比例します。

図 6-1. 連続導通モード (CCM) における SW ノードとインダクタ電流の波形

LV14340 は、固定周波数のピーク電流モード制御を使用します。電圧帰還ループを使用して、電圧オフセットに基づいてピーク電流コマンドを調整することにより、DC 電圧を正確にレギュレートします。ピーク インダクタ電流は下限側スイッチから検出され、ピーク電流と比較することにより、下限側スイッチのオン時間を制御します。電圧帰還ループは内部補償されているため、外付け部品が少なくて済み、設計が簡単です。また、電圧帰還ループは、ほとんどどのような組み合わせの出力コンデンサでも安定した動作を実現します。レギュレータは、通常負荷状況では固定スイッチング周波数で動作します。負荷が非常に軽い場合、LV14340 はパルス スキップ モードで動作することで高い効率を維持し、スイッチング周波数は負荷電流の減少に伴って低下します。

### 6.3.2 スロープ補償

LV14340 は、MOSFET スイッチ電流センス信号に補償ランプを追加します。このスロープ補償により、50% を超えるデューティ・サイクルでの低調波発振を防いでいます。下限側スイッチのピーク電流制限はスロープ補償に影響されず、全デューティ・サイクル範囲を通して一定に保たれます。

### 6.3.3 パルス・スキップ・モード

LV14340 は、軽負荷電流時にはパルス・スキップ・モード (PSM) で動作し、スイッチング損失やゲート駆動損失の低減によって効率を向上させます。出力電圧がレギュレーション範囲内のときに、任意のスイッチング・サイクルの終わりでピーク・スイッチング電流が電流スレッショルド 300mA を下回っている場合、デバイスは PSM に入ります。PSM 電流スレッショルドは、公称内部 COMP 電圧 (400mV) に対応したピーク・スイッチ電流レベルです。

PSM では、内部 COMP 電圧が 400mV にクランプされ、下限側 MOSFET が禁止され、デバイスの入力静止電流は約 120µA です。デバイスはスイッチングを停止しているため、出力電圧は低下し始めます。電圧制御ループでは、この立ち下がり出力電圧に対応して、内部 COMP 電圧を上昇させます。エラー・アンプによって内部 COMP 電圧が 400mV を超えると、下限側 MOSFET がイネーブルになり、スイッチングが再開されます。出力電圧がレギュレーション値に復帰した後、最終的に内部 COMP 電圧が PSM スレッショルドを下回ると、デバイスは再度 PSM に入ります。

### 6.3.4 低ドロップアウト動作とブートストラップ電圧 (BOOT)

LV14340 は、統合型ブートストラップ電圧レギュレータです。BOOT ピンと SW ピンの間にある小型コンデンサは、下限側 MOSFET のゲート駆動電圧を供給します。下限側 MOSFET がオフで、外部上限側ダイオードが導通している場合、BOOT コンデンサはリフレッシュされます。BOOT コンデンサの推奨値は 0.1µF です。テキサス・インスツルメンツは、温度および電圧に対して安定した特性を持つため、X7R または X5R クラスの誘電体を持つ電圧定格 16V 以上のセラミック・コンデンサを推奨します。

入力と出力の電圧差が小さい状態で動作している場合、LV14340 の下限側 MOSFET は約 97% のデューティ・サイクルで動作します。下限側 MOSFET が 5 または 6 スイッチング・サイクル (周波数が 1MHz 未満の場合は 5 または 6 スイッチング・サイクル、また周波数が 1MHz を超える場合は 10 または 11 スイッチング・サイクル) にわたって継続的にオ

ンで、BOOT から SW への電圧が 3.2V を下回ると、下限側 MOSFET がオフになり、内蔵上限側 MOSFET が SW を Low にプルして BOOT コンデンサを再充電します。

BOOT コンデンサからソースされるゲート駆動電流は小さいため、下限側 MOSFET は、MOSFET がオフになってコンデンサをリフレッシュする前に、多数のスイッチング・サイクルにわたってオン状態を維持できます。そのため、スイッチング・レギュレータの実効デューティ・サイクルは高く、97% に近い値で動作できます。ドロップアウト時のコンバータの実効デューティ・サイクルは、主に以下の影響を受けます。

- パワー MOSFET の両端での電圧降下

- インダクタの抵抗

- 上限側ダイオード電圧

- プリント基板の抵抗

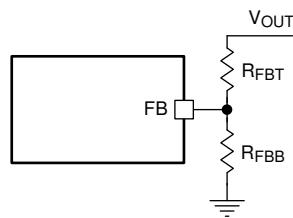

### 6.3.5 可変出力電圧

内部電圧リファレンスは、全動作温度範囲にわたって高精度の 0.75V (標準値) 電圧リファレンスを生成します。出力電圧は、出力電圧と FB ピンとの間の分圧抵抗回路によって設定されます。テキサス・インスツルメントは、公差が 1% 以内で、温度係数が 100ppm 以下の分圧抵抗回路を推奨します。目的の分圧器電流に対応する上限側抵抗  $R_{FBB}$  を選択し、式 2 を使用して下限側  $R_{FBT}$  を計算します。分圧抵抗回路の値が大きいほど、軽負荷時の効率が優れています。ただし、値が大きすぎると、レギュレータがノイズの影響を受けやすくなり、FB 入力電流からの電圧誤差が目立つようになる場合があります。ほとんどのアプリケーションでは、10kΩ～100kΩ の範囲の  $R_{FBB}$  が推奨されています。

図 6-2. 出力電圧設定

$$R_{FBT} = \frac{V_{OUT} - 0.75}{0.75} R_{FBB} \quad (2)$$

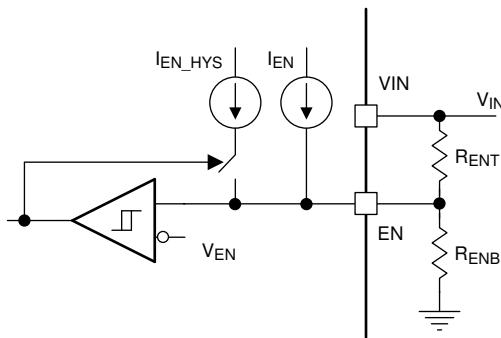

### 6.3.6 イネーブルおよび可変低電圧誤動作防止

LV14340 は、VIN ピンの電圧が 3.7V (標準値) を上回り、EN ピンの電圧がイネーブル スレッショルドの 1.2V (標準値) を超えているときにイネーブルになります。LV14340 は、VIN ピンの電圧が 3.42V (標準値) を下回るか、EN ピンの電圧が 1.2V を下回るとディセーブルになります。EN ピンには内部プルアップ電流源 (通常は  $I_{EN} = 1\mu A$ ) があり、これにより EN ピンがフローティングのとき、LV14340 の動作がイネーブルになります。

多くのアプリケーションでは、図 6-3 に示されるイネーブル分圧抵抗  $R_{ENT}$  および  $R_{ENB}$  を使用することで、段の高精度のシステム UVLO レベルを確立できます。システム UVLO は、商用電源またはバッテリから供給される電源に対して使用できます。システム UVLO は、シーケンシングや、動作の信頼性の確保、バッテリなどの電源の保護に利用できます。また、外部ロジック信号を使用して EN 入力を駆動することでも、システムのシーケンシングや保護を行うことができます。

EN 端子の電圧が 1.2V を超えると、追加のヒステリシス電流 (通常  $I_{HYS} = 3.6\mu A$ ) が EN 端子からソースされます。EN 端子が 1.2V 未満になると、 $I_{HYS}$  電流は停止されます。この追加電流により、可変入力電圧 UVLO のヒステリシスを実現できます。式 3 および式 4 を使用して、目的の UVLO ヒステリシス電圧に対して  $R_{ENT}$  および  $R_{ENB}$  を計算します。

図 6-3. イネーブル分圧抵抗によるシステム UVLO

$$R_{EN} = \frac{V_{START} - V_{STOP}}{I_{HYS}} \quad (3)$$

$$R_{ENB} = \frac{V_{EN}}{V_{START} - V_{EN} + I_{EN}} \quad (4)$$

ここで、

- $V_{START}$  は LV14340 をイネーブルにするための目的の電圧スレッショルドです

- $V_{STOP}$  は、デバイスをディセーブルするための目的の電圧スレッショルドです

### 6.3.7 外部設定可能なソフトスタート

LV14340 にはソフトスタートピンがあり、出力の上昇時間をプログラムできます。ソフトスタート機能を使用すると、電源を最初に供給したときに LV14340 に影響を与える突入電流とその負荷を防止できます。ソフトスタート時間は、SS ピンと GND の間に外付けコンデンサ  $C_{SS}$  を接続することでプログラムできます。内部電流源 (標準値  $I_{SS} = 3\mu A$ ) は  $C_{SS}$  に電荷を供給し、0V から  $V_{REF}$  (標準値 0.75V) まで上昇します。ソフトスタート時間を計算するには、式 5 を使用します。

$$t_{SS}(\text{ms}) = \frac{C_{SS}(\text{nF}) \times V_{REF}(\text{V})}{I_{SS}(\mu\text{A})} \quad (5)$$

内部ソフトスタートは、デバイスがディセーブルの間、またはサーマルシャットダウン中にリセットされます。

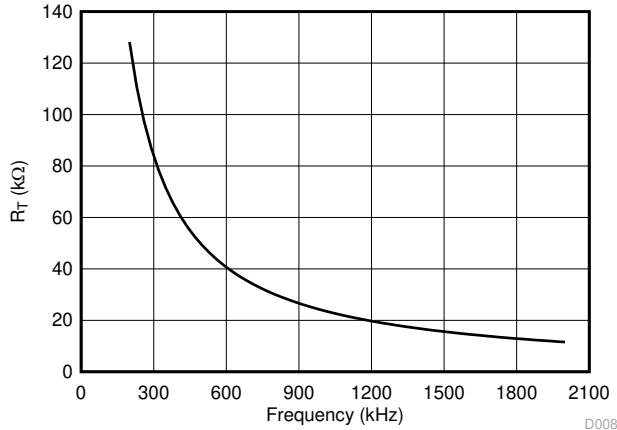

### 6.3.8 スイッチング周波数および同期 (RT / SYNC)

LV14340 のスイッチング周波数は、RT / SYNC ピンと GND ピンからの抵抗  $R_T$  を使用してプログラム可能です。RT / SYNC ピンは、フローティングのままにしたり、グランドに短絡したりすることはできません。特定のスイッチング周波数に対するタイミング抵抗を決定するには、式 6 を使用するか、図 6-4 の曲線を使用します。表 6-1 には、特定の  $f_{SW}$  値に対する  $R_T$  の標準値を示します。

$$R_T(\text{k}\Omega) = 42904 \times f_{SW}(\text{kHz})^{-1.088} \quad (6)$$

図 6-4.  $R_T$  と周波数曲線との関係表 6-1. 周波数に対する  $R_T$  の標準抵抗値

| $f_{SW}$ (kHz) | $R_T$ (kΩ) |

|----------------|------------|

| 200            | 133        |

| 350            | 73.2       |

| 500            | 49.9       |

| 750            | 32.4       |

| 1000           | 23.2       |

| 1500           | 15.0       |

| 1912           | 11.5       |

| 2000           | 11.0       |

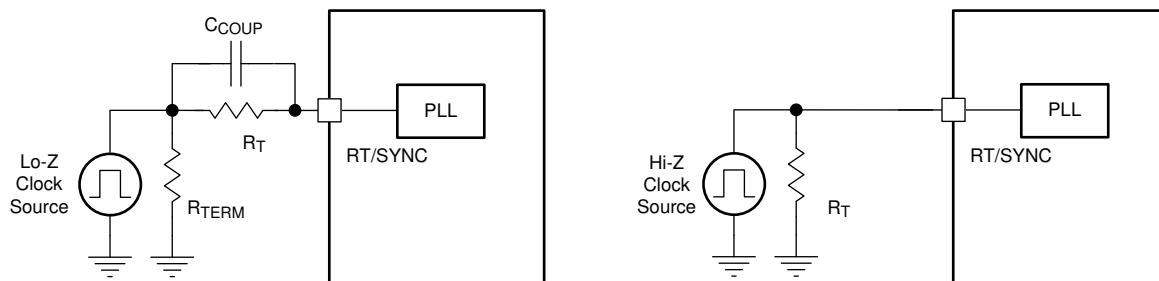

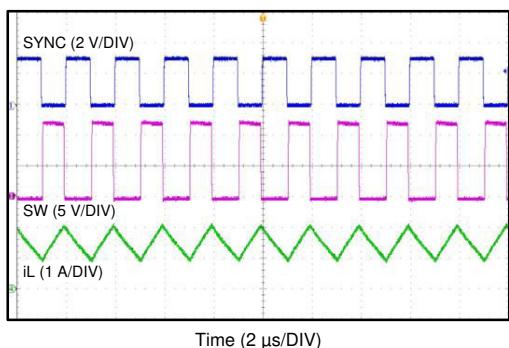

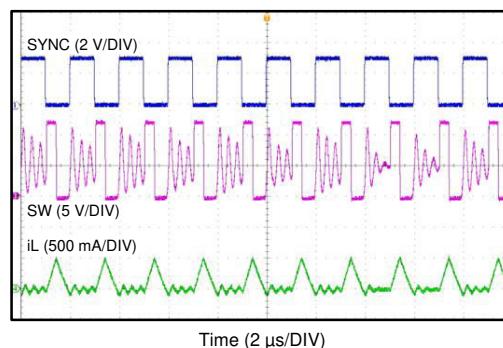

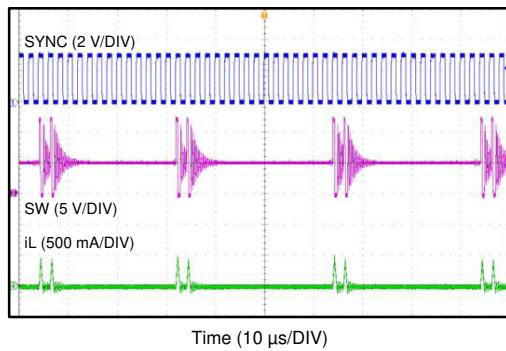

LV14340 のスイッチング動作は、250kHz～2MHz の外部クロックに同期させることもできます。図 6-5 に示すいずれかの回路ネットワークを通して RT / SYNC ピンに方形波を接続します。自己発振器は、外部クロックの立ち下がりエッジによって同期されます。外部クロックの推奨値には、1.7V 以上の High レベル、0.5V 以下の Low レベル、30ns 以上のパルス幅があります。低インピーダンスの信号ソースを使用する場合、周波数設定の抵抗  $R_T$  は AC カップリング・コンデンサ  $C_{COUP}$  と並列になるよう、終端抵抗  $R_{TERM}$  に接続されます (例: 50Ω)。信号ソースがオフの場合、2 つの抵抗を直列に配置すると、デフォルトの周波数設定の抵抗になります。 $C_{COUP}$  には 100pF～470pF のセラミック・コンデンサを使用できます。図 6-6、図 6-7、および図 6-8 に、外部のシステム・クロックに同期したデバイスを示します。

図 6-5. 外部クロックへの同期

図 6-6. CCM の同期

図 6-7. DCM の同期

図 6-8. PSM の同期

式 7 で、最小制御可能オン時間と入力と出力の降圧比によって設定される最大スイッチング周波数制限を計算します。スイッチング周波数をこの値より上に設定すると、レギュレータは最大入力電圧で必要となる低いデューティ・サイクルを実現するために、スイッチング・パルスをスキップします。

$$f_{SW(max)} = \frac{1}{t_{ON}} \times \left( \frac{I_{OUT} \times R_{IND} + V_{OUT} + V_D}{V_{IN\_MAX} - I_{OUT} \times R_{DS\_ON} + V_D} \right) \quad (7)$$

ここで、

- $I_{OUT}$  = 出力電流

- $R_{IND}$  = インダクタの直列抵抗

- $V_{IN\_MAX}$  = 最大入力電圧

- $V_{OUT}$  = 出力電圧

- $V_D$  = ダイオードの電圧降下

- $R_{DS\_ON}$  = 下限側 MOSFET のスイッチ・オン抵抗

- $t_{ON}$  = 最小オン時間

### 6.3.9 過電流および短絡保護

LV14340 は、下限側 MOSFET のピーク電流でサイクル毎に電流を制限することで、過電流状態から保護されます。下限側 MOSFET 過電流保護機能は、ピーク電流のモード制御の性質を利用して実装されています。下限側スイッチ電流は、スイッチング サイクルごとに、誤差アンプ (EA) からスロープ補償を引いた出力と比較されます。詳細については、[セクション 6.2](#) を参照してください。下限側スイッチのピーク電流は、一定であるクランプされた最大ピーク電流スレッショル

ドによって制限されるため、下限側スイッチのピーク電流制限はスロープ補償の影響を受けず、デューティサイクル範囲全体にわたって一定に保たれます。

LV14340 は、重大な過電流または短絡状態でコンバータを保護するため、周波数フォールドバックも実装しています。FB ピンの電圧が  $V_{REF}$  の 75%、50%、25% に低下すると、発振器の周波数は 2、4、8 で分周されます。周波数フォールドバックでは、スイッチングサイクルの周期を長くすることでオフ時間が長くなるため、インダクタ電流が下がる時間が長くなり、平均インダクタ電流が減少します。周波数が低いとスイッチング損失も小さくなります。周波数フォールドバックにより、消費電力が低減され、過熱やデバイスへの潜在的な損傷が防止されます。

### 6.3.10 過電圧保護

LV14340 には、出力過電圧保護 (OVP) 回路が備えられており、設計の出力容量が小さい場合に、出力障害状態や強い無負荷過渡事象からの回復時に発生する電圧オーバーシュートを最小限に抑えます。OVP 機能は、FB 電圧が立ち上がり OVP スレッショルド、すなわち内部電圧リファレンス  $V_{REF}$  の公称 109% に達した時点で、下限側スイッチを直ちにオフにすることで、出力オーバーシュートを最小限に抑えます。FB 電圧が立ち下がり OVP スレッショルド ( $V_{REF}$  の公称 107%) を下回ると、下限側 MOSFET は通常動作に戻ります。

### 6.3.11 サーマル・シャットダウン

LV14340 は、接合部の温度が 170°C (標準値) を超えた場合にデバイス自体を保護するため、内部的なサーマル・シャットダウン機能を提供しています。サーマル・シャットダウンが作動すると、下限側 MOSFET はスイッチングを停止します。ダイ温度が 158°C (標準値) 未満になると、デバイスは内蔵のソフト・スタート回路による制御下で電源投入時シーケンスを再び開始します。

## 6.4 デバイスの機能モード

### 6.4.1 シャットダウン・モード

EN ピンは、LV14340 の電気的なオン / オフを制御します。 $V_{EN}$  が 1.0V を下回ると、デバイスはシャットダウン・モードになります。スイッチング・レギュレータがオフになり、静止電流は標準で  $1.0\mu A$  に低下します。LV14340 は低電圧誤動作防止保護も採用しています。 $V_{IN}$  電圧が UVLO レベルを下回ると、レギュレータはオフになります。

### 6.4.2 アクティブモード

$V_{EN}$  が高精度イネーブル スレッショルドを上回り、 $V_{IN}$  が UVLO レベルを超えていたとき、LV14340 はアクティブ モードになります。LV14340 をイネーブルにする最も簡単な方法は、EN ピンを VIN ピンに接続することです。これにより、入力電圧が動作範囲内 (4.0V~40V) になると自動的に起動できます。これらの動作レベルの設定の詳細については、[セクション 6.3.6](#) を参照してください。

アクティブ モードでは、負荷電流に応じて、LV14340 が次の 3 つのうちいずれかのモードになります。

1. 連続導通モード (CCM)。負荷電流がピークツーピーク インダクタ リップル電流の  $1/2$  より大きくなると、固定スイッチング周波数の連続導通モードになります。

2. 不連続導通モード (DCM)。CCM 動作で負荷電流がピークツーピーク インダクタ リップル電流の  $1/2$  より小さくなると、固定スイッチング周波数の不連続導通モードになります。

3. 非常に軽い負荷で内部 COMP 電圧が  $400mV$  に低下した場合のパルス スキップ モード。

### 6.4.3 CCM モード

負荷電流がピーク・ツー・ピーク・インダクタ電流の  $1/2$  より大きい場合、LV14340 は連続導通モード (CCM) で動作します。連続導通モードの動作では、動作周波数が固定され、このモードでは出力電圧リップルが最小になり、最大出力電流  $3.5A$  が LV14340 により供給できます。

### 6.4.4 軽負荷動作

負荷電流が CCM のピーク・ツー・ピーク・インダクタ電流の  $1/2$  未満の場合、LV14340 は DCM で動作します。電流負荷がさらに軽くなると、パルス・スキップ・モードに入り、スイッチング損失とゲート駆動損失を低減して高効率動作を維持します。

## 7 アプリケーションと実装

### 注

以下のアプリケーション情報は、TI の製品仕様に含まれるものではなく、TI ではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 7.1 アプリケーション情報

LV14340 は、降圧型 DC/DC レギュレータです。デバイスは、標準では、最大出力電流 3.5A で、高い DC 電圧から低い DC 電圧への変換に使用されます。以下に示す設計手順に従うことで、LV14340 に使用する各部品を選択できます。ここでは、設計手順について簡単に説明します。

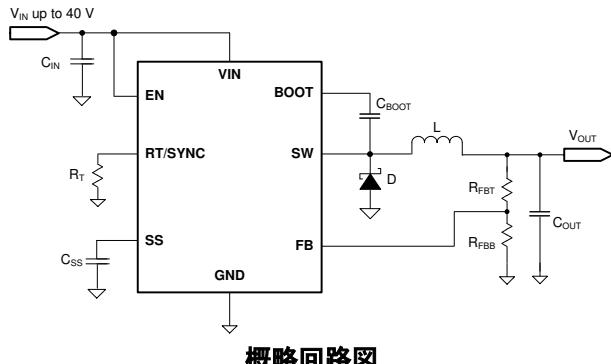

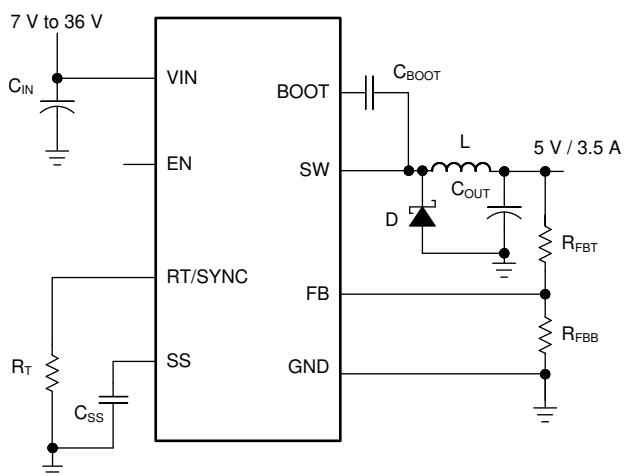

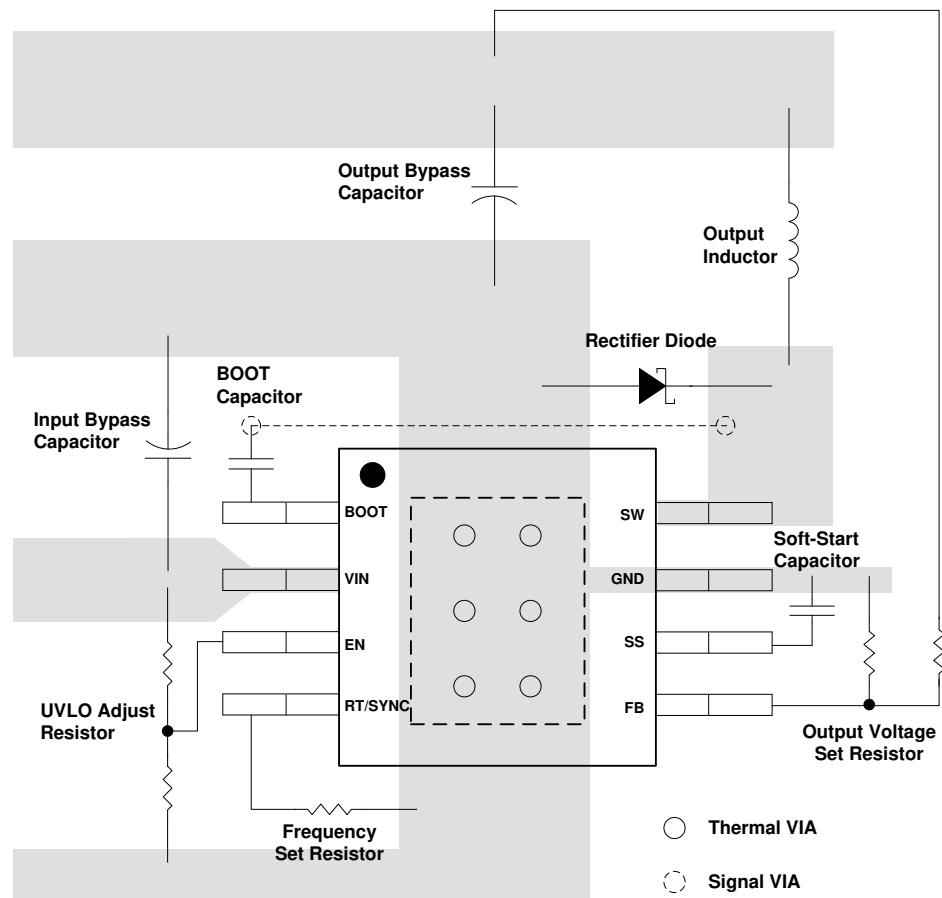

### 7.2 代表的なアプリケーション

LV14340 では、わずか数個の外部部品だけを使用して、幅広い範囲の電源電圧を固定出力電圧に変換できます。図 7-1 に、5V/3.5V アプリケーション回路図を示します。外付け部品は、アプリケーションのニーズだけでなく、デバイスの制御ループの安定性基準も満たしている必要があります。

図 7-1. アプリケーション回路、5V 出力

#### 7.2.1 設計要件

この例では、セラミック出力コンデンサを使用した高周波スイッチング・レギュレータの設計を詳しく示しています。設計プロセスを開始するには、いくつかのパラメータを知っている必要があります。これらのパラメータは一般に、システム・レベルで決定されます。

|                     |                |

|---------------------|----------------|

| 入力電圧、 $V_{IN}$      | 7V~36V、標準値 12V |

| 出力電圧、 $V_{OUT}$     | 5.0V           |

| 最大出力電流 $I_{O\_MAX}$ | 3.5A           |

| 0.35A から 3.5A の過渡応答 | 5%             |

| 出力電圧リップル            | 50mV           |

| 入力電圧リップル            | 400mV          |

| スイッチング周波数 $f_{sw}$  | 500kHz         |

| ソフトスタート時間           | 5ms            |

## 7.2.2 詳細な設計手順

### 7.2.2.1 出力電圧設定ポイント

LV14340 の出力電圧は、分圧抵抗回路を使用して外部で調整可能です。分圧抵抗回路は、上側帰還抵抗  $R_{FBT}$  と下側帰還抵抗  $R_{FBB}$  から構成されます。[式 8](#) を使用して、出力電圧を決定します。

$$R_{FBT} = \frac{V_{OUT} - 0.75}{0.75} R_{FBB} \quad (8)$$

$R_{FBT}$  の値として  $100\text{k}\Omega$  を選択します。目的の出力電圧が  $5\text{V}$  に設定され、 $V_{FB} = 0.75\text{V}$  のとき、 $R_{FBB}$  の値は[式 8](#) で計算できます。この式から、値  $17.65\text{k}\Omega$  が得られます。 $R_{FBB}$  に対して利用可能な最も近い値である  $17.8\text{k}\Omega$  を選択します。

### 7.2.2.2 スイッチング周波数

目的の周波数の場合は、[式 9](#) を使用して、必要な  $R_T$  の値を計算します。

$$R_T(\text{k}\Omega) = 42904 \times f_{SW}(\text{kHz})^{-1.088} \quad (9)$$

$500\text{kHz}$  の場合は、 $R_T$  の計算値が  $49.66\text{k}\Omega$  となるため、標準値の  $49.9\text{k}\Omega$  を使用してスイッチング周波数を  $500\text{kHz}$  に設定できます。

### 7.2.2.3 出力インダクタの選択

インダクタに最も重要なパラメータは、インダクタンス、飽和電流、および RMS 電流です。インダクタンスは、指定のピークツーピーク リップル電流  $\Delta i_L$  によって決まります。リップル電流は入力電圧とともに増大するため、必ず最大入力電圧を使用して最小インダクタンス  $L_{MIN}$  を計算します。出力インダクタの最小値を計算するには、[式 11](#) を使用します。 $K_{IND}$  は、最大出力電流に対するインダクタのリップル電流の量を示す係数です。 $K_{IND}$  の妥当な値として、 $20\% \sim 40\%$  になる必要があります。瞬間短絡、または過電流動作時は、RMS およびピーク インダクタ電流が高くなる可能性があります。インダクタ電流の定格は、電流制限よりも大きくする必要があります。

$$\Delta i_L = \frac{V_{OUT} \times (V_{IN\_MAX} - V_{OUT})}{V_{IN\_MAX} \times L \times f_{SW}} \quad (10)$$

$$L_{MIN} = \frac{V_{IN\_MAX} - V_{OUT}}{I_{OUT} \times K_{IND}} \times \frac{V_{OUT}}{V_{IN\_MAX} \times f_{SW}} \quad (11)$$

一般的に、スイッチング電源には低いインダクタンスを選択することが望ましいとされています。これにより、より高速な過渡応答、小さな DCR、コンパクトな設計のためのサイズ削減が可能になるためです。ただし、インダクタンスが低すぎると、インダクタ電流のリップルが過度に増大するため、全負荷時に過電流保護が誤作動を起こす可能性があります。また、RMS 電流がやや大きくなるため、導通損失も増大します。さらに、インダクタ リップル電流が大きいと、同じ出力コンデンサでの出力電圧リップルも増大します。ピーク電流モード制御では、テキサス・インスツルメンツでは、インダクタ電流のリップルが小さすぎることは推奨していません。ピークリップル電流が大きいほど、コンバレータの信号対雑音比が向上します。

この設計例では、 $K_{IND} = 0.4$  を選択します。インダクタの最小値は  $6.12\mu\text{H}$  と計算できます。最も近い標準値が選択されます。 $6.5\mu\text{H}$  です。RMS 電流  $4\text{A}$ 、飽和電流  $6.5\text{A}$  の標準的な  $6.5\mu\text{H}$  のフェライト インダクタを使用できます。

### 7.2.2.4 出力コンデンサの選択

出力コンデンサ  $C_{OUT}$  の選定には注意が必要です。出力コンデンサは、定常状態の出力電圧リップル、ループ安定性、負荷電流過渡時における電圧オーバーシュート / アンダーシュートに直接影響するからです。

出力リップルは、基本的に 2 つの部分で構成されます。1 つは、出力コンデンサの等価直列抵抗 (ESR) を流れるインダクタリップル電流に起因する成分です。

$$\Delta V_{OUT\_ESR} = \Delta i_L \times ESR = K_{IND} \times I_{OUT} \times ESR \quad (12)$$

もう1つは、出力コンデンサを充電および放電するインダクタリップル電流に起因する成分です。

$$\Delta V_{OUT\_C} = \frac{\Delta i_L}{8 \times f_{SW} \times C_{OUT}} = \frac{K_{IND} \times I_{OUT}}{8 \times f_{SW} \times C_{OUT}} \quad (13)$$

電圧リップルの2つの部品は同相ではなく、実際のピークツーピークリップルは2つのピークの合計よりも小さくなります。

通常、大電流ステップや高速スルーレートといった厳しい電圧レギュレーションが必要とされるシステムでは、出力容量は過渡性能の仕様によって制限されます。大きな負荷が高速で増大すると、出力コンデンサは、インダクタ電流が適切なレベルに増加できるまで必要な電荷を供給します。レギュレータの制御ループは、通常は出力電圧低下に応答するために3クロックサイクル以上が必要です。出力容量は、3クロックサイクルの電流差分を供給し、指定した範囲内での出力電圧を一定に保持するのに十分な大きさがなければなりません。式14に、指定の出力アンダーシュートに必要な最小出力容量を示します。大きな負荷が急激に減少すると、出力コンデンサはインダクタに蓄積されたエネルギーを吸収します。キャッチダイオードは電流をシンクできないため、インダクタに蓄積されたエネルギーは出力電圧のオーバーシュートを引き起こします。式15では、電圧オーバーシュートを指定範囲内に保持するために必要な最小容量を計算しています。

$$C_{OUT} > \frac{3 \times (I_{OH} - I_{OL})}{f_{SW} \times V_{US}} \quad (14)$$

$$C_{OUT} > \frac{I_{OH}^2 - I_{OL}^2}{(V_{OUT} + V_{OS})^2 - V_{OUT}^2} \times L \quad (15)$$

ここで、

- $K_{IND}$  = インダクタリップル電流のリップル比 ( $\Delta i_L / I_{OUT}$ )

- $I_{OL}$  = 負荷過渡時の Low レベル出力電流

- $I_{OH}$  = 負荷過渡時の High レベル出力電流

- $V_{US}$  = 目標出力電圧アンダーシュート

- $V_{OS}$  = 目標出力電圧オーバーシュート

この設計例では、目標出力リップルは 50mV です。 $\Delta V_{OUT\_ESR} = \Delta V_{OUT\_C} = 50mV$  と仮定し、 $K_{IND} = 0.4$  を選択しています。式12では最大 35.7mΩ の ESR が発生し、式13では 7μF 以上の  $C_{OUT}$  が発生します。この設計の目標オーバーシュート/アンダーシュートは、 $V_{US} = V_{OS} = 5\% \times V_{OUT} = 250mV$  です。 $C_{OUT}$  は、式14と式15によってそれぞれ 75.6μF 以上および 30.8μF 以上になるように計算できます。要約すると、出力コンデンサに対する最も厳格な条件は 75.6μF です。ESR 5mΩ の 47μF、16V、X7R セラミックコンデンサを2個並列に使用します。

### 7.2.2.5 ショットキー ダイオードの選択

ダイオードのブレークダウン電圧定格は、最大入力電圧より 25% 高くすることを推奨します。ほとんどのアプリケーションで最高の信頼性を得るには、ダイオードの電流定格が最大出力電流と等しい必要があります。入力電圧が出力電圧よりもはるかに高い場合、平均ダイオード電流は小さくなります。この場合、平均電流定格が約  $(1-D) \times I_{OUT}$  と低いダイオードを使用できます。ただし、ピーク電流定格は最大負荷電流よりも高くする必要があります。4A～5A の定格ダイオードが出発点として適しています。

### 7.2.2.6 入力コンデンサの選択

LV14340 には、アプリケーションに応じて、高周波入力デカップリングコンデンサおよびバルク入力コンデンサが必要となります。高周波デカップリングコンデンサの標準推奨値は、4.7μF～10μF です。テキサス・インスツルメンツでは、十分な電圧定格を持つ高品質セラミックコンデンサのタイプ X5R または X7R を推奨しています。セラミックコンデンサのディレイティングを補償するために、最大入力電圧の2倍の電圧定格を推奨します。また、特に LV14340 回路が入力電圧

源から約 5cm 以上離れている場合は、多少のバルク容量が必要になる場合があります。このコンデンサは、ケーブルまたはパターンのリード インダクタンスによる電圧スパイクを抑制するために使用されます。この設計では、定格 100V の X7R セラミック コンデンサ 2.2 $\mu$ F を 2 個使用します。0.1 $\mu$ F の高周波フィルタリングを行い、デバイスのピンのできるだけ近くに配置します。

#### 7.2.2.7 ブートストラップ・コンデンサの選択

LV14340 のすべての設計で、ブートストラップ・コンデンサ ( $C_{BOOT}$ ) が必要となります。推奨コンデンサは 0.1 $\mu$ F で、定格は 16V 以上です。ブートストラップ・コンデンサは、SW ピンと BOOT ピンの間に配置します。ブートストラップ・コンデンサには、温度安定性のために、X7R または X5R グレードの誘電体を使用した高品質セラミック・タイプを使用してください。

#### 7.2.2.8 ソフト・スタート・コンデンサの選択

ソフト・スタート・コンデンサの値を計算するには、式 16 を使用します。

$$C_{SS}(\text{nF}) = \frac{t_{SS}(\text{ms}) \times I_{SS}(\mu\text{A})}{V_{REF}(\text{V})} \quad (16)$$

ここで、

- $C_{SS}$  = ソフト・スタート・コンデンサの値

- $I_{SS}$  = ソフト・スタート充電電流 (3 $\mu$ A)

- $t_{SS}$  = 目的のソフト・スタート時間

目的のソフト・スタート時間が 5ms、ソフト・スタート充電電流が 3.0 $\mu$ A の場合、式 16 によりソフト・スタート・コンデンサの値は 20nF となります。標準的な 22nF のセラミック・コンデンサを使用します。

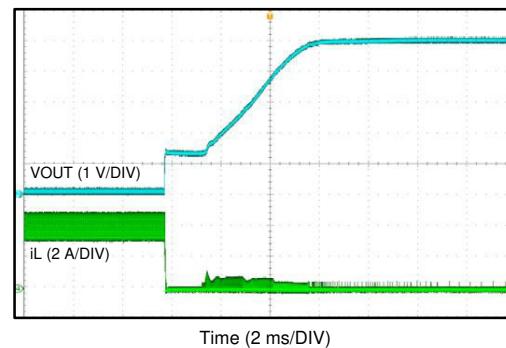

### 7.2.3 アプリケーション曲線

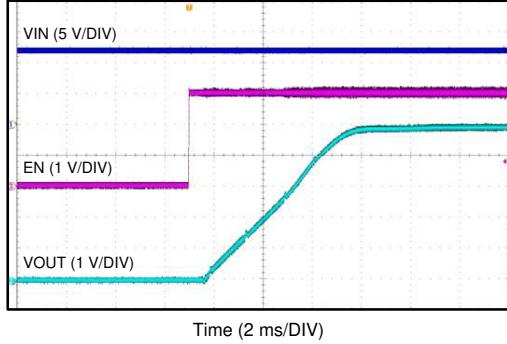

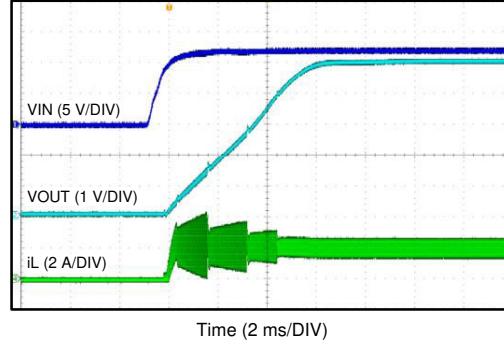

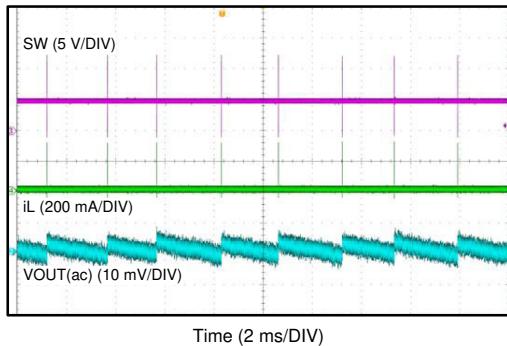

特記のない限り、次の条件が適用されます。 $V_{IN} = 12V$ 、 $f_{SW} = 500kHz$ 、 $L = 5.6\mu H$ 、 $C_{OUT} = 47\mu F \times 2$ 、 $T_A = 25^\circ C$ 。

$V_{IN} = 12V$  $V_{OUT} = 5V$  $I_{OUT} = 2A$

図 7-2. EN によるスタートアップ

$V_{IN} = 12V$  $V_{OUT} = 5V$  $I_{OUT} = 2A$

図 7-3. VIN によるスタートアップ

$V_{IN} = 12V$  $V_{OUT} = 5V$  $I_{OUT} = 0A$

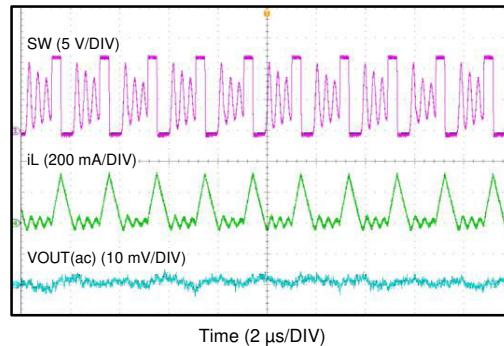

図 7-4. パルス スキップ モード

$V_{IN} = 12V$  $V_{OUT} = 5V$  $I_{OUT} = 100mA$

図 7-5. DCM モード

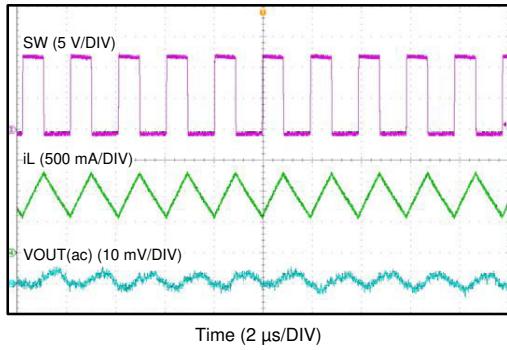

図 7-6. CCM モード

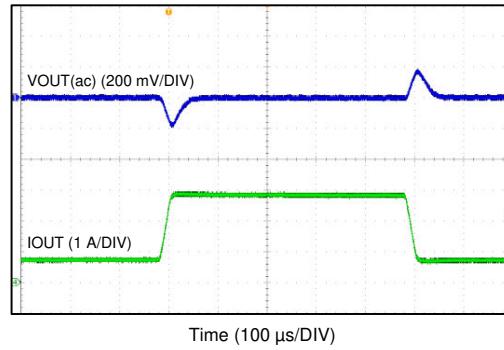

$I_{OUT}: 20\% \rightarrow 3.5A$

の 80%  $\rightarrow 100mA/\mu s$

図 7-7. 負荷過渡

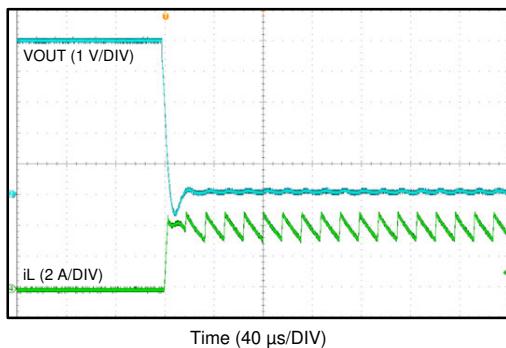

$V_{IN} = 12V$   $V_{OUT} = 5V$

図 7-8. 出力短絡

$V_{IN} = 12V$   $V_{OUT} = 5V$

図 7-9. 出力短絡リカバリ

## 7.3 電源に関する推奨事項

LV14340 は、4V～40V の入力電源電圧範囲で動作するよう設計されています。この入力電源は、最大入力電流を許容し、安定した電圧を保持できる必要があります。入力電源レールの抵抗は、入力過渡電流によって LV14340 の電源電圧が大きく降下し、UVLO の誤作動やシステム・リセットが生じることのないように、十分小さくする必要があります。入力電源が LV14340 から数インチ以上離れている場合は、セラミック入力コンデンサに加えて追加のバルク容量が必要になることがあります。バルク容量の大きさは重要ではありませんが、標準では  $47\mu F$  または  $100\mu F$  の電解コンデンサを選択します。

## 7.4 レイアウト

### 7.4.1 レイアウトのガイドライン

レイアウトは、優れた電源設計のために重要な要素です。以下のガイドラインに従うことで、最高の電力変換性能や熱性能を実現しながら、不要な EMI の生成を最小限に抑える PCB を設計できます。

- 帰還抵抗回路  $R_{FBT}$  および  $R_{FBB}$  は、FB ピンに近づけて配置する必要があります。 $V_{OUT}$  のセンス・パスは、ノイズの多いノードから遠ざけ、可能であれば、基板のシールド層の反対側の層を通します。

- 入力バイアス・コンデンサ  $C_{IN}$  は、 $VIN$  ピンおよびグランドの出来る限り近くに配置する必要があります。入力コンデンサと出力コンデンサのグランド接続はいずれも、GND ピンと PAD に接続される最短距離の最上面プレーンで構成される必要があります。

- インダクタ L は、磁気ノイズと静電気ノイズを低減するため、SW ピンの近くに配置する必要があります。

- 出力コンデンサ  $C_{OUT}$  は、L とダイオード D の接合部の近くに配置する必要があります。L, D,  $C_{OUT}$  のパターンは、伝導および放射ノイズを低減し、全体の効率を高めるためにできるだけ短くする必要があります。

- ダイオード、 $C_{IN}$ 、および  $C_{OUT}$  のグランド接続はできるだけ小さくし、システム・グランド・プレーンの 1箇所だけで接続することにより ( $C_{OUT}$  グランド・ポイントを推奨)、システム・グランド・プレーンでの伝導ノイズを最小限に抑えます。

スイッチング電源のレイアウトに関する考慮事項の詳細については、『AN-1149 スイッチング電源のレイアウトのガイドライン』アプリケーション・レポートを参照してください。

## 7.4.2 レイアウト例

図 7-10. レイアウト例

## 8 デバイスおよびドキュメントのサポート

### 8.1 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 8.2 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの[使用条件](#)を参照してください。

### 8.3 商標

PowerPAD™ and テキサス・インスツルメンツ E2E™ are trademarks of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 8.4 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

## 8.5 用語集

[テキサス・インスツルメンツ用語集](#) この用語集には、用語や略語の一覧および定義が記載されています。

## 9 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| <b>Changes from Revision B (July 2023) to Revision C (December 2024)</b>                                                                                                                                                                            | <b>Page</b> |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| • BOOT から SW への最大電圧定格を 6.5V から 5.5V に、FB から GND への最大電圧定格を 7V から 5.5V にそれぞれ変更.....                                                                                                                                                                   | 4           |

| • DDA パッケージの熱評価基準 $R_{\theta JA}$ を 42.5 から 43.2 に、 $\psi_{JT}$ を 9.9 から 5.2 に、 $\psi_{JB}$ を 25.4 から 16.4 に、 $R_{\theta JC(\text{top})}$ を 56.1 から 52.1 に、 $R_{\theta JC(\text{bot})}$ を 3.8 から 7.8 に、 $R_{\theta JB}$ を 25.5 から 16.4 にそれぞれ変更..... | 5           |

| • パラメータ $R_{DS\_ON}$ の「BOOT から SW = 5.8V」のテスト条件を削除.....                                                                                                                                                                                             | 5           |

| • パラメータ $T_{ON\_MIN}$ の「BOOT から SW = 5.8V」のテスト条件を削除.....                                                                                                                                                                                            | 6           |

| <b>Changes from Revision A (September 2018) to Revision B (July 2023)</b> | <b>Page</b> |

|---------------------------------------------------------------------------|-------------|

| • ドキュメント全体にわたって表、図、相互参照の採番方法を更新.....                                      | 1           |

| • LMR51440 および TLVM13640 へのリンクを追加.....                                    | 1           |

| • 最初の公開リリース.....                                                          | 1           |

| • 現行の標準に合わせて「パッケージ情報」表を更新 .....                                           | 1           |

| • 「ESD 定格」表を現在の規格に合わせて更新 .....                                            | 4           |

| • 「デバイスの機能モード」セクションを追加 .....                                              | 17          |

| • セクション 9.1 および 9.2 を追加.....                                              | 25          |

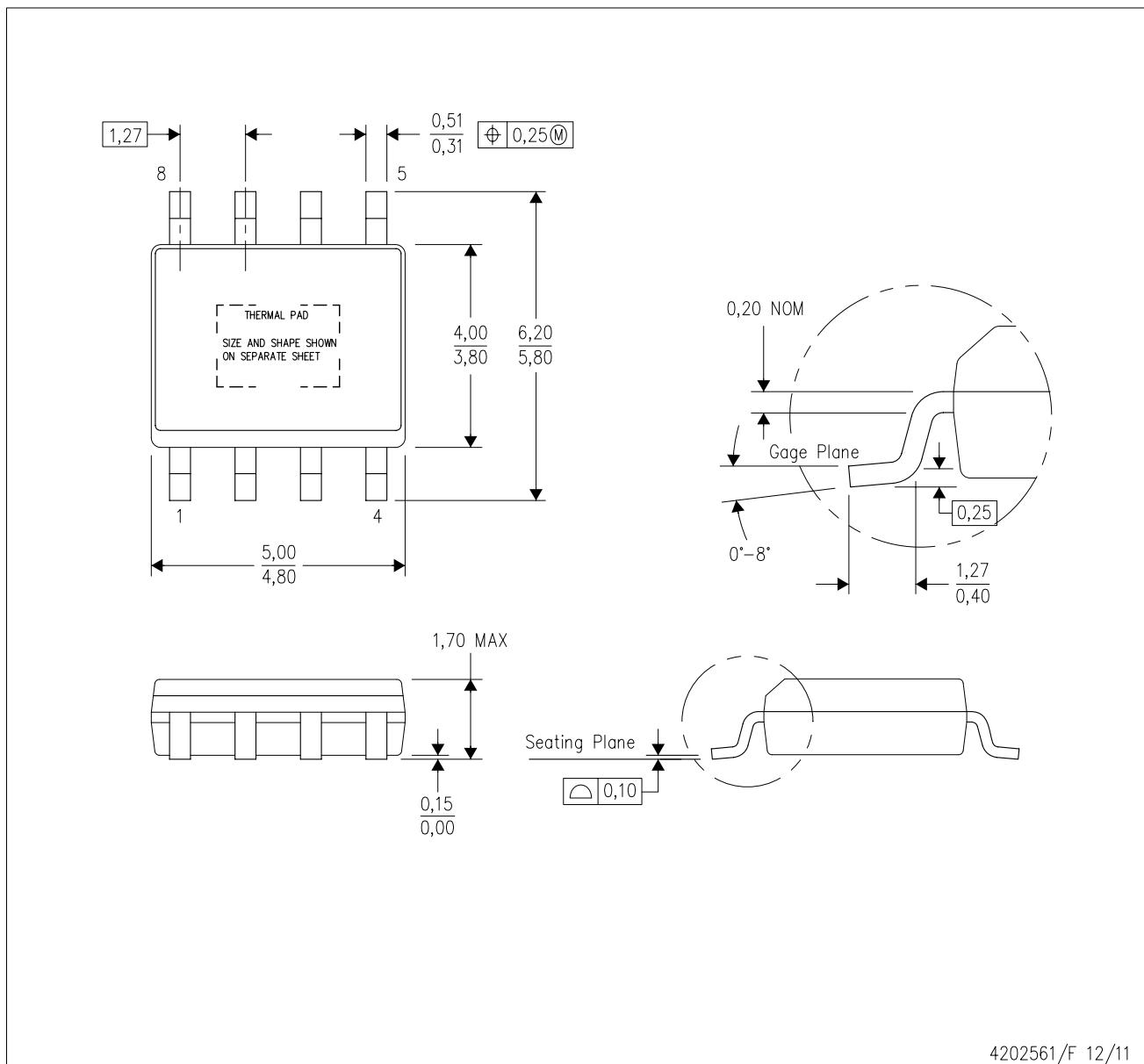

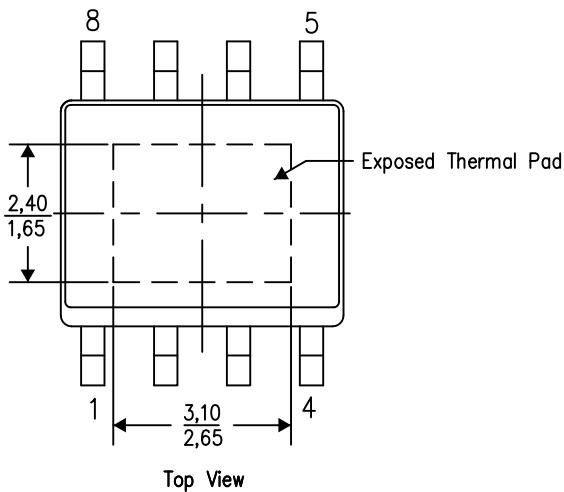

## 10 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに対して提供されている最新のデータです。このデータは予告なく変更されることがあり、本ドキュメントは改訂される場合もあります。本データシートのブラウザ版を使用している場合は、画面左側の説明をご覧ください。

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins           | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|--------------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| LV14340DDAR           | Active        | Production           | SO PowerPAD<br>(DDA)   8 | 2500   LARGE T&R      | Yes         | NIPDAU   NIPDAUAG                    | Level-2-260C-1 YEAR               | -40 to 125   | 14340               |

| LV14340DDAR.A         | Active        | Production           | SO PowerPAD<br>(DDA)   8 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | 14340               |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

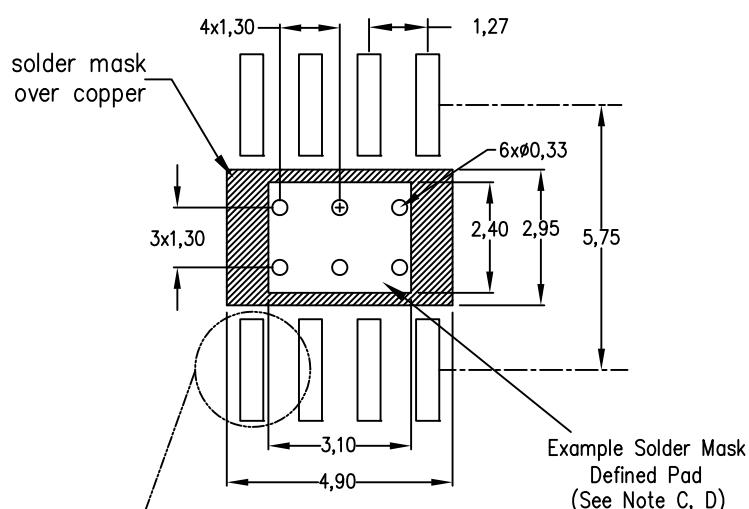

DDA (R-PDSO-G8)

PowerPAD™ PLASTIC SMALL-OUTLINE

4202561/F 12/11

- NOTES:

- A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5-1994.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion not to exceed 0,15.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at [www.ti.com](http://www.ti.com) <<http://www.ti.com>>.

- E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

- F. This package complies to JEDEC MS-012 variation BA

PowerPAD is a trademark of Texas Instruments.

DDA (R-PDSO-G8)

PowerPAD™ PLASTIC SMALL OUTLINE

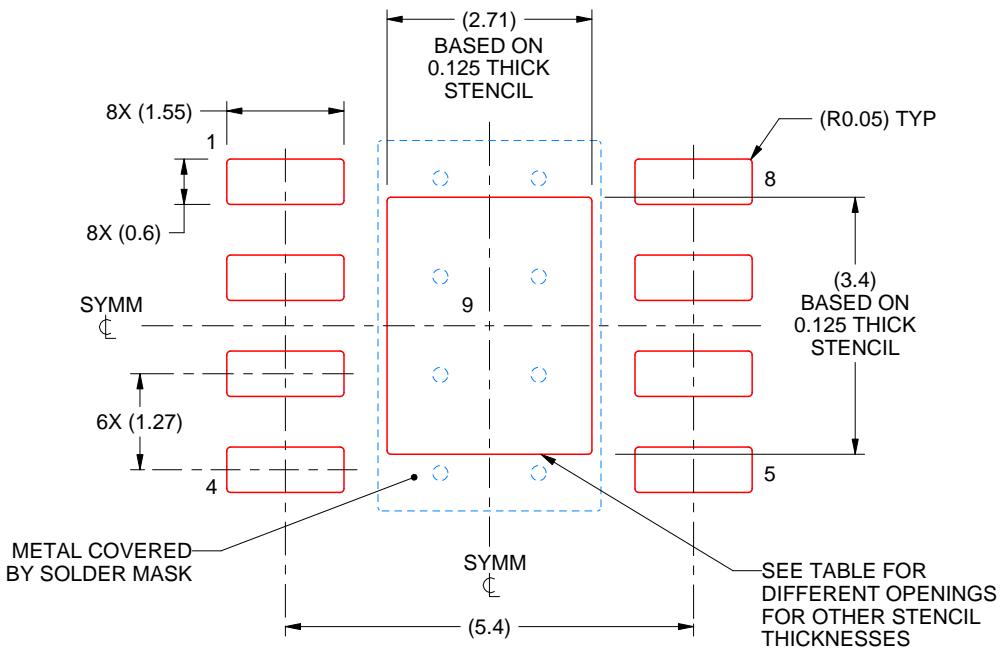

## THERMAL INFORMATION

This PowerPAD™ package incorporates an exposed thermal pad that is designed to be attached to a printed circuit board (PCB). The thermal pad must be soldered directly to the PCB. After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at [www.ti.com](http://www.ti.com).

The exposed thermal pad dimensions for this package are shown in the following illustration.

Exposed Thermal Pad Dimensions

4206322-6/L 05/12

NOTE: A. All linear dimensions are in millimeters

PowerPAD is a trademark of Texas Instruments

DDA (R-PDSO-G8)

PowerPAD™ PLASTIC SMALL OUTLINE

Example Board Layout

Via pattern and copper pad size

may vary depending on layout constraints

0,127mm Thick Stencil Design Example

Reference table below for other

solder stencil thicknesses

(Note E)

| Center Power Pad Solder Stencil Opening |     |     |

|-----------------------------------------|-----|-----|

| Stencil Thickness                       | X   | Y   |

| 0.1mm                                   | 3.3 | 2.6 |

| 0.127mm                                 | 3.1 | 2.4 |

| 0.152mm                                 | 2.9 | 2.2 |

| 0.178mm                                 | 2.8 | 2.1 |

4208951-6/D 04/12

- NOTES:

- All linear dimensions are in millimeters.

- This drawing is subject to change without notice.

- Publication IPC-7351 is recommended for alternate designs.

- This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002, SLMA004, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at [www.ti.com](http://www.ti.com) <<http://www.ti.com>>. Publication IPC-7351 is recommended for alternate designs.

- Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Example stencil design based on a 50% volumetric metal load solder paste. Refer to IPC-7525 for other stencil recommendations.

- Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

PowerPAD is a trademark of Texas Instruments.

DDA0008B

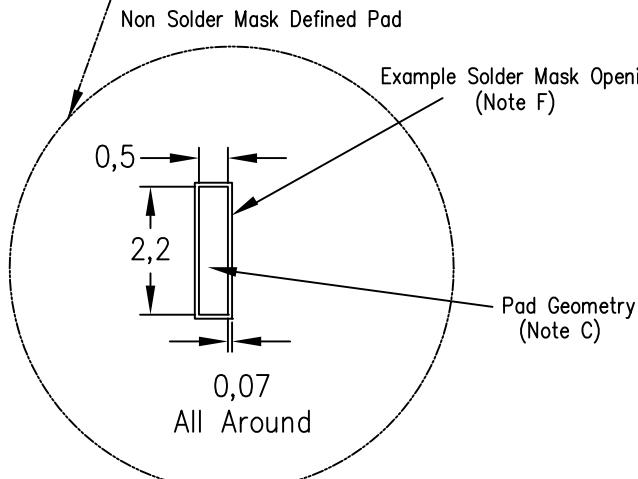

# PACKAGE OUTLINE

PowerPAD™ SOIC - 1.7 mm max height

PLASTIC SMALL OUTLINE

4214849/B 09/2025

NOTES:

PowerPAD is a trademark of Texas Instruments.

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

5. Reference JEDEC registration MS-012.

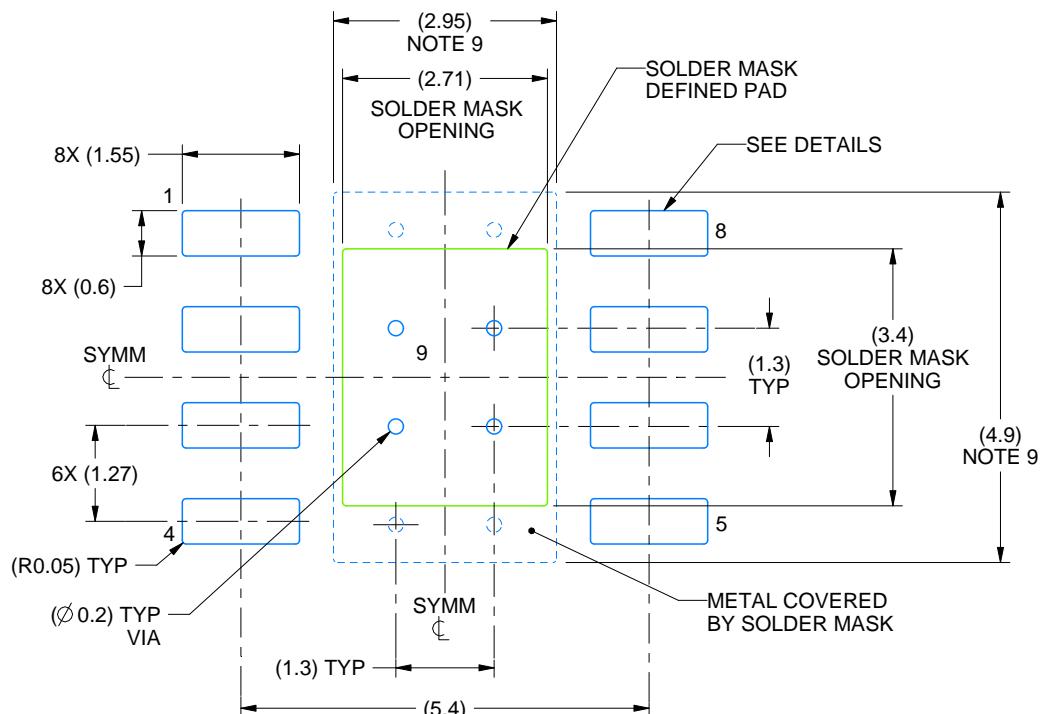

## EXAMPLE BOARD LAYOUT

**DDA0008B**

## PowerPAD™ SOIC - 1.7 mm max height

## PLASTIC SMALL OUTLINE

## LAND PATTERN EXAMPLE

4214840/B 09/2025

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

8. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature numbers SLMA002 ([www.ti.com/lit/slma002](http://www.ti.com/lit/slma002)) and SLMA004 ([www.ti.com/lit/slma004](http://www.ti.com/lit/slma004)).

9. Size of metal pad may vary due to creepage requirement.

10. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

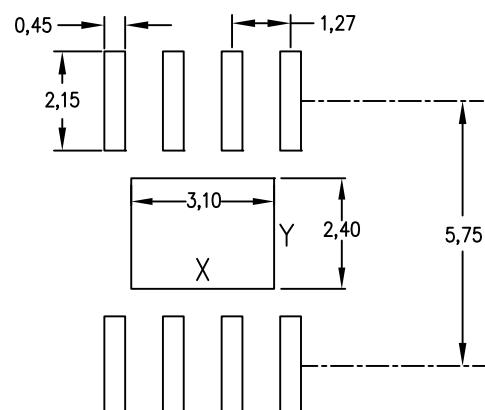

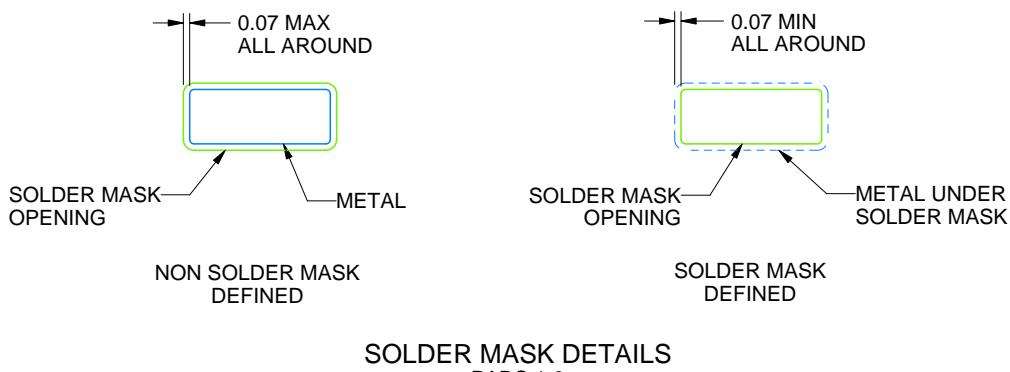

# EXAMPLE STENCIL DESIGN

DDA0008B

PowerPAD™ SOIC - 1.7 mm max height

PLASTIC SMALL OUTLINE

SOLDER PASTE EXAMPLE

EXPOSED PAD

100% PRINTED SOLDER COVERAGE BY AREA

SCALE:10X

| STENCIL THICKNESS | SOLDER STENCIL OPENING |

|-------------------|------------------------|

| 0.1               | 3.03 X 3.80            |

| 0.125             | 2.71 X 3.40 (SHOWN)    |

| 0.150             | 2.47 X 3.10            |

| 0.175             | 2.29 X 2.87            |

4214849/B 09/2025

NOTES: (continued)

11. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

12. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月