**TPA3223** JAJSO54 - NOVEMBER 2022

## TPA3223 200W ステレオ、400W モノラル HD アナログ入力、Class-D アンプ

## 1 特長

- 10V~42V の広い電源電圧範囲

- ステレオ (2 x BTL) およびモノラル (1 x PBTL) 構成

- 10% THD+N での出力電力

- BTL 構成で 4Ω ~ 200W (ステレオ)

- PBTL 構成で 3Ω ~ 300W (モノラル)

- PBTL 構成で 2Ω ~ 425W (モノラル)

- 1% THD+N での出力電力

- BTL 構成で 4Ω ~ 170W (ステレオ)

- PBTL 構成で 2Ω ~ 325W (モノラル)

- 閉ループ帰環設計

- THD+N: 4Ω ~ 1W で 0.02% 未満

- PSRR 60dB (BTL、入力信号なし)

- 出力ノイズ 100µV 未満 (A ウェイト)

- SNR 110dB 超 (A ウェイト)

- 低消費電力動作モード

- スタンバイ・モード:ミュートおよびシャットダウン

- シングル・チャネル BTL 動作

- 複数の入力オプションによりプリアンプ設計を簡素化

- 差動またはシングルエンド・アナログ入力

- 選択可能なゲイン: 20dB、23.5dB、32dB、36dB

- 保護機能を内蔵:低電圧、過電圧、過電流、サイクル 単位の電流制限、短絡、クリッピング検出、過熱警告 およびシャットダウン、DC スピーカー保護

- 複数のデバイスを簡単に同期可能

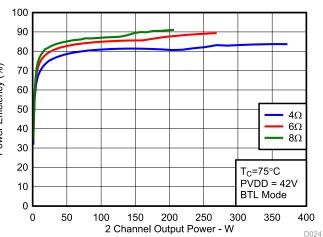

- 効率 90% の Class-D 動作 (4Ω)

## 2 アプリケーション

- Bluetooth および Wi-Fi™ スピーカー

- サウンドバー

- サブウーファー

- プロ用および放送設備 (PA) 用スピーカー

## 3 概要

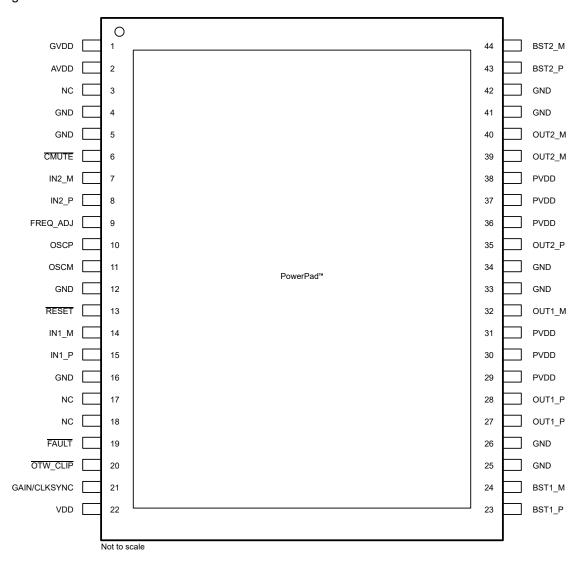

TPA3223 はフルパワー、アイドル、およびスタンバイ状態 での効率的な動作を実現するハイパワー Class-D アンプ です。閉ループ帰還を特長としているため、音声帯域全 体の歪みが小さく、優れたサウンドを提供します。このデバ イスは AD 変調で動作し、 $4\Omega$  の負荷に最大  $2 \times 200W$ 、 2Ω の負荷に最大 1 x 400W の出力を駆動できます。

TPA3223 は、最大 2V<sub>RMS</sub> をサポートするシングルエンド または差動アナログ入力インターフェイスを備えており、4 つのゲインを選択できます。20dB、23.5dB、32dB、 36dB.また、TPA3223 は 90% を上回る高効率を達成し ており、アイドル時の消費電力が低いだけでなく、スタンバ イ時の消費電力も極めて低くなっています (0.1W 未満)。 これは、 $60m\Omega$  の MOSFET、最適化されたゲート・ドライ ブ方式、および低消費電力の動作モードを採用すること で可能となりました。設計をさらに簡素化するため、低電 圧、過電圧、サイクル単位の電流制限、短絡、クリッピング 検出、過熱警告およびシャットダウン、DCスピーカー保護 といった必須の保護機能も統合されています。

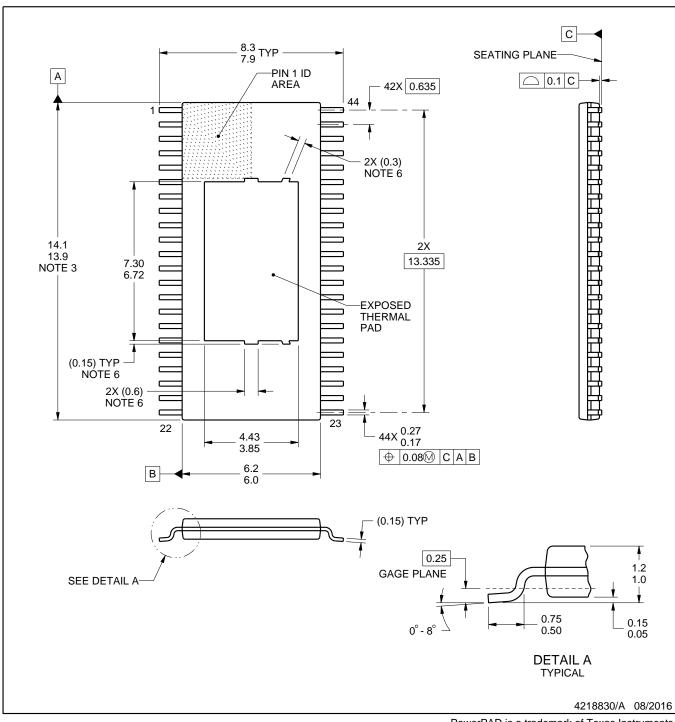

## 製品情報(1)

| 部品番号    | パッケージ       | 本体サイズ (公称)     |

|---------|-------------|----------------|

| TPA3223 | HTSSOP (44) | 6.10mm×14.00mm |

利用可能なパッケージについては、このデータシートの末尾にあ る注文情報を参照してください。

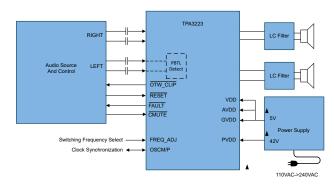

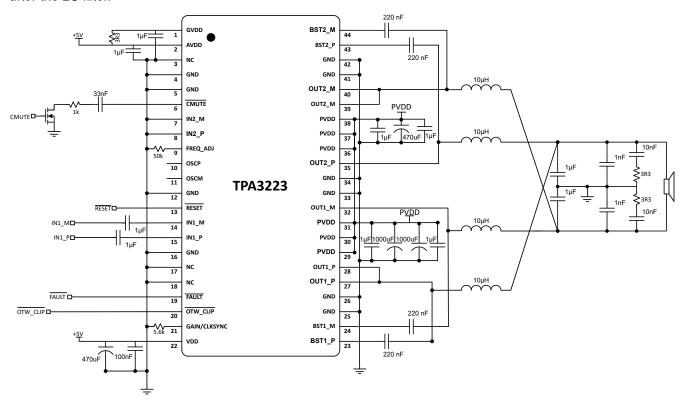

概略回路図

## **Table of Contents**

| 1 特長 1                                               | 9 Detailed Description1                                |    |

|------------------------------------------------------|--------------------------------------------------------|----|

| <b>2</b> アプリケーション1                                   | 9.1 Overview1                                          |    |

| 3 概要                                                 | 9.2 Functional Block Diagrams1                         | 8  |

| 4 Revision History                                   | 9.3 Feature Description2                               | (  |

| 5 Device Comparison                                  | 9.4 Device Functional Modes2                           | 2  |

| 6 Pin Configuration and Functions4                   | 10 Application and Implementation3                     | (  |

| 6.1 Pin Functions5                                   | 10.1 Application Information3                          | (  |

| 7 Specifications 6                                   | 10.2 Typical Applications3                             | (  |

| 7.1 絶対最大定格6                                          | 10.3 Power Supply Recommendations3                     | į  |

| 7.2 ESD 定格                                           | 10.4 Layout3                                           | į  |

|                                                      | 11 Device and Documentation Support3                   | i  |

| 7.3 推奨動作条件                                           | 11.1 Documentation Support3                            | į  |

| 7.4 熱に関する情報7                                         | 11.2 Receiving Notification of Documentation Updates 3 | 8  |

| 7.5 電気的特性8                                           | 11.3 サポート・リソース3                                        | 58 |

| 7.6 オーディオ特性 (BTL)10                                  | 11.4 Trademarks3                                       | 18 |

| 7.7 オーディオ特性 (PBTL)10                                 | 11.5 Electrostatic Discharge Caution3                  | 18 |

| 7.8 Typical Characteristics, BTL Configuration, AD-  | 11.6 Glossary3                                         |    |

| mode11                                               | 12 Mechanical, Packaging, and Orderable                |    |

| 7.9 Typical Characteristics, PBTL Configuration, AD- | Information                                            | 18 |

| mode14                                               |                                                        |    |

| 8 Parameter Measurement Information16                |                                                        |    |

|                                                      |                                                        |    |

## **4 Revision History**

| DATE          | REVISION | NOTES           |

|---------------|----------|-----------------|

| November 2022 | *        | Initial release |

# **5 Device Comparison**

## 表 5-1. Device Comparison Table

| DEVICE NAME | DESCRIPTION                                                                | SUPPLY<br>VOLTAGE | THERMAL PAD LOCATION |

|-------------|----------------------------------------------------------------------------|-------------------|----------------------|

| TPA3220     | 60-W Stereo, 110-W Peak HD Analog-Input, Pad-Down Class-D Amplifier        | 32 V              | Bottom               |

| TPA3221     | 100 W Stereo, 200 W Mono HD, Analog-Input, Class-D Amplifier               | 32 V              | Тор                  |

| TPA3244     | 60-W Stereo, 110-W peak PurePath™ Ultra-HD Pad Down Class-D Amplifier      | 31.5 V            | Bottom               |

| TPA3245     | 115-W Stereo, 230-W Mono PurePath™ Ultra-HD Analog-Input Class-D Amplifier | 31.5 V            | Тор                  |

| TPA3250     | 70 W Stereo, 130 W Peak Ultra-HD, Analog-Input, Pad-Down Class-D Amplifier | 38 V              | Bottom               |

| TPA3251     | 175 W Stereo, 350 W Mono Ultra-HD, Analog-Input Class-D Amplifier          | 38 V              | Тор                  |

| TPA3255     | 315 W Stereo, 600 W Mono Ultra-HD, Analog-Input Class-D Amplifier          | 53.5 V            | Тор                  |

## 6 Pin Configuration and Functions

The TPA3223 is available in a thermally enhanced TSSOP package.

The package type contains a thermal pad that is located on the top side of the device for convenient thermal coupling to the heat sink.

図 6-1. DDV Package, HTSSOP 44-Pin, Top View

Submit Document Feedback

## **6.1 Pin Functions**

#### 表 6-1. Pin Functions Table

| NAME         | NO.                                 | I/O <sup>(1)</sup> | DESCRIPTION                                                                                            |

|--------------|-------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------|

| AVDD         | 2                                   | Р                  | AVDD voltage supply. Refer to: セクション 10.3.1.2                                                          |

| BST1_M       | 24                                  | Р                  | OUT1_M HS bootstrap supply (BST), 0.033 µF capacitor to OUT1_M required.<br>Refer to: セクション 10.2.1.2.3 |

| BST1_P       | 23                                  | Р                  | OUT1_P HS bootstrap supply (BST), 0.033 µF capacitor to OUT1_P required.<br>Refer to: セクション 10.2.1.2.3 |

| BST2_M       | 44                                  | Р                  | OUT2_M HS bootstrap supply (BST), 0.033 µF capacitor to OUT2_M required.<br>Refer to: セクション 10.2.1.2.3 |

| BST2_P       | 43                                  | Р                  | OUT2_P HS bootstrap supply (BST), 0.033 μF capacitor to OUT2_P required.<br>Refer to: セクション 10.2.1.2.3 |

| CMUTE        | 6                                   | Р                  | Mute and Startup Timing Capacitor. Connect a 33 nF capacitor to GND. Refer to: セクション 9.4.3             |

| FAULT        | 19                                  | 0                  | Shutdown signal, open drain; active low. Refer to: セクション 9.3.6                                         |

| FREQ_ADJ     | 9                                   | 0                  | Oscillator frequency programming pin. Refer to: セクション 9.3.4                                            |

| GAIN/CLKSYNC | 21                                  | I                  | Closed loop gain and clock synchronization configuration pin. Refer to: セクション 9.3.1                    |

| GND          | 4,5,12,16,25,<br>26,42,33,34,<br>41 | Р                  | Ground                                                                                                 |

| GVDD         | 1                                   | Р                  | Gate drive supply. Refer to: セクション 10.3.1.2                                                            |

| IN1_M        | 14                                  | I                  | Negative audio input for channel 1                                                                     |

| IN1_P        | 15                                  | 1                  | Positive audio input for channel 1                                                                     |

| IN2_M        | 7                                   | 1                  | Negative audio input for channel 2                                                                     |

| IN2_P        | 8                                   | 1                  | Positive audio input for channel 2                                                                     |

| NC           | 3,17,18                             |                    | Not connected or pulled to ground                                                                      |

| OSCM         | 11                                  | I/O                | Oscillator synchronization interface.<br>Refer to: セクション 9.3.1                                         |

| OSCP         | 10                                  | I/O                | Oscillator synchronization interface.<br>Refer to: セクション 9.3.1                                         |

| OTW_CLIP     | 20                                  | 0                  | Clipping warning and Over-temperature warning; open drain; active low.<br>Refer to: セクション 9.3.6        |

| OUT1_M       | 32                                  | 0                  | Negative output for channel 1                                                                          |

| OUT1_P       | 27,28                               | 0                  | Positive output for channel 1                                                                          |

| OUT2_M       | 39,40                               | 0                  | Negative output for channel 2                                                                          |

| OUT2_P       | 35                                  | 0                  | Positive output for channel 2                                                                          |

| PVDD         | 29,30,31,36,<br>37,38               | Р                  | PVDD supply. Refer to: セクション 10.2.1.2.2 and セクション 10.3.1.3                                             |

| RESET        | 13                                  | I                  | Device reset input; active low. Refer to: セクション 9.4.5.7, セクション 9.4.1, セクション 9.4.2                      |

| VDD          | 22                                  | Р                  | Input power supply. Refer to: セクション 10.3.1.1                                                           |

| PowerPad™    |                                     | Р                  | Ground, connect to grounded heatsink. Placed on top side of device.                                    |

## (1) I=Input, O=Output, I/O= Input/Output, P=Power

## 表 6-2. Mode Selection Pins

| МС          | DDE PINS <sup>(2)</sup> | INPUT MODE(1) | OUTPUT        | DESCRIPTION                                                                                           |  |  |

|-------------|-------------------------|---------------|---------------|-------------------------------------------------------------------------------------------------------|--|--|

| IN2_M IN2_P |                         | INFOT MODE    | CONFIGURATION | DESCRIPTION                                                                                           |  |  |

| X           | X X 1N/2N + 1           |               | 2 × BTL       | Stereo, BTL output configuration, AD mode modulation                                                  |  |  |

| 0           | 0                       | 1N/2N + 1     | 1 x PBTL      | Mono, Paralleled BTL configuration. Connect OUT1_P to OUT2_P and OUT1_M to OUT2_M, AD mode modulation |  |  |

| 1 1         |                         | 1N/2N + 1     | 1 x BTL       | Mono, BTL configuration. OUT1_M and OUT1_P active, AD mode modulation                                 |  |  |

- (1) 2N refers to differential input signal, 1N refers to single ended input signal. +1 refers to number of logic control (RESET) input pins.

- (2) X refers to inputs connected through AC coupling capacitor, 0 refers to logic low (GND), 1 refers to logic high (AVDD).

## 7 Specifications

## 7.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り)(1)

|                  | ·                                                               | 最小値  | 最大值                                                          | 単位 |

|------------------|-----------------------------------------------------------------|------|--------------------------------------------------------------|----|

|                  | PVDD から GND                                                     | -0.3 | 50                                                           | V  |

|                  | PVDD から GND (過渡現象 8ns 未満) <sup>(2)</sup>                        | -0.3 | 57                                                           | V  |

| and the second   | BST_X から GVDD                                                   | -0.3 | 50                                                           | V  |

| 電源電圧             | VDD から GND                                                      | -0.3 | 50                                                           | V  |

|                  | GVDD カンら GND <sup>(2)</sup>                                     | -0.3 | 5.5                                                          | V  |

|                  | AVDD から GND                                                     | -0.3 | 5.5                                                          | V  |

| 111-62-22        | OUT1_M、OUT1_P、OUT2_M、OUT2_P から GND                              | -0.3 | 50                                                           | V  |

| 出力ピン             | OUT1_M、OUT1_P、OUT2_M、OUT2_P から GND (過渡現象 8ns 未満) <sup>(2)</sup> | -0.3 | 50<br>50<br>5.5<br>5.5<br>50<br>57<br>5.5<br>5.5<br>5.5<br>9 | V  |

|                  | IN1_M、IN1_P、IN2_M、IN2_P から GND                                  | -0.3 | 5.5                                                          | V  |

| インターフェイス ピン      | FREQ_ADJ、GAIN/CLKSYNC、CMUTE, RESET、OSCP、OSCM から GND             | -0.3 | 5.5                                                          | V  |

| 1/9-/E1/E2       | FAULT, OTW_CLIP から GND                                          | -0.3 | 5.5                                                          | V  |

|                  | 連続シンク電流、FAULT、OTW_CLIP から GND                                   |      | 9                                                            | mA |

| T <sub>J</sub>   | 動作ジャンクション温度範囲                                                   | 0    | 150                                                          | °C |

| T <sub>stg</sub> | 保管温度範囲                                                          | -40  | 150                                                          | °C |

<sup>(1)</sup> 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を越える状態で本製品が正常に動作することを暗黙的に示すものではありません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

## 7.2 ESD 定格

|                  |       |                                                             | 値     | 単位 |

|------------------|-------|-------------------------------------------------------------|-------|----|

|                  |       | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠、すべてのピン <sup>(1)</sup> | ±3000 | V  |

| V <sub>ESD</sub> | 静電気放電 | デバイス帯電モデル (CDM)、JEDEC 規格 JESD22-C101 準拠、すべてのピン(2)           | ±1500 | V  |

- (1) JEDEC のドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスで安全な製造が可能であると記載されています。

- (2) JEDEC のドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスで安全な製造が可能であると記載されています。

Submit Document Feedback

<sup>(2)</sup> これらの電圧は、あらゆる条件下においてデバイスの端子で測定された DC 電圧 + ピーク AC 波形を表します。

## 7.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                         |                                        |                                                 | 最小值                                 | 代表值 | 最大値  | 単位  |

|-------------------------|----------------------------------------|-------------------------------------------------|-------------------------------------|-----|------|-----|

| PVDD                    | 電力段電源                                  | DC 電源電圧                                         | 10                                  | 42  | 45   | V   |

| VDD <sup>(1)</sup>      | VDD、GVDD、AVDD 用の外部電源                   | DC 電源電圧                                         | 4.5                                 | 5   | 5.5  | V   |

| AVDD                    | アナログ回路の電源電圧                            | DC 電源電圧                                         | 4.5                                 | 5   | 5.5  | V   |

| GVDD                    | ゲート・ドライブ回路の電源電圧                        | DC 電源電圧                                         | 4.5                                 | 5   | 5.5  | V   |

| V <sub>IN</sub>         | 入力電圧の最大振幅 (INx_P、INx_M)                |                                                 |                                     |     | ±2.8 | V   |

| R <sub>L</sub> (BTL)    |                                        | PVDD = 42V、出力フィルタのインダクタンスは推奨<br>範囲内             | 3.5                                 | 4   |      |     |

|                         | 負荷インピーダンス BTL                          | PVDD = 42V 未満、出力フィルタのインダクタンスは推奨範囲内              | PVDD/<br>(I <sub>OC</sub> ,<br>BTL) |     |      | Ω   |

| R <sub>L</sub> (PBTL)   | 負荷インピーダンス PBTL                         | PVDD = 42V、出力フィルタのインダクタンスは推奨<br>範囲内             | 1.6                                 | 3   |      | Ω   |

| L <sub>OUT</sub> (BTL)  | 出力フィルタのインダクタンス                         | Ioc での最小出力インダクタンス                               | 5                                   | 10  |      | μH  |

| L <sub>OUT</sub> (PBTL) | 出力フィルタのインダクタンス、LC フィルタの後の<br>PBTL      | 1/2 I <sub>OC</sub> での各インダクタにおける最小出力インダク<br>タンス | 5                                   | 10  |      | μΗ  |

| L <sub>OUT</sub> (PBTL) |                                        | 公称                                              | 460                                 | 480 | 500  |     |

|                         | AM 干渉回避用に PWM フレーム・レートを選択可能、抵抗の許容誤差 1% | AM1                                             | 510                                 | 533 | 555  | kHz |

|                         | BEN SENTEN HINE BAZE 170               | AM2                                             | 575                                 | 600 | 625  |     |

| f <sub>OSC(IO)</sub>    | OSCM/OSCP の CLK 入力 (ペリフェラル・モード)        |                                                 | 2.3                                 |     | 3.78 | MHz |

|                         |                                        | 公称、1 次モード                                       | 9.9                                 | 10  | 10.1 |     |

| $R_{(FREQ\_ADJ)}$       | PWM フレーム・レート・プログラミング抵抗                 | AM1、1 次モード                                      | 29.7                                | 30  | 30.3 | kΩ  |

|                         |                                        | AM2、1 次モード                                      | 49.5                                | 50  | 50.5 |     |

| C <sub>PVDD</sub>       | PVDD 近接デカップリング・コンデンサ                   |                                                 |                                     | 1.0 |      | μF  |

| V <sub>(FREQ_ADJ)</sub> | ペリフェラル・モード動作用の FREQ_ADJ ピンの<br>電圧      | ペリフェラル・モード (AVDD に接続)                           |                                     | 5   |      | V   |

| T <sub>J</sub>          | 接合部温度                                  |                                                 | 0                                   |     | 125  | °C  |

<sup>(1)</sup> VDD は 5V の電源に接続する必要があります。

## 7.4 熱に関する情報

|                       |                             | TPA3223          |      |

|-----------------------|-----------------------------|------------------|------|

|                       | <b>熱評価基準</b> <sup>(1)</sup> | DDV 44 ピン HTSSOP | 単位   |

|                       |                             | JEDEC 規格 4 層 PCB |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗                | 42.6             | °C/W |

| R <sub>0JC(top)</sub> | 接合部からケース (上面) への熱抵抗         | 0.9              | °C/W |

| $R_{\theta JB}$       | 接合部から基板への熱抵抗                | 13.8             | °C/W |

| ΨЈТ                   | 接合部から上面への熱特性パラメータ           | 0.4              | °C/W |

| ΨЈВ                   | 接合部から基板への熱特性パラメータ           | 13.5             | °C/W |

| $R_{\theta JC(bot)}$  | 接合部からケース (底面) への熱抵抗         | n/a              | °C/W |

<sup>(1)</sup> 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション・レポートを参照してください。

## 7.5 電気的特性

PVDD = 42V、VDD = 5V、GVDD = 5V、AVDD = 5V、T<sub>C</sub> (ケース温度) = 75℃、f<sub>S</sub> = 480kHz (特に記述のない限り)

|                             | パラメータ                                                             | テスト条件                                                | 最小<br>値 | 代表值   | 最大値  | 単位  |

|-----------------------------|-------------------------------------------------------------------|------------------------------------------------------|---------|-------|------|-----|

| 電源電圧および電                    | 流消費                                                               |                                                      |         |       |      |     |

| I <sub>VDD</sub>            |                                                                   | 動作、オーディオ信号なし、VDD = 5V                                |         | 150   |      | μA  |

| I <sub>VDD</sub>            | VDD 電源電流                                                          | リセット・モード、VDD = 5V                                    |         | 5     |      | μA  |

| I <sub>GVDD</sub>           |                                                                   | 50% デューティ・サイクル、VDD = 5V                              |         | 23    |      | mA  |

| I <sub>GVDD</sub>           | ゲート電源電流。AD モード変調                                                  | リセット・モード、VDD = 5V                                    |         | 5     |      | μA  |

| I <sub>PVDD</sub>           | 合計 PVDD アイドル電流、AD モード変調、<br>BTL                                   | 推奨出力フィルタを使用してデューティ・サイクル 50%                          |         | 45    |      | mA  |

| I <sub>PVDD</sub>           | 合計 PVDD アイドル電流、AD モード変調、<br>BTL                                   | 推奨出力フィルタを使用してデューティ・サイクル<br>50%、T <sub>C</sub> = 25°C |         | 35    |      | mA  |

| I <sub>PVDD</sub>           | 合計 PVDD アイドル電流、AD モード変調、<br>BTL                                   | リセット・モード、スイッチングなし                                    |         | 1     |      | mA  |

| アナログ入力                      |                                                                   |                                                      |         |       | ,    |     |

|                             |                                                                   | R <sub>1</sub> = 5.6kΩ、R <sub>2</sub> = オープン         |         | 20    |      |     |

|                             | 反転電圧ゲイン、V <sub>OUT</sub> /V <sub>IN</sub> (1 次クロック同期デ             | $R_1 = 20k\Omega$ , $R_2 = 100k\Omega$               |         | 23.5  |      |     |

|                             | バイス構成)                                                            | $R_1 = 39k\Omega$ , $R_2 = 100k\Omega$               |         | 32    |      |     |

| •                           |                                                                   | $R_1 = 47k\Omega$ , $R_2 = 75k\Omega$                |         | 36    |      |     |

| G                           |                                                                   | $R_1 = 51k\Omega$ , $R_2 = 51k\Omega$                |         | 20    |      | dB  |

|                             | 反転電圧ゲイン、V <sub>OUT</sub> /V <sub>IN</sub> (ペリフェラル・クロッ             | $R_1 = 75k\Omega$ , $R_2 = 47k\Omega$                | 23.5    |       |      |     |

|                             | ク同期デバイス構成)                                                        | $R_1 = 100k\Omega$ , $R_2 = 39k\Omega$               |         |       |      |     |

|                             |                                                                   | $R_1 = 100k\Omega, R_2 = 16k\Omega$                  |         | 36    |      |     |

|                             |                                                                   | G = 20dB                                             | 48      |       |      |     |

|                             |                                                                   | G = 23.5dB                                           | 24      |       |      | †   |

| R <sub>IN</sub>             | 入力抵抗                                                              | G = 32dB                                             |         | 12    |      | kΩ  |

|                             |                                                                   | G = 36dB                                             |         | 7.3   |      |     |

| 発振器                         |                                                                   |                                                      |         |       |      |     |

|                             | 公称、1 次モード                                                         |                                                      | 2.76    | 2.88  | 3    |     |

| f <sub>OSC(IO)</sub> (1)    | AM1、1 次モード                                                        | F <sub>PWM</sub> × 6                                 | 3.06    | 3.198 | 3.33 | MHz |

|                             | AM2、1 次モード                                                        |                                                      | 3.45    | 3.6   | 3.75 |     |

| V <sub>IH</sub>             | High レベル入力電圧                                                      |                                                      | 2.7     |       |      | V   |

| V <sub>IL</sub>             | Low レベル入力電圧                                                       |                                                      |         |       | 0.7  | V   |

|                             | <br>フェラル・モード)                                                     |                                                      |         |       |      |     |

| 出力段 MOSFET                  |                                                                   |                                                      |         |       |      |     |

|                             | ドレイン-ソース間抵抗、ローサイド (LS)                                            | T <sub>J</sub> = 25℃、金属皮膜抵抗を除く、                      |         | 60    |      | mΩ  |

| R <sub>DS(on)</sub>         | ドレイン-ソース間抵抗、ハイサイド (HS)                                            | T <sub>J</sub> = 25 C、並属及膜私机を除く。<br>  GVDD = 5V      |         | 60    |      | mΩ  |

| I/O 保護                      | 1                                                                 | 1                                                    |         |       |      |     |

| V <sub>uvp,AVDD</sub>       | 低電圧保護制限、AVDD                                                      |                                                      |         | 4     |      | V   |

| V <sub>uvp,AVDD,hyst</sub>  | 低電圧保護ヒステリシス、AVDD                                                  |                                                      |         | 0.2   |      | V   |

| V <sub>uvp,PVDD</sub>       | 低電圧保護制限、PVDD_x                                                    |                                                      |         | 9.1   |      | V   |

| V <sub>uvp,PVDD,hyst</sub>  | 低電圧保護ヒステリシス、PVDD_x                                                |                                                      |         | 0.6   |      | V   |

| V <sub>ovp,PVDD</sub> ,nyst | 過電圧保護制限、PVDD_x                                                    |                                                      |         | 46    |      | V   |

| V <sub>ovp,PVDD,hyst</sub>  | 過電圧保護ヒステリシス、PVDD_x                                                |                                                      |         | 0.85  |      | V   |

| OTW                         | 過熱警告、OTW_CLIP                                                     |                                                      |         | 125   |      | ℃   |

| OTW <sub>hyst</sub>         | OTW イベント後に OTW_CLIP が非アクティブ<br>になるためには、温度が OTW 温度より低くなる<br>ことが必要。 |                                                      |         | 20    |      | ℃   |

| OTE                         | 過熱エラー                                                             |                                                      |         | 155   |      | °C  |

| OTE <sub>hyst</sub>         | OTE イベント後に FAULT を解放するにはリセットが必要                                   |                                                      |         | 20    |      | °C  |

# 7.5 電気的特性 (continued)

PVDD = 42V、VDD = 5V、GVDD = 5V、AVDD = 5V、T<sub>C</sub> (ケース温度) = 75℃、f<sub>S</sub> = 480kHz (特に記述のない限り)

|                                   | パラメータ                                    | テスト条件                                     | 最小<br>値 | 代表值 | 最大値 | 単位 |

|-----------------------------------|------------------------------------------|-------------------------------------------|---------|-----|-----|----|

| OTE-OTW <sub>(differential)</sub> | OTE-OTW の差分                              |                                           |         | 25  |     | °C |

| OLPC                              | 過負荷保護カウンタ                                | f <sub>PWM</sub> = 480kHz (1024 PWM サイクル) |         | 2.2 |     | ms |

| I <sub>OC, BTL</sub>              | 過電流制限保護、スピーカー負荷電流                        | 1Ω 負荷での公称ピーク電流                            |         | 10  |     | Α  |

| I <sub>OC, PBTL</sub>             | 過電流制限保護、スピーカー出力電流                        | 1Ω 負荷での公称ピーク電流                            |         | 20  |     | Α  |

| I <sub>OCT</sub>                  | 過電流応答時間                                  | スイッチング遷移から、過電流によって状態がフリップ<br>するまでの時間      |         | 150 |     | ns |

| 静的デジタル仕様                          |                                          |                                           |         |     | '   |    |

| V <sub>IH</sub>                   | High レベル入力電圧                             | - RESET に変更。                              | 2.3     |     |     | V  |

| V <sub>IL</sub>                   | Low レベル入力電圧                              | NESET 仁多文。                                |         |     | 0.7 | V  |

| I <sub>lkg</sub>                  | 入力リーク電流                                  | OSCM, OSCP, RESET                         |         |     | 100 | μA |

| OTW / シャットダウン (                   | FAULT)                                   |                                           |         |     |     |    |

| R <sub>INT_PU</sub>               | 内部プルアップ抵抗、OTW_CLIP から AVDD、FAULT から AVDD |                                           |         | 26  |     | kΩ |

| V <sub>OH</sub>                   | High レベル出力電圧                             | 内部プルアップ抵抗                                 | 4.5     | 5   | 5.5 | V  |

| V <sub>OL</sub>                   | Low レベル出力電圧                              | I <sub>O</sub> = 4mA                      |         | 200 | 500 | mV |

<sup>(1)</sup> 公称値、AM1 と AM2 は同じ内部発振器を使用、固定比率 4:4.5:5

## 7.6 オーディオ特性 (BTL)

PCB とシステムの構成は、推奨ガイドラインに従っています。オーディオ周波数 = 1kHz、PVDD\_X = 42V、VDD = 5V、GVDD = 5V、RL =  $4\Omega$ 、 $f_S$  = 480kHz、 $T_C$  =  $75^{\circ}$ C、出力フィルタ:  $L_{DEM}$  =  $10\mu$ H、 $C_{DEM}$  =  $1\mu$ F、AD 変調、AES17 + AUX-0025 測定フィルタ (特に記述のない限り)。

|                   | パラメータ                                     | テスト条件                                                 | 最小値代 | 表值   | <b>最</b> 大<br>値 | 単位 |

|-------------------|-------------------------------------------|-------------------------------------------------------|------|------|-----------------|----|

| Po                | チャネルごとの電源出力                               | R <sub>L</sub> = 4Ω、10% THD+N                         |      | 200  |                 | W  |

| Po                | チャネルごとの電源出力                               | R <sub>L</sub> = 4Ω、1% THD+N                          |      | 170  |                 | W  |

| THD+N             | 全高調波歪 + ノイズ                               | 1W                                                    |      | 0.02 |                 | %  |

| V <sub>n</sub>    | 出力積分ノイズ                                   | A ウェイト、AES17 フィルタ、入力コンデンサを接地、ゲイン = 20dB               |      | 100  |                 | μV |

| V <sub>OS</sub>   | 出力オフセット電圧                                 | 入力を GND に AC カップリング                                   |      | 5    | 20              | mV |

| SNR               | 信号対雑音比 <sup>(1)</sup>                     | A ウェイト、ゲイン = 20dB                                     |      | 108  |                 | dB |

| DNR               | ダイナミック・レンジ                                | A ウェイト、ゲイン = 20dB                                     |      | 109  |                 | dB |

| P <sub>idle</sub> | アイドル時の電力損失 (I <sub>PVDD_X</sub> ) による電力損失 | $P_O = 0$ 、全出力スイッチング、AD 変調、 $T_C = 25^{\circ}C^{(2)}$ |      | 1.5  |                 | W  |

- (1) SNR は、1% THD+N 出力レベルを基準として計算されています。

- (2) 実際のシステムでのアイドル時の電力損失は、出力インダクタのコア損失の影響も受けます。

## 7.7 オーディオ特性 (PBTL)

PCB とシステムの構成は、推奨ガイドラインに従っています。オーディオ周波数 = 1kHz、PVDD\_X = 42V、VDD = 5V、GVDD = 5V、R<sub>L</sub> = 3 $\Omega$ 、 $f_S$  = 480kHz、 $T_C$  = 75°C、出力フィルタ:  $L_{DEM}$  = 10 $\mu$ H、 $C_{DEM}$  = 1 $\mu$ F、ポスト・フィルタ PBTL、AD 変調、AES17 + AUX-0025 測定フィルタ (特に記述のない限り)。

|                   | パラメータ                        | テスト条件                                                 | 最小値 代表値 最大値 | 単位 |

|-------------------|------------------------------|-------------------------------------------------------|-------------|----|

|                   |                              | $R_L = 2\Omega$ , 10% THD+N                           | 425         | W  |

|                   |                              | R <sub>L</sub> = 3Ω、10% THD+N                         | 300         |    |

| Po                | チャネルごとの電源出力                  | $R_L = 4\Omega$ , 10% THD+N                           | 250         |    |

| F0                | フャイルことの电源田刀<br> <br>         | R <sub>L</sub> = 2Ω、1% THD+N                          | 325         | w  |

|                   |                              | R <sub>L</sub> = 3Ω、1% THD+N                          | 245         |    |

|                   |                              | R <sub>L</sub> = 4Ω、1% THD+N                          | 195         |    |

| THD+N             | 全高調波歪 + ノイズ                  | 1W                                                    | 0.017       | %  |

| V <sub>n</sub>    | 出力積分ノイズ                      | A ウェイト、AES17 フィルタ、入力コンデンサを接地、<br>ゲイン = 20dB           | 100         | μV |

| V <sub>OS</sub>   | 出力オフセット電圧                    | 入力を GND に AC カップリング                                   | 10          | mV |

| SNR               | 信号対雑音比(1)                    | A ウェイト、ゲイン = 20dB                                     | 109         | dB |

| DNR               | ダイナミック・レンジ                   | A ウェイト、ゲイン = 20dB                                     | 110         | dB |

| P <sub>idle</sub> | アイドル時の電力損失 (IPVDD_X) による電力損失 | $P_0 = 0$ 、全出力スイッチング、AD 変調、 $T_C = 25^{\circ}C^{(2)}$ | 1.5         | W  |

Product Folder Links: TPA3223

- (1) SNR は、1% THD+N 出力レベルを基準として計算されています。

- (2) 実際のシステムでのアイドル時の電力損失は、出力インダクタのコア損失の影響を受けます。

omit Document Feedback

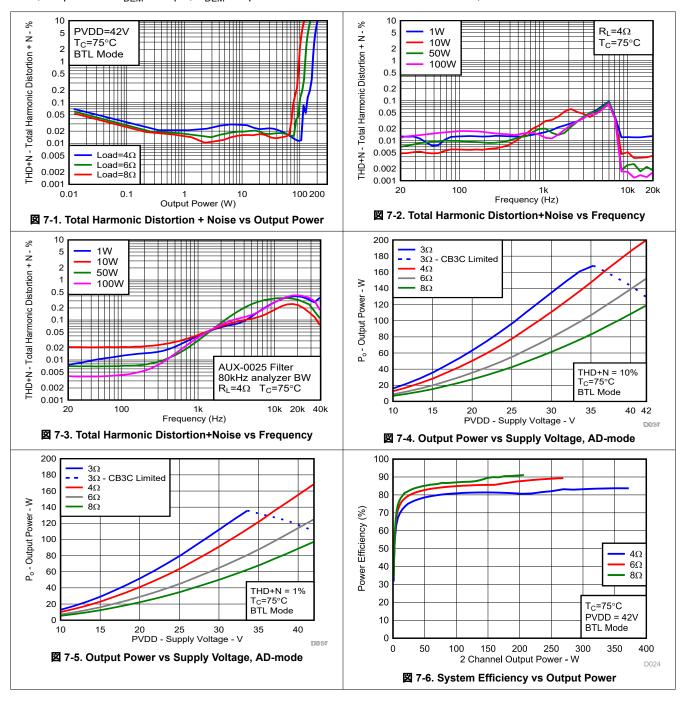

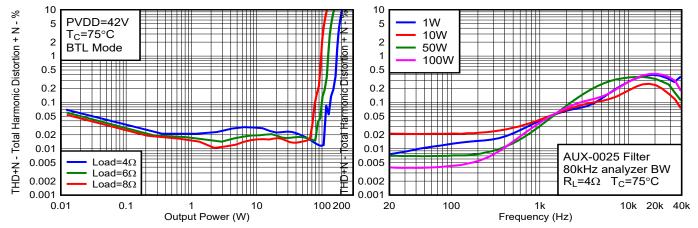

## 7.8 Typical Characteristics, BTL Configuration, AD-mode

All Measurements taken at audio frequency = 1 kHz, PVDD = 42 V, VDD = 5 V, GVDD = 5 V,  $R_L$  = 4  $\Omega$ ,  $f_S$  = 480 kHz,  $T_C$  = 75°C, Output Filter:  $L_{DEM}$  = 10  $\mu$ H,  $C_{DEM}$  = 1  $\mu$ FAES17 + AUX-0025 measurement filters, unless otherwise noted.

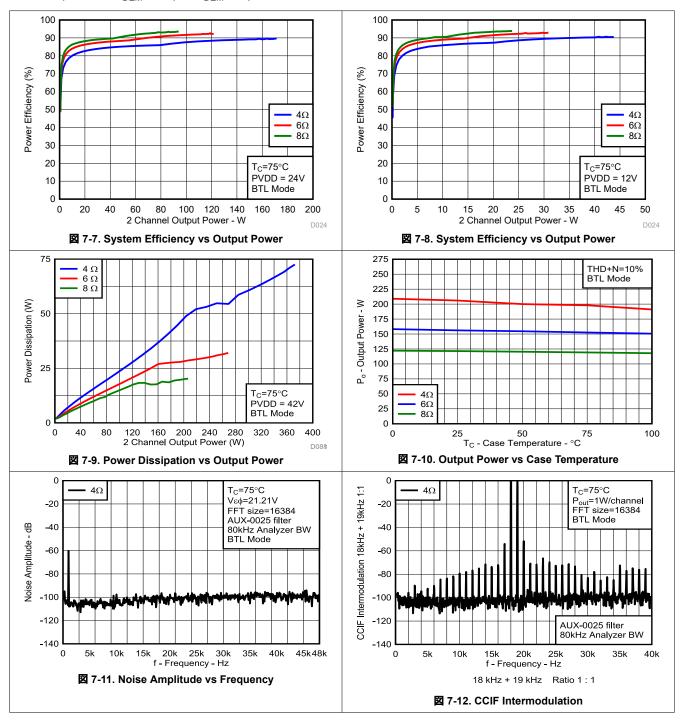

## 7.8 Typical Characteristics, BTL Configuration, AD-mode (continued)

All Measurements taken at audio frequency = 1 kHz, PVDD = 42 V, VDD = 5 V, GVDD = 5 V,  $R_L$  = 4  $\Omega$ ,  $f_S$  = 480 kHz,  $T_C$  = 75°C, Output Filter:  $L_{DEM}$  = 10  $\mu$ H,  $C_{DEM}$  = 1  $\mu$ FAES17 + AUX-0025 measurement filters, unless otherwise noted.

Submit Document Feedback

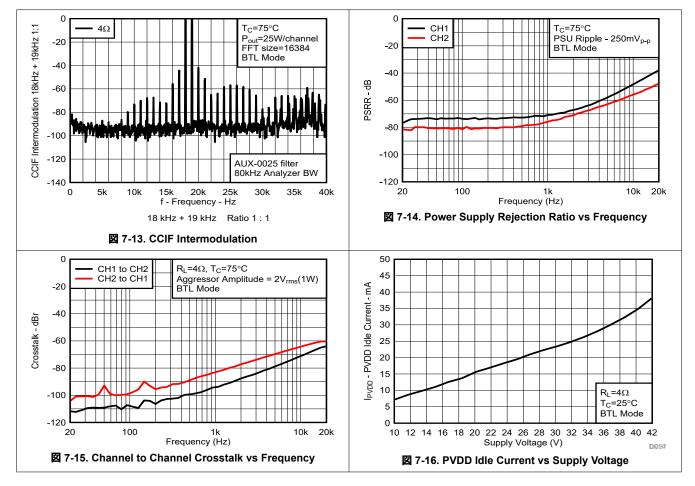

## 7.8 Typical Characteristics, BTL Configuration, AD-mode (continued)

All Measurements taken at audio frequency = 1 kHz, PVDD = 42 V, VDD = 5 V, GVDD = 5 V,  $R_L$  = 4  $\Omega$ ,  $f_S$  = 480 kHz,  $T_C$  = 75°C, Output Filter:  $L_{DEM}$  = 10  $\mu$ H,  $C_{DEM}$  = 1  $\mu$ FAES17 + AUX-0025 measurement filters, unless otherwise noted.

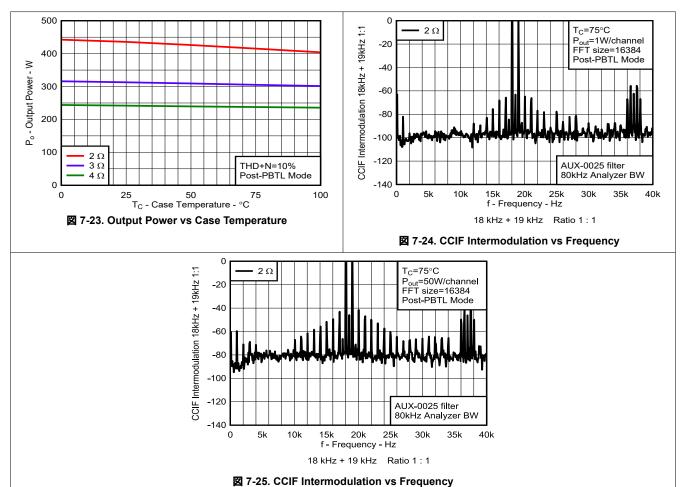

## 7.9 Typical Characteristics, PBTL Configuration, AD-mode

All Measurements taken at audio frequency = 1 kHz, PVDD = 42 V, VDD = 5 V, GVDD = 5 V,  $R_L = 2 \Omega$ ,  $f_S = 480$  kHz,  $T_A = 75^{\circ}$ C, Output Filter:  $L_{DEM} = 10 \mu$ H,  $C_{DEM} = 1 \mu$ F, Post-Filter PBTL, AES17 + AUX-0025 measurement filters, unless otherwise noted.

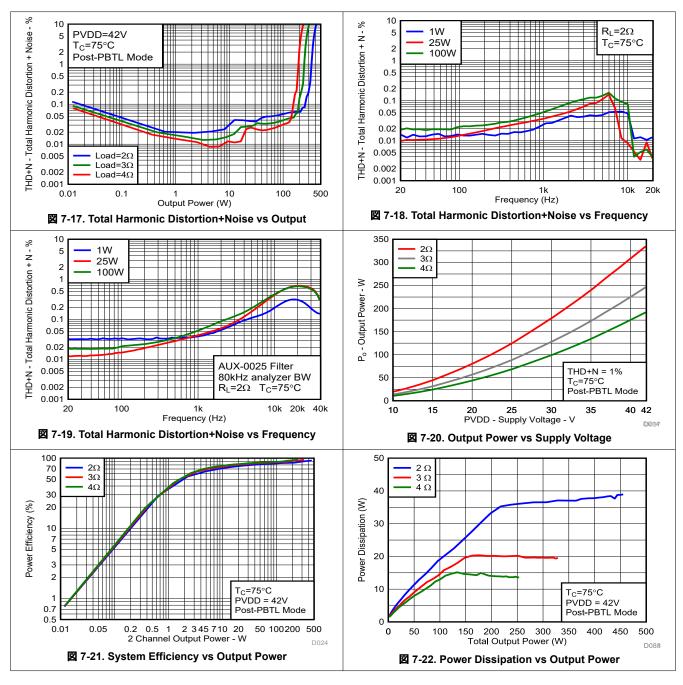

## 7.9 Typical Characteristics, PBTL Configuration, AD-mode (continued)

All Measurements taken at audio frequency = 1 kHz, PVDD = 42 V, VDD = 5 V, GVDD = 5 V,  $R_L = 2 \Omega$ ,  $R_S = 480$  kHz,  $R_A = 75^{\circ}$ C, Output Filter:  $R_D = 10 \mu$ H,  $R_D = 1 \mu$ F, Post-Filter PBTL, AES17 + AUX-0025 measurement filters, unless otherwise noted.

## **8 Parameter Measurement Information**

All parameters are measured according to the conditions described in the セクション 7.3.

Most audio analyzers will not give correct readings of Class-D amplifiers' performance due to their sensitivity to out of band noise present at the amplifier output. AES-17 + AUX-0025 pre-analyzer filters are recommended to use for Class-D amplifier measurements. In absence of such filters, a 30-kHz low-pass filter (10  $\Omega$  + 47 nF) can be used to reduce the out of band noise remaining on the amplifier outputs.

Product Folder Links: TPA3223

## 9 Detailed Description

#### 9.1 Overview

TPA3223 is designed as a feature-enhanced cost efficient high power Class-D audio amplifier. The device has built-in advanced protection circuitry to provide for maximum product robustness as well as a flexible feature set including selectable gain settings, switching frequency, clock synchronization of multiple devices, mute function, temperature and clipping status signals. TPA3223 has a bandwidth up to 100 kHz and low output noise designed for high resolution audio applications and accepts both differential and single ended analog audio inputs at levels from 1  $V_{RMS}$  to 2  $V_{RMS}$ . With the closed loop operation TPA3223 is designed for high audio performance with a system power supply between 10 V and 42 V.

An external 5 V supply is used for the AVDD and VDD supply pins. Although supplied from the same 5 V source, separating AVDD and VDD on the printed-circuit board (PCB) by RC filters (see セクション 10.2 for details) is recommended. These RC filters provide the recommended high-frequency isolation. Special attention needs to be paid to placing all decoupling capacitors as close to their associated pins as possible. In general, the physical loop with the power supply pins, decoupling capacitors and GND return path to the device pins must be kept as short as possible and with as little area as possible to minimize induction (see セクション 10.4.2 for additional information).

The floating supplies for the output stage high side gate drives are supplied by built-in bootstrap circuitry requiring only an external capacitor for each half-bridge.

For a properly functioning bootstrap circuit, a small ceramic capacitor must be connected from each bootstrap pin (BST\_X) to the power-stage output pin (OUT\_X). When the power-stage output is low, the bootstrap capacitor is charged through an internal diode connected between the gate-drive power-supply pin (GVDD) and the bootstrap pins. When the power-stage output is high, the bootstrap capacitor potential is shifted above the output potential and thus provides an acceptable voltage supply for the high-side gate driver. TI recommends to use 33 nF ceramic capacitors, size 0603 or 0805, for the bootstrap supply. These 33 nF capacitors maintain sufficient energy storage, even during minimal PWM duty cycles, to keep the high-side power stage FET (LDMOS) fully turned on during the remaining part of the PWM cycle.

Special attention needs to be paid to the power stage power supply; this includes component selection, PCB placement, and routing.

For good electrical performance, EMI compliance, and system reliability, it is important that each PVDD\_X node is decoupled with 1  $\mu$ F ceramic capacitors placed as close as possible to the PVDD supply pins. TI recommends to follow the PCB layout of the TPA3223 reference design. For additional information on recommended power supply and required components, see  $\forall p > 10.2$ .

The external power supply for the AVDD and VDD supplies must be from a low-noise, low-output-impedance voltage regulator. Likewise, the 42V power stage supply is assumed to have low output impedance throughout the entire audio band, and low noise. The power supply sequence is not critical as facilitated by the internal power-on-reset circuit, but TI recommends to release RESET after the power supply is settled for minimum turn on audible artifacts. Moreover, the TPA3223 is fully protected against erroneous power-stage turn on due to parasitic gate charging. Thus, voltage-supply ramp rates (dV/dt) are noncritical within the specified range (see the topical value).

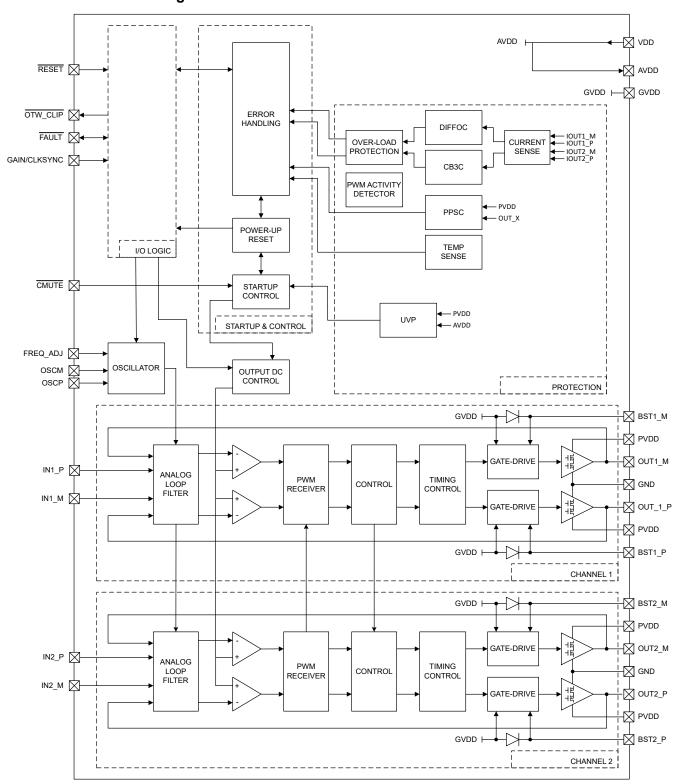

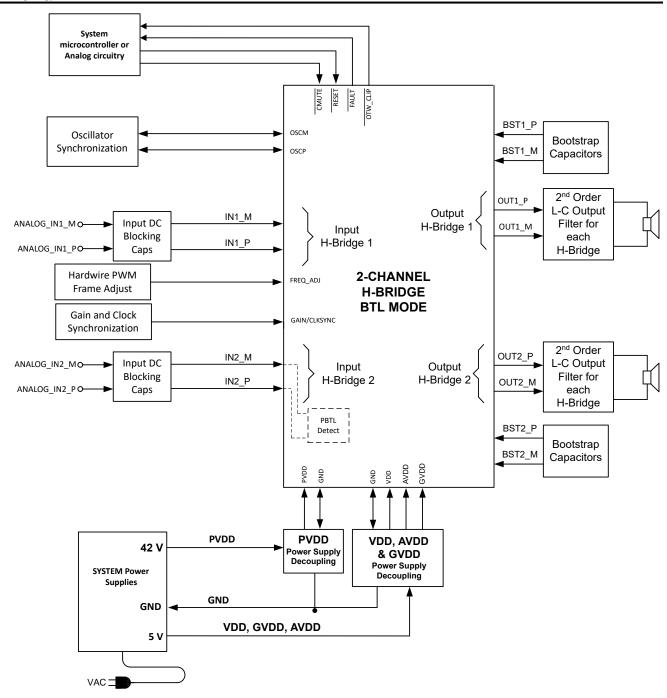

## 9.2 Functional Block Diagrams

図 9-1. Functional Block Diagram

\*NOTE1: Logic AND in or outside microcontroller

図 9-2. System Block Diagram

## 9.3 Feature Description

#### 9.3.1 Input Configuration, Gain Setting And Primary / Peripheral Operation

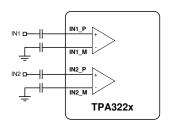

TPA3223 is designed to accept either a differential or a single-ended audio input signal. To accept a wide range of system front ends TPA3223 has selectable input gain that allows full scale output with a wide range of input signal levels.

Best system noise performance is obtained with balanced audio interface. However, in systems with only a single ended audio input signal available, one input terminal can be connected to AC ground to accept single ended audio input signals.

図 9-3. Balanced Audio Input Configuration

In systems with single ended audio inputs, set the device gain higher than for systems with balanced audio input signals.

図 9-4. Single Ended Audio Input Configuration

## 9.3.2 Gain Setting And Clock Synchronization

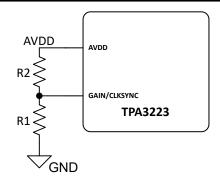

The gain of TPA3223 is set by the voltage divider connected to the GAIN/CLKSYNC control pin. Clock synchronization configuration is also controlled by the same pin. An internal ADC is used to detect the 8 input states. The first four stages sets the GAIN in Primary mode in gains of 20, 23.5, 32 and 36 dB respectively, while the next four stages sets the GAIN in peripheral mode in gains of 20, 23.5, 32 and 36 dB respectively. The gain setting is latched when  $\overline{\text{RESET}}$  goes high and cannot be changed while  $\overline{\text{RESET}}$  is high.  $\frac{1}{5}$  9-1 shows the recommended resistor values, the state and gain:

| 2x 9-1. Clock Synchronization Configuration |         |             |              |                                                  |                                    |  |  |

|---------------------------------------------|---------|-------------|--------------|--------------------------------------------------|------------------------------------|--|--|

| Primary / Peripheral<br>Mode                | Gain    | R1 (to GND) | R2 (to AVDD) | Differential Input Signal Level (each input pin) | Single Ended Input Signal<br>Level |  |  |

| Primary                                     | 20 dB   | 5.6 kΩ      | OPEN         | 2 VRMS                                           | 2 VRMS                             |  |  |

| Primary                                     | 23.5 dB | 20 kΩ       | 100 kΩ       | 1 VRMS                                           | 2 VRMS                             |  |  |

| Primary                                     | 32 dB   | 39 kΩ       | 100 kΩ       | 0.5 VRMS                                         | 1 VRMS                             |  |  |

| Primary                                     | 36 dB   | 47 kΩ       | 75 kΩ        | 0.32 VRMS                                        | 0.63 VRMS                          |  |  |

| Peripheral                                  | 20 dB   | 51 kΩ       | 51 kΩ        | 2 VRMS                                           | 2 VRMS                             |  |  |

| Peripheral                                  | 23.5 dB | 75 kΩ       | 47 kΩ        | 1 VRMS                                           | 2 VRMS                             |  |  |

| Peripheral                                  | 32 dB   | 100 kΩ      | 39 kΩ        | 0.5 VRMS                                         | 1 VRMS                             |  |  |

| Peripheral                                  | 36 dB   | 100 kΩ      | 16 kΩ        | 0.32 VRMS                                        | 0.63 VRMS                          |  |  |

表 9-1. Clock Synchronization Configuration

図 9-5. Clock Synchronization Setup

For easy multi-channel system design TPA3223 has a Clock Synchronization feature that allows automatic synchronization of multiple peripheral devices operated at the PWM switching frequency of a Primary device. Using clock synchronization benefits system noise performance by eliminating spurious crosstalk sum and difference tones due to unsynchronized channel-to-channel switching frequencies. Furthermore, the Clock Synchronization scheme is designed to interleave switching of the individual channels in a multi-channel system such that the power supply current ripple frequency is moved to a higher frequency, which reduces the RMS ripple current in the power supply bulk capacitors.

The Clock Synchronization scheme and the interleaving of the output stage switching are automatically configured by connecting the OSCx pins between a Primary and multiple peripheral devices. There are two different configurations of peripheral devices (secondary or tertiary) depending on how the OSCx pins are connected. Connect the OSCM of the Primary device to the OSCM of a peripheral device and the OSCP of the Primary device to the OSCP pin of a peripheral device to configure as a secondary. Connect the OSCM of the Primary device to the OSCP of a peripheral device and the OSCP of the Primary device to the OSCM pin of a peripheral device to configure as a tertiary. The Primary, secondary and tertiary PWM switching is 30 degrees out of phase with each other. All switching channels are automatically synchronized by releasing RESET on all devices at the same time.

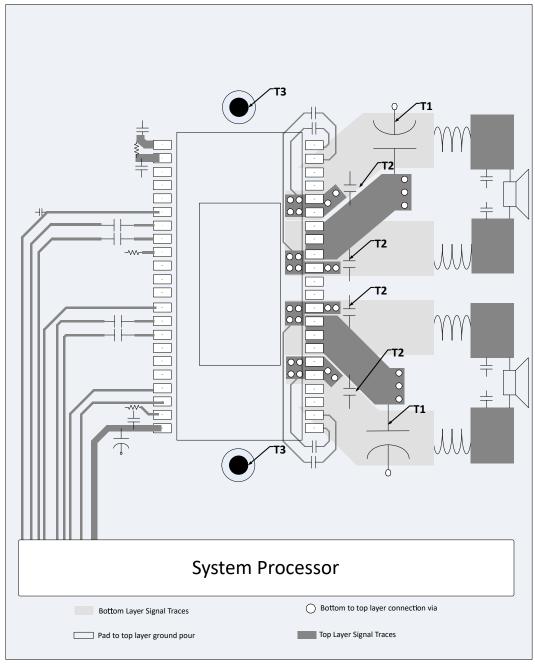

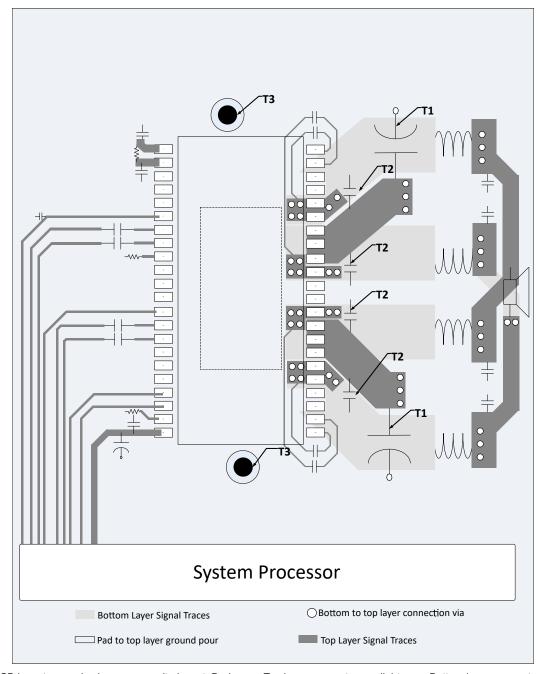

図 9-6. Gain and Primary PCB Implementation

Placement on the PCB and connection of multiple TPA3223 devices in a multi channel system is illustrated in  $\boxtimes$  9-6. Peripheral devices must be placed on either side of the Primary device, with a secondary device on one side of the Primary device, and a tertiary device on the other. In systems with more than 3 TPA3223 devices, the Primary must be in the middle, and every second peripheral device must be a secondary or tertiary as illustrated in  $\boxtimes$  9-6. A 47 k $\Omega$  pull up resistor to AVDD must be connected to the Primary device OSCM output and a 47 k $\Omega$  pull down resistor to GND must be connected to the Primary OSCP CLK outputs.

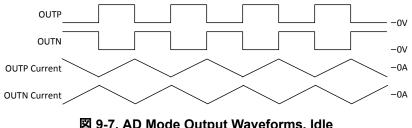

#### 9.3.3 PWM Modulation

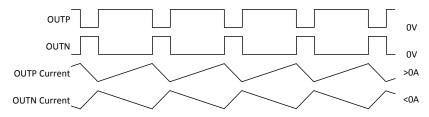

The TPA3223 uses the AD-Mode PWM modulation scheme which continuous switches the two half bridge outputs in each BTL output channel.

図 9-8. AD Mode Output Waveforms, High Level Output

図 9-9. AD Mode Speaker Output Signals, Low or and High Level Output

#### 9.3.4 Oscillator

The oscillator frequency can be trimmed by external control of the FREQ\_ADJ pin.

For peripheral mode operation, turn off the oscillator by pulling the FREQ\_ADJ pin to AVDD. Doing so configures the OSC\_I/O pins as inputs to be controlled from an external differential clock. In a multiple device system, interchannel delay is automatically set up between the switching of the audio channels, which can be illustrated by no idle channels switching at the same time. Doing so will not influence the audio output, but only the switch timing to minimize noise coupling between audio channels through the power supply to optimize audio performance and to get better operating conditions for the power supply. The inter-channel delay will be set up for a peripheral device depending on the polarity of the OSC\_I/O connection such that a secondary is selected by connecting the primary device OSC\_I/O to the secondary device OSC\_I/O with same polarity (+ to + and - to -), and tertiary is selected with the inverse polarity (+ to - and - to +).

#### 9.3.5 Input Impedance

The TPA3223 input stage is a fully differential input stage and the input impedance changes with the gain setting from 7.3 k $\Omega$  at 36 dB gain to 48 k $\Omega$  at 20 dB gain.  $\gtrsim$  9-2 lists the values from min to max gain. The tolerance of the input resistor value is ±20 % so the minimum value is higher than 5.8 k $\Omega$ . The inputs need to be AC-coupled to minimize the output DC-offset and ensure correct ramping of the output voltages during power-ON and power-OFF. The input ac-coupling capacitor together with the input impedance forms a high-pass filter with the following cut-off frequency:

If a flat bass response is required down to 20 Hz, then the recommended cut-off frequency is a tenth of that, which is 2 Hz.  $\frac{1}{2}$  9-2 lists the recommended ac-couplings capacitors for each gain step. If a -3 dB in frequency response is accepted at 20 Hz, then 10 times lower capacitors can be used – for example, a 1  $\mu$ F can be used.

| Gain    | Gain Input Impedance Ir |        | Input High Pass Filter |

|---------|-------------------------|--------|------------------------|

| 20 dB   | 48 kΩ                   | 4.7 μF | 0.7 Hz                 |

| 23.5 dB | 24 kΩ                   | 10 μF  | 0.7 Hz                 |

| 32 dB   | 12 kΩ                   | 10 μF  | 1.3 Hz                 |

| 36 dB   | 7.3 kΩ                  | 10 μF  | 2.2 Hz                 |

表 9-2. Recommended Input AC-Coupling Capacitors

Use an input capacitors with low leakage, like quality electrolytic, tantalum, film or ceramic. If a polarized type of input capacitor is used, then place the positive connection such that the capacitor has a positive DC bias.

## 9.3.6 Error Reporting

The FAULT, and OTW\_CLIP, pins are active-low, open-drain outputs. The FAULT function is for protection-mode signaling to a system-control device. Any fault resulting in device shutdown is signaled by the FAULT pin going low. Also, OTW\_CLIP goes low when the device junction temperature exceeds 125°C (see 表 9-3).

| 表 9-3. | Error | Rep | orting |

|--------|-------|-----|--------|

|--------|-------|-----|--------|

| FAULT | OTW_CLIP (1) | DESCRIPTION                                                                                                                                       |

|-------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | 0            | Overtemperature (OTE), overload (OLP), undervoltage (UVP) or overvoltage (OVP). Junction temperature higher than 125°C (overtemperature warning). |

| 0     | 1            | Overload (OLP), undervoltage (UVP), overvoltage (OVP). Junction temperature lower than 125°C                                                      |

| 1     | 0            | Junction temperature higher than 125°C (overtemperature warning)                                                                                  |

| 1     | 1            | Junction temperature lower than 125°C and no OLP or UVP faults (normal operation)                                                                 |

(1) Static value. OTW\_CLIP is static low when OTW is asserted, and toggling when output signal is CLIP

注

Asserting RESET low forces the FAULT signal high, independent of faults being present. TI recommends monitoring the OTW\_CLIP signal using the system microcontroller and responding to an overtemperature warning signal by turning down the volume to prevent further heating of the device resulting in device shutdown (OTE).

To reduce external component count, an internal pullup resistor to 3.3 V is provided on both FAULT and OTW\_CLIP outputs.

#### 9.4 Device Functional Modes

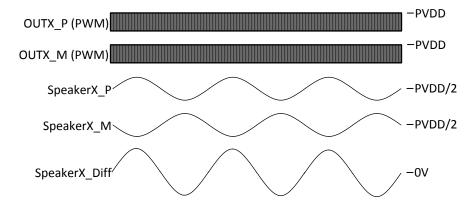

TPA3223 can be configured in either a stereo BTL (Bridge Tied Load) mode, mono BTL mode (only one output BTL channel active), or in a mono PBTL (Parallel Bridge Tied Load) mode. In PBTL mode the two output BTL channels are paralleled with double output current available. The paralleling of the two BTL outputs must be made after the output LC filter.

See 表 6-2 for mode configuration setup.

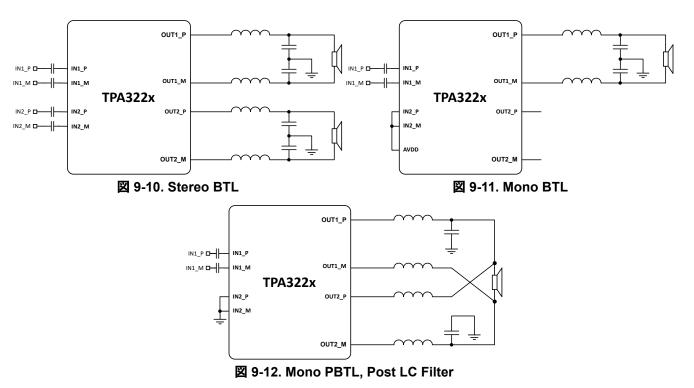

#### 9.4.1 Powering Up

The TPA3223 does not require a power-up sequence because of the integrated undervoltage protection (UVP), but TI recommends to hold RESET low until PVDD supply voltage is stable to avoid audio artifacts. The outputs of the H-bridges remain in a high-impedance state until the gate-drive supply (GVDD) and AVDD voltages are above their UVP voltage thresholds (see the \*\*T/Y=\*\sigma\* 7.5\* table of this data sheet). Doing so allows an internal circuit to charge the external bootstrap capacitors by enabling a weak pull-down of the half-bridge output as well as initiating a controlled ramp up sequence of the output voltage.

図 9-13. Startup Timing

When RESET is released to turn on TPA3223, FAULT signal turns low. FAULT stays low until AVDD reaches the undervoltage protection (UVP) voltage threshold (see the  $\forall \mathcal{I} \mathcal{I} \mathcal{I} \mathcal{I} \mathcal{I} \mathcal{I} \mathcal{I}$ ) table of this data sheet). After a precharge time to stabilize the DC voltage across the input AC coupling capacitors, the ramp up sequence starts and completes once the  $\overline{\text{CMUTE}}$  node is charged to the final value.

## 9.4.1.1 Startup Ramp Time

During the startup ramp the CMUTE capacitor is charged by an internal current generator. With use of the recommended 33 nF CMUTE capacitor value, the startup ramp time is approximately 20 ms. Higher CMUTE capacitor value will increase the ramp time, and a lower value will decrease the ramp time. The recommended CMUTE capacitor value is selected for minimum audible artifacts during startup and shutdown ramp.

#### 9.4.2 Powering Down

The TPA3223 does not require a power-down sequence. The device remains fully operational as long as the VDD, AVDD and PVDD voltages are above their undervoltage protection (UVP) voltage thresholds (see \$\frac{\tau}{2} \frac{\tau}{2} = \frac{\tau}{2} \frac{\tau}{2} = \frac{\tau}{2} \frac{\tau}{2} = \frac{\tau}{2} \frac{\tau}{2} = \frac{\tau}{2}

#### 9.4.2.1 Power Down Ramp Time

During the power down ramp the CMUTE capacitor is discharged by internal circuitry. With use of the recommended 33 nF CMUTE capacitor value, the power-down ramp time is approximately 20 ms.

#### 9.4.3 Device Reset

Asserting RESET low initiates the device ramp down. The output FETs go into a Hi-Z state after the ramp down is complete. Output pull downs are active in both BTL mode and PBTL mode with RESET low.

In BTL modes, to accommodate bootstrap charging prior to switching start, asserting the RESET input low enables weak pull-down of the half-bridge outputs.

Asserting RESET low removes any fault information to be signaled on the FAULT output, that is, FAULT is forced high. A rising-edge transition on RESET allows the device to resume operation after a fault. To make sure of thermal reliability, the rising edge of RESET must occur no sooner than 4 ms after the falling edge of FAULT.

The TPA3223 will enter a low power state once the ramp down sequence is complete.

#### 9.4.4 Device Soft Mute

Asserting CMUTE low initiates the device soft mute function. The soft mute function initiates a ramp down sequence of the outputs, and the output FETs go into a Hi-Z state after the ramp down is complete. All internal circuits are powered while in soft mute state. External control of the soft mute function must provide high impedance output when not engaged (open drain output) to allow the CMUTE node to charge/discharge during device ramp up and ramp down when de-asserting and asserting RESET.

#### 9.4.5 Device Protection System

The TPA3223 contains advanced protection circuitry carefully designed to facilitate system integration and ease of use, as well as to safeguard the device from permanent failure due to a wide range of fault conditions such as short circuits, overload, overtemperature, overvoltage, and undervoltage. The TPA3223 responds to a fault by immediately setting the power stage in a high-impedance (Hi-Z) state and asserting the FAULT pin low. In situations other than overload and overtemperature error (OTE), the device automatically recovers when the fault condition has been removed, that is, the supply voltage has increased. The device will handle errors, as shown in 表 9-4.

| BTL I                    | MODE | PBTL           | MODE      |  |  |  |

|--------------------------|------|----------------|-----------|--|--|--|

| LOCAL ERROR IN TURNS OFF |      | LOCAL ERROR IN | TURNS OFF |  |  |  |

| A                        | A+B  | A              |           |  |  |  |

| В                        | A.P  | В              | A+B+C+D   |  |  |  |

| С                        | C+D  | С              | ATBTCTD   |  |  |  |

| D                        | C+D  | D              |           |  |  |  |

表 9-4. Device Protection

Bootstrap UVP does not shutdown according to the table, it shuts down the respective half-bridge (non-latching, does not assert FAULT).

#### 9.4.5.1 Overload and Short Circuit Current Protection

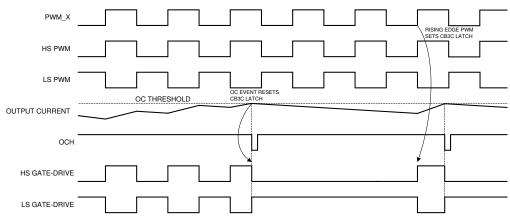

TPA3223 has fast reacting current sensors on all high-side and low-side FETs. To prevent output current from increasing beyond the overcurrent threshold, TPA3223 uses current limiting of the output current for each switching cycle (Cycle By Cycle Current Control, CB3C) in case of excess output current. CB3C prevents premature shutdown due to high output current transients caused by high level music transients and a drop of the real load impedance of the speaker, and allows the output current to be limited to a maximum programmed level. If the maximum output current persists, for example the power stage being overloaded with too low load impedance, then the device will shut down the affected output channel and the affected output is put in a highimpedance (Hi-Z) state until a RESET cycle is initiated. CB3C works individually for each full-bridge output. If an over current event is triggered, then the CB3C performs a state flip of the full-bridged output that is cleared upon beginning of next PWM frame.

Product Folder Links: TPA3223

図 9-14. CB3C Timing Example

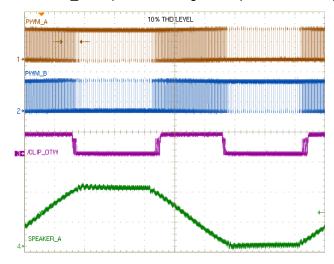

### 9.4.5.2 Signal Clipping and Pulse Injector

A built-in activity detector monitors the PWM activity of the OUT\_X pins. TPA3223 is designed to drive unclipped output signals all the way to PVDD and GND rails. In case of audio signal clipping when applying excessive input signal voltage, or in case of CB3C current protection being active, the amplifier feedback loop of the audio channel will respond to this condition with a saturated state, and the output PWM signals will stop unless special circuitry is implemented to handle this situation. To prevent the output PWM signals from stopping in a clipping or CB3C situation, narrow pulses are injected to the gate drive to maintain output activity. The injected narrow pulses are injected at every 4<sup>th</sup> PWM frame, and thus the effective switching frequency during this state is reduced to 1/4 of the normal switching frequency.

Signal clipping is signaled on the OTW\_CLIP pin and is self clearing when signal level reduces and the device reverts to normal operation. The OTW\_CLIP pulses start at the onset to output clipping, typically at a THD level around 0.01%, resulting in narrow OTW\_CLIP pulses starting with a pulse width of approximately 500 ns.

図 9-15. Signal Clipping PWM and Speaker Output Signals

#### 9.4.5.3 DC Speaker Protection

The output DC protection scheme protects a speaker from excess DC current in case one terminal of the speaker is connected to the amplifier while the other is accidentally shorted to the chassis ground. Such a short circuit results in a DC voltage of PVDD/2 across the speaker, which potentially can result in destructive current levels. The output DC protection detects any unbalance of the output and input current of a BTL or PBTL output configuration (current into/out of one half-bridge equals current out of/into the other half-bridge), and in the event of the imbalance exceeding a programmed threshold, the overload counter increments until the maximum value and the affected output channel is shut down. DC Speaker Protection is enabled in both BTL and PBTL mode operation.

#### 9.4.5.4 Pin-to-Pin Short Circuit Protection (PPSC)

The PPSC detection system protects the device from permanent damage in the case that a power output pin (OUT\_X) is shorted to GND\_X or PVDD\_X. For comparison, the OC protection system detects an overcurrent after the demodulation filter where PPSC detects shorts directly at the pin before the filter. PPSC detection is performed at startup after RESET is pulled high. When PPSC detection is activated by a short on the output, all half-bridges are kept in a Hi-Z state until the short is removed; the device then continues the startup sequence and starts switching. The detection is controlled globally by a two step sequence. The first step ensures that there are no shorts from OUT\_X to GND\_X, the second step tests that there are no shorts from OUT\_X to PVDD\_X. The total duration of this process is roughly proportional to the capacitance of the output LC filter. The typical duration is < 15 ms/µF. While the PPSC detection is in progress, FAULT is kept low. If no shorts are present, then the PPSC detection passes, and FAULT is released. A device reset will start a new PPSC detection. PPSC detection is enabled in both BTL and PBTL output configurations. To ensure not to trip the PPSC detection system, TI recommends not to insert a resistive load to GND\_X or PVDD\_X.

## 9.4.5.5 Overtemperature Protection OTW and OTE

TPA3223 has a two-level temperature-protection system that asserts an active-low warning signal ( \overline{OTW\_CLIP}) when the device junction temperature exceeds 125°C (typical). If the device junction temperature exceeds 155°C (typical), then the device is put into thermal shutdown, resulting in all half-bridge outputs being set in the high-impedance (Hi-Z) state and \overline{FAULT} being asserted low. OTE is latched in this case. To clear the OTE latch, \overline{RESET} must be asserted. Thereafter, the device resumes normal operation.

#### 9.4.5.6 Undervoltage Protection (UVP), Overvoltage Protection (OVP), and Power-on Reset (POR)

The UVP, OVP and POR circuits of the TPA3223 fully protect the device in any power-up/down and brownout situation, and also in overvoltage situation with PVDD not exceeding the values stated in セクション 7.1. While powering up, the POR circuit ensures that all circuits are fully operational when the AVDD supply voltage reaches the value stated in セクション 7.5. Although AVDD is independently monitored, a supply voltage drop below the UVP threshold on AVDD pin results in all half-bridge outputs immediately being set in the high-impedance (Hi-Z) state. The device automatically resumes operation when all supply voltages have increased above their UVP threshold. In case of an OVP event, all half-bridge outputs are immediately set in the high-impedance (Hi-Z) state and FAULT is asserted low until PVDD is below the OVP threshold.

Product Folder Links: TPA3223

#### 9.4.5.7 Fault Handling

If a fault situation occurs while in operation, then the device acts accordingly to the fault being a global or a channel fault. A global fault is a chip-wide fault situation and causes all PWM activity of the device to be shut down, and asserts FAULT low. A global fault is a latching fault and clearing FAULT and restarting operation requires resetting the device by toggling RESET. De-asserting RESET is never allowed with excessive system temperature, so TI recommends to monitor RESET with a system microcontroller and only release RESET (RESET high) if the OTW\_CLIP signal is cleared (high). A channel fault results in shutdown of the PWM activity of the affected channels.

注

Asserting RESET low forces the FAULT signal high, independent of faults being present.

表 9-5. Error Reporting

| ₹ 5-6. End Reporting          |                                       |                   |                  |                          |                                     |                                    |  |  |

|-------------------------------|---------------------------------------|-------------------|------------------|--------------------------|-------------------------------------|------------------------------------|--|--|

| Fault/Event                   | Fault/Event<br>Description            | Global or Channel | Reporting Method | Latched/Self<br>Clearing | Action needed to<br>Clear           | Output FETs                        |  |  |

| PVDD_X UVP                    |                                       |                   |                  |                          | Increase affected supply voltage    |                                    |  |  |

| PVDD_X OVP                    | Voltage Fault                         | Global            | FAULT pin        | Self Clearing            | Decrease affected supply voltage    | HI-Z                               |  |  |

| AVDD UVP                      |                                       |                   |                  |                          | Increase affected supply voltage    |                                    |  |  |

| POR (AVDD UVP)                | Power On Reset                        | Global            | FAULT pin        | Self Clearing            | Allow AVDD to rise                  | HI-Z                               |  |  |

| OTW                           | Thermal Warning                       | Global            | OTW_CLIP pin     | Self Clearing            | Cool below OTW threshold            | Normal operation                   |  |  |

| OTE                           | Thermal Shutdown                      | Global            | FAULT pin        | Latched                  | Toggle RESET                        | HI-Z                               |  |  |

| OLP (CB3C>2.1 ms)             | OC Shutdown                           | Channel           | FAULT pin        | Latched                  | Toggle RESET                        | HI-Z                               |  |  |

| CB3C                          | OC Limiting                           | Channel           | None             | Self Clearing            | Reduce signal level or remove short | Flip state, cycle by cycle at fs/3 |  |  |

| Stuck at Fault <sup>(1)</sup> | No OSC_IO activity in Peripheral Mode | Global            | None             | Self Clearing            | Resume OSC_IO activity              | HI-Z                               |  |  |

<sup>(1)</sup> Stuck at Fault occurs when input OSC\_IO input signal frequency drops below minimum frequency given in the *Electrical Characteristics* table of this data sheet.

Copyright © 2022 Texas Instruments Incorporated

Submit Document Feedback

## 10 Application and Implementation

注

以下のアプリケーション情報は、TIの製品仕様に含まれるものではなく、TIではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

## 10.1 Application Information

TPA3223 can be configured either in stereo BTL, mono BTL or mono PBTL mode depending on output power conditions and system design.

## 10.2 Typical Applications

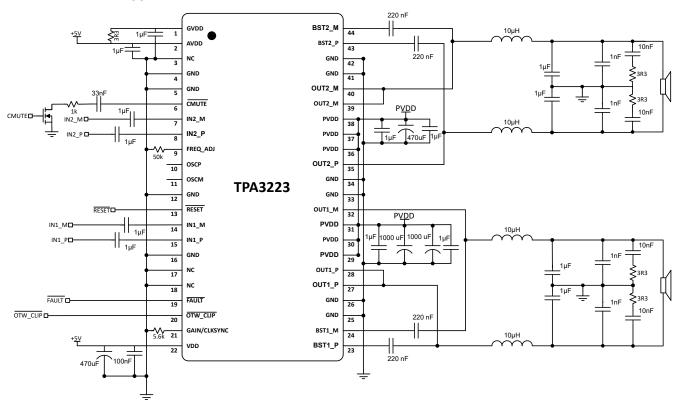

## 10.2.1 Stereo BTL Application

図 10-1. Typical Differential (2N) AD-Mode BTL Application

Submit Document Feedback

#### 10.2.1.1 Design Requirements

For this design example, use the parameters in 表 10-1.

表 10-1. Design Requirements, BTL Application

| DESIGN PARAMETER            | EXAMPLE                                           |

|-----------------------------|---------------------------------------------------|

| Low Power Supply            | 5 V                                               |

| High Power Supply           | 10 - 42 V                                         |

|                             | IN1_M = ±2.8V (peak, max)                         |

| Analog Inputs               | IN1_P = ±2.8V (peak, max)                         |

| Arialog inputs              | IN2_M = ±2.8V (peak, max)                         |

|                             | IN2_P = ±2.8V (peak, max)                         |

| Output Filters              | Inductor-Capacitor Low Pass Filter (10 μH + 1 μF) |

| Speaker Impedance 3.5 - 8 Ω |                                                   |

## 10.2.1.2 Detailed Design Procedures

A rising-edge transition on RESET input allows the device to execute the startup sequence and start switching.

A toggling OTW\_CLIP signal is indicating that the output is approaching clipping. The signal can be used either to decrease audio volume or to control an intelligent power supply nominally operating at a low rail adjusting to a higher supply rail.

The device inverts the audio signal from input to output.

#### 10.2.1.2.1 Decoupling Capacitor Recommendations

In order to design an amplifier that has robust performance, passes regulatory requirements, and exhibits good audio performance, good quality decoupling capacitors should be used. In practice, use X7R in this application.

The voltage of the decoupling capacitors should be selected in accordance with good design practices. Temperature, ripple current, and voltage overshoot must be considered. This is particularly true in the selection of the 1  $\mu$ F capacitor that is placed on the power supply to each full-bridge. The capacitor must withstand the voltage overshoot of the PWM switching, the heat generated by the amplifier during high power output, and the ripple current created by high power output. A minimum voltage rating of 75 V is required for use with a 42 V power supply.

#### 10.2.1.2.2 PVDD Capacitor Recommendation

The large capacitors used in conjunction with each full-bridge, are referred to as the PVDD Capacitors. Select these capacitors for proper voltage margin and adequate capacitance to support the power requirements. In practice, with a well designed system power supply, two 1000  $\mu$ F capacitors, 75 V supports most applications. Use PVDD capacitors with low ESR type because they are used in a circuit associated with high-speed switching.

## 10.2.1.2.3 BST capacitors

To make sure of a large enough bootstrap energy storage for the high side gate drive to work correctly with all audio source signals, 33 nF / 50 V X7R BST capacitors are recommended.

#### 10.2.1.2.4 PCB Material Recommendation

FR-4 Glass Epoxy material with 2 oz. (70  $\mu$ m) copper is recommended for use with the TPA3223. The use of this material can provide for higher power output, improved thermal performance, and better EMI margin due to lower PCB trace inductance.

#### 10.2.2 Application Curves

Relevant performance plots for TPA3223 in BTL configuration are shown in セクション 7.8

図 10-2. Total Harmonic Distortion + Noise vs Output Power

200  $3\Omega$ 180  $3\Omega$  - CB3C Limited  $4\Omega$ 160  $6\Omega$ Po - Output Power - W 140  $8\Omega$ Power Efficiency (%) 120 100 80 60 40 THD+N = 10% T<sub>C</sub>=75°C 20 BTL Mode 15 40 42 10 25 30 35 PVDD - Supply Voltage - V D0184

図 10-4. Output Power vs Supply Voltage, AD-mode

図 10-3. Total Harmonic Distortion+Noise vs Frequency

図 10-5. System Efficiency vs Output Power

Submit Document Feedback

#### 10.2.3 Typical Application, Differential (2N), AD-Mode PBTL (Outputs Paralleled after LC filter)

TPA3223 can be configured in mono PBTL mode by paralleling the outputs before the LC filter (see ) or after the LC filter. Paralleled outputs after the LC filter can be preferred if a single board design must support both PBTL and BTL, or in the case multiple, smaller paralleled inductors are preferred due to size or cost. Paralleling after the LC filter requires four inductors, one for each OUT\_x. This section shows an example of paralleled outputs after the LC filter.

図 10-6. Typical Differential (2N) AD-Mode PBTL Application

#### 10.2.3.1 Design Requirements

Refer to セクション 10.2.1 for the Design Requirements.

表 10-2. Design Requirements, PBTL Application

| DESIGN PARAMETER  | EXAMPLE                                           |  |  |

|-------------------|---------------------------------------------------|--|--|

| Low Power Supply  | 5 V                                               |  |  |

| High Power Supply | 10 - 42 V                                         |  |  |

| Analog Inputs     | IN1_M = ±2.8 V (peak, max)                        |  |  |

|                   | IN1_P = ±2.8 V (peak, max)                        |  |  |

|                   | IN2_M = Grounded                                  |  |  |

|                   | IN2_P = Grounded                                  |  |  |

| Output Filters    | Inductor-Capacitor Low Pass Filter (10 μH + 1 μF) |  |  |

| Speaker Impedance | 2 - 4 Ω                                           |  |  |

Copyright © 2022 Texas Instruments Incorporated

Submit Document Feedback

## 10.3 Power Supply Recommendations

#### 10.3.1 Power Supplies

The TPA3223 device requires an external power supply for PVDD to power the output stage of the speaker amplifier and the associated circuitry.

An external power supply must be connected to GVDD, AVDD and VDD to power the gate-drive and other internal digital and analog circuit blocks in the device.

The allowable voltage range for both the PVDD and GVDD/AVDD/VDD supplies are listed in セクション 7.3. Ensure both the PVDD and the GVDD/AVDD/VDD supplies can deliver more current than listed in セクション 7.3.

## 10.3.1.1 VDD Supply

An external 5 V power supply needs to be connected to VDD, AVDD and GVDD.

Proper connection, routing, and decoupling techniques are highlighted in the TPA3223 EVM User's Guide (as well as \(\frac{\psi\_1\sum\_2}{2\sum\_2}\) 10.1 and \(\frac{\psi\_2\sum\_2}{2\sum\_2}\) 10.4.2) and must be followed as closely as possible for proper operation and performance. Deviation from the guidance offered in the TPA3223 device EVM User's Guide, which followed the same techniques as those shown in \(\frac{\psi\_1\sum\_2}{2\sum\_2}\) 10.1, may result in reduced performance, errant functionality, or even damage to the TPA3223 device.

### 10.3.1.2 AVDD and GVDD Supplies

AVDD and GVDD can be supplied through an external 5 V power supply to power internal analog and digital circuits and the gate-drivers for the output H-bridges. Proper connection, routing, and decoupling techniques are highlighted in the TPA3223 device EVM User's Guide (as well as  $2000 \pm 10.1$  and  $2000 \pm 10.4.2$ ) and must be followed as closely as possible for proper operation and performance. Deviation from the guidance offered in the TPA3223 device EVM User's Guide, which followed the same techniques as those shown in  $2000 \pm 10.1$  may result in reduced performance, errant functionality, or even damage to the TPA3223 device.

#### 10.3.1.3 PVDD Supply