# TPS3704x クワッド、トリプル、デュアル・ウィンドウまたは標準電圧スーパーバイザ

## 1 特長

- 最大 4 つの独立した電圧スーパーバイザ・チャネル:

- 固定および調整可能なウインドウ、UV、OV の電圧オプション。使用可能なオプションについては、表 4-1 を参照してください。

- 可変バージョン用の使いやすい計算ツール

- 高いスレッショルド精度:  $\pm 0.25\%$  (標準値)

- 高精度のヒステリシス:  $0.75\%$  (標準値)

- 固定リセット遅延時間オプション

- オープン・ドレイン出力

- TDA4、Sitara AM33xx などの Arm ベースのプロセッサや、高度な FPGA と SoC をサポートするように設計済み

- 低静止電流:  $15\mu\text{A}$  以下

- 温度範囲:  $-40^\circ\text{C} \sim +125^\circ\text{C}$

- 機能安全準拠**

- SIL 3 までを対象とする決定論的対応能力

- SIL 1 までを対象とするハードウェア機能

## 2 アプリケーション

- ファクトリ・オートメーション

- ビル・オートメーション

- 医療用

- モータ・ドライブ

- グリッド・インフラストラクチャ

- ワイヤレス・インフラ

- データ・センターおよびエンタープライズ・コンピューティング

## 3 概要

TPS3704x は、クワッド、トリプル、デュアル・チャネルとして構成できる、低消費電力の高精度ウインドウ / 標準電圧スーパーバイザです。各チャネルのスレッショルド精度は  $\pm 1\%$  で、8 ピン ( $1.6\text{mm} \times 2.9\text{mm}$ ) の SOT-23 パッケージに搭載されており、ソリューション・サイズを小型化できます。TPS3704x は高精度のスレッショルド検出を採用しており、高分解能です。低電圧の電源レールで動作し、電源許容誤差が狭いシステムに最適です。低いスレッショルド・ヒステリシスと固定のリセット遅延が組み込まれているため、複数の電圧レール監視中の誤ったリセット信号の発生が防止されます。

TPS3704x は、外付け抵抗なしで過電圧および低電圧リセットのスレッショルドを設定できるため、総合的な高精度、コスト、ソリューション・サイズをさらに最適化でき、安全性システムの信頼性も向上します。

VDD ピンと SENSEx ピンは独立しており、VDD 以外のレール電圧を監視することや、プッシュ・ボタン入力として使用することもできます。SENSEx ピンは、外部抵抗のオプション使用をサポートします。TPS3704x の各チャネルは、対称型または非対称型にすることができる上限スレッショルドと下限スレッショルドの許容誤差により、過電圧 / 低電圧ウインドウ検出を独自にカスタマイズできます。

### 製品情報

| 部品番号     | パッケージ <sup>(1)</sup> | 本体サイズ (公称)    |

|----------|----------------------|---------------|

| TPS3704x | DDF (8 ピン SOT-23)    | 1.6mm × 2.9mm |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

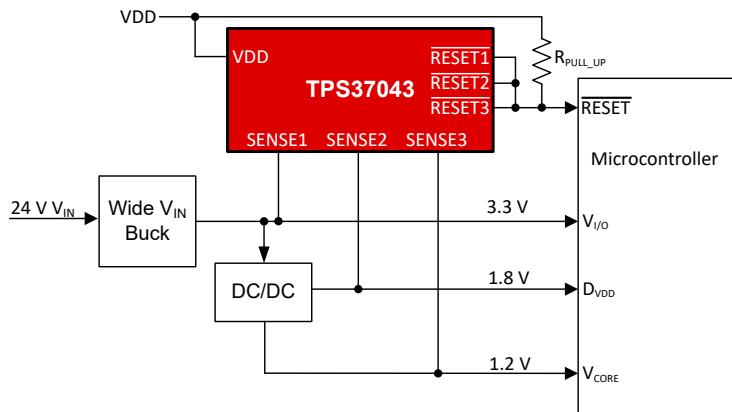

代表的なアプリケーション回路

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                  |    |                             |    |

|------------------|----|-----------------------------|----|

| 1 特長.....        | 1  | 7.3 機能説明.....               | 19 |

| 2 アプリケーション.....  | 1  | 7.4 デバイスの機能モード.....         | 21 |

| 3 概要.....        | 1  | 8 アプリケーションと実装.....          | 22 |

| 4 デバイス命名規則.....  | 3  | 8.1 アプリケーション情報.....         | 22 |

| 5 ピン構成と機能.....   | 5  | 8.2 代表的なアプリケーション.....       | 24 |

| 6 仕様.....        | 8  | 8.3 電源に関する推奨事項.....         | 27 |

| 6.1 絶対最大定格.....  | 8  | 8.4 レイアウト.....              | 28 |

| 6.2 ESD 定格.....  | 8  | 9 デバイスおよびドキュメントのサポート.....   | 29 |

| 6.3 推奨動作条件.....  | 8  | 9.1 デバイス命名規則.....           | 29 |

| 6.4 熱に関する情報..... | 8  | 9.2 ドキュメントの更新通知を受け取る方法..... | 30 |

| 6.5 電気的特性.....   | 9  | 9.3 サポート・リソース.....          | 30 |

| 6.6 タイミング要件..... | 10 | 9.4 商標.....                 | 30 |

| 6.7 タイミング図.....  | 11 | 9.5 静電気放電に関する注意事項.....      | 31 |

| 6.8 代表的特性.....   | 13 | 9.6 用語集.....                | 31 |

| 7 詳細説明.....      | 17 | 10 改訂履歴.....                | 31 |

| 7.1 概要.....      | 17 | 11 メカニカル、パッケージ、および注文情報..... | 31 |

| 7.2 機能ブロック図..... | 17 |                             |    |

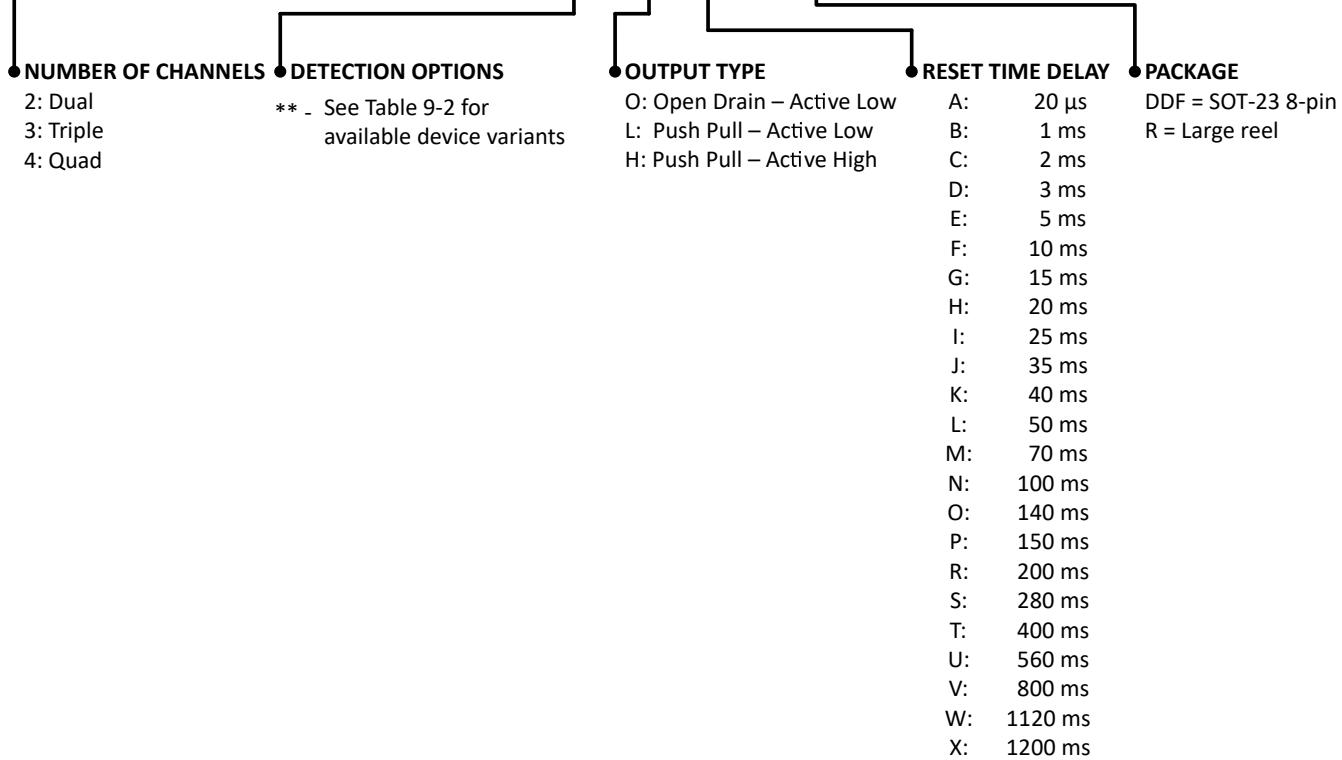

## 4 デバイス命名規則

図 4-1 に、さまざまなデバイス バリアントを比較するためのデバイス命名規則を示します。詳細については、表 9-1 を参照してください。使用可能なデバイス バリアントについては、表 4-1 または 表 9-2 を参照してください。

**表 4-1. デバイス スレッショルド表**

| 発注用部品名             | VARIANT <sup>(3)</sup> | チャネル数 | リセット時間 | SENSE1 <sup>(1) (2)</sup> | SENSE2 <sup>(1) (2)</sup> | SENSE3 <sup>(1) (2)</sup> | SENSE4 <sup>(1) (2)</sup> |

|--------------------|------------------------|-------|--------|---------------------------|---------------------------|---------------------------|---------------------------|

| TPS37042BJOFDDFRQ1 | ADJ                    | 2     | 10ms   | 0.8V ( $\pm 4\%$ )        | 0.8V ( $\pm 4\%$ )        | -                         | -                         |

| TPS37042A3OFDDFRQ1 | 固定                     | 2     | 10ms   | 3.3V ( $\pm 5\%$ )        | 1.2V ( $\pm 5\%$ )        | -                         | -                         |

| TPS37042ZJOFDDFRQ1 | 固定                     | 2     | 10ms   | 1.95V ( $\pm 4\%$ )       | 3.8V ( $\pm 6\%$ )        | -                         | -                         |

| TPS37043DJOFDDFR   | ADJ / 固定               | 3     | 10ms   | 3.3V (-11%)               | 1.2V (-11%)               | 0.8V (-8%)                | -                         |

| TPS37043A4OFDDFRQ1 | 固定                     | 3     | 10ms   | 2.8V ( $\pm 5\%$ )        | 1.8V ( $\pm 5\%$ )        | 1.2V ( $\pm 5\%$ )        | -                         |

| TPS37043A8OFDDFRQ1 | 固定                     | 3     | 10ms   | 3.3V ( $\pm 5\%$ )        | 1.8V ( $\pm 5\%$ )        | 1.0V ( $\pm 5\%$ )        | -                         |

| TPS37043CPOFDDFRQ1 | ADJ / 固定               | 3     | 10ms   | 3.3V ( $\pm 4\%$ )        | 0.75V ( $\pm 4\%$ )       | 0.8V ( $\pm 3\%$ )        | -                         |

| TPS37043ZJOFDDFRQ1 | 固定                     | 3     | 10ms   | 0.95V ( $\pm 4\%$ )       | 1.35V ( $\pm 4\%$ )       | 1.8V ( $\pm 4\%$ )        | -                         |

| TPS37043LJOFDDFRQ1 | ADJ                    | 3     | 10ms   | 0.4V ( $\pm 5\%$ )        | 0.4V ( $\pm 5\%$ )        | 0.8V ( $\pm 5\%$ )        | -                         |

| TPS37043CJOFDDFRQ1 | ADJ                    | 3     | 10ms   | 0.8V ( $\pm 6\%$ )        | 0.8V ( $\pm 6\%$ )        | 0.8V ( $\pm 6\%$ )        | -                         |

| TPS37043MJOFDDFRQ1 | ADJ                    | 3     | 10ms   | 0.4V ( $\pm 7\%$ )        | 0.4V ( $\pm 7\%$ )        | 0.8V ( $\pm 7\%$ )        | -                         |

| TPS37043A5OFDDFRQ1 | 固定                     | 3     | 10ms   | 3.3V ( $\pm 4\%$ )        | 1.8V ( $\pm 4\%$ )        | 1.2V ( $\pm 4\%$ )        | -                         |

| TPS37043BJOFDDFRQ1 | ADJ                    | 3     | 10ms   | 0.8V ( $\pm 4\%$ )        | 0.8V ( $\pm 4\%$ )        | 0.8V ( $\pm 4\%$ )        | -                         |

| TPS37044BJOFDDFR   | ADJ                    | 4     | 10ms   | 0.8V ( $\pm 4\%$ )        |

| TPS37044LJOJDDFR   | ADJ                    | 4     | 35ms   | 0.4V ( $\pm 5\%$ )        | 0.4V ( $\pm 5\%$ )        | 0.8V ( $\pm 5\%$ )        | 0.8V ( $\pm 5\%$ )        |

| TPS37044BJOFDDFRQ1 | ADJ                    | 4     | 10ms   | 0.8V ( $\pm 4\%$ )        |

| TPS37044CJOFDDFRQ1 | ADJ                    | 4     | 10ms   | 0.8V ( $\pm 6\%$ )        |

| TPS37044MJOFDDFRQ1 | ADJ                    | 4     | 10ms   | 0.4V ( $\pm 7\%$ )        | 0.4V ( $\pm 7\%$ )        | 0.8V ( $\pm 7\%$ )        | 0.8V ( $\pm 7\%$ )        |

| TPS37044A4OGDDFRQ1 | 固定                     | 4     | 15ms   | 3.3V ( $\pm 8\%$ )        | 1.8V ( $\pm 4\%$ )        | 1.15V ( $\pm 6\%$ )       | 1.15V ( $\pm 6\%$ )       |

(1) パーセント表示はウインドウの許容誤差を示します。詳細については、図 6-1 を参照してください。

(2) VIT スレッショルド 0.8V と 0.4V は、調整可能なチャネルを示します。

(3) ADJ は、外付け分圧抵抗によって設定される調整可能な電圧スレッショルドを示します。詳細については、セクション 8.1.2 を参照してください。

# TPS3704 X XX X X XXXR

図 4-1. デバイスの命名規則

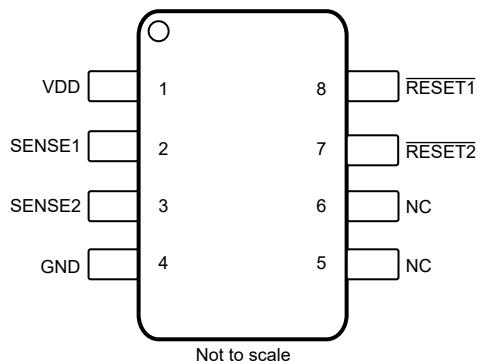

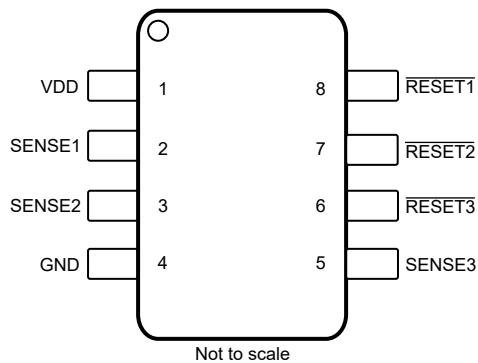

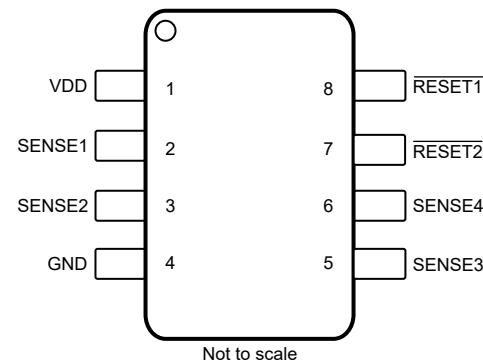

## 5 ピン構成と機能

**図 5-1. SOT-23 8 ピン DDF パッケージ

TPS37042

(上面図)**

**図 5-2. SOT-23 8 ピン DDF パッケージ

TPS37043

(上面図)**

**図 5-3. SOT-23 8 ピン DDF パッケージ

TPS37044

(上面図)**

表 5-1. ピンの機能

| ピン                |          |          |          |          |   | I/O | 説明                                                                                                                                                                                                                                                                                                      |

|-------------------|----------|----------|----------|----------|---|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称                | TPS37041 | TPS37042 | TPS37043 | TPS37044 |   |     |                                                                                                                                                                                                                                                                                                         |

| VDD               | 1        | 1        | 1        | 1        | I |     | 電源入力。0.1μF コンデンサで GND にバイパスします。                                                                                                                                                                                                                                                                         |

| SENSE1            | 2        | 2        | 2        | 2        | I |     | 監視対象電圧に直接接続します。SENSE1 がウインドウ スレッショルドを外れると、RESET1/RESET1 がアサートされます。SENSE1 ピンには外付けコンデンサは必要ありません。TPS37044 (クワッドタイプ) の場合、SENSE1 または SENSE2 のいずれかがウインドウ スレッショルドを外れると、RESET1/RESET1 がアサートされます。ノイズの多いアプリケーションでは、最適な性能を得るために、このピンの近くに 10nF~100nF のセラミックコンデンサを配置する必要があるかもしれません。入力ピンを使用しない場合は、フローティングのままでもかまいません。 |

| SENSE2            | -        | 3        | 3        | 3        | I |     | 監視対象電圧に直接接続します。SENSE2 がウиндウ スレッショルドを外れると、RESET2/RESET2 がアサートされます。SENSE2 ピンには外付けコンデンサは必要ありません。TPS37044 (クワッドタイプ) の場合、SENSE1 または SENSE2 のいずれかがウиндウ スレッショルドを外れると、RESET1/RESET1 がアサートされます。ノイズの多いアプリケーションでは、最適な性能を得るために、このピンの近くに 10nF~100nF のセラミックコンデンサを配置する必要があるかもしれません。入力ピンを使用しない場合は、フローティングのままでもかまいません。 |

| SENSE3            | -        | -        | 5        | 5        | I |     | 監視対象電圧に直接接続します。SENSE3 がウиндウ スレッショルドを外れると、RESET3/RESET3 がアサートされます。SENSE3 ピンには外付けコンデンサは必要ありません。TPS37044 (クワッドタイプ) の場合、SENSE3 または SENSE4 のいずれかがウиндウ スレッショルドを外れると、RESET2/RESET2 がアサートされます。ノイズの多いアプリケーションでは、最適な性能を得るために、このピンの近くに 10nF~100nF のセラミックコンデンサを配置する必要があるかもしれません。入力ピンを使用しない場合は、フローティングのままでもかまいません。 |

| SENSE4            | -        | -        | -        | 6        | I |     | 監視対象電圧に直接接続します。TPS37044 (クワッドタイプ) の場合、SENSE3 または SENSE4 のいずれかがウиндウ スレッショルドを外れると、RESET2/RESET2 がアサートされます。ノイズの多いアプリケーションでは、最適な性能を得るために、このピンの近くに 10nF~100nF のセラミックコンデンサを配置する必要があるかもしれません。入力ピンを使用しない場合は、フローティングのままでもかまいません。                                                                                |

| RESET1/<br>RESET1 | 8        | 8        | 8        | 8        | O |     | SENSE1 が過電圧または低電圧のスレッショルド ウиндウを外れると、RESET1/RESET1 がアサートされます。<br>SENSE1 がウиндウ スレッショルド内に戻った後、RESET1/RESET1 はリセットタイムアウト期間アサートされたままになります。アクティブ LOW、オープンドレン出力には、外付けのプルアップ抵抗が必要です。TPS37044 の場合、SENSE1 または SENSE2 のいずれかがウиндウ スレッショルドを外れると、RESET1/RESET1 がアサートされます。このピンを使用しない場合は、フローティングのままでもかまいません。         |

| RESET2/<br>RESET2 | -        | 7        | 7        | 7        | O |     | SENSE2 が過電圧または低電圧のスレッショルド ウиндウを外れると、RESET2/RESET2 がアサートされます。<br>SENSE2 がウиндウ スレッショルド内に戻った後、RESET2/RESET2 はリセットタイムアウト期間アサートされたままになります。アクティブ LOW、オープンドレン出力には、外付けのプルアップ抵抗が必要です。TPS37044 の場合、SENSE3 または SENSE4 のいずれかがウиндウ スレッショルドを外れると、RESET2/RESET2 がアサートされます。このピンを使用しない場合は、フローティングのままでもかまいません。         |

| RESET3/<br>RESET3 | -        | -        | 6        | -        | O |     | SENSE3 が過電圧または低電圧のスレッショルド ウиндウを外れると、RESET3/RESET3 がアサートされます。<br>SENSE3 がウindh ウ スレッショルド内に戻った後、RESET3/RESET3 はリセットタイムアウト期間アサートされたままになります。アクティブ LOW、オープンドレン出力には、外付けのプルアップ抵抗が必要です。このピンを使用しない場合は、フローティングのままでもかまいません。                                                                                       |

表 5-1. ピンの機能 (続き)

| ピン  |            |          |          |          | I/O | 説明   |

|-----|------------|----------|----------|----------|-----|------|

| 名称  | TPS37041   | TPS37042 | TPS37043 | TPS37044 |     |      |

| GND | 4          | 4        | 4        | 4        | -   | グランド |

| NC  | 3, 5, 6, 7 | 5, 6     | -        | -        | -   | 接続なし |

## 6 仕様

### 6.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|                   |                                                           |              | 最小値      | 最大値 | 単位 |

|-------------------|-----------------------------------------------------------|--------------|----------|-----|----|

| 電圧                | $V_{DD}$                                                  |              | -0.3     | 6.5 | V  |

|                   | $V_{RESET1}$ 、 $V_{RESET2}$ 、 $V_{RESET3}$                |              | -0.3     | 6.5 | V  |

|                   | $V_{SENSE1}$ 、 $V_{SENSE2}$ 、 $V_{SENSE3}$ 、 $V_{SENSE4}$ |              | -0.3     | 6.5 | V  |

| 電流                | $I_{RESET1}$ 、 $I_{RESET2}$ 、 $I_{RESET3}$ SINK           |              | $\pm 20$ |     | mA |

| 温度 <sup>(2)</sup> | 連続総許容損失                                                   | 「熱に関する情報」を参照 |          |     |    |

|                   | 動作時の接合部温度、 $T_J$                                          |              | -40      | 150 | °C |

|                   | 自由気流での動作温度 ( $T_A$ )                                      |              | -40      | 150 | °C |

|                   | 保管温度、 $T_{stg}$                                           |              | -65      | 150 | °C |

(1) 絶対最大定格 (AMR) を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみに関するものであり、絶対最大定格において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗黙的に示すものではありません。AMR 定格の状態が長時間続くと、デバイスの信頼性に影響を与える可能性があります。

(2) このデバイスの消費電力は低いため、 $T_J = T_A$  と想定されます。

### 6.2 ESD 定格

|             |       |                                                        |  | 値          | 単位 |

|-------------|-------|--------------------------------------------------------|--|------------|----|

| $V_{(ESD)}$ | 静電気放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>   |  | $\pm 2000$ | V  |

|             |       | デバイス帶電モデル (CDM)、JEDEC 仕様 JESD22-C101 準拠 <sup>(2)</sup> |  | $\pm 750$  |    |

(1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 制御プロセスで安全な製造が可能であると記載されています。

(2) JEDEC のドキュメント JEP157 には、250V CDM であれば標準的な ESD 制御プロセスにより安全な製造が可能であると記載されています。

### 6.3 推奨動作条件

|                                                 |            | 最小値 | 公称値 | 最大値 | 単位 |

|-------------------------------------------------|------------|-----|-----|-----|----|

| $V_{DD}$                                        | 電源ピンの電圧    | 1.7 | 6.0 | 6.0 | V  |

| $V_{SENSE1, 2, 3, 4}$                           | 入力ピンの電圧    | 0   | 6.0 | 6.0 | V  |

| $V_{RESET1}$ 、 $V_{RESET2}$ 、 $V_{RESET3}$      | 出力ピン電圧     | 0   | 6.0 | 6.0 | V  |

| $I_{RESET1}$ 、 $I_{RESET2}$ 、 $I_{RESET3}$ SINK | 出力ピンの電流シンク | 0.3 | 5   | 5   | mA |

| $T_A$                                           | 自由気流での動作温度 | -40 | 125 | 125 | °C |

### 6.4 热に関する情報

| 热評価基準 <sup>(1)</sup> |                     | TPS3704x | 単位   |

|----------------------|---------------------|----------|------|

|                      |                     | DDF      |      |

|                      |                     | ピン       |      |

| $R_{\theta JA}$      | 接合部から周囲への熱抵抗        | 121.5    | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース (上面) への熱抵抗 | 60.6     | °C/W |

| $R_{\theta JB}$      | 接合部から基板への熱抵抗        | 42.3     | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ    | 2.2      | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ    | 42.1     | °C/W |

| 熱評価基準 (1)            |                   | TPS3704x | 単位   |

|----------------------|-------------------|----------|------|

|                      |                   | DDF      |      |

|                      |                   | ピン       |      |

| $R_{\theta JC(bot)}$ | 接合部からケース(底面)への熱抵抗 | 該当なし     | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体およびICパッケージの熱評価基準』アプリケーション・レポートを参照してください。

## 6.5 電気的特性

$1.7V \leq V_{DD} \leq 6.0V$ 、 $\overline{RESETx}$  電圧 ( $V_{RESETx}$ ) =  $10k\Omega$  から  $V_{DD}$ 、 $\overline{RESETx}$  負荷 =  $10pF$ 、および自由気流での動作温度範囲 –  $40^{\circ}\text{C} \sim 125^{\circ}\text{C}$  (特に記述のない限り)。代表値は  $T_A = 25^{\circ}\text{C}$ 、代表条件は  $V_{DD} = 3.3V$ 。

| パラメータ                 | テスト条件                                   | 最小値                                                     | 標準値  | 最大値  | 単位            |

|-----------------------|-----------------------------------------|---------------------------------------------------------|------|------|---------------|

| $V_{DD}$              | 電源電圧                                    | 1.7                                                     | 6.0  |      | V             |

| UVLO                  | 低電圧誤動作防止 (1)                            | $V_{DD}$ が $1.7V$ 未満で下降する                               | 1.2  | 1.4  | 1.6           |

| UVLO(HYS)             | UVLO ヒステリシス (2)                         | $V_{DD}$ が $1.7V$ 未満で上昇する                               | 65   |      | mV            |

| $V_{POR}$             | パワー オン リセット電圧 (3)                       | $V_{OL(\text{MAX})} = 0.3V$ , $I_{OUT} = 15\mu\text{A}$ | 0.7  |      | V             |

| $V_{IT}$ 範囲           | スレッショルドのプログラミング範囲                       | 0.4                                                     | 5.55 |      | V             |

| $V_{IT- (\text{UV})}$ | UV 精度 ( $25^{\circ}\text{C}$ )          |                                                         | 0.1  |      | %             |

| $V_{IT+ (\text{OV})}$ | OV 精度 ( $25^{\circ}\text{C}$ )          |                                                         | 0.1  |      | %             |

| TOL_min               | 許容誤差プログラミングの最小値                         |                                                         | 3    |      | %             |

| TOL_max               | 許容誤差プログラミングの最大値                         |                                                         | 11   |      | %             |

| THR RES Low           | スレッショルドのプログラミング分解能 Low                  | $V_{IT} \leq 0.8V$                                      | 20   |      | mV / ステップ     |

| THR RES Mid           | スレッショルドのプログラミング分解能 Mid                  | $0.8V < V_{IT} \leq 4.0V$                               | 0.5  |      | % / ステップ      |

| THR RES High          | スレッショルドのプログラミング分解能 High                 | $V_{IT} > 4.0V$                                         | 20   |      | mV / ステップ     |

| $V_{IT}$              | 許容誤差を含む絶対スレッショルドの精度                     | $V_{IT} < 0.8V$                                         | -1.6 | 1.6  | %             |

| $V_{IT}$              | 許容誤差を含む絶対スレッショルドの精度                     | $V_{IT} = 0.8V \sim 5.55V$                              | -1   | 1    | %             |

| $V_{HYS}$             | $V_{IT} < 0.80V$                        |                                                         | 1.1  | 1.4  | 1.7           |

| $V_{HYS}$             | $V_{IT} \geq 0.80V$                     |                                                         | 0.40 | 0.75 | 1             |

| $I_{DD}$              | TPS3704x                                | $V_{DD} \leq 6.0V$                                      | 5.5  | 15   | $\mu\text{A}$ |

| $I_{SENSEx}$          | 入力電流、SENSEx ピン                          | $V_{SENSEx} = 5.5V$                                     | 1    | 2.5  | $\mu\text{A}$ |

| $I_{SENSE\_ADJ}$      | 入力電流、SENSE ピン (バイパスの内部分圧抵抗) - 調整可能バージョン | $V_{SENSEx} = 5.5V$                                     |      | 350  | nA            |

| $V_{OL}$              | Low レベル出力電圧                             | $V_{DD} = 1.7V$ , $I_{SINK} = 0.4mA$                    | 300  |      | mV            |

| $V_{OL}$              | Low レベル出力電圧                             | $V_{DD} = 2V$ , $I_{SINK} = 3mA$                        | 300  |      | mV            |

| $V_{OL}$              | Low レベル出力電圧                             | $V_{DD} = 6.0V$ , $I_{SINK} = 5mA$                      | 300  |      | mV            |

| $I_{(lkg)}$           | オープンドレイン出力リード电流                         | $V_{DD} = V_{RESETx} = 6.0V$                            | 350  |      | nA            |

(1)  $V_{DD}$  が UVLO 未満になると、 $\overline{RESETx}$  ピンは Low に駆動されます。

(2) ヒステリシスは、トリポイント ( $V_{IT- (\text{UV})}$ 、 $V_{IT+ (\text{OV})}$ ) と関連しています。

(3)  $V_{POR}$  は、制御された出力状態の最小  $V_{DD}$  電圧レベルです。スルーレート =  $100mV/\mu\text{s}$

## 6.6 タイミング要件

$1.7V \leq V_{DD} \leq 6.0V$ 、 $\overline{\text{RESETx}}$  電圧 ( $V_{\text{RESETx}}$ ) =  $10k\Omega$  から  $V_{DD}$ 、 $\overline{\text{RESETx}}$  負荷 =  $10pF$ 、および自由気流での動作温度範囲 –  $40^{\circ}\text{C} \sim 125^{\circ}\text{C}$  (特に記述のない限り)。代表値は  $T_A = 25^{\circ}\text{C}$ 、代表条件は  $V_{DD} = 3.3V$ 。

| パラメータ          |                                         | テスト条件                                 | 最小値 | 公称値   | 最大値 | 単位            |

|----------------|-----------------------------------------|---------------------------------------|-----|-------|-----|---------------|

| $t_D$          | リセット解放時間遅延                              | 固定遅延オプション $t_D < 4ms$ 、オーバードライブ = 10% | -40 | $t_D$ | 40  | %             |

| $t_D$          | リセット解放時間遅延                              | 固定遅延オプション $t_D > 5ms$ 、オーバードライブ = 10% | -30 | $t_D$ | 30  | %             |

| $t_{PD}$       | 伝搬検出遅延 <sup>(1)</sup>                   | 固定遅延時間 $t_D > 1ms$ 、オーバードライブ 10%      |     |       | 10  | $\mu\text{s}$ |

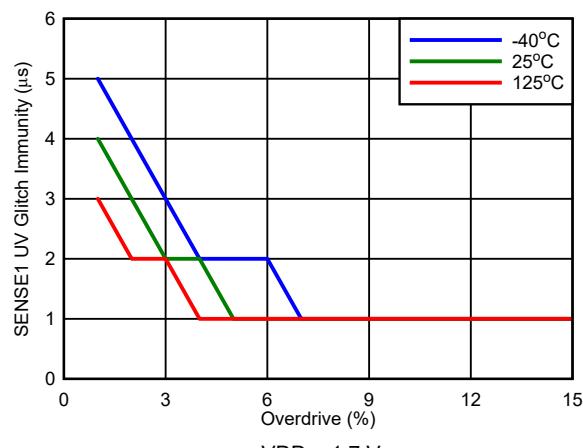

| $t_{GI(VIT-)}$ | グリッヂ耐性低電圧 (5% オーバードライブ) <sup>(2)</sup>  |                                       |     | 2     |     | $\mu\text{s}$ |

| $t_{GI(VIT+)}$ | グリッヂ耐性過電圧 (5% オーバードライブ) <sup>(2)</sup>  |                                       |     | 2     |     | $\mu\text{s}$ |

| $t_R$          | 出力立ち上がり (プッシュアップ) <sup>(2) (3)</sup>    |                                       |     | 25    |     | $\text{ns}$   |

| $t_R$          | 出力立ち上がり時間 (オープンドレイン) <sup>(2) (3)</sup> |                                       |     | 2.2   |     | $\mu\text{s}$ |

| $t_F$          | 出力立ち下がり時間 <sup>(2) (3)</sup>            |                                       |     | 0.2   |     | $\mu\text{s}$ |

| $t_{STRT}$     | スタートアップ遅延 <sup>(4)</sup>                |                                       |     | 1     |     | $\text{ms}$   |

(1) スレッショルドトリップ ポイント ( $V_{IT-(UV)}$  または  $V_{IT+(OV)}$ ) から  $\overline{\text{RESETx}}$   $V_{OL}$  電圧までの  $T_{PD}$  測定値

(2) スレッショルドから 5% オーバードライブオーバードライブ % =  $[(V_{SENSEX} - V_{IT}) / V_{IT}]$ 、ここで  $V_{IT}$  は  $V_{IT-(UV)}$  または  $V_{IT+(OV)}$  を表します。

(3) 立ち上がり時間は  $V_{OL}$  から  $V_{OH}$  または ( $V_{\text{RESETx}}$ ) へ、立ち下がり時間は  $V_{OH}$  または ( $V_{\text{RESETx}}$ ) から  $V_{OL}$  へ出力が遷移します。

(4) パワーオン シーケンスの間、出力が適切な状態になる前に、 $V_{DD}$  が少なくとも  $t_{STRT} + t_D$  の間、 $V_{DD(\text{MIN})}$  以上でなければなりません。 $VDD$  が  $V_{DD(\text{MIN})}$  と  $VPOR$  の間であるとき、 $\overline{\text{RESETx}}$  ピンはアクティブになります。

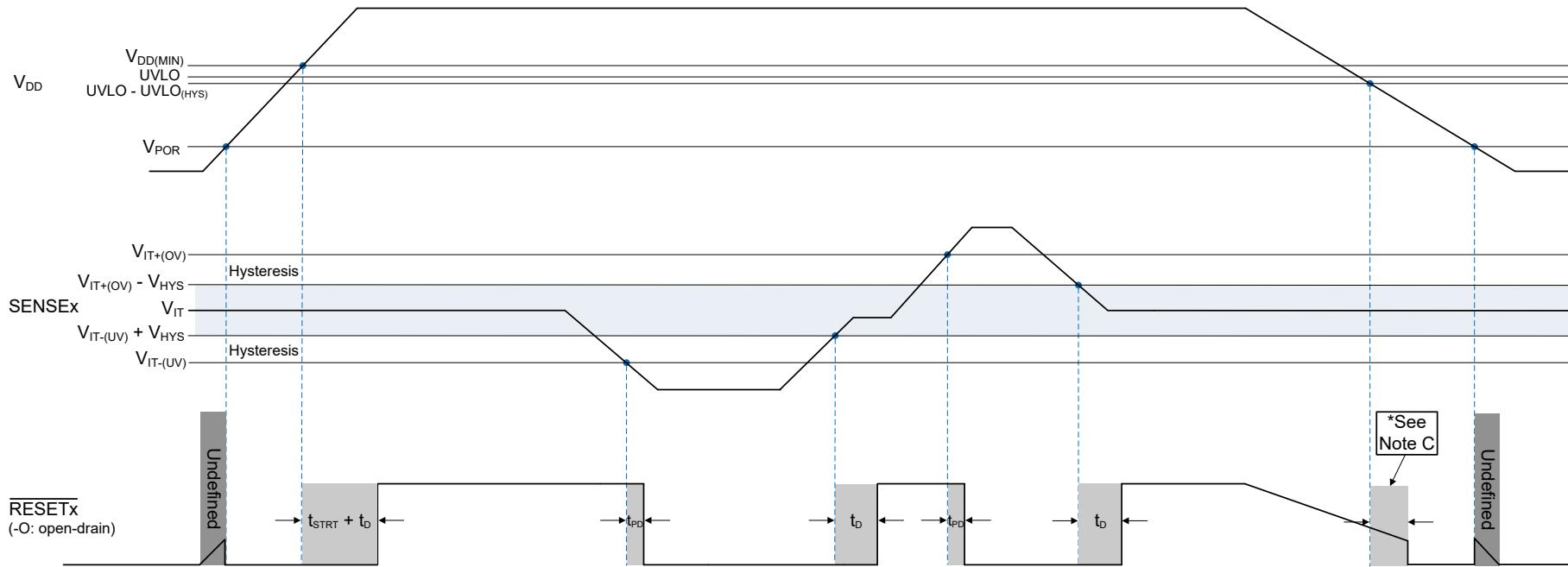

## 6.7 タイミング図

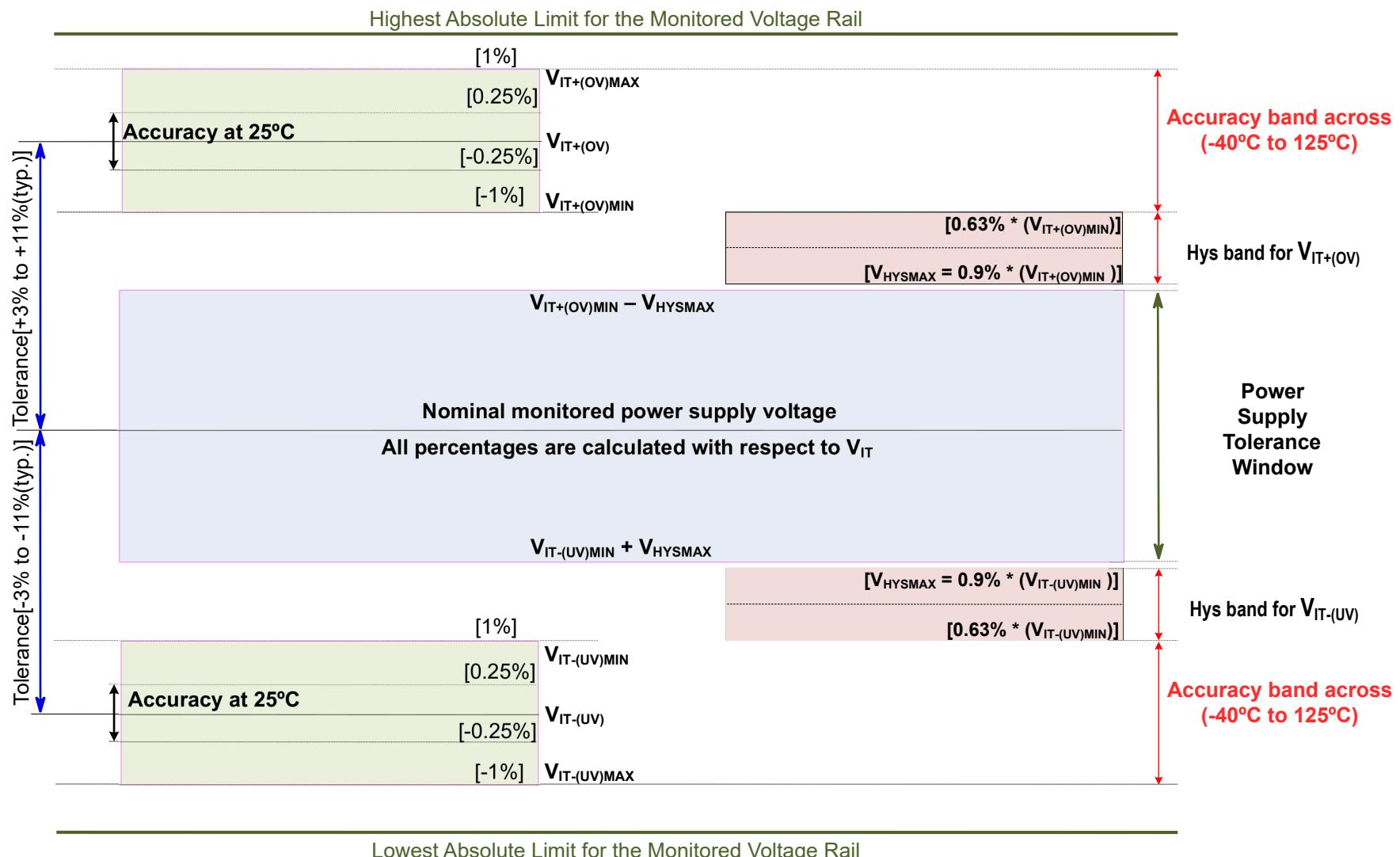

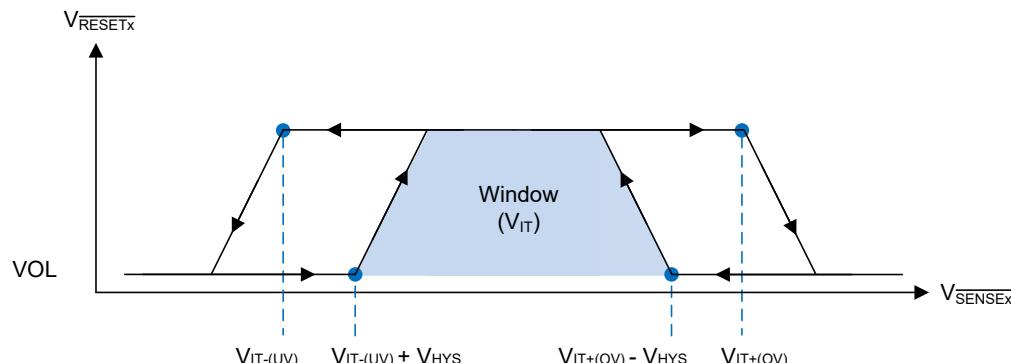

図 6-1. 電圧スレッショルドとヒステリシスの精度

- A. オープンドレインのタイミング図では、**RESETx**/**RESETx** ピンが外付けのプルアップ抵抗を介して **VDD** に接続されていることを想定しています。

- B. 図 6-2 は、**VDD** の立ち下がりスルーレートが遅いか、または **VDD** の減衰時間が伝搬検出遅延 ( $t_{PD}$ ) 時間よりもはるかに長いことを示していることに注意してください。

- C. **RESETx**/**RESETx** は、**VDD** が **UVLO-UVLO<sub>(HYS)</sub>** スレッショルドを下回ると、代表値 100  $\mu$ s の時間遅延後にアサートされます。

図 6-2. SENSEx のタイミング図

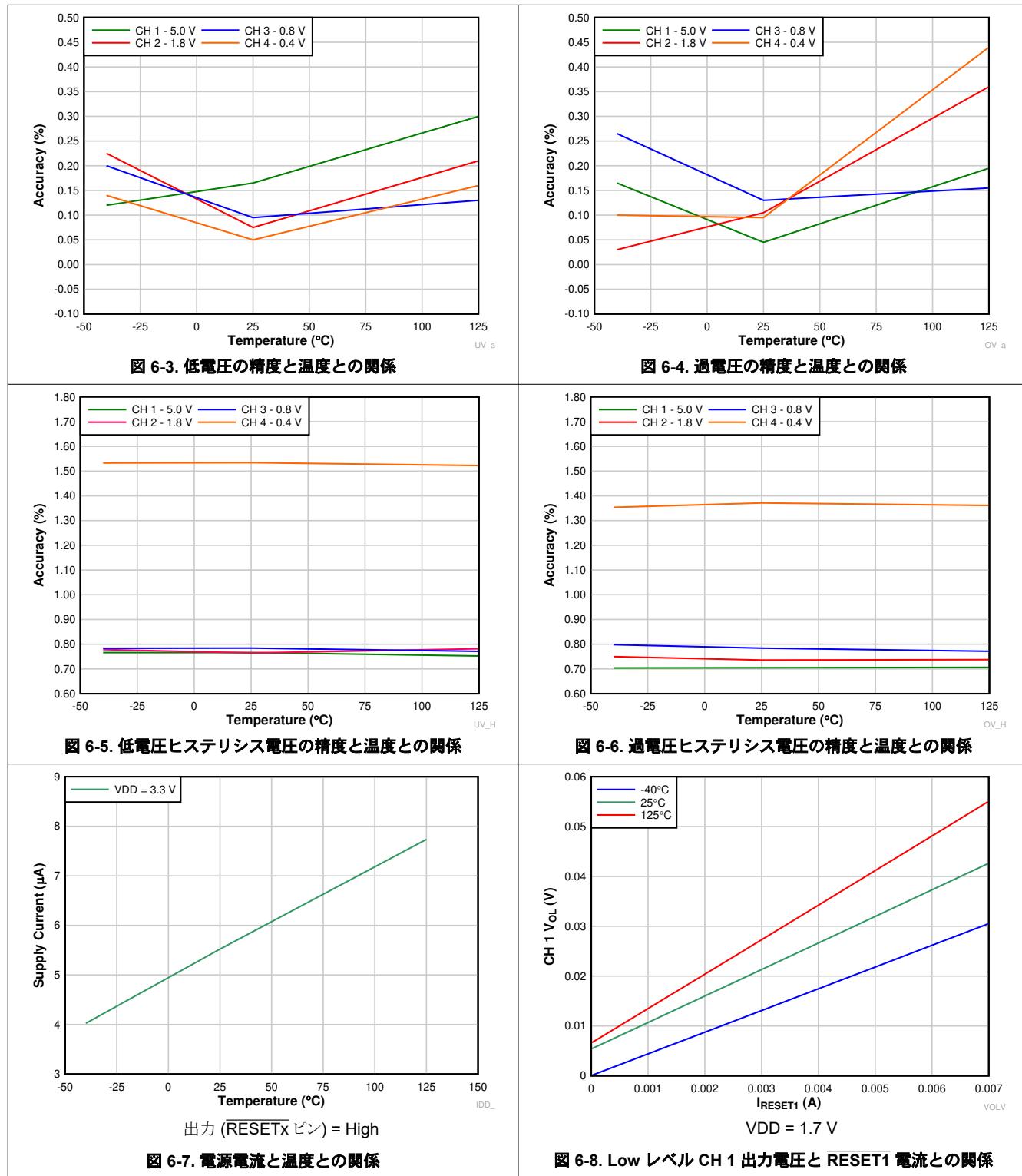

## 6.8 代表的特性

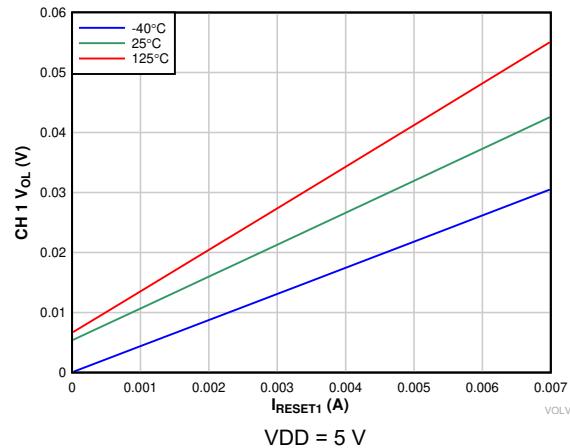

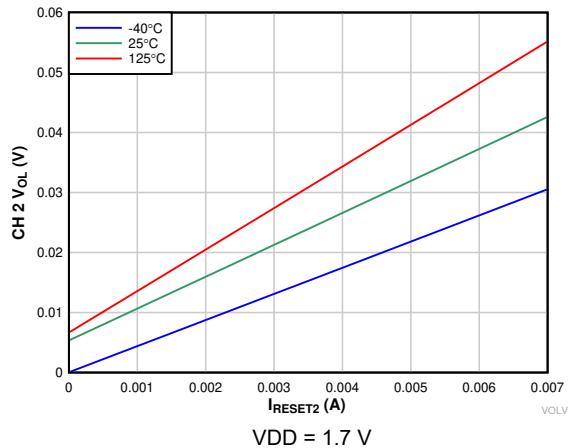

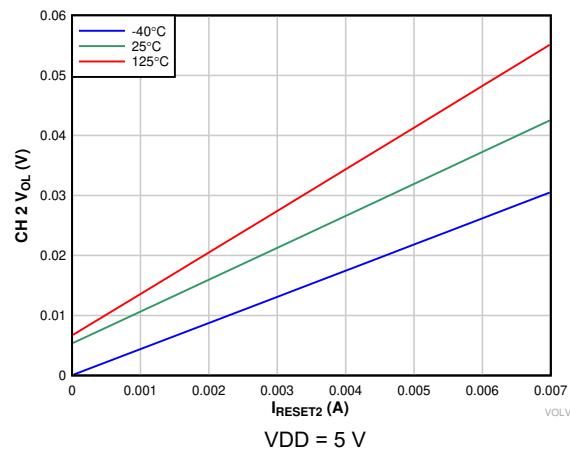

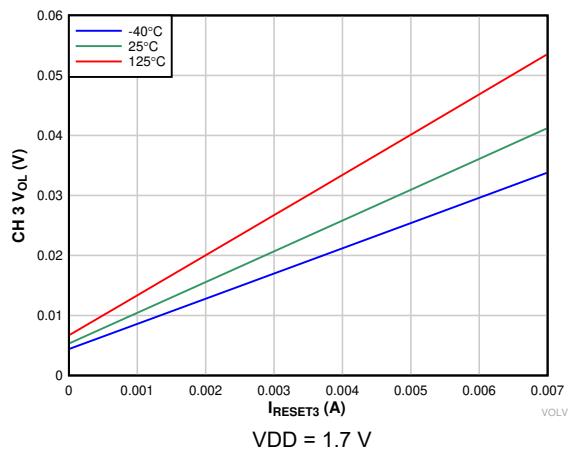

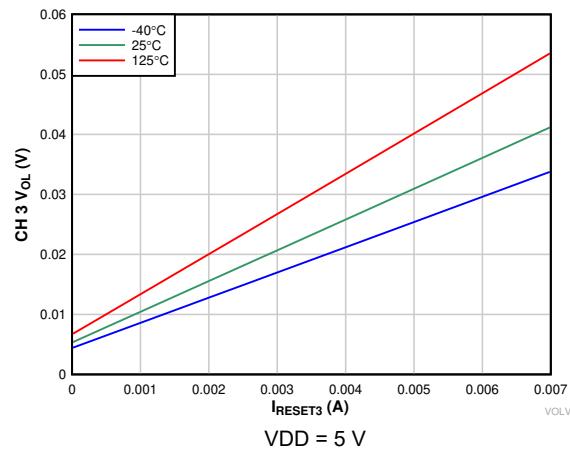

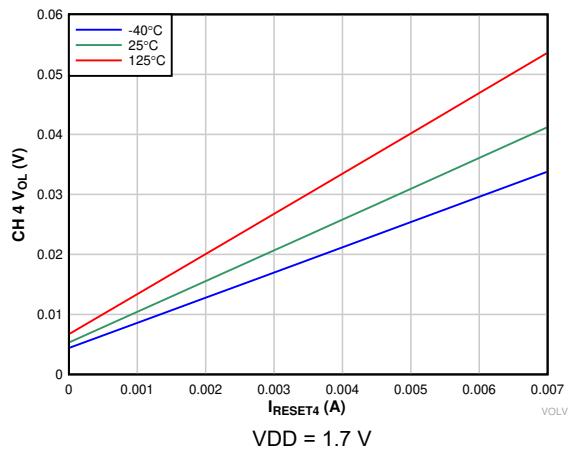

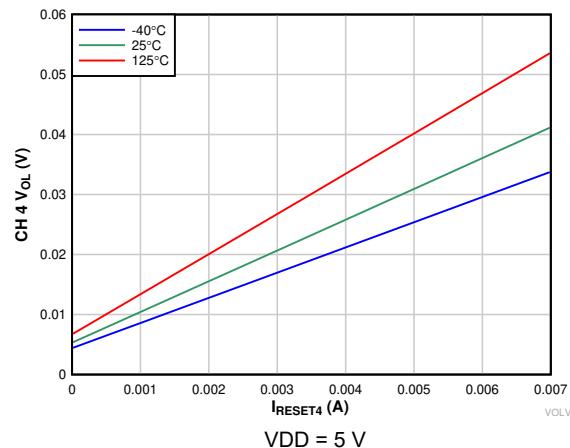

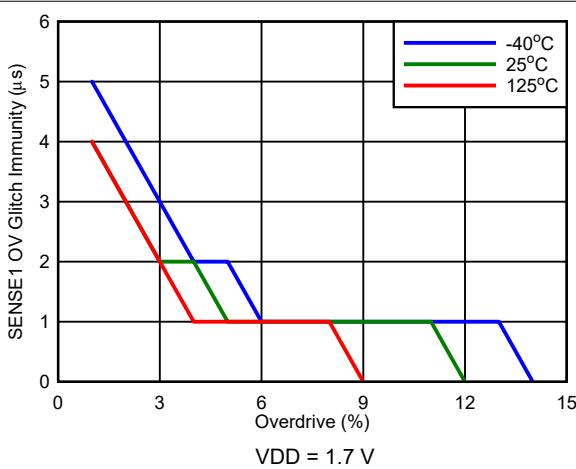

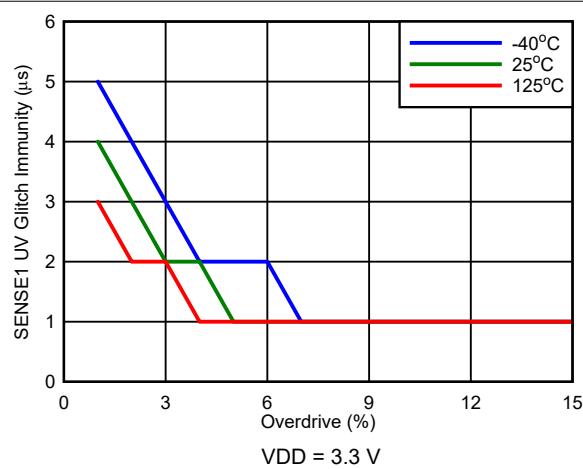

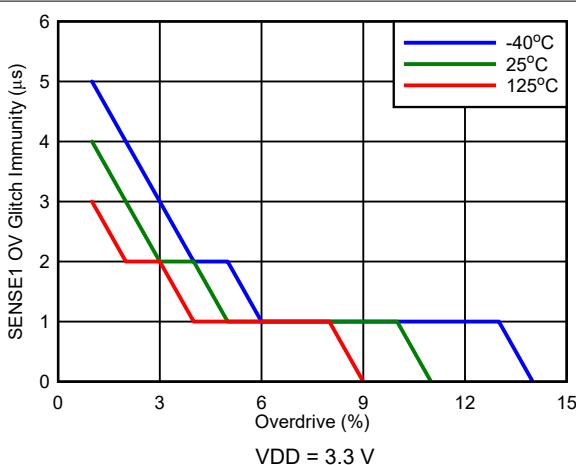

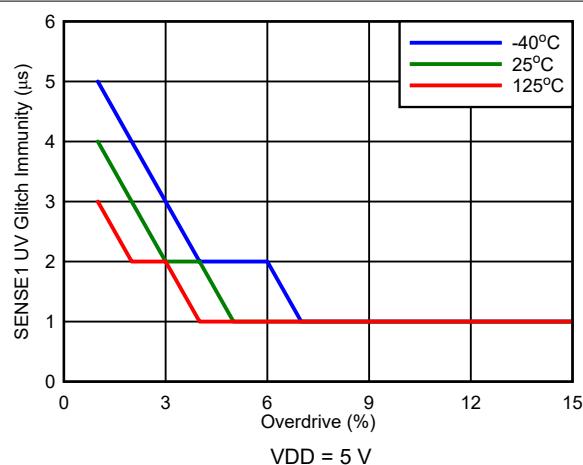

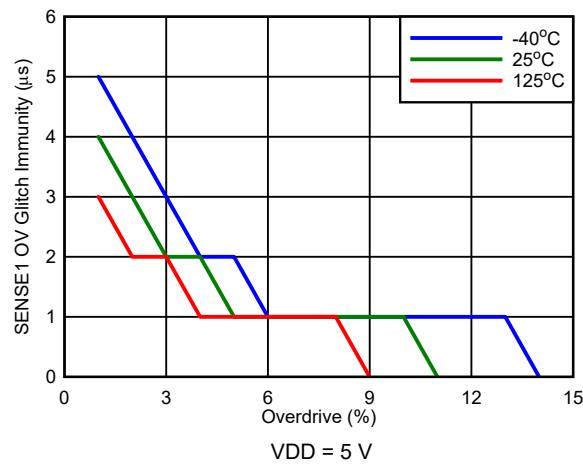

このセクションでは、TPS3704x デバイスの代表的特性を示します。テスト条件は、特に記述のない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{DD} = 3.3\text{V}$ 、 $R_{pull-up} = 10\text{k}\Omega$ 、 $C_{LOAD} = 50\text{pF}$  になります。

## 6.8 代表的特性 (続き)

このセクションでは、TPS3704x デバイスの代表的特性を示します。テスト条件は、特に記述のない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{DD} = 3.3\text{V}$ 、 $R_{pull-up} = 10\text{k}\Omega$ 、 $C_{LOAD} = 50\text{pF}$  になります。

図 6-9. Low レベル CH 1 出力電圧と RESET1 電流との関係

図 6-10. Low レベル CH 2 出力電圧と RESET2 電流との関係

図 6-11. Low レベル CH 2 出力電圧と RESET3 電流との関係

図 6-12. Low レベル CH 3 出力電圧と RESET4 電流との関係

図 6-13. Low レベル CH 3 出力電圧と RESET5 電流との関係

図 6-14. Low レベル CH 4 出力電圧と RESET6 電流との関係

## 6.8 代表的特性 (続き)

このセクションでは、TPS3704x デバイスの代表的特性を示します。テスト条件は、特に記述のない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{DD} = 3.3\text{V}$ 、 $R_{pull-up} = 10\text{k}\Omega$ 、 $C_{LOAD} = 50\text{pF}$  になります。

図 6-15. Low レベル CH 4 出力電圧と RESET4 電流との関係

図 6-16. SENSE1 グリッチ耐性 ( $V_{IT}$ ) とオーバードライブとの関係

図 6-17. SENSE1 グリッチ耐性 ( $V_{IT+}$ ) とオーバードライブとの関係

図 6-18. SENSE1 グリッチ耐性 ( $V_{IT}$ ) とオーバードライブとの関係

図 6-19. SENSE1 グリッチ耐性 ( $V_{IT+}$ ) とオーバードライブとの関係

図 6-20. SENSE1 グリッチ耐性 ( $V_{IT}$ ) とオーバードライブとの関係

## 6.8 代表的特性 (続き)

このセクションでは、TPS3704x デバイスの代表的特性を示します。テスト条件は、特に記述のない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{DD} = 3.3\text{V}$ 、 $R_{pull-up} = 10\text{k}\Omega$ 、 $C_{LOAD} = 50\text{pF}$  になります。

図 6-21. SENSE1 グリッチ耐性 ( $V_{IT+}$ ) とオーバードライブとの関係

## 7 詳細説明

### 7.1 概要

TPS3704x は、クワッド、トリプル、デュアルの高精度電圧スーパーバイザ ファミリで、各チャネルに過電圧および低電圧の検出機能を搭載しています。TPS3704x は高精度のウインドウ レッショルド電圧を特長とし、上限レッショルドと下限レッショルドを対称または非対称の許容誤差に合わせてカスタマイズできます。センス電圧が過電圧レッショルドおよび低電圧レッショルドを外れたとき、PS3704x のリセット信号は、フォルト検出遅延時間 ( $t_{PD}$  = 最大 10μs) でアサートされます。

TPS3704x には、デバイス内部で過電圧レッショルドおよび低電圧レッショルドを設定するための抵抗が含まれています。これらの内部抵抗によって、部品点数が削減でき、外部抵抗の精度を考慮したマージンを追加する必要がないため、設計を大幅に簡略化できます。TPS3704x の高い統合度によって、どんなアプリケーションにもコンパクトなソリューションが可能になります。

TPS3704x は、あらゆる電圧レールを高分解能 ( $V_{IT} \leq 0.8V$ 、20mV ステップ /

$V_{IT} > 0.8V$ 、0.5% または 20mV ステップのいずれか低い方) で監視できます。TPS3704x の各チャネルは、ウインドウ、OV、または UV のスーパーバイザとして個別に構成できます。また、各チャネルの  $V_{IT}$  レッショルド電圧は非対称に設定できます。たとえば、過電圧スーパーバイザとして構成されたチャネルは許容誤差 +5% で設定でき、低電圧チャネルスーパーバイザは許容誤差 -4% でプログラムできます。ウインドウスーパーバイザが構成されている場合、電圧レッショルドの許容誤差は対称型と非対称型のいずれかになります。

TPS3704x は、20μs～1200ms の範囲の固定リセット遅延時間 ( $t_D$ ) オプションを備えており、15μA (最大値) の超低  $I_Q$  電流を維持しながら、最大 4 つのチャネルを監視できます。

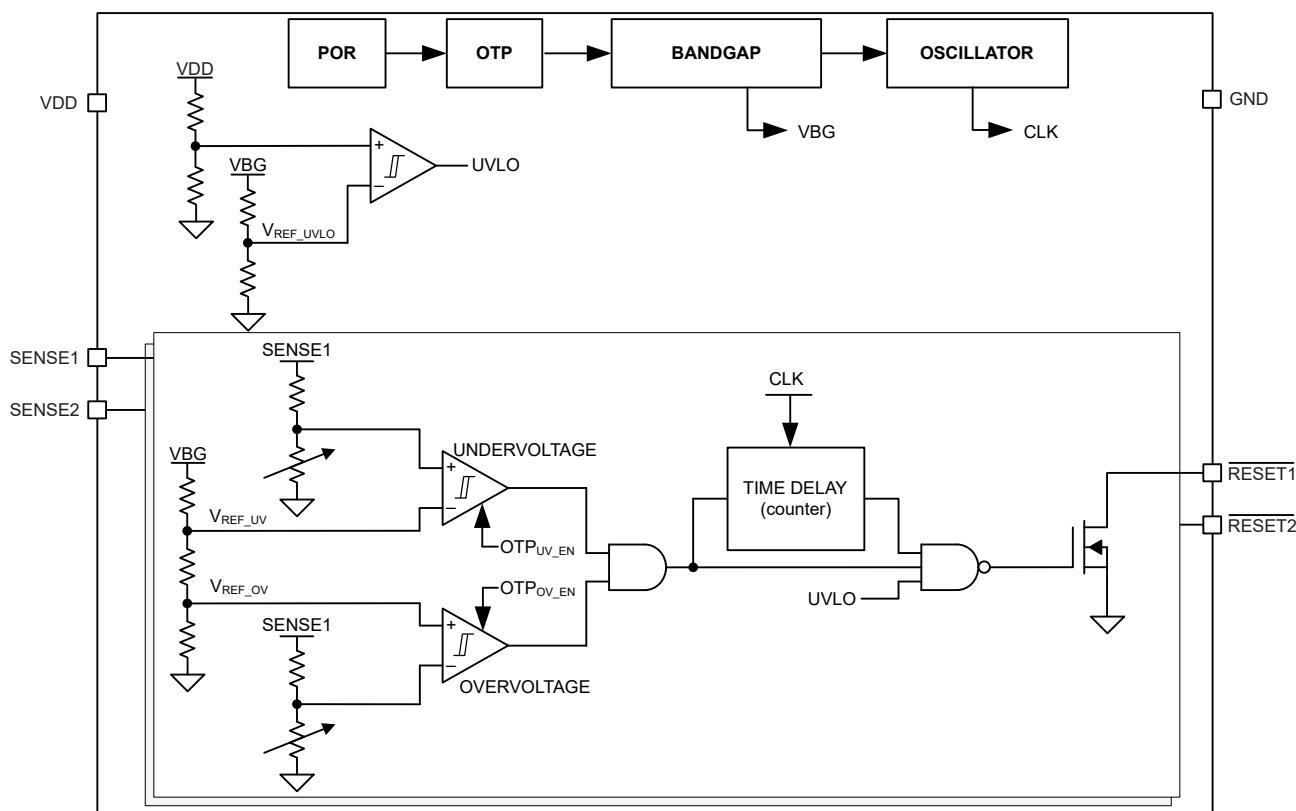

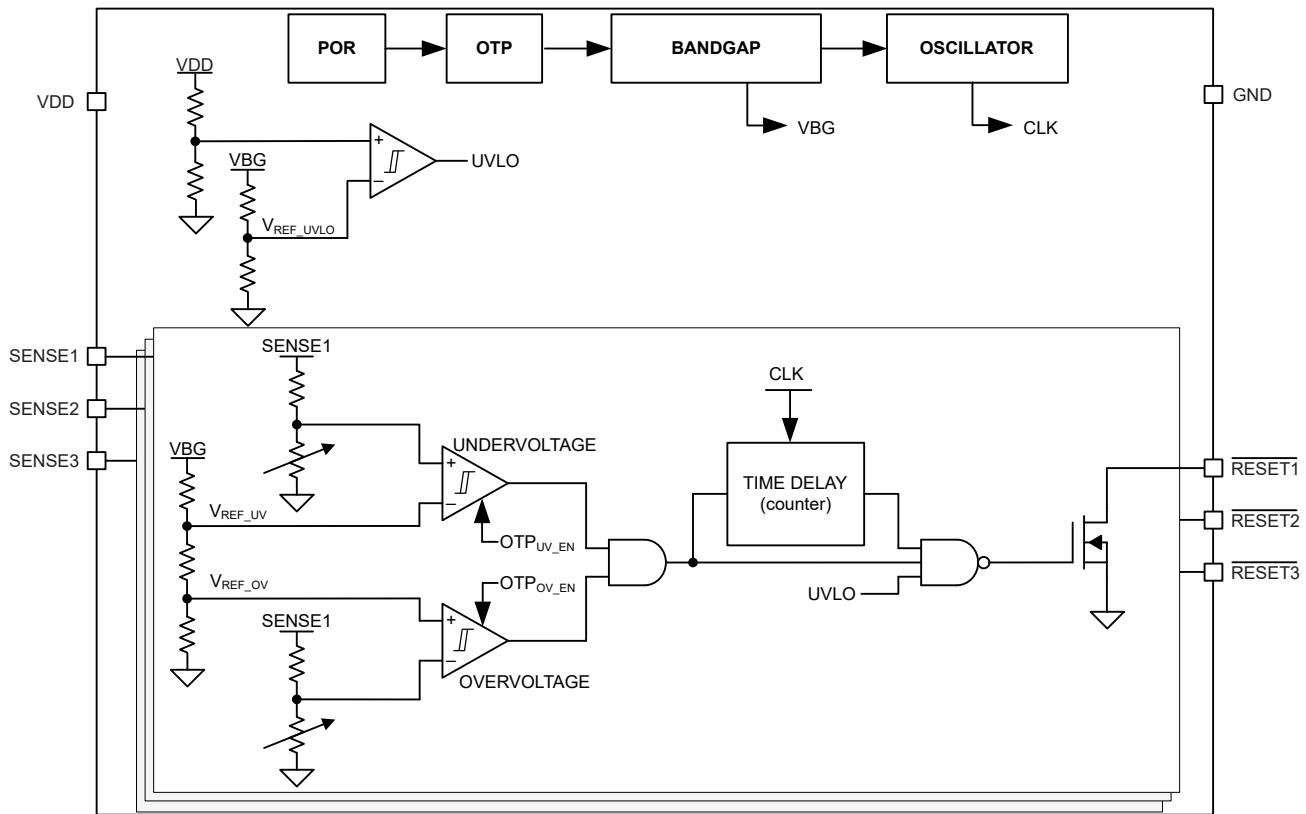

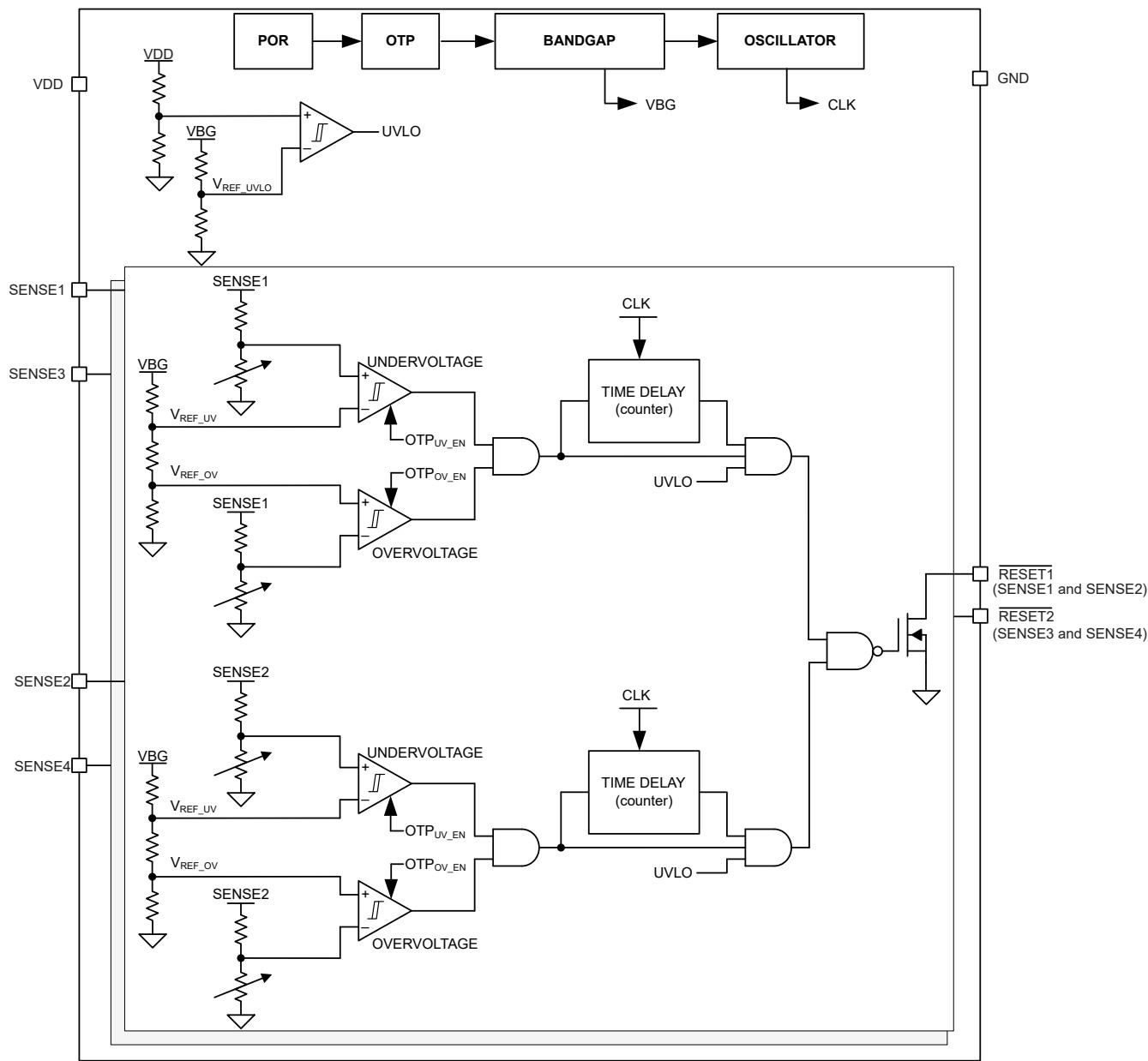

### 7.2 機能ブロック図

図 7-1. TPS37042 デュアル・チャネルの機能ブロック図

図 7-2. TPS37043 トリプル・チャネルの機能ブロック図

図 7-3. TPS37044 クワッド・チャネルの機能ブロック図

\* 利用可能な電圧、ウィンドウ許容誤差、時間遅延、および UV/OV スレッショルドのオプションについては、表 9-2 を参照してください。

## 7.3 機能説明

### 7.3.1 VDD

TPS3704x は、1.7V~6V の入力電源電圧範囲で動作するよう設計されており、内部コンパレータによって SENSE<sub>x</sub> ピンが監視されます。また VDD は、内部バンドギャップ、内部レギュレータ、ステートマシン、バッファ、およびその他の制御ブロックの電源としても機能します。VDD > V<sub>POR</sub> のとき、リセット信号は既知の状態になります。低電圧誤動作防止機能により、VDD が VDD 最小電圧を下回ったとき、リセット出力が強制的にアサートされます。

このデバイスに VDD コンデンサは必要ありませんが、入力電源にノイズがある場合は、VDD ピンと GND ピンの間に 0.1μF~1μF のバイパスコンデンサを配置し、デバイスが正常に電源投入されるのに十分な電荷を確保するのが優れた

設計手法といえます。スタートアップ遅延 ( $t_{START} + t_D$ ) の開始と、デバイスが完全に機能するためには、VDD が  $V_{DD(MIN)}$  以上である必要があります。

### 7.3.2 SENSEx 入力

SENSEx 入力は、使用するデバイス電源電圧に関係なく、0V~5.55V の電源レールを監視できます。重要な電圧レベルやプッシュボタン入力の監視には、SENSEx ピンを使用します。このピンの電圧が  $V_{IT-(UV)}$  を下回るか、 $V_{IT+(OV)}$  を上回ると、RESETx/RESETx がアサートされます。SENSEx ピンの電圧が正のスレッショルド電圧  $V_{IT-(UV)} + V_{HYS}$  を上回るか、負のスレッショルド電圧  $V_{IT+(OV)} - V_{HYS}$  を下回ると、設定された RESETx/RESETx 遅延時間経過後に RESETx/RESETx がディアサートされます。

内部コンパレータにはヒステリシスが内蔵されているため、監視対象の電圧レールにわずかな変化があっても、RESETx/RESETx のアサートおよびディアサートが確実に行われるようになっています。

TPS3704x は、コンパレータと高精度基準電圧およびトリムされた分圧抵抗を組み合わせています。この構成によって、すべての抵抗許容誤差が精度と性能仕様において考慮されているため、デバイスの精度が最適化されます。TPS3704x デバイスは、SENSEx ピンで発生する短い過渡に対して比較的の耐性があります。大半の場合必要ではありませんが、ノイズの多いアプリケーションでは、SENSEx 入力に 10nF~100nF のバイパスコンデンサを配置して、監視対象の信号の過渡電圧に対する感度を低減するのが優れたアナログ設計手法といえます。

#### 7.3.2.1 SENSEx ピンの電圧過渡耐性

TPS3704x は、入力 SENSEx ピンで発生する短い電圧過渡スパイクに耐性があります。過渡に対する感度は、過渡の持続時間とオーバードライブ（振幅）の両方に依存します。

オーバードライブは、 $V_{SENSEx}$  が指定されたスレッショルドをどれだけ上回るかで定義され、オーバードライブが小さいほど (RESETx/RESETx) 出力の応答が遅くなることを知っておくことが重要です。スレッショルド オーバードライブは、式 1 に示すように、対象のスレッショルドに対するパーセンテージとして計算されます。

$$\text{オーバードライブ \%} = |(V_{SENSEx} - (V_{IT-(UV)} \text{ または } V_{IT+(OV)})) / V_{IT} (\text{公称}) \times 100\%| \quad (1)$$

ここで

- $V_{SENSEx}$ : SENSEx ピンの電圧

- $V_{IT}$  (公称): 公称スレッショルド電圧

- $V_{IT-(UV)}$  および  $V_{IT+(OV)}$ : 実際の低電圧トリップ電圧または過電圧トリップ電圧

#### 7.3.2.1.1 SENSEx ヒステリシス

過電圧コンパレータおよび低電圧コンパレータには、ノイズ耐性と安定動作が保証されるヒステリシスが内蔵されています。たとえば、SENSEx ピンの電圧が  $V_{IT-(UV)}$  を下回るか、 $V_{IT+(OV)}$  を上回ると、RESETx/RESETx がアサートされます。SENSEx ピンの電圧が正のスレッショルド電圧と負のスレッショルド電圧の間にある場合、RESETx/RESETx は設定された RESETx/RESETx 遅延時間経過後にディアサートされます。図 7-4 に、 $V_{IT-(UV)}$ 、 $V_{IT+(OV)}$  とヒステリシス電圧 ( $V_{HYS}$ ) の関係を示します。

図 7-4. SENSEx ピンのヒステリシス

### 7.3.3 $\overline{\text{RESETx}}/\text{RESETx}$

代表的な TPS3704x アプリケーションでは、 $\overline{\text{RESETx}}/\text{RESETx}$  出力は、プロセッサ [デジタル信号プロセッサ (DSP)、特定用途向け集積回路 (ASIC)、その他のプロセッサ タイプなど] のリセット入力またはイネーブル入力、または電圧レギュレータ [DC/DC コンバータ、低ドロップアウトレギュレータ (LDO) など] のイネーブル入力に接続されます。

TPS3704x にはオープンドレインのアクティブ LOW 出力があり、これらのラインを必要な電圧ロジックまで High に保持するために外付けプルアップ抵抗が必要です。外付けプルアップ抵抗を適切な電圧レールに接続し、出力を適切なインターフェイス電圧レベルで他のデバイスに接続できるようにします。適切な電圧レベルを確保するためには、外付けプルアップ抵抗の値を選択する際にある程度の配慮が必要になります。外付けプルアップ抵抗の値は、 $V_{OL}$ 、出力容量性負荷、および出力リーク電流によって決定されます。これらの値は、[セクション 6.5](#) で規定されています。

オープンドレイン出力は、他の  $\overline{\text{RESETx}}/\text{RESETx}$  オープンドレイン ピンとワイヤード OR ロジックとして接続できます。

図 7-5.  $\overline{\text{RESETx}}$  出力

## 7.4 デバイスの機能モード

表 7-1. 機能モードの真理値表

| 概要                     | 条件                                   | VDD ピン                        | 出力 $\overline{\text{RESETx}} / (\text{RESETx})$ ピン |

|------------------------|--------------------------------------|-------------------------------|----------------------------------------------------|

| 通常動作                   | $V_{IT-(UV)} < SENSEx < V_{IT+(OV)}$ | $V_{DD} > V_{DD(\text{MIN})}$ | High / (Low)                                       |

| 通常動作 (UV のみ)           | $SENSEx > V_{IT-(UV)}$               | $V_{DD} > V_{DD(\text{MIN})}$ | High / (Low)                                       |

| 過電圧検出                  | $SENSEx > V_{IT+(OV)}$               | $V_{DD} > V_{DD(\text{MIN})}$ | Low / (High)                                       |

| Undervoltage detection | $SENSEx < V_{IT-(UV)}$               | $V_{DD} > V_{DD(\text{MIN})}$ | Low / (High)                                       |

| UVLO アクティブ化            | $V_{IT-(UV)} < SENSEx < V_{IT+(OV)}$ | $V_{POR} < V_{DD} < UVLO$     | Low / (High)                                       |

### 7.4.1 通常動作 ( $V_{DD} > V_{DD(\text{MIN})}$ )

$V_{DD}$  の電圧が  $(t_{\text{STRT}} + t_D)$  程度  $V_{DD(\text{MIN})}$  を上回ると、 $\overline{\text{RESETx}}/\text{RESETx}$  出力状態は  $SENSEx$  ピン電圧のスレッショルド限界値に対応し、 $SENSEx$  電圧がスレッショルド限界値を外れると、 $\overline{\text{RESETx}}/\text{RESETx}$  電圧はアサートされます。

### 7.4.2 低電圧誤動作防止 ( $V_{POR} < V_{DD} < UVLO$ )

$V_{DD}$  の電圧がデバイスの UVLO 電圧未満で、パワーオンリセット電圧 ( $V_{POR}$ ) よりも高い場合、 $\overline{\text{RESETx}}/\text{RESETx}$  ピンは、 $SENSEx$  ピンの電圧に関係なくアサートされます。

### 7.4.3 パワーオン リセット ( $V_{DD} < V_{POR}$ )

$V_{DD}$  の電圧が、アサートされた出力を内部で GND にプルするために必要な電圧 ( $V_{POR}$ ) を下回った場合、 $\overline{\text{RESETx}}/\text{RESETx}$  信号は未定義であり、デバイスが適切に機能するために信頼できるものではありません。

## 8 アプリケーションと実装

### 注

以下のアプリケーション情報は、TI の製品仕様に含まれるものではなく、TI ではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 アプリケーション情報

#### 8.1.1 電圧スレッショルド精度

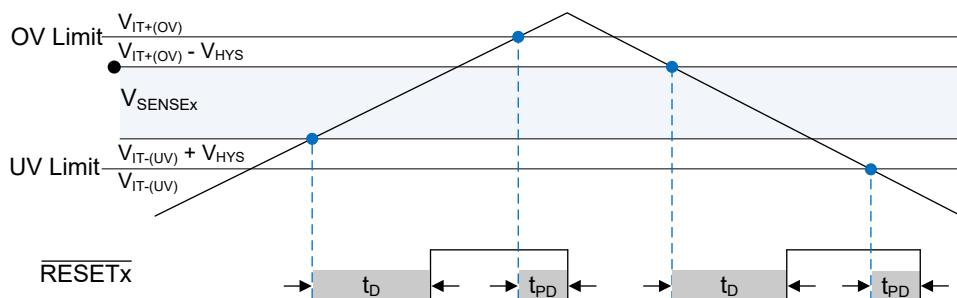

電圧監視の要件は、電力供給されるデバイスの電源電圧許容誤差によって異なります。TPS3704x は高精度（最大  $\pm 1\%$ ）であるため、電源電圧マージンやスレッショルド ヘッドルームを広く確保でき、許容誤差の厳しいアプリケーションにも対応できます。

たとえば、MCU のコア電圧レールに電力を供給する DC/DC レギュレータを考えてみましょう。MCU の許容誤差は、DC/DC の公称出力電圧の  $\pm 5\%$  です。ユーザーが設定する理想的な電圧スレッショルドは  $\pm 4\%$  で、これでスレッショルド精度は  $\pm 1\%$  になります。TPS3704x のスレッショルド精度は  $\pm 1\%$  であるため、電源電圧マージンが大きくなり、電源電圧の設計に余裕を持たせることができます。これによって、電圧リップルや過渡に対する電圧 WINDOW が大きくなるため、より小さな出力コンデンサやインダクタを使用できる柔軟性が DC/DC に与えられることになります。また、TPS3704x がリセット信号をアサートせずに、電圧電源が誤動作の可能性のある領域になることがないように、最低システム電圧と MCU の電圧許容誤差の間にヘッドルームを確保しています。

図 8-1 に、上述した例における TPS3704x の電源の低電圧マージンと精度を示します。低い精度のスーパーバイザを使用すると、電源のリップルや過渡応答に使用できる予算が圧迫されて、ユーザーに対する柔軟性が低下し、より厳格な DC/DC コンバータの設計が必要になります。

図 8-1. TPS3704x の電圧スレッショルド精度

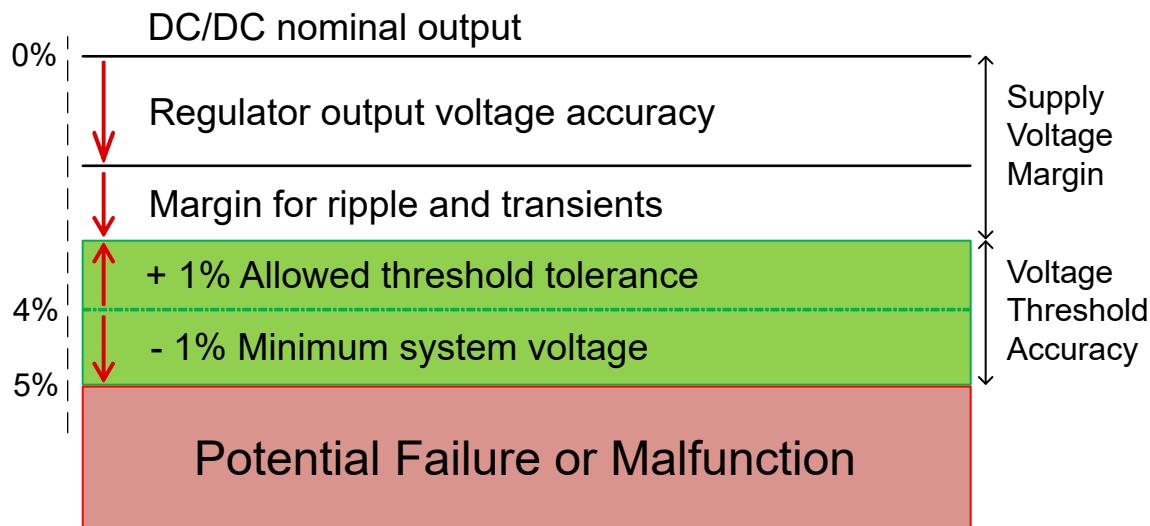

### 8.1.2 可変電圧スレッショルド

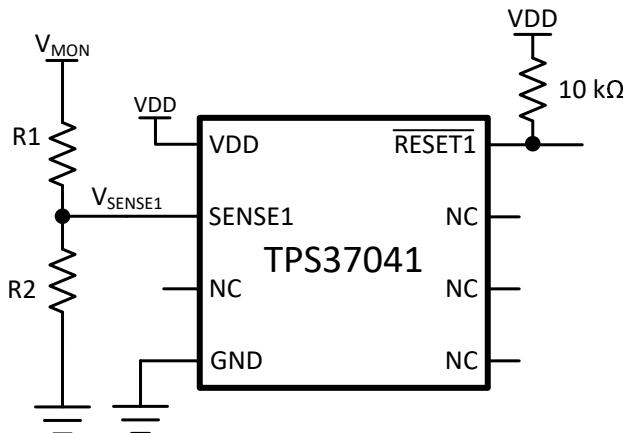

TPS3704x の最大精度 (1%) によって、デバイスに大きなばらつきを与えることなく、外付け抵抗を使用して電圧スレッショルドを調整することができます。監視したい電圧が利用できない場合、外付け分圧抵抗を使用して目標の電圧スレッショルドを設定することができます。**図 8-2** に、外付け分圧抵抗を使用して、電圧スレッショルドを調整する方法の例を図示します。外付け抵抗の計算については、**TPS3704** 製品ページの「設計ツールおよびシミュレーション」セクションの「**TPS3704 可変スレッショルド電圧抵抗の計算**」にアクセスしてください。抵抗は、目標の電圧スレッショルドとデバイス部品番号に応じて計算できます。テキサス・インスツルメンツでは、内部抵抗ラダーのバイパス モードのため、可変電圧スレッショルド デバイス バリエントを使用することを推奨します。

たとえば、**TPS3704** の 0.8V 可変バリエントを使用して、2.0V レールを監視 ( $V_{MON}$ ) するとします。**式 2** を使用すると、 $R_2 = 10\text{k}\Omega$ 、 $V_{MON} = 2\text{V}$ 、 $V_{SENSE1} = 0.8\text{V}$  であるため、 $R_1 = 15\text{k}\Omega$  となります。このデバイスは通常、 $\pm 4\%$  の電圧スレッショルドで 0.8V レールを監視することを意図しています。つまり、デバイスの低電圧スレッショルド ( $V_{IT-(UV)}$ ) と過電圧スレッショルド ( $V_{IT+(OV)}$ ) は、それぞれ 0.768V と 0.832V になります。**式 2** を使用すると、 $V_{SENSE1} = V_{IT-(UV)}$  のとき、 $V_{MON} = 1.92\text{V}$  になります。これは、デバイスがリセット信号をアサートする監視対象の低電圧しきい値、 $V_{MON-}$  と表すことができます。**式 2** を再度使用すると、 $V_{SENSE1} = V_{IT+(OV)}$  のとき、監視対象の過電圧スレッショルド ( $V_{MON+}$ ) = 2.08V となります。より広範囲の許容誤差が必要な場合や、UV のみのスレッショルドが必要な場合は、**表 9-2** に示すデバイス バリエントを使用して、実際のアプリケーションに適合するデバイスの部品番号を決定してください。

$$V_{SENSE1} = V_{MON} \times (R_2 / (R_1 + R_2)) \quad (2)$$

電圧スレッショルドを調整する際には、誤差を考慮する必要があります。分圧抵抗の許容誤差とは別に、分圧抵抗の精度に影響を及ぼす可能性のある **SENSE1** ピンの内部抵抗があります。非常に高いインピーダンスになることが予想されますが、設計仕様の数値を計算することを推奨します。内部センス抵抗  $R_{SENSE1}$  は、**式 4** に示すように、センス電圧  $V_{SENSE1}$  をセンス電流  $I_{SENSE1}$  で除算することで計算できます。 $V_{SENSE1}$  は、分圧抵抗と監視対象電圧に応じて、**式 2** を使用して計算できます。

$I_{SENSE1}$  は、**式 3** を使用して計算できます。

$$I_{SENSE1} = [(V_{MON} - V_{SENSE1}) / R_1] - (V_{SENSE1} / R_2) \quad (3)$$

$$R_{SENSE1} = V_{SENSE1} / I_{SENSE1} \quad (4)$$

**図 8-2. 外付け分圧抵抗による可変電圧スレッショルド**

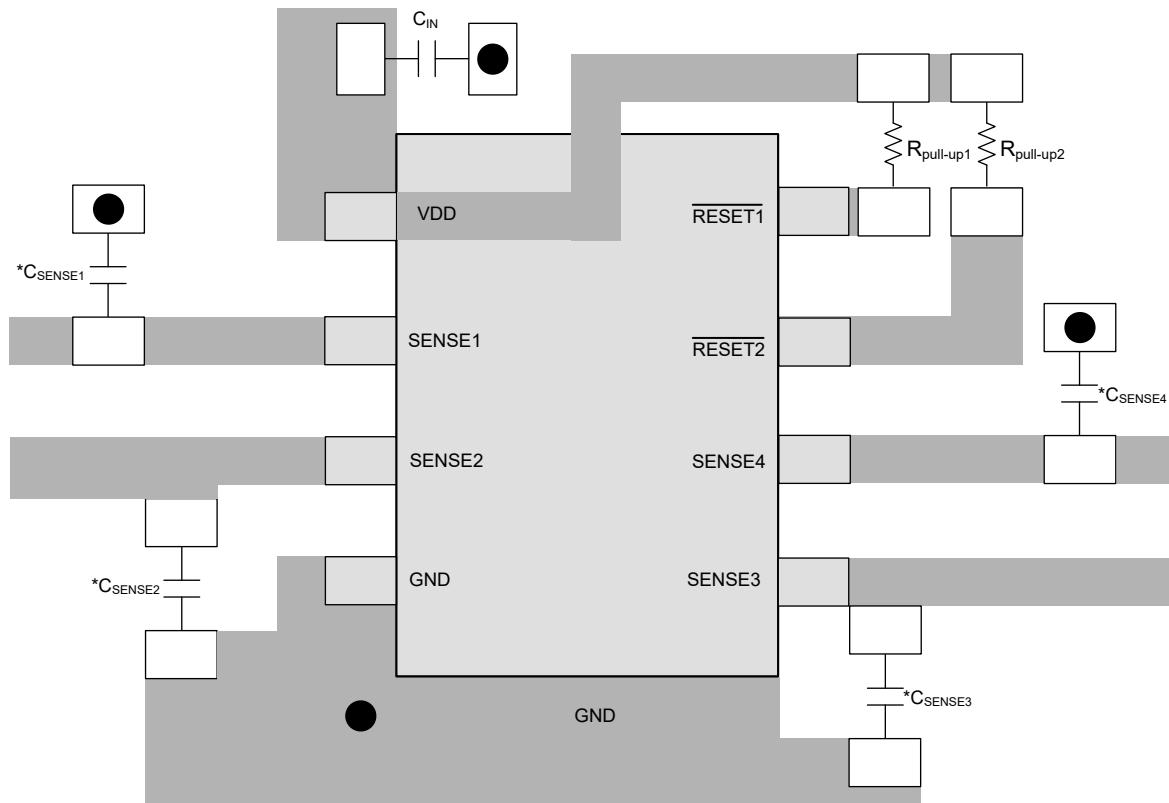

## 8.2 代表的なアプリケーション

### 8.2.1 設計 1：マイクロコントローラの電源レール用のマルチレール・ウィンドウ監視

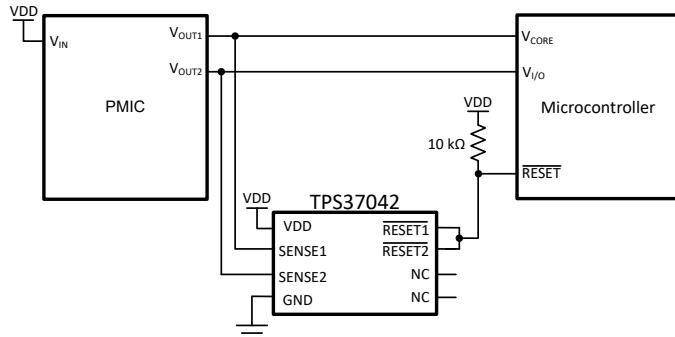

図 8-3 に、TPS37042 の代表的なアプリケーションを示します。TPS37042 は、正確なリセット遅延と電圧監視が必要なマイクロコントローラのコア電圧と I/O 電圧に電力供給する 2 つの PMIC 電圧レールを監視するために使用されます。TPS37042 を使用して、以下の回路と同様に、MCU のコア電圧レールを監視します。

図 8-3. 2 つのマイクロコントローラ電源レールを監視する TPS37042 デュアル チャネル

#### 8.2.1.1 設計要件

表 8-1. 設計要件

| パラメータ         | 設計要件                                                                       | 設計結果                                                                                            |

|---------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| 監視対象レール       | 公称 $3.3V_{I/O}$ 、 $3.3V$ の $\pm 8\%$ (デバイス精度を含む) を外れた場合は警告あり、10ms のリセット遅延  | ワースト ケース $V_{IT+(OV)} = 3.533V$ ( $7.06\%$ )<br>ワースト ケース $V_{IT-(UV)} = 3.071V$ ( $-6.94\%$ )   |

|               | 公称 $1.2V_{CORE}$ 、 $1.2V$ の $\pm 5\%$ (デバイス精度を含む) を外れた場合は警告あり、10ms のリセット遅延 | ワースト ケース $V_{IT+(OV)} = 1.2484V$ ( $4.03\%$ )<br>ワースト ケース $V_{IT-(UV)} = 1.1524V$ ( $-3.97\%$ ) |

| 出力ロジック電圧      | 5V CMOS                                                                    | 5V CMOS                                                                                         |

| システム監視の最大消費電流 | 25μA                                                                       | 5.5μA (最大 15μA)                                                                                 |

#### 8.2.1.2 詳細な設計手順

TPS3704x のどのバージョンが、表 9-2 に示されている監視対象レール ( $V_{MON}$ ) とウィンドウ許容誤差に最適であるかを判断してください。TPS3704x は、過電圧および低電圧の監視が可能で、 $0.4V \sim 5.55V$  のコモンレールの電圧を正確に監視できます。このアプリケーションでは、 $1.2V_{CORE}$  レールに  $\pm 5\%$  のばらつきしか許容されないため、レールを非常に厳しく監視する必要があります。この要件を満たすために、 $\pm 3\%$  のスレッショルドを持つ TPS37042 が選ばされました。 $3.3V_{I/O}$  はより柔軟で、最大  $8\%$  のばらつきまで動作可能です。TPS3704x にはさまざまな許容誤差オプションがあるため、この電圧レールに対しては  $\pm 6\%$  のスレッショルドを選択することができます。 $V_{IT+(OV)}$  と  $V_{IT-(UV)}$  のワーストケースを計算するには、精度も考慮する必要があります。 $V_{IT+(OV)}$  と  $V_{IT-(UV)}$  のワーストケースは、式 5 と 式 6 でそれぞれ計算できます。

$$V_{IT+(OV)-Worst Case} = V_{MON} \times (1 + \% \text{ スレッショルド}) \times (1 + \% \text{ 精度}) = 1.2 \times (1.03) \times (1.01) = 1.2484V \quad (5)$$

$$V_{IT-(UV)-Worst Case} = V_{MON} \times (1 - \% \text{ スレッショルド}) \times (1 - \% \text{ 精度}) = 1.2 \times (0.97) \times (0.99) = 1.1524V \quad (6)$$

また、OV スレッショルドや UV スレッショルドを決定する際には、フォルト後の解放ポイントが電源の許容誤差限界よりも高くなるように、ヒステリシスを考慮する必要があります。詳細については、図 6-1 を参照してください。

出力が高インピーダンス状態に切り替わるとき、RESETx/RESETx ピンの立ち上がり時間はそのノードのプルアップ抵抗と容量に依存します。プルアップ抵抗は、ダウンストリームタイミング要件と、アプリケーションに必要な  $V_{OL}$  を十分に低くするために必要なシンク電流の両方を満たすものを選択してください。低容量性負荷には  $10k\Omega \sim 1M\Omega$  の抵抗が適しています。

## 8.2.2 設計 2 : 機能安全のユースケースを強化するための手動セルフ・テスト・オプション

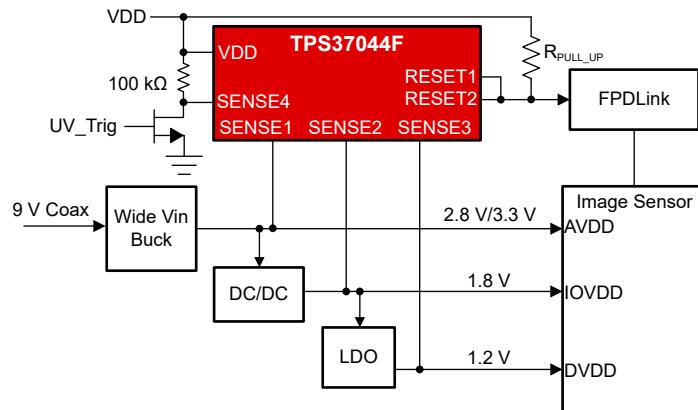

図 8-4 に、手動セルフ テスト機能を実装できるセルフ テスト方式を示します。任意の SENSE<sub>x</sub> ピンを予約し、出力で観察されるフォルトのトリガーに使用することで、フォルト検出のために TPS3704 をあらかじめ確認することができます。TPS3704 は、機能安全に準拠したマルチチャネルスーパーバイザであり、ファクトリ オートメーションやモーター ドライバなどのアプリケーションで IEC 61508 要件および産業用セーフティ インテグリティ レベルを達成しています。この例では、SENSE4 スレッショルドが OV で 5.5V、UV で 2V に設定された個別の低電圧および過電圧 (UV/OV) 出力用に構成された TPS37044F を使用しています。

図 8-4. TPS37044F クワッド チャネル監視、機能安全用手動セルフ テスト オプション付き

### 8.2.2.1 設計要件

表 8-2. 設計要件

| パラメータ                     | 設計要件                                                          | 設計結果                                                                             |

|---------------------------|---------------------------------------------------------------|----------------------------------------------------------------------------------|

| 監視対象レール                   | 公称 3.3V AVDD、3.3V の ±4% (デバイス精度を含む) を外れた場合は警告あり、10ms のリセット遅延  | ワースト ケース $V_{IT+(OV)} = 3.432V (+4\%)$<br>ワースト ケース $V_{IT-(UV)} = 3.168V (-4\%)$ |

|                           | 公称 1.8V IOVDD、1.8V の ±4% (デバイス精度を含む) を外れた場合は警告あり、10ms のリセット遅延 | ワースト ケース $V_{IT+(OV)} = 1.872V (+4\%)$<br>ワースト ケース $V_{IT-(UV)} = 1.728V (-4\%)$ |

|                           | 公称 1.2V DVDD、1.2V の ±4% (デバイス精度を含む) を外れた場合は警告あり、10ms のリセット遅延  | ワースト ケース $V_{IT+(OV)} = 1.248V (+4\%)$<br>ワースト ケース $V_{IT-(UV)} = 1.152V (-4\%)$ |

| SENSE4<br>(セルフ テスト オプション) | VDD への 100kΩ プルアップ抵抗、GND への NFET プルダウントランジスタ付き                | UV_Trig = High - SENSE4 ピンが Low になる<br>UV_Trig = Low - 通常動作時                     |

| 出力ロジック電圧                  | 5V CMOS                                                       | 5V CMOS                                                                          |

| システム最大 IDD 電流             | 25µA                                                          | 5.5µA (最大 20µA)                                                                  |

### 8.2.2.2 詳細な設計手順

図 8-4 に、手動セルフ テスト機能を実装できるセルフ テスト方式を示します。SENSE4 は、過電圧 (OV) スレッショルドが 5.5V、低電圧 (UV) スレッショルドが 2V に設定されており、100kΩ の抵抗を介して VDD に接続できます。セルフ テストの設定によって、TPS37044F に電力供給するレールには過電圧検出器が組み込まれ、追加の利点となります。機能安全の観点からは、電圧スーパーバイザが動作限界の推奨値を外れて動作している場合、電圧スーパーバイザの信頼性は低くなります。

手動セルフ テストをトリガするには、UV\_Trig を High にプルすると SENSE4 がロジック Low になり、低電圧 (UV) フォルトがトリガされます。UV フォルトは、アサートされた Low 信号として RESET2 に示されます。両方のリセット出力をプロセッサの NMI または割り込み入力に接続することで、このセルフ テスト オプション方式により、TPS37044F の RESET2 が適切に動作していることを確認できます。機能安全の詳細については、『機能安全マニュアル』を参照してください。

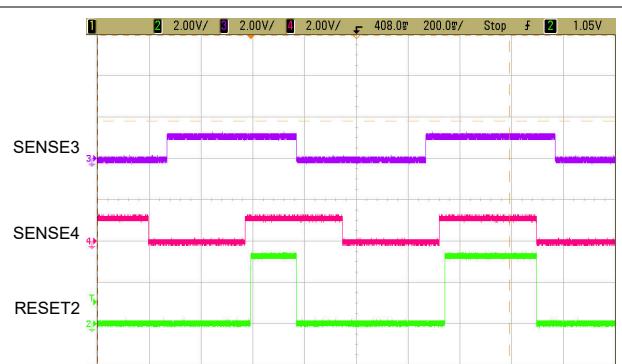

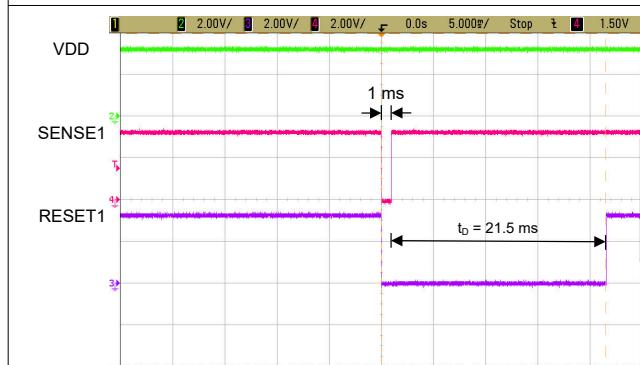

### 8.2.3 アプリケーション曲線

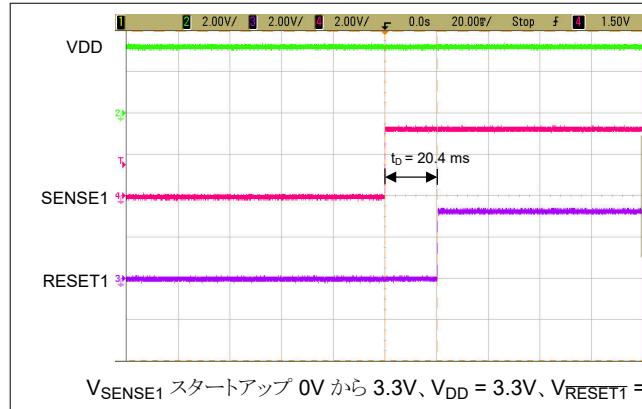

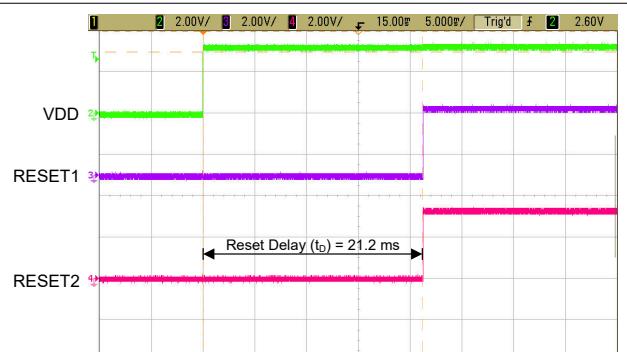

これらのアプリケーション曲線は、TPS3704Q1EVM で測定されたものです。詳細については、『[TPS3704Q1EVM ユーザーガイド](#)』を参照してください。

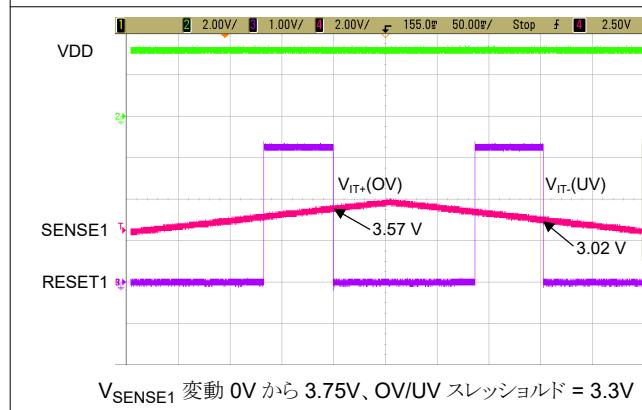

図 8-5. TPS37044 SENSE1 スタートアップ機能

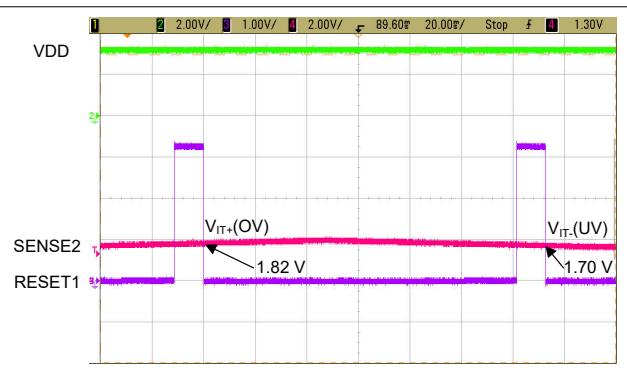

図 8-6. TPS37044 VDD スタートアップ機能

図 8-7. TPS37044 過電圧および低電圧機能

図 8-8. TPS37044 過電圧および低電圧機能

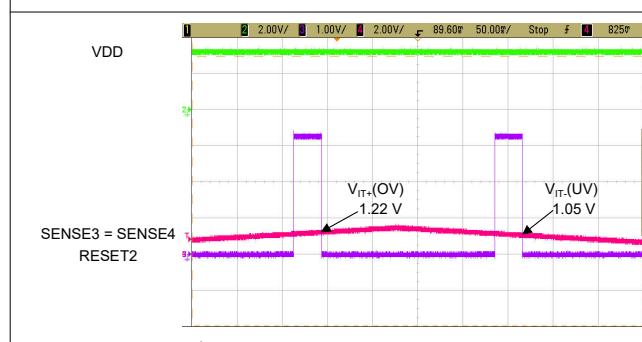

図 8-9. TPS37044 過電圧および低電圧機能

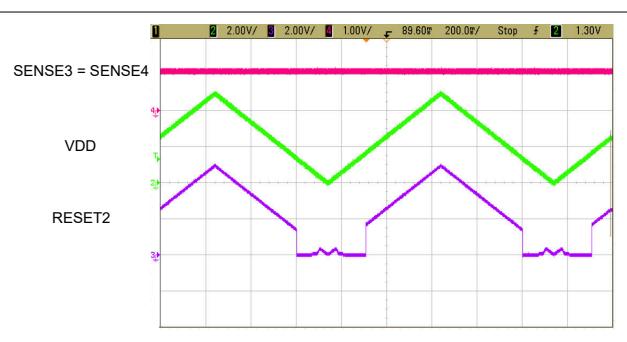

図 8-10. TPS37044 VDD 上昇機能

$V_{SENSE1}$  0V から 3.3V への切り替え [OV/UV スレッショルド = 3.3V ( $\pm 8\%$ )],  $V_{SENSE2}$  0V から 1.8V への切り替え [OV/UV スレッショルド = 1.8V ( $+4\%$ ,  $-3.5\%$ )],  $V_{DD} = 3.3V$ ,  $V_{RESET1} = 3.3V$ , TPS37044A7OHDDFR

図 8-11. TPS37044 SENSE 1 と SENSE 2 の切り替え

$V_{SENSE3}$  0V から 1.15V への切り替え [OV/UV スレッショルド = 1.15V ( $+7.5\%$ ,  $-5.5\%$ )],  $V_{SENSE4}$  0V から 1.15V への切り替え [OV/UV スレッショルド = 1.15V ( $+7.5\%$ ,  $-5.5\%$ )],  $V_{DD} = 3.3V$ ,  $V_{RESET1} = 3.3V$ , TPS37044A7OHDDFR

図 8-12. TPS37044 SENSE 3 と SENSE 4 の切り替え

$V_{SENSE1} = 3.3V$ , プッシュボタンで  $V_{SENSE1} = 0V$  を 1ms,  $V_{DD} = 3.3V$ ,  $V_{RESET1} = 3.3V$ , TPS37044A7OHDDFR

図 8-13. TPS37044 SENSE1 プッシュボタン監視機能、リセット時間遅延付き

$V_{SENSE1}$  3.3V から 0V への切り替え,  $V_{DD} = 3.3V$ ,  $V_{RESET1}$  3.3V から 0V への切り替え, TPS37044A7OHDDFR

図 8-14. TPS37044 SENSE1 伝搬遅延機能

## 8.3 電源に関する推奨事項

### 8.3.1 電源に関するガイドライン

このデバイスは、1.7V~6V の電圧範囲の入力電源で動作するよう設計されており、VDD ピンの絶対最大定格は 6.5V です。入力電圧の電源ノイズに応じて、VDD ピンと GND ピンの間に  $0.1\mu F$ ~ $1\mu F$  のコンデンサを配置するのが優れたアナログ手法といえます。VDD に電力を供給する電源電圧が、最大仕様を超えるような大きな電圧過渡の影響を受けやすい場合は、追加の予防措置を講じる必要があります。詳細については、SNVA849 を参照してください。

## 8.4 レイアウト

### 8.4.1 レイアウトのガイドライン

- 外付け部品は、可能な限りデバイスに近く配置します。こうすることで、寄生誤差の発生を防ぐことができます。

- VDD 電源ノードには、長いトレースを使用しないでください。VDD コンデンサは、電源からコンデンサまでの寄生インダクタンスとともに LC 回路を形成し、最大 VDD 電圧を上回るピーク電圧のリングを発生させる可能性があります。

- SENSE ピンに対して、長い電圧トレースを使用しないでください。長いトレースを使用すると、寄生インダクタンスを増加させて、正確な監視や診断ができなくなります。

- SENSEx コンデンサ ( $C_{SENSEx}$ ) を使用する場合は、コンデンサを SENSEx ピンのできるだけ近くに配置して、SENSEx ピンのノイズ耐性をさらに向上させてください。SENSEx ピンと GND の間に  $10nF \sim 100nF$  のコンデンサを配置すると、監視対象信号の過渡電圧に対する感度を低減できます。

- デジタル・パターンと並行して敏感なアナログ・パターンを配線しないでください。デジタル・パターンとアナログ・パターンはできるだけ交差しないようにします。どうしても必要な場合には、直角に交差させます。

### 8.4.2 レイアウト例

● Vias used to connect pins for application-specific connections

\* $C_{SENSEx}$  capacitors can be added for improve noise immunity

図 8-15. 推奨レイアウト

## 9 デバイスおよびドキュメントのサポート

### 9.1 デバイス命名規則

セクション 4 の 図 4-1 と 表 9-1 に、表 9-2 に示す部品番号からデバイスの機能を識別する方法を示します。

**表 9-1. デバイスの命名規則**

| 説明                 | 項目表記            | 値                           |

|--------------------|-----------------|-----------------------------|

| ジェネリック型番           | TPS3704x        | TPS3704x                    |

| チャネル オプション         | 1               | シングル チャネル オプション             |

|                    | 2               | デュアル チャネル オプション             |

|                    | 3               | トリプル チャネル オプション             |

|                    | 4               | クワッド チャネル オプション             |

| 検出オプション            | Ax, Bx, Cx, ... | 表 9-2 を参照。                  |

| バリエント・コード (出力トポロジ) | O               | オープン・ドレイン、アクティブ LOW         |

|                    | L               | プッシュプル、アクティブ LOW            |

|                    | H               | プッシュプル、アクティブ HIGH           |

|                    |                 |                             |

| リセット遅延時間オプション      | A               | 20µs リセット時間遅延               |

|                    | B               | 1ms リセット時間遅延                |

|                    | C               | 2ms リセット時間遅延                |

|                    | D               | 3ms リセット時間遅延                |

|                    | E               | 5ms リセット時間遅延                |

|                    | F               | 10ms リセット時間遅延               |

|                    | G               | 15ms リセット時間遅延               |

|                    | H               | 20ms リセット時間遅延               |

|                    | I               | 25ms リセット時間遅延               |

|                    | J               | 35ms リセット時間遅延               |

|                    | K               | 40ms リセット時間遅延               |

|                    | L               | 50ms リセット時間遅延               |

|                    | M               | 70ms リセット時間遅延               |

|                    | N               | 100ms リセット時間遅延              |

|                    | O               | 140ms リセット時間遅延              |

|                    | P               | 150ms リセット時間遅延              |

|                    | R               | 200ms リセット時間遅延              |

|                    | S               | 280ms リセット時間遅延              |

|                    | T               | 400ms リセット時間遅延              |

|                    | U               | 560ms リセット時間遅延              |

|                    | V               | 800ms リセット時間遅延              |

|                    | W               | 1120ms リセット時間遅延             |

|                    | X               | 1200ms リセット時間遅延             |

| パッケージ              | DDF             | SOT-23 8 ピン (1.6mm × 2.9mm) |

| リール                | R               | 大型リール                       |

**表 9-2. デバイス スレッショルド表**

| 発注用部品名             | VARIANT <sup>(3)</sup> | チャネル数 | リセット時間 | SENSE1 <sup>(1) (2)</sup> | SENSE2 <sup>(1) (2)</sup> | SENSE3 <sup>(1) (2)</sup> | SENSE4 <sup>(1) (2)</sup> |

|--------------------|------------------------|-------|--------|---------------------------|---------------------------|---------------------------|---------------------------|

| TPS37042BJOFDDFRQ1 | ADJ                    | 2     | 10ms   | 0.8V ( $\pm 4\%$ )        | 0.8V ( $\pm 4\%$ )        | -                         | -                         |

| TPS37042A3OFDDFRQ1 | 固定                     | 2     | 10ms   | 3.3V ( $\pm 5\%$ )        | 1.2V ( $\pm 5\%$ )        | -                         | -                         |

| TPS37042ZJOFDDFRQ1 | 固定                     | 2     | 10ms   | 1.95V ( $\pm 4\%$ )       | 3.8V ( $\pm 6\%$ )        | -                         | -                         |

| TPS37043DJOFDDFR   | ADJ / 固定               | 3     | 10ms   | 3.3V (-11%)               | 1.2V (-11%)               | 0.8V (-8%)                | -                         |

| TPS37043A4OFDDFRQ1 | 固定                     | 3     | 10ms   | 2.8V ( $\pm 5\%$ )        | 1.8V ( $\pm 5\%$ )        | 1.2V ( $\pm 5\%$ )        | -                         |

| TPS37043A8OFDDFRQ1 | 固定                     | 3     | 10ms   | 3.3V ( $\pm 5\%$ )        | 1.8V ( $\pm 5\%$ )        | 1.0V ( $\pm 5\%$ )        | -                         |

| TPS37043CPOFDDFRQ1 | ADJ / 固定               | 3     | 10ms   | 3.3V ( $\pm 4\%$ )        | 0.75V ( $\pm 4\%$ )       | 0.8V ( $\pm 3\%$ )        | -                         |

| TPS37043ZJOFDDFRQ1 | 固定                     | 3     | 10ms   | 0.95V ( $\pm 4\%$ )       | 1.35V ( $\pm 4\%$ )       | 1.8V ( $\pm 4\%$ )        | -                         |

| TPS37043LJOFDDFRQ1 | ADJ                    | 3     | 10ms   | 0.4V ( $\pm 5\%$ )        | 0.4V ( $\pm 5\%$ )        | 0.8V ( $\pm 5\%$ )        | -                         |

| TPS37043CJOFDDFRQ1 | ADJ                    | 3     | 10ms   | 0.8V ( $\pm 6\%$ )        | 0.8V ( $\pm 6\%$ )        | 0.8V ( $\pm 6\%$ )        | -                         |

| TPS37043MJOFDDFRQ1 | ADJ                    | 3     | 10ms   | 0.4V ( $\pm 7\%$ )        | 0.4V ( $\pm 7\%$ )        | 0.8V ( $\pm 7\%$ )        | -                         |

| TPS37043A5OFDDFRQ1 | 固定                     | 3     | 10ms   | 3.3V ( $\pm 4\%$ )        | 1.8V ( $\pm 4\%$ )        | 1.2V ( $\pm 4\%$ )        | -                         |

| TPS37043BJOFDDFRQ1 | ADJ                    | 3     | 10ms   | 0.8V ( $\pm 4\%$ )        | 0.8V ( $\pm 4\%$ )        | 0.8V ( $\pm 4\%$ )        | -                         |

| TPS37044BJOFDDFR   | ADJ                    | 4     | 10ms   | 0.8V ( $\pm 4\%$ )        |

| TPS37044LJOJDDFR   | ADJ                    | 4     | 35ms   | 0.4V ( $\pm 5\%$ )        | 0.4V ( $\pm 5\%$ )        | 0.8V ( $\pm 5\%$ )        | 0.8V ( $\pm 5\%$ )        |

| TPS37044BJOFDDFRQ1 | ADJ                    | 4     | 10ms   | 0.8V ( $\pm 4\%$ )        |

| TPS37044CJOFDDFRQ1 | ADJ                    | 4     | 10ms   | 0.8V ( $\pm 6\%$ )        |

| TPS37044MJOFDDFRQ1 | ADJ                    | 4     | 10ms   | 0.4V ( $\pm 7\%$ )        | 0.4V ( $\pm 7\%$ )        | 0.8V ( $\pm 7\%$ )        | 0.8V ( $\pm 7\%$ )        |

| TPS37044A4OGDDFRQ1 | 固定                     | 4     | 15ms   | 3.3V ( $\pm 8\%$ )        | 1.8V ( $\pm 4\%$ )        | 1.15V ( $\pm 6\%$ )       | 1.15V ( $\pm 6\%$ )       |

(1) パーセント表示はウインドウの許容誤差を示します。詳細については、図 6-1 を参照してください。

(2) VIT スレッショルド 0.8V と 0.4V は、調整可能なチャネルを示します。

(3) ADJ は、外付け分圧抵抗によって設定される調整可能な電圧スレッショルドを示します。詳細については、セクション 8.1.2 を参照してください。

## 9.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

## 9.3 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

## 9.4 商標

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

## 9.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことをお奨めします。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

## 9.6 用語集

### テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 10 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| <b>Changes from Revision D (September 2022) to Revision E (December 2023)</b> | <b>Page</b> |

|-------------------------------------------------------------------------------|-------------|

| • デバイスのスレッショルド表から TPS37044UJOFDDFR および TPS37044GJONDDFR を削除.....              | 3           |

| • シングル チャネルのピン配置を削除.....                                                      | 5           |

| • デバイスのスレッショルド表から TPS37044UJOFDDFR および TPS37044GJONDDFR を削除.....              | 29          |

| <b>Changes from Revision C (September 2022) to Revision D (September 2023)</b> | <b>Page</b> |

|--------------------------------------------------------------------------------|-------------|

| • ウィンドウ許容誤差の仕様に内容を明確にする文章を追加.....                                              | 1           |

| • デバイスのスレッショルド表のハイライト表示と計算ツール.....                                             | 1           |

| • シングル・チャネルについての言及を省いて文章を簡潔化.....                                              | 1           |

| • 表 4-1 の追加.....                                                               | 3           |

| • 図 6-1 のウィンドウ許容誤差の仕様に内容を明確にする文章を追加.....                                       | 11          |

| • シングル チャネル スーパーバイザーに関する参照を削除.....                                             | 17          |

| • シングル・チャネルのブロック図を削除.....                                                      | 17          |

| • 可変スレッショルド抵抗の計算に関する参照を追加.....                                                 | 23          |

| • 表 9-2 に発注用部品名を追加.....                                                        | 29          |

| <b>Changes from Revision B (November 2021) to Revision C (September 2022)</b> | <b>Page</b> |

|-------------------------------------------------------------------------------|-------------|

| • 機能安全の情報を追加.....                                                             | 1           |

| • 「手動セルフ テスト オプション」セクションを追加.....                                              | 25          |

| <b>Changes from Revision A (July 2021) to Revision B (November 2021)</b> | <b>Page</b> |

|--------------------------------------------------------------------------|-------------|

| • 「事前情報」から「量産データ」に変更.....                                                | 1           |

## 11 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用している場合は、画面左側のナビゲーションをご覧ください。

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins        | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-----------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| TPS37043DJOFDDFR      | Active        | Production           | SOT-23-THIN (DDF)   8 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 3DJOF               |

| TPS37043DJOFDDFR.A    | Active        | Production           | SOT-23-THIN (DDF)   8 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 3DJOF               |

| TPS37044BJOFDDFR      | Active        | Production           | SOT-23-THIN (DDF)   8 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 4BJOF               |

| TPS37044BJOFDDFR.A    | Active        | Production           | SOT-23-THIN (DDF)   8 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 4BJOF               |

| TPS37044LJOJDDFR      | Active        | Production           | SOT-23-THIN (DDF)   8 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 4LJOJ               |

| TPS37044LJOJDDFR.A    | Active        | Production           | SOT-23-THIN (DDF)   8 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 4LJOJ               |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

**OTHER QUALIFIED VERSIONS OF TPS3704 :**

- Automotive : [TPS3704-Q1](#)

NOTE: Qualified Version Definitions:

- Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects

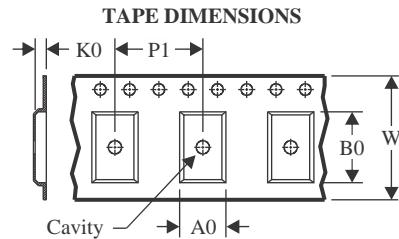

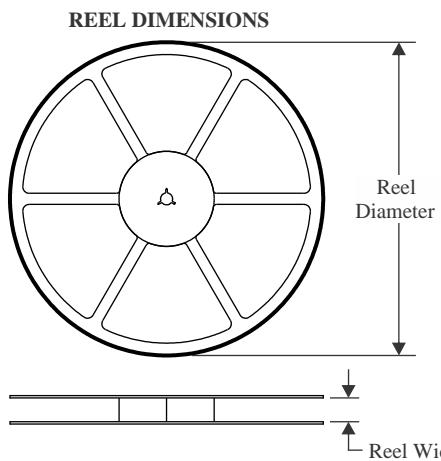

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device           | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|------------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| TPS37043DJOFDDFR | SOT-23-THIN  | DDF             | 8    | 3000 | 180.0              | 8.4                | 3.2     | 3.2     | 1.4     | 4.0     | 8.0    | Q3            |

| TPS37044BJOFDDFR | SOT-23-THIN  | DDF             | 8    | 3000 | 180.0              | 8.4                | 3.2     | 3.2     | 1.4     | 4.0     | 8.0    | Q3            |

| TPS37044LJOJDDFR | SOT-23-THIN  | DDF             | 8    | 3000 | 180.0              | 8.4                | 3.2     | 3.2     | 1.4     | 4.0     | 8.0    | Q3            |

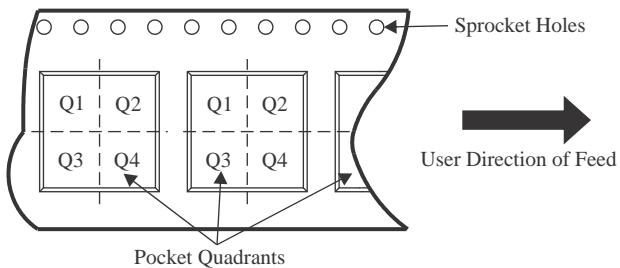

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device           | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS37043DJOFDDFR | SOT-23-THIN  | DDF             | 8    | 3000 | 210.0       | 185.0      | 35.0        |

| TPS37044BJOFDDFR | SOT-23-THIN  | DDF             | 8    | 3000 | 210.0       | 185.0      | 35.0        |

| TPS37044LJOJDDFR | SOT-23-THIN  | DDF             | 8    | 3000 | 210.0       | 185.0      | 35.0        |

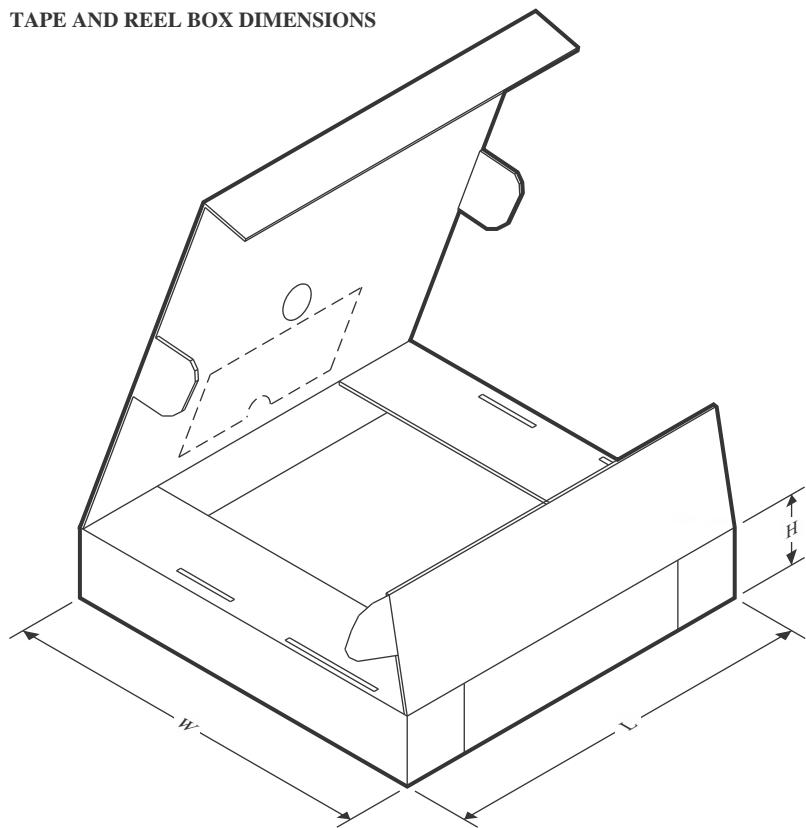

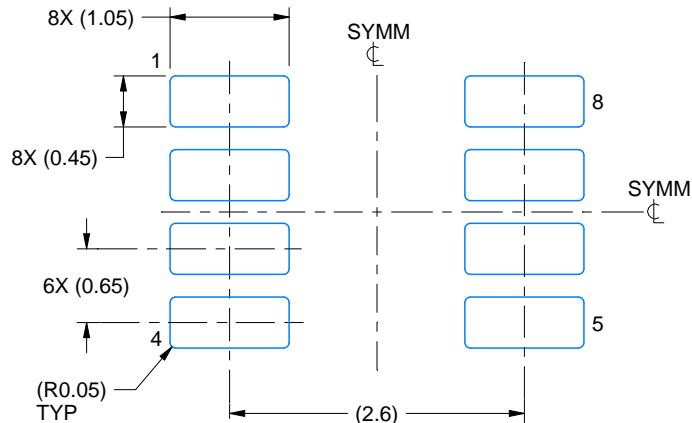

# PACKAGE OUTLINE

**DDF0008A**

**SOT-23-THIN - 1.1 mm max height**

PLASTIC SMALL OUTLINE

4222047/E 07/2024

## NOTES:

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- This drawing is subject to change without notice.

- This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

# DDF0008A

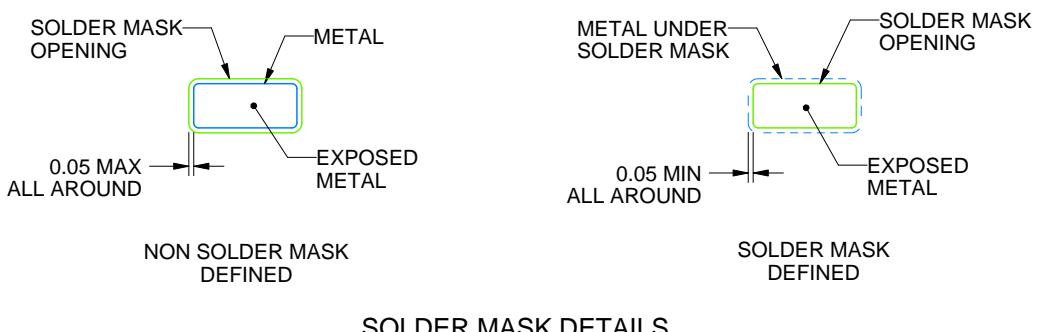

## EXAMPLE BOARD LAYOUT

### SOT-23-THIN - 1.1 mm max height

PLASTIC SMALL OUTLINE

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE:15X

SOLDER MASK DETAILS

4222047/E 07/2024

NOTES: (continued)

4. Publication IPC-7351 may have alternate designs.

5. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

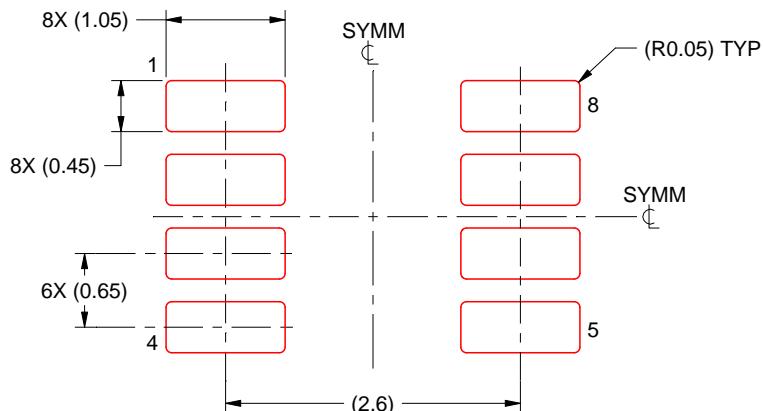

**DDF0008A**

# EXAMPLE STENCIL DESIGN

**SOT-23-THIN - 1.1 mm max height**

PLASTIC SMALL OUTLINE

SOLDER PASTE EXAMPLE

BASED ON 0.125 mm THICK STENCIL

SCALE:15X

4222047/E 07/2024

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

7. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月