# UCC28056 6端子单相遷移モードPFCコントローラ

## 1 特長

- 最低10%の負荷まで入力電流歪みが小さく、ユニティに近い力率を実現

- IEC1000-3-2への準拠を実現

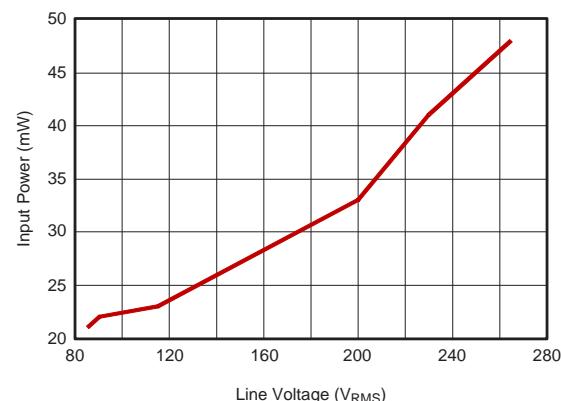

- 無負荷時入力電力が極めて低い(<50mW @265V)

- さまざまな負荷で優れた効率

- PFCをオフにすることなく、グリーン電力規格への準拠を実現

- EuP Lot 6 Tier 2、CoC Ver. 5 Tier 2、Energy Star for computers Ver. 6.1、DOE Level VI

- 超低可聴ノイズ出力

- ソフト起動/ソフト終了期間付きバースト・モード

- 強化されたEA、入力電流歪みの増大なしに負荷ステップに素早く応答

- 高いゲート駆動性能: -0.7Aおよび1.0A

- バレー同期開始により、ブースト・インダクタに2次巻線が不要

- ユーザー調整可能なバレー遅延

- 低スタートアップ消費電流(<46μA)

- 広いVCC範囲: 8.5V~34V

- ソフト起動/ソフト終了による出力電圧制限

- サイクル単位の電流制限

- 独立した2次出力電圧保護

- 過熱保護機能を内蔵

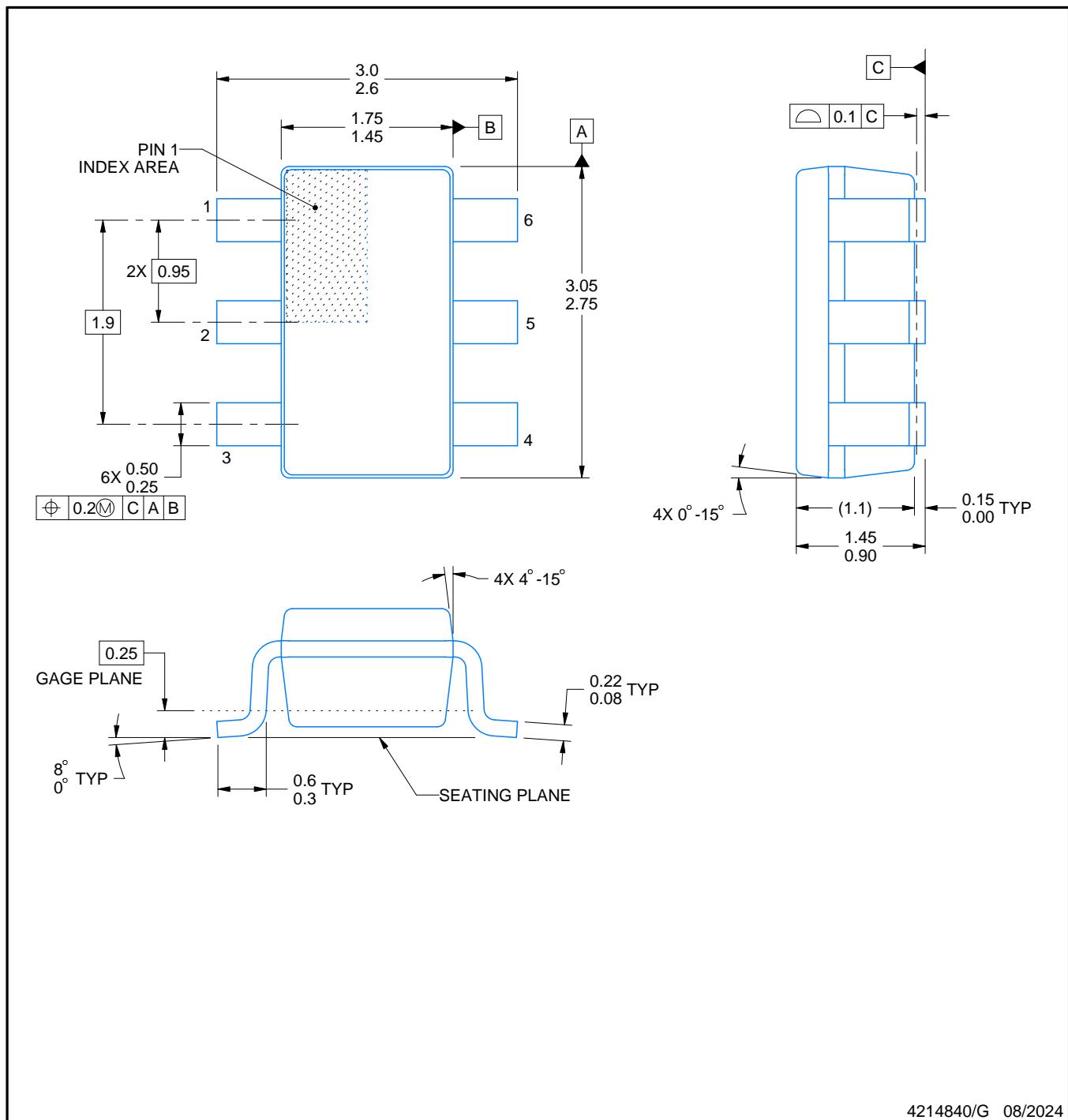

- 占有面積の小さい6端子SOT-23(6)パッケージ

- WEBENCH® Power Designer**により、TLV28056を使用するカスタム設計を作成

## 2 アプリケーション

- デスクトップ・コンピューティング/デジタル・テレビ

- ゲーム/セットトップ・ボックス/ACアダプタ・フロントエンド

- LEDドライバ/照明

- エントリレベル・サーバー/Webサーバー

## 3 概要

UCC28056は、最大300Wの電力段を直接駆動するPFCコントローラであり、歪みの小さい正弦波の入力電流とユニティに近い力率を実現します。軽負荷効率に優れ、スタンバイ消費電力も低く抑えることができます。また、高い力率と現在の厳しいグリーン電力規格への準拠が要求される電源システムの設計を簡素化できます。全負荷時には遷移モードでPFC電力段を動作させ、負荷が減ると不連続導通モードに移行して、自動的にスイッチング周波数を下げ、効率の最大化を図ります。軽負荷時には、DCM動作とバースト・モード動作の組み合わせにより、さらに軽負荷効率が向上し、スタンバイ消費電力も低減されます。高性能で安定したPFC段の実装に必要な機能をすべて6端子パッケージに搭載しているため、外付け部品を最小限に抑えることができます。

### 製品情報<sup>(1)</sup>

| 型番       | パッケージ      | 本体サイズ(公称)    |

|----------|------------|--------------|

| UCC28056 | SOT-23 (6) | 2.90mm×1.6mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末尾にある注文情報を参照してください。

### スタンバイ消費電力

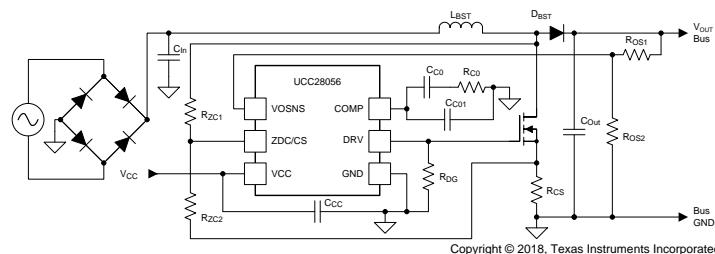

### アプリケーション概略図

Copyright © 2018, Texas Instruments Incorporated

英語版のTI製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、www.ti.comで閲覧でき、その内容が常に優先されます。TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、必ず最新版の英語版をご参照くださいますようお願いいたします。

English Data Sheet: SLUSD37

## 目次

|          |                   |           |                                     |           |

|----------|-------------------|-----------|-------------------------------------|-----------|

| <b>1</b> | 特長 .....          | <b>1</b>  | 7.4 コントローラの機能モード .....              | 23        |

| <b>2</b> | アプリケーション .....    | <b>1</b>  | <b>8</b> アプリケーションと実装 .....          | <b>24</b> |

| <b>3</b> | 概要 .....          | <b>1</b>  | 8.1 アプリケーション情報 .....                | 24        |

| <b>4</b> | 改訂履歴 .....        | <b>2</b>  | 8.2 代表的なアプリケーション .....              | 24        |

| <b>5</b> | 端子構成および機能 .....   | <b>3</b>  | <b>9</b> 電源に関する推奨事項 .....           | <b>41</b> |

| <b>6</b> | 仕様 .....          | <b>4</b>  | <b>10</b> レイアウト .....               | <b>41</b> |

|          | 6.1 絶対最大定格 .....  | 4         | 10.1 レイアウトのガイドライン .....             | 41        |

|          | 6.2 ESD定格 .....   | 4         | 10.2 レイアウト例 .....                   | 41        |

|          | 6.3 推奨動作条件 .....  | 4         | <b>11</b> デバイスおよびドキュメントのサポート .....  | <b>44</b> |

|          | 6.4 熱特性 .....     | 4         | 11.1 WEBENCH®ツールによるカスタム設計 .....     | 44        |

|          | 6.5 電気的の特性 .....  | 4         | 11.2 ドキュメントの更新通知を受け取る方法 .....       | 44        |

|          | 6.6 代表的特性 .....   | 9         | 11.3 コミュニティ・リソース .....              | 44        |

| <b>7</b> | 詳細説明 .....        | <b>12</b> | 11.4 商標 .....                       | 44        |

|          | 7.1 概要 .....      | 12        | 11.5 静電気放電に関する注意事項 .....            | 44        |

|          | 7.2 機能ブロック図 ..... | 13        | 11.6 Glossary .....                 | 44        |

|          | 7.3 機能説明 .....    | 14        | <b>12</b> メカニカル、パッケージ、および注文情報 ..... | <b>44</b> |

## 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Revision A (November 2017) から Revision B に変更 | Page |

|----------------------------------------------|------|

| • アプリケーション概略図を更新 .....                       | 1    |

| • ドキュメント・ステータスを事前情報から量産データに 変更 .....         | 1    |

| 2017年10月発行のものから更新              | Page |

|--------------------------------|------|

| • データシートにWEBENCHへのリンクを追加 ..... | 1    |

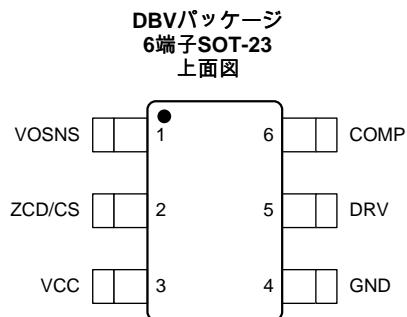

## 5 端子構成および機能

**端子機能**

| 端子     |    | I/O | 説明                                                                                                                                                                                                                                                                                                                       |

|--------|----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名前     | 番号 |     |                                                                                                                                                                                                                                                                                                                          |

| COMP   | 6  | I/O | 内部トランスコンダクタンス・エラー・アンプの出力と電力要求入力。電圧帰還ループの補償を行うには、この端子とGNDの間に適切なRCネットワークを接続します。エラー・アンプの出力は内部で $V_{COICmp}$ に制限されます。UCC28056がStopb状態になるか、またはOvp2コンバレータがトリップされると、内部抵抗 $R_{CODisCh}$ が外部補償ネットワークを放電します。COMP端子の電圧が $V_{BSTRall}$ を下回ると、スイッチングは停止し、UCC28056が低消費電力状態(BstOffb)に移行します。COMP端子の電圧が $V_{BSTRise}$ を上回ると、スイッチングは再開します。 |

| DRV    | 5  | I/O | メイン・パワーMOSFETを駆動するGATE接続。この出力は内部で $V_{DRHigh}$ に制限されます。これにより内蔵ドライバの消費電力を削減し、UCC28056が高いVCC電圧で動作できます。DRVとGNDの間に接続する外付け抵抗により、 $V_{In}$ を下回るドレイン波形の立ち下がりからDRVの立ち上がりエッジまでの遅延が調整され、広いアイドル・リング発振周波数にわたって、遷移開始をバレー(谷)の最小値に正確に合わせることができます。                                                                                       |

| GND    | 4  | G   | グランド基準端子。電流検知抵抗 $R_{CS}$ の2次端子でのみ電力段に接続します。                                                                                                                                                                                                                                                                              |

| VCC    | 3  | P   | 正電源電圧。VCCが $V_{CCStart}$ を上回ると、スイッチング動作を開始できます。VCCが $V_{CCStop}$ を下回る状態が $T_{UVLOBk}$ を超えると、スイッチング動作は停止します。                                                                                                                                                                                                              |

| ZCD/CS | 2  | I   | この端子には、パワーMOSFETスイッチのドレイン/ソース端子に接続した分圧器によって電力が送り込まれます。DRV = Hの間は、この端子が電流検知抵抗 $R_{CS}$ を通った電圧を監視します。この端子には過電流保護機能があります。DRV = Lの間は、この端子がドレイン電圧波形を監視します。ドレイン波形をフィルタ処理して、電力段に印加された入力電圧を取得することができます。入力電圧を用いて、入力電圧フィードフォワードおよび入力ブロウンイン機能を提供します。またドレイン電圧波形を用いて、ZCD検出、バレー同期、2次出力過電圧保護といった機能も提供します。                               |

| VOSNS  | 1  | I   | 電圧エラー・アンプ反転入力。エラー・アンプ非反転入力は内蔵基準電圧 $V_{OSReg}$ に接続します。誤差の規模に応じてエラー・アンプ・ゲインが大きくなり、入力電流歪みの増大を伴わずに過渡応答性能を向上させます。この端子には出力過電圧保護機能が実装されています。この端子の電圧が $V_{Ovp1Rise}$ を上回るとスイッチング動作は停止し、 $V_{Ovp1Fall}$ を下回ると再開します。                                                                                                               |

## 6 仕様

### 6.1 絶対最大定格

動作温度範囲内（特に記述のない限り）<sup>(1)</sup>

|                             |                  | 最小    | MAX | UNIT |

|-----------------------------|------------------|-------|-----|------|

| Input voltage               | VCC              | - 0.5 | 36  | V    |

|                             | ZCD/CS           | - 0.5 | 7   |      |

|                             | VOSNS            | - 0.5 | 7   |      |

| 出力電圧                        | COMP             | - 0.5 | 7   | V    |

|                             | DRV              | -0.3  | 20  |      |

| 接合部温度範囲                     | T <sub>J</sub>   | -40   | 150 | °C   |

| 保管温度範囲、<br>T <sub>stg</sub> | T <sub>stg</sub> | -65   | 150 |      |

| Lead temperature            | ハンダ付け、10秒        |       | 300 |      |

|                             | Reflow           |       | 260 |      |

- (1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を超える状態で本製品が正常に動作することを暗黙的に示すものではありません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

### 6.2 ESD定格

|                    |       | 値                                                                                        | 単位    |

|--------------------|-------|------------------------------------------------------------------------------------------|-------|

| V <sub>(ESD)</sub> | 静電気放電 | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>              | ±2000 |

|                    |       | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> |       |

- (1) JEDECのドキュメントJEP155に、500V HBMでは標準のESD管理プロセスで安全な製造が可能であると規定されています。

(2) JEDECのドキュメントJEP157に、250V CDMでは標準のESD管理プロセスで安全な製造が可能であると規定されています。

### 6.3 推奨動作条件

動作温度範囲内（特に記述のない限り）

|                |        | 最小  | 標準 | 最大  | UNIT |

|----------------|--------|-----|----|-----|------|

| VCC            | 入力電圧   |     | 12 |     | V    |

| T <sub>A</sub> | 動作周囲温度 | -40 |    | 125 | °C   |

### 6.4 热特性

| 熱特性 <sup>(1)</sup>    | UCC28056          | 単位    |

|-----------------------|-------------------|-------|

|                       | SOT23-6           |       |

|                       | 6端子               |       |

| R <sub>θJA</sub>      | 接合部から周囲温度への熱抵抗    | 116.4 |

| R <sub>θJC(top)</sub> | 接合部からケース(上面)への熱抵抗 | 74.9  |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗      | 36.1  |

| Ψ <sub>JT</sub>       | 接合部から上面への熱特性      | 18.8  |

| Ψ <sub>JB</sub>       | 接合部から基板への熱特性      | 36.0  |

- (1) 従来および新しい熱測定値の詳細については、アプリケーション・レポート『半導体およびICパッケージの熱測定値』、SPRA953を参照してください。

### 6.5 電気的特性

動作温度範囲内（特に記述のない限り）

| PARAMETER            | TEST CONDITIONS | MIN      | TYP | MAX   | UNIT |

|----------------------|-----------------|----------|-----|-------|------|

| 電源電圧                 |                 |          |     |       |      |

| V <sub>CCStart</sub> | 起動開始閾値          | VCC立ち上がり |     | 10.65 | 11   |

## 電気的特性 (continued)

動作温度範囲内 (特に記述のない限り)

| PARAMETER        | TEST CONDITIONS                                         | MIN                                                              | TYP   | MAX   | UNIT       |            |

|------------------|---------------------------------------------------------|------------------------------------------------------------------|-------|-------|------------|------------|

| $V_{CCStop}$     | 停止閾値                                                    | VCC立ち下がり                                                         | 8.5   | 8.85  | 9.2        | V          |

| $V_{CCHyst}$     | UVLOヒステリシス( $V_{CCStart} - V_{CCStop}$ ) <sup>(1)</sup> |                                                                  | 1.5   |       |            | V          |

| $T_{UVLOBlk}$    | 動作停止ブランディング時間                                           |                                                                  | 27    | 35    | 42         | $\mu s$    |

| <b>消費電流</b>      |                                                         |                                                                  |       |       |            |            |

| $I_{CC_Startup}$ | 起動開始前消費電流                                               | $VCC = V_{CCStart} - 200mV, T_A < 110^\circ C$                   |       | 46    | $\mu A$    |            |

| $I_{CC_FAULT}$   | 異常検出状態での消費電流                                            | $VCC = 12V$                                                      |       | 130   | $\mu A$    |            |

| $I_{CC_BSTOFF}$  | バースト・オフ期間中の消費電流                                         | $VCC = 12V$                                                      |       | 132   | $\mu A$    |            |

| $I_{CC_RUN}$     | DRV端子無負荷時動作電流                                           | $VCC = 12V$                                                      | 1.8   | 2.2   | mA         |            |

| <b>ゲート・トライプ</b>  |                                                         |                                                                  |       |       |            |            |

| $V_{DRLow}$      | DRV出力低電圧                                                | $I_{DR} = 100mA$                                                 |       | 0.9   | V          |            |

| $V_{DRHigh}$     | DRV出力電圧高値、制限付き                                          | $VCC = 25V, I_{DR} = - 10mA$                                     | 10    | 13.7  | 15         | V          |

| $V_{DRHighMin}$  | DRV最小高電圧値                                               | $VCC = V_{CCStop} + 200mV, I_{DR} = - 8mA$                       | 8     |       |            | V          |

| $R_{DRH}$        | DRV、プルアップ抵抗                                             | $T_A = - 40^\circ C \sim 125^\circ C, I_{DR} = - 8mA, VCC = 12V$ |       | 9.7   | 16         | $\Omega$   |

| $R_{DRL}$        | DRV、プルダウン抵抗                                             | $T_A = - 40^\circ C \sim 125^\circ C, I_{DR} = 100mA$            | 2.0   | 4.6   | 9          | $\Omega$   |

| $t_R$            | 立ち上がり時間                                                 | $CLOAD = 1nF, DRV = 1V \sim 6V, VCC = 12V$                       | 10    | 34    | 61         | ns         |

| $t_F$            | 立ち下がり時間                                                 | $CLOAD = 1nF, DRV = 6V \sim 1V, VCC = 12V$                       | 4     | 15    | 40         | ns         |

| $I_{source}$     | DRV端子のソース・ピーク電流 <sup>(1)</sup>                          |                                                                  |       | - 0.7 | A          |            |

| $I_{sink}$       | DRV端子のシンク・ピーク電流 <sup>(1)</sup>                          |                                                                  |       | 1     | A          |            |

| $R_{DG0}$        | $T_{ZCDR0}$ を選択するDRV-GND間の抵抗値 <sup>(1)</sup>            |                                                                  | 130   | 200   | k $\Omega$ |            |

| $R_{DG1}$        | $T_{ZCDR1}$ を選択するDRV-GND間の抵抗値 <sup>(1)</sup>            |                                                                  | 81.18 | 82    | 82.82      | k $\Omega$ |

| $R_{DG2}$        | $T_{ZCDR2}$ を選択するDRV-GND間の抵抗値 <sup>(1)</sup>            |                                                                  | 61.38 | 62    | 62.62      | k $\Omega$ |

| $R_{DG3}$        | $T_{ZCDR3}$ を選択するDRV-GND間の抵抗値 <sup>(1)</sup>            |                                                                  | 42.57 | 43    | 43.43      | k $\Omega$ |

| $R_{DG4}$        | $T_{ZCDR4}$ を選択するDRV-GND間の抵抗値 <sup>(1)</sup>            |                                                                  | 26.73 | 27    | 27.27      | k $\Omega$ |

| $R_{DG5}$        | $T_{ZCDR5}$ を選択するDRV-GND間の抵抗値 <sup>(1)</sup>            |                                                                  | 17.82 | 18    | 18.18      | k $\Omega$ |

| $R_{DG6}$        | $T_{ZCDR6}$ を選択するDRV-GND間の抵抗値 <sup>(1)</sup>            |                                                                  | 12.87 | 13    | 13.13      | k $\Omega$ |

| $R_{DG7}$        | $T_{ZCDR7}$ を選択するDRV-GND間の抵抗値 <sup>(1)</sup>            |                                                                  | 9     | 9.1   | 9.2        | k $\Omega$ |

| $T_{DGSmpl}$     | $R_{DG}$ 値の検出に要する時間。                                    | $T_A < 85^\circ C$                                               | 3.95  | 4.4   | 4.95       | ms         |

| $V_{DGClmp}$     | $R_{DG}$ 値の検出中にDRV端子で印加される最大電圧。                         |                                                                  | 1     | 1.05  | 1.1        | V          |

| <b>エラー・アンプ</b>   |                                                         |                                                                  |       |       |            |            |

| $V_{OSReg}$      | 帰還基準電圧                                                  |                                                                  | 2.45  | 2.5   | 2.55       | V          |

| $I_{OSBias}$     | ISNS端子バイアス電流                                            | $V_{OS} = V_{OSReg}$                                             | - 100 |       | 100        | nA         |

| $g_M$            | エラー・アンプ・トランスコンダクタス・ゲイン                                  | $ V_{OS} - V_{OSReg}  < DSuThs$                                  |       | 50    |            | $\mu S$    |

| $g_{MNL}$        | 大きな誤差におけるエラー・アンプ・トランスコンダクタンス・ゲイン                        | $ V_{OS} - V_{OSReg}  > DSuThs$                                  |       | 300   |            | $\mu S$    |

| $DSuThs$         | 非線形ゲイン閾値                                                |                                                                  | 67    |       |            | mV         |

(1) 実製品の検査は行っていません。設計により保証されています。

## 電気的特性 (continued)

動作温度範囲内 (特に記述のない限り)

| PARAMETER     | TEST CONDITIONS                                           | MIN                                        | TYP   | MAX  | UNIT |

|---------------|-----------------------------------------------------------|--------------------------------------------|-------|------|------|

| $R_{CODisch}$ | STOPb状態でのCOMP-GND間の内蔵抵抗。                                  | 4.3                                        | 5     | 5.7  | kΩ   |

| $V_{COClmp}$  | COMP端子内部高クランプ電圧                                           | 5.5                                        | 5.6   | 5.71 | V    |

| $V_{COSat}$   | COMP端子内部低クランプ電圧 <sup>(1)</sup>                            | 0                                          |       |      | V    |

| $I_{COMin}$   | COMP最大ソース電流                                               | -120                                       |       |      | μA   |

| $I_{COMax}$   | COMP最大シンク電流                                               | 120                                        |       |      | μA   |

| 入力電圧フィードフォワード |                                                           |                                            |       |      |      |

| $T_{HLinMax}$ | 入力ピーク・サンプリング・ウィンドウ <sup>(1)</sup>                         | スイッチング中                                    | 11    | 12.3 | 13.6 |

| $V_{FF0Rise}$ | $G_{FF3}$ から $G_{FF1}$ に切り替わるコンパレータ立ち上がり閾値 <sup>(1)</sup> |                                            | 0.348 |      | V    |

| $V_{FF1Rise}$ | $G_{FF1}$ から $G_{FF2}$ に切り替わるコンパレータ立ち上がり閾値 <sup>(1)</sup> |                                            | 0.406 |      | V    |

| $V_{FF2Rise}$ | $G_{FF2}$ から $G_{FF3}$ に切り替わるコンパレータ立ち上がり閾値 <sup>(1)</sup> |                                            | 0.473 |      | V    |

| $V_{FF3Rise}$ | $G_{FF3}$ から $G_{FF4}$ に切り替わるコンパレータ立ち上がり閾値 <sup>(1)</sup> |                                            | 0.552 |      | V    |

| $V_{FF4Rise}$ | $G_{FF4}$ から $G_{FF5}$ に切り替わるコンパレータ立ち上がり閾値 <sup>(1)</sup> |                                            | 0.644 |      | V    |

| $V_{FF5Rise}$ | $G_{FF5}$ から $G_{FF6}$ に切り替わるコンパレータ立ち上がり閾値 <sup>(1)</sup> |                                            | 0.751 |      | V    |

| $V_{FF6Rise}$ | $G_{FF6}$ から $G_{FF7}$ に切り替わるコンパレータ立ち上がり閾値 <sup>(1)</sup> |                                            | 0.875 |      | V    |

| $V_{FF0Fall}$ | $G_{FF1}$ から $G_{FF0}$ に切り替わるコンパレータ立ち下がり閾値 <sup>(1)</sup> | $V_{InSynth}$ のピーク値( $T_{HLinMax}$ ウィンドウ内) | 0.331 |      | V    |

| $V_{FF1Fall}$ | $G_{FF2}$ から $G_{FF1}$ に切り替わるコンパレータ立ち下がり閾値 <sup>(1)</sup> | $V_{InSynth}$ のピーク値( $T_{HLinMax}$ ウィンドウ内) | 0.386 |      | V    |

| $V_{FF2Fall}$ | $G_{FF3}$ から $G_{FF2}$ に切り替わるコンパレータ立ち下がり閾値 <sup>(1)</sup> | $V_{InSynth}$ のピーク値( $T_{HLinMax}$ ウィンドウ内) | 0.45  |      | V    |

| $V_{FF3Fall}$ | $G_{FF4}$ から $G_{FF3}$ に切り替わるコンパレータ立ち下がり閾値 <sup>(1)</sup> | $V_{InSynth}$ のピーク値( $T_{HLinMax}$ ウィンドウ内) | 0.524 |      | V    |

| $V_{FF4Fall}$ | $G_{FF5}$ から $G_{FF4}$ に切り替わるコンパレータ立ち下がり閾値 <sup>(1)</sup> | $V_{InSynth}$ のピーク値( $T_{HLinMax}$ ウィンドウ内) | 0.612 |      | V    |

| $V_{FF5Fall}$ | $G_{FF6}$ から $G_{FF5}$ に切り替わるコンパレータ立ち下がり閾値 <sup>(1)</sup> | $V_{InSynth}$ のピーク値( $T_{HLinMax}$ ウィンドウ内) | 0.713 |      | V    |

| $V_{FF6Fall}$ | $G_{FF7}$ から $G_{FF6}$ に切り替わるコンパレータ立ち下がり閾値 <sup>(1)</sup> | $V_{InSynth}$ のピーク値( $T_{HLinMax}$ ウィンドウ内) | 0.832 |      | V    |

| $G_{FF0}$     | 入力フィードフォワード・ゲイン値0 <sup>(1)</sup>                          |                                            | 1     |      | V    |

| $G_{FF1}$     | 入力フィードフォワード・ゲイン値1 <sup>(1)</sup>                          |                                            | 0.735 |      | V    |

| $G_{FF2}$     | 入力フィードフォワード・ゲイン値2 <sup>(1)</sup>                          |                                            | 0.541 |      | V    |

| $G_{FF3}$     | 入力フィードフォワード・ゲイン値3 <sup>(1)</sup>                          |                                            | 0.398 |      | V    |

| $G_{FF4}$     | 入力フィードフォワード・ゲイン値4 <sup>(1)</sup>                          |                                            | 0.292 |      | V    |

| $G_{FF5}$     | 入力フィードフォワード・ゲイン値5 <sup>(1)</sup>                          |                                            | 0.215 |      | V    |

| $G_{FF6}$     | 入力フィードフォワード・ゲイン値6 <sup>(1)</sup>                          |                                            | 0.158 |      | V    |

| $G_{FF7}$     | 入力フィードフォワード・ゲイン値7 <sup>(1)</sup>                          |                                            | 0.116 |      | V    |

| 最大オン時間        |                                                           |                                            |       |      |      |

## 電気的特性 (continued)

動作温度範囲内 (特に記述のない限り)

| PARAMETER                                                                      | TEST CONDITIONS                                                                                | MIN   | TYP   | MAX   | UNIT    |

|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-------|-------|-------|---------|

| $T_{ONMAX0}$ $G_{FF} = G_{FF0}$ のときの最大オン時間                                     |                                                                                                | 12.1  | 12.8  | 13.2  | $\mu s$ |

| $T_{ONMAX1}$ $G_{FF} = G_{FF1}$ のときの最大オン時間                                     |                                                                                                | 10.42 | 10.98 | 11.28 | $\mu s$ |

| $T_{ONMAX2}$ $G_{FF} = G_{FF2}$ のときの最大オン時間                                     |                                                                                                | 8.85  | 9.41  | 9.64  | $\mu s$ |

| $T_{ONMAX3}$ $G_{FF} = G_{FF3}$ のときの最大オン時間                                     |                                                                                                | 7.59  | 8.07  | 8.32  | $\mu s$ |

| $T_{ONMAX4}$ $G_{FF} = G_{FF4}$ のときの最大オン時間                                     |                                                                                                | 6.52  | 6.92  | 7.18  | $\mu s$ |

| $T_{ONMAX5}$ $G_{FF} = G_{FF5}$ のときの最大オン時間                                     |                                                                                                | 5.56  | 5.93  | 6.16  | $\mu s$ |

| $T_{ONMAX6}$ $G_{FF} = G_{FF6}$ のときの最大オン時間                                     |                                                                                                | 4.73  | 5.09  | 5.28  | $\mu s$ |

| $T_{ONMAX7}$ $G_{FF} = G_{FF7}$ のときの最大オン時間                                     |                                                                                                | 4.07  | 4.36  | 4.57  | $\mu s$ |

| <b>バースト・モード動作</b>                                                              |                                                                                                |       |       |       |         |

| $V_{BSTFall}$ VCOMP/バースト閾値立ち下がり                                                |                                                                                                | 0.5   |       |       | V       |

| $V_{BSTRise}$ VCOMP/バースト閾値立ち上がり                                                |                                                                                                | 0.625 |       |       | V       |

| <b>ゼロ電流検出およびバレー同期</b>                                                          |                                                                                                |       |       |       |         |

| $V_{ZcdVinHyst}$ ZcdVinコンパレータ・ヒステリシス <sup>(1)</sup>                            |                                                                                                | 12    | 19    | 26    | mV      |

| $T_{DCHVinMin}$ DRV立ち下がりエッジからのZcdVinコンパレータ・ブランкиング <sup>(1)</sup>              |                                                                                                | 250   | 358   | 467   | ns      |

| $T_{ZCDTo}$ この期間にVinコンパレータで負過渡が生じなければバレーを待たない                                  |                                                                                                | 2.035 | 2.4   | 3.0   | $\mu s$ |

| $T_{ZCDR0}$ ZCD-DRV間の最小遅延。                                                     | $V_{ZC} < V_{InSynth}$ からDRV = 6V、 $C_{DR} = 1nF$ 、 $F_{res} = 1.2MHz$ 、 $R_{DG} = R_{DG0}$ まで | 170   | 235   |       | ns      |

| $\Delta T_{ZCDR1}$ $T_{ZCDR1} = T_{ZCDR0} + \Delta T_{ZCDR1}$ <sup>(1)</sup>   | $R_{DG} = R_{DG1}$                                                                             | 34.6  | 45.5  | 58.5  | ns      |

| $\Delta T_{ZCDR2}$ $T_{ZCDR2} = T_{ZCDR0} + \Delta T_{ZCDR2}$ <sup>(1)</sup>   | $R_{DG} = R_{DG2}$                                                                             | 76    | 90    | 107   | ns      |

| $\Delta T_{ZCDR3}$ $T_{ZCDR3} = T_{ZCDR0} + \Delta T_{ZCDR3}$ <sup>(1)</sup>   | $R_{DG} = R_{DG3}$                                                                             | 114   | 130   | 147   | ns      |

| $\Delta T_{ZCDR4}$ $T_{ZCDR4} = T_{ZCDR0} + \Delta T_{ZCDR4}$ <sup>(1)</sup>   | $R_{DG} = R_{DG4}$                                                                             | 157   | 175   | 193   | ns      |

| $\Delta T_{ZCDR5}$ $T_{ZCDR5} = T_{ZCDR0} + \Delta T_{ZCDR5}$ <sup>(1)</sup>   | $R_{DG} = R_{DG5}$                                                                             | 229   | 255   | 281   | ns      |

| $\Delta T_{ZCDR6}$ $T_{ZCDR6} = T_{ZCDR0} + \Delta T_{ZCDR6}$ <sup>(1)</sup>   | $R_{DG} = R_{DG6}$                                                                             | 301   | 335   | 369   | ns      |

| $\Delta T_{ZCDR7}$ $T_{ZCDR7} = T_{ZCDR0} + \Delta T_{ZCDR7}$ <sup>(1)</sup>   | $R_{DG} = R_{DG7}$                                                                             | 373   | 415   | 457   | ns      |

| $V_{DDAmp1}$ 二一検出器の検知に必要なZCD/CS端子の500kHz正弦波信号の振幅                               |                                                                                                | 25    |       |       | mV      |

| $T_{DCHDDMin}$ 二一ポイント検出器のブランкиング期間 <sup>(1)</sup>                              | DRV/パルスの立ち下がりエッジから測定                                                                           | 1.5   |       |       | $\mu s$ |

| <b>異常保護</b>                                                                    |                                                                                                |       |       |       |         |

| $T_{LongFlt}$ 長い異常期間 <sup>(1)</sup>                                            |                                                                                                | 1     |       |       | s       |

| <b>入力ブラウンイン保護</b>                                                              |                                                                                                |       |       |       |         |

| $V_{ZCBoRise}$ StopB状態でのブラウンアウト保護閾値                                            | ZCD/CS端子のピーク・サイクル平均電圧。                                                                         | 0.282 | 0.3   | 0.318 | V       |

| $I_{ZCBias}$ ZCD/CS端子バイアス電流 <sup>(1)</sup>                                     | $V_{ZC} = V_{ZCBoFall}$                                                                        | - 100 | 100   |       | nA      |

| <b>過電流保護</b>                                                                   |                                                                                                |       |       |       |         |

| $V_{ZCOcp1}$ ZCD/CS 1次過電流保護閾値                                                  |                                                                                                | 450   | 500   | 550   | mV      |

| $V_{ZCOcp2}$ ZCD/CS 2次過電流保護閾値                                                  |                                                                                                | 670   | 750   | 825   | mV      |

| $T_{Ocp1Blk}$ DRV立ち上がりエッジからOcp1コンパレータ出力カイネーブルまでのZCD/CSブランкиング時間 <sup>(1)</sup> |                                                                                                | 450   |       |       | ns      |

| $T_{Ocp2Blk}$ DRV立ち上がりエッジからOcp2コンパレータ出力カイネーブルまでのZCD/CSブランкиング時間 <sup>(1)</sup> |                                                                                                | 250   |       |       | ns      |

| $T_{OcpDrvDel}$ ZCD/CSが $V_{OcpxTh}$ を交差してからDRV立ち下がりエッジまで。                     |                                                                                                | 56    | 120   |       | ns      |

## 電気的特性 (continued)

動作温度範囲内 (特に記述のない限り)

| PARAMETER                                                                            | TEST CONDITIONS       | MIN   | TYP   | MAX   | UNIT          |

|--------------------------------------------------------------------------------------|-----------------------|-------|-------|-------|---------------|

| $T_{DCHMax0}$<br>ZCD信号が検出されない場合の $T_{DCHb}$ 状態の最長期間。OCPx事象がなかつた後 <sup>(1)</sup>      |                       |       | 250   |       | $\mu\text{s}$ |

| $T_{DCHMax1}$<br>ZCD信号が検出されない場合の $T_{DCHb}$ 状態の最長期間。OCPx事象が1回生じた後 <sup>(1)</sup>     |                       |       | 500   |       | $\mu\text{s}$ |

| $T_{DCHMax2}$<br>ZCD信号が検出されない場合の $T_{DCHb}$ 状態の最長期間。OCPx事象が2回連続して生じた後 <sup>(1)</sup> |                       |       | 1000  |       | $\mu\text{s}$ |

| <b>出力過電圧保護</b>                                                                       |                       |       |       |       |               |

| $V_{OSOovp1Rise}$<br>VOSNS過電圧閾値、立ち上がり                                                | $V_{CC} = 12\text{V}$ | 2.69  | 2.75  | 2.81  | V             |

| $V_{OSOovp1Fall}$<br>VOSNS過電圧閾値、立ち下がり                                                | $V_{CC} = 12\text{V}$ | 2.60  | 2.675 | 2.73  | V             |

| $V_{OSOovp1Hyst}$<br>$V_{OSOovp1Rise} - V_{OSOovp1Fall}$ <sup>(1)</sup>              |                       | 0.072 |       |       | V             |

| $T_{Ovp2Blk}$<br>DRVの立ち下がリエッジ後のこの期間にOvp2コンパレータ出力がブランкиングされる <sup>(1)</sup>           |                       | 520   | 620   | 720   | ns            |

| $T_{Ovp2bEn}$<br>Ovp3コンパレータ出力の立ち下がリエッジ後のこの期間にOvp2b異常が検出され、ZCDが検出される <sup>(1)</sup>   |                       | 620   | 720   | 820   | ns            |

| $V_{Ovp2Th}$<br>2次出力過電圧異常閾値                                                          |                       | 1.102 | 1.125 | 1.148 | V             |

| <b>過熱保護動作</b>                                                                        |                       |       |       |       |               |

| $T_{TSDRise}$<br>温度上昇中に過熱保護動作を開始する温度閾値 <sup>(1)</sup>                                | スイッチング動作時             | 135   | 145   | 155   | °C            |

| $T_{TSDFall}$<br>温度が下降中に過熱保護動作を停止する温度閾値 <sup>(1)</sup>                               | スイッチング動作停止中           | 95    | 105   | 115   | °C            |

| $T_{TSDHyst}$<br>$T_{TSDRise} - T_{TSDFall}$ <sup>(1)</sup>                          |                       | 38    | 40    | 42    | °C            |

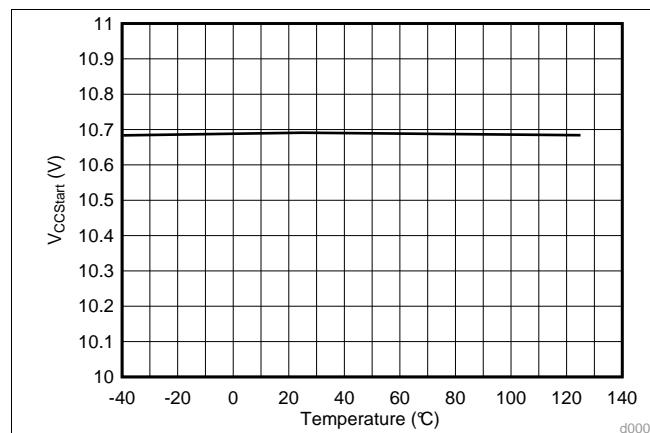

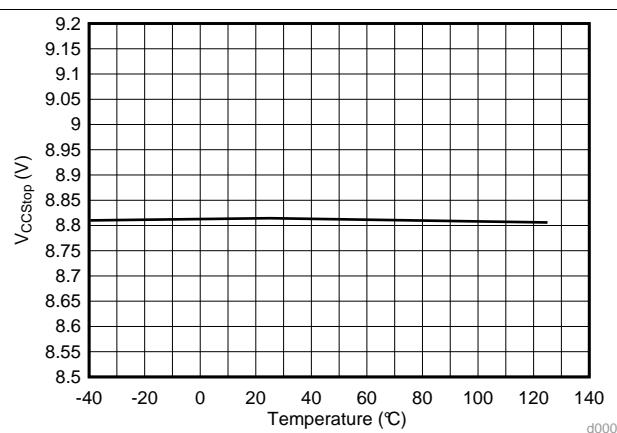

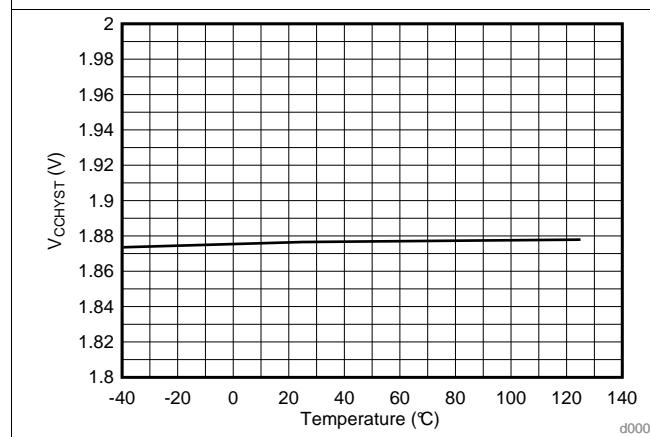

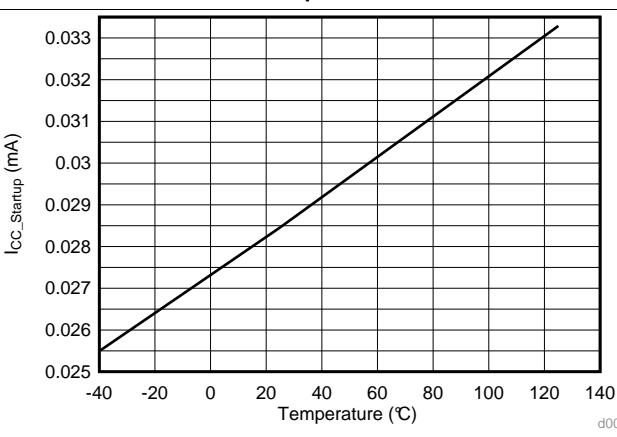

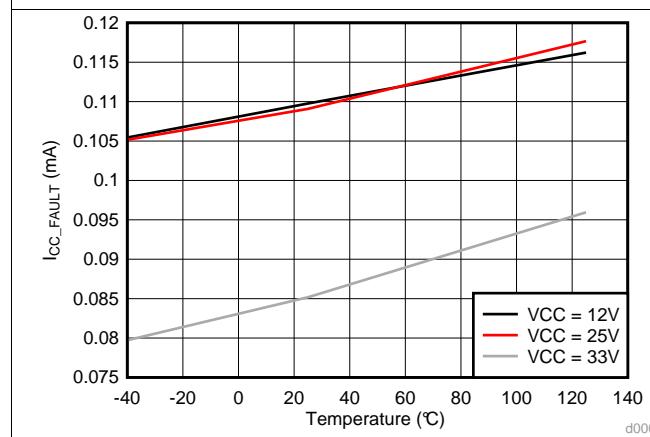

## 6.6 代表的特性

図 1. VCCStart閾値と温度との関係

図 2. VCCStop閾値と温度との関係

図 3. VCCヒステリシスと温度との関係

図 4. VCCスタートアップ電流と温度との関係

図 5. VCC異常電流と温度との関係

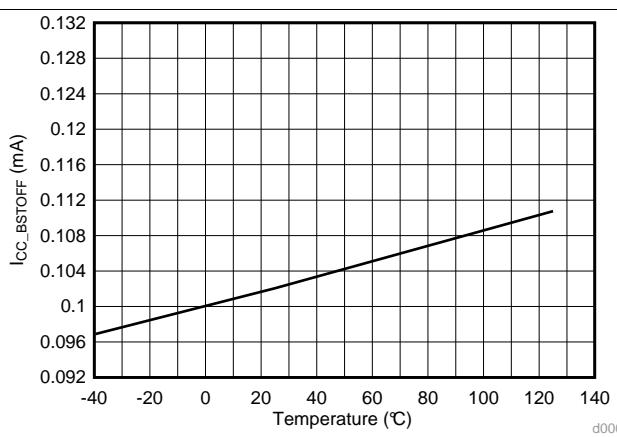

図 6. VCC/バースト・オフ電流と温度との関係

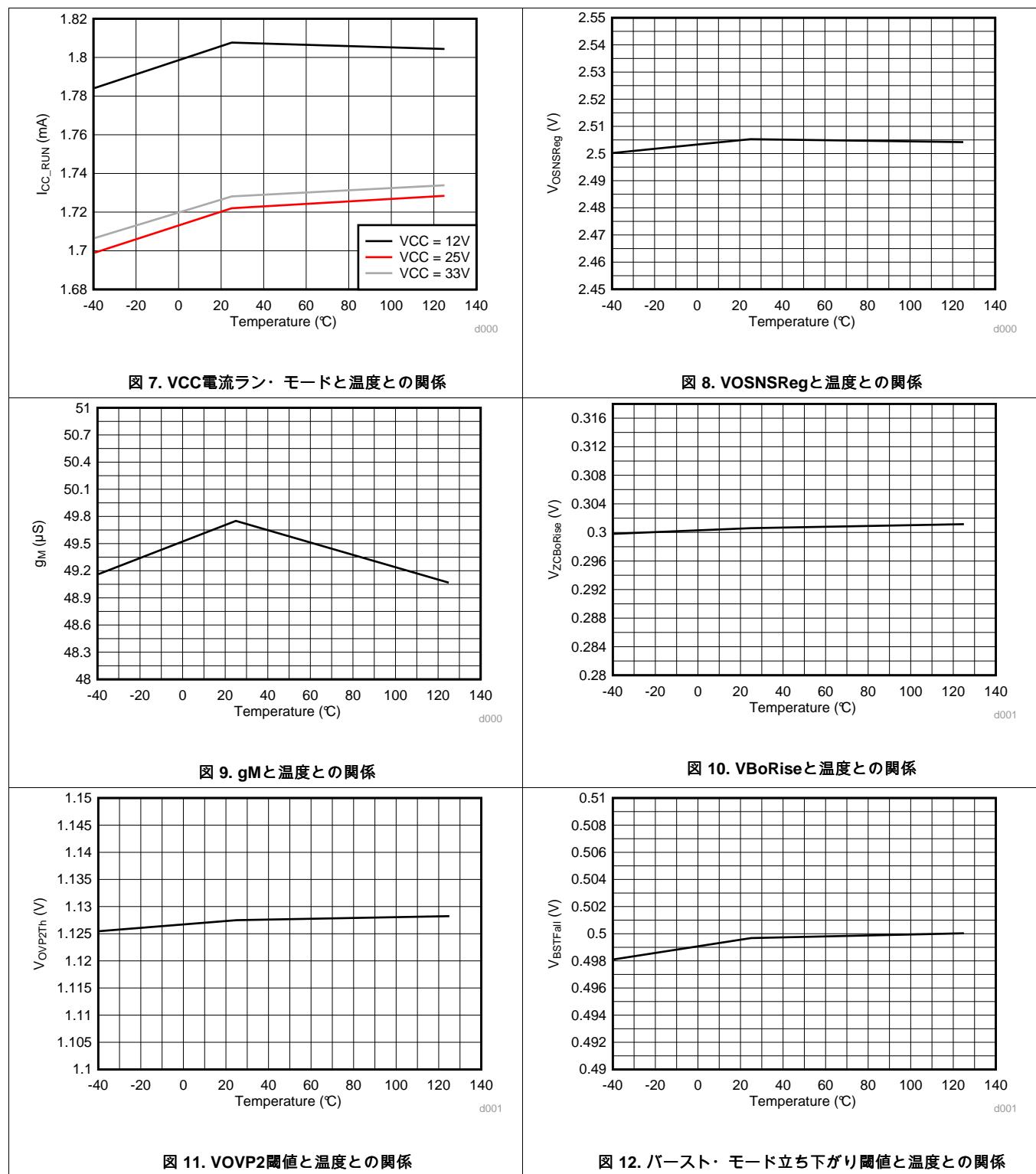

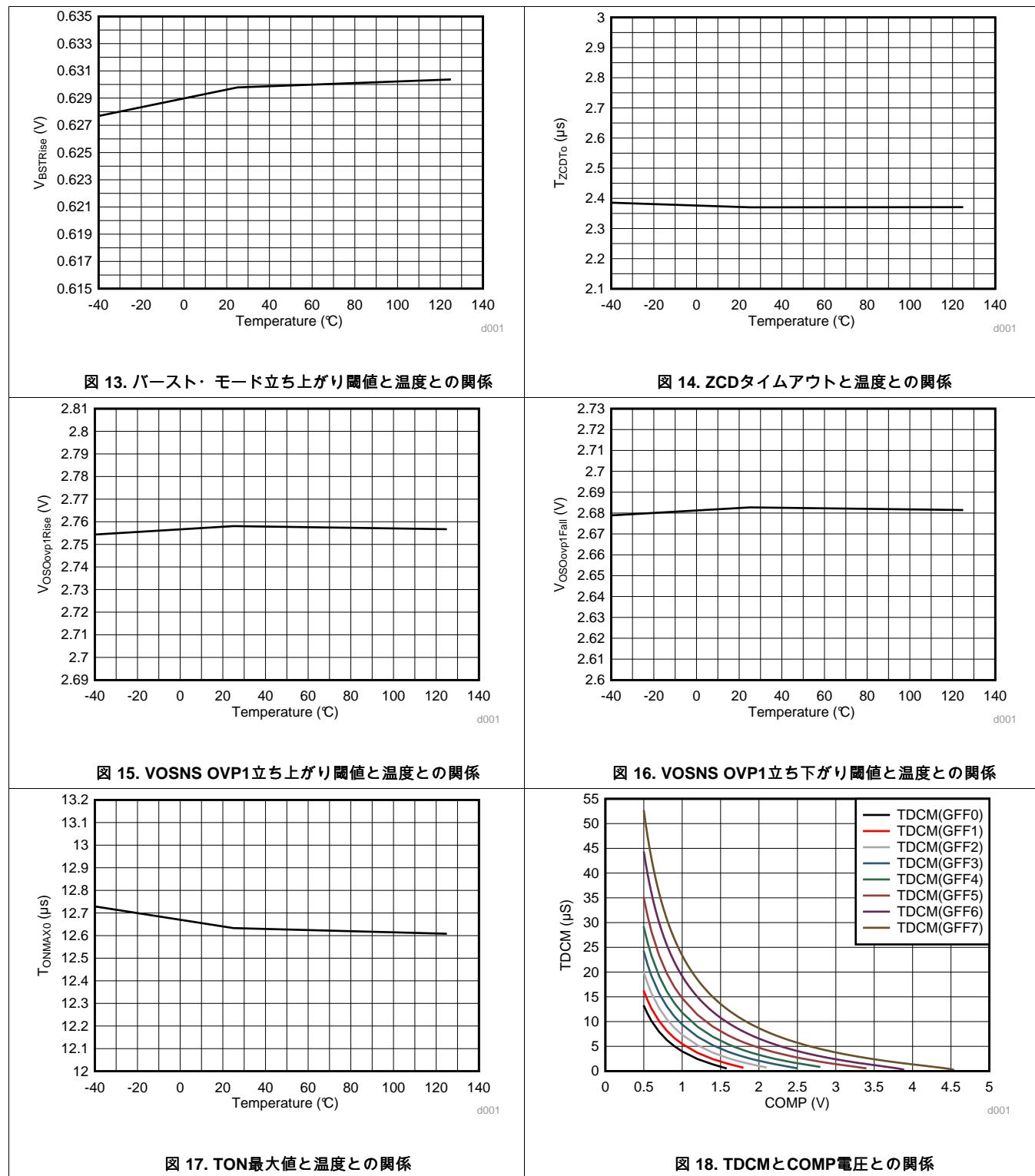

**代表的特性 (continued)**

## 代表的特性 (continued)

## 7 詳細説明

### 7.1 概要

UCC28056とUCC256301を組み合わせることにより、300W超を供給する完全なPFC/LLC絶縁型オフライン電源システムを制御できます。この複合電源は、効率とスタンバイ消費電力の厳しい要件を満たすように設計されており、補助フライバック・コンバータが不要である上に、軽負荷条件下でPFCをオフする必要もありません。このため、より簡素で低成本の電源を設計し、最新のグリーン電力基準を満たすことができます。

UCC28056には、全入力/負荷範囲にわたって動作効率を最大限に高める機能が豊富に搭載されています。汎用性の高いCrM/DCM制御アルゴリズムにより、フルパワー時には遷移モードで動作し、その後、負荷が下がるとシームレスにDCMに移行でき、入力電流高調波や力率が犠牲になることもありません。全負荷時には最大周波数(遷移モード)で動作し、その後、負荷が低減すると自動的にスイッチング周波数を下げ、DCM動作に移行することにより、最大限の効率を確保します。

負荷が10%を下回ると自動的にバースト・モードでの動作に移行するため、さらに軽負荷効率は向上し、スタンバイ消費電力も低減されます。バースト・オフ期間中は、内部回路の大半をオフにして、コントローラの消費電力を最小限に抑えます。

UCC28056は、サイクル単位の電流制限、過電流保護、デュアル個別出力過電圧保護、入力ブラウンイン、過熱保護動作、電源低電圧誤動作防止(UVLO)といった多種多様な異常保護機能を備えています。

量子化された7つの値の入力電圧フィードフォワードにより、ループ・ゲインが入力電圧からほぼ独立した形になるため、出力電圧制御ループの設計が簡単です。非線形エラー・アンプにより、定常状態の入力電流高調波を増大させずに、負荷の大きな変動に対する応答を大幅に改善することができます。

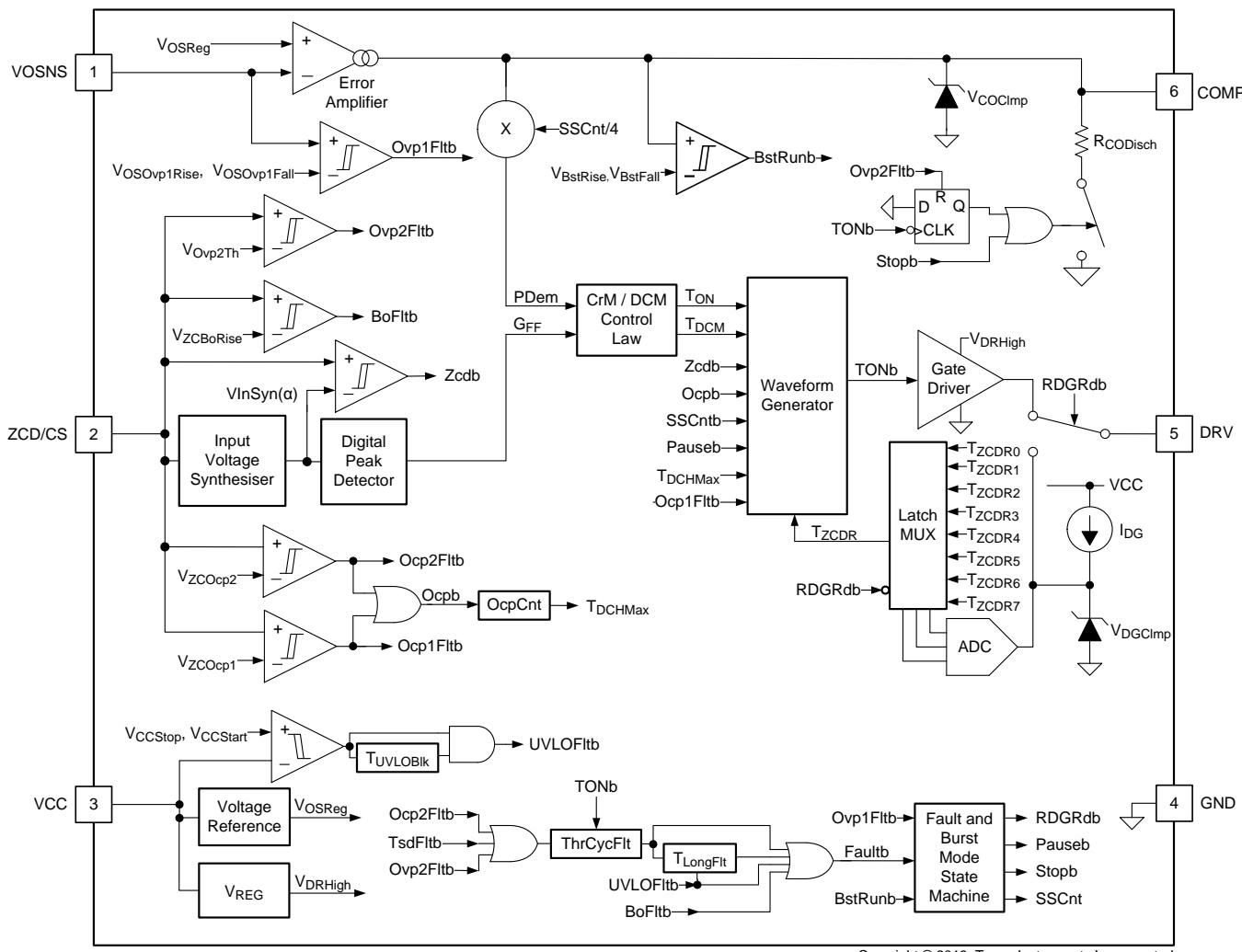

## 7.2 機能ブロック図

Copyright © 2018, Texas Instruments Incorporated

## 7.3 機能説明

### 7.3.1 CrM/DCM制御原理

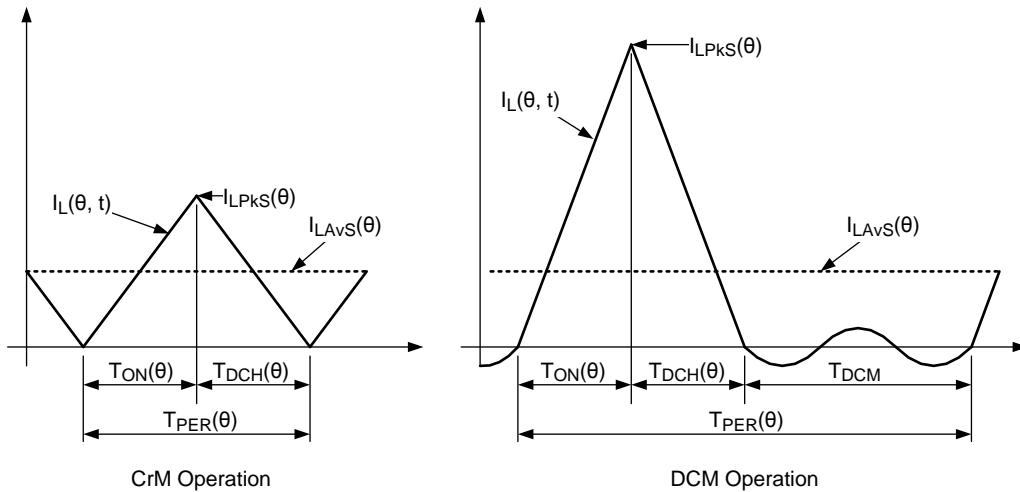

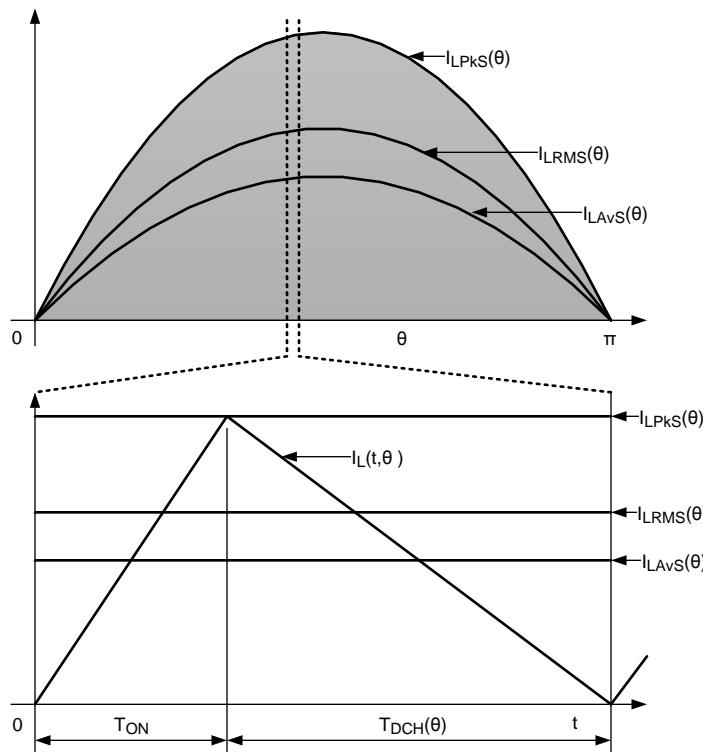

図 19. CrM/DCM動作におけるPFCインダクタ電流の波形

入力サイクル中に角度( $\theta$ )で発生する1つのスイッチング・サイクルについて考えます。理想的なCrM動作を仮定すると、スイッチング・サイクル中に流れる平均インダクタ電流( $I_{L\text{AvS}}(\theta)$ )は次の式で求められます。

$$I_{L\text{AvS}}(\theta) = \frac{I_{L\text{PkS}}(\theta)}{2} = V_{\text{In}}(\alpha) \times \frac{T_{\text{ON}}(\theta)}{2 \times L_{\text{BST}}} = \frac{V_{\text{In}}(\theta)}{R_{\text{InEq}}}$$

(1)

固定回路には定インダクタンス( $L_{\text{BST}}$ )があるため、入力サイクル全体にわたってオン期間( $T_{\text{ON}}(\theta)$ )が一定( $T_{\text{ON}}$ )を保てば、平均入力電流は入力電圧に比例したままとなります。つまり、この方法で制御すると、ブースト・コンバータが入力に接続した負荷抵抗( $R_{\text{InEq}}$ )のように振る舞います。

$$R_{\text{InEq}} = \frac{2 \times L_{\text{BST}}}{T_{\text{ON}}}$$

(2)

次にDCM動作について考えます。式3はスイッチング・サイクル中に流れる平均インダクタ電流を表します。

$$I_{L\text{AvS}}(\theta) = \frac{I_{L\text{PkS}}(\theta)}{2} \times \frac{T_{\text{ON}}(\theta) + T_{\text{DCH}}(\theta)}{T_{\text{PER}}(\theta)} = V_{\text{In}}(\theta) \times \frac{T_{\text{ON}}(\theta) \times \delta_{\text{ONDCH}}(\theta)}{2 \times L_{\text{BST}}} = \frac{V_{\text{In}}(\theta)}{R_{\text{InEq}}}$$

(3)

平均入力電流が入力電圧に比例するためには、入力サイクル全体にわたってオンタイムの積 $T_{\text{ON}}(\theta) \times \delta_{\text{ONDCH}}(\theta)$ が一定に保たれる必要があります。式4に等価入力抵抗を示します。

$$R_{\text{InEq}} = \frac{2 \times L_{\text{BST}}}{T_{\text{ON}} \times \delta_{\text{ONDCH}}}$$

(4)

最小入力電圧( $V_{\text{InMinPkL}}$ )から最大電力( $P_{\text{InMax}}$ )を引き出すには、最小実効入力抵抗( $R_{\text{InEqMin}}$ )が必要です。

$$P_{\text{InMax}} = \frac{V_{\text{InMinPkL}}}{2 \times R_{\text{InEqMin}}}$$

(5)

## 機能説明 (continued)

最小入力動作時のフルパワー動作はCrMモードであると仮定します。式 6を用いて、最小入力から最大電力を引き出すために必要なPFCインダクタ値を計算します。

$$R_{InEqMin} = \frac{2 \times L_{BST}}{T_{ONMAX0}}$$

ここで

- $T_{ONMAX0}$ は最大オン時間です。 (6)

入力電力要求は、最大入力電力に対する入力電力の比で表します。

$$\frac{P_{In}}{P_{InMax}} = \frac{V_{InPkl}^2}{V_{InMinPkl}^2} \times \frac{R_{InEqMin}}{R_{InEq}} = \frac{V_{InPkl}^2}{V_{InMinPkl}^2} \times \frac{T_{ON}(\theta) \times \delta_{ONDCH}(\theta)}{T_{ONMAX0}} \quad (7)$$

式 8は式 7を並べ替えて、 $T_{ON}(\theta)$ 時間を電力要求の関数として表しています。

$$T_{ON}(\theta) = P_{Dem} \times \frac{V_{InMinPkl}^2}{V_{InPkl}^2} \times T_{ONMAX0} \times \frac{1}{\delta_{ONDCH}(\theta)} = \frac{V_{CO}}{V_{COMax}} \times G_{FF} \times \frac{T_{ONMAX0}}{\delta_{ONDCH}(\theta)} \quad (8)$$

式 8はUCC28056に実装されているCrM/DCM  $T_{ON}$ 制御原理を示しています。この式は本来は二次式ですが、UCC28056では前のサイクルの $\delta_{ONDCH}(\theta)$ の値を基準にして、現在のサイクルの $T_{ON}(\theta)$ を計算します。このプロセスは、反復法により方程式を数値的に解くのと似ています。

CrM/DCMでの軽負荷動作には、幅広い動作周波数の選択肢があります。定電流パルス、高周波のCrMモード( $T_{DCM} = 0$ )で動作できる一方、最大振幅の電流パルス、最低周波のDCMモード( $T_{DCM} = T_{DCMMax}$ )でも動作可能であり、この2つの値の間でUCC28056が $T_{DCM}$ 値を選択できます。導通損失は通常、最低動作周波数での動作時に集中しており、効率の低下につながります。スイッチング損失は通常、最高動作周波数(CrM)での動作時に集中しており、これもまた効率の低下につながります。一般に、最も効率のよい動作周波数が生じるのは、パルス電流振幅が最大値の約1/3になるときです。

$$\frac{I_{LPkSOpt}}{2 \times I_{LMaxPkl}} = \frac{1}{3.5} \quad (9)$$

$$I_{LMaxPkl} = \frac{V_{InMinPkl} \times T_{ONMAX0}}{2 \times L_{BST}} \quad (10)$$

UCC28056では、入力サイクルのピーク・インダクタ電流が $I_{LPkSOpt}$ を下回ると、CrM動作からDCM動作に遷移します。DCM動作時には、スイッチング周波数を調整して、あらゆる入力/負荷状態でも入力サイクルのピーク・インダクタ電流が $I_{LPkSOpt}$ 付近に保たれるようにします。このようにUCC28056は、あらゆる負荷、入力電圧条件下で最大限の効率を実現しようとします。

## 機能説明 (continued)

### 7.3.2 入力電圧フィードフォワード

UCC28056では、入力電圧フィードフォワードをCOMP端子の電圧( $V_{CO}$ )に印加してから、 $T_{ON}$ および $T_{DCM}$ 期間を計算します。この制御順序により、入力電圧に関係なく、COMP電圧が入力電力を表現し、すべての入力電圧において同じ値の出力電力でバースト動作が生じることになります。また、COMP端子電圧と入力電力の間に固定ゲインが確保されるため、電圧制御ループの補償も簡素化されます。

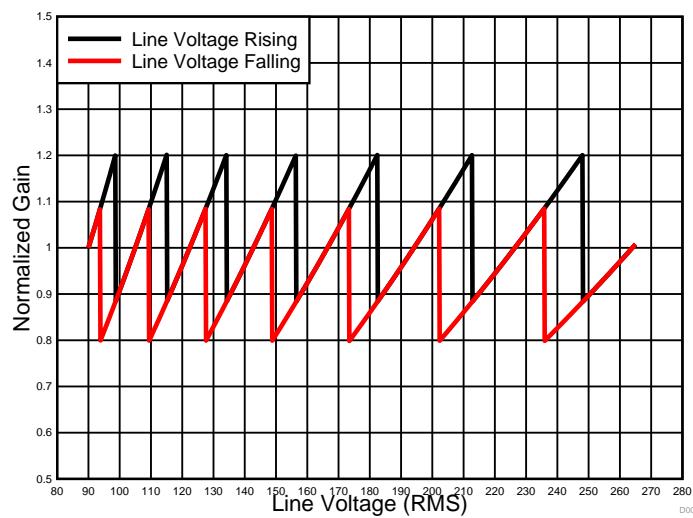

$$G_{FF} = \left( \frac{V_{InMinPkL}}{V_{InPkL}} \right)^2 \quad (11)$$

計算を容易にするため、UCC28056では7つの離散的な $G_{FF}$ 値を採用しており、ピーク入力電圧値を監視する一連のコンパレータによって最適な値が選択されます。各コンパレータにはヒステリシスが組み込まれているため、選択した $G_{FF}$ 値の反復的な変動と、その結果生じる入力電流のステップ変動を回避できます。コンパレータの閾値と $G_{FF}$ 値は、入力電力ゲイン( $P_{In}/V_{CO}$ )に対する要求が全ユニバーサル入力電圧範囲(90 ~ 264V<sub>RMS</sub>)で±20%を超えて変動しないように選択されます。

#### 7.3.2.1 ピーク入力電圧検出

UCC28056は、ピーク入力電圧検知およびゼロ電流検出(ZCD)に向けて、内部で入力電圧波形を再構成します。DCM/CRMモードでは、ブースト・インダクタを通ったサイクル平均電圧がゼロでなければいけません。

UCC28056は、ZCD/CS端子の波形からドレイン波形を抽出し、それをフィルタ処理してスイッチング・サイクルの平均ドレイン電圧( $V_{InSyn}(\theta)$ )を抽出することにより、入力電圧の内部表現を生成します。

デジタル・ピーク検出器は、 $G_{FF}$ の値を、 $T_{HLinMax}$ 期間に交差した最も高いコンパレータ閾値に基づいて選択します。高い $G_{FF}$ 値へのスイッチは、当該閾値を公差するとすぐ実行されます。低い $G_{FF}$ 値へのスイッチは、 $T_{HLinMax}$ 期間が満了し、ピーク検出器が入力電圧ピークを捕捉した時点でしか実行されません。 $T_{HLinMax}$ タイマは入力動作周波数に同期しません。

スイッチング動作の開始前、電源投入時、またはバースト・オフ期間後に、ZCD/CS端子の電圧をサンプリングし、これを用いて適切な始動 $G_{FF}$ 値を選択します。この方法は、スイッチングを行っていない期間中に、入力整流器および整流器ブリッジ後のコンデンサがピーク入力電圧を捕捉したと仮定しています。

図 20. 正規化したゲインと入力電圧との関係

## 機能説明 (continued)

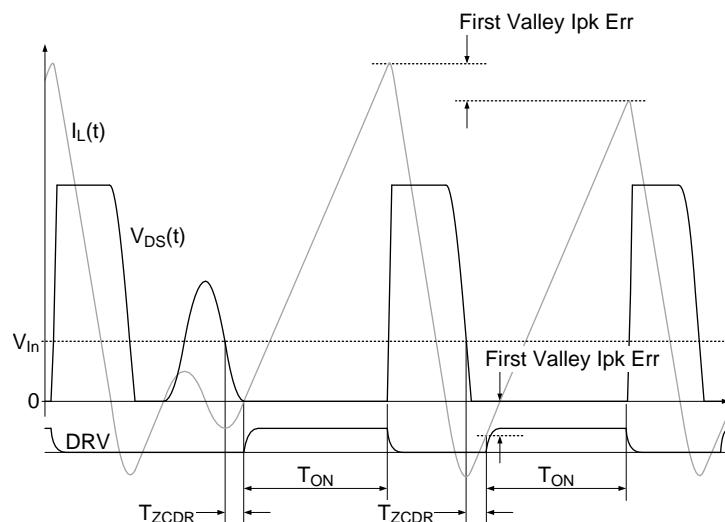

### 7.3.3 バレー・スイッチングとCrM/DCMヒステリシス

UCC28056は最大限の効率を実現し、これにより $T_{DCM}$ 期間中に生じる共振に関して、MOSFETのドレイン電圧が最小(バレーともいう)であるときの電力スイッチング動作が可能になります。ドレイン・ノード容量( $C_{DE}$ )に蓄積した電力は、その遷移時間中に電源スイッチで消費されます。バレー・スイッチングでは、動作開始前に最小限の電力が $C_{DE}$ に蓄積されるため、スイッチング損失を最小限に抑えることができます。 $T_{DCM}$ 期間の後、UCC28056は次の利用可能なドレイン電圧のバレーを待ってから、新しいスイッチング・サイクルを起動します。このため、実際の $T_{DCM}$ 期間は、常にドレイン共振期間の整数倍となります。計算した $T_{DCM}$ 期間がバレー境界を超えている場合、実際の $T_{DCM}$ 期間の値は1共振期間分ステップアップします。この $T_{DCM}$ 期間のステップ変動は、入力電流のステップ変動を引き起こし、 $T_{ON}(\theta)$ の計算が $T_{DCM}$ 期間のステップ変動を反映するように新しい解を求めて反復するため急速に減衰します。バレー遷移の結果生じる入力電流歪みは、COMP電圧から $T_{DCM}$ 期間を計算することによって最小限に抑えます。COMP電圧は入力サイクルの期間にわたって若干変動するため、計算した $T_{DCM}$ 期間は入力サイクルの期間にわたってごくわずかに変動します。

入力電流歪みは、特に入力電圧が低いときの最初のバレー(CrM)から次のバレー(DCM)動作への遷移中に大きくなります。この領域では、電源スイッチ・ボディ・ダイオードのクランピング動作によって、最初のバレー期間が延長されます。この領域では、最初のバレー(CrM)をオンにした時点で入力電流が低減します。これは、オン期間の開始時にインダクタ電流が負になるためです。入力電流の低減は、2つ目以降のバレー(DCM)動作では確認されません。これは、インダクタ電流がゼロからオン期間を開始するためです。UCC28056には $T_{DCM}$ 計算のヒステリシスが内蔵されているため、入力サイクルにおいてCrM/DCM遷移が繰り返される可能性はほとんどありません。そのような遷移が起こるのは、CrM/DCM境界で、COMP電圧における入力周波数の2倍のリップルが12%を上回っている場合のみです。

図 21. DCMからCrMに遷移するドレイン電圧とインダクタ電流

#### 7.3.3.1 バレー遅延調整

UCC28056は、さまざまな自然共振周波数を持つ電力段の制御に際して、最大限の効率を実現します。各用途でこのような効率を実現できるのは、ZcdVInコンパレータの交差からDRVの立ち上がりエッジまでの遅延( $T_{ZCDR}$ )を外部で調整するからです。多種多様な自然共振周波数を持つさまざまな電力段の設計に最適なバレー・スイッチングです。

$T_{ZCDR}$ 遅延は、8つの値( $T_{ZCDR0}$  ~  $T_{ZCDR7}$ )のいずれかに設定でき、これはDRV端子とGND端子の間に外付けする抵抗( $R_{DG}$ )の値を設定して行います。スタートアップ期間中や長い異常からの回復時には、UCC28056はStopb状態からRDGRdb状態、その後BstOffb状態へと遷移します。RDGRdb状態では、内蔵電流源( $I_{DG}$ )がDRV端子に遷移します。この電流から生じる電圧によって、適切な $T_{ZCDR}$ 遅延が決まります。長い異常によって再びStopb状態になるまでは、この遅延期間をすべてのバレー・スイッチング動作に用います。

RDGRdb状態になつたら、 $T_{DGSmp}$ の間待機してから端子電圧を読み取ります。UCC28056が常に外付け抵抗値を正しく検出できるよう、DRV端子とGND端子の間にに入る外部容量の合計は12nFを超えないものとします。

## 機能説明 (continued)

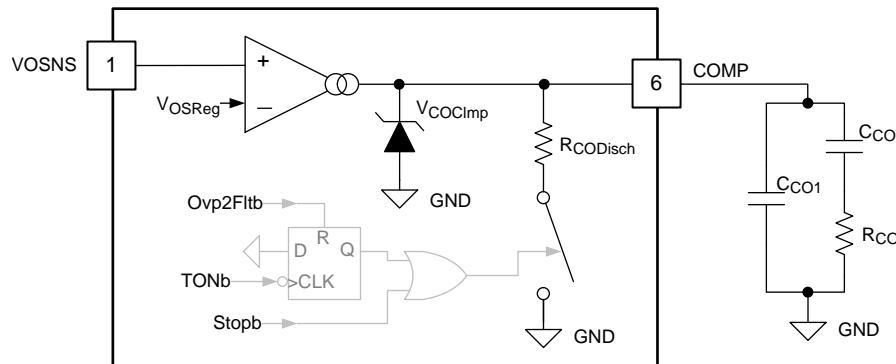

### 7.3.4 過渡応答高速化機能を備えたトランスコンダクタンス・アンプ

電圧エラー・アンプは、トランスコンダクタンス・アンプです。電圧ループ補償はエラー・アンプ出力から COMP、グランドへと接続します。推奨するタイプ2補償ネットワークを示します。ループ安定性を確保するため、UCC28056は公称トランスコンダクタンス・ゲイン $g_M$ を使用し、出力電圧の小信号変動に基づいて補償ネットワーク値を計算します。

図 22. 標準的な補償ネットワークを備えたトランスコンダクタンス・エラー・アンプ

大きな変動に対する過渡応答性能を高めるため、エラー・アンプ入力が $V_{OSReg}$ から $\pm 3\%$ を超えて逸脱すると、エラー・アンプ・ゲインが6倍に増大します。この増大により、負荷電流のステップ変動から回復するための補償部品の充電/放電を高速化できます。

### 7.3.5 異常と保護

UCC28056は多種多様な保護機能を備えているため、あらゆる条件下でも安定した動作を行います。

## 機能説明 (continued)

### 7.3.5.1 電源低電圧誤動作防止

電源低電圧誤動作防止(UVLO)機能により、正常動作と電源スイッチ駆動に必要な電圧振幅を担保するためにUVLO閾値を上回るまではUCC28056は休止状態となります。

$I_{CC}$ 電流の消費を最低限におさえています。 $V_{CCStart}$ を上回った時点で、UCC28056はウェークアップしてStopb状態に移行します。ウェークアップ後は通常のスタートアップ・プロセスを実行します。

VCC端子電圧が $V_{CCStop}$ を下回る状態が $T_{UVLOBlk}$ を超えると、UCC28056はスイッチングを停止します。そして再び休止状態となります。この休止期間中は、再び $V_{CCStart}$ 閾値を上回るまで消費電流( $I_{CC}$ )が比較的少なくなります。

### 7.3.5.2 2つの値の過電流保護

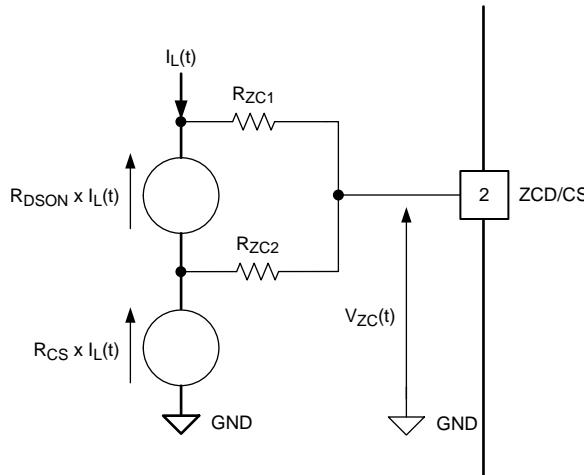

UCC28056は2つの過電流保護回路を採用しているため、過渡動作時の誤検知の危険性がなく、安全かつ安定した保護を提供します。スイッチがオンの間は、電源スイッチのソース・リードに接続した電流検知抵抗( $R_{CS}$ )がインダクタ電流を検知します。ZCD/CS端子は電流検知抵抗を通った電圧を検出します。式 12はZCD/CS端子に印加される電流検知電圧信号を表しています。一般に、括弧内の第2項は電流検知抵抗値( $R_{CS}$ )よりはるかに小さくなり、無視できます。

$$V_{ZC}(t) = I_L(t) \times \left( R_{CS} + R_{DSON} \times \frac{R_{ZC2}}{R_{ZC1} + R_{ZC2}} \right) \approx I_L(t) \times R_{CS} \quad (12)$$

図 23. 外部電流検知ネットワークの等価回路

#### 7.3.5.2.1 サイクル単位の電流制限Ocp1

電流検知電圧が0.5Vを上回ると、サイクル単位のピーク電流保護(Ocp1)がオンタイム( $T_{ON}$ )期間を早期終了します。この電流保護方式により、ピーク・インダクタ電流を抑制して、インダクタの飽和や電力段の損傷を防ぐことができます。サイクル単位の電流制限がアクティブになると、入力電流歪みに影響を与えますが、それ以外の点では通常のスイッチング動作が継続し、UCC28056は出力レギュレーションを維持します。

UCC28056は電流検知電圧信号にリーディング・エッジ・ブランкиングを印加し、こうすることで $C_{DE}$ の放電によって生じる電流スパイクが原因で、Ocp1コンパレータが時期尚早にDRVパルスを停止してしまうことを避けられます。

## 機能説明 (continued)

### 7.3.5.2.2 Ocp2による重大過電流/CCM保護

閾値が高く、ブランкиング時間が短い2次コンパレータ(Ocp2)も電流検知電圧信号を監視します。この2次コンパレータ(Ocp2)も、検知されると電流オンタイム( $T_{ON}$ )期間を早期終了します。またUCC28056は、3スイッチング・サイクル連続でOcp2コンパレータを検知した場合、長い異常も検知します。長い異常によってスイッチング動作は停止し、 $T_{LongFlt}$ 期間中はリスタートできません。この遅延の後に、UCC28056は通常のスタートアップ・プロセスを実行します。いずれの過渡条件または軽異常条件でも、Ocp1コンパレータが低い閾値により最初に検知するため、Ocp2コンパレータが動作することはありません。Ocp2コンパレータは、出力コンデンサやバイパス・ダイオードの短絡といった重大異常が生じた場合にのみ動作します。

出力過負荷など一部の異常条件では、リセット電圧が低いためにインダクタ電流が持続することがあります。この場合、比較的短いOcp1のブランкиング時間でも、インダクタ電流が継続的に上昇することができます。UCC28056はスイッチング周波数を下げることでこの条件に対処しており、これによりオンタイム・パルス間でインダクタ電流が降下する期間を延長できます。

いずれかのOcpコンパレータによってオンタイム期間が早期終了するたびに、最大許容ダイオード導通期間( $T_{DCHMax}$ )は順に倍増していきます(250μs、500μs、1000μs)。インダクタ電流がゼロまで降下したことを示すZCD信号がなければ、次のスイッチング・サイクルの前に $T_{DCHMax}$ 期間が満了し、スイッチング周波数が半分になるようにしなければなりません。いずれかのOcpコンパレータによってオンタイム期間が早期終了しないたびに $T_{DCHMax}$ 期間を順に半減していき、スイッチング周波数を回復します。ZCD信号がインダクタ電流がゼロに達したことを示していれば、 $T_{DCHMax}$ は何ら影響せず、自動的に通常動作が再開します。

### 7.3.5.3 出力過電圧保護

UCC28056には2つの独立した出力過電圧保護方式があります。これは、いかなる信号異常によっても過剰な出力電圧が生じないようにするためです。

#### 7.3.5.3.1 1次出力過電圧保護(Ovp1)

VOSNS端子は $R_{OS1}$ と $R_{OS2}$ からなる外付け分圧抵抗を通じて、出力コンデンサ電圧を監視します。内蔵コンパレータ(Ovp1)はVOSNS端子電圧( $V_{OS}$ )を監視します。この端子の電圧が $V_{Ovp1Rise}$ を上回れば、出力コンデンサ電圧が過剰であることを示しているため、UCC28056はBstOffb状態に遷移します。この状態では、出力コンデンサ電圧のさらなる上昇を防ぐためにスイッチングが停止します。 $V_{OS}$ が $V_{Ovp1Fall}$ を下回って、出力電圧が通常範囲に戻ると、UCC28056は再びRunb状態になり、スイッチング動作を再開します。可聴ノイズを抑制するため、Runb状態-BstOffb状態間の遷移中にオンタイム・パルス幅が動作を開始します。このランプ方式はバースト・モード動作の場合と同じです。

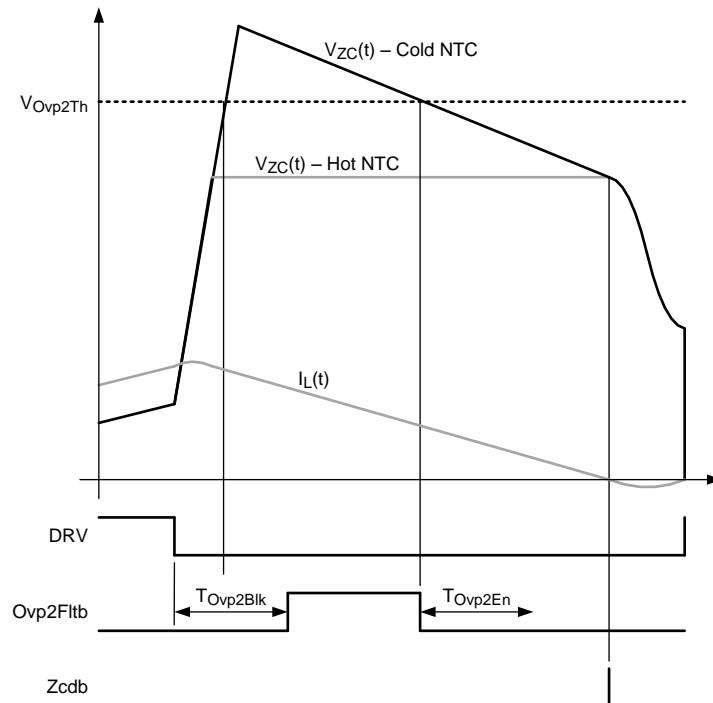

#### 7.3.5.3.2 2次過電圧保護(Ovp2)

バースト・ダイオードが導通している(また、バースト・ダイオードと直列のインピーダンスを無視している) $T_{DCH}$ 期間中は、MOSFETの電圧が出力電圧にほぼ等しくなります。UCC28056はZCD/CS端子に接続した外付け分圧ネットワークを介して、MOSFETの電圧を監視します。この監視により、VOSNS端子の分圧器が万一損傷しても、別の方法で過剰な出力電圧を検出することができます。固定閾値( $V_{Ovp2Th}$ )を持つOvp2コンパレータは、 $T_{DCH}$ 期間中にZCD/CS端子の電圧を監視します。DRV波形の立ち下がりエッジ後に固定ブランкиング期間( $T_{Ovp2Bk}$ )を印加することで、ドレンイン波形のリーディング・エッジにおける誘導性スパイクによりOvp2コンパレータがトリップしないようにします。

UCC28056は、突入電流制限NTC抵抗をバーストMOSFETの負荷側に配置して動作できます。NTC抵抗をこの位置に配置することで、定格電流の小さい小型のコントローラの使用が可能になり、効率が向上します。特に低温時には、NTCによる直列抵抗を通した電圧降下が原因で、バースト・ダイオードおよびNTC抵抗を流れる電流が最高値をとる $T_{DCH}$ 期間の前半などに、バーストMOSFETにおける電圧降下が出力電圧より高くなってしまいます。低温NTCが引き起こすバーストMOSFETの過電圧は、次の2つの重大な影響をもたらします。

- 出力電圧が過剰でないときにOvp2コンパレータがトリップされることがある。

- コールドスタート時にバーストMOSFETに印加された過電圧ストレスが原因で損傷することがある。

3スイッチング・サイクル連続でOvp2コンパレータ出力の立ち下がりエッジからZcdb信号までの時間が $T_{Ovp2En}$ を下回ると、UCC28056はOvp2異常を検知します。NTC抵抗を流れる電流が小さければ、Ovp2コンパレータをZcdb点付近にトリップしなければならないため、誤ったOvp2異常の検知に要する直列インピーダンスが大幅に増大します。

## 機能説明 (continued)

各スイッチング・サイクルでCOMP端子とGND端子の間の内蔵放電抵抗( $R_{C0Disch}$ )が接続されることによって、Ovp2コンパレータはトリップします。この内蔵抵抗は、外部補償ネットワークを放電して、電力要求を低減し、ひいてはNTC抵抗を流れるピーク電流を低減します。内蔵COMP放電抵抗は、Ovp2コンパレータを検知するスイッチング・サイクルでは、接続されたままとなります。Ovp2コンパレータを検知しない最初のスイッチング・サイクルの後、内蔵COMP放電抵抗は切断されます。この回路は、低温NTC抵抗を流れるピーク電流を抑制することにより、コールドスタート時にブーストMOSFETに印加されるピーク電圧を抑制できます。

図 24. Ovp2の動作を示す波形

### 7.3.5.4 過熱保護動作

UCC28056には温度センサが内蔵されています。スイッチング期間中に、3スイッチング・サイクル連続で内部シリコン温度が $T_{TSDRise}$ を上回ると、過熱保護動作(TSD)異常を検知します。TSD異常によりスイッチング動作は停止し、UCC28056は $T_{LongFlt}$ の間Stopb状態になります。この遅延の後、UCC28056は通常のスタートアップ・プロセスを続行します。

内部シリコン温度が $T_{TSDFall}$ を上回っている限り、Stopb状態を終了して、スイッチング動作を開始することはできません。

## 機能説明 (continued)

### 7.3.5.5 低入力電圧/ブラウンイン

入力整流器およびコンデンサはアナログ・ピーク検出器を形成し、入力に印加されるピーク入力電圧による電荷を蓄積します。このピーク入力電圧はブーストMOSFETを通して表れます。UCC28056はZCD/CS端子に接続した外付け分圧ネットワークを介して、ピーク入力電圧を監視します。入力電圧スタート・コンパレータにより、ZCD/CS端子電圧が $V_{ZCBoRise}$ 閾値を上回るまではStopb状態を終了できません。このため、入力電圧が出力電力をフルに供給できるほど十分高くなるまで(85V<sub>RMS</sub>)、スイッチング動作は開始しません。スイッチング動作中は、異常によりStopb状態に移行しない限り、入力電圧に関係なく動作を継続します。

### 7.3.6 大電流ドライバ

内蔵された大電流ドライバにより、UCC28056はパワーMOSFETスイッチを直接駆動できます。UCC28056はDRV端子に印加される電圧を $V_{DRHigh}$ に制限します。この制限により、パワーMOSFETの $V_{GS}$ 定格電圧を上回ることなく、高VCC電源電圧がUCC28056を駆動できます。また、この制限によって、 $V_{DRHigh}$ を上回るVCC電源電圧からUCC28056が動作する場合に内蔵ゲート・ドライバの消費電力が削減されます。

内蔵ドライバは、DRV端子およびGND端子の一時的な短絡から保護されます。

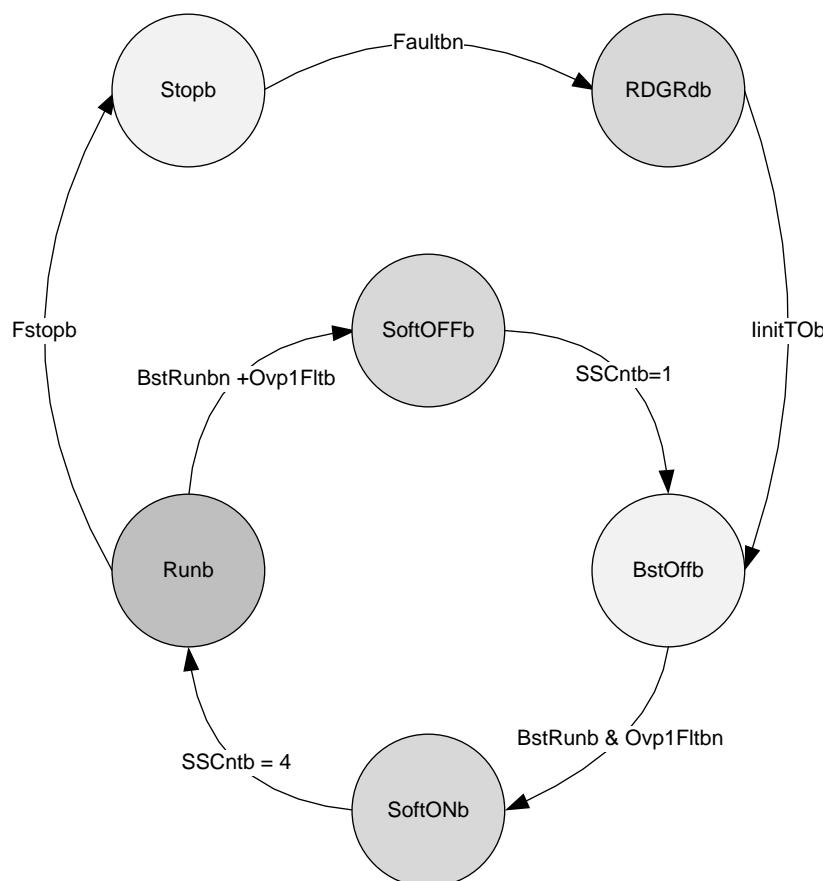

## 7.4 コントローラの機能モード

### 7.4.1 バースト・モード動作

UCC28056は、次のような特長を備えたバースト・モード動作を実装することで、業界トップクラスの軽負荷効率とスタンバイ消費電力を実現しています。

1. すべての入力電圧値で、バースト中の電力は最大出力電力の約11%になるように制御されます。

2. バースト・オフ期間中は、UCC28056の消費電流が $132\mu A$ 未満に下がります。

3. 各バースト・オン期間の最初の4サイクルで $T_{ON}$ パルス幅は動作を開始し、最後の4サイクルで動作を終了します。このソフトオン/オフ方式は、各バースト・オン期間のエッジで入力電流を流し始めることで、可聴ノイズおよびEMIフィルタの外乱を抑制します。

COMP端子電圧に印加される2つのコンパレータ閾値により、バースト・モード動作を行います。COMP端子電圧が $V_{BstFall}$ 閾値を下回ると、4ソフトオフ・サイクル後にスイッチングが停止します。COMP端子電圧が $V_{BstRise}$ 閾値を上回ると、4ソフトオン・サイクルでスイッチングが再開します。この2つの閾値の平均電圧は約11%の $V_{COMax}$ に相当します。バースト・オン中に供給される電力は最大入力電力の約11%です。

図 25. 異常およびバースト・モード状態の図

### 7.4.2 ソフト・スタート

Stopb状態での動作中、内蔵抵抗( $R_{CODisch}$ )はCOMP端子とGND端子の間に接続され、外部補償ネットワークを放電します。COMP端子電圧が $V_{BstRise}$ 閾値を上回って初めて、スタートアップからBstOffb状態を経て、スイッチングが開始します。したがって、スイッチングは常に電力要求がその最大値の12.5%になると開始します。ソフトオン機能によって、最初の4スイッチング・サイクルで、オンタイム期間が要求される値まで上昇するようになります。この機能により、スタートアップ時の可聴ノイズを抑制できます。

UCC28056はスタートアップ時にエラー・アンプの高速過渡ゲインをイネーブルするため、入力電力は外部補償ネットワークの時定数のみが制限する速度で最大まで上昇します。このため、出力容量が素早く変化して、スタートアップ遅延を抑制することができます。

## 8 アプリケーションと実装

### 注

以降のアプリケーション情報は、TIの製品仕様に含まれるものではなく、TIではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 アプリケーション情報

UCC28056は、PFC段を必要とする幅広いアプリケーションに使用できます。この設計例はUCC28056の機能を紹介するものです。

- EVMハードウェア

- Excel設計計算ツール

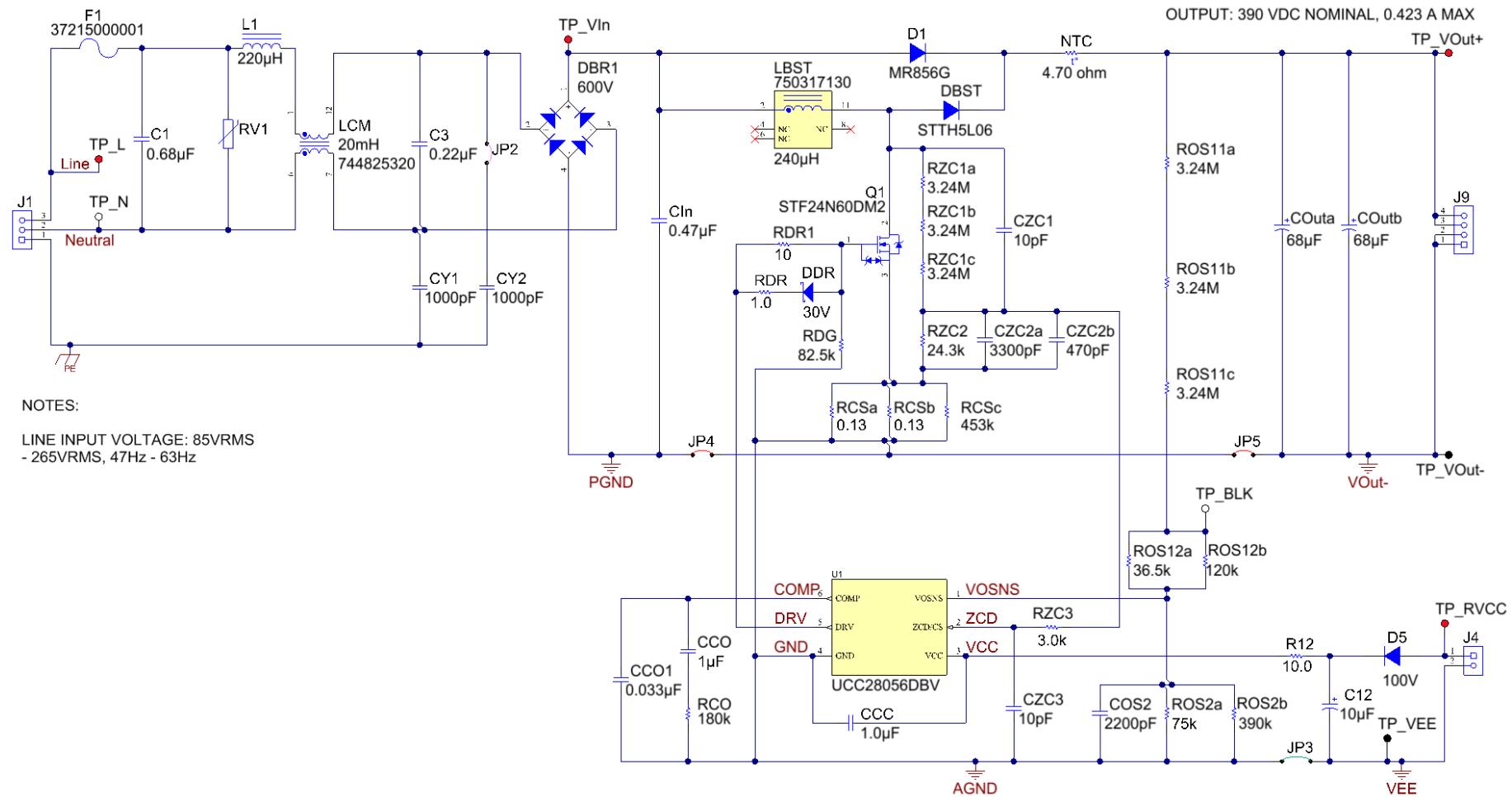

### 8.2 代表的なアプリケーション

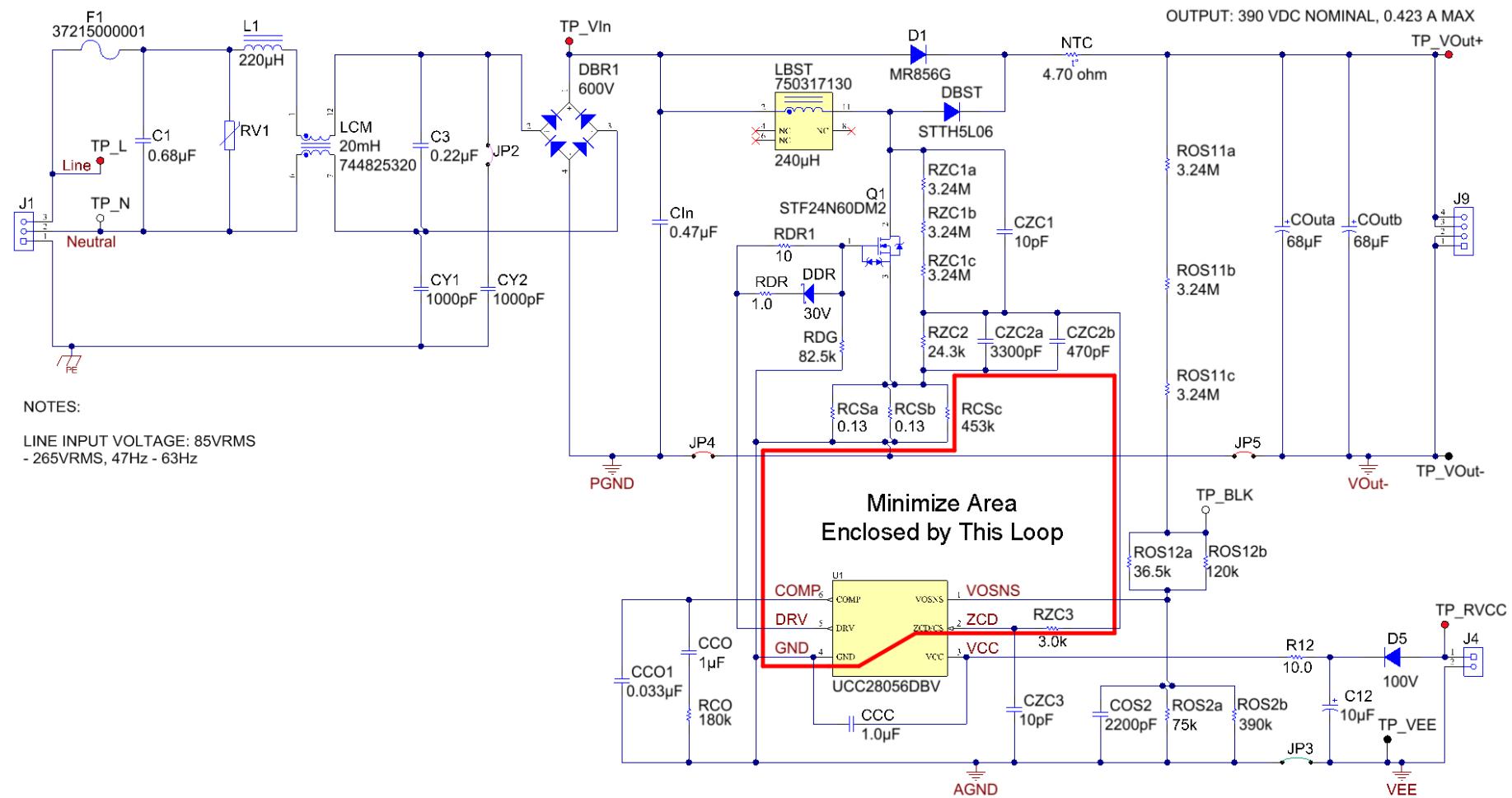

図 26 にUCC28056を高効率・高効率のプリレギュレータとする代表的なアプリケーションを示します。次の2つの独立した部品で構成されます。

- UCC28056を中心とする制御回路

- 電力部

電力部はブースト・コンバータで、入力および負荷に応じてインダクタが遷移モード(TM/CrM)または不連続モード(DCM)で動作します。

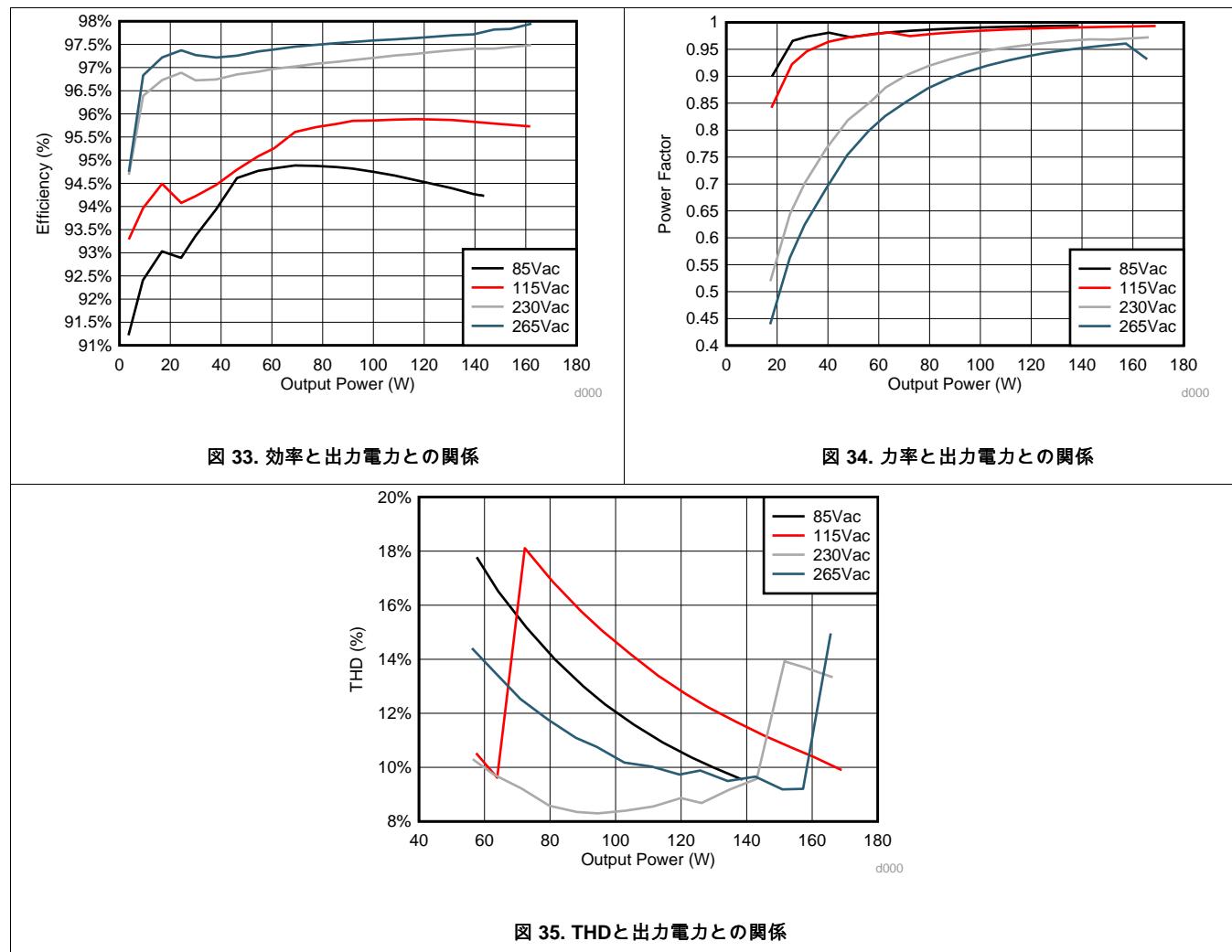

図 26. 165Wプリレギュレータの代表的アプリケーション回路図

## 8.2.1 設計要件

この設計例では、以下の表に示される仕様項目を入力条件として使用します。

表 1. システム設計仕様

| PARAMETER                | TEST CONDITIONS | MIN | TYP | MAX | UNITS |

|--------------------------|-----------------|-----|-----|-----|-------|

| 入力特性                     |                 |     |     |     |       |

| AC電圧範囲                   |                 | 85  |     | 265 | VAC   |

| AC電圧周波数                  |                 | 47  |     | 63  | Hz    |

| 出力特性                     |                 |     |     |     |       |

| 出力電力、P <sub>OutMax</sub> | 85VAC ~ 265VAC  |     |     | 165 | W     |

## 8.2.2 詳細な設計手順

### 8.2.2.1 WEBENCH®ツールによるカスタム設計

ここをクリックすると、WEBENCH® Power Designerにより、UCC28056を使用するカスタム設計を作成できます。

- 最初に、入力電圧(V<sub>IN</sub>)、出力電圧(V<sub>OUT</sub>)、出力電流(I<sub>OUT</sub>)の要件を入力します。

- オプティマイザのダイヤルを使用して、主要なパラメータ(効率、占有面積、コスト)について設計を最適化します。

- 生成された設計を、テキサス・インスツルメンツが提供する他のソリューションと比較します。

WEBENCH Power Designerでは、カスタマイズされた回路図と部品リストを、リアルタイムの価格と部品の在庫情報と併せて参照できます。

ほとんどの場合、次の操作を実行可能です。

- 電気的なシミュレーションを実行し、重要な波形と回路の性能を確認する。

- 熱シミュレーションを実行し、基板の熱特性を把握する。

- カスタマイズされた回路図やレイアウトを、一般的なCADフォーマットでエクスポートする。

- 設計のレポートをPDFで印刷し、同僚と設計を共有する。

WEBENCHツールの詳細は、[www.ti.com/WEBENCH](http://www.ti.com/WEBENCH)でご覧になれます。

### 8.2.2.2 電力段設計

電力段設計では、まず仕様を満たす上で必要なPFCインダクタ値を計算します。これにより、その他の電力部品の定格を計算することができます。

#### 8.2.2.2.1 ブースト・インダクタ設計

ブーストPFC段の入力によって入力に与えられる最小等価抵抗は、入力電流フィードフォワード設定に応じて変化します。R<sub>InEqMin0</sub>とR<sub>InEqMin1</sub>は、最初の2つの入力フィードフォワード値において最小等価入力抵抗を提供します。

$$R_{InEqMin0} = \frac{2 \times L_{BST}}{T_{ONMAX0}} \quad (13)$$

$$R_{InEqMin1} = \frac{2 \times L_{BST}}{T_{ONMAX1}} \quad (14)$$

式 15 で所定の入力電圧から引き出せる最大入力電力を計算します。電力段の効率を明らかにするため、最大入力電力はP<sub>OutMax</sub>の110%に設定します。

$$P_{InMax} = \frac{V_{InRMSMin}^2}{R_{InEqMin}} = 110\% \times P_{OutMax} \quad (15)$$

式 16 で最小入力電圧から最大負荷を供給できるようするために必要なブースト・インダクタンス値を計算します。

$$L_{BST0} = \frac{V_{InRMSMin}^2}{110\% \times P_{OutMax}} \times \frac{T_{ONMAX0}}{2} = 255 \mu H \quad (16)$$

$G_{FF1}$ で最低入力電圧から  $P_{OutMax}$  を供給できるようにします。式 17を用いて、必要なブースト・インダクタ値を計算します。

$$L_{BST1} = \frac{(K_{ZC} \times V_{FF0Fall})^2}{110\% \times 2 \times P_{OutMax}} \times \frac{T_{ONMAX1}}{2} = 266 \mu H \quad (17)$$

式 16および式 17 ( $L_{BST0}$  および  $L_{BST1}$ )で計算した2つの値のうち低いほうを選択します。小さいインダクタンス値を採用すると、軽負荷効率が損なわれます。大きいインダクタンス値では、必要とされる入力電圧範囲で必要とされる最大負荷電力( $P_{OutMax}$ )を供給できません。

250μHのブースト・インダクタ値を選択します。最大負荷電力を供給するには、インダクタが  $I_{LPk0}$  と  $I_{LPk1}$  の両方を上回るピーク電流で動作できなければなりません。

$$L_{BST} = 250 \mu H \quad (18)$$

$$I_{LPk0} = \frac{V_{InRMSMin} \times \sqrt{2} \times T_{ONMAX0}}{L_{BST}} = 6.15 A \quad (19)$$

$$I_{LPk1} = \frac{K_{ZC} \times V_{FF0Fall} \times T_{ONMAX1}}{L_{BST}} = 5.83 A \quad (20)$$

$$I_{LPk} = I_{LPk0} = 6.15 A \quad (21)$$

式 22を用いて、必要とされるピーク・インダクタ電流( $I_{LPk}$ )によって  $T_{ON}$ 期間が早期終了することのない電流検知抵抗を計算します。

$$R_{CS} = \frac{V_{ZCOcp1Min}}{I_{LPk}} = 0.073 \Omega \quad (22)$$

3つの抵抗を並列につないで、これだけの抵抗を実現します。

$$R_{CS} = \frac{1}{\frac{2}{0.15 \Omega} + \frac{1}{3 \Omega}} = 0.073 \Omega \quad (23)$$

式 24を用いて、最大Ocp1電流制限値を上回る飽和電流を許容するインダクタンス値を計算します。

$$I_{LSat} = \frac{V_{ZCOcp1Max}}{R_{CS}} = 7.5 A \quad (24)$$

最小入力電圧から供給する場合、最大負荷を供給する間、電力部品には最大電流が流れます。この条件では、UCC28056は常に遷移モード(CrM)で動作します。に理想的なCrM動作のインダクタ電流波形を示します。

図 27. 理想的な遷移モード(CrM)のインダクタ電流

式 25 はライン・ハーフサイクルで角度 $\theta$ 時の1スイッチング・サイクルでのブースト・インダクタRMS電流を表します。

$$I_{LRMS}(\theta) = \frac{I_{LPkS}(\theta)}{\sqrt{3}} = \frac{2 \times I_{AvS}(\theta)}{\sqrt{3}} = \frac{2}{\sqrt{3}} \times \frac{V_{InPkL}}{R_{InEqMin}} \times \sin(\theta) \quad (25)$$

式 26 は完全な入力サイクルでのブースト・インダクタRMS電流を表します。

$$I_{LRMS} = \sqrt{\frac{1}{\pi} \times \int_0^{\pi} I_{LRMS}(\theta)^2 d\theta} = \frac{2}{\sqrt{3}} \times \frac{V_{InRMS}}{R_{InEq}} \quad (26)$$

最大ブースト・インダクタRMS電流は、最小入力電圧および最大入力電力時に発生します。

$$I_{LRMSMax} = \frac{2}{\sqrt{3}} \times \frac{110\% \times P_{OutMax}}{V_{InRMSMin}} = 2.5 \text{ A} \quad (27)$$

インダクタ要件に基づいて、カスタム磁気設計を行ったり、最適な既製のコントローラを選択することができます。

表 2. インダクタ要件

| 概要      | 値   | 単位            |

|---------|-----|---------------|

| インダクタンス | 250 | $\mu\text{H}$ |

| RMS電流   | 2.5 | A             |

| 飽和電流    | 7.5 | A             |

#### 8.2.2.2.2 ブースト・スイッチの選定

電源スイッチはオン期間( $T_{ON}$ )中にブースト・インダクタに電流が流れます。オフ期間( $T_{DCH}$ )中には電流は流れません。式 28 は、ライン・ハーフサイクルのうちの任意の角度 $\theta$ における、1スイッチングサイクル期間のRMS電流を示します。

$$I_{MosRMS}(\theta) = I_{LPkS}(\theta) \times \sqrt{\frac{\delta_{Mos}(\theta)}{3}} = 2 \times \frac{V_{InPKL}}{R_{InEq}} \times \sin(\theta) \times \sqrt{\frac{\delta_{Mos}(\theta)}{3}} \quad (28)$$

式 29 は理想的な遷移モード(CrM)動作におけるスイッチON時のデューティ・サイクルを表します。

$$\delta_{Mos}(\theta) = \frac{T_{ON}}{T_{ON} + T_{DCH}(\theta)} \quad (29)$$

オン時間は入力サイクル全体で一定となります。オフ時間は入力サイクルでの位置に応じて変化します。各スイッチング・サイクルにおいて、ブースト・インダクタでのボルト秒バランスをとるにはそれが必要です。

$$\frac{T_{DCH}(\theta)}{T_{ON}} = \frac{|V_{In}(\theta)|}{V_{Out} - |V_{In}(\theta)|} \quad (30)$$

式 31 でスイッチON時のデューティ・サイクルを計算します。

$$\delta_{Mos}(\theta) = 1 - \sqrt{2} \times \frac{V_{InRMS}}{V_{Out}} \times |\sin(\theta)| \quad (31)$$

式 32 は完全なライン・ハーフサイクルでのRMSスイッチ電流を表します。

$$I_{MosRMS} = \sqrt{\frac{1}{\pi} \times \int_0^{\pi} I_{MosRMS}(\theta)^2 d\theta} = \frac{V_{InRMS}}{R_{InEq}} \times \sqrt{\frac{4}{3} - \frac{32 \times \sqrt{2} \times V_{InRMS}}{9 \times \pi \times V_{Out}}} \quad (32)$$

スイッチの最大RMS電流は、最大負荷および最小入力時に発生します。

$$I_{MosRMSMax} = \frac{110\% \times P_{OutMax}}{V_{InRMSMin}} \times \sqrt{\frac{4}{3} - \frac{32 \times \sqrt{2} \times V_{InRMSMin}}{9 \times \pi \times V_{Out}}} = 2.1 \text{ A} \quad (33)$$

ブースト・スイッチに関しては、次のMOSFET選定ガイドラインを採用します。

- 定格電圧は最大出力電圧を上回っていなければなりません。過渡/入力サージ試験では、出力電圧が通常のレギュレーション値を上回ることがあります。この設計例では、MOSFETの定格電圧は650Vで、レギュレートされた出力電圧390Vをサポートしています。

- MOSFETの許容導通損失値に基づき、最大RMS電流から必要なオン抵抗( $r_{DS(on)}$ )値を計算できます。この設計例では、オン抵抗0.37Ω、 $T_J = 125^\circ\text{C}$ でMOSFETの最大導通電力損失(1.7W未満)を許容することから、STMicroelectronicsのSTF24N60DM2 MOSFETを選定しました。

- 最高の効率を実現するため、高速ボディ・ダイオードを搭載したMOSFETを採用します。低速ボディ・ダイオードを搭載したMOSFETを採用すると、低入力電圧から不連続インダクタ電流を使用する動作(DCM)により、スイッチング電力損失が増大します。

### 8.2.2.2.3 ブースト・ダイオードの選定

ブースト・ダイオードは、スイッチがオフの間( $T_{DCH}$ )はブースト・インダクタ電流を伝導し、スイッチがオンの間( $T_{ON}$ )はゼロ電流を伝導します。[式 34](#)はライン・ハーフサイクルで角度 $\theta$ 時の1スイッチング・サイクルでのRMSダイオード電流を計算します。

$$I_{DioRMS}(\theta) = I_{LPkS}(\theta) \times \sqrt{\frac{\delta_{Dio}(\theta)}{3}} = 2 \times \frac{V_{InPkL}}{R_{InEq}} \times \sin(\theta) \times \sqrt{\frac{\delta_{Dio}(\theta)}{3}} \quad (34)$$

[式 35](#)は理想的な遷移モード動作におけるブースト・ダイオード導通のデューティ・サイクルを表します。

$$\delta_{Dio}(\theta) = 1 - \delta_{Mos}(\theta) = \sqrt{2} \times \frac{V_{InRMS}}{V_{Out}} \times |\sin(\theta)| \quad (35)$$

[式 36](#)は完全なライン・ハーフサイクルでのRMSブースト・ダイオード電流を表します。

$$I_{DioRMS} = \sqrt{\frac{1}{\pi} \times \int_0^{\pi} I_{DioRMS}(\theta)^2 d\theta} = \frac{4}{3} \times \frac{V_{InRMS}}{R_{InEq}} \times \sqrt{\frac{2 \times \sqrt{2}}{\pi} \times \frac{V_{InRMS}}{V_{Out}}} \quad (36)$$

ブースト・ダイオードの最大RMS電流は、最大負荷および最小入力時に発生します。

$$I_{DioRMSMax} = \frac{4}{3} \times \frac{110\% \times P_{OutMax}}{V_{InRMSMin}} \times \sqrt{\frac{2 \times \sqrt{2}}{\pi} \times \frac{V_{InRMSMin}}{V_{Out}}} = 1.3 \text{ A} \quad (37)$$

ブースト・ダイオードの導通電力損失は、主に平均出力電流の関数となります。

$$I_{DioAVGMax} = \frac{P_{OutMax}}{V_{Out}} = 0.42 \text{ A} \quad (38)$$

上記の計算と以下のガイドラインを参考にして、ブースト・ダイオードを選定します。

- ブースト・ダイオードの定格電圧は最大出力電圧を上回るようにします。過渡/入力サージ試験では、出力電圧が通常のレギュレーション値をはるかに上回ることがあります。

- ブースト・ダイオードの平均/RMS定格電流は[式 37](#)および[式 38](#)で計算した数値を上回っていなければなりません。

- ダイオードはさまざまな速度/回復電荷で供給されています。逆回復電荷が小さい高速ダイオードでは通常、順方向電圧降下が大きくなります。高速ダイオードは導通損失が大きいものの、スイッチング損失は小さくなります。逆回復電荷が大きい低速ダイオードでは通常、順方向電圧降下が小さくなります。低速ダイオードは導通損失が小さいものの、スイッチング損失は大きくなります。用途に合った定格速度のダイオードを選定することで、最大限の効率を確保できます。

- ブースト・コンバータ入力に電圧が最初に印加されると、出力コンデンサが入力電圧ピーク値まで充電する間に、制御されていない電流がブースト・ダイオードを流れます。充電電流は入力およびEMIフィルタ段のインピーダンスによってのみ制限されるため、出力コンデンサ充電期間中に非常に高い値に達することがあります。この電流を伝導するダイオードの定格は、この非反復サージ電流を伝導できるものとします。通常はバイパス・ダイオードを追加して、この充電電流の大半をブースト・ダイオードからそらします。バイパス・ダイオードには、順方向電圧降下が小さい低速タイプを使用できます。このため、高速なブースト・ダイオードに比べて安価でより安定しています。

- この設計例では、STMicroelectronics®のSTTH5L06ダイオードを選定しました。このダイオードは定格電圧が600Vで、平均定格電流は5Aです。順方向電圧降下が約0.85Vであるため、ブースト・ダイオードの導通損失は0.5W未満となります。

### 8.2.2.2.4 出力コンデンサの選定

入力電源からPFC段が引き出す電力は次の式で表します。

$$P_{In}(\theta) = 2 \times V_{InRMS} \times I_{InRMS} \times \sin(\theta)^2 \quad (39)$$

負荷電力が一定である代表的なアプリケーションを仮定すると、入力サイクルの一部では、電源から過剰な電力が引き出され、出力コンデンサに蓄積されます。入力サイクルの他の部分では、負荷電力が入力電力を上回り、この不足分を出力コンデンサから供給しなければなりません。出力コンデンサと電力をやり取りするこのプロセスによって、必然的に入力周波数の2倍の出力電圧リップルが生じることとなります。この入力周波数の2倍のリップルは、 $P_{Out}/C_{Out}$ 比と入力周波数にのみ依存します。

$$\Delta V_{Outpp} = \frac{P_{Out}}{C_{Out}} \times \frac{1}{2 \times \pi \times f_{Line} \times V_{OutReg}} \quad (40)$$

いくつかあるアプリケーション要件のいずれかを優先して、出力コンデンサ値を選択します。

- 最大負荷時に入力周波数の2倍の出力リップル電圧。

- 入力電源切断後の出力電圧ホールドアップ時間。

- 過渡負荷ステップの結果としての出力電圧偏差。

この設計例では、入力周波数の2倍の出力リップル電圧の振幅はそのレギュレーション値の3%未満であると仮定します。これを実現するために必要な $P_{OutMax}/C_{Out}$ 比は、式 41 を用いて計算できます。

$$\frac{P_{OutMax}}{C_{Out}} \geq \left( 2 \times \pi \times f_{Line} \times V_{OutReg}^2 \times 3\% \right) = 1.43 \frac{W}{\mu F} \quad (41)$$

式 42 を用いて、この165Wの設計例に必要な容量値を計算します。

$$C_{Out} \geq \frac{165W}{1.43 \frac{W}{\mu F}} = 115 \mu F \quad (42)$$

入力電流の全高調波歪み(THD)を最小に抑えるには、最大出力電圧リップル振幅が式 43 に示す条件を満たしていなければなりません。この条件を満たしていれば、出力電圧リップルの極値によりエラー・アンプの非線形ゲインがアクティブになることはありません。

$$\frac{\Delta V_{Outpp}}{V_{OutReg}} = \frac{2 \times DSuThs}{V_{OSReg}} = 5.4\% \quad (43)$$

式 44 を用いて、出力コンデンサを流れる最大RMSリップル電流を計算します。

$$I_{COutRMSMax} = \sqrt{I_{DioRMSMax}^2 - \left( \frac{P_{OutMax}}{V_{OutReg}} \right)^2} = 1.19 A \quad (44)$$

出力コンデンサに流れ込むこの電流には、スイッチング周波数成分( $I_{COutRMSHF}$ )と入力周波数の2倍のリップル成分( $I_{COutRMSLF}$ )があります。

$$I_{COutRMSLF} = \frac{1}{\sqrt{2}} \times \frac{P_{OutMax}}{V_{OutReg}} = 0.3 A \quad (45)$$

$$I_{COutRMSHF} = \sqrt{I_{DioRMSMax}^2 - \frac{3}{2} \times \left( \frac{P_{OutMax}}{V_{OutReg}} \right)^2} = 1.15 A \quad (46)$$

電解コンデンサには通常、入力周波数の2倍(120Hz)でのリップル定格電流と、これとは異なるスイッチング周波数(100kHz)でのリップル定格電流があります。これらの定格は、入力周波数の2倍ではコンデンサのESRが高くなり、したがって、この周波数で発生するリップル電流は同じ振幅のスイッチング周波数リップルよりも大きな電力損失を招くという事実を反映しています。最適なコンデンサを選定するには、コンデンサを流れる等価高周波リップル電流を考慮してください。

$$I_{C_{EquRMSHF}} = \sqrt{I_{C_{OutRMSLF}}^2 \times K_{HLP}^2 + I_{C_{OutRMSHF}}^2} \quad (47)$$

パラメータ  $K_{HLP}$  は、使用予定であるコンデンサ・シリーズの高周波と低周波のRMSリップル定格電流の比です。

$$K_{HLP} = \frac{100\text{kHz\_ripple\_current\_rating}}{120\text{Hz\_ripple\_current\_rating}} \quad (48)$$

この設計例では、サイズと定格を考えて、Rubycon BXWシリーズ(450BXW68MEFC12.5X45)の68μF/450Vコンデンサ2個を選定し、並列接続します。これにより、コンデンサ値の要件とリップル定格電流の両方を満たし、マージンも若干増やすことができます。

$$C_{Out} = 2 \times 68 \mu\text{F} = 136 \mu\text{F} \quad (49)$$

$$I_{C_{EquRMSHF}} = \sqrt{(0.3 \text{ A})^2 \times \left(\frac{1.525}{0.610}\right)^2 + (1.15 \text{ A})^2} = 1.37 \text{ A} \quad (50)$$

### 8.2.2.3 ZCD/CS端子

ZCD/CS端子に実装する外付け分圧ネットワークは、減衰ドレイン電圧波形( $V_{DS}$ )と電流検知信号( $V_{CS}$ )の両方をコントローラに伝達します。このような伝達が可能である理由は、電流検知信号はスイッチがオンで $V_{DS}$ 信号がゼロに近いときにしか監視を必要としないからです。一方のドレイン電圧波形は、スイッチがオフで電流検知信号がゼロに近いときにしか検知を必要としません。

$$V_{ZC}(t) = V_{CS}(t) + V_{DS}(t) \times \frac{Z_{ZC2}}{Z_{ZC1} + Z_{ZC2}} \quad (51)$$

式 52 はMOSFETがオンになっているオンタイム期間中の減衰ドレイン電圧を表しています。

$$V_{ZC}(t) = I_L(t) \times \left( R_{CS} + R_{DSON} \times \frac{Z_{ZC2}}{Z_{ZC1} + Z_{ZC2}} \right) \quad (52)$$

MOSFETのオン状態抵抗( $R_{DSON}$ )は通常、電流検知抵抗( $R_{CS}$ )と同様の値になります。分圧器( $Z_{ZC1}$ ,  $Z_{ZC2}$ )の減衰率は1/401であるため、式 52 の第2項は無視して構いません。

$$V_{ZC}(t) = I_L(t) \times R_{CS} \quad (53)$$

したがって、必要とされる電流検知抵抗値はで出した最大ピーク・インダクタ電流から計算できます。[セクション9.2.2.1](#)

MOSFETがオフになっている、 $T_{ON}$ 期間以外では、電流検知抵抗を流れる電流がゼロに近くなります。この場合、式 51 は次のようになります。

$$V_{ZC}(t) = V_{DS}(t) \times \frac{Z_{ZC2}}{Z_{ZC1} + Z_{ZC2}} \quad (54)$$

UCC28056は、ZCD/CS端子の電圧波形に漸増負勾配が検出されるまで、新しいスイッチング・サイクルが開始されないようにします。漸増負勾配は、インダクタ電流がゼロまで降下し、出力ダイオードがすでにオフになっていることを示しています。新しい各スイッチング・サイクルの開始をドレイン波形の最小値(バレー)と同期することで、動作開始時のスイッチング損失をさらに削減できます。

理論上は、単純な分圧抵抗を使用して、ZCD/CS端子に送り込まれるドレイン電圧波形を減衰できます。実際には、PCB配線とZCD/CS端子に関連する寄生容量が減衰した信号をフィルタ処理し、位相シフトをもたらします。結果として生じる歪みと位相シフトは、部品がゼロ・インダクタ電流遷移と同期する機能に悪影響を及ぼします。分圧抵抗の消費電力を抑制する必要があるため、高い抵抗値を採用しなければならず、減衰した信号のフィルタ処理が増大するなど、問題はさらに悪化します。

フィルタ処理とそれに伴う位相シフトを招かずに高抵抗を使用するには、分圧コンデンサを分圧抵抗と並列に接続します。このとき、無効分圧比が分圧抵抗比と等しくなるようにします。

$$\frac{R_{ZC2}}{R_{ZC1} + R_{ZC2}} = \frac{X_{ZC2}}{X_{ZC1} + X_{ZC2}} \quad (55)$$

よって、

$$\frac{R_{ZC1}}{R_{ZC2}} = \frac{C_{ZC2}}{C_{ZC1}} \quad (56)$$

ZCD/CS端子に供給される減衰したドレイン電圧信号が駆動する内部電圧閾値はいくつかあります。ブラウンアウト( $V_{ZCBoRise}$ )、入力フィードフォワード( $V_{FFxRise}$ 、 $V_{FFxFall}$ )、2次出力過電圧( $V_{Ovp2Th}$ )がこれに該当します。これらの閾値は、いずれも同じ外付け分圧比( $K_{ZC}$ )で駆動されます。このすべての閾値に同時に影響を与えるため、指定の減衰比を変更する余地は限られています。

$$K_{ZC} = \frac{R_{ZC1}}{R_{ZC2}} + 1 = 401 \quad (57)$$

$$V_{InRMSBoRise} = V_{ZCBoRise} \times \frac{K_{ZC}}{\sqrt{2}} = 85.1 \text{ V} \quad (58)$$

UCC28056は、ドレイン・ノードのスイッチング・サイクル平均電圧から入力電圧を推測します。各サイクル(TM/CrM/DCM)の終了時にブースト・インダクタ電流がゼロに戻るとすると、ブースト・インダクタの抵抗電圧降下を無視すれば、これは入力整流器から供給される電圧と等しくなるはずです。入力整流ブリッジおよびEMIフィルタ段での電圧降下により、閾値の予測値と測定値の間には誤差が生じます。内蔵ピーク検出器によって、ライン・ハーフサイクルでのピーク入力電圧が特定されます。上記の式 58は、このピーク値をRMS量に変換していますが、理想的な正弦波入力電源を想定しています。

式 59 で2次出力過電圧コンバレータ(Ovp2)を検知するのに必要な出力電圧を計算します。

$$V_{OutOvp2} = V_{Ovp2Th} \times K_{ZC} = 451 \text{ V} \quad (59)$$

このパラメータは、ドレイン波形、ブースト・ダイオードでの電圧降下、直列NTC抵抗を通じて監視され、これにより低出力電圧値時にOvp2コンバレータがトリップします。

ドレイン検知分圧抵抗チェーンの消費電力は、バースト・オフ状態で最大値に達します。バースト・オフ状態において、ドレイン電圧はDC電圧 = 入力電圧ピークと概算します。この概算では、入力ハーフ期間に比べて時定数 $C_{IN} \times (R_{ZC1} + R_{ZC2})$ が長いと仮定しています。無負荷条件ではバースト・オフのデューティ・サイクルが高くなるため、式 60で表すとおり、ドレイン検知分圧抵抗チェーンの最大消費電力は高入力および無負荷時に発生します。

$$P_{ZCMax} = \frac{V_{InRMSMax}^2 \times 2}{R_{ZC1} + R_{ZC2}} \quad (60)$$

式 61で $R_{ZC1}$ の最大値を計算し、入力バイアス電流( $I_{ZCBias}$ )による1%の誤差を、最低電圧閾値( $V_{ZCBoRise}$ )で許容します。

$$R_{ZC1} \leq \frac{\text{Err\%} \times K_{ZC} \times V_{ZCBoRise}}{I_{ZCBias}} = \frac{1\% \times \sqrt{2} \times 85V}{100nA} = 12.0 M\Omega \quad (61)$$

分圧チェーンの1次抵抗( $R_{ZC1}$ )は、サージ試験においてピーク出力電圧に耐えるものとします。耐久性の高いソリューションの場合、この位置に使用する抵抗の定格電圧は、ブーストMOSFETのアバランシェ定格を上回っている必要があります。この設計では、3つの1206 SMT 3.24MΩ抵抗からなる直列チェーンを使用して、600Vを上回るDC電圧耐性を実現します。

$$R_{ZC1} = 3 \times 3.24 M\Omega = 9.72 M\Omega \quad (62)$$

$$R_{ZC2} = \frac{R_{ZC1}}{K_{ZC} - 1} = 24.3 k\Omega \quad (63)$$

式 60を用いて、ZCD/CS端子分圧抵抗の消費電力を計算します。

$$P_{ZCMax} = \frac{V_{InRMSMax}^2 \times 2}{R_{ZC1} + R_{ZC2}} = 14 mW \quad (64)$$

分圧抵抗回路をPCBに配置すると、1次( $R_{ZC1}$ )および2次( $R_{ZC2}$ )抵抗の両方に寄生容量が若干発生します。3つの1206 SMT部品で構成し、小型のPCBレイアウトと仮定すると、経験上、抵抗 $R_{ZC1}$ には約0.1pFの寄生容量( $C_{ZC1}$ )が生じるものと思われます。理論上は、この寄生容量を加えて $C_{ZC1}$ の全体的な値とし、 $C_{ZC2}$ の適切な値を追加して、式 56で要求される比率を達成できます。実際には、ほとんどの設計者がこの位置に明示的なコンデンサを追加して、オシロスコープ・プローブの接続時に生じるような、レイアウトの小さな変更に対する公差を広げることを選びます。分圧器の時定数は、多くのスイッチング・サイクルに及ぶことがないようにします。この制限により、入力サージやシステムのESD過渡事象がZCD/CS端子のDC値を乱すことはあっても、過剰な数のスイッチング・サイクルにわたって持続することはありません。

公差5%の10pF、1000V、0805 SMTコンデンサ1個を選定します。

$$C_{ZC1} = 10 pF \quad (65)$$

式 66を用いて、2次分圧コンデンサ値を計算します。

$$C_{ZC2} = K_{ZC} \times C_{ZC1} = 4.01 nF \quad (66)$$

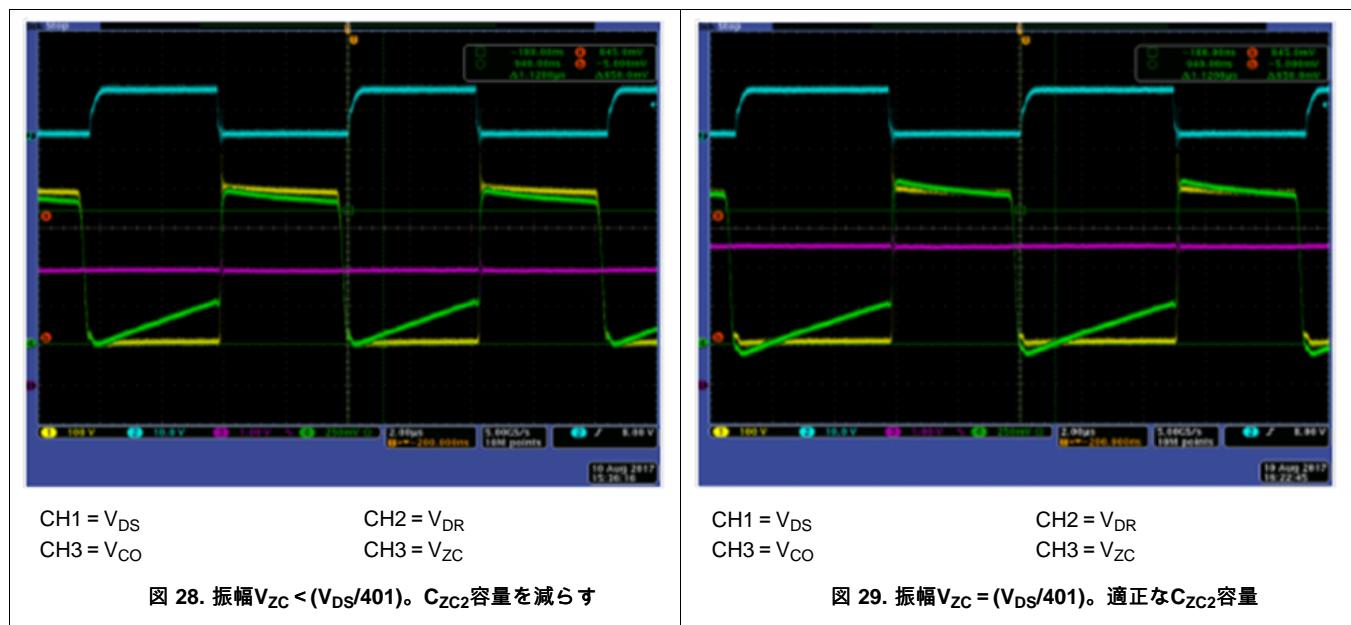

実際には、最終PCBレイアウトが完成した時点で、2次コンデンサ値を調整して、PCBに生じる寄生容量を明らかにします。ドレインとZCD/CS端子の両方の波形を考慮して、2次容量値( $C_{ZC2}$ )が必要な信号振幅比を許容するまで調整します。ZCD/CS端子接続には低容量プローブを使用します。図 28、図 29、図 30に、この転換プロセスで生じる波形のタイプを示します。

#### 8.2.2.3.1 ZCD/CS端子波形に生じる電圧スパイク

ZCD/CS端子での電圧オフセットは、この端子に印加される波形に生じる大振幅のスイッチング・エッジ・スパイクに起因する傾向があります。こうしたスイッチング・エッジ・スパイクは、内蔵ESD構造のような非線形コントローラによってクランプされ、分圧器のDC動作ポイントをアップセットします。これは、特に電流の変化率が最高値(入力電圧ピーク程度の高負荷)のときに、ZCD/CS端子信号での電圧オフセットとして観測できます。ZCD/CS端子分圧器の設計に際しては、スイッチング・エッジ・スパイクを捕捉しないようにします。低インダクタンス・タイプの電流検知抵抗の採用も、同じ理由で重要となります。必要であれば、時定数が約30nsのRCフィルタを分圧器とZCD/CS端子の間に追加して、スイッチング・エッジ・スパイクを減衰することもできます。このフィルタの容量( $C_{ZC3}$ )は $C_{ZC2}$ の値に比べて小さくなるようにします。直列抵抗が式 67で計算した値を下回るようにして、R-Cフィルタに起因する誤差を1%未満に制限します。

$$R_{ZC3} < \frac{V_{ZCBoRise}}{I_{ZCBias}} \times 1\% = 30 \text{ k}\Omega \quad (67)$$

この設計例では、RCフィルタに次の値を選択してスイッチング・エッジ・スパイクを減衰します。

$$R_{ZC3} = 3 \text{ k}\Omega \quad (68)$$

$$C_{ZC3} = 10 \text{ pF} \quad (69)$$

#### 8.2.2.4 VOSNS端子

VOSNS端子電圧は、内蔵するトランジスタコンダクタンス・エラー・アンプの反転入力に印加されます。非反転入力には固定基準電圧( $V_{OSReg}$ )が印加されます。エラー・アンプは高ゲインであるため、定常状態で、 $V_{COMP} < 5\text{V}$ と仮定すると、VOSNS端子の平均電圧は基準電圧( $V_{OSReg}$ )とほぼ等しくなるはずです。したがって、出力電圧レギュレーション設定点( $V_{OutReg}$ )は、次の式により、出力電圧をVOSNS端子に接続する外付け分圧抵抗ネットワークで決まります。

$$V_{OutReg} = V_{OSReg} \times \left( \frac{R_{OS1}}{R_{OS2}} + 1 \right) \quad (70)$$

VOSNS端子に電力を送る分圧抵抗は、無負荷時入力電力に大きく貢献します。抵抗値が高いほど、分圧器の消費電力を削減できます。

$$P_{OSDiv} = \frac{V_{OutReg}^2}{R_{OS1} + R_{OS2}} \quad (71)$$

VOSNS端子バイアス電流( $I_{OSBias}$ )の影響により、抵抗値が高くなるとレギュレーション精度は低下します。

$$\frac{\Delta V_{OSReg}}{V_{OSReg}} = \frac{I_{OSBias} \times R_{OS1}}{V_{OutReg}} \quad (72)$$

VOSNS端子バイアス電流による出力電圧レギュレーション精度の低下を1%未満にするため、式73に示すように1次分圧抵抗値を制限する必要があります。

$$R_{OS1} < \frac{\Delta V_{OSReg}}{V_{OSReg}} \times \frac{V_{OutReg}}{I_{OSBias}} = 1\% \times \frac{390 \text{ V}}{100 \text{ nA}} = 39 \text{ M}\Omega \quad (73)$$

式73はVOSNS分圧器の消費電力が4mWを下回っても、レギュレーション精度に悪影響がないことを裏付けています。

この設計例のPFC段は、UCC256301が制御するLLC段に追従されます。UCC28056とUCC256301を組み合わせることによって、軽負荷効率が高く、スタンバイ消費電力の低い完全なオフライン電源システムが実現します。無負荷時入力電力を抑制するため、1つの分圧抵抗でVOSNS端子(UCC28056)とBLK端子(UCC256301)の両方に電力を送ります。UCC28056に必要な分圧比( $K_{OS}$ )とUCC256301に必要な分圧比( $K_{BLK}$ )は異なるため、タップが2つある分圧抵抗が必要です。1次分圧抵抗( $R_{OS1}$ )を2つのパート( $R_{OS11}$ 、 $R_{OS12}$ )に分けることで、タップを2つに増やせます。

$$K_{OS} = \frac{V_{OutReg}}{V_{OSReg}} = \frac{R_{OS11} + R_{OS12} + R_{OS2}}{R_{OS1}} = 156 \quad (74)$$

$$K_{BLK} = \frac{R_{OS11} + R_{OS12} + R_{OS2}}{R_{OS12} + R_{OS2}} = 108 \quad (75)$$

この設計例では、3つの3.24MΩ、1206 SMT抵抗を直列接続して構成した1次分圧抵抗を選定します。このコンパクトでコスト効果の高い設計により、最適な高電圧抵抗が実現します。単一抵抗がよければ、高電圧タイプで、入力サージ試験で出力コンデンサを通る最大電圧に対応する定格のものを採用します。

$$R_{OS11} = 3 \times 3.24 \text{ M}\Omega = 9.72 \text{ M}\Omega \quad (76)$$

式74と式75を同時に解くと、次のようにになります。

$$R_{OS12} = \frac{R_{OS11}}{K_{OS}} \times \left( \frac{K_{OS} - 1}{K_{BLK} - 1} - 1 \right) = 27.95 \text{ k}\Omega \quad (77)$$

$$R_{OS2} = \frac{R_{OS11} + R_{OS12}}{K_{OS} - 1} = 62.89 \text{ k}\Omega \quad (78)$$

この2つの分圧抵抗値は、次のように入手しやすい値を用いて求めることができます。

$$R_{OS2} = 75 \text{ k}\Omega // 390 \text{ k}\Omega = 62.9 \text{ k}\Omega \quad (79)$$

$$R_{OS12} = 36.5 \text{ k}\Omega // 120 \text{ k}\Omega = 28.0 \text{ k}\Omega \quad (80)$$

したがって、実際のレギュレーション設定点は次のとおりです。

$$V_{OutReg} = \frac{R_{OS11} + R_{OS12} + R_{OS2}}{R_{OS2}} \times V_{OSReg} = 390 \text{ V} \quad (81)$$

VOSNS分圧抵抗の消費電力は次のとおりです。

$$P_{OSDiv} = \frac{V_{OutReg}^2}{R_{OS11} + R_{OS12} + R_{OS2}} = 15.5 \text{ mW} \quad (82)$$

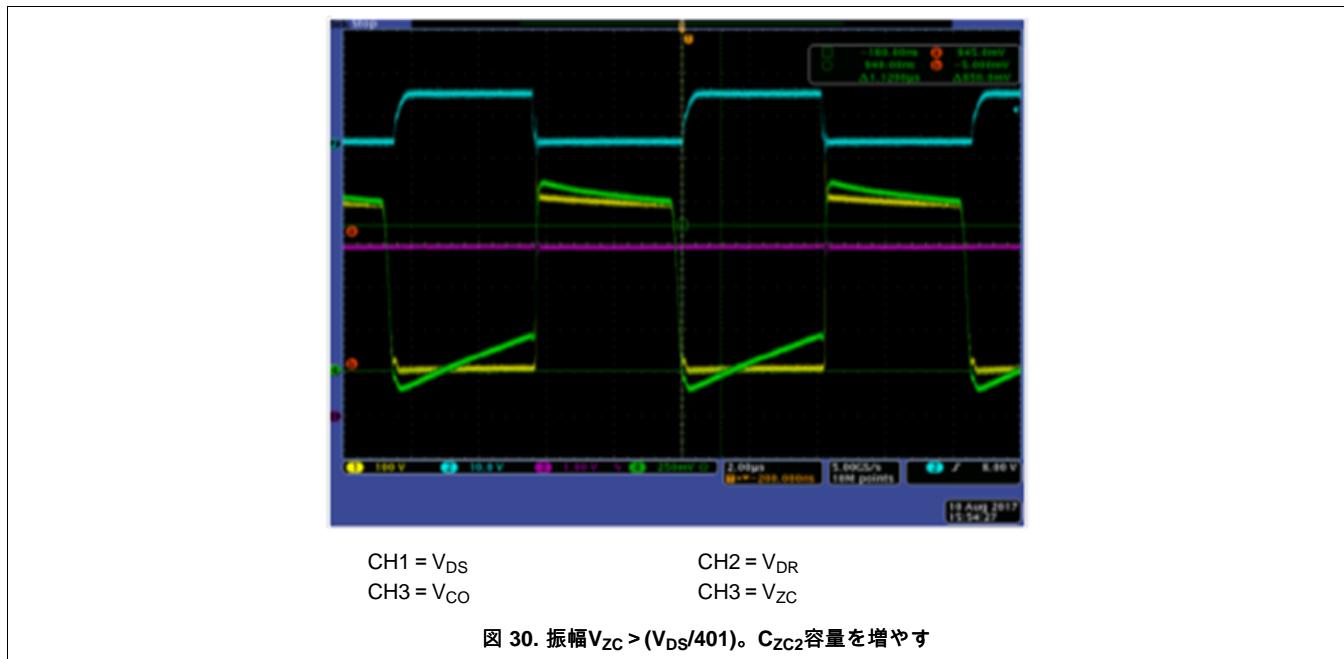

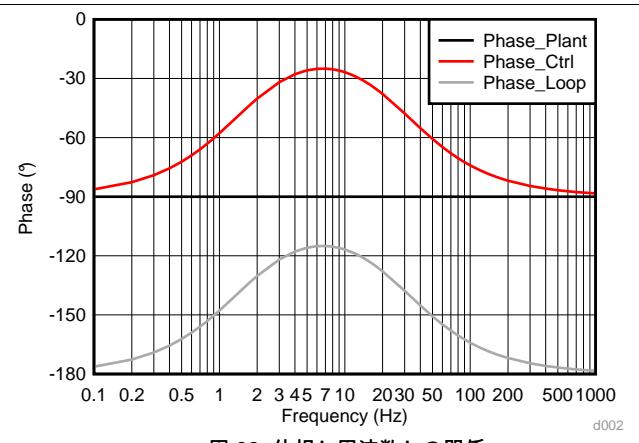

### 8.2.2.5 電圧ループ補償

PFC段の電圧制御ループの設計には妥協が必要です。負荷電流のステップに対して優れた過渡応答を実現するには電圧制御ループが高速でなければいけませんが、入力電流の歪みを最小限に抑えるには低速でなければいけません。このセクションでは、目標とする入力電流歪みと位相マージンを実現する補償部品の選定について述べます。

### 8.2.2.5.1 プラント・モデル

まず、PFCブースト・コンバータの小信号モデルを作成します。定電力負荷は出力コンデンサを通して接続すると仮定します。これで、定出力電圧を供給するスイッチ・モード・レギュレータを極めて正確に再現できます。内蔵する入力電圧フィードフォワード回路の動作により、プラント・ゲインは入力電圧に依存しないものと仮定します。実際には、入力電圧フィードフォワード回路の量子化特性により、ユニバーサル入力電圧範囲(90V<sub>RMS</sub> ~ 264V<sub>RMS</sub>)において、プラント・ゲインは±20%変動します。

$$\frac{v_{\text{Out}}(j\omega)}{v_{\text{CO}}(j\omega)} = G_{\text{Plant}}(j\omega) = \frac{1}{j\omega} \times G_{\text{Plant0}} = \frac{1}{j\omega} \times \frac{P_{\text{OutMax}}}{V_{\text{COMax}} \times V_{\text{OutReg}} \times C_{\text{Out}}} \quad (83)$$

### 8.2.2.5.2 補償設計

プラントの積分器の応答により、ゲイン・ロールオフは1デイケード当たり -20dBとなり、90°の位相遅れが生じます。単純な積分補償ネットワークでは、電圧ループにもう一回90°の位相遅れが生じるため、容認しがたい位相マージンになります。十分な位相マージンを確保するには、タイプ2補償ネットワークを採用して、ゲイン・クロスオーバー周波数で希望する位相ブーストを得るようにします。式 84はエラー・アンプとタイプ2補償ネットワークを組み合わせた場合の小信号ゲインを表します。

$$\frac{v_{\text{CO}}(j\omega)}{v_{\text{Out}}(j\omega)} = G_{\text{Ctrl}}(j\omega) = \frac{V_{\text{OSReg}}}{V_{\text{OutReg}}} \times g_M \times \frac{\left( R_{\text{CO}} + \frac{1}{j\omega \times C_{\text{CO}}} \right) \times \frac{1}{j\omega \times C_{\text{CO1}}}}{R_{\text{CO}} + \frac{1}{j\omega \times C_{\text{CO}}} + \frac{1}{j\omega \times C_{\text{CO1}}}} \quad (84)$$

式(84)は次のように表すこともできます。

$$G_{\text{Ctrl}}(j\omega) = \frac{G_{\text{Ctrl0}}}{j\omega} \times \frac{1 + \frac{j\omega}{2 \times \pi \times f_Z}}{1 + \frac{j\omega}{2 \times \pi \times f_P}}$$

ここで

$$f_Z = \frac{1}{2 \times \pi \times (C_{\text{CO}} \times R_{\text{CO}})} \quad (86)$$

$$f_P = \frac{C_{\text{CO}} + C_{\text{CO1}}}{2 \times \pi \times (C_{\text{CO}} \times C_{\text{CO1}} \times R_{\text{CO}})} \quad (87)$$

$$G_{\text{Ctrl0}} = \frac{V_{\text{OSReg}}}{V_{\text{OutReg}}} \times g_M \times \frac{1}{(C_{\text{CO}} + C_{\text{CO1}})} \quad (88)$$

式 86、式 87、式 88を並べ替えると次のようになります。

$$C_{\text{CO1}} = \frac{f_Z}{f_P} \times \frac{1}{G_{\text{Ctrl0}}} \times \left( \frac{V_{\text{OutReg}}}{V_{\text{OSReg}}} \times g_M \right) \quad (89)$$

$$C_{\text{CO}} = \frac{f_P - f_Z}{f_Z} \times C_{\text{CO1}} \quad (90)$$

$$R_{\text{CO}} = \frac{1}{2 \times \pi \times f_Z} \times \frac{1}{C_{\text{CO}}} \quad (91)$$

ゲイン・クロスオーバー周波数で最大の位相ブーストを得るために、補償設計に際し、ボード線図で極/ゼロはゲイン・クロスオーバー周波数(f<sub>B</sub>)を中心に対照的に配置します。周波数軸は対数目盛りとするため、これにより次のような極(f<sub>P</sub>)およびゼロ(f<sub>Z</sub>)周波数が得られます。

$$f_Z = \frac{f_B}{K} \quad (92)$$

$$f_P = f_B \times K \quad (93)$$

プラントに採用されている積分器の特性と補償器により $180^\circ$ の位相遅れが生じるため、ループの位相マージンはタイプ2補償による位相ブーストと等しくなります。 $f_B$ で所望する位相マージン( $\Phi_{PM}$ )を実現するために、式 92 および式 93 を式 85 に代入し、位相ブースト角度となるKを解いて、極周波数とゼロ周波数の分離を確認します。

$$K = \tan\left(\frac{\Phi_{PM}}{2} + \frac{\pi}{4}\right) \quad (94)$$

次に、希望する位相マージンを選択します。標準的な位相マージンの範囲は $45^\circ \sim 75^\circ$ です。この設計例では、目標位相マージンを $65^\circ$ とします。

$$\Phi_{PM} = 65^\circ \times \frac{\pi}{180^\circ} \quad (95)$$

$$K = \tan\left(\frac{\Phi_{PM}}{2} + \frac{\pi}{4}\right) = 4.51 \quad (96)$$

次に、ループ・ゲイン・クロスオーバー周波数( $f_B$ )を決定します。高速ループでは、COMP端子電圧における入力周波数の2倍のリップルが増えて、入力電流歪みの増大につながります。

まず、入力周波数の2倍のCOMP電圧リップルによる第三高調波歪み1%という目標を設定します。この目標を達成するには、定常状態フルパワー動作時に入力周波数の2倍のCOMP端子リップルをDC値の2%未満に抑える必要があります。次に、入力周波数の2倍のCOMP端子リップルの振幅がDC値の2%を超えないようなループ・ゲイン・クロスオーバー周波数( $f_B$ )を選択します。

式 97 を用いて、出力コンデンサにおける入力周波数の2倍の電圧リップルの振幅を計算します。

$$\Delta V_{Out} = \frac{P_{OutMax}}{V_{OutReg}} \times \frac{1}{2 \times 2 \times \pi \times f_{Line} \times C_{Out}} = 4.95 \text{ V} \quad (97)$$

COMP端子電圧で2%のリップル振幅という目標を達成するには、出力電圧リップルの振幅を帰還ネットワークで減衰する必要があります。

$$|G_{Ctrl}(j2 \times \pi \times 2 \times f_{Line})| = \frac{V_{COMax} \times 2\%}{\Delta V_{Out}} \quad (98)$$

式 99 は式 98 を簡単にしたものです。

$$G_{Ctrl0} = \frac{0.0202}{K^2} \times 4 \times \pi \times f_{Line} = 0.624 \text{ Hz}$$

ここで

- $2 \times f_{Line} \gg f_P$

- $2 \times f_{Line} \gg f_Z$

- (99)

式 100 はゲイン・クロスオーバー周波数でのユニティを表します。

$$|G_{Plant}(j2 \times \pi \times f_B)| \times |G_{Ctrl}(j2 \times \pi \times f_B)| = 1 \quad (100)$$

式 100 は式 101 のように表すこともできます。

$$f_B = \frac{1}{2 \times \pi} \times \sqrt{G_{Plant0} \times G_{Ctrl0} \times K} = 6.66 \text{ Hz} \quad (101)$$

式 92 および式 93 を用いて、極周波数とゼロ周波数を計算します。それから式 89、式 90、式 91 を用いて補償部品の値を求めます。

$$f_Z = \frac{f_B}{K} = 1.48 \text{ Hz} \quad (102)$$

$$f_P = f_B \times K = 30.0 \text{ Hz} \quad (103)$$

$$C_{CO1} = \frac{f_Z}{f_P} \times \frac{1}{G_{Ctrl0}} \times \frac{V_{OSReg}}{V_{OutReg}} \times g_M = 25 \text{ nF} \quad (104)$$

$$C_{CO} = \frac{f_P - f_Z}{f_P} \times C_{CO1} = 0.49 \mu\text{F} \quad (105)$$

$$R_{CO} = \frac{1}{2 \times \pi \times f_Z} \times \frac{1}{C_{CO}} = 220 \text{ k}\Omega \quad (106)$$

**図 31. ゲインと周波数との関係**

**図 32. 位相と周波数との関係**

### 8.2.3 アプリケーション曲線

## 9 電源に関する推奨事項

UCC28056を動作させるには、11V～34Vの外付けVCC電源電圧から駆動する必要があります。パッケージの消費電力を抑えるため、電源電圧は12Vを上回らないようにします。短いPCB配線を使用してVCC端子とGND端子の間に $1\mu F$ 以上のコンデンサを接続し、VCC電源をローカル・デカッピングします。UCC28056は長期間にわたってVCC電源電圧から電流を消費しますが、その正確な期間は、出力電圧( $V_{out}$ )がレギュレーションに達する前の入力および負荷によって決まります。UCC28056の駆動に用いる電源には、出力電圧がレギュレーションに達するまでの期間、この電力をソースできる能力が必要です。

## 10 レイアウト

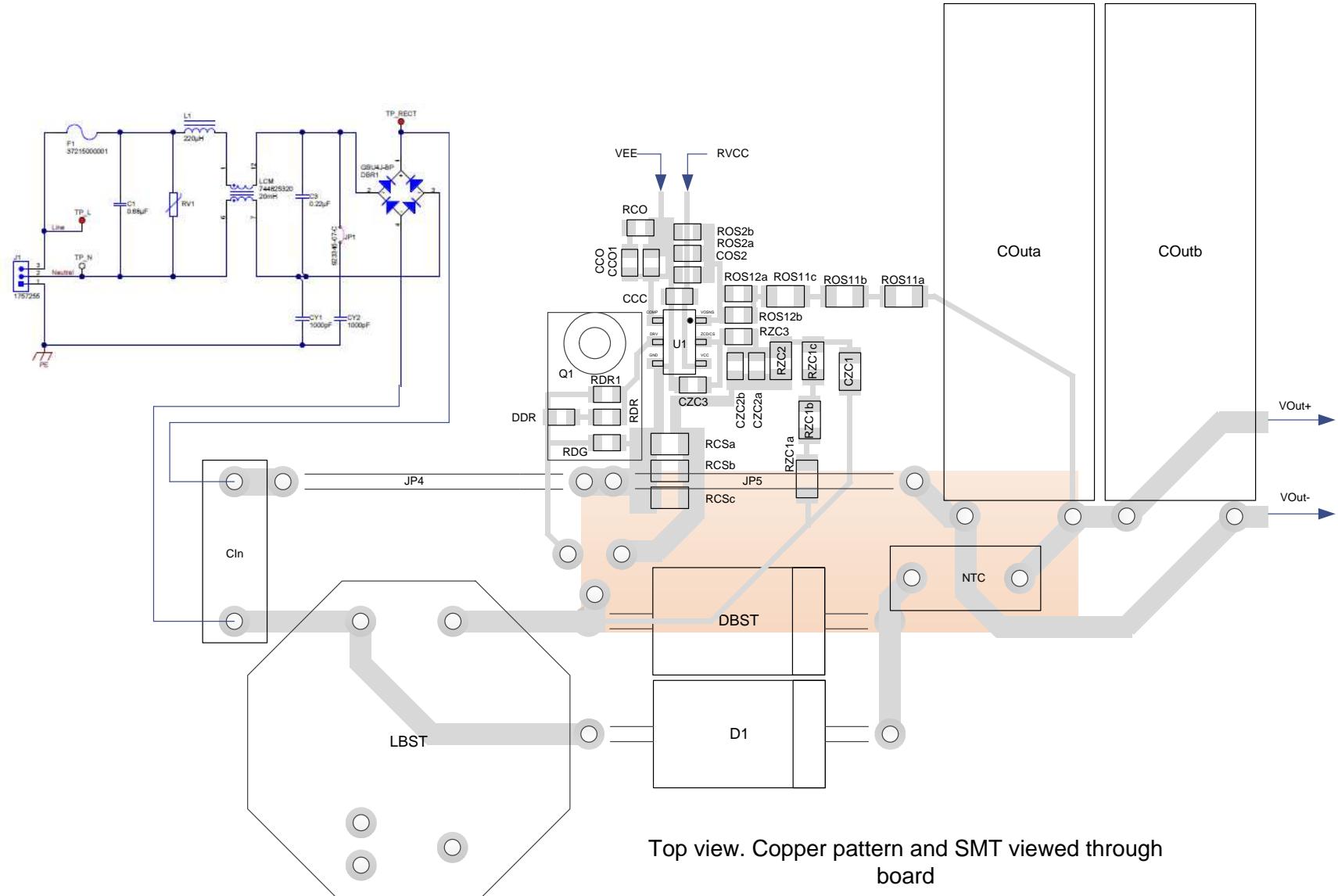

### 10.1 レイアウトのガイドライン

#### 10.1.1 VOSNS端子

$R_{OS2}$ と $C_{OS2}$ の部品は、 $R_{OS1}$ からなる最低抵抗とともにVOSNS端子に隣接して配置します。高電圧は $R_{OS1}$ からなる抵抗を通って降下します。 $R_{OS1}$ およびその内部に接続する高電圧ノードの周囲に十分なスペースを確保して、PCB表面における空中放電を回避します。

#### 10.1.2 ZCD/CS端子

この端子に電力を送る信号にスイッチング・エッジ・スパイクが生じると、内蔵するESD構造が導通し、この端子に電力を送る分圧コンデンサに電圧オフセットが生じます。このリスクを抑えるため、分圧器はZCD/CS端子には近く、高速充電磁界の領域からは離して配置します。[図 37](#)に示す網掛け部分を参照してください。分圧器の抵抗とコンデンサとの接続を少なく維持することで、分圧チェーン内の容量ピックアップを抑えます。[図 36](#)に示すループは小さくしておき、磁気ピックアップを抑制する最小限の領域を含めます。電流検知抵抗とUCC28056の間の接続は、抵抗端まで直接伸ばし、電源回路の配線とは共有しません。

PCBのレイアウトに際しては、ZCD/CS端子分圧器の配置と配線から始めて、この端子のニーズを最優先するものとします。

#### 10.1.3 VCC端子

短い専用のPCB配線を介して、ローカル・デカッピング・コンデンサをVCC端子とGND端子の間に直接接続する必要があります。このコンデンサは、パワーMOSFETのゲート容量を充電するために必要な大電流パルスを供給します。

#### 10.1.4 GND端子

UCC28056のGND接続用のPCB配線は、必ず電源回路のGND接続から離して配置してください。UCC28056のGND端子は、電流検知抵抗の一端でのみ電源回路GNDに接続します。この接続方法により、UCC28056のGND端子とZCD/CS端子の間の電圧をMOSFET導通期間中に電流検知抵抗を通った電圧と等しく維持できます。

#### 10.1.5 DRV端子

DRV端子の配線は、ZCD/CSやVOSNSなど他の高インピーダンスな接続部に近接して配置しないでください。この端子の波形に関連する高速な立ち上がり/立ち下がりエッジが、これらの高インピーダンスな接続部に容量結合して、スイッチング・エッジ付近で外乱を生じることがあります。

#### 10.1.6 COMP端子

この端子に実装するRCネットワークを、端子に近接して配置します。GND端子へのリターンは、短いPCB配線を介する必要があります。

## 10.2 レイアウト例

図 36. レイアウト・ガイドラインによる回路図

図 37. 推奨するPCBレイアウト

(片面部品)

## 11 デバイスおよびドキュメントのサポート

### 11.1 WEBENCH®ツールによるカスタム設計

ここをクリックすると、WEBENCH® Power Designerにより、UCC28056デバイスを使用するカスタム設計を作成できます。

- 最初に、入力電圧( $V_{IN}$ )、出力電圧( $V_{OUT}$ )、出力電流( $I_{OUT}$ )の要件を入力します。

- オプティマイザのダイヤルを使用して、効率、占有面積、コストなどの主要なパラメータについて設計を最適化します。

- 生成された設計を、テキサス・インスツルメンツが提供する他のソリューションと比較します。

WEBENCH Power Designerでは、カスタマイズされた回路図と部品リストを、リアルタイムの価格と部品の在庫情報と一緒に参照できます。

ほとんどの場合、次の操作を実行可能です。

- 電気的なシミュレーションを実行し、重要な波形と回路の性能を確認する。

- 熱シミュレーションを実行し、基板の熱特性を把握する。

- カスタマイズされた回路図やレイアウトを、一般的なCADフォーマットでエクスポートする。

- 設計のレポートをPDFで印刷し、同僚と設計を共有する。

WEBENCHツールの詳細は、[www.ti.com/WEBENCH](http://www.ti.com/WEBENCH)でご覧になれます。

### 11.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、ti.comのデバイス製品フォルダを開いてください。右上の隅にある「通知を受け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

### 11.3 コミュニティ・リソース

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's [Terms of Use](#).

**TI E2E™オンライン・コミュニティ** *TIのE2E ( Engineer-to-Engineer )* コミュニティ。エンジニア間の共同作業を促進するために開設されたものです。e2e.ti.comでは、他のエンジニアに質問し、知識を共有し、アイディアを検討して、問題解決に役立てることができます。

**設計サポート** *TIの設計サポート* 役に立つE2Eフォーラムや、設計サポート・ツールをすばやく見つけることができます。技術サポート用の連絡先情報も参照できます。

### 11.4 商標

E2E is a trademark of Texas Instruments.

WEBENCH is a registered trademark of Texas Instruments.

STMicroelectronics is a registered trademark of STMicroelectronics.

All other trademarks are the property of their respective owners.

### 11.5 静電気放電に関する注意事項

すべての集積回路は、適切なESD保護方法を用いて、取扱いと保存を行なうようにして下さい。

静電気放電はわずかな性能の低下から完全なデバイスの故障に至るまで、様々な損傷を与えます。高精度の集積回路は、損傷に対して敏感であり、極めてわずかなパラメータの変化により、デバイスに規定された仕様に適合しなくなる場合があります。

### 11.6 Glossary

[SLYZ022 — TI Glossary](#).

This glossary lists and explains terms, acronyms, and definitions.

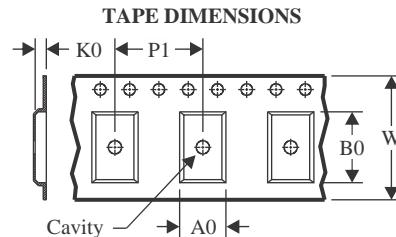

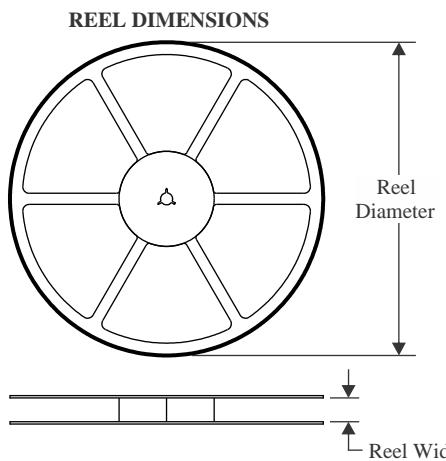

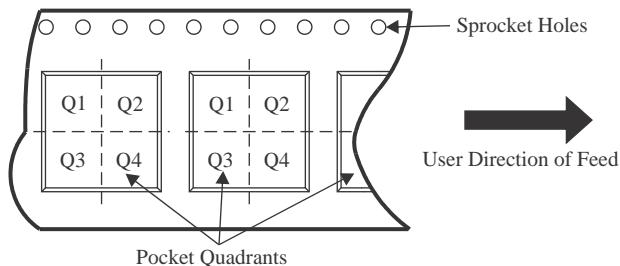

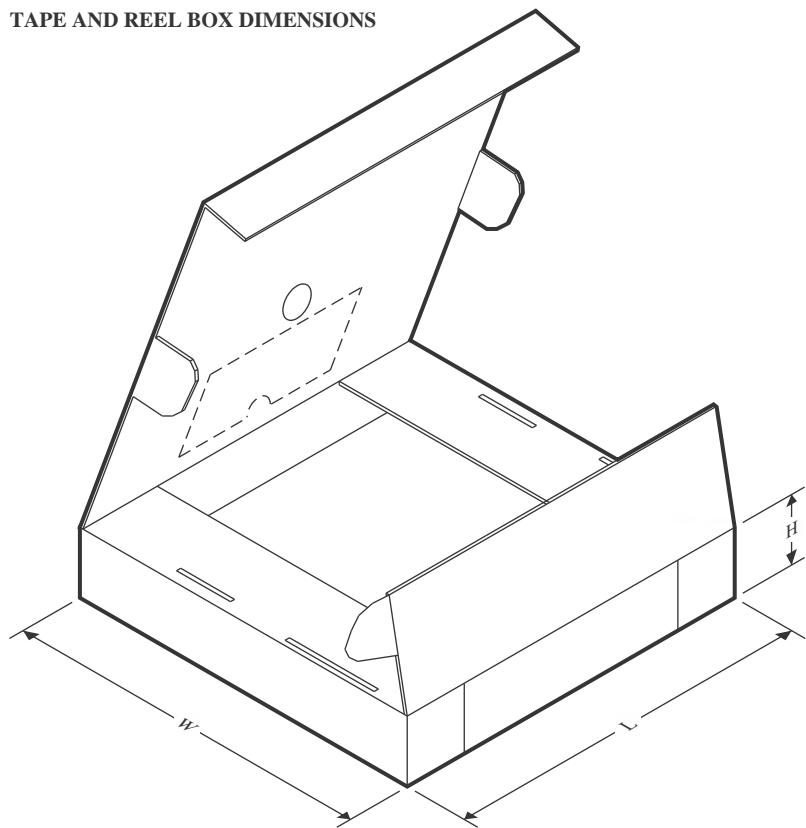

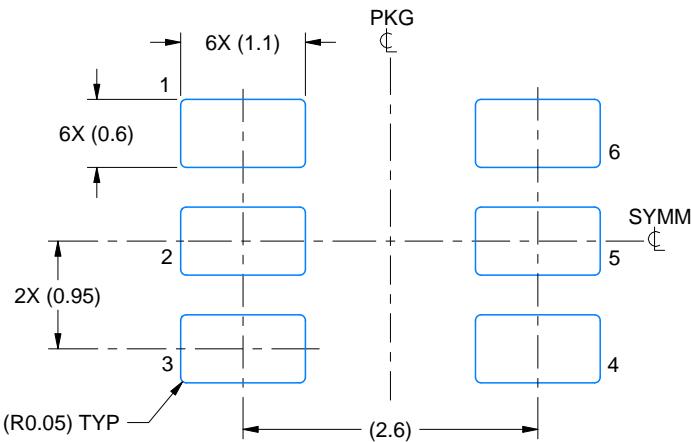

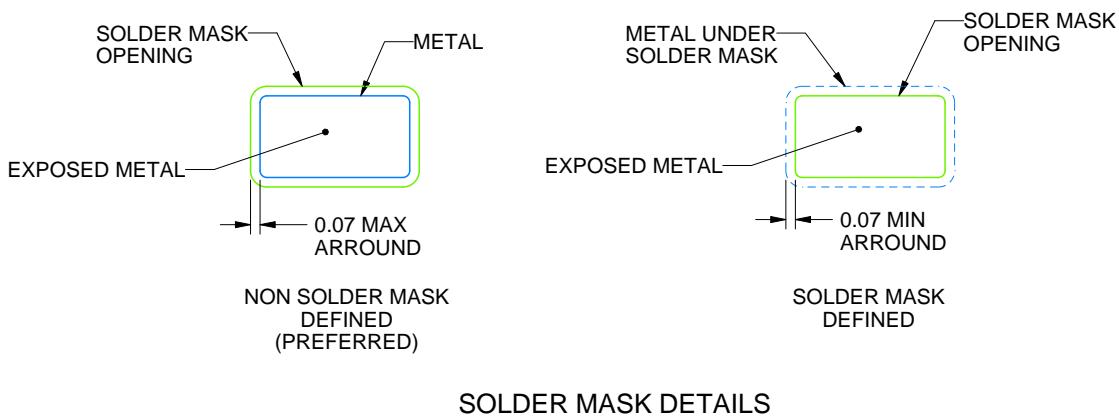

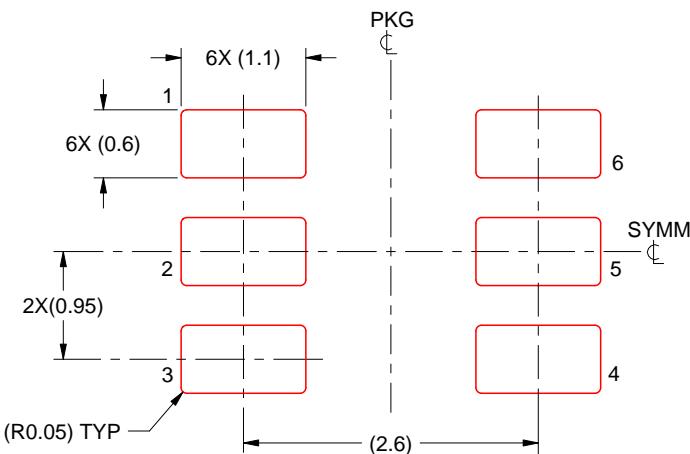

## 12 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、そのデバイスについて利用可能な最新のデータです。このデータは予告なく変更されることがあります。ドキュメントが改訂される場合もあります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

**PACKAGING INFORMATION**

| Orderable part number         | Status<br>(1) | Material type<br>(2) | Package   Pins   | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-------------------------------|---------------|----------------------|------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| <a href="#">UCC28056ADBVR</a> | Active        | Production           | SOT-23 (DBV)   6 | 3000   LARGE T&R      | Yes         | Call TI   Nipdau                     | Level-1-260C-UNLIM                | -40 to 125   | 805A                |

| UCC28056ADBVR.A               | Active        | Production           | SOT-23 (DBV)   6 | 3000   LARGE T&R      | Yes         | Call TI                              | Level-1-260C-UNLIM                | -40 to 125   | 805A                |

| UCC28056ADBVR.B               | Active        | Production           | SOT-23 (DBV)   6 | 3000   LARGE T&R      | Yes         | Call TI                              | Level-1-260C-UNLIM                | -40 to 125   | 805A                |

| <a href="#">UCC28056ADBVT</a> | Active        | Production           | SOT-23 (DBV)   6 | 250   SMALL T&R       | Yes         | Call TI   Nipdau                     | Level-1-260C-UNLIM                | -40 to 125   | 805A                |

| UCC28056ADBVT.A               | Active        | Production           | SOT-23 (DBV)   6 | 250   SMALL T&R       | Yes         | Call TI                              | Level-1-260C-UNLIM                | -40 to 125   | 805A                |

| UCC28056ADBVT.B               | Active        | Production           | SOT-23 (DBV)   6 | 250   SMALL T&R       | Yes         | Call TI                              | Level-1-260C-UNLIM                | -40 to 125   | 805A                |

| UCC28056ADBVTG4               | Active        | Production           | SOT-23 (DBV)   6 | 250   SMALL T&R       | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 805A                |

| UCC28056ADBVTG4.A             | Active        | Production           | SOT-23 (DBV)   6 | 250   SMALL T&R       | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 805A                |

| UCC28056ADBVTG4.B             | Active        | Production           | SOT-23 (DBV)   6 | 250   SMALL T&R       | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 805A                |

| <a href="#">UCC28056BDBVR</a> | Active        | Production           | SOT-23 (DBV)   6 | 3000   LARGE T&R      | Yes         | Call TI   Nipdau                     | Level-1-260C-UNLIM                | -40 to 125   | 805B                |

| UCC28056BDBVR.A               | Active        | Production           | SOT-23 (DBV)   6 | 3000   LARGE T&R      | Yes         | Call TI                              | Level-1-260C-UNLIM                | -40 to 125   | 805B                |

| UCC28056BDBVR.B               | Active        | Production           | SOT-23 (DBV)   6 | 3000   LARGE T&R      | Yes         | Call TI                              | Level-1-260C-UNLIM                | -40 to 125   | 805B                |

| <a href="#">UCC28056BDBVT</a> | Active        | Production           | SOT-23 (DBV)   6 | 250   SMALL T&R       | Yes         | Call TI   Nipdau                     | Level-1-260C-UNLIM                | -40 to 125   | 805B                |

| UCC28056BDBVT.A               | Active        | Production           | SOT-23 (DBV)   6 | 250   SMALL T&R       | Yes         | Call TI                              | Level-1-260C-UNLIM                | -40 to 125   | 805B                |