ALM2403-Q1

# ALM2403-Q1

# 車載用、低歪み、デュアル・チャネル・オ レゾルバ駆動向け保護機能搭載、 ペアンプ

#### 1 特長

- 車載アプリケーション用に AEC-Q100 認定済み:

- 温度グレード 1:T<sub>A</sub> = -40℃~+125℃

- 機能安全に対応

- 機能安全システムの設計に役立つ資料を利用可

- 大出力電流の駆動:ピーク 500mA (チャネル毎)

- ディスクリート・オペアンプおよびトランジスタの代替

- 両方の電源について広い電源電圧範囲 (最高 24V)

- 過熱シャットダウン

- 電流制限

- 低 I<sub>O</sub> アプリケーション用のシャットダウン・ピン

- 21MHz のゲイン帯域幅、50V/µs のスルーレート

- パッケージ:14 ピン HTSSOP (PWP)

# 2 アプリケーション

- リゾルバを使用した車載用および産業用アプリケーショ

- インバータおよびモーター制御

- ブレーキ・システム

- 電動パワー・ステアリング (EPS)

- リアビュー・ミラー・モジュール

- 車載用電子ミラー

- サーボ・ドライブの電力段モジュール

- 飛行制御システム

### 3 概要

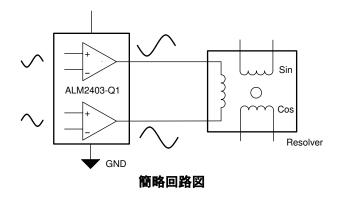

ALM2403-Q1 は、レゾルバを使用したアプリケーションに 最適な機能と性能を備えたデュアルパワー・オペアンプで す。大出力電流を連続的に駆動できると同時に、デバイス のゲイン帯域幅が広く、スルーレートが大きいため、リゾル バの 1 次コイルの励起に必要な低歪みの差動大振幅励 磁の実現に適しています。電流制限と過熱検出により、特 にフォルトが発生しやすい有線によるアナログ信号の駆動 時に、システム全体の堅牢性を高めることができます。

サーマル・パッド付きで R<sub>0JA</sub> が小さい小型の HTSSOP パッケージにより、基板面積を最小化すると同時に大電流 を負荷に供給できます。ALM2403-Q1 のゲイン帯域幅が 広いため、高出力駆動能力を保った状態で、デバイスをフ ィルタ段として構成できます。その結果、レゾルバ駆動の シグナル・チェーン全体のソリューション・サイズを大幅に 縮小できます。このソリューション・サイズの縮小は、 ALM2403-Q1 を車載用および産業用アプリケーションで 使用する場合の主な利点のひとつです。

## パッケージ情報

| 部品番号       | パッケージ <sup>(1)</sup> | 本体サイズ (公称)      |

|------------|----------------------|-----------------|

| ALM2403-Q1 | HTSSOP (14)          | 5.00mm × 4.40mm |

利用可能なパッケージについては、データシートの末尾にあるパ ッケージ・オプションについての付録を参照してください。

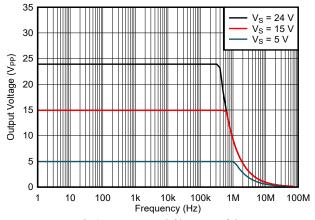

出力電圧と周波数との関係

# **Table of Contents**

| 1 特長1                                 | 7.4 Device Functional Modes             | 14              |

|---------------------------------------|-----------------------------------------|-----------------|

| 2 アプリケーション1                           | 8 Application and Implementation        | 15              |

| 3 概要1                                 | 8.1 Application Information             | 15              |

| 4 Revision History2                   | 8.2 Typical Application                 |                 |

| 5 Pin Configuration and Functions3    | 8.3 Power Supply Recommendations        | 19              |

| 6 Specifications4                     | 8.4 Layout                              | 19              |

| 6.1 Absolute Maximum Ratings4         | 9 Device and Documentation Support      | <mark>22</mark> |

| 6.2 ESD Ratings4                      | 9.1 Documentation Support               | 22              |

| 6.3 Recommended Operating Conditions4 | 9.2ドキュメントの更新通知を受け取る方法                   | 22              |

| 6.4 Thermal Information4              | 9.3 サポート・リソース                           | 22              |

| 6.5 Electrical Characteristics5       | 9.4 Trademarks                          | 22              |

| 6.6 Typical Characteristics7          | 9.5 静電気放電に関する注意事項                       | 22              |

| 7 Detailed Description12              | 9.6 用語集                                 | 22              |

| 7.1 Overview12                        | 10 Mechanical, Packaging, and Orderable |                 |

| 7.2 Functional Block Diagram12        | Information                             | 22              |

| 7.3 Feature Description13             |                                         |                 |

| ·                                     |                                         |                 |

# **4 Revision History**

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision * (November 2020) to Revision A (March 2023)                                                              | Page           |

|---------------------------------------------------------------------------------------------------------------------------------|----------------|

| <ul><li>「特長」の出力電流を 650mA から 500mA に変更</li></ul>                                                                                 | 1              |

| • 表紙のプロットでタイトルと Y 軸の単位を変更                                                                                                       | 1              |

| Changed pin names to synchronize pin naming throughout document                                                                 | 3              |

| Changed thermal pad description text for clarity                                                                                |                |

| Changed voltage range for V <sub>OTF/SH DN</sub> in the Absolute Maximum Ratings                                                |                |

| • Changed all V <sub>S</sub> voltages to single-supply nomenclature in the <i>Electrical Characteristics</i> and <i>Typical</i> |                |

| Chacteristics                                                                                                                   | 5              |

| • Deleted test conditions from enable high and low input voltages in the Electrical Characteristics                             | 5              |

| • Moved shutdown current parameter to Power Supply section in the Electrical Characteristics                                    | 5              |

| Changed Figures 6-12 through 6-16 to correct axis units and values                                                              | <mark>7</mark> |

| Changed functional block diagram to correct inaccuracies                                                                        | 12             |

| Changed EMC capacitance from 50 nF to 10 nF in Table 8-1, Design Parameters                                                     |                |

| Added test condition to first bullet of Detailed Design Procedure                                                               |                |

| Changed R3 to R2 in 2nd paragraph of Filter Design section                                                                      |                |

| Changed terms in Equation 4 to Equation 6 for clarity                                                                           |                |

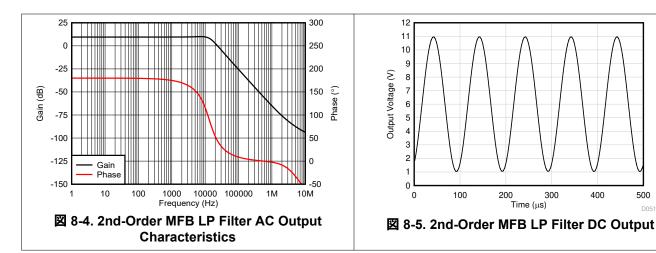

| Changed Figure 8-4, 2nd-Order MFB LP Filter AC Output Characteristics                                                           |                |

| Changed values in Table 8-2, Signal Attenuation vs Frequency                                                                    |                |

| Changed Figure 8-6, ALM2403-Q1 Layout Example, to match EVM layout                                                              |                |

|                                                                                                                                 |                |

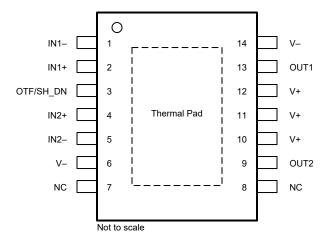

# **5 Pin Configuration and Functions**

図 5-1. PWP Package, 14-Pin HTSSOP (Top View)

表 5-1. Pin Functions

| Р           | PIN TYPE    |              | DESCRIPTION                                                                                                                                                                                                                                            |  |

|-------------|-------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NO.         | NAME        | IIPE         | DESCRIPTION                                                                                                                                                                                                                                            |  |

| 1           | IN1-        | Input        | Inverting op amp input for channel 1                                                                                                                                                                                                                   |  |

| 2           | IN1+        | Input        | Noninverting op amp input for channel 1                                                                                                                                                                                                                |  |

| 3           | OTF/SH_DN   | Input/Output | Overtemperature flag and shutdown (see 表 7-1, Shutdown Truth Table)                                                                                                                                                                                    |  |

| 4           | IN2+        | Input        | Noninverting op amp input for channel 2                                                                                                                                                                                                                |  |

| 5           | IN2-        | Input        | Inverting op amp input for channel 2                                                                                                                                                                                                                   |  |

| 6, 14       | V–          | _            | Negative supply pin (both negative supply pins must be used and connected together)                                                                                                                                                                    |  |

| 7, 8        | NC          | _            | No internal connection (do not connect)                                                                                                                                                                                                                |  |

| 9           | OUT2        | Output       | Op amp output for channel 2                                                                                                                                                                                                                            |  |

| 10, 11, 12  | V+          | _            | Positive supply pin                                                                                                                                                                                                                                    |  |

| 13          | OUT1        | Output       | Op amp output for channel 1                                                                                                                                                                                                                            |  |

| Thermal Pad | Thermal Pad | _            | Connect the exposed thermal pad to the most negative supply on the device, V–, for best thermal performance. The thermal pad can also be left floating electrically; the heat spread of the pad can be thermally maximized and conducted into the PCB. |  |

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                        |                                     |                                   | MIN        | MAX               | UNIT |

|------------------------|-------------------------------------|-----------------------------------|------------|-------------------|------|

| V                      | Supply voltage                      | Single-supply, $V_S = (V+) - GND$ |            | 26                | V    |

| V <sub>S</sub>         | Supply voltage                      | Dual-supply, $V_S = (V+) - (V-)$  |            | ±13               | V    |

| Ciamal immediate       | Common-mode                         | (V-) - 0.7                        | (V+) + 0.7 | V                 |      |

| Signal input voltage   |                                     | Differential                      |            | (V+) - (V-) + 0.2 | V    |

| V <sub>OTF/SH_DN</sub> | OTF/SH_DN OTF/SH_DN pin voltage     |                                   | (V-) - 0.2 | (V-) + 5.7        | V    |

|                        | Signal input current                |                                   |            | ±10               | mA   |

|                        | Output short circuit <sup>(2)</sup> |                                   | Continuous | Continuous        |      |

| T <sub>A</sub>         | Operating temperature               |                                   | -55        | 150               | °C   |

| T <sub>J</sub>         | Junction temperature                |                                   |            | 150               | °C   |

| T <sub>stg</sub>       | Storage temperature                 |                                   | -65        | 150               | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

## 6.2 ESD Ratings

|                    |                         |                                                                                           | VALUE | UNIT |

|--------------------|-------------------------|-------------------------------------------------------------------------------------------|-------|------|

|                    | Electrostatic discharge | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup><br>HBM ESD classification level 2 | ±2000 | V    |

| V <sub>(ESD)</sub> | Liectrostatic discharge | Charged-device model (CDM), per AEC Q100-011<br>CDM ESD classification level C5           | ±750  | V    |

<sup>1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

#### **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                               |                       |                                            | MIN  | NOM MAX | UNIT |

|-------------------------------|-----------------------|--------------------------------------------|------|---------|------|

| V <sub>S</sub> Supply voltage | Supply voltage        | Single-supply, V <sub>S</sub> = (V+) – GND | 5    | 24      | V    |

|                               | Supply voltage        | Dual-supply, $V_S = (V+) - (V-)$           | ±2.5 | ±12     | V    |

| T <sub>A</sub>                | Operating temperature |                                            | -40  | 125     | °C   |

#### 6.4 Thermal Information

|                       |                                              | ALM2403-Q1   |      |

|-----------------------|----------------------------------------------|--------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | PWP (HTSSOP) | UNIT |

|                       |                                              | 14 PINS      |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 46.9         | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 42.1         | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 22.6         | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 1.2          | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 22.5         | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 5.9          | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2025 Texas Instruments Incorporated

<sup>(2)</sup> Short-circuit to ground, one amplifier per package.

## 6.5 Electrical Characteristics

at  $T_A$  = 25°C,  $V_S$  = V+ = 24 V, V- = GND,  $R_L$  = 10 k $\Omega$  connected to  $V_S$  / 2, and  $V_{CM}$  =  $V_{OUT}$  =  $V_S$  / 2 (unless otherwise noted)

|                                  | PARAMETER                                                                      | TEST CONDI                                                                                                                                                         | TIONS                                                          | MIN        | TYP    | MAX        | UNIT               |

|----------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------------|--------|------------|--------------------|

| OFFSET V                         | OLTAGE                                                                         |                                                                                                                                                                    |                                                                |            |        | ı          |                    |

| V <sub>OS</sub>                  | Input offset voltage                                                           |                                                                                                                                                                    |                                                                |            | ±6     | ±25        | mV                 |

| dV <sub>OS</sub> /dT             | Input offset voltage drift                                                     | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$                                                                                                                     |                                                                |            | ±15    | ±50        | μV/°C              |

| 2022                             | Power-supply rejection                                                         | V <sub>S</sub> = 5 V to 24 V                                                                                                                                       | V <sub>S</sub> = 5 V to 24 V                                   |            | ±10    | ±47        | 1/0/               |

| PSRR                             | ratio                                                                          | $V_S = 5 \text{ V to } 24 \text{ V}, T_A = -40^{\circ}\text{C to } +12$                                                                                            | V <sub>S</sub> = 5 V to 24 V, T <sub>A</sub> = -40°C to +125°C |            |        | ±50        | μV/V               |

|                                  | Channel separation                                                             | f = 10 kHz                                                                                                                                                         |                                                                |            | 120    |            | dB                 |

| INPUT BIA                        | AS CURRENT                                                                     |                                                                                                                                                                    |                                                                |            |        | I.         |                    |

|                                  | land bing somet                                                                |                                                                                                                                                                    |                                                                |            | 10     | ±100       | pA                 |

| I <sub>B</sub>                   | Input bias current                                                             | $T_A = -40$ °C to +125°C                                                                                                                                           |                                                                |            |        | ±100       | nA                 |

|                                  | Innut offset surrent                                                           |                                                                                                                                                                    |                                                                |            | 10     | ±200       | pА                 |

| los                              | Input offset current                                                           | $T_A = -40$ °C to +125°C                                                                                                                                           |                                                                |            |        | ±100       | nA                 |

| NOISE                            |                                                                                |                                                                                                                                                                    |                                                                |            |        |            |                    |

|                                  | Input voltage noise                                                            | f = 0.1 Hz to 10 Hz                                                                                                                                                |                                                                |            | 8      |            | μV <sub>RMS</sub>  |

| _                                | Input voltage noise                                                            | f = 1 kHz                                                                                                                                                          |                                                                |            | 150    |            | nV/√ <del>Hz</del> |

| e <sub>N</sub>                   | density                                                                        | f = 100 kHz                                                                                                                                                        |                                                                |            | 22     |            | IIV/√⊓Z            |

| i <sub>N</sub>                   | Input current noise                                                            | f = 1 kHz                                                                                                                                                          |                                                                |            | 48     |            | fA/√Hz             |

| INPUT VO                         | LTAGE                                                                          |                                                                                                                                                                    |                                                                |            |        | •          |                    |

| V <sub>CM</sub>                  | Common-mode voltage                                                            |                                                                                                                                                                    |                                                                | (V-) - 0.2 |        | (V+) + 0.2 | V                  |

| CMRR Common-mode rejection ratio |                                                                                | $(V-) - 0.5 V < V_{CM} < (V+) + 0.5 V, 1$                                                                                                                          | 0 V ≤ V <sub>S</sub> < 24 V                                    | 49         | 72     |            |                    |

|                                  |                                                                                | $(V-) - 0.2 \text{ V} < V_{CM} < (V+) + 0.2 \text{ V},$<br>$T_A = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, 10 \text{ V} < \text{V}_{\text{S}} < 0.00$ | 24 V                                                           | 52         |        |            |                    |

|                                  | (V-) + 2.5 V < V <sub>CM</sub> < (V+) - 2.5 V,<br>10 V < V <sub>S</sub> < 24 V |                                                                                                                                                                    | 80                                                             | 94         |        | dB         |                    |

|                                  |                                                                                | $(V-) + 2.5 \text{ V} < V_{CM} < (V+) - 2.5 \text{ V},$<br>$T_A = -40 ^{\circ}\text{C} \text{ to } +125 ^{\circ}\text{C}, 10 \text{ V} < \text{V}_S <$             | 24 V                                                           | 75         |        |            |                    |

|                                  |                                                                                | $(V-) - 0.5 V < V_{CM} < (V+) + 0.5 V, 5$                                                                                                                          | V < V <sub>S</sub> < 24 V                                      | 44         | 59     |            |                    |

| INPUT CA                         | PACITANCE                                                                      |                                                                                                                                                                    |                                                                |            |        |            |                    |

| Z <sub>ID</sub>                  | Differential                                                                   |                                                                                                                                                                    |                                                                |            | 1    2 |            | 00 !! [            |

| Z <sub>ICM</sub>                 | Common-mode                                                                    |                                                                                                                                                                    |                                                                |            | 1    2 |            | GΩ    pF           |

| OPEN-LO                          | OP GAIN                                                                        |                                                                                                                                                                    |                                                                | -          |        |            |                    |

|                                  |                                                                                | $(V-) + 0.5 V < V_O < (V+) - 0.5 V$                                                                                                                                |                                                                | 103        | 111    |            |                    |

|                                  | 0                                                                              | V <sub>S</sub> = 24 V                                                                                                                                              | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$                 | 96         |        |            | -ID                |

| A <sub>OL</sub>                  | Open-loop voltage gain                                                         | (V–) + 1.5 V < V <sub>O</sub> < (V+) – 1.5 V,                                                                                                                      |                                                                | 96         | 104    |            | dB                 |

|                                  |                                                                                | $R_L = 225 \Omega, V_S = 24 V$                                                                                                                                     | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$           | 94         |        |            |                    |

| FREQUEN                          | ICY RESPONSE                                                                   |                                                                                                                                                                    |                                                                |            |        |            |                    |

| GBW                              | Gain-bandwidth product                                                         | V <sub>S</sub> = 24 V                                                                                                                                              |                                                                |            | 21     |            | MHz                |

| SR                               | Slew rate                                                                      | 10-V step, gain = +1                                                                                                                                               |                                                                |            | 50     |            | V/µs               |

|                                  | 0-441:                                                                         | To 0.1%, 10-V step , gain = +1, C <sub>L</sub> =                                                                                                                   | 10 pF                                                          |            | 0.31   |            |                    |

| t <sub>S</sub>                   | Settling time                                                                  | To 0.1%, 10-V step , gain = -1, C <sub>L</sub> = 10 pF                                                                                                             |                                                                |            | 0.40   |            | μs                 |

|                                  | Overload recovery time                                                         | $V_{IN} \times gain > V_{S}$                                                                                                                                       |                                                                |            | 0.28   |            | μs                 |

| THD+N                            | Total harmonic distortion + noise                                              | V <sub>S</sub> = 15 V, V <sub>O</sub> = 10 Vpp, gain = –1,<br>f = 10 kHz, R <sub>L</sub> = 100 Ω                                                                   |                                                                |            | 74     |            | dB                 |

# 6.5 Electrical Characteristics (続き)

at  $T_A$  = 25°C,  $V_S$  = V+ = 24 V, V- = GND,  $R_L$  = 10 k $\Omega$  connected to  $V_S$  / 2, and  $V_{CM}$  =  $V_{OUT}$  =  $V_S$  / 2 (unless otherwise noted)

|                        | PARAMETER                      | TEST CONDITIONS                                        | MIN | TYP | MAX | UNIT |

|------------------------|--------------------------------|--------------------------------------------------------|-----|-----|-----|------|

| OUTPUT                 |                                |                                                        |     |     |     |      |

|                        | Voltage output swing from rail | I <sub>OUT</sub> = ±5 mA                               |     | 35  | 60  | mV   |

| 1                      | Short-circuit current          | Sinking                                                |     | 400 |     | mA   |

| I <sub>SC</sub>        | Short-circuit current          | Sourcing                                               |     | 500 |     | IIIA |

| ENABLE                 |                                |                                                        |     |     |     |      |

| V <sub>IH_OTF</sub>    | Enable high input voltage      |                                                        | 1.2 |     |     | V    |

| V <sub>IL_OTF</sub>    | Enable low input voltage       |                                                        |     |     | 0.5 | V    |

|                        | Enable hysteresis              |                                                        |     | 220 |     | mV   |

| t <sub>OTF/SH_DN</sub> | Enable start-up time           |                                                        |     | 5   |     | μs   |

| POWER SU               | JPPLY                          |                                                        |     |     | '   | -    |

|                        | Total suissant surrent         | I <sub>O</sub> = 0 A                                   |     | 3.6 | 5.5 | mA   |

| IQ                     | Total quiescent current        | I <sub>O</sub> = 0 A, T <sub>A</sub> = -40°C to +125°C |     |     | 6   | mA   |

| I <sub>SD</sub>        | Shutdown current               | V <sub>OTF/SH_DN</sub> = 0 V                           |     |     | 260 | μA   |

| TEMPERAT               | TURE                           |                                                        |     |     |     |      |

|                        | Thermal shutdown               |                                                        |     | 172 |     | °C   |

|                        | Thermal shutdown recovery      |                                                        |     | 150 |     | °C   |

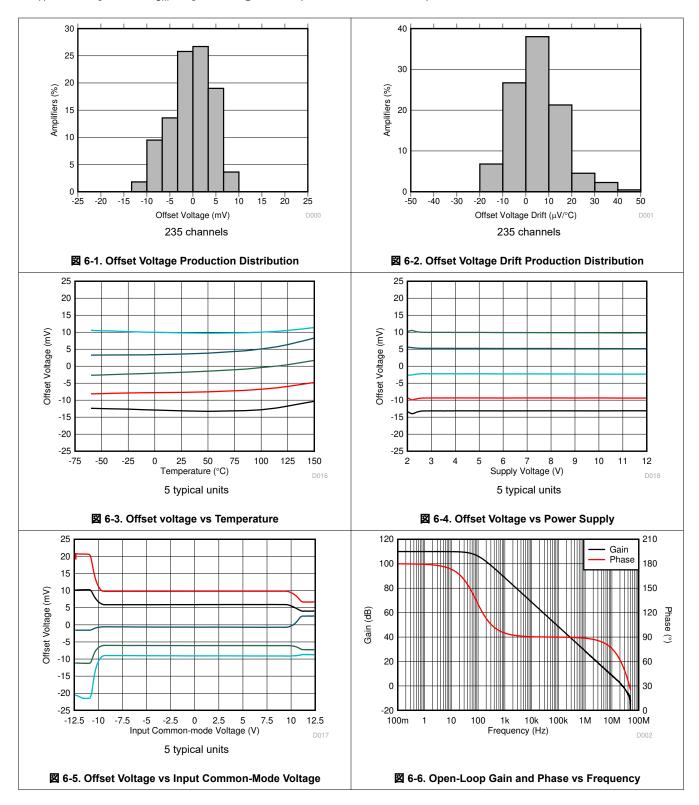

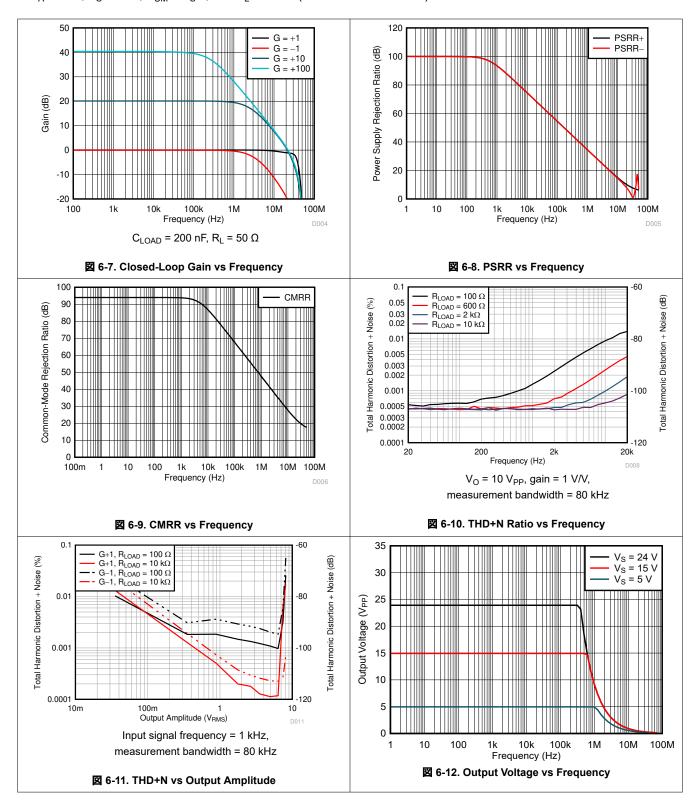

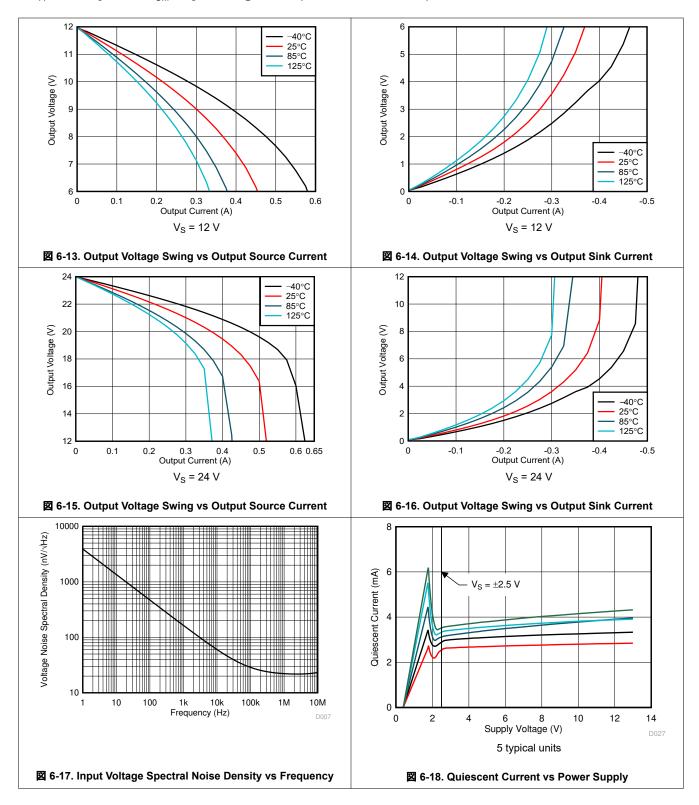

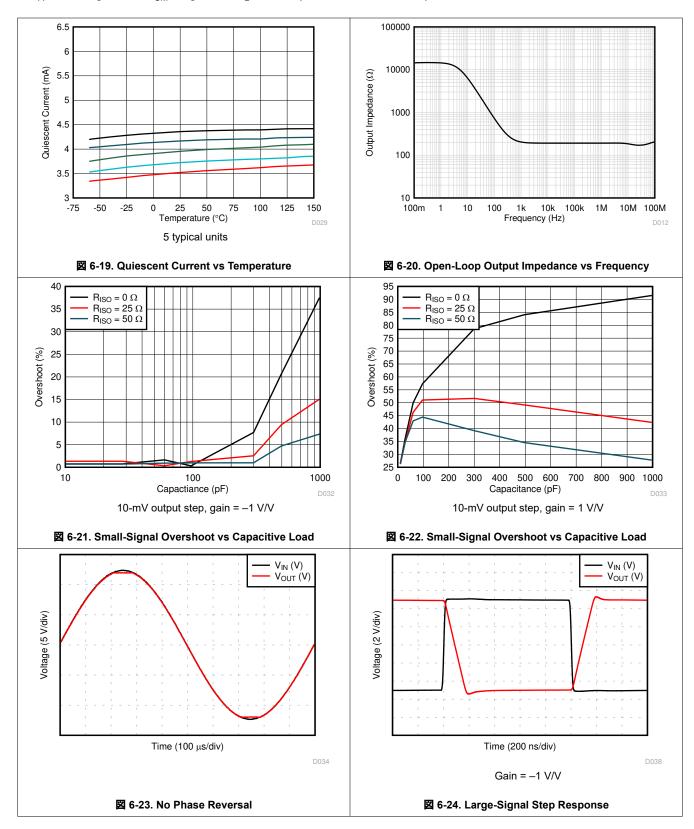

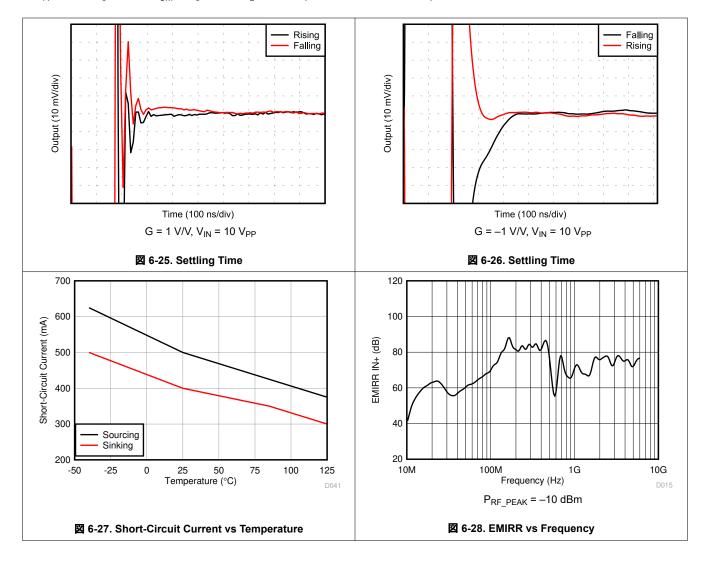

# **6.6 Typical Characteristics**

at  $T_A$ = 25°C,  $V_S$  = 24 V,  $V_{CM}$  =  $V_S/2$ , and  $R_L$  = 10 k $\Omega$  (unless otherwise noted)

at  $T_A$ = 25°C,  $V_S$  = 24 V,  $V_{CM}$  =  $V_S/2$ , and  $R_L$  = 10 k $\Omega$  (unless otherwise noted)

at  $T_A$ = 25°C,  $V_S$  = 24 V,  $V_{CM}$  =  $V_S/2$ , and  $R_L$  = 10 k $\Omega$  (unless otherwise noted)

English Data Sheet: SBOSA37

at  $T_A$ = 25°C,  $V_S$  = 24 V,  $V_{CM}$  =  $V_S/2$ , and  $R_L$  = 10 k $\Omega$  (unless otherwise noted)

at  $T_A$ = 25°C,  $V_S$  = 24 V,  $V_{CM}$  =  $V_S/2$ , and  $R_L$  = 10 k $\Omega$  (unless otherwise noted)

# 7 Detailed Description

#### 7.1 Overview

The ALM2403-Q1 is a dual-power op amp qualified for use in automotive applications. Key features for this device are low offset voltage, high output current drive capability, and high FPBW capability. The device also offers protection features such as thermal shutdown and current limit. The 14-pin HTSSOP package minimizes board space and power dissipation.

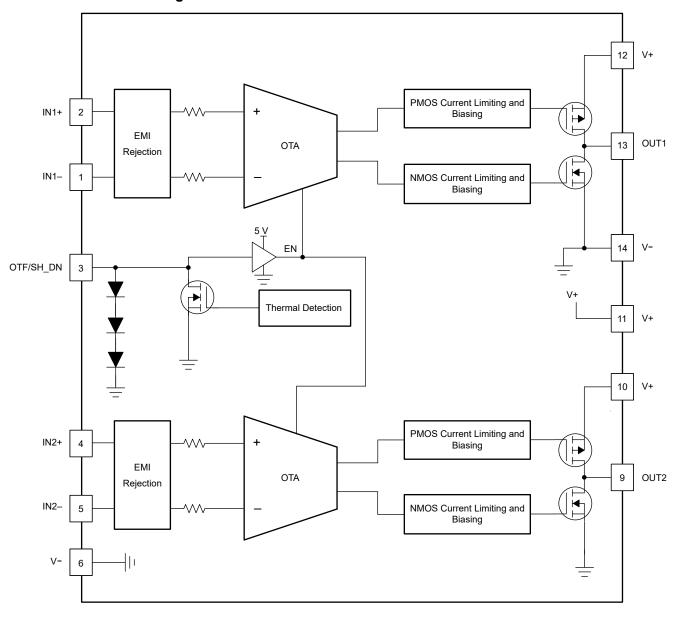

## 7.2 Functional Block Diagram

#### 7.3 Feature Description

#### 7.3.1 Overtemperature and Shutdown Pin (OTF/SH DN)

The overtemperature and shutdown pin, OTF/SH\_DN, is bidirectional and allows both op amps to be put into a low  $I_Q$  state (approximately 200  $\mu$ A per amplifier) when forced low or to less than  $V_{IL\_OTF}$ . As a result of being bidirectional, and the respective enable and disable functionality, this pin must be pulled high or greater than  $V_{IH\_OTF}$  through a pullup resistor. The use of a 10-k $\Omega$  pullup resistor leads to a drive current of approximately 210  $\mu$ A when used with a pullup voltage of 3.3 V.

When the junction temperature of the ALM2403-Q1 exceeds the specified limits, OTF/SH\_DN goes low to alert the application that both the outputs have turned off because of an overtemperature event.

When OTF/SH\_DN is pulled low and the op amps are shut down, the op amps are in an open loop, even when there is negative feedback applied. This occurrence is due to the loss of the open-loop gain in the op amps when the biasing is disabled.

#### 7.3.2 Thermal Shutdown

If the die temperature exceeds safe limits, all outputs are disabled, and the OTF/SH\_DN pin is driven low. After the die temperature has fallen to a safe level, operation automatically resumes. The OTF/SH\_DN pin is released after operation has resumed.

When operating the die at a high temperature, the op amp toggles on and off between the thermal shutdown hysteresis. In this event, the safe limits for the die temperature must be taken in to account. Do not continuously operate the device in thermal hysteresis for long periods of time.

#### 7.3.3 Current-Limit and Short-Circuit Protection

Each op amp in the ALM2403-Q1 has separate internal current limiting for the PMOS (high-side) and NMOS (low-side) output transistors. If the output is shorted to ground, then the PMOS (high-side) current limit is activated, and limits the current to 500 mA nominally. If the output is shorted to supply, then the NMOS (low-side) current limit is activated and limits the current to 400 mA nominally at 25°C. The current limit value is inversely proportional to temperature; therefore, the current limit value increases at low temperatures.

When current is limited, the safe limits for the die temperature must be taken in to account. With too much power dissipation, the die temperature can surpass thermal shutdown limits; the op amp shuts down and reactivates after the die has fallen below thermal limits.

#### 注意

Do not continuously operate the device in thermal hysteresis for long periods of time because this action may cause irreversible damage to the device.

#### 7.3.4 Input Common-Mode Range

The input common-mode range of the ALM2403-Q1 is between (V-) - 0.2 V and (V+) + 0.2 V. Staying within this range allows the op amps to perform and operate within specification. Operating beyond these limits can cause distortion and nonlinearities.

English Data Sheet: SBOSA37

#### 7.3.5 Reverse Body Diodes in Output-Stage Transistors

Designed as a high-voltage, high current operational amplifier, the ALM2403-Q1 delivers robust output drive capability. A class AB output stage with common-source transistors is used to achieve full rail-to-rail output swing capability. Different load conditions change the ability of the amplifier to swing close to the rails.

Each output transistor has internal reverse diodes between drain and source that conduct if the output is forced to greater than the supply or less than ground (reverse current flow). These diodes can be used as flyback protection in inductive-load-driving applications. Limit the use of these diodes to pulsed operation in order to minimize junction temperature overheating due to  $(V_F \times I_F)$ . Internal current-limiting circuitry does not operate when current is flown in the reverse direction and the reverse diodes are active. A method to protect these reverse body diodes is shown in 299328.2.2.1.2.

### 7.3.6 EMI Filtering

Op amps vary with regard to the susceptibility of the device to electromagnetic interference (EMI). If conducted EMI enters the op amp, the dc offset observed at the amplifier output may shift from the nominal value while EMI is present. This shift is a result of signal rectification associated with the internal semiconductor junctions. While all op-amp pin functions can be affected by EMI, the signal input pins are likely to be the most susceptible. The ALM2403-Q1 incorporates an internal input low-pass filter that reduces the amplifiers response to EMI. Both common-mode and differential mode filtering are provided by this filter.

Texas Instruments has developed the ability to accurately measure and quantify the immunity of an operational amplifier over a broad frequency spectrum extending from 10 MHz to 990 MHz. The EMI rejection ratio (EMIRR) metric allows op amps to be directly compared by the EMI immunity. Detailed information can also be found in the EMI Rejection Ratio of Operational Amplifiers application report, available for download from www.ti.com.

#### 7.4 Device Functional Modes

#### 7.4.1 Open-Loop and Closed-Loop Operation

As a result of the very-high, open-loop dc gain of the ALM2403-Q1, the device functions as a comparator in open loop for most applications. A majority of electrical characteristics are verified in negative feedback, closed-loop configurations. Certain dc electrical characteristics, like offset, may have a higher drift across temperature and lifetime when continuously operated in open loop over the lifetime of the device.

#### 7.4.2 Shutdown

When the OTF/SH\_DN pin is left floating or is grounded, the op amp shuts down to a low I<sub>Q</sub> state and does not operate; the op amp outputs go to a high-impedance state.

表 7-1. Shutdown Truth Table

| PIN NAME    | LOGIC STATE OP AMP STATE |                                     |

|-------------|--------------------------|-------------------------------------|

| OTF/SH DN   | High ( > VIH_OTF )       | Operating                           |

| 011/311_DIV | Low ( < VIL_OTF )        | Shutdown (low I <sub>Q</sub> state) |

English Data Sheet: SBOSA37

# 8 Application and Implementation

注

以下のアプリケーション情報は、TIの製品仕様に含まれるものではなく、TIではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 Application Information

The ALM2403-Q1 is a dual-power op amp with performance and protection features that are optimal for many applications. For op amps, there are many general design consideration that must be taken into account. The following subsections describe what to consider for most closed-loop applications. セクション 8.2 gives a specific example of the ALM2403-Q1 being used in a resolver application.

#### 8.1.1 Capacitive Load and Stability

The ALM2403-Q1 is designed for applications where driving a capacitive load is required. As with all op amps, specific instances can occur where the ALM2403-Q1 device can become unstable. The particular op-amp circuit configuration, layout, gain, and output loading are some of the factors to consider when establishing whether or not an amplifier is stable in operation. An op amp in a unity-gain (1-V/V) buffer configuration that drives a capacitive load exhibits a greater tendency to become unstable compared to an amplifier operated at a highernoise gain. The capacitive load, in conjunction with the op-amp output resistance, creates a pole within the feedback loop that degrades the phase margin. The degradation of the phase margin increases as the capacitive loading increases. When operating in a unity-gain configuration, the ALM2403-Q1 remains stable with a pure capacitive load up to approximately 30 pF. Increasing the amplifier closed-loop gain allows the amplifier to drive increasingly larger capacitance. This increased capability is evident when observing the overshoot response of the amplifier at higher voltage gains.

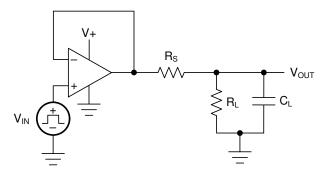

One technique for increasing the capacitive load drive capability of the amplifier operating in a unity-gain configuration is to insert a small resistor ( $R_S$ ; typically, 100 m $\Omega$  to 10  $\Omega$ ) in series with the output, as shown in  $\boxtimes$  8-1. This resistor significantly reduces the overshoot and ringing associated with large capacitive loads.

図 8-1. Capacitive Load Drive

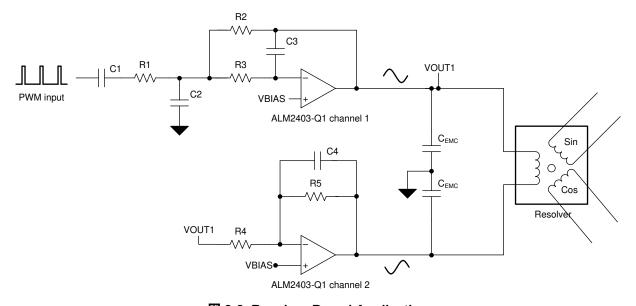

#### 8.2 Typical Application

High-power ac and brushless dc (BLDC) motor-drive applications need position feedback to efficiently and accurately drive the motor. Position feedback can be achieved by using optical encoders, hall sensors, or resolvers. Resolvers are the main choice when environmental or longevity requirements are challenging and extensive.

A resolver acts as a transformer with one primary coil and two secondary coils. The primary coil, or excitation coil, is located on the rotor of the resolver. As the rotor of the resolver spins, the excitation coil induces a current into the sine and cosine sensing coils. These coils are oriented 90 degrees from one another, and the voltage

Copyright © 2025 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

15

from the sine and cosine coils is translated into a vector position by the microcontroller or resolver-to-digital converter chip.

Resolver excitation coils can have a very low dc resistance (<  $100 \Omega$ ), requiring a sink and a source of up to 200 mA from the excitation driver. The ALM2403-Q1 can source and sink this current while providing current-limiting and thermal-shutdown protection. Incorporating these protections in a resolver design can increase the life of the end product.

The input to the ALM2403-Q1 can be an analog sine wave generated by the resolver-to-digital converter chip or a pulse-width modulation (PWM) signal generated from a microcontroller I/O pin. In the case of the latter, a filter stage is needed to extract a lower bandwidth sine wave from the PWM signal. This sine wave would then be the input signal to the ALM2403-Q1. As a result of high gain bandwidth, the ALM2403-Q1 can be configured as a filter stage while providing the required output drive. This configuration significantly reduces the total solution size and design complexity of the resolver-drive signal chain. The fundamental design steps to achieve this functionality are shown in this application example, and can be applied to other inductive-load applications as well.

図 8-2. Resolver-Based Application

#### 8.2.1 Design Requirements

For this design example, use the parameters listed in 表 8-1 as the input parameters.

| DESIGN PARAMETER                  | EXAMPLE VALUE      |  |

|-----------------------------------|--------------------|--|

| Ambient temperature range         | -40°C to +125°C    |  |

| Available supply voltages         | 15 V               |  |

| EMC capacitance (CL)              | 10 nF              |  |

| Resolver excitation input voltage | 7 V <sub>RMS</sub> |  |

| Excitation frequency              | 10 kHz             |  |

| PWM signal frequency              | 320 kHz            |  |

| PWM signal amplitude              | 3.3 V              |  |

| Functional safety capable         | Yes                |  |

| Short-to-battery protection       | Yes                |  |

表 8-1. Design Parameters

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2025 Texas Instruments Incorporated

#### 8.2.2 Detailed Design Procedure

When using the ALM2403-Q1 in a resolver application, determine:

- Resolver excitation input impedance or resistance and inductance:  $Z_0$  = 100 + j188, R = 100  $\Omega$ , and L = 3 mH at 10 kHz

- Resolver transformation ratio (V<sub>SINCOS</sub> / V<sub>EXC</sub>): 0.5 V/V at 10 kHz

- Package and R<sub>θ,JA</sub>: HTSSOP, 46.9°C/W

- Op amp maximum junction temperature: 150°C

- Op amp bandwidth: 21 MHz

Op amp slew rate: 50 V/µS

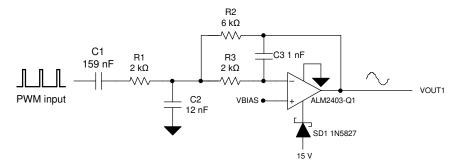

#### 8.2.2.1 Resolver Excitation Amplifier Combined With MFB 2nd-Order, Low-Pass Filter

図 8-3. Two-Pole MFB Filter

When designing a low-pass filter, the most important design criteria is to decide the corner frequency. In this design example, the resolver excitation frequency is 10 kHz and PWM frequency is 320 kHz. Thus, we want to make sure that the low-pass filter corner frequency is greater than 10 kHz, and there is maximum attenuation of harmonic interference generated from the PWM signal.

8-3 shows a single channel of the ALM2403-Q1 configured as a 2-pole multiple feedback (MFB) filter with a -40 dB/decade rolloff. The MFB topology enables a steep rolloff while reducing BOM count. The output from this circuit is a sine wave that can then be inverted using the second channel of the ALM2403-Q1; see 8-2. Thus, both ALM2403-Q1 channels combined provide the required resolver excitation signal.

#### 8.2.2.1.1 Filter Design

The corner frequency of the 2nd-order MFB filter is set to approximately twenty times less than the PWM frequency. The corner frequency defined at -3 dB is shown in  $\pm 1$ .

$$f_p = \frac{1}{2 \times \pi \times \sqrt{R_3 \times C_3 \times R_2 \times C_2}} \tag{1}$$

The 2nd-order MFB active filter uses an inverted input topology and the op amp gain is determined by the ratios of resistors R2 and R1:

$$Gain = -\frac{R_2}{R_1} \tag{2}$$

The gain settings are based on the output drive requirements and PWM signal amplitude. With different gain settings, the filter characteristics, such as rolloff, can change. The design must be fine-tuned to meet optimal performance needs.

The quality (Q) factor of the low-pass filter is configured with Q = 1. The purpose of designing for this Q factor is to minimize attenuation around the corner frequency of 10 kHz, thus extending the pass-band gain. The Q factor of the 2nd-order MFB filter is given by  $\pm 3$ :

$$Q = \frac{\sqrt{C_2/C_3}}{\sqrt{R_3/R_2} + \sqrt{R_2/R_3} + \sqrt{R_3 \times R_2}/R_1}$$

(3)

#### 8.2.2.1.2 Short-to-Battery Protection

Resolver-based applications require the power op amp stage to provide the resolver excitation signal over long cables. In many applications, such as automotive traction inverters, the cables are housed in a harness and a short-circuit condition between different cables in the same harness can occur. In this situation, the output of the ALM2403-Q1 can see a higher voltage than provided at the positive supply pin. This condition causes the body diode in the output stage PMOS to become forward-biased and start conducting. As a precaution, use a blocking diode in series with the positive power supply; see also  $\boxtimes$  8-3.

For related information, see the *ALM2403-Q1 Overvoltage Protection of Resolver-Based Circuits* application note.

#### 8.2.2.2 Power Dissipation and Thermal Reliability

Power dissipation is critical to many industrial and automotive applications. Resolvers are typically chosen over other position feedback techniques because of reliability and accuracy in harsh conditions and high temperatures.

The ALM2403-Q1 is capable of high output current with power-supply voltages up to 24 V. Internal power dissipation increases when operating at high supply voltages. The power dissipated in the op amp ( $P_{OPA}$ ) is calculated using  $\pm 4$ :

$$P_{OPA} = (V_S - V_{OUT}) \times I_{OUT} = (V_S - V_{OUT}) \times \frac{V_{OUT}}{R_L}$$

(4)

To calculate the worst-case power dissipation in the op amp, the ac and dc cases must be considered separately.

In the case of constant output current (dc) to a resistive load, the maximum power dissipation in the op amp occurs when the output voltage is half the positive supply voltage. This calculation assumes that the op amp is sourcing current from the positive supply to a grounded load. If the op amp sinks current from a grounded load, modify  $\pm$  5 to include the negative supply voltage instead of the positive.

$$P_{OPA(MAX\_DC)} = P_{OPA}\left(\frac{V_S}{2}\right) = \frac{(V_S)^2}{4 \times R_L}$$

(5)

The ac maximum of average power dissipation in the op amp for a sinusoidal output current (ac) to a resistive load occurs when the peak output voltage is  $2/\pi$  times the supply voltage, given symmetrical supply voltages, as shown in  $\pm$  6:

$$P_{OPA(PEAK\_AC)} = P_{OPA}\left(\frac{2 \times V_S}{\pi}\right) = \frac{2 \times (V_S)^2}{\pi^2 \times R_I}$$

(6)

After the total power dissipation is determined, the junction temperature at the worst expected ambient temperature case must be determined by using  $\pm 7$ :

$$T_{I(MAX)} = P_{OPA} \times R_{\theta IA} + T_{A(MAX)} \tag{7}$$

#### 8.2.2.2.1 Improving Package Thermal Performance

The value of  $R_{\theta JA}$  depends on the printed circuit board (PCB) layout. An external heat sink, a cooling mechanism such as a cold air fan, or both, can help reduce  $R_{\theta JA}$ , and thus improve device thermal capabilities. See TI's design support web page at www.ti.com/thermal for general guidance on improving device thermal performance.

500

#### 8.2.3 Application Curves

The roll of characteristics and output waveform for the designed MFB filter are shown in ⊠ 8-4 and ⊠ 8-5. The attenuation is specified in 表 8-2.

表 8-2. Signal Attenuation vs Frequency

| 2ND-ORDER MFB LPF FREQUENCY<br>(kHz) | ATTENUATION<br>(dB) |  |  |  |  |

|--------------------------------------|---------------------|--|--|--|--|

| DC                                   | 9.54                |  |  |  |  |

| 10.0                                 | 9.70                |  |  |  |  |

| 15.4                                 | 6.54                |  |  |  |  |

| 19                                   | 3.54                |  |  |  |  |

| 30                                   | -4.38               |  |  |  |  |

| 320                                  | -45.9               |  |  |  |  |

### 8.3 Power Supply Recommendations

The ALM2403-Q1 is recommended for continuous operation from 5 V to 24 V (±2.5 V to ±12 V) for V<sub>S</sub>, and many specifications apply from -40°C to +125°C.

Place 0.1-µF bypass capacitors close to the power-supply pins to reduce errors coupling from noisy or highimpedance power supplies.

#### 注意

Supply voltages larger than 26 V can permanently damage the device (see セクション 6.1).

#### 8.4 Layout

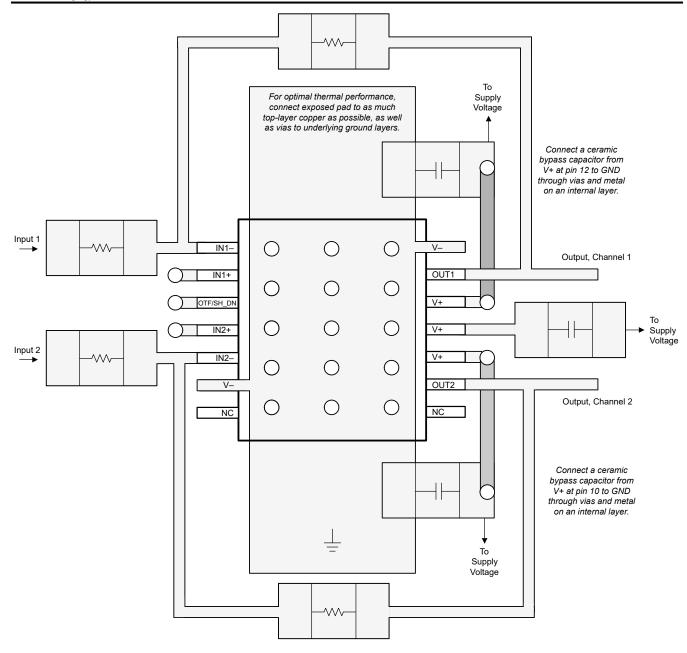

# 8.4.1 Layout Guidelines

For best operational performance of the device, use good PCB layout practices, including:

- Noise can propagate into analog circuitry through the power pins of the circuit as a whole, as well as the operational amplifier. Bypass capacitors are used to reduce the coupled noise by providing low impedance power sources local to the analog circuitry.

- Connect low-ESR, 0.1-µF ceramic bypass capacitors between each supply pin and ground, placed as close as possible to the device. A single bypass capacitor from V+ to ground is applicable for singlesupply applications.

Copyright © 2025 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

19

- Separate grounding for analog and digital portions of circuitry is one of the simplest and most-effective

methods of noise suppression. One or more layers on multilayer PCBs are usually devoted to ground planes.

A ground plane helps distribute heat and reduces EMI noise pickup. Make sure to physically separate digital

and analog grounds, paying attention to the flow of the ground current. For more detailed information, see

Circuit Board Layout Techniques.

- To reduce parasitic coupling, run the input traces as far away as possible from the supply or output traces. If keeping the traces separate is not possible, then cross the sensitive trace perpendicular, as opposed to in parallel with the noisy trace.

- Keep the length of input traces as short as possible. Always remember that the input traces are the most sensitive part of the circuit.

#### 8.4.2 Layout Example

This layout does not verify optimum thermal impedance performance. See TI's design support web page at www.ti.com/thermal for general guidance on improving device thermal performance.

図 8-6. ALM2403-Q1 Layout Example

21

# 9 Device and Documentation Support

### 9.1 Documentation Support

#### 9.1.1 Related Documentation

For related documentation see the following: ALM2403-Q1 Evaluation Module user's guide.

### 9.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、ti.com のデバイス製品フォルダを開いてください。「更新の通知を受け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

# 9.3 サポート・リソース

TI E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、該当する貢献者により、現状のまま提供されるものです。これらは TI の仕様を構成するものではなく、必ずしも TI の見解を反映したものではありません。TI の使用条件を参照してください。

#### 9.4 Trademarks

TI E2E<sup>™</sup> is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

#### 9.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

#### 9.6 用語集

テキサス・インスツルメンツ用語集 この用語集には、用語や略語の一覧および定義が記載されています。

#### 10 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

www.ti.com 9-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins    | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|-------------------|-----------------------|------|-------------------------------|----------------------------|--------------|------------------|

|                       |        |               |                   |                       |      | (4)                           | (5)                        |              |                  |

| ALM2403QPWPRQ1        | Active | Production    | HTSSOP (PWP)   14 | 2000   LARGE T&R      | Yes  | NIPDAU                        | Level-3-260C-168 HR        | -40 to 125   | A2403Q           |

| ALM2403QPWPRQ1.A      | Active | Production    | HTSSOP (PWP)   14 | 2000   LARGE T&R      | Yes  | NIPDAU                        | Level-3-260C-168 HR        | -40 to 125   | A2403Q           |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 24-Jul-2025

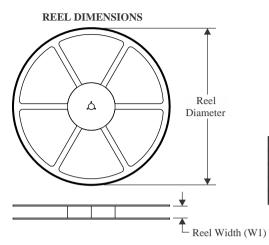

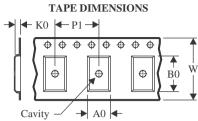

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

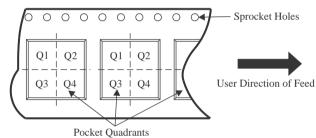

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

|   | Device         | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---|----------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| ĺ | ALM2403QPWPRQ1 | HTSSOP          | PWP                | 14 | 2000 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 24-Jul-2025

### \*All dimensions are nominal

| Г | Device         | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---|----------------|--------------|-----------------|------|------|-------------|------------|-------------|

|   | ALM2403QPWPRQ1 | HTSSOP       | PWP             | 14   | 2000 | 353.0       | 353.0      | 32.0        |

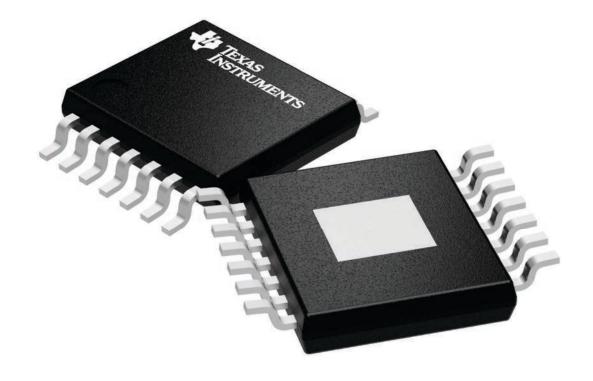

4.4 x 5.0, 0.65 mm pitch

PLASTIC SMALL OUTLINE

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

**INSTRUMENTS** www.ti.com

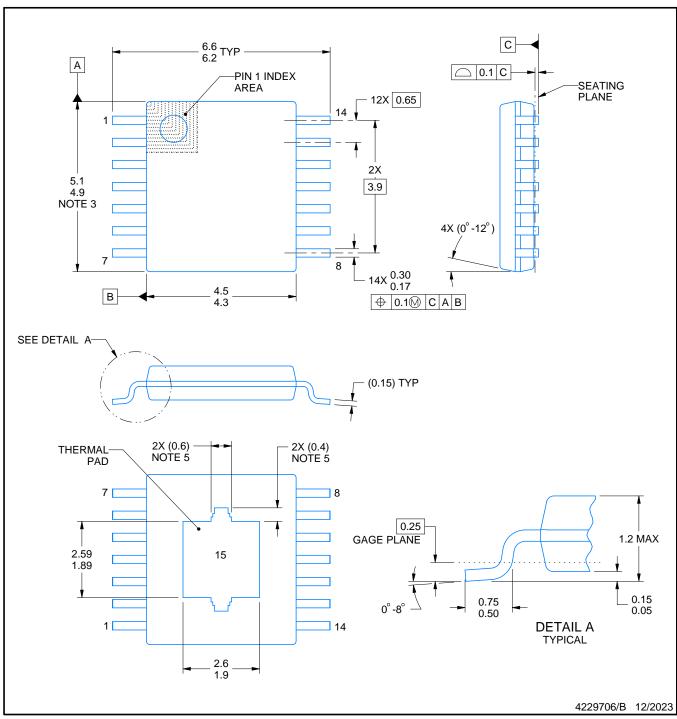

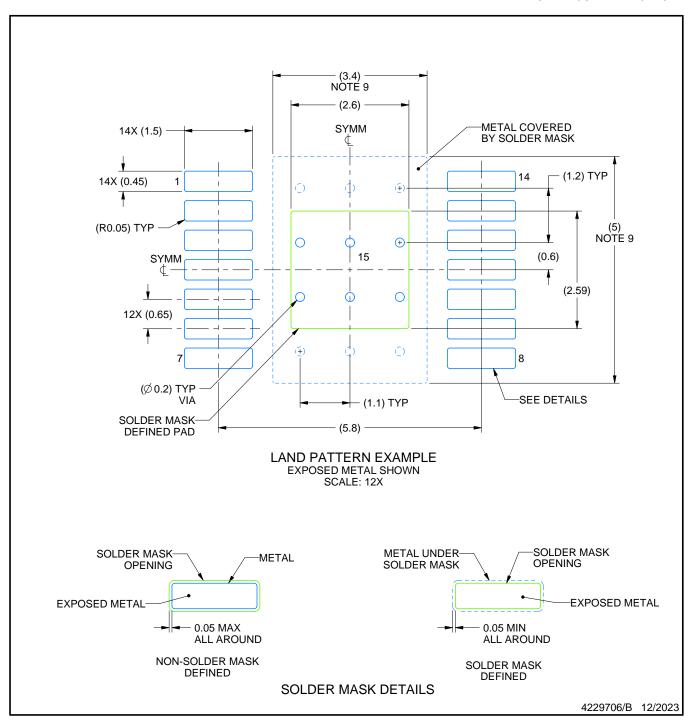

# PowerPAD<sup>™</sup> TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

#### NOTES:

PowerPAD is a trademark of Texas Instruments.

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

4. Reference JEDEC registration MO-153.

- 5. Features may differ or may not be present.

SMALL OUTLINE PACKAGE

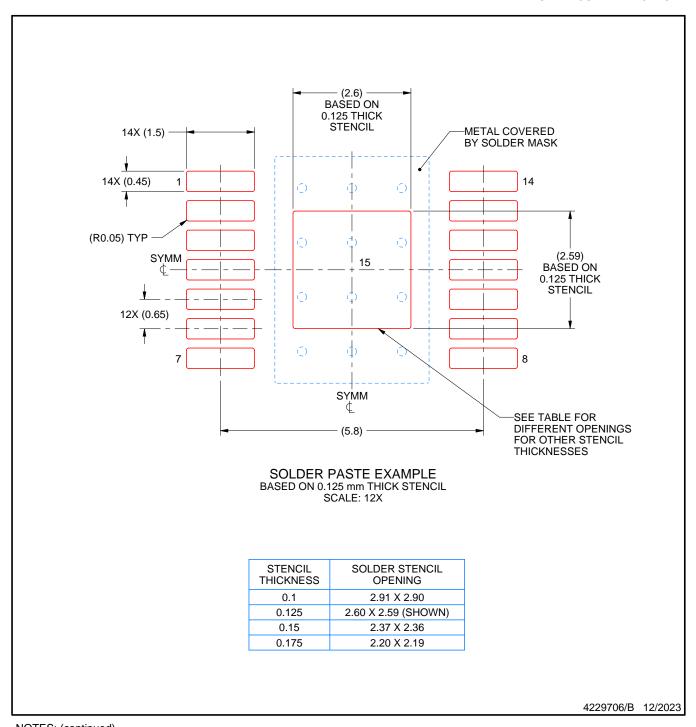

NOTES: (continued)

- 6. Publication IPC-7351 may have alternate designs.

- 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

- 8. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature numbers SLMA002 (www.ti.com/lit/slma002) and SLMA004 (www.ti.com/lit/slma004).

- 9. Size of metal pad may vary due to creepage requirement.

- 10. Vias are optional depending on application, refer to device data sheet. It is recommended that vias under paste be filled, plugged or tented.

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 11. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 12. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TIの製品は、TIの販売条件、TIの総合的な品質ガイドライン、 ti.com または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。 TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日: 2025 年 10 月