# AMC0106M05 高精度、 $\pm 50\text{mV}$ 入力、機能絶縁、外部クロックによるデルタ シグマ変調器

## 1 特長

- リニア入力電圧範囲: $\pm 50\text{mV}$

- 電源電圧範囲:

- ハイサイド (AVDD): 3.0V ~ 5.5V

- ローサイド (DVDD): 2.7V ~ 5.5V

- 小さい DC 誤差:

- オフセット誤差: $\pm 200\mu\text{V}$  (最大値)

- オフセットドリフト: $\pm 1.2\mu\text{V}/^\circ\text{C}$  (最大値)

- ゲイン誤差: $\pm 0.3\%$  (最大値)

- ゲインドリフト: $\pm 50\text{ppm}/^\circ\text{C}$  (最大値)

- 高 CMTI: 150V/ns (最小値)

- ハイサイド電源喪失の検出

- 低 EMI:CISPR-11 および CISPR-25 規格に準拠

- 機能的分離:

- 200V<sub>RMS</sub>、280V<sub>DC</sub> の動作電圧

- 570V<sub>RMS</sub>、800V<sub>DC</sub> の過渡の過電圧 (60 秒)

- 拡張産業用温度範囲にわたって仕様を完全に規定 – 40°C ~ +125°C

## 2 アプリケーション

- 48V モータードライブ

- 48V 周波数インバータ

- アナログ入力モジュール

- 電源

## 3 説明

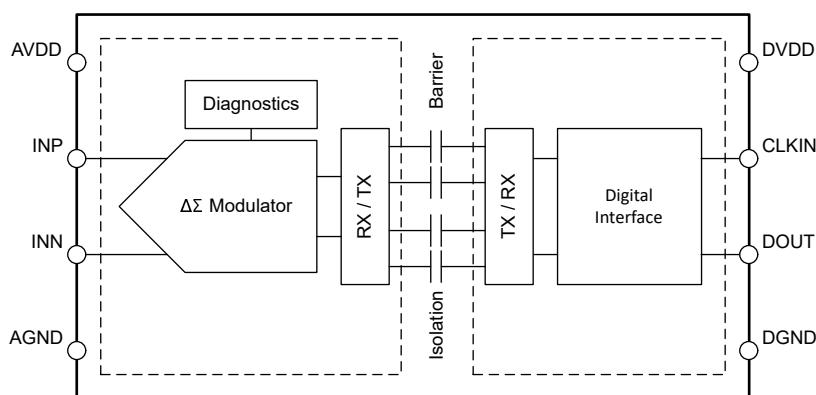

AMC0106M05 は、 $\pm 50\text{mV}$  の入力電圧範囲を持つ高精度の機能絶縁デルタシグマ変調器です。この絶縁バリアは、異なる同相電圧レベルで動作するシステム領域を分離します。この絶縁バリアは、最高 200V<sub>RMS</sub> または 280V<sub>DC</sub> の動作電圧と、最高 570V<sub>RMS</sub> または 800V<sub>DC</sub> の過渡電圧に対応しています。

AMC0106M05 は、小さいパッケージサイズと低い入力電圧範囲を備え、スペースに制約のあるアプリケーションでの高精度絶縁型電流センシングを実現するように設計されています。ガルバニック絶縁バリアは高い同相過渡に対応し、感受性の高い制御回路を電力段のスイッチングノイズから絶縁できます。

AMC0106M05 の出力ビットストリームは、外部クロックと同期します。このデバイスは、sinc<sup>3</sup> や OSR 256 フィルタと組み合わせることにより、16 ビットの分解能、84dB のダイナミックレンジ、78kSPS のデータレートを実現します。

AMC0106M05 は 8 ピン、0.65mm ピッチの VSON パッケージで供給され、-40°C ~ +125°C の拡張産業用温度範囲で動作が規定されています。

### パッケージ情報

| 部品番号       | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|------------|----------------------|--------------------------|

| AMC0106M05 | DEN (VSON、8)         | 3.5mm × 2.7mm            |

(1) 詳細については、「メカニカル、パッケージ、および注文情報」をご参照ください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピントを含みます。

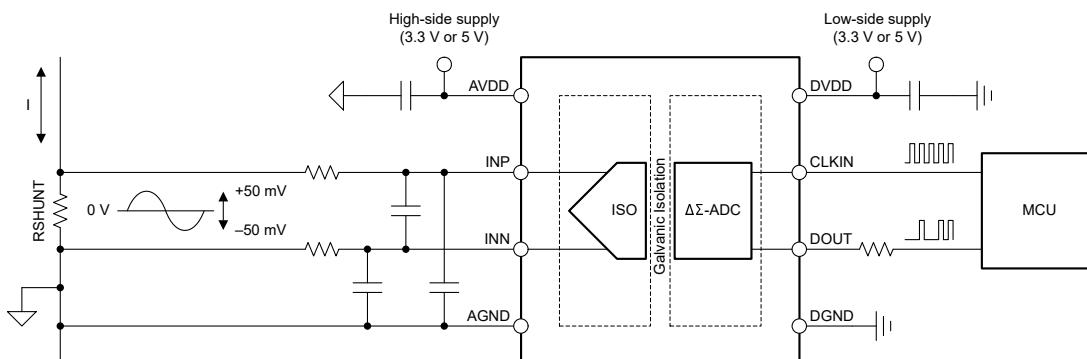

代表的なアプリケーション

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                              |           |                                     |           |

|------------------------------|-----------|-------------------------------------|-----------|

| <b>1 特長</b> .....            | <b>1</b>  | 6.3 機能説明.....                       | <b>17</b> |

| <b>2 アプリケーション</b> .....      | <b>1</b>  | 6.4 デバイスの機能モード.....                 | <b>21</b> |

| <b>3 説明</b> .....            | <b>1</b>  | <b>7 アプリケーションと実装</b> .....          | <b>22</b> |

| <b>4 ピン構成および機能</b> .....     | <b>3</b>  | 7.1 アプリケーション情報.....                 | <b>22</b> |

| <b>5 仕様</b> .....            | <b>4</b>  | 7.2 代表的なアプリケーション.....               | <b>22</b> |

| 5.1 絶対最大定格 .....             | 4         | 7.3 設計のベスト プラクティス.....              | <b>26</b> |

| 5.2 ESD 定格.....              | 4         | 7.4 電源に関する推奨事項.....                 | <b>27</b> |

| 5.3 推奨動作条件 - .....           | 5         | 7.5 レイアウト.....                      | <b>27</b> |

| 5.4 熱に関する情報 (DEN パッケージ)..... | 6         | <b>8 デバイスおよびドキュメントのサポート</b> .....   | <b>28</b> |

| 5.5 パッケージ特性 .....            | 6         | 8.1 ドキュメントのサポート.....                | <b>28</b> |

| 5.6 電気的特性 .....              | 7         | 8.2 ドキュメントの更新通知を受け取る方法.....         | <b>28</b> |

| 5.7 スイッチング特性 .....           | 9         | 8.3 サポート・リソース.....                  | <b>28</b> |

| 5.8 タイミング図.....              | 9         | 8.4 商標.....                         | <b>28</b> |

| 5.9 代表的特性 .....              | 10        | 8.5 静電気放電に関する注意事項.....              | <b>28</b> |

| <b>6 詳細説明</b> .....          | <b>16</b> | 8.6 用語集.....                        | <b>28</b> |

| 6.1 概要.....                  | 16        | <b>9 改訂履歴</b> .....                 | <b>28</b> |

| 6.2 機能ブロック図.....             | 16        | <b>10 メカニカル、パッケージ、および注文情報</b> ..... | <b>29</b> |

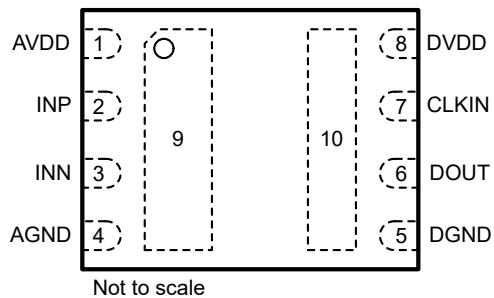

## 4 ピン構成および機能

図 4-1. DEN パッケージ、8 ピン VSON (上面図)

表 4-1. ピンの機能

| ピン                  |       | タイプ         | 説明                                             |

|---------------------|-------|-------------|------------------------------------------------|

| 番号                  | 名称    |             |                                                |

| 1                   | AVDD  | ハイサイド電源     | アナログ (ハイサイド) 電源。 <sup>(1)</sup>                |

| 2                   | INP   | アナログ入力      | 非反転アナログ入力。10nF のフィルタコンデンサを INP と INN の間に接続します。 |

| 3                   | INN   | アナログ入力      | 反転アナログ入力。10nF のフィルタコンデンサを INP と INN の間に接続します。  |

| 4、9 <sup>(2)</sup>  | AGND  | ハイサイド グラウンド | アナログ (ハイサイド) グラウンド。                            |

| 5、10 <sup>(2)</sup> | DGND  | ローサイド グラウンド | デジタル (ローサイド) グラウンド。                            |

| 6                   | DOUT  | デジタル出力      | 変調器のデータ出力。                                     |

| 7                   | CLKIN | デジタル入力      | 内部プルダウン抵抗付きの変調器クロック入力 (標準値: 1.5MΩ)。            |

| 8                   | DVDD  | ローサイド電源     | デジタル (ローサイド) 電源。 <sup>(1)</sup>                |

(1) 電源のデカップリングに関する推奨事項については、「[電源に関する推奨事項](#)」セクションを参照してください。

(2) どちらのピンも低インピーダンスバスを介して内部接続されています。

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|                       |                              | 最小値        | 最大値        | 単位               |

|-----------------------|------------------------------|------------|------------|------------------|

| 電源電圧                  | ハイサイド AVDD から AGND への接続      | -0.3       | 6.5        | V                |

|                       | ローサイド DVDD から DGND への接続      | -0.3       | 6.5        |                  |

| アナログ入力電圧              | INP、INN から AGND へ、           | AGND - 4   | AVDD + 0.5 | V                |

| デジタル入力電圧              | CLKIN から DGND へ              | DGND - 0.5 | DVDD+ 0.5  | V                |

| デジタル出力電圧              | DOUT から DGND へ               | DGND - 0.5 | DVDD + 0.5 | V                |

| 過渡絶縁電圧 <sup>(2)</sup> | AC 電圧、t = 60s <sup>(3)</sup> |            | 570        | V <sub>RMS</sub> |

|                       | DC 電圧、t = 60s <sup>(3)</sup> |            | 800        | V <sub>DC</sub>  |

| 入力電流                  | 連続、電源ピンを除く任意のピン              | -10        | 10         | mA               |

| 温度                    | 接合部、T <sub>J</sub>           |            | 150        | °C               |

|                       | 保存、T <sub>stg</sub>          | -65        | 150        |                  |

- (1) 絶対最大定格を超えた動作は、デバイスに恒久的な損傷を与える可能性があります。絶対最大定格は、これらの条件において、または推奨動作条件に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

- (2) パッケージの左側 (ピン 1 から 4 まで) から右側 (ピン 5 から 8 まで) への同相モード。

- (3) 累積。

### 5.2 ESD 定格

|                    |      |                                                                                                                  | 値     | 単位 |

|--------------------|------|------------------------------------------------------------------------------------------------------------------|-------|----|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup><br>デバイス帶電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 準拠 <sup>(2)</sup> | ±2000 | V  |

- (1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

- (2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

## 5.3 推奨動作条件 -

動作時周辺温度範囲内 (特に記述のない限り)

|                 |                           |                                     | 最小値      | 公称値  | 最大値       | 単位  |

|-----------------|---------------------------|-------------------------------------|----------|------|-----------|-----|

| <b>電源</b>       |                           |                                     |          |      |           |     |

| AVDD            | ハイサイド電源                   | AVDD から AGND へ                      | 3        | 5.0  | 5.5       | V   |

| DVDD            | ローサイド電源                   | DVDD から DGND へ                      | 2.7      | 3.3  | 5.5       | V   |

| <b>アナログ入力</b>   |                           |                                     |          |      |           |     |

| $V_{Clipping}$  | 出力クリッピング前の差動入力電圧          | $V_{IN} = V_{INP} - V_{INN}$        | $\pm 64$ |      | mV        |     |

| $V_{FSR}$       | 線形差動入力電圧を規定               | $V_{IN} = V_{INP} - V_{INN}$        | -50      | 50   |           | mV  |

| $V_{CM}$        | 動作時同相入力電圧                 | $(V_{INP} + V_{INN}) / 2 \sim AGND$ | -0.032   | 1    |           | V   |

| $C_{IN, EXT}$   | 入力に接続された最小外部容量            | INP から INN へ                        | 10       |      | nF        |     |

| <b>デジタル I/O</b> |                           |                                     |          |      |           |     |

| $V_{IO}$        | デジタル入出力電圧                 | 0                                   |          | DVDD | V         |     |

| $f_{CLKIN}$     | 入力クロック周波数                 | 5                                   |          | 20   | 21        | MHz |

| $t_{HIGH}$      | 入力クロック high 時間            | 21.5                                |          | 25   | 110       | ns  |

| $t_{LOW}$       | 入力クロック low 時間             | 21.5                                |          | 25   | 110       | ns  |

| <b>絶縁バリア</b>    |                           |                                     |          |      |           |     |

| $V_{IOWM}$      | 機能的絶縁の動作電圧 <sup>(1)</sup> | AC 電圧 (正弦波)                         | 200      |      | $V_{RMS}$ |     |

|                 |                           | DC 電圧                               | 280      |      | $V_{DC}$  |     |

| <b>温度範囲</b>     |                           |                                     |          |      |           |     |

| $T_A$           | 規定周囲温度                    | -40                                 |          | 125  | °C        |     |

(1) パッケージの左側 (ピン 1 から 4 まで) から右側 (ピン 5 から 8 まで) への同相モード。

## 5.4 热に関する情報 (DEN パッケージ)

| 热評価基準 <sup>(1)</sup>  |                     | DEN (VSON) | 単位   |

|-----------------------|---------------------|------------|------|

|                       |                     | 8 ピン       |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗        | 64.7       | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース (上面) への熱抵抗 | 53.7       | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗        | 29.6       | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ    | 10.1       | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ    | 29.4       | °C/W |

| R <sub>θJC(bot)</sub> | 接合部からケース (底面) への熱抵抗 | 23.4       | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション ノートを参照してください。

## 5.5 パッケージ特性

| パラメータ            | テスト条件                     | 値                                             | 単位                   |

|------------------|---------------------------|-----------------------------------------------|----------------------|

| <b>DEN パッケージ</b> |                           |                                               |                      |

| CLR              | 外部空間距離                    | 空気中での最短のピン間距離                                 | ≥ 1 mm               |

| CPG              | 外部沿面距離                    | パッケージ表面に沿った最短のピン間距離                           | ≥ 1 mm               |

| CTI              | 比較トラッキング インデックス           | DIN EN 60112 (VDE 0303-11)、IEC 60112          | ≥ 600 V              |

|                  | 材料グループ                    | IEC 60664-1 に準拠                               | I                    |

| C <sub>IO</sub>  | 容量、入力から出力へ <sup>(1)</sup> | V <sub>IO</sub> = 0.5V <sub>PP</sub> (1MHz 時) | ≈ 1.5 pF             |

| R <sub>IO</sub>  | 抵抗、入力から出力へ <sup>(1)</sup> | T <sub>A</sub> = 25°C                         | > 10 <sup>12</sup> Ω |

(1) バリアのそれぞれの側にあるすべてのピンは互いに接続され、実質的に 2 ピンのデバイスになります。

## 5.6 電気的特性

最小値と最大値の仕様は、 $T_A = -40^\circ\text{C} \sim 125^\circ\text{C}$ 、AVDD = 3.0V ~ 5.5V、DVDD = 2.7V ~ 5.5V、 $V_{\text{INP}} = -50\text{mV} \sim 50\text{mV}$ 、 $V_{\text{INN}} = 0\text{V}$ 、sinc<sup>3</sup> フィルタ (OSR = 256) での値です (特に記述のない限り)。標準値の仕様は、 $T_A = 25^\circ\text{C}$ 、CLKIN = 20MHz (50% のデューティサイクル)、AVDD = 5V、DVDD = 3.3V での値です。

| パラメータ                                |                    | テスト条件                                                                                                                                       | 最小値        | 標準値        | 最大値  | 単位     |

|--------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|------|--------|

| <b>アナログ入力</b>                        |                    |                                                                                                                                             |            |            |      |        |

| $C_{\text{IN}}$                      | 実効入力サンプリング容量       |                                                                                                                                             | 8          |            |      | pF     |

| $R_{\text{IN}}$                      | 入力インピーダンス          | $f_{\text{CLK}} = 10\text{MHz}$                                                                                                             | 10.5       | 12.5       | 14.5 | kΩ     |

|                                      |                    | $f_{\text{CLK}} = 20\text{MHz}$                                                                                                             | 5.3        | 6.3        | 7.3  |        |

| $I_{\text{INP}}$                     | 入力電流               | $V_{\text{IN}} = (V_{\text{INP}} - V_{\text{INN}}) = V_{\text{FSR, MAX}}$ ,<br>$f_{\text{CLK}} = 10\text{MHz}$                              | 4          |            |      | μA     |

|                                      |                    | $V_{\text{IN}} = (V_{\text{INP}} - V_{\text{INN}}) = V_{\text{FSR, MAX}}$ ,<br>$f_{\text{CLK}} = 20\text{MHz}$                              | 8          |            |      |        |

| $I_{\text{INN}}$                     | 入力電流               | $V_{\text{IN}} = (V_{\text{INP}} - V_{\text{INN}}) = V_{\text{FSR, MAX}}$ ,<br>$f_{\text{CLK}} = 10\text{MHz}$                              | -4         |            |      | μA     |

|                                      |                    | $V_{\text{IN}} = (V_{\text{INP}} - V_{\text{INN}}) = V_{\text{FSR, MAX}}$ ,<br>$f_{\text{CLK}} = 20\text{MHz}$                              | -8         |            |      |        |

| CMTI                                 | 同相電圧過渡耐性           |                                                                                                                                             | 150        |            |      | kV/μs  |

| <b>DC 精度</b>                         |                    |                                                                                                                                             |            |            |      |        |

| $E_O$                                | オフセット誤差            | $\text{INP} = \text{INN} = \text{AGND}, T_A = 25^\circ\text{C}$                                                                             | -200       | 10         | 200  | μV     |

| TCE <sub>O</sub>                     | オフセット誤差の温度ドリフト (3) |                                                                                                                                             | -1.2       |            | 1.2  | μV/°C  |

| $E_G$                                | ゲイン誤差 (1)          | $T_A = 25^\circ\text{C}$                                                                                                                    | -0.3%      | ±0.04%     | 0.3% |        |

| TCE <sub>G</sub>                     | ゲイン誤差の温度ドリフト (4)   |                                                                                                                                             | -50        | ±20        | 50   | ppm/°C |

| INL                                  | 積分非直線性 (2)         | 分解能: 16 ビット                                                                                                                                 | -6         | ±1         | 6    | LSB    |

| DNL                                  | 微分非直線性             | 分解能: 16 ビット                                                                                                                                 | -0.99      |            | 0.99 | LSB    |

| CMRR                                 | 同相信号除去比            | $\text{INP} = \text{INN}, f_{\text{IN}} = 0\text{Hz},$<br>$V_{\text{CM min}} \leq V_{\text{IN}} \leq V_{\text{CM max}}$                     | -99        |            |      | dB     |

|                                      |                    | $\text{INP} = \text{INN}, f_{\text{IN}} = 0.1\text{Hz} \sim 10\text{kHz},$<br>$V_{\text{CM min}} \leq V_{\text{IN}} \leq V_{\text{CM max}}$ | -100       |            |      |        |

| PSRR                                 | 電源除去比              | $\text{AVDD DC PSRR}, \text{INP} = \text{INN} = \text{AGND},$<br>$\text{AVDD} = 3.0\text{V} \sim 5.5\text{V}$                               | -100       |            |      | dB     |

|                                      |                    | $\text{AVDD AC PSRR}, \text{INP} = \text{INN} = \text{AGND},$<br>$\text{AVDD} \pm 10\text{kHz} / 100\text{mV}$ のリップル                        | -100       |            |      |        |

| <b>AC 精度</b>                         |                    |                                                                                                                                             |            |            |      |        |

| SNR                                  | 信号対雑音比             | $f_{\text{IN}} = 1\text{kHz}$                                                                                                               | 84         |            |      | dB     |

| SINAD                                | 信号対雑音 + 歪み比        | $f_{\text{IN}} = 1\text{kHz}$                                                                                                               | 84         |            |      | dB     |

| THD                                  | 全高調波歪み (5)         | $3.0\text{V} \leq \text{AVDD} \leq 5.5\text{V}, f_{\text{IN}} = 1\text{kHz},$<br>$5\text{MHz} \leq f_{\text{CLKIN}} \leq 21\text{MHz}$      | -103       |            |      | dB     |

| <b>デジタル入力 (シェミットトリガ付き CMOS ロジック)</b> |                    |                                                                                                                                             |            |            |      |        |

| $I_{\text{IN}}$                      | 入力電流               | $\text{DGND} \leq V_{\text{IN}} \leq \text{DVDD}$                                                                                           | 0          | 7          |      | μA     |

| $C_{\text{IN}}$                      | 入力容量               |                                                                                                                                             | 4          |            |      | pF     |

| $V_{\text{IH}}$                      | High レベル入力電圧       |                                                                                                                                             | 0.7 × DVDD | + 0.3      |      | V      |

| $V_{\text{IL}}$                      | Low レベル入力電圧        |                                                                                                                                             | -0.3       | 0.3 × DVDD |      | V      |

| <b>デジタル出力 (CMOS)</b>                 |                    |                                                                                                                                             |            |            |      |        |

| $C_{\text{LOAD}}$                    | 出力負荷容量             |                                                                                                                                             | 15         | 30         |      | pF     |

| $V_{\text{OH}}$                      | High レベル出力電圧       | $I_{\text{OH}} = -4\text{mA}$                                                                                                               | DVDD - 0.4 |            |      | V      |

## 5.6 電気的特性 (続き)

最小値と最大値の仕様は、 $T_A = -40^\circ\text{C} \sim 125^\circ\text{C}$ 、 $\text{AVDD} = 3.0\text{V} \sim 5.5\text{V}$ 、 $\text{DVDD} = 2.7\text{V} \sim 5.5\text{V}$ 、 $V_{\text{INP}} = -50\text{mV} \sim 50\text{mV}$ 、 $V_{\text{INN}} = 0\text{V}$ 、 $\text{sinc}^3$  フィルタ ( $\text{OSR} = 256$ ) での値です (特に記述のない限り)。標準値の仕様は、 $T_A = 25^\circ\text{C}$ 、 $\text{CLKIN} = 20\text{MHz}$  (50% のデューティサイクル)、 $\text{AVDD} = 5\text{V}$ 、 $\text{DVDD} = 3.3\text{V}$  での値です。

| パラメータ                     |                    | テスト条件                           | 最小値 | 標準値  | 最大値 | 単位 |

|---------------------------|--------------------|---------------------------------|-----|------|-----|----|

| $V_{\text{OL}}$           | Low レベル出力電圧        | $I_{\text{OL}} = 4\text{mA}$    |     |      | 0.4 | V  |

| <b>電源</b>                 |                    |                                 |     |      |     |    |

| $I_{\text{AVDD}}$         | ハイサイド電源電流          |                                 | 6.2 | 8.0  | mA  |    |

| $I_{\text{DVDD}}$         | ローサイド電源電流          | $C_{\text{LOAD}} = 15\text{pF}$ | 4.5 | 7.0  | mA  |    |

| $\text{AVDD}_{\text{UV}}$ | ハイサイド低電圧検出スレッショルド  | AVDD 立ち上がり                      | 2.4 | 2.6  | 2.8 | V  |

|                           |                    | AVDD 立ち下がり                      | 1.9 | 2.05 | 2.2 |    |

| $\text{DVDD}_{\text{UV}}$ | ローサイドの低電圧検出スレッショルド | DVDD 立ち上がり                      | 2.3 | 2.5  | 2.7 | V  |

|                           |                    | DVDD 立ち下がり                      | 1.9 | 2.05 | 2.2 |    |

- (1) このパラメータは入力換算です。

- (2) 積分非線形性は、LSB の数、または指定された線形性を有する入力電圧範囲 FSR のパーセンテージとして表される、理想的な ADC 伝達関数の終点を通過する直線からの、最大偏移と定義されます。

- (3) オフセット誤差温度ドリフトは、次の式で説明されるボックス法を使用して計算されます。

$$TCE_O = (E_{O,\text{MAX}} - E_{O,\text{MIN}}) / \text{TempRange}$$

, ここで、 $E_{O,\text{MAX}}$  および  $E_{O,\text{MIN}}$  は、温度範囲 (-40 ~ 125°C) で測定された最大および最小の  $E_O$  値を指します。

- (4) ゲイン誤差の温度ドリフトは、次の式で記述されるボックス法を使用して計算されます。

$$TCE_G (\text{ppm}) = ((E_{G,\text{MAX}} - E_{G,\text{MIN}}) / \text{TempRange}) \times 10^4$$

, ここで、 $E_{G,\text{MAX}}$  および  $E_{G,\text{MIN}}$  は、温度範囲 (-40 ~ 125°C) で測定された最大および最小  $E_G$  値 (%) を表します。

- (5) THD は、最初の 5 つより高い高調波の振幅の rms 合計と、基本波の振幅との比です。

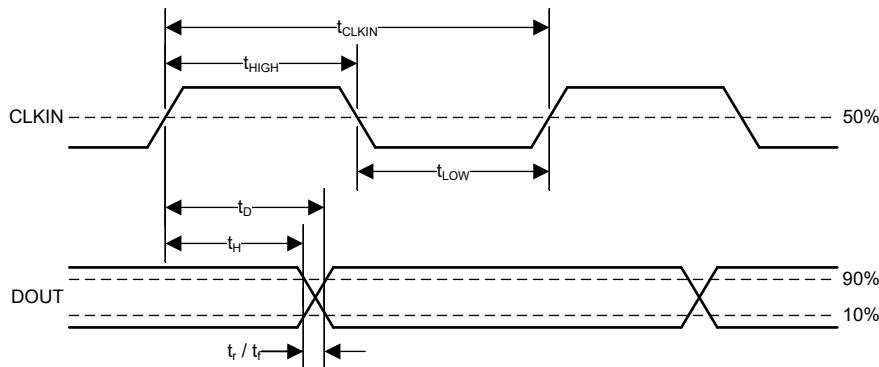

## 5.7 スイッチング特性

| パラメータ       |                                | テスト条件                                                                              | 最小値 | 標準値 | 最大値 | 単位            |

|-------------|--------------------------------|------------------------------------------------------------------------------------|-----|-----|-----|---------------|

| $t_H$       | CLKIN 立ち上がりエッジ後の DOUT ホールド時間   | $C_{LOAD} = 15\text{pF}$                                                           | 12  |     |     | ns            |

| $t_D$       | CLKIN の立ち上がりエッジから DOUT 有効までの遅延 | $C_{LOAD} = 15\text{pF}$                                                           |     | 30  |     | ns            |

| $t_r$       | DOUT の立ち上がり時間                  | 10% ~ 90%、 $2.7\text{V} \leq DVDD \leq 3.6\text{V}$ 、 $C_{LOAD} = 15\text{pF}$     | 2.5 | 6   |     | ns            |

|             |                                | 10% ~ 90%、 $4.5\text{V} \leq DVDD \leq 5.5\text{V}$ 、 $C_{LOAD} = 15\text{pF}$     | 3.2 | 6   |     |               |

| $t_f$       | DOUT の立ち下がり時間                  | 10% ~ 90%、 $2.7\text{V} \leq DVDD \leq 3.6\text{V}$ 、 $C_{LOAD} = 15\text{pF}$     | 2.2 | 6   |     | ns            |

|             |                                | 10% ~ 90%、 $4.5\text{V} \leq DVDD \leq 5.5\text{V}$ 、 $C_{LOAD} = 15\text{pF}$     | 2.9 | 6   |     |               |

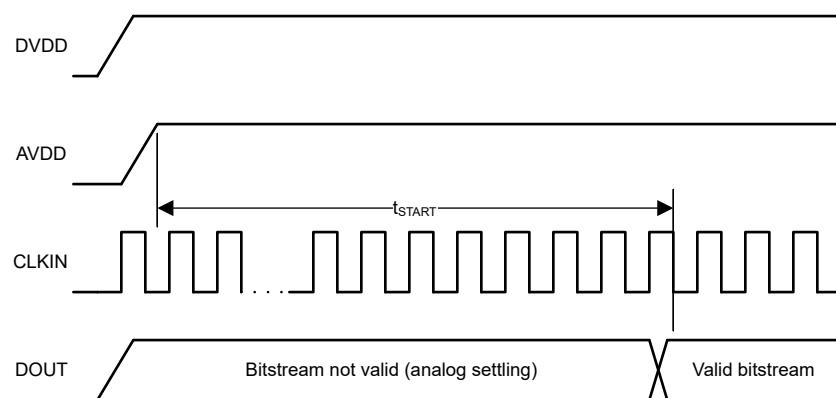

| $t_{START}$ | デバイスの起動時間                      | AVDD $\geq 2.7\text{V}$ からビットストリームが有効、0.1% セリングで、AVDD が 0 から $3.0\text{V}$ までのステップ | 100 |     |     | $\mu\text{s}$ |

## 5.8 タイミング図

図 5-1. デジタルインターフェイスのタイミング

図 5-2. デバイスの起動時間

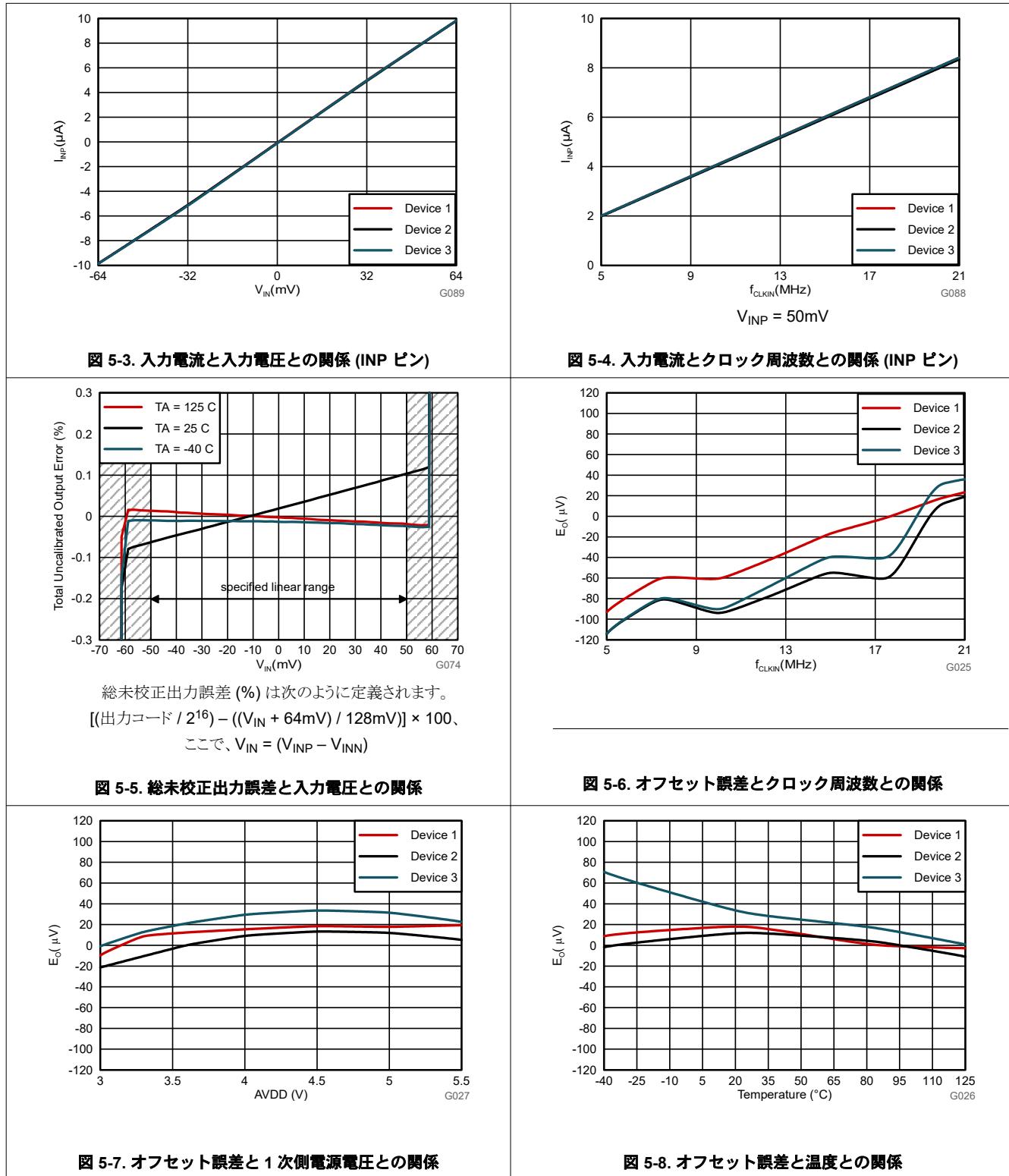

## 5.9 代表的特性

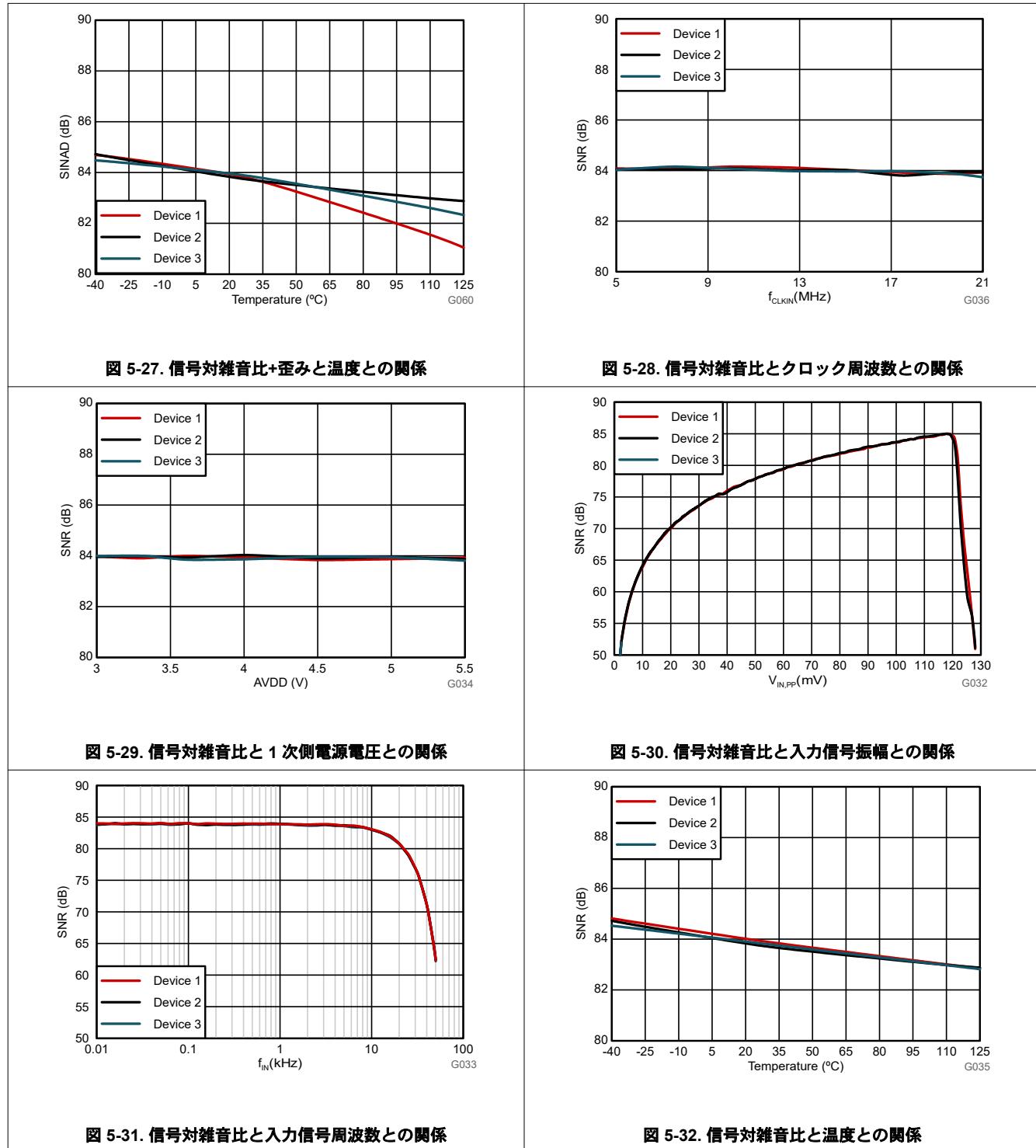

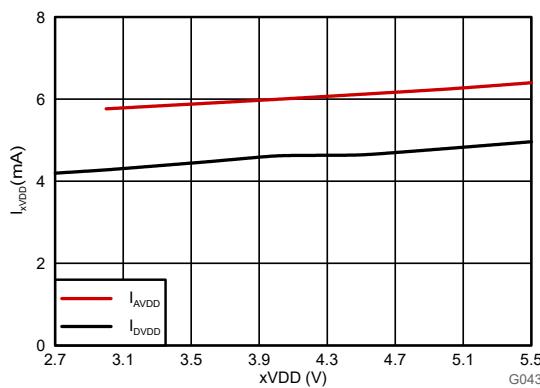

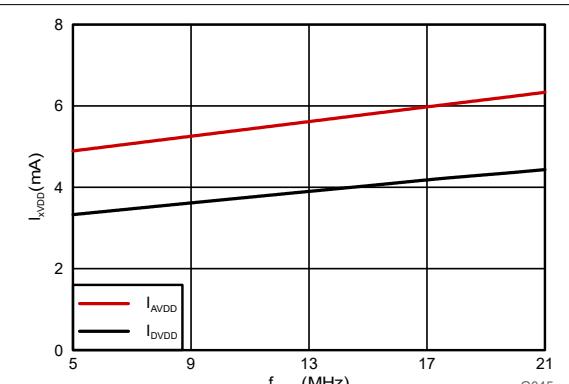

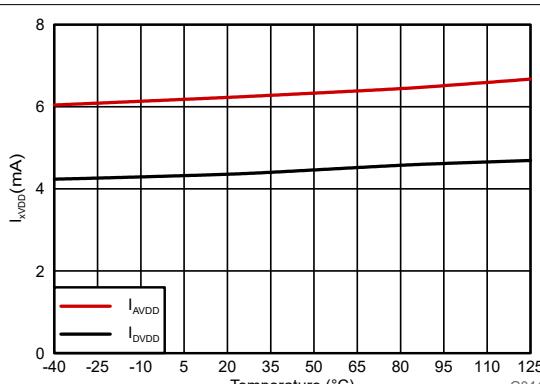

AVDD = 5V、DVDD = 3.3V、VINP = -50mV ~ +50mV、INN = AGND、fCLKIN = 20MHz (50% のデューティ サイクル)、sinc<sup>3</sup> フィルタ (OSR = 256) での特性評価 (特に記述のない限り)。

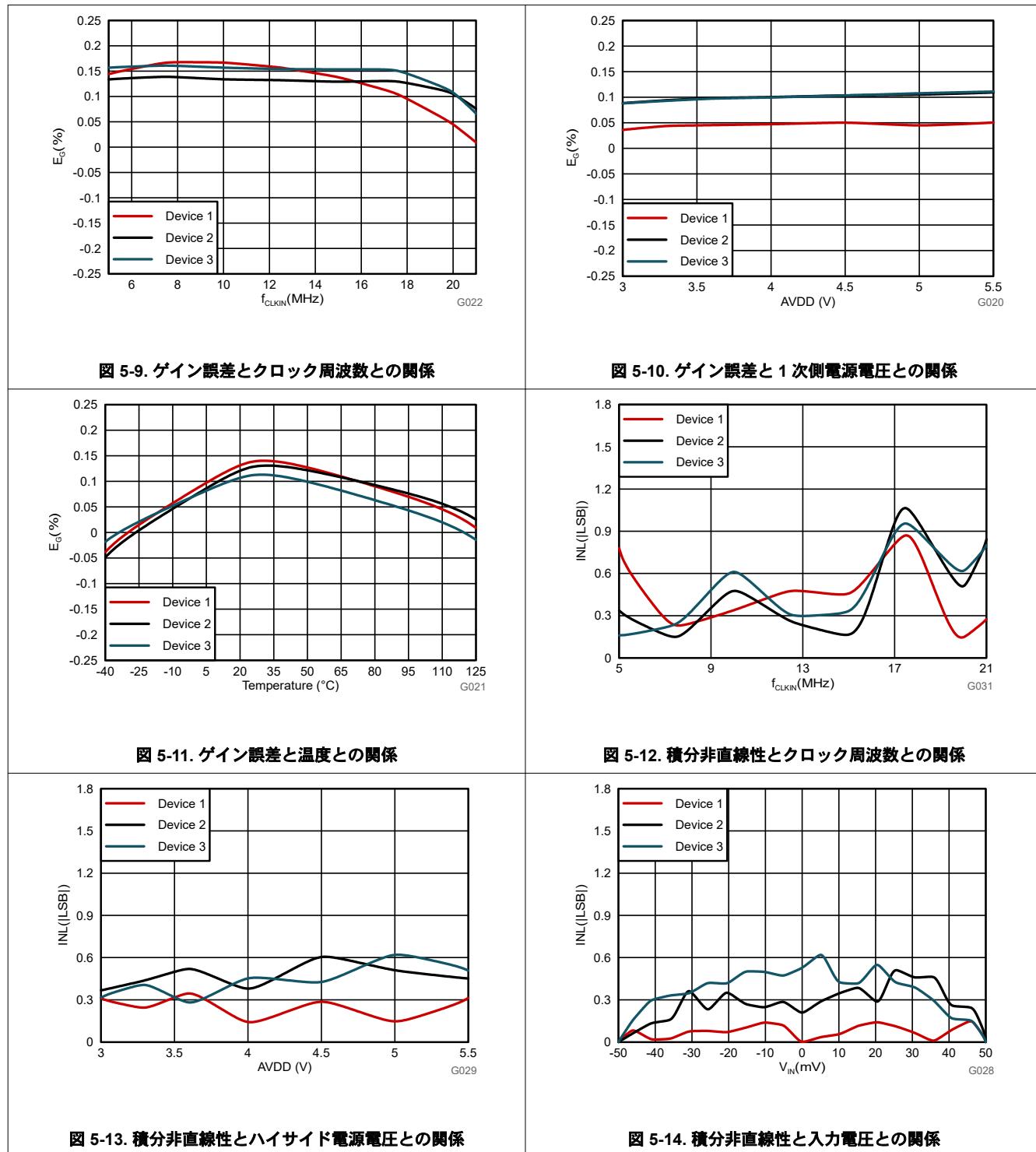

## 5.9 代表的特性 (続き)

AVDD = 5V、DVDD = 3.3V、 $V_{INP} = -50mV \sim +50mV$ 、INN = AGND、 $f_{CLKIN} = 20MHz$  (50% のデューティ サイクル)、sinc<sup>3</sup> フィルタ (OSR = 256) での特性評価 (特に記述のない限り)。

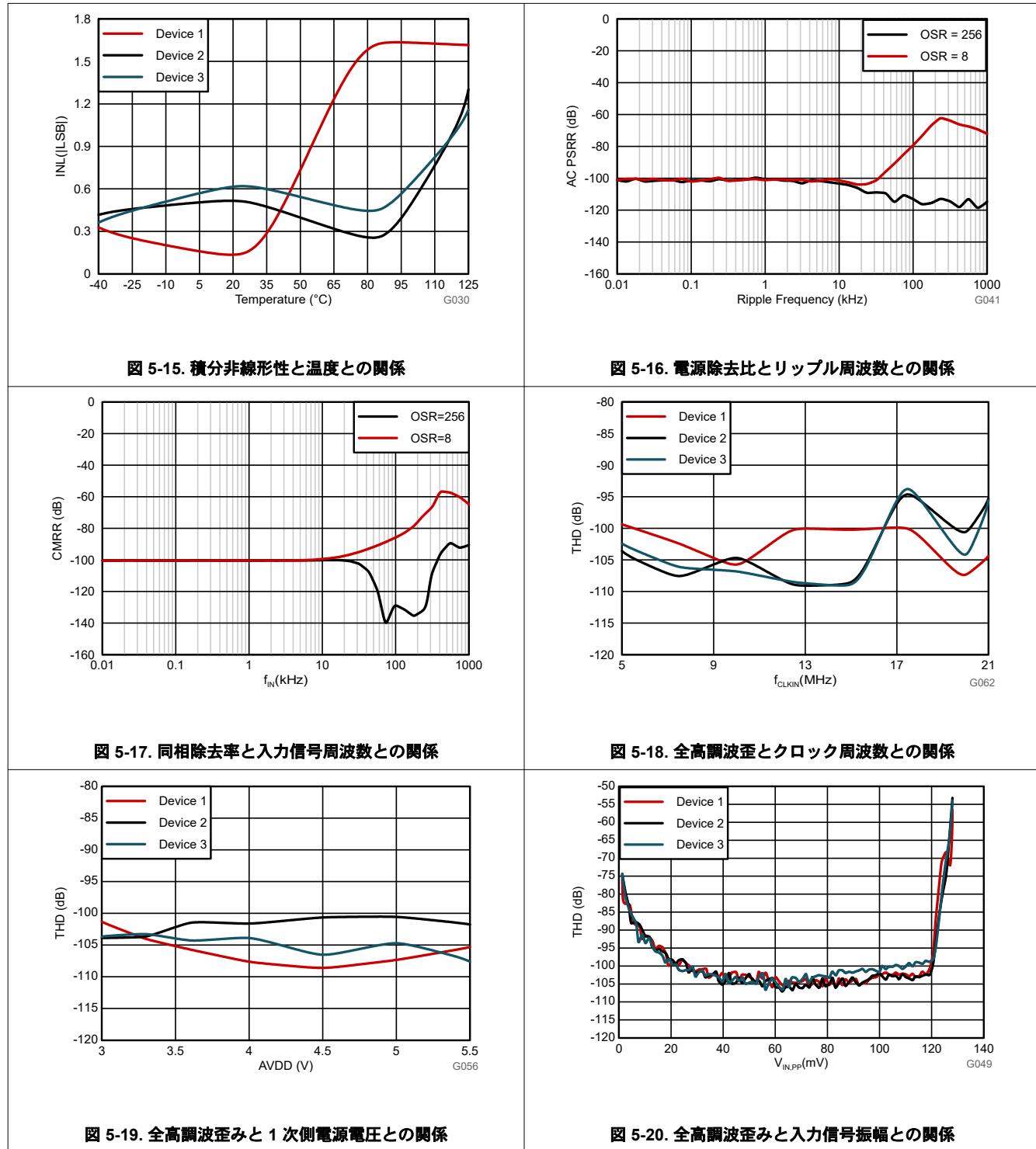

## 5.9 代表的特性 (続き)

AVDD = 5V、DVDD = 3.3V、 $V_{INP} = -50mV \sim +50mV$ 、INN = AGND、 $f_{CLKIN} = 20MHz$  (50% のデューティ サイクル)、sinc<sup>3</sup> フィルタ (OSR = 256) での特性評価 (特に記述のない限り)。

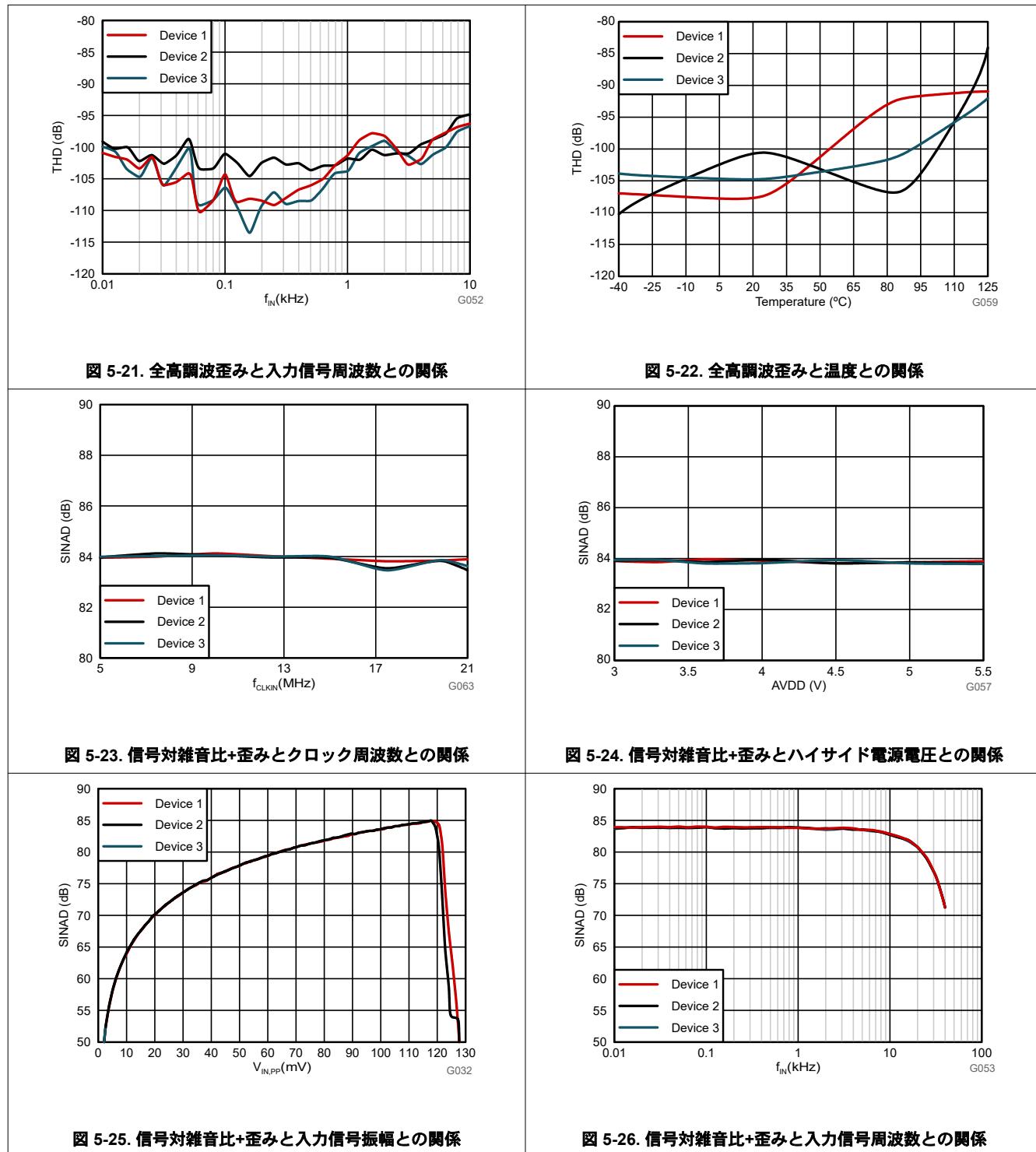

## 5.9 代表的特性 (続き)

AVDD = 5V、DVDD = 3.3V、 $V_{INP} = -50\text{mV} \sim +50\text{mV}$ 、INN = AGND、 $f_{CLKIN} = 20\text{MHz}$  (50% のデューティ サイクル)、sinc<sup>3</sup> フィルタ (OSR = 256) での特性評価 (特に記述のない限り)。

## 5.9 代表的特性 (続き)

AVDD = 5V、DVDD = 3.3V、 $V_{INP} = -50mV \sim +50mV$ 、INN = AGND、 $f_{CLKIN} = 20MHz$  (50% のデューティ サイクル)、sinc<sup>3</sup> フィルタ (OSR = 256) での特性評価 (特に記述のない限り)。

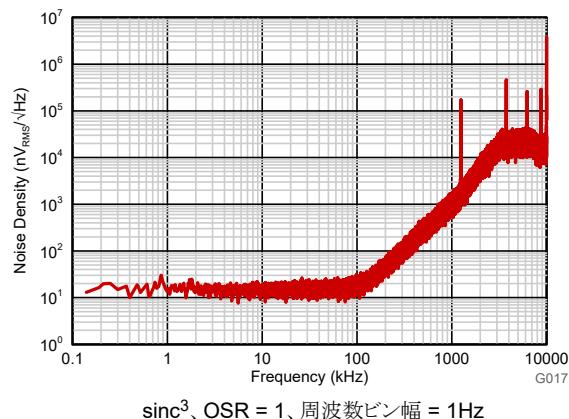

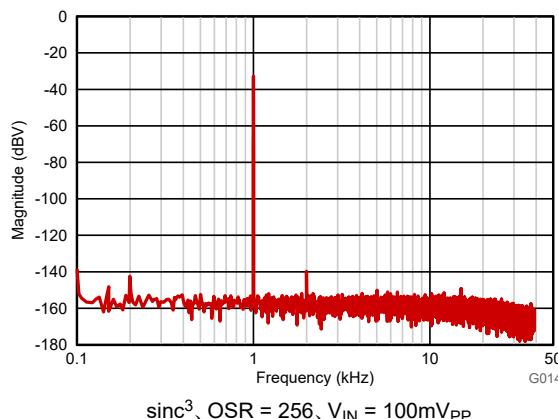

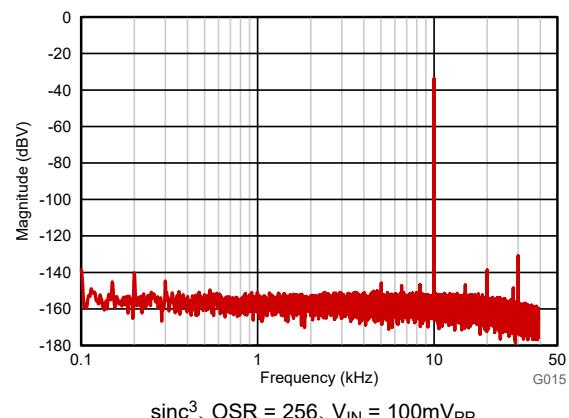

## 5.9 代表的特性 (続き)

AVDD = 5V、DVDD = 3.3V、VINP = -50mV ~ +50mV、INN = AGND、fCLKIN = 20MHz (50% のデューティ サイクル)、sinc<sup>3</sup> フィルタ (OSR = 256) での特性評価 (特に記述のない限り)。

図 5-33. 両方の入力を HGND に短絡した場合のノイズ密度

図 5-34. 1kHz 入力信号に対する周波数スペクトラム

図 5-35. 10kHz 入力信号に対する周波数スペクトラム

図 5-36. 電源電流と電源電圧との関係

図 5-37. 消費電流とクロック周波数との関係

図 5-38. 電源電流と温度との関係

## 6 詳細説明

### 6.1 概要

AMC0106M05 は、AC 信号の高分解能 A/D 変換用に設計された、シングル チャネル、2 次、CMOS、デルタ シグマ ( $\Delta\Sigma$ ) 変調器です。AMC0106M05 の差動アナログ入力は、スイッチトコンデンサ回路を使用して実装されています。コンバータの絶縁型出力 (DOUT) は、CLKIN ピンに印加される外部クロックに同期して、デジタル 1 および 0 のストリームを供給します。このシリアル出力の時間平均は、アナログ入力電圧に比例します。

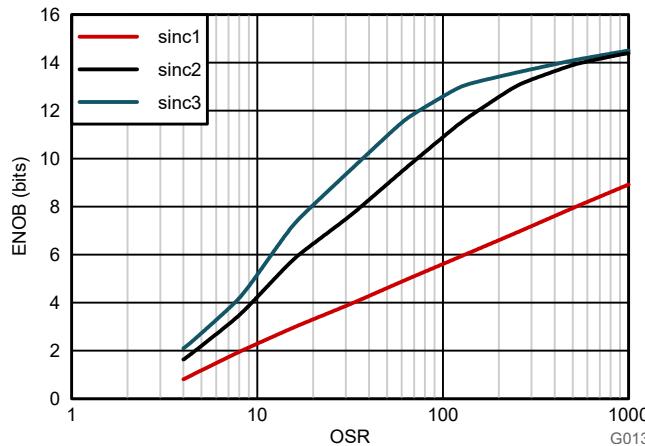

変調器は、量子化ノイズを高周波数にシフトします。このため、全体的な性能を高めるために、デバイスの出力で sinc フィルタなどのデジタル ローパス フィルタを使用します。このフィルタは、高いサンプリング レートの 1 ビット データ ストリームを、より低いレートでビット数の多いデータ ワードに変換します(間引き)。フィルターを実装するには、マイクロコントローラ ( $\mu$ C) またはフィールド プログラム可能ゲートアレイ (FPGA) を使用します。

全体的な性能 (速度と分解能) は、適切なオーバー サンプリング比 (OSR) とフィルタ タイプの選択によって異なります。OSR が高いほど分解能が高くなり、低いリフレッシュ レートで動作します。OSR が低いほど分解能は低くなりますが、データのリフレッシュ レートは高くなります。複数のフィルタを並行して実行できます。たとえば、高速過電流検出用の低 OSR フィルタや、高分解能の電流測定用の高 OSR フィルタが挙げられます。

二酸化シリコン ( $\text{SiO}_2$ ) ベースの容量性絶縁バリアは、高レベルの磁場耐性をサポートします。[ISO72x デジタル アインレータの磁界耐性』アプリケーション ノート](#) を参照してください。AMC0106M05 はオン / オフ キーリング (OOK) 変調を使用して、絶縁バリアをまたぐデータを送信します。この変調および絶縁バリアの特性から、ノイズの多い環境における高い信頼性と、高い同相過渡耐性が得られます。

### 6.2 機能ブロック図

## 6.3 機能説明

### 6.3.1 アナログ入力

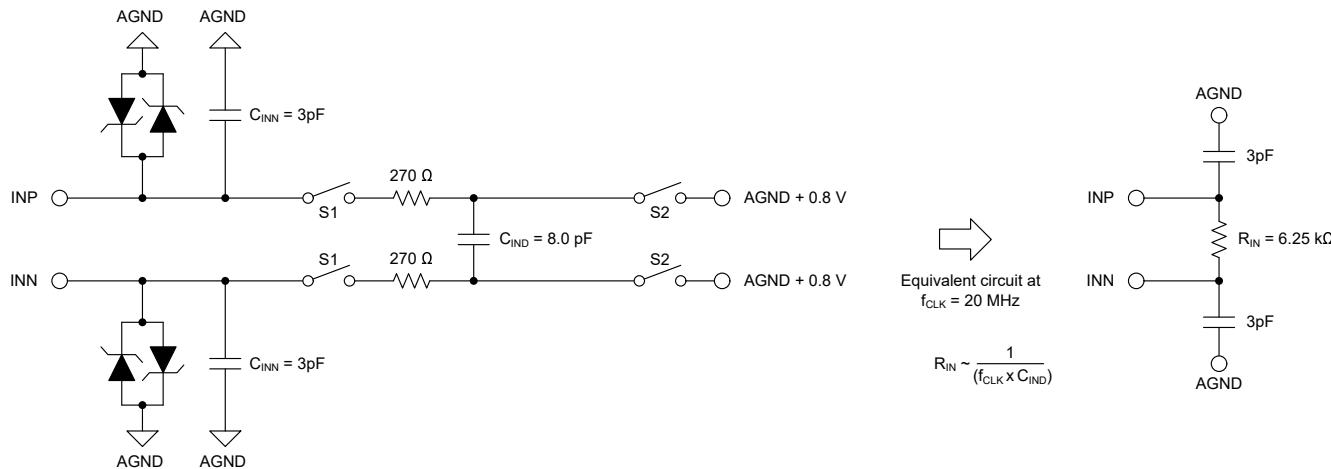

図 6-1 に示すように、AMC0106M05 の入力は、20MHzにおいて  $6.25\text{k}\Omega$  の動的入力インピーダンスを持つ完全差動スイッチトコンデンサ回路です。

サンプリングコンデンサは、 $f_{\text{CLK}}$  の周波数で連続的に充放電されます。S1 スイッチが閉になると、 $C_{\text{IND}}$  は  $V_{\text{INP}}$  と  $V_{\text{INN}}$  の間の電圧差まで充電されます。放電フェーズでは、両方の S1 スイッチが最初に開き、次に両方の S2 スイッチが閉じます。このフェーズの間、 $C_{\text{IND}}$  はおよび  $\text{AGND} + 0.8\text{V}$  の値となるまで放電されます。

図 6-1. 等価入力回路

アナログ入力範囲は、電流センシングに使用されるシャント抵抗の両端での電圧ドロップに直接適合するようカスタマイズされます。アナログ入力信号(INP および INN)には 2 つの制限があります。まず、入力電圧が **絶対最大定格** の表に規定された入力範囲を超える場合は、静電放電(ESD)保護がオンになるため、入力電流を絶対最大値に制限します。次に、デバイスの直線性およびノイズ性能は、差動アナログ入力電圧が指定された  $V_{\text{FSR}}$  および  $V_{\text{CM}}$  の範囲内に維持される場合にのみ規定されます。 $V_{\text{FSR}}$  は線形フルスケール範囲、 $V_{\text{CM}}$  は入力同相電圧範囲です。

### 6.3.2 変調器

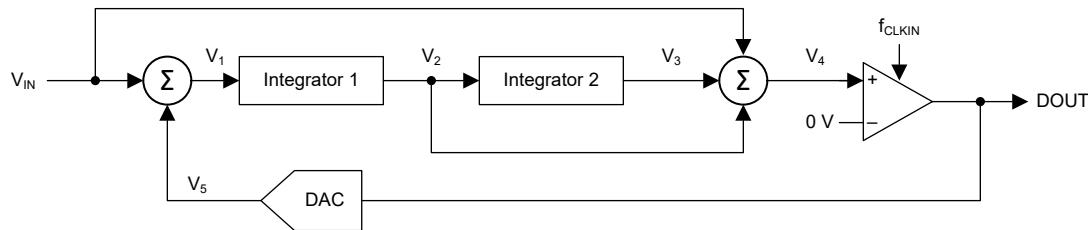

図 6-2 は、AMC0106M05 に実装されている 2 次スイッチトコンデンサ、フィードフォワード  $\Delta\Sigma$  変調器の概念を解説します。1 ビットの D/A コンバータ (DAC) の出力  $V_5$  が、入力電圧  $V_{IN} = (V_{INP} - V_{INN})$  から減算されます。この減算により、最初の積分器段の入力にアナログ電圧  $V_1$  が供給されます。最初の積分器の出力は、2 番目の積分器段の入力に供給されます。結果は、出力電圧  $V_3$  で、これが  $V_{IN}$  および最初の積分器の出力  $V_2$  と加算されます。その結果生成される電圧  $V_4$  の極性に応じて、コンパレータの出力が変化します。この場合、1 ビット DAC は、次のクロックパルスで、関連するアナログ出力電圧  $V_5$  を変更することで応答します。そのため、積分器は逆方向へ進行し、積分器の出力値は強制的に入力の平均値をトラッキングします。

図 6-2. 2 次変調器のブロック図

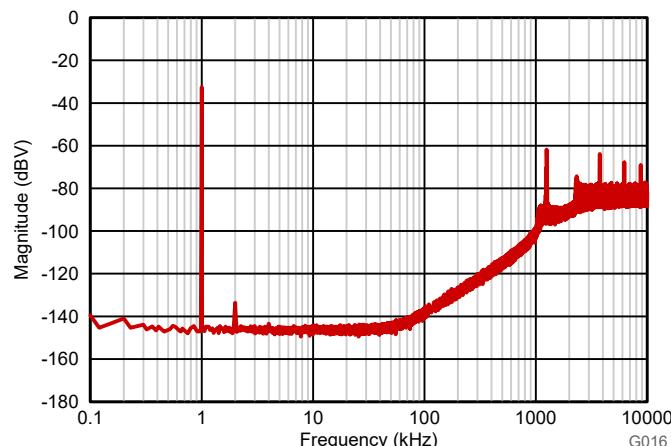

オフセットおよびオフセットのドリフトを低減するため、積分器はチョッピング周波数を  $f_{CLKIN}/16$  に設定してチョップ安定化されます。20MHz の変調器クロックのチョッピング周波数によって生成される 1.25MHz のスプリアスを、図 6-3 に示します。

sinc<sup>3</sup> フィルタ、OSR = 1、 $f_{CLKIN} = 20\text{MHz}$ 、 $f_{IN} = 1\text{kHz}$

図 6-3. 量子化ノイズ成形

### 6.3.3 絶縁チャネルの信号伝送

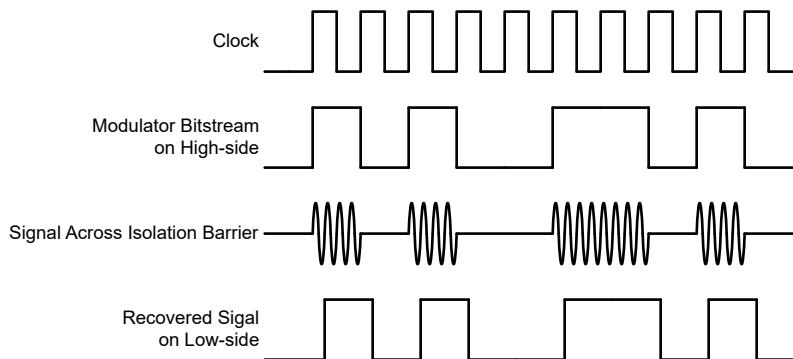

AMC0106M05 は、オン/オフ キーイング (OOK) 変調方式を使用して、変調器の出力ビット ストリームを、 $\text{SiO}_2$  ベースの絶縁バリア越しに送信します。機能ブロック図に示す送信ドライバ (TX) は、内部で生成された高周波キャリアを絶縁バリア越しに送信し、デジタル 1 を表現します。ただし、TX はデジタル 0 を表す信号を送信しません。AMC0106M05 で使用されるキャリアの公称周波数は 480MHz です。

オン/オフ キーイング方式の概念を、図 6-4 に示します。

図 6-4. OOK ベースの変調方式

### 6.3.4 デジタル出力

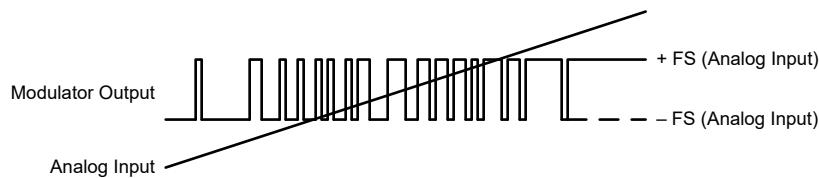

0V の差動入力信号は、理想的には時間の 50% が "High" である 1 と 0 のストリームを生成します。50mV の差動入力は、理想的には時間の 89.06% が "High" である 1 と 0 のストリームを生成します。分解能が 16 ビットであるため、このパーセンテージは理想的にはコード 58368 に対応します。50mV の差動入力は、理想的には時間のうち 10.94% が "High" である 1 と 0 のストリームを生成します。分解能が 16 ビットであるため、このパーセンテージは理想的にはコード 7168 に対応します。これらの入力電圧は、AMC0106M05 と規定された線形範囲でもあります。入力電圧の値がこの範囲を超えた場合、変調器の出力には非線形の動作が見られるようになり、量子化ノイズが増大します。変調器の出力は、64mV 以下の入力でゼロの固定ストリーム、または 64mV 以上の入力で 1 の一定ストリームでクリッピングされます。ただしこの場合、AMC0106M05 は 128 クロック サイクルごとに 1 または 0 を生成し、デバイスが正しく機能していることを示します。入力が負のフルスケールにある場合、1 つの 1 が生成され、入力が正のフルスケールにある場合には 0 が生成されます。詳細については、「[フルスケール入力の場合の出力動作](#)」セクションを参照してください。入力電圧と、変調器の出力信号との関係を、図 6-5 に示します。

図 6-5. 变调器出力とアナログ入力の関係

出力ビット ストリームの 1 の密度は、任意の入力電圧 ( $V_{IN} = V_{INP} - V_{INN}$ ) の値に対して式 1 を使用して計算されます。[フルスケール入力の場合の出力動作](#) のセクションで説明しているとおり、フルスケール入力信号を除きます。

$$\rho = \frac{V_{IN} + V_{Clipping}}{2 \times V_{Clipping}} \quad (1)$$

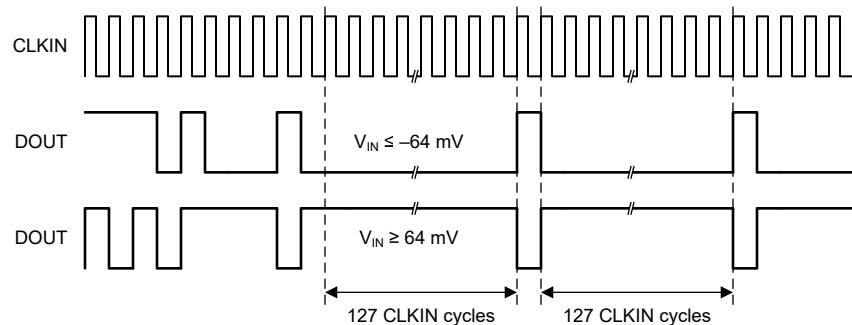

#### 6.3.4.1 フルスケール入力の場合の出力動作

AMC0106M05 にフルスケール入力信号が印加された場合、デバイスは DOUT の 128 ビットごとに 1 または 0 を生成します。このプロセスのタイミング図を、図 6-6 に示します。検出される信号の実際の極性に応じて、単一の 1 または 0 が生

成されます。フルスケール信号は、 $|V_{IN}| \geq |V_{Clipping}|$  の場合に定義されます。この方法により、AVDD が消失した状態と、フルスケール入力信号の状態とを、システムレベルで区別できます。

図 6-6. AMC0106M05 のフルスケール出力

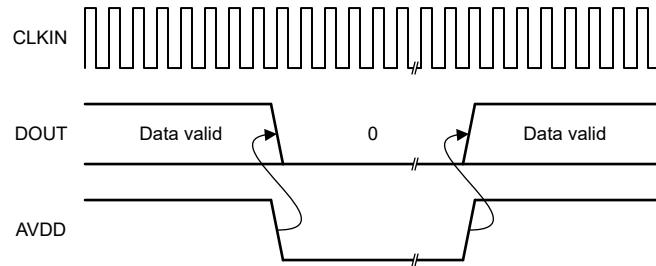

#### 6.3.4.2 ハイサイド電源が消失した場合の出力動作

図 6-7 に示すように、ハイサイド電源がなければ、デバイスは出力にロジック 0 の一定のビットストリームを提供します。ハイサイド電源が喪失すると、DOUT は永続的に "Low" になります。128 のクロック パルスごとに 1 が生成されるわけではなく、この状況が有効な負のフルスケール入力と区別されます。この機能は、基板上のハイサイド電源の問題を識別するのに役立ちます。

図 6-7. ハイサイド電源が消失した場合の AMC0106M05 の出力

## 6.4 デバイスの機能モード

AMC0106M05 は、次の状態のいずれかで動作します。

- OFF 状態: デバイスのローサイド (AVDD) には電源が供給されません。デバイスは応答せず、DOUT はハイインピーダンス状態です。内部では、DOUT は ESD 保護ダイオードによって DVDD および DGND にクランプされます。

- ハイサイド電源喪失: DVDD は [推奨動作条件](#) 内で供給されますが、 $V_{AVDD}$  は  $AVDD_{UV}$  スレッショルドよりも低くなっています。このデバイスは、[ハイサイド電源が消失した場合の出力動作](#) のセクションで説明されているように、ロジック 0 の一定のビットストリームを出力します。

- 同相モード入力違反: AVDD および DVDD はそれぞれの推奨動作条件の範囲内で供給されます。ただし、同相入力電圧  $V_{CM} = (V_{INP} + V_{INN}) / 2$  は推奨動作条件の範囲外です。デバイスは、差動入力電圧  $V_{IN}$  にかかわらず、無効なデータを出力します。

- 差動入力電圧範囲違反 (フルスケール入力):  $V_{AVDD}$ 、 $V_{DVDD}$ 、 $V_{CM}$  は推奨動作条件内です。ただし、差動入力電圧  $V_{IN} = (V_{INP} - V_{INN})$  はクリッピング電圧 ( $|V_{IN}| > |V_{Clipping}|$ ) を超えます。このデバイスは、[ハイサイド電源が消失した場合の出力動作](#) のセクションで説明されているように、固定パターンを出力します。

- 通常動作の場合:  $V_{AVDD}$ 、 $V_{DVDD}$ 、 $V_{CM}$ 、 $V_{IN}$  は推奨動作条件内です。このデバイスは、[デジタル出力](#) のセクションで説明されているように、デジタルビットストリームを出力します。

**表 6-1. デバイスの動作モード**

| 動作条件       | $V_{DVDD}$             | $V_{AVDD}$             | $V_{CM}$<br>( $V_{INP} + V_{INN}) / 2$ )             | $V_{IN}$<br>( $V_{INP} - V_{INN}$ ) | デバイス<br>の応答                                                               |

|------------|------------------------|------------------------|------------------------------------------------------|-------------------------------------|---------------------------------------------------------------------------|

| OFF        | $V_{DVDD} < DVDD_{UV}$ | 未使用                    | 未使用                                                  | 未使用                                 | DOUT はハイインピーダンス状態。<br>DOUT は ESD 保護ダイオードによつて DVDD および DGND にクランプさ<br>れます。 |

| ハイサイド電源喪失  | 有効 <sup>(1)</sup>      | $V_{AVDD} < AVDD_{UV}$ | 未使用                                                  | 未使用                                 | DOUT は常時 "Low" です                                                         |

| 同相入力電圧範囲違反 | 有効 <sup>(1)</sup>      | 有効 <sup>(1)</sup>      | $V_{CM} < V_{CM, MIN}$ または<br>$V_{CM} > V_{CM, MAX}$ | 未使用                                 | デバイスは無効なデータを出力                                                            |

| 差動入力電圧範囲違反 | 有効 <sup>(1)</sup>      | 有効 <sup>(1)</sup>      | 有効 <sup>(1)</sup>                                    | $ V_{IN}  > V_{Clipping}$           | デバイスは 128 クロック サイクルごと<br>に 1 つの 1 または 1 つの 0 を出力                          |

| 通常動作       | 有効 <sup>(1)</sup>      | 有効 <sup>(1)</sup>      | 有効 <sup>(1)</sup>                                    | 有効 <sup>(1)</sup>                   | 通常動作                                                                      |

(1) 「有効」は、推奨動作条件の範囲内にあることを示します。

7 アプリケーションと実装

注

以下のアプリケーション情報は、テキサス・インスツルメンツの製品仕様に含まれるものではなく、テキサス・インスツルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

## 7.1 アプリケーション情報

絶縁型変調器は、安全上の理由または機能的な理由により、高電圧ドメインが低電圧ドメインから電気的に絶縁されているアプリケーションで広く使用されています。代表的なアプリケーションは、周波数インバータにおける相電流のセンシングです。

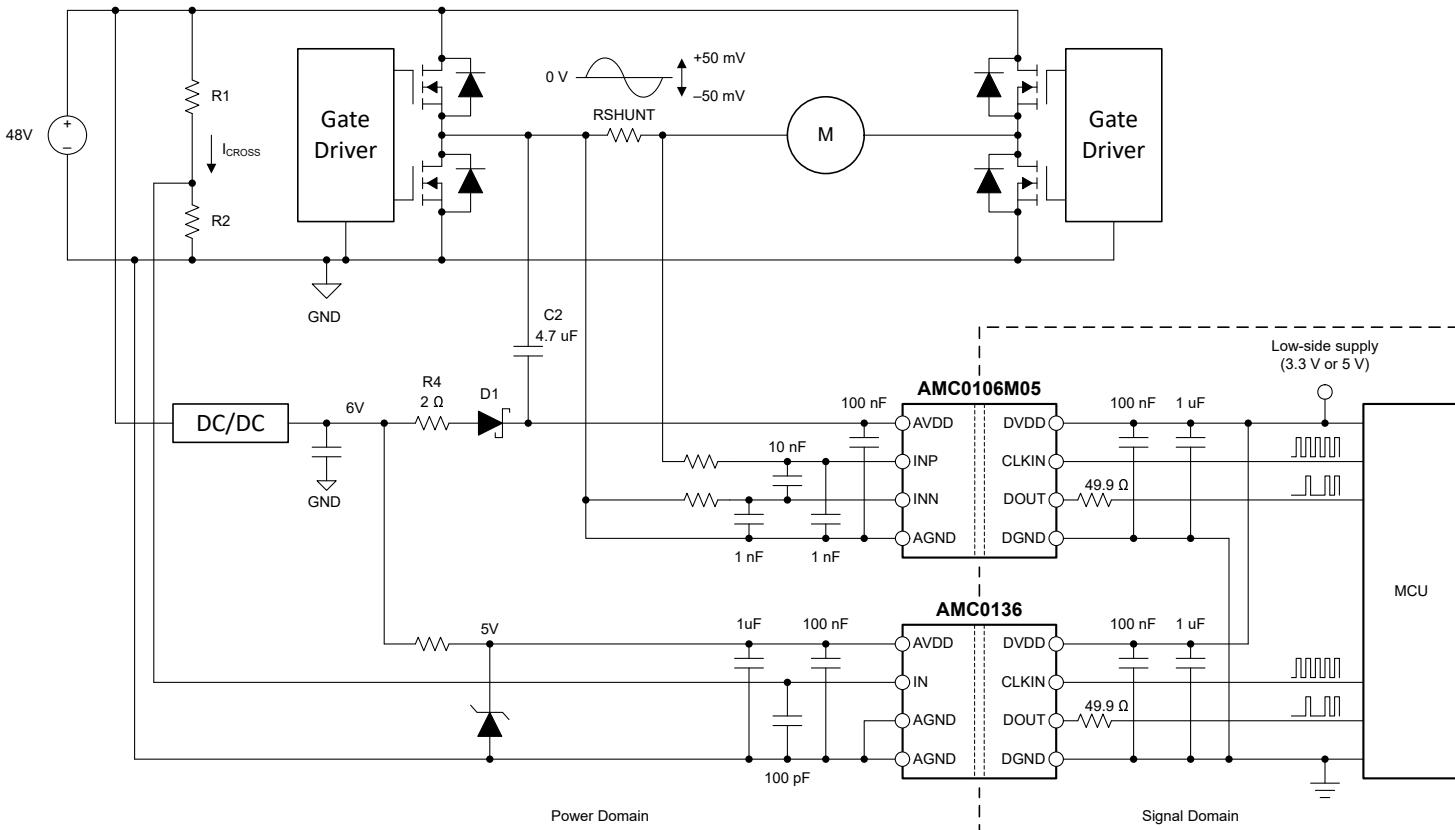

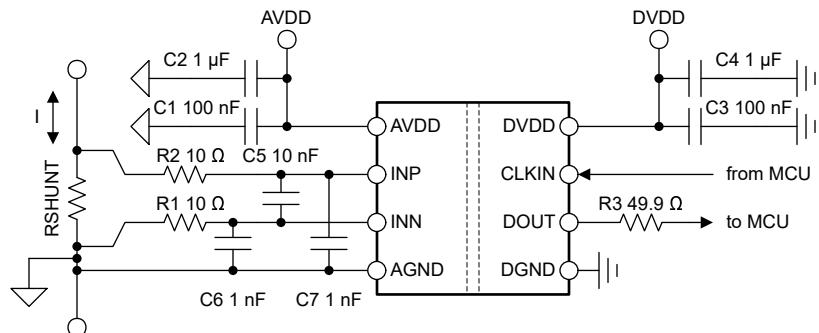

## 7.2 代表的なアプリケーション

図 7-1 に、AMC0106M05 を使用してモーター電流を検出するフルブリッジモータードライブの概略回路図を示します。外付けのシャント抵抗 **RSHUNT** を流れる電流が電圧降下を発生させ、これが、AMC0106M05 によって検出されます。AMC0106M05 は、ハイサイドでのアナログ入力信号をデジタル化し、絶縁バリアを経由してローサイドにデータを転送します。次に、デバイスは、**CLKIN** ピンに印加されたクロックに同期したデジタルビットストリームを **DOUT** ピンに出力します。デジタルビットストリームは、マイクロ制御ユニット (MCU) または FPGA 内のローパスデジタルフィルタによって処理されます。

このアプリケーションでの 48V DC リンク電圧は、AMC0136 絶縁型変調器によって検出されます。

図 7-1. フルブリッジ 48V モーター ドライバの設計での AMC0106M05 を使用した電流センシング

ハイサイド電源 (AVDD) は、ブートストラップ回路 (R4、D1、C2) から生成されます。ローサイド電源は、信号ドメインの回路と共有されます。受信側のシグナル インテグリティを向上させるために、ライン終端にはオプションの  $49.9\Omega$  抵抗を DOUT ピンに使用します。

ガルバニック絶縁バリアと優れた同相過渡耐性 (CMTI) を備えた AMC0106M05 を使うと、ノイズの多い環境でも信頼性と精度の高い動作を実現できます。

### 7.2.1 設計要件

表 7-1 に、この代表的なアプリケーションのパラメータを一覧します。

表 7-1. 設計要件

| パラメータ                             | 値         |

|-----------------------------------|-----------|

| システム電圧、電力段                        | 48V       |

| ブートストラップ電源電圧 ( $V_{BS}$ )         | 6V        |

| AVDD 電源の最大リップル電圧 ( $V_{RIPPLE}$ ) | 200mV     |

| PWM 周波数                           | 16kHz     |

| PWM デューティ サイクル範囲                  | 5%~95%    |

| リニア電流検出範囲                         | $\pm 25A$ |

### 7.2.2 詳細な設計手順

図 7-1 では、ハイサイド電源 (AVDD) はブートストラップ回路 (R4、D1、C2) から生成されます。

ハイサイドのグランドリファレンス (AGND) は、AMC0106M05 の負の入力 (INN) に接続されているシャント抵抗の片端から派生されます。4 端子のシャントの場合、デバイス入力をシャントの内部リードに接続し、AGND を外部リードに接続します。オフセットを最小化し、精度を向上させるには、グランド接続を個別のパターンとして配線します。AGND は、本デバイスの入力で AGND を INN に短絡させるのではなく、シャント抵抗に直接接続します。詳細については、「レイアウト」セクションを参照してください。

#### 7.2.2.1 シャント抵抗の決定

シャント抵抗 ( $R_{SHUNT}$ ) の値は、デバイスの線形入力電圧範囲 ( $\pm 50mV$ ) と、必要な線形電流センシング範囲である  $\pm 25A$  によって決定されます。 $R_{SHUNT}$  は  $50mV / 25A = 2m\Omega$  として計算されます。シャント抵抗で消費されるピーク電力は、 $R_{SHUNT} \times I_{PEAK}^2 = 2m\Omega \times (25A)^2 = 1.25W$  です。線形応答を得るには、定格電力の  $2/3$  を超えないようにシャント抵抗を動作させます。そのため、公称電力定格が約  $1.8W$  のシャント抵抗を選択します。

システムで AMC0106M05 の線形入力電圧範囲を超える過渡的な過電流が予想される場合は、より低いシャント抵抗の値を選択します。ただし、過電流範囲に対して線形性の低下と分解能の低下を許容できる場合は、シャントの両端での電圧降下は、AMC0106M05 のクリッピング電圧まで、線形入力電圧範囲を超えることが可能です。どのような場合でも、最大過電流により発生する電圧降下は、クリッピング出力を起こす入力電圧を超えてはいけません。つまり、 $|V_{SHUNT}| \leq |V_{Clipping}|$  となることを徹底してください。

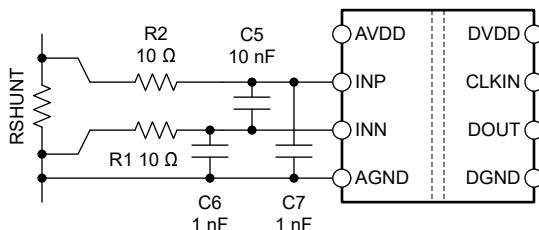

### 7.2.2.2 入力フィルタの設計

絶縁型変調器の前に差動 RC フィルタ ( $R_1$ 、 $R_2$ 、 $C_5$ ) を配置し、信号路の信号対雑音比性能を向上させます。 $\Delta\Sigma$  変調器のサンプリング周波数に近い周波数（通常は 20MHz）の入力ノイズは、変調器によって低周波数の範囲にフォールドバックされます。入力における RC フィルタの目的は、高周波ノイズを測定に必要なノイズレベルを下回るように減衰させることです。入力フィルタは次のように設計します。

- フィルタ容量 ( $C_5$ ) は最小 10nF

- フィルタのカットオフ周波数は、 $\Delta\Sigma$  変調器のサンプリング周波数 ( $f_{CLKIN}$ ) より 1 枠以上低い値

- 動的入力バイアス電流では、入力フィルタの DC インピーダンス ( $R_1$ 、 $R_2$ ) の両端で大きな電圧降下は発生しない

- アナログ入力から測定されたインピーダンスは等しい ( $R_1 = R_2$ )

コンデンサ  $C_6$  および  $C_7$  はオプションであり、高周波数 (>1MHz) での同相除去を改善します。最高の性能を得るには、 $C_6$  が  $C_7$  の値と一致し、両方のコンデンサの容量が  $C_5$  の 10 ~ 20 分の 1 となるようにします。NP0 タイプのコンデンサは温度ドリフトと電圧係数が低く、同相モード フィルタリングに適しています。ほとんどのアプリケーションでは、図 7-2 に示す構造により優れた性能を実現します。

図 7-2. 入力フィルタ

### 7.2.2.3 ピットストリーム フィルタリング

変調器は、デジタル フィルタによって処理されたビットストリームを生成し、従来型の A/D コンバータ (ADC) の変換結果と同じようなデジタル ワードを生成します。式 2 に  $\text{sinc}^3$  タイプのフィルタを示します。このフィルタは、最小限の労力とハードウェアで構築される、非常にシンプルなフィルタです。

$$H(z) = \left( \frac{1 - z^{-OSR}}{1 - z^{-1}} \right)^3 \quad (2)$$

このフィルタは 2 次変調器用に、最も小さなハードウェア(デジタル ゲート数)で、最良の出力性能が得られます。このドキュメントに記載されているすべての特性は、オーバーサンプリングレート (OSR) が 256 の  $\text{sinc}^3$  フィルタおよび、16 ビットの出力ワード幅で測定されたものです。

『ADS1202 と FPGA デジタル フィルタとの組み合わせによるモーター制御アプリケーションでの電流測定』アプリケーション ノートでは、サンプル コードについて説明されています。FPGA に  $\text{sinc}^3$  フィルタを実装するには、このサンプル コードを使用します。このアプリケーション ノートは、[www.ti.com](http://www.ti.com) からダウンロードできます。

変調器の出力するビット ストリームのフィルタ処理には、テキサス インスツルメンツの C2000 または Sitara マイコン ファミリーのデバイスを使用します。これらのファミリーは、チャネルごとに 2 つのフィルタ処理パスを提供することで、システム レベルの設計を大幅に簡素化する、マルチチャネルの専用ハードワイヤード フィルタ構造をサポートしています 1 つのパスは制御ループの高精度結果をもたらし、もう 1 つのパスは過電流検出の高速応答パスです。

デルタ シグマ 変調器のフィルタ計算機は、[www.ti.com](http://www.ti.com) からダウンロードできます。これは、フィルタ設計および正しい OSR とフィルタ次数の選択に役立ちます。この計算機は、目的の出力分解能とフィルタ応答時間を実現するのに役立ちます。

#### 7.2.2.4 ブートストラップ電源の設計

ブートストラップ コンデンサ (C2、図 7-1) は、左側ハーフ ブリッジのローサイド FET の PWM オン時間中に充電されます。PWM オフ時間中は、C2 はスイッチ ピンの電圧とともに立ち上がり、AMC0106M05 電源として機能します。R4 は充電フェーズ中の電流制限抵抗として機能します。D1 は、放電フェーズ中に逆電流がブートストラップ電源に逆流することを防止します。

PWM オン時間中に C2 に充電される電圧は、ブートストラップ電源および電流制限抵抗 R2 の値に依存します。さらに、この電圧は PWM デューティ サイクルおよびダイオード D1 の順方向電圧 ( $V_{F,D1}$ ) に依存します。

PWM オフ時間中に C2 から放電される電圧は、D1 の逆回復時間に依存します。また、この電圧は PWM デューティ サイクルおよび AMC0106M05 の消費電流 ( $I_{AVDD}$ ) に依存します。スイッチング損失を最小限に抑えるには、順方向電流能力の高い高速スイッチング ダイオードを選択します。

最大 PWM オフ時間の間に最大  $I_{AVDD}$  電流をサポートできるように、C2 のサイズを設定してください。この時間中は、C2 が AVDD の最小推奨電圧である 3V を下回るまで放電しないようにしてください。容量値が小さいほど充電を高速化できるため、より低い PWM デューティ サイクルがサポートされます。ただし、値が小さいと、生成される電圧リップルが大きくなり、最大 PWM オフ時間が制限されます。この例では、リップル電圧 ( $V_{RIPPLE}$ ) が 200mV 未満となることを目標としています。最大 PWM オフ時間は  $95\% \times (1 / f_{PWM}) = 0.95 \times 62.5\mu s$  であり、これは約 60 $\mu s$  です。 $I_{AVDD, MAX}$  は 8.8mA に規定されています。最小容量値は  $C_{2, MIN} = I_{AVDD, MAX} \times t_{PWM-OFF, MAX} / V_{RIPPLE} = 8.8mA \times 60\mu s / 200mV = 2.6\mu F$  として計算されます。部品の許容差を考慮して、設計にマージンを追加できるように 4.7 $\mu F$  のコンデンサを選択しています。

ブートストラップ回路が、 $5\% \times (1 / f_{PWM}) = 0.05 \times 62.5\mu s$ 、または約 3.1 $\mu s$  の最小 PWM オン時間内に C2 の再充電をサポートしていることを確認します。この間の平均充電電流は、 $C_2 \times V_{RIPPLE} / t_{PWM-ON, MIN} = 4.7\mu F \times 200mV / 3.1\mu s$  であり、約 300mA です。この電流は、ダイオード D1 がサポートする必要のある最小順方向電流です。ダイオード D1 および電流制限抵抗 R4 の両端に許容される最大電圧降下は、コンデンサ電圧の最小値と  $V_{BS}$  の値によって決定されます。コンデンサの最小電圧は 3V で、AVDD<sub>MIN</sub> に相当します。 $V_{BS}$  はブートストラップ電源電圧であり、6V です。1V のダイオード順方向電圧を使用することが前提です。R4 が  $(V_{BS} - V_{F, D1} - V_{C2, MIN}) / I_{CHARGE} = (6V - 1V - 3V) / 300mA = 6\Omega$  未満であることを確認します。2Ω の抵抗を選択すると、設計にマージンが得られます。

### 7.2.3 アプリケーション曲線

多くの場合、ADC と  $\Delta\Sigma$  変調器の性能を比較するには、実効ビット数(ENOB)が使用されます。各種のオーバーサンプリング率における AMC0106M05 の ENOB を、図 7-3 に示します。

図 7-3. 測定された実効ビット数とオーバー サンプリング率との関係

### 7.3 設計のベスト プラクティス

デバイスの入力に(INP から INN へ) 10nF 以上のコンデンサを配置します。このコンデンサは、スイッチトコンデンサの入力段のサンプリング期間中に入力での電圧ドリープを防止するのに役立ちます。

AMC0106M05 デバイスが電力供給されている場合、入力を無接続 (フローティング) のままにはしないでください。変調器入力のいずれかがフローティングのままになっている場合、出力のビットストリームは有効ではありません。

ハイサイド グランド (AGND) を INN に、ハード短絡または抵抗性パスを介して接続します。入力同相電圧を定義するには、INN と AGND の間に DC 電流パスが必要です。[推奨動作条件](#) の表に指定されているように、入力同相範囲を超えないようにします。最高の精度を得るには、センス抵抗に直接接続する個別のパターンとして、グランド接続を配線します。デバイスの入力で AGND を INN には直接短絡しないでください。詳細については、「[レイアウト](#)」セクションを参照してください。

## 7.4 電源に関する推奨事項

AMC0106M05 は、特定のパワーアップ シーケンスを必要としません。ハイサイド電源 (AVDD) は、低 ESR の  $1\mu\text{F}$  コンデンサ (C2) と並列接続された低 ESR の  $100\text{nF}$  コンデンサ (C1) でデカップリングされます。ローサイド電源 (DVDD) は、低 ESR の  $1\mu\text{F}$  コンデンサ (C4) と並列接続された低 ESR の  $100\text{nF}$  コンデンサ (C3) で同様にデカップリングされます。4 つのコンデンサ (C1, C2, C3, C4) はすべてデバイスのできるだけ近くに配置します。図 7-4 に、AMC0106M05 のデカップリング回路を示します。

図 7-4. AMC0106M05 のデカップリング

アプリケーションで発生する DC バイアス条件の下で、コンデンサは十分な実効容量を保つ必要があります。マルチレイヤ セラミック コンデンサ (MLCC) は通常、実際の使用条件下における容量は、公称容量よりはるかに小さい値となります。これらのコンデンサを選択する際は、この要素を考慮してください。この問題は、背の高い部品よりも絶縁体電界強度が高くなる薄型コンデンサで特に深刻です。信頼できるコンデンサメーカーは、部品選択を非常に簡単に容量対 DC バイアス曲線を提供しています。

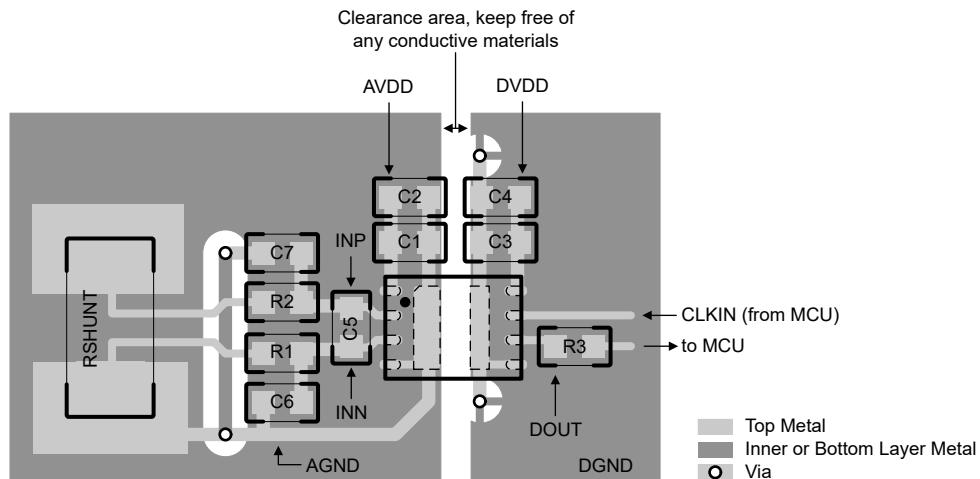

## 7.5 レイアウト

### 7.5.1 レイアウトのガイドライン

レイアウト例のセクションでは、デカップリング コンデンサの重要な配置 (AMC0106M05 の電源ピンにできるだけ近い場所) に関するレイアウトの推奨事項について詳しく説明します。このセクションでは、デバイスに必要な他の部品の配置も示しています。最高の性能を得るために、センサ抵抗はデバイスの入力ピン (INN および INP) の近くに配置します。

### 7.5.2 レイアウト例

図 7-5. AMC0106M05 の推奨レイアウト

## 8 デバイスおよびドキュメントのサポート

### 8.1 ドキュメントのサポート

#### 8.1.1 関連資料

関連資料については、以下を参照してください。

- テキサス インスツルメンツ、『絶縁の用語集』アプリケーション ノート

- テキサス インスツルメンツ、『半導体およびIC パッケージの熱評価基準』アプリケーション ノート

- テキサス インスツルメンツ、『ISO72x デジタル アイソレータの磁界耐性』アプリケーション ノート

- テキサス インスツルメンツ、『ADS1202 と FPGA デジタル フィルタとの組み合わせによるモータ制御アプリケーション での電流測定』アプリケーション ノート

- テキサス インスツルメンツ、デルタシグマ変調フィルタ カリキュレータ設計ツール

### 8.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 8.3 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

### 8.4 商標

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 8.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことをお勧めします。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 8.6 用語集

テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 9 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

Changes from AUGUST 2, 2024 to JUNE 10, 2025 (from Revision \* (August 2024) to Revision A (June 2025))

Page

- |                                         |   |

|-----------------------------------------|---|

| • ドキュメントのステータスを「事前情報」から「量産データ」に変更 ..... | 1 |

|-----------------------------------------|---|

## 10 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ（データシートを含みます）、設計リソース（リファレンス デザインを含みます）、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかる テキサス・インスツルメンツ製品の関連資料などのいづれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| AMC0106M05DENR        | Active        | Production           | VSON (DEN)   8 | 5000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | 0106M5              |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

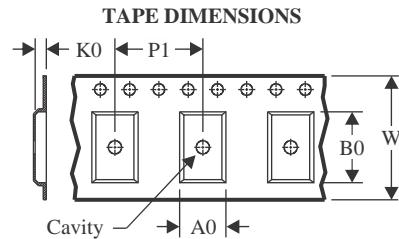

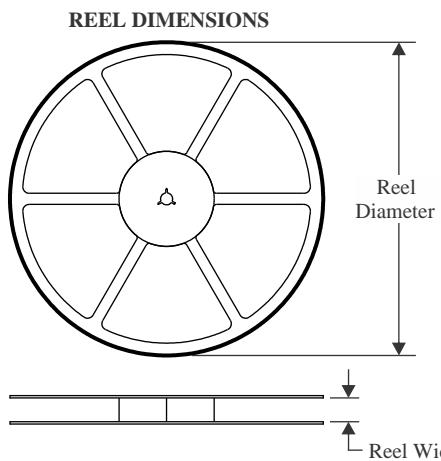

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

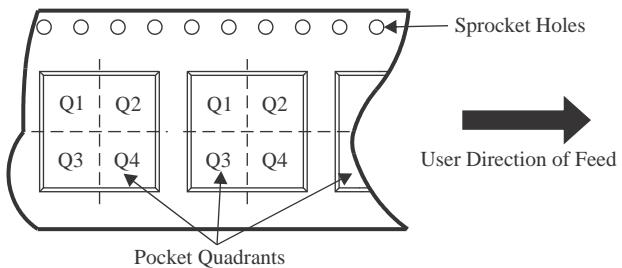

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|----------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| AMC0106M05DENR | VSON         | DEN             | 8    | 5000 | 330.0              | 12.4               | 3.0     | 3.8     | 1.2     | 8.0     | 12.0   | Q2            |

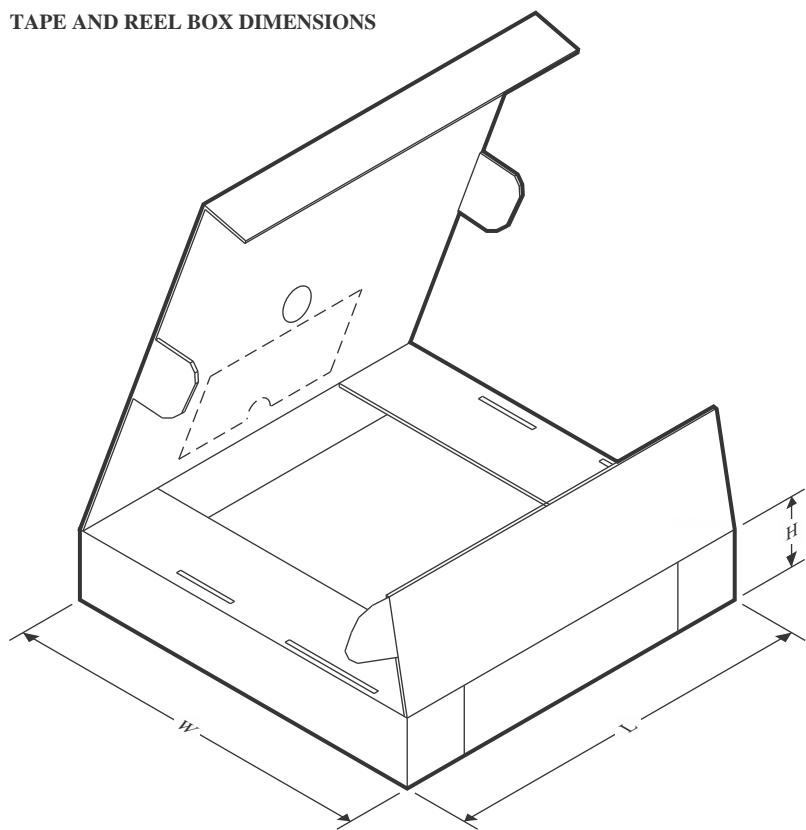

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| AMC0106M05DENR | VSON         | DEN             | 8    | 5000 | 346.0       | 346.0      | 33.0        |

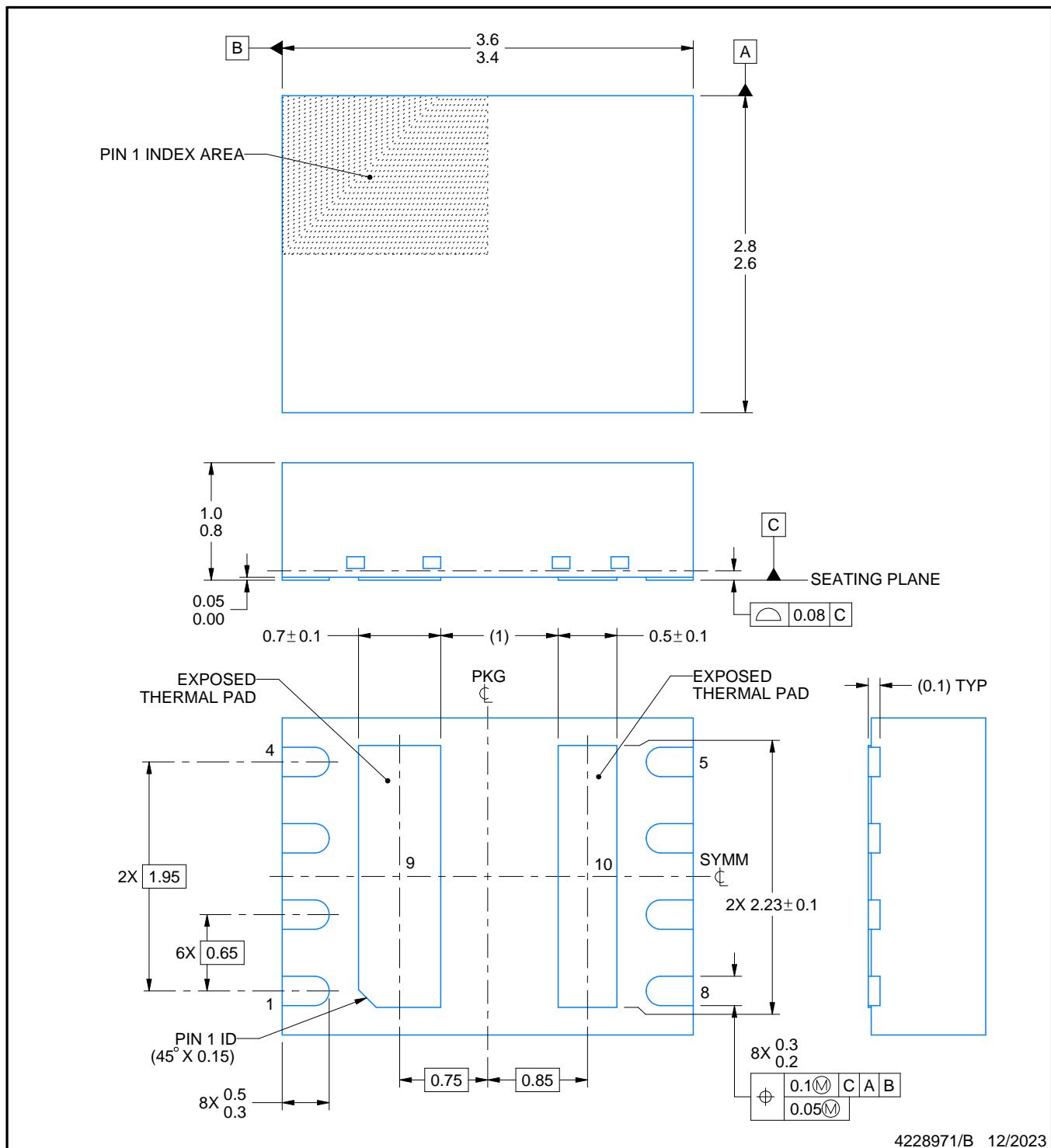

DEN0008A

# PACKAGE OUTLINE

VSON - 1 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

4228971/B 12/2023

## NOTES:

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- This drawing is subject to change without notice.

- The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

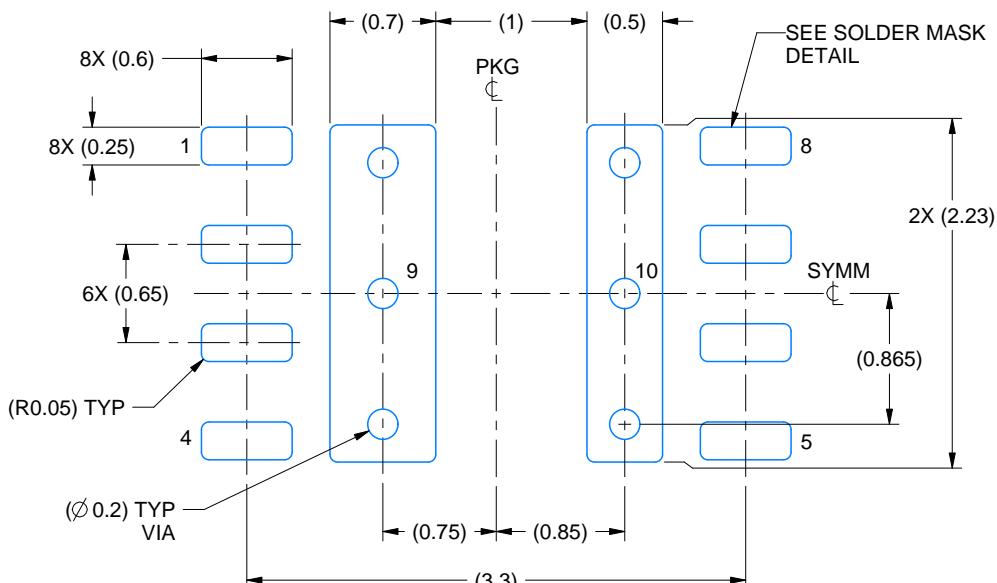

# EXAMPLE BOARD LAYOUT

DEN0008A

VSON - 1 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE: 20X

SOLDER MASK DETAILS

4228971/B 12/2023

NOTES: (continued)

4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 ([www.ti.com/lit/slua271](http://www.ti.com/lit/slua271)).

5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

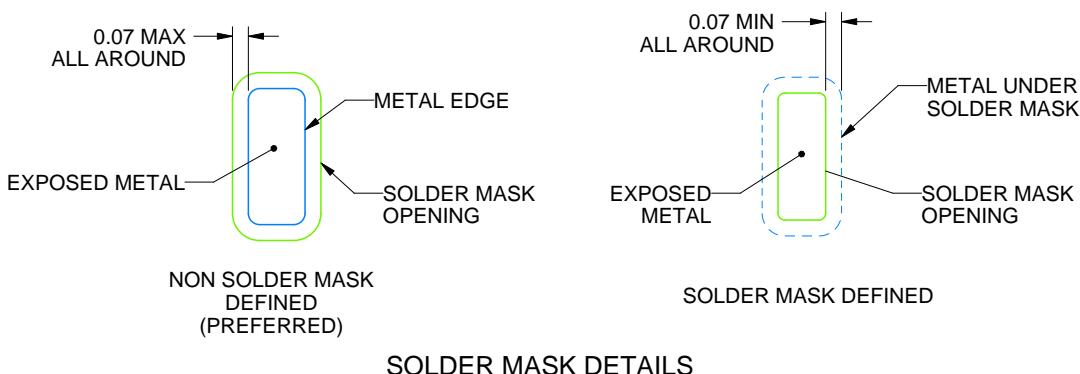

# EXAMPLE STENCIL DESIGN

DEN0008A

VSON - 1 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

SOLDER PASTE EXAMPLE

BASED ON 0.125 MM THICK STENCIL

SCALE: 20X

PRINTED SOLDER COVERAGE BY AREA UNDER PACKAGE

PADS 9 & 10: 77%

4228971/B 12/2023

NOTES: (continued)

- Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2026, Texas Instruments Incorporated

最終更新日：2025 年 10 月