BQ76920, BQ76930, BQ76940

JAJSH19I – OCTOBER 2013 – REVISED MARCH 2022

# BQ769x0 3~15 直列セル・バッテリ・モニタ・ファミリ、 リチウムイオンおよびリン酸塩アプリケーション向け

# 1 特長

- AFE 監視機能

- 完全デジタル・インターフェイス

- セル電圧、ダイ温度、外部サーミスタを測定する内蔵 ADC

- バッテリ・パック電流を測定する独立した内蔵 ADC (クーロン・カウンタ)

- 最大 3 つのサーミスタ (103AT) を直接サポート

- ハードウェア保護機能

- 放電時の過電流 (OCD)

- 故電時の短絡 (SCD)

- 過電圧 (OV)

- 低電圧 (UV)

- セカンダリ・プロテクタ・フォルト検出

- 追加機能

- セル・バランシング FET を内蔵

- 充放電用ローサイド NCH FET ドライバ

- ホスト・マイクロコントローラへのアラート割り込み

- 2.5V~3.3V の出力電圧レギュレータ

- EEPROM プログラミング不要

- 電源電圧の絶対最大定格が高い (最大 108V)

- シンプルな I<sup>2</sup>C 互換インターフェイス (CRC オプション)

- セルをランダムに接続可能

# 2 アプリケーション

- LEV (軽量電気車両): 電動バイク、電動スクーター、電動アシスト自転車

- 電動工具、園芸用器具

- バッテリ・バックアップ・ユニット (BBUS)、エネルギー・ストレージ・システム (ESS)、無停電電源 (UPS) システム

- その他の産業用バッテリ・パック (10S 以上)

## 3 概要

BQ769x0 高信頼性アナログ・フロント・エンド (AFE) デバイス・ファミリは、軽量電気車両、電動工具、無停電電源装置など、次世代大電力システムの包括的なパック監視および保護ソリューションの一部としての役割を果たします。BQ769x0 は、低消費電力を考慮して設計されています。IC 内のサブブロックは、チップ全体の消費電流を制御するために有効または無効にできます。また、シップ・モードを使うと、パックを簡単に超低消費電力状態に移行させることができます。

BQ76920 デバイスは最大 5 直列セルまたは 18V (標準値) パック、BQ76930 は最大 10 直列セルまたは 36V (標準値) パック、BQ76940 は最大 15 直列セルまたは 48V (標準値) パックをそれぞれサポートしています。これらの AFE を使用して、リチウムイオン、リン酸鉄リチウムを含む各種バッテリ・ケミストリを管理できます。ホスト・コントローラで BQ769x0 を I<sup>2</sup>C 制御することで、多くのバッテリ・パック管理機能 (例:監視 (セル電圧、パック電流、パック温度)、保護 (充放電 FET の制御)、平衡化) を実現できます。内蔵 A/D コンバータを使うと、重要なシステム・パラメータを純粋にデジタル的に読み出すことができます。この A/D コンバータは TI の製造プロセスでキャリブレーション済みです。

#### 製品情報

| 部品番号1   | パッケージ      | 本体サイズ (公称)       |  |  |

|---------|------------|------------------|--|--|

| BQ76920 | TSSOP (20) | 6.50mm × 4.40mm  |  |  |

| BQ76930 | TSSOP (30) | 7.80mm × 4.40mm  |  |  |

| BQ76940 | TSSOP (44) | 11.00mm × 4.40mm |  |  |

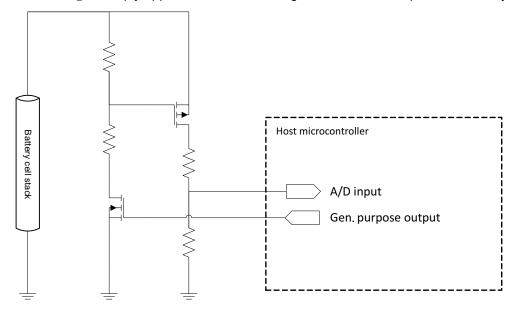

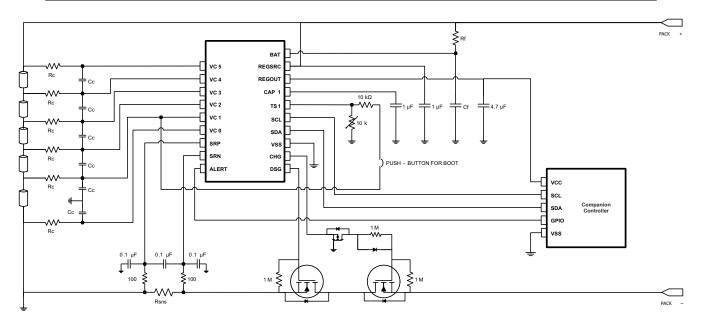

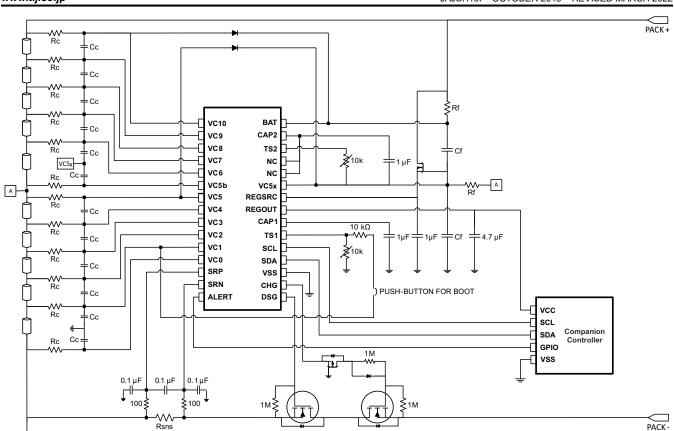

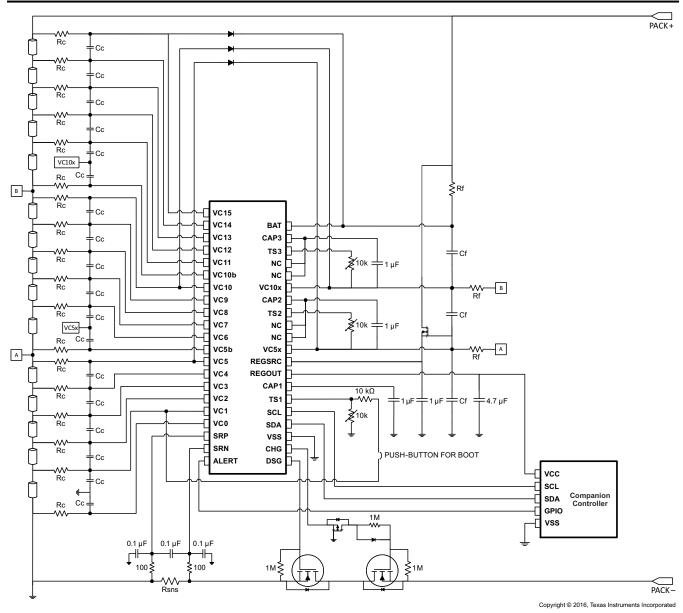

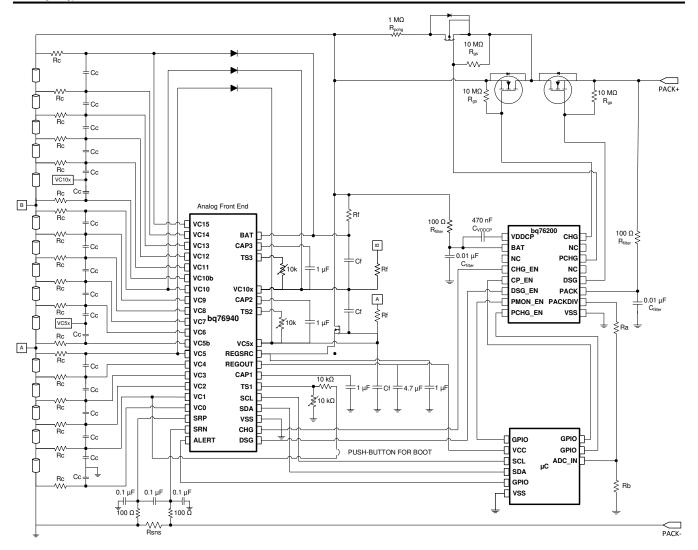

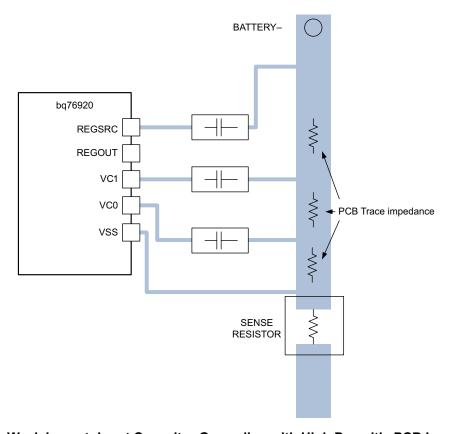

概略回路図

# **Table of Contents**

| 1 特長                                 | 1 | 8.2 Functional Block Diagram                         | 16  |

|--------------------------------------|---|------------------------------------------------------|-----|

| 2 アプリケーション                           |   | 8.3 Feature Description                              |     |

| 3 概要                                 |   | 8.4 Device Functional Modes                          | 27  |

| 4 Revision History                   |   | 8.5 Register Maps                                    | 29  |

| 5 Device Comparison Table            |   | 9 Application and Implementation                     | 39  |

| 6 Pin Configuration and Functions    |   | 9.1 Application Information                          | 39  |

| 6.1 Versions                         |   | 9.2 Typical Applications                             | 42  |

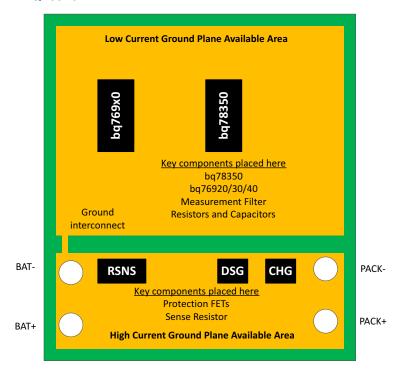

| 6.2 BQ76920 Pin Diagram              |   | 10 Power Supply Recommendations                      | 47  |

| 6.3 BQ76930 Pin Diagram              |   | 11 Layout                                            | 48  |

| 6.4 BQ76940 Pin Diagram              |   | 11.1 Layout Guidelines                               | 48  |

| 7 Specifications                     |   | 11.2 Layout Example                                  | 48  |

| 7.1 Absolute Maximum Ratings         |   | 12 Device and Documentation Support                  | 50  |

| 7.2 ESD Ratings                      |   | 12.1 Third-Party Products Disclaimer                 | 50  |

| 7.3 Recommended Operating Conditions |   | 12.2 Documentation Support                           | 50  |

| 7.4 Thermal Information              |   | 12.3 Related Links                                   | 50  |

| 7.5 Electrical Characteristics       |   | 12.4 Receiving Notification of Documentation Update: | s50 |

| 7.6 Timing Requirements              |   | 12.5 Trademarks                                      | 50  |

| 7.7 Typical Characteristics          |   | 13 Mechanical, Packaging, and Orderable              |     |

| 8 Detailed Description               |   | Information                                          | 50  |

| 8.1 Overview                         |   |                                                      |     |

# **4 Revision History**

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision H (March 2019) to Revision I (March 2022)                   | Page |

|-----------------------------------------------------------------------------------|------|

| - 全体を通して書式設定を変更                                                                   |      |

| Added VCn rows in Absolute Maximum Ratings table                                  |      |

| Changed tablenote for POR and referenced entries                                  |      |

| Changed the scale in the VCx and OV Protection plots                              |      |

| Updated 16-Bit Pack Voltage                                                       |      |

| Changed "OV Trip" to "UV Trip" in the description of undervoltage protection      |      |

| Changed the LSB bit count from 2 to 4 for the OV_TRIP register                    |      |

| Updated Application Information                                                   |      |

| Added Device Timing                                                               |      |

| Added Random Cell Connection                                                      |      |

| Added Power Pin Diodes                                                            | 39   |

| Added Alert Pin                                                                   |      |

| Added Sense Inputs                                                                | 39   |

| Added TSn Pins                                                                    |      |

| Updated Unused Pins                                                               | 40   |

| Updated Step-by-Step Design Procedure                                             |      |

| Changes from Revision G (April 2016) to Revision H (March 2019)                   | Page |

| <ul><li>「アプリケーション」を変更</li></ul>                                                   | 1    |

| • 「概要」を変更                                                                         | 1    |

| Added High-Side FET Driving                                                       |      |

| Added the link to the BQ769x0 Boot Switch Alternatives Application Report         |      |

| Added the link to the BQ769x0 Family Top Design Considerations Application Report |      |

| Added ☑ 9-4 to provide an example of a high-side FET configuration                |      |

| · · · · · · · · · · · · · · · · · · ·                                             | ·-   |

Added BQ769x0 Family Top Design Considerations Application Report link......47

# **5 Device Comparison Table**

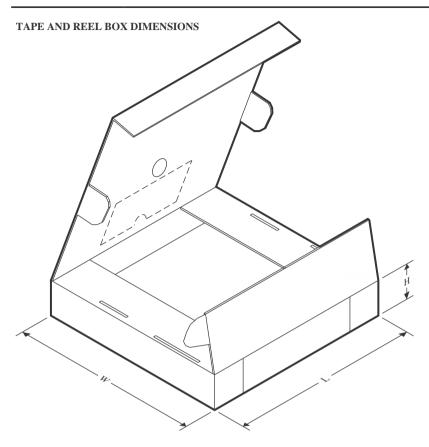

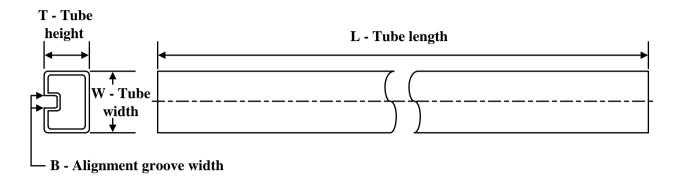

| TUBE                       | TAPE & REEL                 | CELLS                                | I <sup>2</sup> C ADDRESS (7-<br>Bit) | LDO (V) | CRC            | PACKAGE        |

|----------------------------|-----------------------------|--------------------------------------|--------------------------------------|---------|----------------|----------------|

| BQ7692000PW                | BQ7692000PWR                |                                      |                                      | 2.5     | No             |                |

| BQ7692001PW <sup>(1)</sup> | BQ7692001PWR <sup>(1)</sup> |                                      | 0x08                                 | 2.5     | Yes            |                |

| BQ7692002PW <sup>(1)</sup> | BQ7692002PWR <sup>(1)</sup> | 3–5                                  | 0,000                                |         | No             | 20-TSSOP (PW)  |

| BQ7692003PW                | BQ7692003PWR                |                                      |                                      | 3.3     | Yes            |                |

| BQ7692006PW                | BQ7692006PWR                |                                      | 0x18                                 |         | No             |                |

| BQ7693000DBT               | BQ7693000DBTR               | 2.5 Y R R 6–10 0x08 2.5 Y 0x08 N 3.3 |                                      | 2.5     | No             |                |

| BQ7693001DBT               | BQ7693001DBTR               |                                      | 0.08                                 | 2.0     | Yes            |                |

| BQ7693002DBT               | BQ7693002DBTR               |                                      | 6–10                                 | No      | 30-TSSOP (DBT) |                |

| BQ7693003DBT               | BQ7693003DBTR               |                                      |                                      |         | 2.2            | Yes            |

| BQ7693006DBT               | BQ7693006DBTR               |                                      | 0v10                                 | 3.3     | No             |                |

| BQ7693007DBT               | BQ7693007DBTR               |                                      | 0.00                                 |         | Yes            |                |

| BQ7694000DBT               | BQ7694000DBTR               |                                      |                                      | 2.5     | No             |                |

| BQ7694001DBT               | BQ7694001DBTR               |                                      | 0x08                                 | 2.5     | Yes            |                |

| BQ7694002DBT               | BQ7694002DBTR               | 9–15                                 | 0,000                                |         | No             | 44-TSSOP (DBT) |

| BQ7694003DBT               | BQ7694003DBTR               |                                      |                                      | 3.3     | Yes            |                |

| BQ7694006DBT               | BQ7694006DBTR               |                                      | 0x18                                 |         | No             |                |

# (1) Product Preview only

Texas Instruments preconfigures the BQ769x0 devices for a specific  $I^2C$  address, LDO voltage, and more. These settings are permanently stored in EEPROM and cannot be further modified.

Contact Texas Instruments for other options not listed above, as well as any options noted as "Product Preview only."

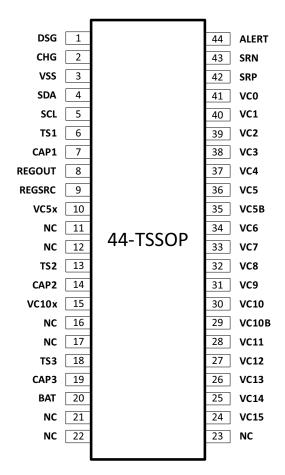

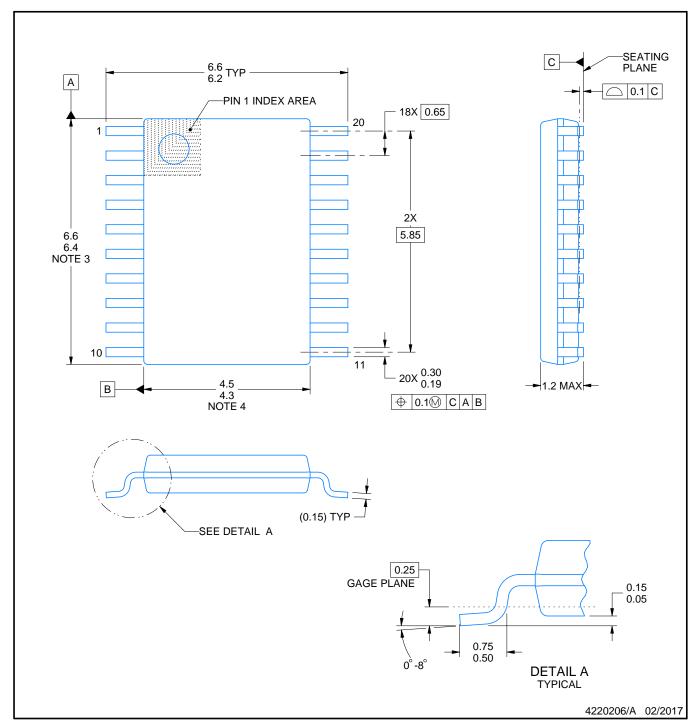

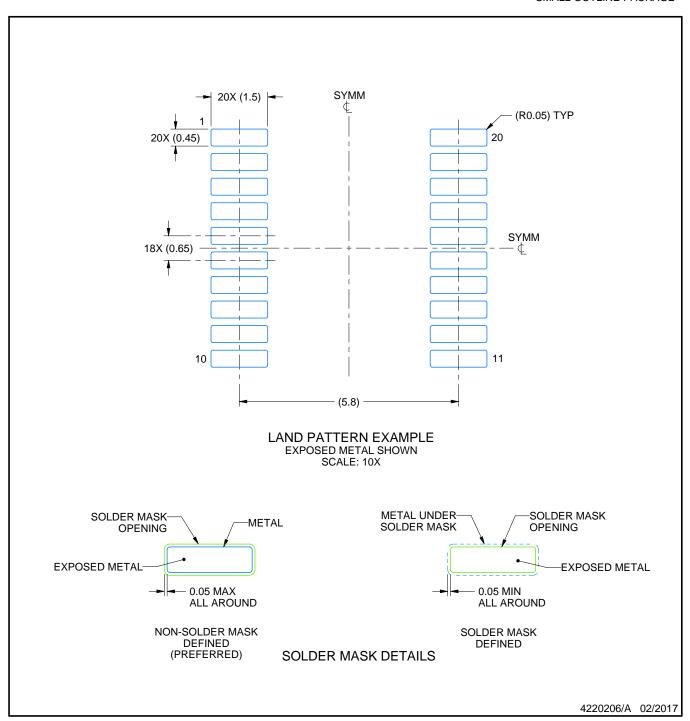

# 6 Pin Configuration and Functions

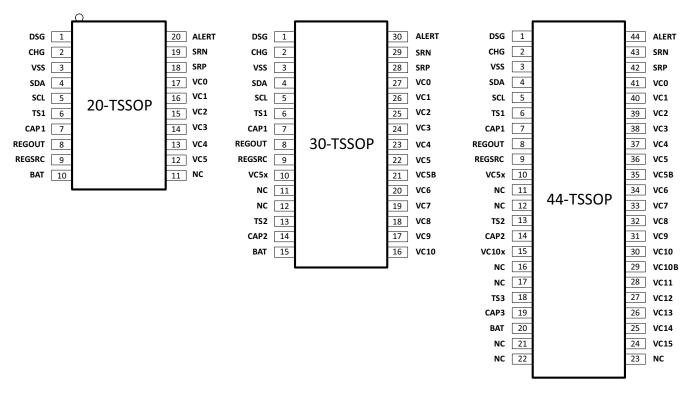

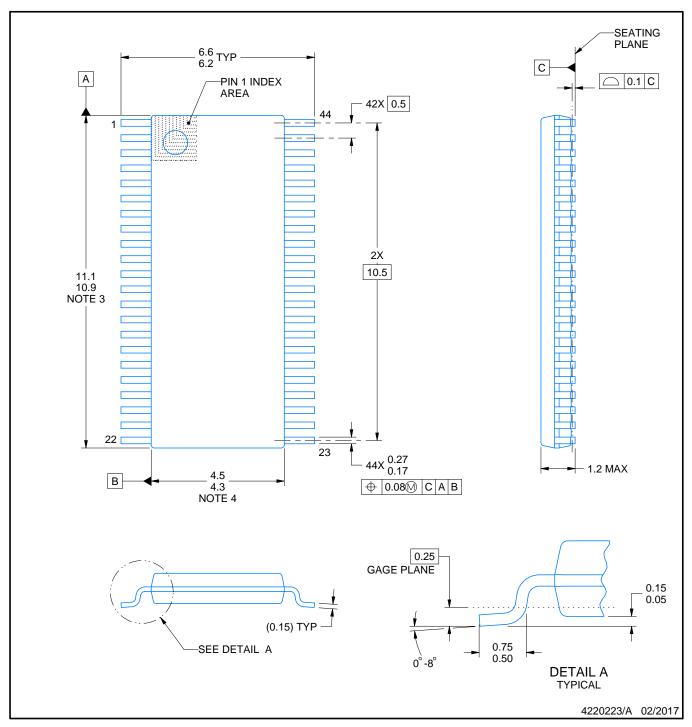

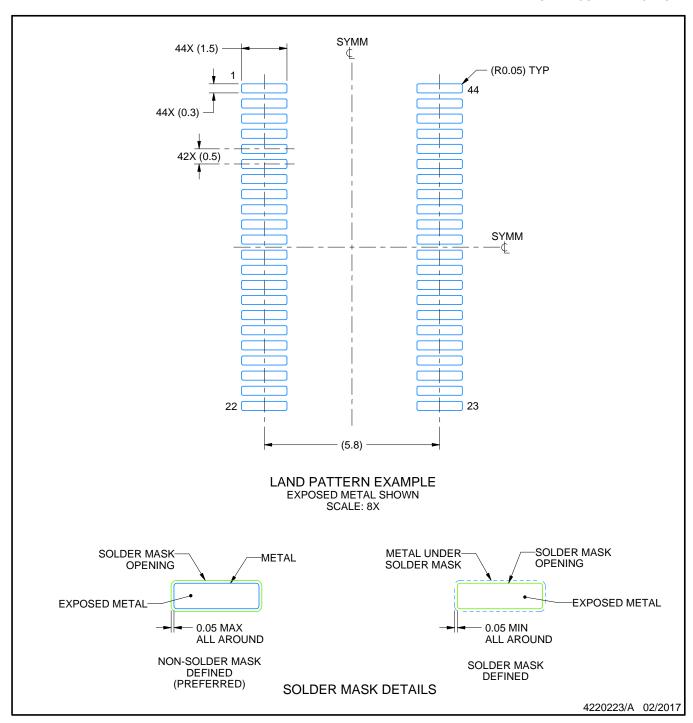

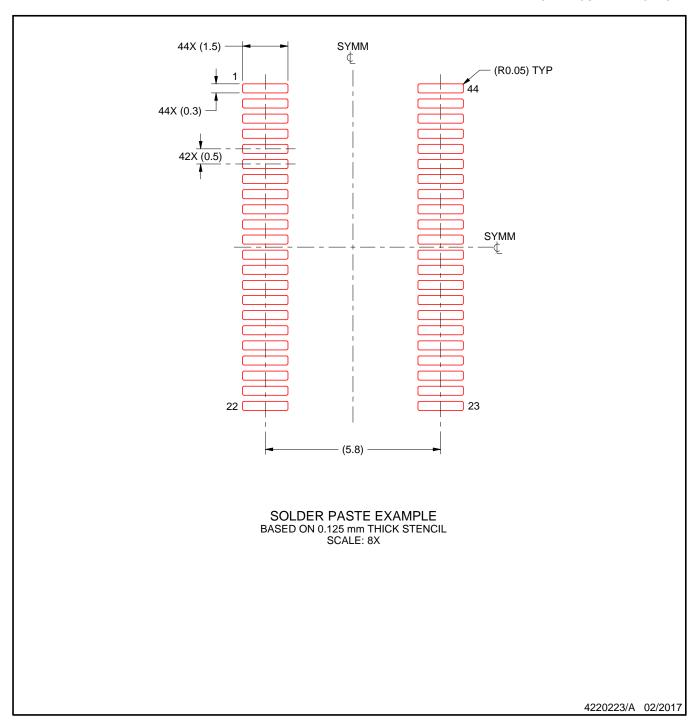

# **6.1 Versions**

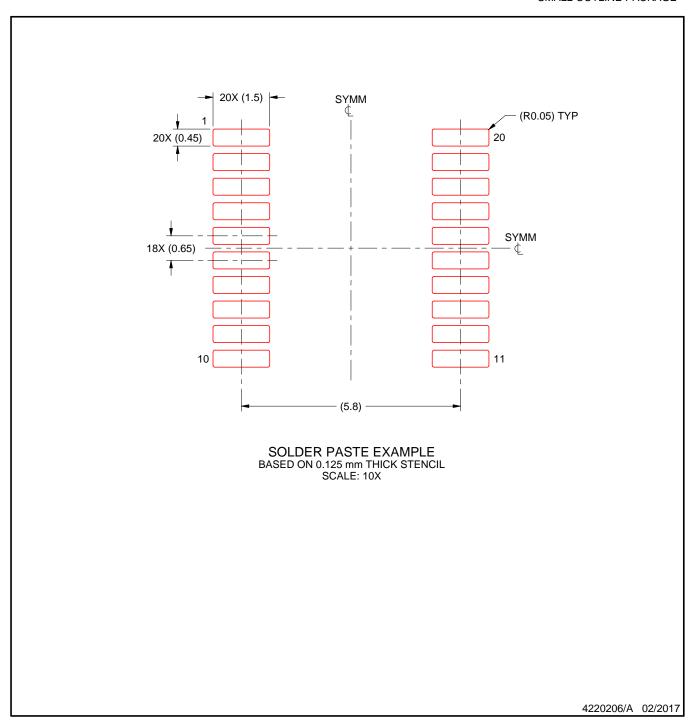

BQ76920: 3-5 Series Cells (20-TSSOP)

• 6.5 mm x 4.4 mm x 1.2 mm

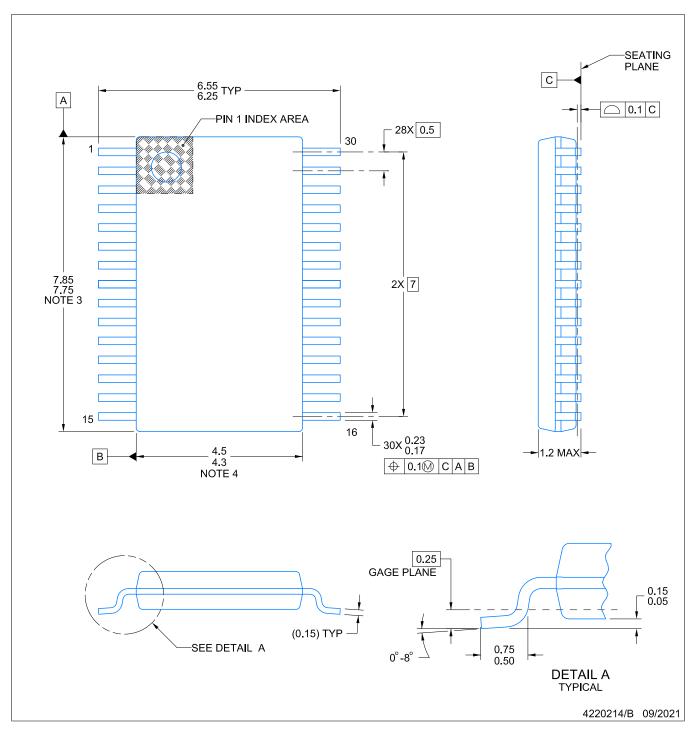

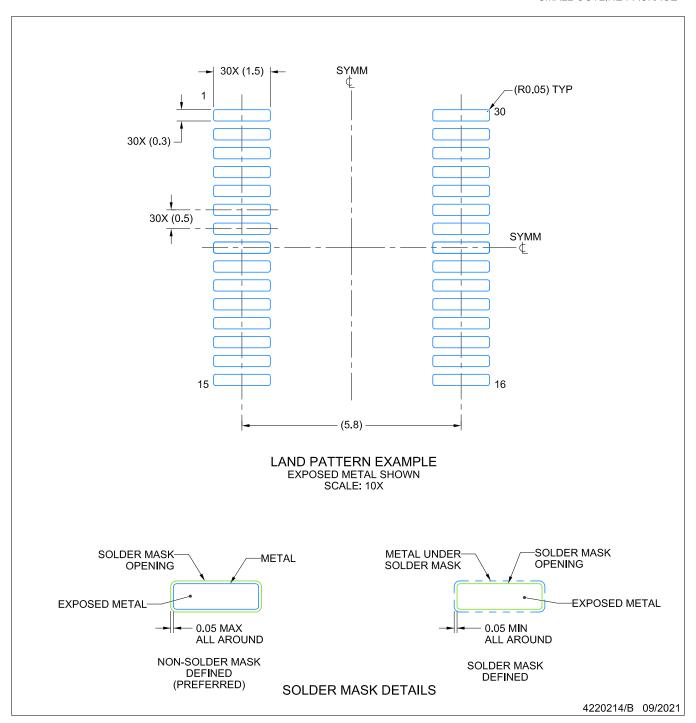

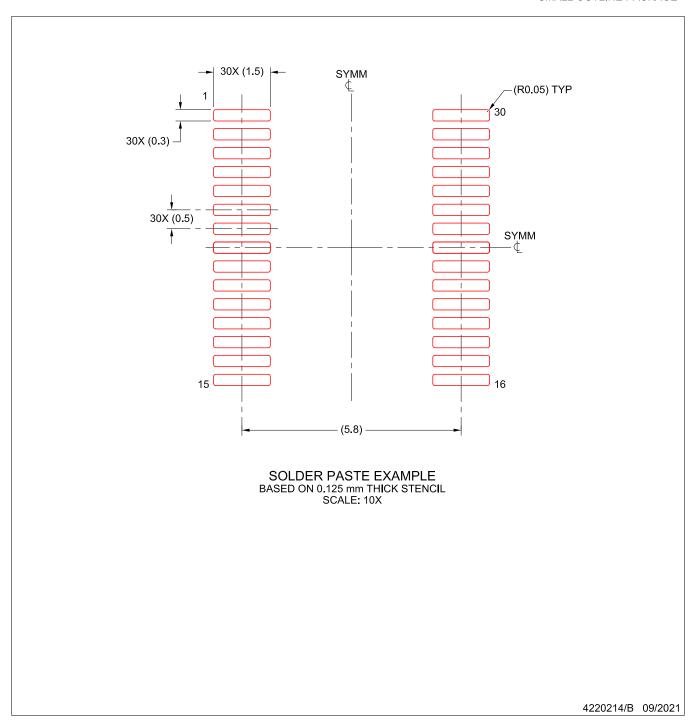

BQ76930: 6-10 Series Cells (30-TSSOP)

• 7.8 mm x 4.4 mm x 1.2 mm

BQ76940: 9-15 Series Cells (44-TSSOP)

• 11.3 mm x 4.4 mm x 1.2 mm

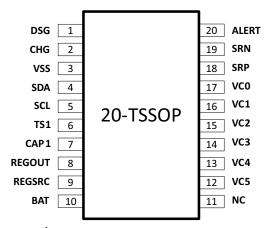

# 6.2 BQ76920 Pin Diagram

表 6-1. BQ76920 Pin Functions

| PIN | NAME   | TYPE | DESCRIPTION                                           |

|-----|--------|------|-------------------------------------------------------|

| 1   | DSG    | 0    | Discharge FET driver                                  |

| 2   | CHG    | 0    | Charge FET driver                                     |

| 3   | VSS    | _    | Chip VSS                                              |

| 4   | SDA    | I/O  | I <sup>2</sup> C communication to the host controller |

| 5   | SCL    | I    | I <sup>2</sup> C communication to the host controller |

| 6   | TS1    | I    | Thermistor #1 positive terminal <sup>(1)</sup>        |

| 7   | CAP1   | 0    | Capacitor to VSS                                      |

| 8   | REGOUT | Р    | Output LDO                                            |

| 9   | REGSRC | I    | Input source for output LDO                           |

| 10  | BAT    | Р    | Battery (top-most) terminal                           |

| 11  | NC     | _    | No connect                                            |

| 12  | VC5    | 1    | Sense voltage for 5th cell positive terminal          |

| 13  | VC4    | 1    | Sense voltage for 4th cell positive terminal          |

| 14  | VC3    | I    | Sense voltage for 3rd cell positive terminal          |

| 15  | VC2    | I    | Sense voltage for 2nd cell positive terminal          |

| 16  | VC1    | I    | Sense voltage for 1st cell positive terminal          |

| 17  | VC0    | 1    | Sense voltage for 1st cell negative terminal          |

| 18  | SRP    | I    | Negative current sense (nearest VSS)                  |

| 19  | SRN    | I    | Positive current sense                                |

| 20  | ALERT  | I/O  | Alert output and override input                       |

(1) If not used, pull down to VSS with a 10-k $\Omega$  nominal resistor.

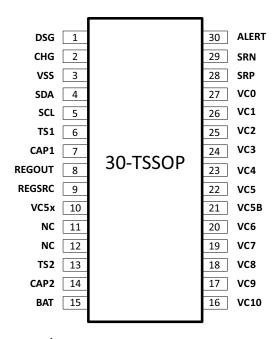

# 6.3 BQ76930 Pin Diagram

表 6-2. BQ76930 Pin Functions

| PIN | NAME   | TYPE | DESCRIPTION                                           |

|-----|--------|------|-------------------------------------------------------|

| 1   | DSG    | 0    | Discharge FET driver                                  |

| 2   | CHG    | 0    | Charge FET driver                                     |

| 3   | VSS    | _    | Chip VSS                                              |

| 4   | SDA    | I/O  | I <sup>2</sup> C communication to the host controller |

| 5   | SCL    | I    | I <sup>2</sup> C communication to the host controller |

| 6   | TS1    | I    | Thermistor #1 positive terminal <sup>(1)</sup>        |

| 7   | CAP1   | 0    | Capacitor to VSS                                      |

| 8   | REGOUT | Р    | Output LDO                                            |

| 9   | REGSRC | I    | Input source for output LDO                           |

| 10  | VC5X   | Р    | Thermistor #2 negative terminal                       |

| 11  | NC     | _    | No connect (short to CAP2)                            |

| 12  | NC     | _    | No connect (short to CAP2)                            |

| 13  | TS2    | I    | Thermistor #2 positive terminal <sup>(1)</sup>        |

| 14  | CAP2   | 0    | Capacitor to VC5X                                     |

| 15  | BAT    | Р    | Battery (top-most) terminal                           |

| 16  | VC10   | I    | Sense voltage for 10th cell positive terminal         |

| 17  | VC9    | I    | Sense voltage for 9th cell positive terminal          |

| 18  | VC8    | I    | Sense voltage for 8th cell positive terminal          |

| 19  | VC7    | I    | Sense voltage for 7th cell positive terminal          |

| 20  | VC6    | I    | Sense voltage for 6th cell positive terminal          |

| 21  | VC5B   | I    | Sense voltage for 6th cell negative terminal          |

| 22  | VC5    | I    | Sense voltage for 5th cell positive terminal          |

| 23  | VC4    | I    | Sense voltage for 4th cell positive terminal          |

| 24  | VC3    | I    | Sense voltage for 3rd cell positive terminal          |

| 25  | VC2    | I    | Sense voltage for 2nd cell positive terminal          |

| 26  | VC1    | l    | Sense voltage for 1st cell positive terminal          |

# 表 6-2. BQ76930 Pin Functions (continued)

| PIN | NAME  | TYPE | DESCRIPTION                                  |

|-----|-------|------|----------------------------------------------|

| 27  | VC0   | I    | Sense voltage for 1st cell negative terminal |

| 28  | SRP   | I    | Negative current sense (nearest VSS)         |

| 29  | SRN   | I    | Positive current sense                       |

| 30  | ALERT | I/O  | Alert output and override input              |

(1) If not used, pull down to group ground reference (VSS for TS1 and VC5X for TS2) with a  $10-k\Omega$  nominal resistor.

# 6.4 BQ76940 Pin Diagram

### **BQ76940 Pin Functions**

| PIN | NAME   | TYPE | DESCRIPTION                                           |  |  |

|-----|--------|------|-------------------------------------------------------|--|--|

| 1   | DSG    | 0    | Discharge FET driver                                  |  |  |

| 2   | CHG    | 0    | Charge FET driver                                     |  |  |

| 3   | VSS    |      | Chip VSS                                              |  |  |

| 4   | SDA    | I/O  | I <sup>2</sup> C communication to the host controller |  |  |

| 5   | SCL    | I    | I <sup>2</sup> C communication to the host controller |  |  |

| 6   | TS1    | I    | Thermistor #1 positive terminal <sup>(1)</sup>        |  |  |

| 7   | CAP1   | 0    | Capacitor to VSS                                      |  |  |

| 8   | REGOUT | Р    | Output LDO                                            |  |  |

| 9   | REGSRC | I    | Input source for output LDO                           |  |  |

| 10  | VC5X   | Р    | Thermistor #2 negative terminal                       |  |  |

| 11  | NC     |      | No connect (short to CAP2)                            |  |  |

| 12  | NC     |      | No connect (short to CAP2)                            |  |  |

# **BQ76940 Pin Functions (continued)**

| PIN | NAME  | TYPE | DESCRIPTION                                    |  |

|-----|-------|------|------------------------------------------------|--|

| 13  | TS2   | Į.   | Thermistor #2 positive terminal <sup>(1)</sup> |  |

| 14  | CAP2  | 0    | Capacitor to VC5X                              |  |

| 15  | VC10X | Р    | Thermistor #3 negative terminal                |  |

| 16  | NC    | _    | No connect (short to CAP3)                     |  |

| 17  | NC    | _    | No connect (short to CAP3)                     |  |

| 18  | TS3   | I    | Thermistor #3 positive terminal <sup>(1)</sup> |  |

| 19  | CAP3  | 0    | Capacitor to VC10X                             |  |

| 20  | BAT   | Р    | Battery (top-most) terminal                    |  |

| 21  | NC    | _    | No connect                                     |  |

| 22  | NC    | _    | No connect                                     |  |

| 23  | NC    | _    | No connect                                     |  |

| 24  | VC15  | I    | Sense voltage for 15th cell positive terminal  |  |

| 25  | VC14  | I    | Sense voltage for 14th cell positive terminal  |  |

| 26  | VC13  | I.   | Sense voltage for 13th cell positive terminal  |  |

| 27  | VC12  | I    | Sense voltage for 12th cell positive terminal  |  |

| 28  | VC11  | I    | Sense voltage for 11th cell positive terminal  |  |

| 29  | VC10B | I    | Sense voltage for 11th cell negative terminal  |  |

| 30  | VC10  | I    | Sense voltage for 10th cell positive terminal  |  |

| 31  | VC9   | I.   | Sense voltage for 9th cell positive terminal   |  |

| 32  | VC8   | I    | Sense voltage for 8th cell positive terminal   |  |

| 33  | VC7   | Į.   | Sense voltage for 7th cell positive terminal   |  |

| 34  | VC6   | I    | Sense voltage for 6th cell positive terminal   |  |

| 35  | VC5B  | I    | Sense voltage for 6th cell negative terminal   |  |

| 36  | VC5   | I.   | Sense voltage for 5th cell positive terminal   |  |

| 37  | VC4   | I    | Sense voltage for 4th cell positive terminal   |  |

| 38  | VC3   | Į.   | Sense voltage for 3rd cell positive terminal   |  |

| 39  | VC2   | I    | Sense voltage for 2nd cell positive terminal   |  |

| 40  | VC1   | I    | Sense voltage for 1st cell positive terminal   |  |

| 41  | VC0   | ı    | Sense voltage for 1st cell negative terminal   |  |

| 42  | SRP   | I    | Negative current sense (nearest VSS)           |  |

| 43  | SRN   | I    | Positive current sense                         |  |

| 44  | ALERT | I/O  | Alert output and override input                |  |

|     |       |      |                                                |  |

<sup>(1)</sup> If not used, pull down to group ground reference (VSS for TS1, VC5X for TS2, and VC10X for TS3) with a 10-k $\Omega$  nominal resistor.

# 7 Specifications

# 7.1 Absolute Maximum Ratings

Over-operating free-air temperature range (unless otherwise noted) (1)

|                  |                   |                                                                                                                                        |                                 | MIN  | MAX                                                                               | UNIT |

|------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------|-----------------------------------------------------------------------------------|------|

|                  |                   | (BAT-VSS)                                                                                                                              | BQ76920                         |      |                                                                                   |      |

| V <sub>BAT</sub> | Supply voltage    | (BAT-VC5x), (VC5x-VSS)                                                                                                                 | BQ76930                         | -0.3 | 3 36  (n × 7.2)  (n-5) × 7.2  (n-10) × 7.2  3 9  3 3.6  3 3.6  3 3.6  3 VCHGCLAMP | V    |

|                  |                   | (BAT-VC10x), (VC10x-VC5x), (VC5x-VSS)                                                                                                  | BQ76940                         |      |                                                                                   |      |

|                  |                   | (VCn–VSS) where n = 15                                                                                                                 | BQ76920,<br>BQ76930,<br>BQ76940 |      | (n × 7.2)                                                                         |      |

|                  |                   | (VCn-VC5x) where n = 610                                                                                                               | BQ76930,<br>BQ76940             | -0.3 | (n-5) × 7.2                                                                       | V    |

|                  |                   | (VCn–VC10x) where n = 1115                                                                                                             | BQ76940                         |      | ` ,                                                                               |      |

| V <sub>I</sub>   | Input voltage     | Cell input pins, differential (VCn–VCn–1) where n = 11 (BQ76940/BQ76930/BQ76920, respectively)                                         | 5/10/5                          | -0.3 | 9                                                                                 | V    |

| •                | input voltage     | SRN, SRP, SCL, SDA                                                                                                                     |                                 |      | 3.6                                                                               | V    |

|                  |                   | (VC0-VSS), (CAP1-VSS), (TS1-VSS) <sup>(2)</sup>                                                                                        | BQ76920                         |      |                                                                                   |      |

|                  |                   | (VC0-VSS), (VC5b-VC5x), (CAP2-VC5x), (CAP1-<br>VSS), (TS2-VC5x), (TS1-VSS) <sup>(2)</sup>                                              | BQ76930                         | -0.3 |                                                                                   |      |

|                  |                   | (VC0–VSS), (VC5b–VC5x), (VC10b–VC10x), (CAP3–<br>VC10x), (CAP2–VC5x), (CAP1–VSS), (TS3–VC10x),<br>(TS2–VC5x), (TS1–VSS) <sup>(2)</sup> | BQ76940                         |      |                                                                                   | ·    |

|                  |                   | REGSRC                                                                                                                                 |                                 | -0.3 | 36                                                                                |      |

|                  |                   | REGOUT, ALERT                                                                                                                          |                                 | -0.3 | 3.6                                                                               |      |

| Vo               | Output voltage    | DSG                                                                                                                                    |                                 | -0.3 | 20                                                                                | V    |

|                  |                   | CHG                                                                                                                                    |                                 | -0.3 | V <sub>CHGCLAMP</sub>                                                             |      |

|                  |                   | BQ76920 70 bil balancing current (per cell) BQ76930, BQ76940 5                                                                         |                                 | 7    | 0                                                                                 | mA   |

| I <sub>CB</sub>  | Cell balancing cu |                                                                                                                                        |                                 | 5    | mA                                                                                |      |

| I <sub>DSG</sub> | Discharge pin inp | out current when disabled (measured into terminal)                                                                                     |                                 | 7    | ,                                                                                 | mA   |

| т                | Storage tempera   | ture                                                                                                                                   |                                 | -65  | 150                                                                               | °C   |

| T <sub>STG</sub> | Lead temperature  | e (soldering, 10 s)                                                                                                                    |                                 |      | 300                                                                               | C    |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

## 7.2 ESD Ratings

|                    |               |                                                              | VALUE | UNIT |

|--------------------|---------------|--------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic | Human body model (HBM) ESD stress voltage <sup>(1)</sup>     | ±2    | kV   |

|                    | discharge     | Charged device model (CDM) ESD stress voltage <sup>(2)</sup> | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> The Absolute Maximum Ratings for (TS1–VSS) apply after the device completes POR and should be observed after t<sub>BOOTREADY</sub> (10 ms), following the application of the boot signal on TS1. Prior to completion of POR, TS1 should not exceed 5 V.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 7.3 Recommended Operating Conditions

Over-operating free-air temperature range (unless otherwise noted). See セクション 9.1.8 for more information on cell configurations. All voltages are relative to VSS, except "Cell input differential."

|                    |                                  |                                                                                                            |         | MIN  | TYP | MAX   | UNIT |

|--------------------|----------------------------------|------------------------------------------------------------------------------------------------------------|---------|------|-----|-------|------|

|                    |                                  | (BAT-VSS)                                                                                                  | BQ76920 |      |     |       |      |

| $V_{BAT}$          | Supply voltage                   | (BAT-VC5x), (VC5x-VSS)                                                                                     | BQ76930 | 6    |     | 25    | V    |

| V BAI              | Supply Voltage                   | (BAT–VC10x), (VC10x–VC5x),<br>(VC5x–VSS)                                                                   | BQ76940 | Ü    |     | 20    | v    |

|                    |                                  | Cell input pins, differential (VCn–VC<br>115/10/5 (BQ76940/BQ76930/BQ7<br>respectively), in-use cells only |         | 2    |     | 5     | V    |

|                    |                                  | (VCn–VSS) where n = 15                                                                                     | BQ76920 |      |     |       |      |

|                    |                                  | (VCn–VSS) where n = 15, (VCn–<br>VC5x) where n = 610                                                       | BQ76930 | 0    |     | 5 × n | V    |

|                    |                                  | (VCn–VSS) where n = 15, (VCn–<br>VC5x) where n = 610, (VCn–<br>VC10x) where n = 1115                       | BQ76940 |      |     |       | •    |

|                    |                                  | SRP                                                                                                        |         |      |     |       |      |

| V <sub>IN</sub>    | Input voltage                    | (VC0-VSS)                                                                                                  | BQ76920 |      |     |       |      |

| V IN               | input voltage                    | (VC0-VSS), (VC5b-VC5x)                                                                                     | BQ76930 | -10  |     | 10    | mV   |

|                    |                                  | (VC0–VSS), (VC5b–VC5x),<br>(VC10b–VC10x)                                                                   | BQ76940 |      |     |       |      |

|                    |                                  | SRN                                                                                                        |         | -200 |     | 200   | mV   |

|                    |                                  | SCL, SDA                                                                                                   |         |      |     |       |      |

|                    |                                  | (TS1-VSS)                                                                                                  | BQ76920 |      |     | 3.6   |      |

|                    |                                  | (TS1-VSS), (TS2-VC5x)                                                                                      | BQ76930 | 0    |     |       | V    |

|                    |                                  | (TS1-VSS), (TS2-VC5x), (TS3-<br>VC10x)                                                                     | BQ76940 |      |     |       | ·    |

|                    |                                  | REGSRC                                                                                                     |         | 6    |     | 25    |      |

|                    |                                  | CHG, DSG                                                                                                   |         | 0    |     | 16    | V    |

|                    |                                  | REGOUT, ALERT                                                                                              |         | ,    |     |       |      |

| V <sub>OUT</sub>   | Output voltage                   | (CAP1-VSS)                                                                                                 | BQ76920 |      |     |       |      |

| *001               | Output Voltago                   | (CAP1-VSS), (CAP2-VC5x)                                                                                    | BQ76930 | 0    |     | 3.6   | V    |

|                    |                                  | (CAP1–VSS), (CAP2–VC5x),<br>(CAP3–VC10x)                                                                   | BQ76940 |      |     |       |      |

|                    | Cell balancing                   | BQ76920                                                                                                    |         | 0    |     | 50    | mA   |

| I <sub>CB</sub>    | current (internal, per cell)     | BQ76930, BQ76940                                                                                           | )       | 0    |     | 5     | mA   |

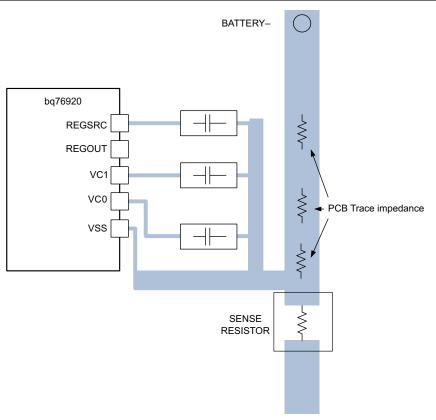

| R <sub>C</sub>     | External cell input              | BQ76920                                                                                                    |         | 40   | 100 | 1K    | Ω    |

| K <sub>C</sub>     | resistance                       | BQ76930, BQ76940                                                                                           | )       | 500  | 1K  | 1K    | Ω    |

| C <sub>C</sub>     | External cell input cap          | pacitance                                                                                                  |         | 0.1  | 1   | 10    | μF   |

| R <sub>f</sub>     | External supply filter r         | resistance                                                                                                 |         | 40   | 100 | 1K    | Ω    |

| C <sub>f</sub>     | External supply filter           | capacitance                                                                                                |         | 1    | 10  | 40    | μF   |

| R <sub>FILT</sub>  | Sense resistor filter resistance |                                                                                                            |         | 100  | 1K  |       | Ω    |

| R <sub>ALERT</sub> | ALERT pin to VSS res             | sistor                                                                                                     |         |      | 1M  |       | Ω    |

| CL                 | REGOUT loading cap               | REGOUT loading capacitance                                                                                 |         |      |     |       | μF   |

| C <sub>CAP</sub>   | REGSRC, CAP1, CA                 | P2, and CAP3 output capacitance                                                                            |         | 1    |     |       | μF   |

| R <sub>TS</sub>    | External thermistor no           | ominal resistance (103AT) at 25°C                                                                          |         | 10K  |     |       | Ω    |

| T <sub>OPR</sub>   | Operating free-air ten           | nperature                                                                                                  |         | -40  |     | 85    | °C   |

## 7.4 Thermal Information

Over-operating free-air temperature range (unless otherwise noted)

|                          |                                              |                           | TSSOP                      |                            |      |

|--------------------------|----------------------------------------------|---------------------------|----------------------------|----------------------------|------|

|                          | THERMAL METRIC <sup>(1)</sup>                | BQ76920xy<br>20 PINS (PW) | BQ76930xy<br>30 PINS (DBT) | BQ76940xy<br>44 PINS (DBT) | UNIT |

| R <sub>0JA, High K</sub> | Junction-to-ambient thermal resistance       | 93.7                      | 86.5                       | 70.1                       | °C/W |

| R <sub>0JC(top)</sub>    | Junction-to-case(top) thermal resistance     | 28.7                      | 19.4                       | 17.5                       | °C/W |

| R <sub>0JB</sub>         | Junction-to-board thermal resistance         | 44.6                      | 41.3                       | 33.9                       | °C/W |

| ΨЈТ                      | Junction-to-top characterization parameter   | 1.3                       | 0.5                        | 0.5                        | °C/W |

| ΨЈВ                      | Junction-to-board characterization parameter | 44.1                      | 40.6                       | 33.4                       | °C/W |

| $R_{\theta JC(bottom)}$  | Junction-to-case(bottom) thermal resistance  | n/a                       | n/a                        | n/a                        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics Application Report (SPRA953).

## 7.5 Electrical Characteristics

Typical conditions are measured at 25°C with nominal BAT voltages of 18 V (BQ76920), 36 V (BQ76930), or 48 V (BQ76940) with  $V_{CELL}$  = 4 V. Min and max values include full recommended operating condition temperature range from -40°C to +85°C. Certain characteristics may be shown at different voltage or temperature ranges, as clarified in the Test Condition sections.

|                         | PARAMETER                                                                          | TEST CONDITION                                                           | MIN        | TYP  | MAX | UNIT |

|-------------------------|------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------|------|-----|------|

| SUPPLY CUR              | RENTS                                                                              |                                                                          |            |      |     |      |

|                         | NORMAL mode: ADC off, CC off                                                       |                                                                          |            | 40   | 60  |      |

| ı                       | NORMAL mode: ADC on, CC off                                                        | Sum of ICC_BAT and ICC_REGSRC                                            |            | 60   | 90  |      |

| I <sub>DD</sub>         | NORMAL mode: ADC off, CC on                                                        | currents                                                                 |            | 110  | 165 |      |

|                         | NORMAL mode: ADC on, CC on                                                         |                                                                          |            | 130  | 195 | μA   |

| 1                       | NORMAL mode: ADC off                                                               | Into DAT nin                                                             | ,          | 30   | 45  |      |

| I <sub>CC_BAT</sub>     | NORMAL mode: ADC on                                                                | Into BAT pin                                                             |            | 50   | 75  |      |

|                         | NORMAL mode: CC off                                                                | Into REGSRC pin                                                          |            | 10   | 15  |      |

| I <sub>CC_REGSRC</sub>  | NORMAL mode: CC on                                                                 |                                                                          |            | 80   | 120 |      |

| I <sub>SHIP</sub>       | SHIP/SHUTDOWN mode                                                                 | Device in full shutdown, only VSTUP/BG and BOOT detector on              |            | 0.6  | 1.8 |      |

| LEAKAGE AN              | ID OFFSET CURRENTS                                                                 |                                                                          |            |      |     |      |

| dl <sub>NOM</sub>       | NORMAL mode supply current offset                                                  | Measured into VC5x (BQ76930.                                             | <b>–</b> 5 | ±2.5 | 5   |      |

| dl <sub>SHIP</sub>      | SHIP mode supply current offset                                                    | BQ76940) and VC10x (BQ76940)                                             | -1.0       | ±0.1 | 1.0 |      |

| dl <sub>ALERT</sub>     | Supply current when ALERT active                                                   | Measured into VC5x (BQ76930,<br>BQ76940) or added to BAT (BQ76920)       |            | 15   | 25  | μΑ   |

| dl <sub>CELL</sub>      | Cell measurement input                                                             | Measured into VC0–VC15 except VC5, VC10, VC15                            | -0.3       | ±0.1 | 0.3 |      |

|                         | current                                                                            | Measured into VC5, VC10, VC15                                            |            |      | 0.5 |      |

| I <sub>LKG</sub>        | Terminal input leakage                                                             |                                                                          |            |      | 1   |      |

| INTERNAL PO             | OWER CONTROL (STARTUP &                                                            | and SHUTDOWN)                                                            |            |      |     |      |

| V <sub>PORA</sub>       | Analog POR threshold                                                               | V <sub>BAT</sub> rising. See <sup>(4)</sup> .                            | 4          |      | 5   | V    |

| V <sub>SHUT</sub>       | Shutdown voltage                                                                   | V <sub>BAT</sub> falling. See <sup>(4)</sup> .                           |            |      | 3.6 | V    |

| t <sub>I2CSTARTUP</sub> | Time delay after boot signal on TS1 before I <sup>2</sup> C communications allowed | Delay after boot sequence when I <sup>2</sup> C communication is allowed |            | 1    |     | ms   |

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

# 7.5 Electrical Characteristics (continued)

Typical conditions are measured at 25°C with nominal BAT voltages of 18 V (BQ76920), 36 V (BQ76930), or 48 V (BQ76940) with  $V_{CELL}$  = 4 V. Min and max values include full recommended operating condition temperature range from -40°C to +85°C. Certain characteristics may be shown at different voltage or temperature ranges, as clarified in the Test Condition sections.

|                         | PARAMETER                                                   | TEST CONDITION                                                          | MIN  | TYP    | MAX    | UNIT     |

|-------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------|------|--------|--------|----------|

| t <sub>BOOTREADY</sub>  | Device boot startup delay                                   | Delay after boot signal when device has completed full boot-up sequence |      |        | 10     | ms       |

| T <sub>SHUTD</sub>      | Thermal shutdown voltage                                    |                                                                         |      | 100    | 150    | °C       |

| MEASUREME               | NT SCHEDULE                                                 |                                                                         |      |        |        |          |

| t <sub>VCELL</sub>      | Cell voltage measurement interval                           | BQ76920, BQ76930, BQ76940                                               |      | 250    |        |          |

|                         | Individual cell                                             | Per cell, balancing off                                                 |      | 50     |        |          |

| INDCELL                 | measurement time                                            | Per cell, balancing on                                                  |      | 12.5   |        |          |

| CB_RELAX                | Cell balancing relaxation time before cell voltage measured |                                                                         |      | 12.5   |        | ms       |

| TEMP_DEC                | Temperature measurement decimation time                     | Measurement duration for temperature reading                            |      | 12.5   |        |          |

| t <sub>BAT</sub>        | Pack voltage calculation interval                           |                                                                         |      | 250    |        |          |

| t <sub>TEMP</sub>       | Temperature measurement interval                            | Period of measurement of either TS1/TS2/TS3 or internal die temp        |      | 2      |        | s        |

| 14-BIT ADC F            | OR CELL VOLTAGE AND TEN                                     | IPERATURE MEASUREMENT                                                   |      |        |        |          |

| 400                     | ADC measurement                                             | V <sub>CELL</sub> measurements                                          | 2    |        | 5      | V        |

| ADC <sub>RANGE</sub>    | recommend operation range                                   | TS/Temp measurements                                                    | 0.3  |        | 3      | V        |

| ADC <sub>LSB</sub>      | ADC LSB value                                               |                                                                         |      | 382    |        | μV       |

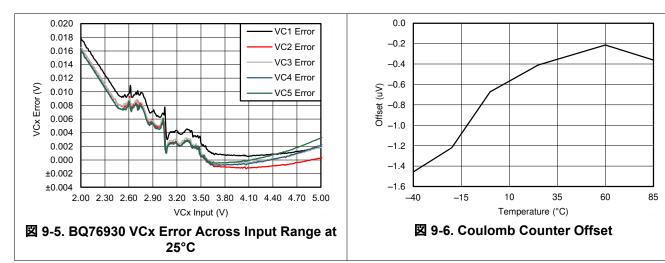

|                         | ADC cell welters comment                                    | V <sub>CELL</sub> = 3.6 V – 4.3 V                                       |      | ±10    |        |          |

|                         | ADC cell voltage accuracy at 25°C                           | V <sub>CELL</sub> = 3.2 V – 4.6 V                                       |      | ±15    |        |          |

|                         |                                                             | V <sub>CELL</sub> = 2.0 V – 5.0 V                                       |      | ±25    |        |          |

|                         |                                                             | V <sub>CELL</sub> = 3.6 V – 4.3 V                                       |      | ±20    |        |          |

| ADC                     | ADC cell voltage accuracy 0°C to 60°C                       | V <sub>CELL</sub> = 3.2 V – 4.6 V                                       |      | ±25    |        | mV       |

|                         |                                                             | V <sub>CELL</sub> = 2.0 V – 5.0 V                                       |      | ±35    |        |          |

|                         |                                                             | V <sub>CELL</sub> = 3.6 V – 4.3 V                                       | -40  |        | 40     |          |

|                         | ADC cell voltage accuracy –40°C to 85°C                     | V <sub>CELL</sub> = 3.2 V – 4.6 V                                       | -40  |        | 40     |          |

|                         | 10 0 10 00 0                                                | V <sub>CELL</sub> = 2.0 V – 5.0 V                                       | -50  |        | 50     |          |

| 16-BIT CC FO            | R PACK CURRENT MEASURI                                      | EMENT                                                                   |      |        | '      |          |

| CC <sub>RANGE</sub>     | CC input voltage range                                      |                                                                         | -200 |        | 200    | mV       |

| CC <sub>FSR</sub>       | CC full scale range                                         |                                                                         | -270 |        | 270    | mV       |

| CC <sub>LSB</sub>       | CC LSB value                                                | CC running constantly                                                   |      | 8.44   |        | μV       |

| CC <sub>READ</sub>      | Conversion time                                             | Single conversion                                                       | ,    | 250    |        | ms       |

| CC <sub>INL</sub>       | Integral nonlinearity                                       | 16-bit, best fit over input voltage range ± 200 mV                      |      | ± 2    | ± 40   | LSB      |

| CC <sub>OFFSET</sub>    | Offset error                                                |                                                                         |      | ± 1    | ± 3    | LSB      |

| CC <sub>GAIN</sub>      | Gain error                                                  | Over input voltage range                                                | ,    | ± 0.5% | ± 1.5% | FSR      |

| CC <sub>GAINDRIFT</sub> | Gain error drift                                            | Over input voltage range                                                | ,    |        | 150    | PPM / °C |

| CC <sub>RIN</sub>       | Effective input resistance                                  |                                                                         |      | 2.5    |        | ΜΩ       |

| THERMISTOR              | RBIAS                                                       |                                                                         |      |        |        |          |

| R <sub>TS</sub>         | Pull-up resistance                                          | T <sub>A</sub> = 25°C                                                   | 9.85 | 10     | 10.15  | kΩ       |

| R <sub>TSDRIFT</sub>    | Pull-up resistance across temp                              | T <sub>A</sub> = -40°C to 85°C                                          | 9.7  |        | 10.3   | kΩ       |

# 7.5 Electrical Characteristics (continued)

Typical conditions are measured at 25°C with nominal BAT voltages of 18 V (BQ76920), 36 V (BQ76930), or 48 V (BQ76940) with  $V_{CELL}$  = 4 V. Min and max values include full recommended operating condition temperature range from -40°C to +85°C. Certain characteristics may be shown at different voltage or temperature ranges, as clarified in the Test Condition sections.

|                           | PARAMETER                     | TEST CONDITION                                                                                          | MIN      | TYP      | MAX    | UNIT  |

|---------------------------|-------------------------------|---------------------------------------------------------------------------------------------------------|----------|----------|--------|-------|

| DIETEMP                   |                               |                                                                                                         |          |          |        |       |

| V <sub>DIETEMP25</sub>    | Die temperature voltage       | T <sub>A</sub> = 25°C                                                                                   |          | 1.20     |        | V     |

| V <sub>DIETEMPDRIFT</sub> | Die temperature voltage drift |                                                                                                         |          | -4.2     |        | mV/°C |

| INTEGRATED                | HARDWARE PROTECTIONS          |                                                                                                         |          |          |        |       |

| OV <sub>RANGE</sub>       | OV threshold range            |                                                                                                         | 0x2008   |          | 0x2FF8 | ADC   |

| UV <sub>RANGE</sub>       | UV threshold range            |                                                                                                         | 0x1000   |          | 0x1FF0 | ADC   |

| OV <sub>UVSTEP</sub>      | OV and UV threshold step size |                                                                                                         |          | 16       |        | LSB   |

| UV <sub>MINQUAL</sub>     | UV minimum value to qualify   | Below UV <sub>MINQUAL</sub> , the cell is shorted (unused)                                              |          | 0x0518   |        | ADC   |

|                           |                               | OV delay = 1 s                                                                                          | 0.7      | 1        | 1.75   |       |

|                           |                               | OV delay = 2 s                                                                                          | 1.6      | 2        | 2.75   | S     |

| $OV_{DELAY}$              | OV delay timer options        | OV delay = 4 s                                                                                          | 3.5      | 4        | 5      |       |

|                           |                               | OV delay = 8 s                                                                                          | 7        | 8        | 10     |       |

|                           |                               | UV delay = 1 s                                                                                          | 0.7      | 1        | 1.75   |       |

|                           |                               | UV delay = 4 s                                                                                          | 3.5      | 4        | 5      |       |

| UV <sub>DELAY</sub>       | UV delay timer options        | UV delay = 8 s                                                                                          | 7        | 8        | 10     |       |

|                           |                               | UV delay = 16 s                                                                                         | 14       | 16       | 20     |       |

| OCD <sub>RANGE</sub>      | OCD threshold options         | Measured across (SRP–SRN) <sup>(2)</sup>                                                                | 8        |          | 100    | mV    |

|                           |                               | RSNS = 0                                                                                                |          | 2.78     |        | mV    |

| OCD <sub>STEP</sub>       | OCD threshold step size       | RSNS = 1                                                                                                |          | 5.56     |        | mV    |

| OCD <sub>DELAY</sub>      | OCD delay options             | See Note <sup>(3)</sup>                                                                                 | 8        |          | 1280   | ms    |

| SCD <sub>RANGE</sub>      | SCD threshold options         | Measured across (SRP–SRN) <sup>(2)</sup>                                                                | 22       |          | 200    | mV    |

|                           |                               | RSNS = 0                                                                                                |          | 11.1     |        | mV    |

| SCD <sub>STEP</sub>       | SCD threshold step size       | RSNS = 1                                                                                                |          | 22.2     |        | mV    |

|                           |                               |                                                                                                         | 35       | 70       | 105    | μs    |

|                           | 000 11 11                     |                                                                                                         | 50       | 100      | 150    | μs    |

| SCD <sub>DELAY</sub>      | SCD delay options             |                                                                                                         | 140      | 200      | 260    | μs    |

|                           |                               |                                                                                                         | 280      | 400      | 520    | μs    |

| t <sub>PROTACC</sub>      | Delay accuracy for OCD        |                                                                                                         | -20%     |          | 20%    |       |

| OC <sub>OFFSET</sub>      | OCD and SCD voltage offset    |                                                                                                         | -2.5     |          | 2.5    | mV    |

| OC <sub>SCALEERR</sub>    | OCD and SCD scale accuracy    |                                                                                                         | -10%     |          | 10%    |       |

| CHARGE AND                | DISCHARGE DRIVERS             |                                                                                                         |          |          |        |       |

| W                         | CHC and DSC an                | REGSRC $\geq$ 12 V with load resistance of 10 M $\Omega$                                                | 10       | 12       | 14     | V     |

| V <sub>FETON</sub>        | CHG and DSG on                | REGSRC < 12 V with load resistance of 10 $M\Omega$                                                      | REGSRC – | REGSRC – | REGSRC | V     |

| t <sub>FET_ON</sub>       | CHG and DSG ON rise time      | CHG/DSG driving an equivalent load capacitance of 10 nF, measured from 10% to 90% of V <sub>FETON</sub> |          | 200      | 250    | μs    |

| t <sub>DSG_OFF</sub>      | DSG pull-down OFF fall time   | DSG driving an equivalent load capacitance of 10 nF, measured from 90% to 10%                           |          | 60       | 90     | μs    |

# 7.5 Electrical Characteristics (continued)

Typical conditions are measured at 25°C with nominal BAT voltages of 18 V (BQ76920), 36 V (BQ76930), or 48 V (BQ76940) with  $V_{CELL}$  = 4 V. Min and max values include full recommended operating condition temperature range from -40°C to +85°C. Certain characteristics may be shown at different voltage or temperature ranges, as clarified in the Test Condition sections.

|                           | PARAMETER                                          | TEST CONDITION                                                                                                                         | MIN              | TYP  | MAX              | UNIT |

|---------------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------------------|------|------------------|------|

| R <sub>CHG_OFF</sub>      | CHG pull-down OFF resistance to VSS                | When CHG disabled, CHG held at 12 V                                                                                                    | 750              | 1000 | 1250             | kΩ   |

| R <sub>DSG_OFF</sub>      | DSG pull-down OFF resistance to VSS                | When DSG disabled, DSG held at 12 V                                                                                                    | 1.75             | 2.50 | 4.25             | kΩ   |

| V <sub>LOAD_DETECT</sub>  | Load detection threshold                           |                                                                                                                                        | 0.4              | 0.7  | 1.0              | V    |

| V <sub>CHG_CLAMP</sub>    | CHG clamp voltage                                  | If the CHG pin externally pulled high (through PACK–, if load applied), 500-μA max sink current into CHG pin. With CHG_ON bit cleared. | 18               | 20   | 22               | V    |

| ALERT PIN                 |                                                    |                                                                                                                                        |                  |      |                  |      |

| V <sub>ALERT_OH</sub>     | ALERT output voltage high                          | I <sub>OL</sub> = 1 mA                                                                                                                 | REGOUT x<br>0.75 |      |                  | V    |

| V <sub>ALERT_OL</sub>     | ALERT output voltage low                           | Unloaded                                                                                                                               |                  |      | REGOUT<br>x 0.25 | V    |

| V <sub>ALERT_IH</sub>     | ALERT input high                                   | ALERT externally forced high when internally driven low. See note <sup>(1)</sup> .                                                     | 1                |      | 1.5              | V    |

| R <sub>ALERT_PD</sub>     | ALERT pin weak pulldown resistance when driven low | Measured into ALERT pin with ALERT = REGOUT                                                                                            | 0.8              | 2.5  | 8                | МΩ   |

| CELL BALANC               | CING DRIVER                                        |                                                                                                                                        |                  |      | •                |      |

| R <sub>DSFET</sub>        | Internal cell balancing driver resistance          | V <sub>CELL</sub> = 3.6 V                                                                                                              | 1                | 5    | 10               | Ω    |

| X <sub>BAL</sub>          | Cell balancing duty cycle when enabled             | Every 250 ms                                                                                                                           |                  | 70%  |                  |      |

| EXTERNAL RE               | EGULATOR                                           |                                                                                                                                        |                  |      |                  |      |

|                           | External LDO voltage                               | Nominal values, TI factory programmed,                                                                                                 | 2.45             | 2.50 | 2.55             | V    |

| V <sub>EXTLDO</sub>       | options                                            | unloaded, across temp                                                                                                                  | 3.20             | 3.30 | 3.40             | V    |

| V <sub>EXTLDO_LN</sub>    | Line regulation                                    | REGSRC pin stepped from 6 to 25 V, with 10-mA load, in 100 μs                                                                          |                  |      | 100              | mV   |

| V <sub>EXTLDO_LD</sub>    | Load regulation                                    | I <sub>REGOUT</sub> = 0 mA to 10 mA                                                                                                    | -4%              |      | 4%               |      |

|                           |                                                    | REGOUT = 10-mA DC, 2.5-V version                                                                                                       | 2.4              |      |                  | V    |

| V                         | External LDO minimum                               | REGOUT = 20-mA DC, 2.5-V version                                                                                                       | 2.3              |      |                  | V    |

| V <sub>EXTLDO_DC</sub>    | voltage under DC load                              | REGOUT = 10-mA DC, 3.3-V version                                                                                                       | 3.15             |      |                  | V    |

|                           |                                                    | REGOUT = 20-mA DC, 3.3-V version                                                                                                       | 3.05             |      |                  | V    |

| I <sub>EXTLDO_LIMIT</sub> | External LDO current limit                         | REGOUT = 0 V                                                                                                                           | 30               | 38   | 45               | mA   |

| BOOT DETEC                | TOR                                                |                                                                                                                                        |                  |      | "                |      |

| V <sub>BOOT</sub>         | Boot threshold voltage                             | Measured at TS1 pin with device in SHIP mode. Below MIN, the device does not boot up. Above MAX, the device boots up.                  | 300              |      | 1000             | mV   |

| t <sub>BOOT_max</sub>     | Boot threshold application time                    | Measured at TS1 pin. Below MIN, the device does not boot up. Above MAX, the device boots up.                                           | 10               |      | 2000             | μs   |

<sup>(1)</sup> MIN specifies the threshold below which the device will never register that an external alert has occurred. MAX specifies the minimum threshold above which the device will always register that an external alert has occurred.

<sup>(2)</sup> Values indicate nominal thresholds only. For min and max variation, apply OC<sub>OFFSET</sub> and OC<sub>SCALERR</sub>.

<sup>(3)</sup> Values indicate nominal thresholds only. For min and max variation, apply terror thresholds only.

<sup>(4)</sup> Measured at each V<sub>BAT</sub>

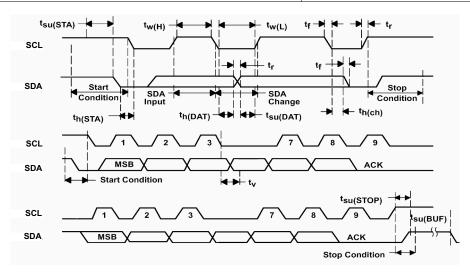

# 7.6 Timing Requirements

|                     | I <sup>2</sup> C COMPATIBLE INTERFACE                                | MIN              | TYP MAX          | UNIT |

|---------------------|----------------------------------------------------------------------|------------------|------------------|------|

| V <sub>IL</sub>     | Input low logic threshold                                            |                  | REGOUT x<br>0.25 | V    |

| V <sub>IH</sub>     | Input high logic threshold                                           | REGOUT x<br>0.75 |                  | V    |

| V <sub>OL</sub>     | Output low logic drive                                               |                  | 0.20             | V    |

| t <sub>f</sub>      | SCL, SDA fall time                                                   |                  | 0.40             |      |

| V <sub>OH</sub>     | Output high logic drive (not applicable due to open-drain outputs)   | N/A              | N/A              | V    |

| t <sub>HIGH</sub>   | SCL pulse width high                                                 | 4.0              |                  | μs   |

| t <sub>LOW</sub>    | SCL pulse width low                                                  | 4.7              |                  | μs   |

| t <sub>SU;STA</sub> | Setup time for START condition                                       | 4.7              |                  | μs   |

| t <sub>HD;STA</sub> | START condition hold time after which first clock pulse is generated | 4.0              |                  | μs   |

| t <sub>SU;DAT</sub> | Data setup time                                                      | 250              |                  | ns   |

| t <sub>HD;DAT</sub> | Data hold time                                                       | 0                |                  | μs   |

| t <sub>SU;STO</sub> | Setup time for STOP condition                                        | 4.0              |                  | μs   |

| t <sub>BUF</sub>    | Time the bus must be free before new transmission can start          | 4.7              |                  | μs   |

| t <sub>VD;DAT</sub> | Clock low to data out valid                                          |                  | 900              | ns   |

| t <sub>HD;DAT</sub> | Data out hold time after clock low                                   | 0                |                  | ns   |

| f <sub>SCL</sub>    | Clock frequency                                                      | 0                | 100              | kHz  |

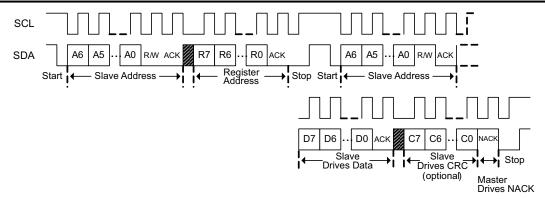

図 7-1. I<sup>2</sup>C Timing

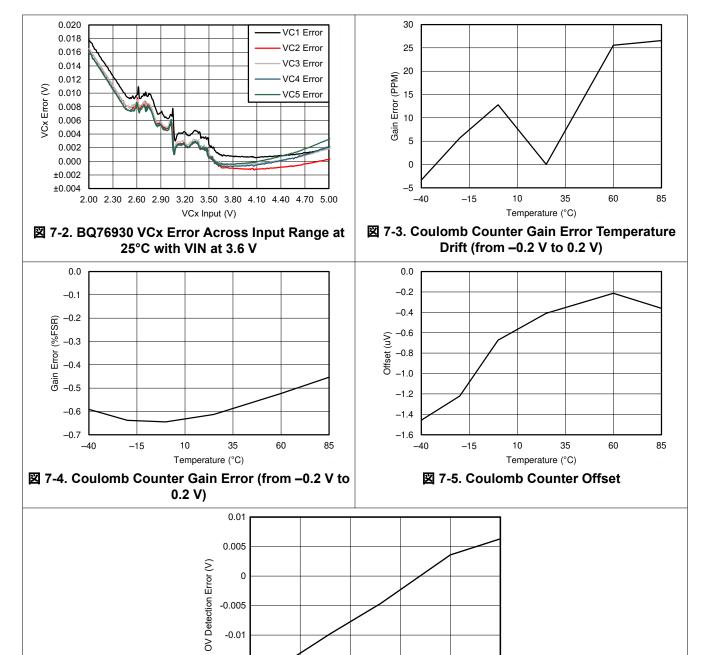

# 7.7 Typical Characteristics

-0.015

10 35 Temperature (°C)

図 7-6. OV Protection Detection Error (0xFF Setting)

# 8 Detailed Description

## 8.1 Overview

In the BQ769x0 family of analog front-end (AFE) devices, the BQ76920 device supports up to 5-series cells, the BQ76930 device supports up to 10-series cells, and the BQ76940 device supports up to 15-series cells. Through I<sup>2</sup>C, a host controller can use the BQ769x0 to implement battery pack management functions, such as monitoring (cell voltages, pack current, pack temperatures), protection (controlling charge/discharge FETs), and balancing. Integrated A/D converters enable a purely digital readout of critical system parameters including cell voltages and internal or external temperature, with calibration handled in TI's manufacturing process. For an additional degree of pack reliability, the BQ769x0 includes hardware protections for voltage (OV, UV) and current (OCD, SCD).

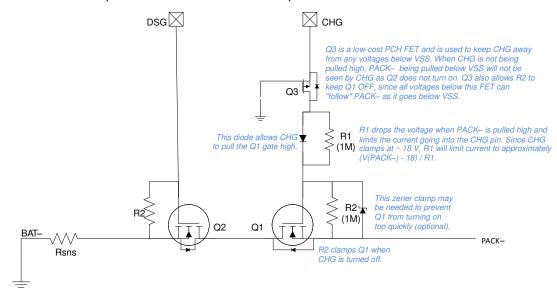

The BQ769x0 provides two low-side FET drivers, charge (CHG) and discharge (DSG), which may be used to directly manipulate low-side power NCH FETs, or as signals that control an external circuit that enables high-side PCH or NCH FETs. A dedicated ALERT input/output pin serves as an interrupt signal to the host microcontroller, quickly informing the microcontroller of an updated status in the AFE. This may include a fault event or that a coulomb counter sample is available for reading. An available ALERT pin may also be driven externally by a secondary protector to provide a redundant means of disabling the CHG and DSG signals and higher system visibility.

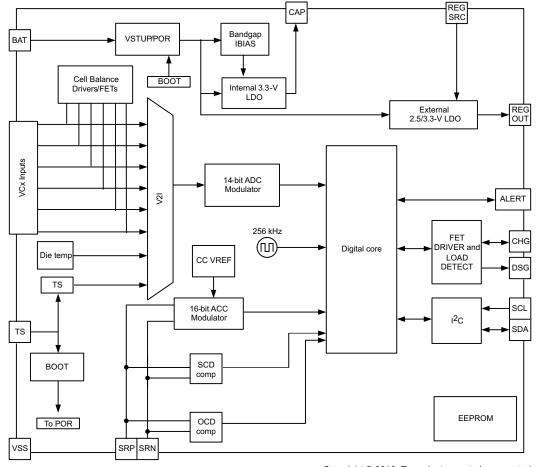

# 8.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

## 8.3 Feature Description

### 8.3.1 Subsystems

BQ769x0 consists of three major subsystems: Measurement, Protection, and Control. These work together to ensure that the fundamental battery pack parameters—voltage, current and temperature—are accurately captured and easily available to a host controller, while ensuring a baseline or secondary level of hardware protection in the event that a host controller is unable or unavailable to manage certain fault conditions.

#### **Note**

The BQ769x0 is intended to serve as an analog front-end (AFE) as part of a chipset system solution: A companion microcontroller is required to oversee and control this AFE.

- The Measurement subsystem's core responsibility is to digitize the cell voltages, pack current (integrated into a passed charge calculation), external thermistor temperature, and internal die temperature. It also performs an automatic calculation of the total battery stack voltage, by simply adding up all measured cell voltages.

- The Protection subsystem provides a baseline or secondary level of hardware protections to better support a battery pack's FMEA requirements in the event of a loss of host control or simply if a host is unable to respond to a certain fault event in time. Integrated protections include pack-level faults such as OV, UV, OCD, SCD, detection of an external secondary protector fault, and internal logic "watchdog"-style device fault (XREADY). Protection events will trigger toggling of the ALERT pin, as well as automatic disabling of the DSG or CHG FET driver (depending on the fault). Recovery from a fault event must be handled by the host microcontroller.

- The Control subsystem implements a suite of useful pack features, including direct low-side NCH FET drivers, cell balancing drivers, the ALERT digital output, an external LDO and more.

The following sections describe each subsystem in greater detail, as well as explaining the various power states that are available.

#### 8.3.1.1 Measurement Subsystem Overview

The monitoring subsystem ensures that all cell voltages, temperatures, and pack current may be easily measured by the host. All ADCs are trimmed by TI.

ADC and CC data are always returned as atomic values if both high and low registers are read in the same transaction (using address auto-increment).

#### 8.3.1.1.1 Data Transfer to the Host Controller

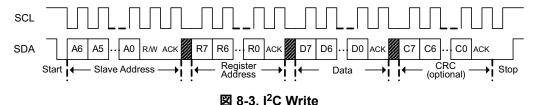

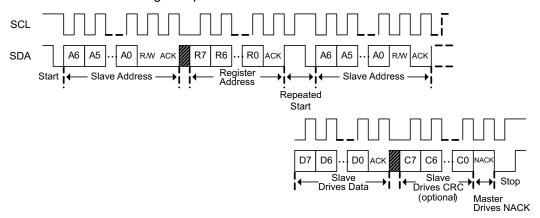

The BQ769x0 has a fully digital interface: All information is transferred through I<sup>2</sup>C, simply by reading and/or writing to the appropriate register(s) storing the relevant data. Block reads and writes, buffered by an 8-bit CRC code per byte, ensure a fast and robust transmission of data.

### 8.3.1.1.2 14-Bit ADC

Each BQ769x0 device measures cell voltages and temperatures using a 14-bit ADC. This ADC measures all differential cell voltages, thermistors and/or die temperature with a nominal full-scale unsigned range of 0–6.275 V and LSB of  $382 \,\mu\text{V}$ .

To enable the ADC, the <code>[ADC\_EN]</code> bit in the SYS\_CTRL1 register must be set. This bit is set automatically whenever the device enters NORMAL mode. When enabled, the ADC ensures that the integrated OV and UV protections are functional.

For each contiguous set of five cells (VC1 to VC5, VC6 to VC10), when no cells in that particular set are being balanced, each cell is measured over a 50-ms decimation window and a complete update is available every 250 ms. In the BQ76930 and BQ76940, every set of five cells above the primary five cells is measured in parallel. The 50-ms decimation greatly assists with removing the aliasing effects present in a noisy motor environment.

When any cells in a contiguous set of 5 cells are being balanced, those affected cells are measured in a reduced 12.5-ms decimation period, to allow the cell balancing to function properly without affecting the integrated OV and UV protections. Since cell balancing is typically only performed during pack charge or idle periods, the

shortened decimation periods should not impact accuracy as the system noise during these times is greatly reduced. This reduced decimation period is only applied to sets where one of the cells is being balanced. The following summarizes this for the BQ76920–BQ76940 devices:

- VC1 to VC5 measurements are each taken in a 50-ms decimation period when all bits in CELLBAL1 register are 0, and a 12.5-ms decimation period when any bits in CELLBAL1 register are 1.

- VC6 to VC10 measurements are each taken in a 50-ms decimation period when all bits in CELLBAL2 register are 0, and a 12.5-ms decimation period when any bits in CELLBAL2 register are 1.

- VC11 to VC15 measurements are each taken in a 50-ms decimation period when all bits in CELLBAL3

register are 0, and a 12.5-ms decimation period when any bits in CELLBAL3 register are 1.

- Total update interval is 250 ms.

Each differential cell input is factory-trimmed for gain or offset, such that the resulting reading through I<sup>2</sup>C is always consistent from part-to-part and requires no additional calibration or correction factor application.

The ADC is required to be enabled in order for the integrated OV and UV protections to be operating.

The following shows how to convert the 14-bit ADC reading into an analog voltage. Each device is factory calibrated, with a GAIN and OFFSET stored into EEPROM.

The ADC transfer function is a linear equation defined as follows:

(1)

GAIN is stored in units of  $\mu V/LSB$ , while OFFSET is stored in mV units.