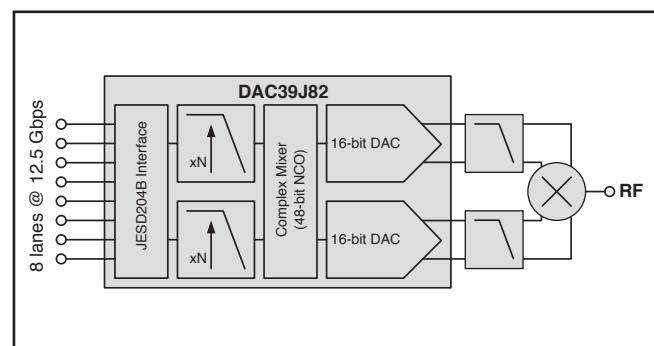

# DAC39J82デュアル・チャネル、16ビット、2.8GSPS、 デジタル/アナログ・コンバータ 12.5Gbps JESD204Bインターフェイス搭載

## 1. 特 長

- 分解能：16ビット

- 最大サンプル・レート：2.8GSPS

- 最大入力データ・レート：1.4GSPS

- JESD204Bインターフェイス

- 8つのJESD204Bシリアル入力レーン

- レーンごとに最大12.5Gbpsのビット・レート

- サブクラス1のマルチDAC同期

- オンチップの超低ジッタPLL

- 1x～16xの補間を選択可能

- 48ビットNCO/または $\pm n \times F_s/8$ の、独立の複合ミキサー

- 広帯域デジタル直交変調器補正

- $S_{in}/x$ 補正フィルタ

- フラクショナル・サンプル・グループ遅延の補正

- 出力マルチプレクサによる、4つのアナログ出力への柔軟なルーティング

- 3/4線のシリアル制御バス(SPI)

- 組み込みの温度センサ

- JTAG境界スキャナー

- クワッド・チャネルのDAC39J84とピン互換

- 消費電力：2.8GSPSにおいて1.1W

- パッケージ：10 × 10mm、144ボールのフリップ・チップBGA

## 2. アプリケーション

- 携帯基地局

- ダイバーシティ送信

- 広帯域通信

- 直接デジタル合成(DDS)計測器

- ミリメートル/マイクロ波のバックホール

- 自動テスト機器

- ケーブル・インフラストラクチャ

- レーダー

## 3. 概 要

DAC39J82は、非常に低消費電力でJESD204Bインターフェイスを搭載した16ビット、デュアル・チャネル、2.8GSPSのデジタル/アナログ・コンバータ(DAC)です。最大入力データ・レートは1.4GSPSです。

デジタル・データは1、2、4、8本の構成可能なシリアルJESD204Bレーンでデバイスへ入力され、それぞれが最大12.5Gbpsで動作し、オンチップのターミネーションとプログラマブルなイコライゼーションが搭載されています。このインターフェイスにより、JESD204Bはサブクラス1のSYSREFベースの調整可能なレイテンシと、複数デバイスの完全な同期を実現しています。

このデバイスには、複雑な転送アーキテクチャの設計を簡素化

### デバイス情報<sup>(1)</sup>

| 部品番号     | パッケージ       | 本体サイズ(公称)           |

|----------|-------------|---------------------|

| DAC39J82 | FCBGA (144) | 10.00 mm x 10.00 mm |

(1) 利用可能なすべてのパッケージについては、データシートの最後にある注文可能製品についての付録を参照してください。

するための機能が組み込まれています。完全にバイパス可能な、90dBを超えるストップ・バンド減衰を持つ2x~16xのデジタル補間フィルタにより、データ・インターフェイスとフィルタを簡素化できます。オンチップの48ビット数値制御発振器(NCO)および独立の複合ミキサーにより、柔軟かつ正確なキャリアの配置が可能です。

高パフォーマンスで低ジッタのPLLにより、デバイスのダイナミック・レンジに大きな影響を及ぼすことなく、クロック設定を簡素化できます。デジタル直交変調器補正(QMC)および

グループ遅延補正(QDC)により、直接の昇圧変換アプリケーションにおいて、チャネル間のゲイン、オフセット、位相、およびグループ遅延の完全なIQ補償が可能になります。入力データに異常な電力動作が検出された場合にパワーアンプ(PA)を保護するため、プログラマブルなPA保護機構が利用可能です。

DAC39J82には4つのアナログ出力があり、内部にある2つのデジタル・パスからのデータは、出力マルチプレクサ経由で、これら4つのDAC出力のうち任意の2つヘルーティングできます。

(SLASE47)

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins    | Package qty   Carrier      | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-------------------|----------------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| DAC39J82IAAV          | Active        | Production           | FCCSP (AAV)   144 | 168   JEDEC<br>TRAY (10+1) | Yes         | SNAGCU                               | Level-3-260C-168 HR               | -40 to 85    | DAC39J82I           |

| DAC39J82IAAVR         | Active        | Production           | FCCSP (AAV)   144 | 1000   LARGE T&R           | Yes         | SNAGCU                               | Level-3-260C-168 HR               | -40 to 85    | DAC39J82I           |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

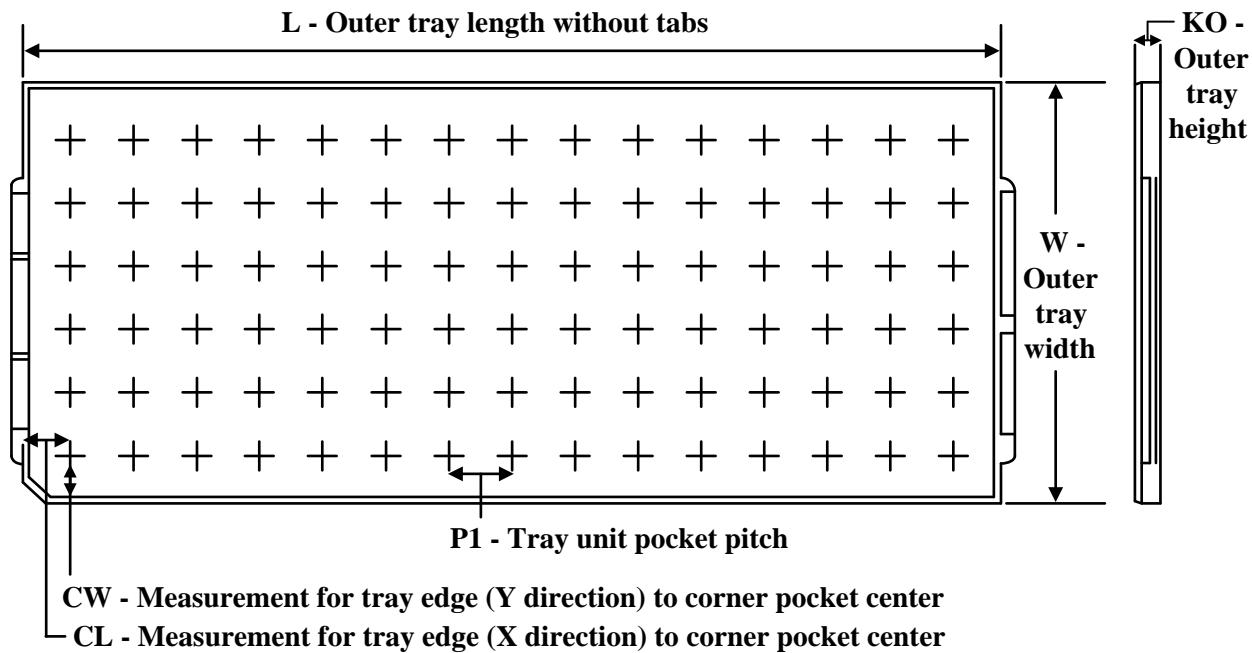

**TRAY**

Chamfer on Tray corner indicates Pin 1 orientation of packed units.

\*All dimensions are nominal

| Device       | Package Name | Package Type | Pins | SPQ | Unit array matrix | Max temperature (°C) | L (mm) | W (mm) | K0 (µm) | P1 (mm) | CL (mm) | CW (mm) |

|--------------|--------------|--------------|------|-----|-------------------|----------------------|--------|--------|---------|---------|---------|---------|

| DAC39J82IAAV | AAV          | FCCSP        | 144  | 168 | 8 X 21            | 150                  | 315    | 135.9  | 7620    | 14.65   | 11      | 11.95   |

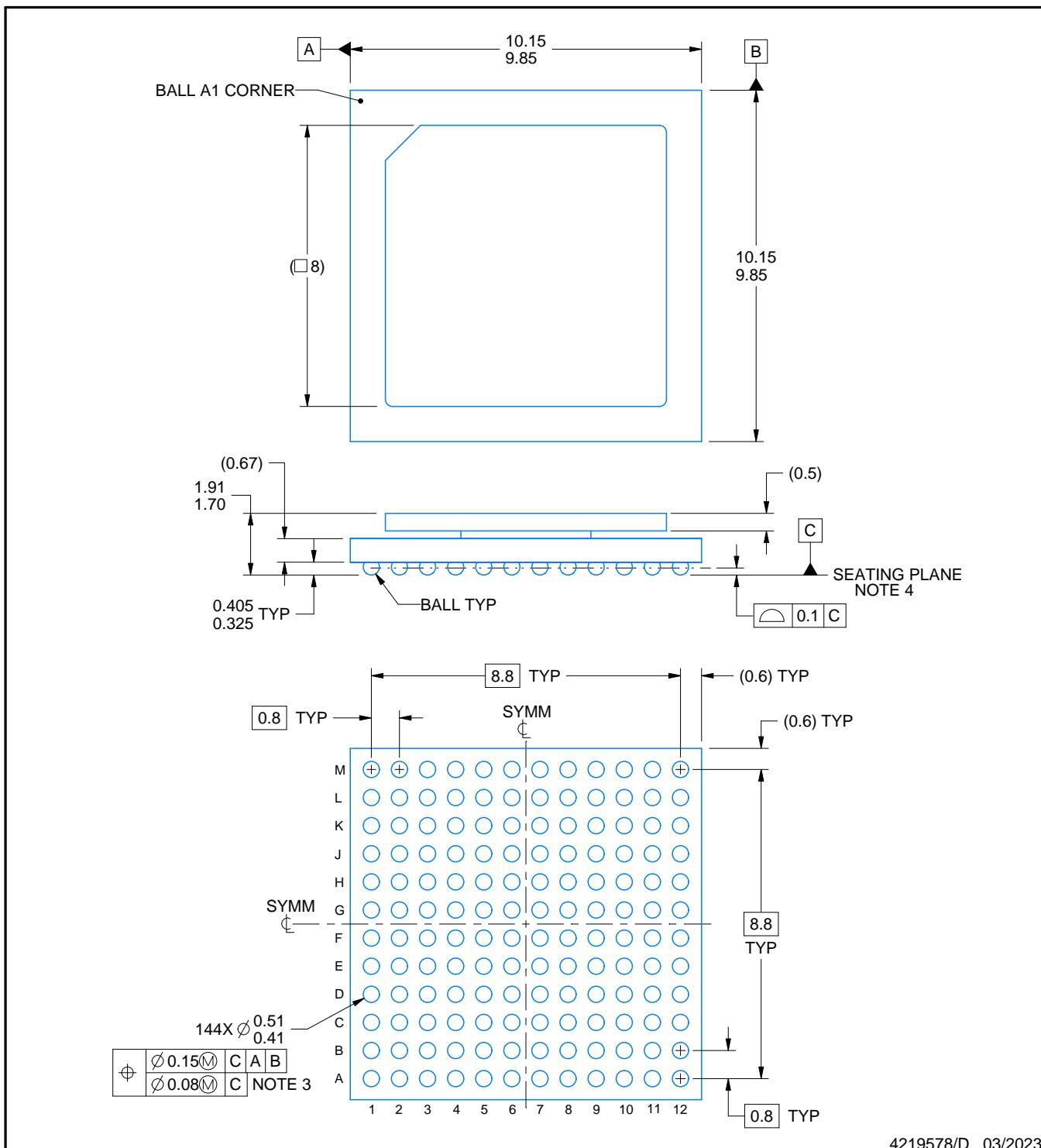

# PACKAGE OUTLINE

AAV0144A

FCBGA - 1.91 mm max height

BALL GRID ARRAY

4219578/D 03/2023

## NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. Dimension is measured at the maximum solder ball diameter, parallel to primary datum C.

4. Primary datum C and seating plane are defined by the spherical crowns of the solder balls.

5. The lids are electrically floating (e.g. not tied to GND).

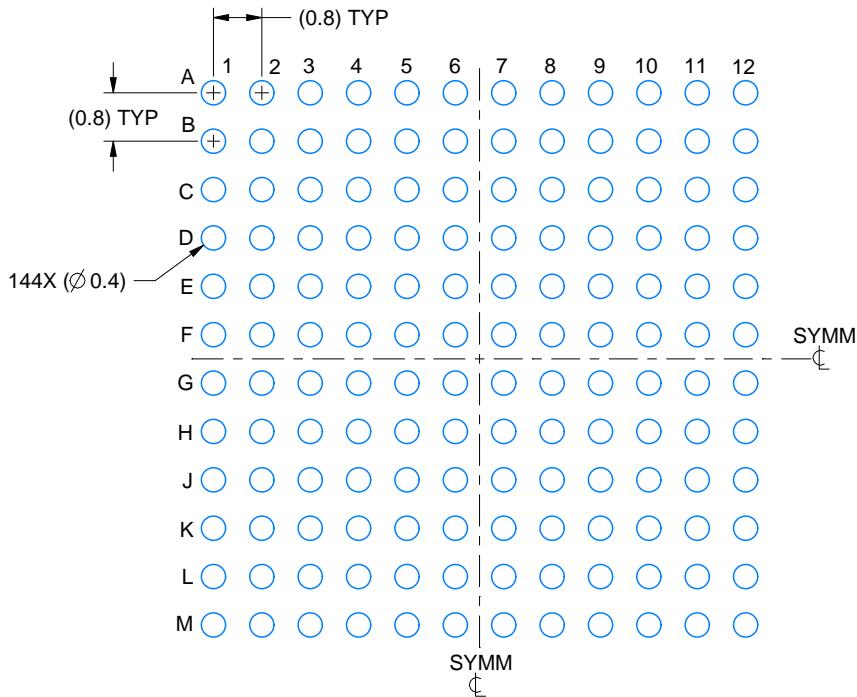

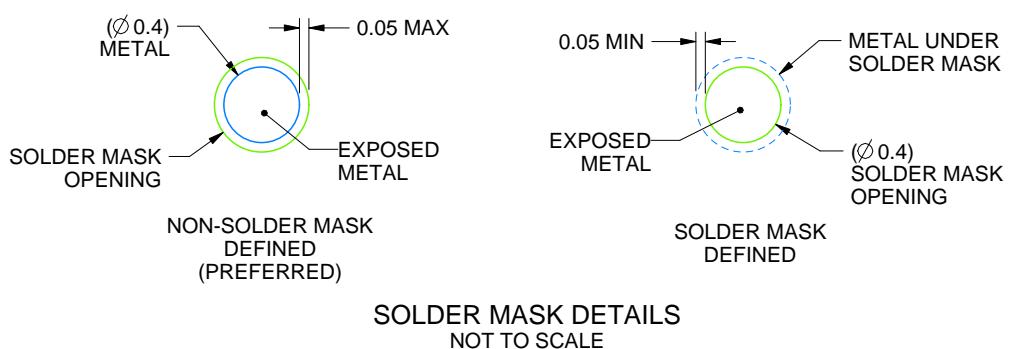

# EXAMPLE BOARD LAYOUT

AAV0144A

FCBGA - 1.91 mm max height

BALL GRID ARRAY

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE:8X

4219578/D 03/2023

NOTES: (continued)

- Final dimensions may vary due to manufacturing tolerance considerations and also routing constraints.

For more information, see Texas Instruments literature number SPRU811 ([www.ti.com/lit/spru811](http://www.ti.com/lit/spru811)).

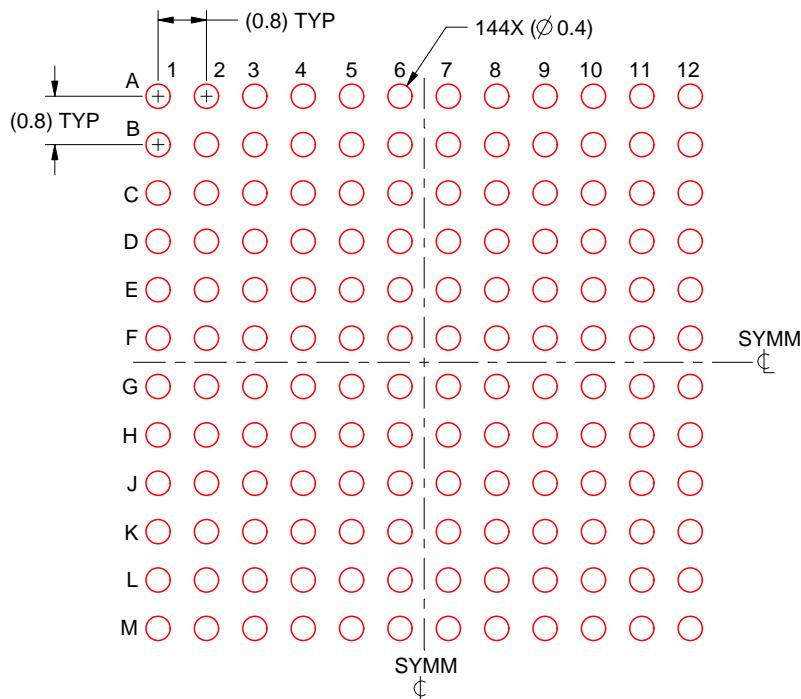

# EXAMPLE STENCIL DESIGN

AAV0144A

FCBGA - 1.91 mm max height

BALL GRID ARRAY

SOLDER PASTE EXAMPLE

BASED ON 0.15 mm THICK STENCIL

SCALE:8X

4219578/D 03/2023

NOTES: (continued)

7. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release.

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月